## MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102012902112817 |

|------------------------------|-----------------|

| Data Deposito                | 20/12/2012      |

| Data Pubblicazione           | 20/06/2014      |

Classifiche IPC

Titolo

CIRCUITO E METODO DI COMPENSAZIONE DINAMICA DELL'OFFSET PER UN DISPOSITIVO SENSORE MEMS

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"CIRCUITO E METODO DI COMPENSAZIONE DINAMICA DELL'OFFSET PER UN DISPOSITIVO SENSORE MEMS"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

Inventori: SPINELLA Giuseppe, DEPASCALIS Daniele, SAPIENZA Marco Vito, CERAVOLO Maria, MILUZZI Eugenio

\* \* \*

La presente invenzione è relativa ad un circuito e ad un metodo di compensazione dinamica dell'offset in un dispositivo sensore MEMS.

Sono noti dispositivi sensori includenti strutture micromeccaniche realizzate, almeno in parte, con materiali semiconduttori e con la tecnologia dei MEMS (Micro Electro Mechanical Systems).

Tali dispositivi sensori vengono integrati in apparecchi elettronici portatili, quali ad esempio computer portatili, laptop o ultrabook, PDA, tablet, telefoni cellulari, smartphone, riproduttori di audio digitale, foto- o videocamere, consolle per videogames, consentendo di ottenere importanti vantaggi per quanto riguarda l'occupazione di spazio, in termini di area e spessore.

Tali dispositivi sensori comprendono generalmente: una struttura sensibile micromeccanica, atta a trasdurre una grandezza meccanica da rilevare (ad esempio, accelerazione lineare o angolare, una pressione, un insieme di onde acustiche, ecc.) in una grandezza elettrica (ad una variazione capacitiva); ed esempio un circuito elettronico di lettura, atto ad effettuare opportune operazioni di elaborazione (tra cui operazioni amplificazione e filtraggio) di tale grandezza elettrica in modo da fornire un segnale elettrico di uscita, analogico (ad esempio una tensione elettrica), o digitale (ad esempio un segnale PDM, Pulse Density Modulation, in modulazione a densità di impulsi).

Tale segnale elettrico, eventualmente elaborato ulteriormente da un circuito elettronico di interfaccia, viene quindi reso disponibile per un sistema elettronico esterno, ad esempio un circuito di controllo a microprocessore di un apparecchio elettronico incorporante il dispositivo sensore.

La struttura sensibile micromeccanica comprende in generale una o più parti mobili, in grado di deformarsi o eseguire uno o più movimenti di rilevamento in presenza di corrispondenti grandezze meccaniche da rilevare.

Nel caso di strutture di rilevamento capacitive, alla parte mobile sono associati in modo solidale primi

elettrodi, disposti affacciati a secondi elettrodi, fissi, per realizzare i piatti di un elemento condensatore di rilevamento, la cui capacità risulta variabile in funzione della grandezza da rilevare.

modo noto, al segnale utile in uscita dal dispositivo sensore si sovrappone un segnale di offset (ovvero una deviazione rispetto al segnale utile), con un contributo in frequenza in continua, il cui valore dipende dal processo di fabbricazione utilizzato ed inoltre dagli stress e dalle sollecitazioni termiche e meccaniche a cui dispositivo sensore è sottoposto il durante i 1 funzionamento operativo. Tali sollecitazioni sono ad esempio indotte attraverso il contenitore (package) dello stesso dispositivo sensore, in particolare a causa dei differenti coefficienti di espansione termica dei vari materiali utilizzati.

Nel caso peggiore, il valore del segnale di offset può portare il circuito elettronico di lettura a lavorare al di fuori della dinamica per cui è progettato, causando errori, ad esempio la sua saturazione, o l'impossibilità di misurare le grandezze meccaniche da rilevare.

Sono state dunque proposte soluzioni per la compensazione e la cancellazione dell'offset, che prevedono in particolare una regolazione ("trimming") di opportuni parametri circuitali ed elementi elettrici, ad esempio

resistori o condensatori variabili e regolabili, al termine del processo di fabbricazione della struttura sensibile micromeccanica.

Tali soluzioni prevedono ad esempio l'impiego di una struttura di compensazione dell'offset all'ingresso del circuito elettronico di lettura, atta a generare uno sbilanciamento uguale e contrario a quello generato dall'offset dovuto alla struttura sensibile micromeccanica, in modo tale da compensarne, idealmente annullarne, gli effetti. Ad esempio, nel caso di una struttura sensibile micromeccanica di tipo capacitivo, questo sbilanciamento può essere costituito da una variazione di carica iniettata all'ingresso del circuito elettronico di lettura.

Queste soluzioni non consentono tuttavia la compensazione di una variazione nel tempo dell'offset, che si verifichi durante l'utilizzo del dispositivo sensore, ad esempio a causa dei possibili stress termici e meccanici a cui è sottoposto.

A questo riguardo, la sempre più spinta richiesta di riduzione delle dimensioni dei dispositivi sensori MEMS comporta una corrispondente riduzione del valore delle grandezze elettriche rilevate (che possono ad esempio arrivare nell'ordine di alcune decine di aF, nel caso di strutture sensibili capacitive).

Di consequenza, le suddette variazioni di offset

possono risultare confrontabili, se non addirittura superiori, rispetto al segnale elettrico utile, rendendo di fatto difficoltosa, se non impossibile, l'esecuzione delle misure e delle operazioni di rilevamento.

In altre parole, il problema dell'offset risulta sempre più critico al diminuire delle dimensioni dei dispositivi sensori MEMS, dato che tale riduzione delle dimensioni comporta un incremento della sensibilità agli stress ed una diminuzione del guadagno di trasduzione e quindi del segnale elettrico rilevato.

Scopo della presente invenzione è quello di fornire una soluzione che consenta di risolvere, almeno in parte, il problema dell'offset in condizione dinamica, ovvero durante il funzionamento dei dispositivi sensori MEMS.

Secondo la presente invenzione vengono pertanto forniti un circuito ed un metodo di compensazione dell'offset, come definiti nelle rivendicazioni allegate.

Per una migliore comprensione della presente invenzione, ne vengono ora descritte forme di realizzazione preferite, a puro titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

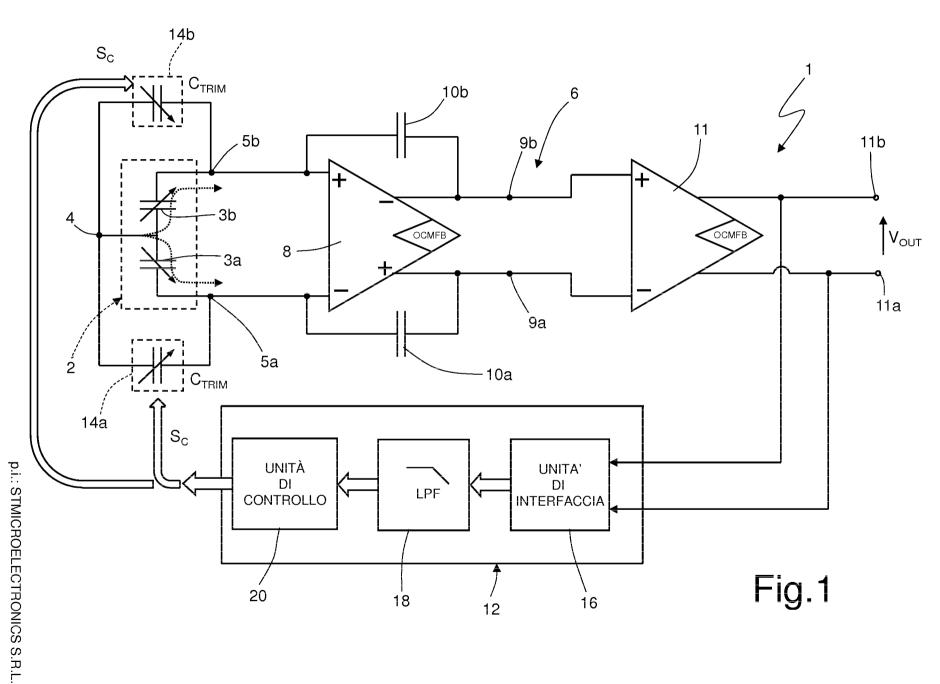

- la figura 1 è un diagramma circuitale schematico di un dispositivo sensore MEMS, dotato di un circuito di compensazione dell'offset, secondo la presente soluzione;

- la figura 2 è un diagramma circuitale più dettagliato, che mostra una forma di realizzazione del circuito di compensazione dell'offset;

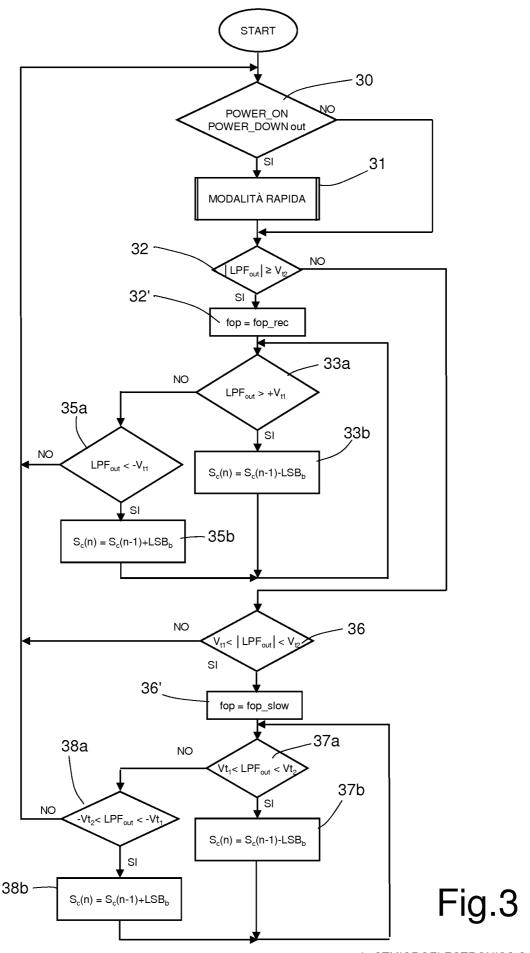

- le figure 3 e 4 sono diagrammi di flusso relativi ad un metodo di compensazione dell'offset implementato nel circuito di figura 2;

- le figure 5 e 6 mostrano grafici di grandezze elettriche relative al circuito ed al metodo di compensazione dell'offset; e

- la figura 7 mostra uno schema a blocchi di massima di un apparecchio elettronico portatile dotato del dispositivo sensore MEMS.

La figura 1 mostra un dispositivo sensore MEMS 1, comprendente una struttura micromeccanica di rilevamento 2, nell'esempio di tipo capacitivo, di cui viene mostrato lo schema elettrico equivalente, costituito da un primo e da un secondo condensatore di rilevamento 3a, 3b, aventi capacità variabile in modo opposto in funzione di una grandezza da rilevare, ad esempio una accelerazione lineare.

Il primo ed il secondo condensatore di rilevamento 3a, 3b presentano un primo terminale 4, in comune, in particolare un terminale mobile, cosiddetto di rotore, a cui sono collegate elettricamente le armature mobili degli stessi condensatori, ed un rispettivo terminale fisso

(meccanicamente vincolato) 5a, 5b, in particolare un terminale cosiddetto di statore, a cui sono collegate elettricamente le rispettive armature fisse.

Il dispositivo sensore MEMS 1 comprende inoltre un circuito elettronico di lettura 6, in particolare realizzato in maniera integrata con le tecnologie dei semiconduttori, ovvero un circuito ASIC (Application Specific Integrated Circuit).

La struttura micromeccanica di rilevamento 2 ed il circuito elettronico di lettura 6 possono essere ad esempio integrati, ciascuno, in una rispettiva piastrina (die) di materiale semiconduttore, ad esempio includente silicio, ed essere alloggiati in uno stesso contenitore (package), che ne costituisce il rivestimento e ne definisce i contatti elettrici verso l'esterno. In alternativa, la struttura micromeccanica di rilevamento 2 ed il circuito elettronico di lettura 6 possono essere integrati in una stessa piastrina di materiale semiconduttore.

Il circuito elettronico di lettura 6 comprende uno stadio amplificatore di carica 8, in configurazione completamente differenziale ("fully differential") con stadio di retroazione di modo comune di uscita (OCMFB - Output Common Mode Feedback), avente terminale di ingresso invertente collegato al terminale fisso 5a del primo condensatore di rilevamento 3a, e terminale di ingresso non

invertente collegato al terminale fisso 5b del secondo condensatore di rilevamento 3b.

Lo stadio amplificatore di carica 8 presenta inoltre una prima uscita 9a ed una seconda uscita 9b, ed un primo condensatore di amplificazione 10a, collegato tra la prima uscita 9a ed il terminale di ingresso invertente, ed un secondo condensatore di amplificazione 10b, collegato tra la seconda uscita 9b ed il terminale di ingresso non invertente dello stesso stadio amplificatore di carica 8.

Il circuito elettronico di lettura 6 comprende inoltre uno stadio di amplificazione 11, includente un amplificatore completamente differenziale, anch'esso dotato di uno stadio OCMFB di retroazione di modo comune di uscita, avente terminale di ingresso invertente collegato alla prima uscita 9a, e terminale di ingresso non invertente collegato alla seconda uscita 9b, dello stadio amplificatore di carica 8.

Lo stadio di amplificazione 11 presenta inoltre una rispettiva prima uscita 11a ed una rispettiva seconda uscita 11b, tra cui fornisce un segnale di uscita  $V_{\rm out}$ , ad esempio una tensione elettrica, avente valore indicativo della grandezza da rilevare.

Il circuito elettronico di lettura 6 comprende inoltre uno stadio di compensazione dell'offset 12 (in particolare, realizzato in maniera integrata, nella stessa piastrina,

con il circuito elettronico di lettura 6), collegato in retroazione tra la prima e la seconda uscita 11a, 11b dello stadio di amplificazione 11 ed i terminali invertente e non invertente dello stadio amplificatore di carica 8.

Lo stadio di compensazione dell'offset 12 comprende elementi di regolazione 14a, 14b, collegati ai terminali invertente e non invertente dello stadio amplificatore di carica 8, e configurati in modo tale da generare sugli stessi terminali invertente e non invertente una grandezza di sbilanciamento, idealmente uguale e contraria a quella generata dall'offset, in modo tale da compensarne ed idealmente annullarne gli effetti.

Ad esempio, nel caso illustrato, in cui la struttura micromeccanica di rilevamento 2 è di tipo capacitivo, questo sbilanciamento è costituito da una variazione di carica iniettata all'ingresso del circuito elettronico di lettura 6, e gli elementi di regolazione 14a, 14b includono un rispettivo condensatore con capacità regolabile, cosiddetto "captrim" (termine che deriva da: "trimmable capacitor").

Ciascun condensatore regolabile 14a, 14b presenta: un primo ed un secondo terminale, tra cui fornisce una capacità variabile  $C_{\text{TRIM}}$  di valore selezionabile; ed un terminale di controllo, su cui riceve un segnale di controllo  $S_{\text{c}}$ , ad esempio di tipo digitale, che determina il

valore della suddetta capacità variabile  $C_{\text{TRIM}}$ . Il primo ed il secondo condensatore regolabile 14a, 14b sono atti a generare, in funzione della rispettiva capacità variabile  $C_{\text{TRIM}}$ , rispettivamente una prima ed una seconda grandezza di compensazione, in questo caso costituite da variazioni di una carica iniettata ad un rispettivo ingresso dello stadio amplificatore di carica 8.

In maggiore dettaglio, un primo terminale di ciascun condensatore regolabile 14a, 14b è collegato al terminale mobile 4 della struttura micromeccanica di rilevamento 2; mentre il secondo terminale del primo e del secondo condensatore regolabile 14a, 14b è collegato rispettivamente al terminale invertente ed al terminale non invertente dello stadio amplificatore di carica 8.

Lo stadio di compensazione dell'offset 12 comprende inoltre, collegati in cascata tra le uscite 11a, 11b dello stadio di amplificazione 11 ed i terminali di controllo degli elementi di regolazione 14a, 14b: un'unità di interfaccia 16, ricevente il segnale di uscita Vout; un'unità di filtraggio passa-basso (LPF - Low Pass Filter) 18, ricevente il segnale di uscita Vout, eventualmente preelaborato dall'unità di interfaccia 16, e ne estrae le componenti in bassa o bassissima frequenza, idealmente la sola componente in continua (DC - Direct Current), dovuta alla presenza dell'offset ed indicativa del valore dello

stesso offset in uscita; ed un'unità di controllo 20, ricevente l'uscita dell'unità di filtraggio passa-basso 18 e generante il segnale di controllo  $S_c$ , in funzione del valore della componente in bassa frequenza (rappresentativo dell'offset agente sul dispositivo sensore MEMS 1).

Secondo un aspetto della presente soluzione, l'unità di controllo 20 implementa un algoritmo di controllo e compensazione continua dell'offset presente sul segnale di uscita V<sub>out</sub>, andando a generare, mediante i condensatori regolabili 14a, 14b un opportuno sbilanciamento all'ingresso del circuito elettronico di lettura 6, che è funzione del valore dello stesso offset presente in uscita. In tal modo, risulta possibile compensare in modo dinamico variazioni dell'offset che si verificano durante l'utilizzo del dispositivo sensore MEMS 1, ad esempio a causa di stress termici e/o meccanici.

In particolare, l'unità di controllo 20 è configurata per implementare un controllo di soglia, ovvero per confrontare il valore dell'offset estratto dal segnale di uscita V<sub>out</sub> con uno o più valori di soglia di riferimento, indicativi di un valore di offset desiderato e consentito sull'uscita (ad esempio, un valore tale per cui lo stesso segnale di uscita V<sub>out</sub> non esca dalla dinamica consentita), e per generare il segnale di controllo S<sub>c</sub> per i condensatori regolabili 14a, 14b, in funzione del risultato

del confronto (in tal modo adattando l'entità della regolazione in base alla distanza del valore dell'offset presente in uscita dal valore desiderato di riferimento).

In figura 2 viene mostrata in maggiore dettaglio una possibile forma di realizzazione dell'unità di controllo 20; in tale forma di realizzazione, l'unità di filtraggio passa-basso 18 è configurata in modo da avere frequenza di taglio regolabile in funzione di un segnale di controllo  $S_{t}$ , ad esempio nell'intervallo di valori compreso tra 0,1Hz e 3kHz.

In generale, in questa forma di realizzazione, l'unità di controllo 20 opera in modo tale da implementare un algoritmo di compensazione adattativa dell'offset, controllando la frequenza di taglio dell'unità di filtraggio passa-basso 18, per ottenere di volta in volta il migliore compromesso tra la velocità dell'operazione di compensazione dell'offset e l'accuratezza della stessa operazione di compensazione.

Nel caso in cui l'errore in continua, o distanza, tra il valore dell'offset in uscita ed il valore desiderato di riferimento sia elevato, l'algoritmo prevede l'implementazione di una correzione rapida mediante la selezione di un valore più elevato della frequenza di taglio dell'unità di filtraggio passa-basso 18, a scapito dell'accuratezza e dell'errore residuo, risultante dalla

stessa operazione di compensazione. Al contrario, nel caso in cui l'errore tra il valore dell'offset in uscita ed il valore desiderato di riferimento sia ridotto, l'algoritmo prevede l'implementazione di una correzione più lenta, mediante la selezione di un valore minore della frequenza di taglio dell'unità di filtraggio passa-basso 18, ottenendo in tal modo una maggiore accuratezza ed un minore errore residuo.

In dettaglio, l'unità di controllo 20 comprende in tal caso un modulo rilevatore di soglia 22, che riceve in ingresso il segnale di uscita filtrato dall'unità di filtraggio passa-basso 18, indicato con LPF $_{\rm out}$ , ed è configurato per confrontare tale segnale con una pluralità di valori di soglia di valore prefissato, ed in particolare con un primo valore di soglia  $V_{t1}$  e con un secondo valore di soglia  $V_{t2}$ , entrambi indicativi di valori di offset di riferimento, con  $V_{t2}$  >  $V_{t1}$  > 0; il modulo rilevatore di soglia 22 fornisce in uscita uno o più segnali di confronto, indicativi del risultato del confronto.

L'unità di controllo 20 comprende inoltre un modulo convertitore ADC 24 ed un modulo di elaborazione 26.

Il modulo convertitore ADC 24 riceve anch'esso il segnale di uscita filtrato LPF $_{\rm out}$  dall'unità di filtraggio passa-basso 18, indicativo del valore di offset sul segnale di uscita  $V_{\rm out}$ , ed è configurato in modo da effettuarne la

conversione da analogico a digitale, ad esempio fornendo un segnale digitale convertito  $ADC_{\text{out}}$  con un numero di bit pari a quattro.

Il modulo di elaborazione 26, di tipo digitale, riceve in ingresso sia il segnale di confronto dal modulo rilevatore di soglia 22, sia il segnale digitale convertito  $ADC_{out}$  fornito dal modulo convertitore ADC 24, ed in funzione di tali segnali genera il segnale di controllo  $S_c$  per gli elementi di regolazione 14a, 14b, in modo tale da implementare la compensazione dell'offset in uscita; il segnale di controllo  $S_c$  è ad esempio un segnale digitale a 12 bit:  $S_c[b_0, b_1, ..., b_{11}]$ .

In particolare, il modulo di elaborazione 26 è configurato in modo da implementare tre differenti modalità di compensazione, a seconda della condizione operativa rilevata:

- una modalità di compensazione rapida, che viene eseguita all'accensione (Power-On) o all'uscita dalla modalità di Power-Down (o stand-by) del dispositivo sensore MEMS 1, e che consiste in una rapida azione di correzione per riportare il circuito all'interno della dinamica consentita, con una elevata frequenza di taglio dell'unità di filtraggio passa-basso 18, ad esempio pari a 100 Hz; come sarà descritto in dettaglio in seguito, la modalità di compensazione rapida viene eseguita ad una elevata

frequenza operativa  $f_{op}$ , ad esempio pari a 300 Hz, ed implementa una ricerca binaria che coinvolge i bit del segnale di controllo  $S_c$ , con un errore residuo finale dovuto al modulo convertitore ADC 24, pari a  $LSB_a/2$  (dove  $LSB_a$  indica il bit meno significativo - Least Significant Bit - dello stesso modulo convertitore ADC 24);

- una modalità di compensazione di recupero ("recovery"), di tipo veloce, con una frequenza di taglio dell'unità di filtraggio passa-basso 18, ad esempio pari a 50 Hz, inferiore rispetto alla modalità di compensazione rapida, che viene eseguita quando il segnale di uscita filtrato LPFout è maggiore, in valore assoluto, del secondo valore di soglia  $V_{t2}$ ; come sarà descritto in dettaglio in seguito, la modalità di compensazione di recupero viene eseguita a passi iterativi ad una frequenza operativa  $f_{op}$ , minore rispetto alla modalità di compensazione rapida, ad esempio pari a 150 Hz, di volta in volta variando il valore del segnale di uscita filtrato LPF out di una variazione incrementale pari al valore del bit meno significativo (indicato con LSB<sub>b</sub>) del segnale di controllo  $S_{c}$ , con un errore residuo che è pari a  $\pm V_{t1}$ ; ed

- una modalità di compensazione lenta, con una frequenza di taglio dell'unità di filtraggio passa-basso 18 ridotta, ad esempio pari a 0,5 Hz, che viene eseguita quando il segnale di uscita filtrato  $LPF_{out}$  è compreso, in

valore assoluto, tra il primo ed il secondo valore di soglia  $V_{t1}$ ,  $V_{t2}$ ; come sarà descritto in dettaglio in seguito, la modalità di compensazione lenta viene eseguita a passi iterativi ad una frequenza operativa  $f_{op}$ , minore rispetto ad entrambe le modalità di compensazione precedenti, ad esempio pari a 1,5 Hz, di volta in volta variando il valore del segnale di uscita filtrato LPF $_{out}$  della variazione incrementale pari al valore del bit meno significativo (indicato con LSB $_{b}$ ) del segnale di controllo  $S_{c}$ , con un errore residuo che è nuovamente pari a  $\pm V_{t1}$ .

In maggiore dettaglio, e facendo riferimento alla figura 3, l'algoritmo di compensazione implementato dal modulo di elaborazione 26, ad esempio mediante l'esecuzione di opportune istruzioni software all'interno di un microprocessore, microcontrollore, o analoga unità di calcolo, prevede una prima fase 30, in cui si verifica se il dispositivo sensore MEMS 1 è in una condizione operativa di "Power-on" o di uscita dalla condizione di "Power-Down" o stand-by (condizione indicata come "Power-Down out").

Nel caso in cui tale verifica dia esito positivo, in una fase 31 viene eseguita la modalità di compensazione rapida, in funzione del segnale digitale convertito  $ADC_{out}$  in uscita dal modulo convertitore ADC 24.

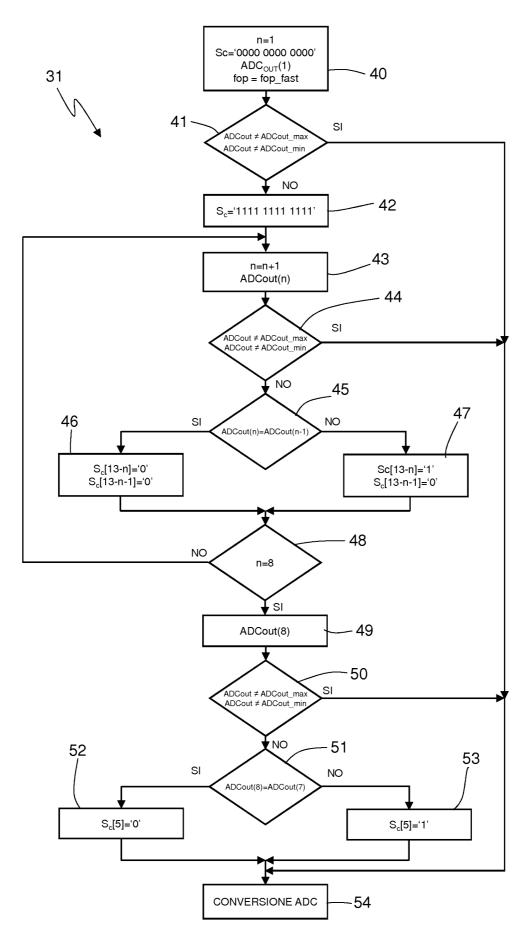

In una possibile forma di realizzazione, mostrata in figura 4, la modalità di compensazione rapida viene

eseguita in un certo numero di passi di elaborazione iterativa, ad esempio pari a nove, eseguiti alla frequenza operativa  $f_{\text{op}}$  propria di tale modalità di compensazione.

In un primo passo, fase 40, viene inizializzato un contatore n, che viene posto pari a 1, e viene letto e memorizzato un primo valore  $ADC_{out}$  (1) del segnale digitale convertito  $ADC_{out}$ , in corrispondenza di un primo valore del segnale di controllo  $S_c$  '0000 0000 0000', con tutti i bit  $b_0-b_{11}$  pari a '0'. La frequenza operativa  $f_{op}$  viene inoltre impostata ad un valore desiderato  $f_{op\_fast}$ , ad esempio pari a 300 Hz.

Se il primo valore  $ADC_{out}(1)$ , fase 41, risulta diverso da un valore di uscita massimo  $ADC_{out\_max}$  o da un valore di uscita minimo  $ADC_{out\_min}$  consentiti dal modulo convertitore ADC 24, l'algoritmo prosegue verso una fase finale, descritta in seguito.

Altrimenti, fase 42, il valore del segnale di controllo  $S_c$  viene posto a '1111 1111 1111', con tutti i bit  $b_0-b_{11}$  pari a '1'.

Per i passi dell'algoritmo da 2 a 8, il valore del contatore n viene incrementato, fase 43, e viene letto e memorizzato un corrispondente valore  $ADC_{out}$  (n) del segnale digitale convertito  $ADC_{out}$ .

Nuovamente, se tale valore  $ADC_{out}(n)$ , fase 44, risulta diverso dal valore di uscita massimo  $ADC_{out\ max}$  o dal valore

di uscita minimo  $ADC_{out\_min}$ , l'algoritmo prosegue verso la sua fase finale.

Altrimenti, fase 45, se un valore corrente  $ADC_{out}(n)$  è uguale ad un valore precedente  $ADC_{out}(n-1)$  del segnale digitale convertito  $ADC_{out}$ , in una fase 46, i bit  $b_{13-n}$  e  $b_{13-n}$  del segnale di controllo  $S_c$  vengono posti a '0'.

Altrimenti, fase 47, il bit  $b_{13-n}$  del segnale di controllo  $S_c$  viene posto a '1', mentre il bit  $b_{13-n-1}$  dello stesso segnale di controllo  $S_c$  viene posto a '0'.

Una volta eseguito l'ultimo passo (n=8), come verificato nella fase 48, viene letto e memorizzato un valore corrente  $ADC_{out}(8)$  del segnale digitale convertito  $ADC_{out}$ , fase 49.

Nuovamente, se tale valore  $ADC_{out}(8)$ , fase 50, risulta diverso dal valore di uscita massimo  $ADC_{out\_max}$  o dal valore di uscita minimo  $ADC_{out\_min}$  consentiti dal modulo convertitore ADC 24, l'algoritmo prosegue verso la sua fase finale.

Altrimenti, fase 51, se il valore corrente  $ADC_{out}(8)$  del segnale digitale convertito  $ADC_{out}$  è uguale al valore precedente  $ADC_{out}(7)$ , in una fase 52, il bit  $b_5$  del segnale di controllo  $S_c$  viene posto a '0'.

Al contrario, ovvero se il valore corrente  $ADC_{out}(8)$  del segnale digitale convertito  $ADC_{out}$  non risulta uguale al valore precedente  $ADC_{out}(7)$ , il bit  $b_5$  del segnale di

controllo  $S_c$  viene posto a '1'.

Nella sua fase finale, fase 54 (a cui si giunge anche dalle suddette fasi 41, 44 e 50), l'algoritmo prevede la conversione finale da analogico a digitale del segnale di uscita filtrato LPF $_{\rm out}$ , per la generazione del corrispondente segnale di controllo  $S_{\rm c}$  per la compensazione dell'offset sul segnale di uscita  $V_{\rm out}$  con un errore residuo minore, in valore assoluto, della metà del valore del bit meno significativo LSB $_{\rm a}$  del modulo convertitore ADC 24.

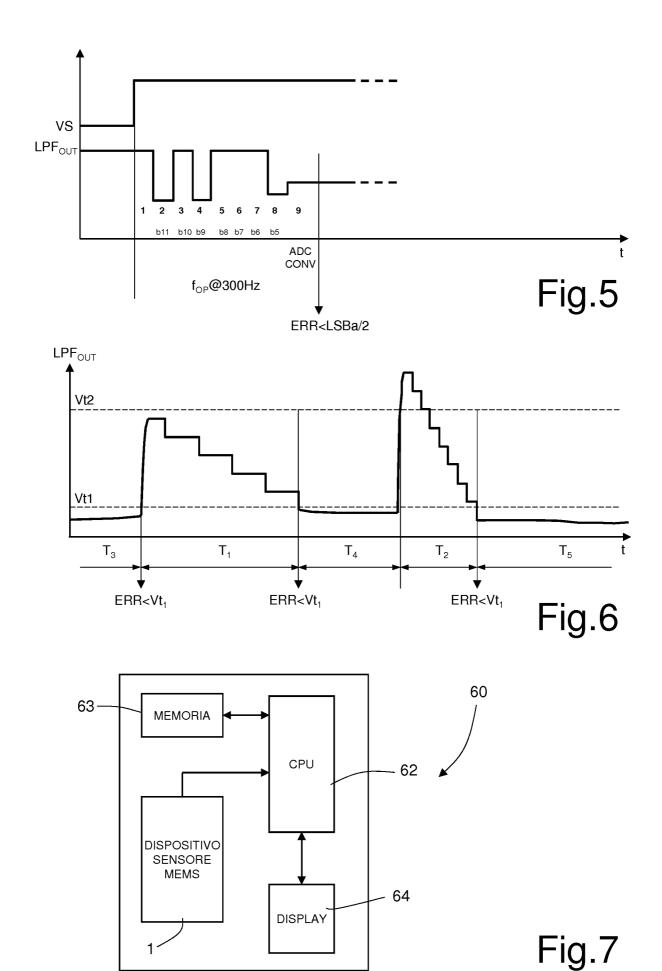

Il funzionamento dell'algoritmo precedentemente descritto è visualizzato in maniera esemplificativa in figura 5, in cui si mostra l'andamento del segnale di uscita filtrato LPFout durante la modalità di compensazione rapida, che viene attivata quando un segnale digitale VS commuta il suo valore (nell'esempio da basso a alto), indicando la condizione operativa di "Power-on" o di "Power-Down out". Nella stessa figura 5, si evidenziano i passi da 1 a 9 dell'algoritmo, ed inoltre i bit del segnale di controllo S<sub>c</sub> di volta in volta interessati dallo stesso algoritmo.

Tornando ora alla figura 3, l'algoritmo di compensazione implementato dal modulo di elaborazione 26 esegue la modalità di compensazione di recupero, qualora si verifichi, fase 32, che il segnale di uscita filtrato LPF<sub>out</sub> è maggiore o uguale, in valore assoluto, al secondo valore

di soglia  $V_{t2}$ .

La frequenza operativa  $f_{\text{op}}$  viene impostata ad un valore desiderato  $f_{\text{op\_rec}}$ , ad esempio pari a 150 Hz, fase 32'.

La stessa modalità operativa si interrompe, ritornando alla fase iniziale 30, quando si verifica la condizione:  $\left|\text{LPF}_{\text{out}}\right| \leq V_{\text{t1}}.$

Si noti che tali, ed analoghe, verifiche vengono effettuate dal modulo di elaborazione 26 in funzione del segnale di confronto fornito dal modulo rilevatore di soglia 22.

In tale modalità operativa di recupero, se il valore corrente del segnale di uscita filtrato  $LPF_{out}$  è maggiore del primo valore di soglia  $+V_{t1}$ , fase 33a:

$$LPF_{out} > +V_{t1}$$

il valore digitale attuale del segnale di controllo  $S_{\text{c}}$  viene decrementato di una quantità pari al valore del bit meno significativo LSB $_{\text{b}}$ , fase 33b:

$$S_c(n) = S_c(n-1) - LSB_b$$

.

Se invece il valore corrente del segnale di uscita filtrato LPF $_{\text{out}}$  è minore del primo valore di soglia, negato,  $-V_{\text{tl}}$ , fase 35a:

$$LPF_{OUT} < -V_{t1}$$

il valore digitale attuale del segnale di controllo  $S_{\text{c}}$  viene incrementato della stessa quantità pari al valore del

bit meno significativo LSBb, fase 35b:

$$S_c(n) = S_c(n-1) + LSB_b$$

.

Inoltre, l'algoritmo di compensazione implementato dal modulo di elaborazione 26 esegue la modalità di compensazione lenta, qualora si verifichi, fase 36, che il segnale di uscita filtrato  $LPF_{out}$  è, in valore assoluto, compreso tra il primo valore di soglia  $V_{t1}$  ed il secondo valore di soglia  $V_{t2}$ .

La frequenza operativa  $f_{\text{op}}$  viene impostata ad un valore desiderato  $f_{\text{op\_slow}}$ , ad esempio pari a 1,5 Hz, fase 36'.

La stessa modalità operativa si interrompe, ritornando alla fase iniziale 30, quando si verifica la condizione:  $\left|\text{LPF}_{\text{out}}\right| \leq V_{t1}.$

In tale modalità operativa lenta, se il valore corrente del segnale di uscita filtrato  $LPF_{out}$  è positivo e compreso tra il primo ed il secondo valore di soglia, fase 37a:

$$+V_{t1} < LPF_{out} < +V_{t2}$$

il valore digitale attuale del segnale di controllo  $S_c$  viene decrementato di una quantità pari al valore del bit meno significativo LSB<sub>b</sub>, fase 37b:  $S_c(n) = S_c(n-1)$ -LSB<sub>b</sub>.

Se invece il valore corrente del segnale di uscita filtrato  $LPF_{out}$  è negativo e compreso tra il secondo valore di soglia, negato,  $-V_{t2}$ , ed il primo valore di soglia,

negato,  $-V_{t1}$ , fase 38a:

$$-V_{t2} < LPF_{out} < -V_{t1}$$

il valore digitale attuale del segnale di controllo  $S_c$  viene incrementato della stessa quantità pari al valore del bit meno significativo  $LSB_b$ , fase 38b:

$$S_c(n) = S_c(n-1) + LSB_b$$

.

Il funzionamento dell'algoritmo precedentemente descritto, per quanto riguarda le modalità di compensazione di recupero e lenta, è visualizzato in maniera esemplificativa in figura 6, in cui si mostra l'andamento del segnale di uscita filtrato LPF<sub>out</sub> durante la modalità di compensazione lenta, durante un primo intervallo temporale T1, e durante la modalità di compensazione di recupero, durante un secondo intervallo temporale T2.

Nella stessa figura 6, si evidenziano inoltre, nuovamente a titolo di esempio, intervalli temporali T3, T4 e T5, corrispondenti ad una modalità operativa normale, in cui l'algoritmo di compensazione non interviene per modificare il valore del segnale di controllo  $S_{\rm c}$ , in quanto l'offset sul segnale di uscita  $V_{\rm out}$  presenta un valore desiderato o consentito; in particolare, il segnale di uscita filtrato LPF $_{\rm out}$ , indicativo di tale offset, e dunque l'errore risultante, è minore, in valore assoluto, del primo valore di soglia  $V_{\rm t1}$ .

I vantaggi della soluzione descritta emergono in

maniera evidente dalla discussione precedente.

In particolare, tale soluzione realizza una compensazione dinamica, continua nel tempo durante il funzionamento del dispositivo sensore MEMS 1, dell'offset presente in uscita, adattandosi tempestivamente ad eventuali variazioni delle condizioni operative e del valore dello stesso offset, ad esempio a causa di stress termici o meccanici.

La soluzione descritta risulta inoltre ampiamente adattabile a differenti condizioni di utilizzo, ad esempio mediante l'opportuna selezione del numero delle soglie, dei valori delle soglie stesse, o dell'intervallo di variabilità della frequenza di taglio dell'unità di filtraggio passa-basso 18.

I vantaggi suddetti risultano ancora più evidenti nel caso di dispositivi di ultima generazione, in cui le esigenze di miniaturizzazione e riduzione generale delle dimensioni rendono il problema dell'offset ancora più rilevante.

A questo riguardo, la figura 7 mostra schematicamente un apparecchio portatile 60, quale ad esempio uno smartphone di ultima generazione, in cui è integrato il dispositivo sensore MEMS 1, precedentemente descritto in dettaglio.

Ad esempio, il dispositivo sensore MEMS 1 rileva

un'accelerazione lineare agente sull'apparecchio portatile 60, durante il suo funzionamento.

L'apparecchio portatile 60 comprende una CPU (Central Unit) 62, collegata Processing operativamente al dispositivo sensore MEMS 1, per ricevere il segnale uscita V<sub>out</sub> ed implementare opportune azioni in funzione del valore dello stesso segnale; la CPU 62 coopera operativamente con una memoria 63, di tipo non volatile.

Ad esempio, la CPU 62 può intervenire su una modalità di visualizzazione corrente di un display 64 dell'apparecchio portatile 62, o attivare determinate funzioni dello stesso apparecchio portatile 62.

Risulta infine chiaro che a quanto qui descritto ed illustrato possono essere apportate modifiche e varianti senza per questo uscire dall'ambito di protezione della presente invenzione, come definito nelle rivendicazioni allegate.

In particolare, è evidente che la soluzione descritta può essere applicata per qualsiasi tipologia di struttura micromeccanica di rilevamento (anche differente dalla struttura capacitiva precedentemente descritta a titolo di esempio) e per qualsiasi tipologia dell'associata struttura di regolazione e compensazione dell'offset, che viene in ogni caso controllata, come precedentemente descritto in dettaglio, mediante il segnale di controllo  $S_{\rm c}$  generato

dallo stadio di compensazione dell'offset 12.

Ad esempio, la struttura micromeccanica di rilevamento può essere di tipo resistivo.

La stessa struttura di compensazione, di tipo capacitivo, precedentemente descritta in dettaglio può essere differente da quella dell'esempio illustrato.

## RIVENDICAZIONI

1. Circuito di compensazione dell'offset (12) per un dispositivo sensore MEMS (1), dotato di una struttura micromeccanica di rilevamento (2) atta a trasdurre una grandezza da rilevare in una grandezza elettrica rilevamento e di un circuito elettronico di lettura (6), accoppiato in ingresso alla struttura micromeccanica di rilevamento (2) e configurato in modo da elaborare detta grandezza elettrica di rilevamento per fornire un segnale di uscita  $(V_{out})$ , che è funzione di detta grandezza da rilevare; detto circuito di compensazione dell'offset (12) comprendendo un'unità di controllo (20) configurata in modo da controllare una struttura di compensazione (14a, 14b), atta ad essere accoppiata elettricamente all'ingresso del circuito elettronico di lettura (6), per generare una grandezza elettrica di compensazione, di valore regolabile, atta a compensare un offset presente su detto segnale di uscita  $(V_{out})$ ,

caratterizzato dal fatto che detta unità di controllo (20) è configurata in modo da: leggere il segnale di uscita  $(V_{\text{out}})$  durante il funzionamento del dispositivo sensore MEMS (1); ricavare un'informazione sull'offset presente su detto segnale di uscita  $(V_{\text{out}})$ ; e controllare detta struttura di compensazione (14a, 14b) in funzione di detta informazione sull'offset.

- 2. Circuito secondo la rivendicazione 1, comprendente un modulo di filtraggio passa-basso (18), atto ad essere collegato ad un'uscita (11a, 11b) di detto circuito elettronico di lettura (6) e configurato in modo da generare un segnale di uscita filtrato (LPF $_{\rm out}$ ) in funzione di detto segnale di uscita ( $V_{\rm out}$ ); in cui detta unità di controllo (20) è configurata in modo da ricavare detta informazione sull'offset in funzione di segnale di uscita filtrato (LPF $_{\rm out}$ ).

- 3. Circuito secondo la rivendicazione 2, comprendente inoltre un modulo rilevatore di soglia (22), accoppiato a detto modulo di filtraggio passa-basso (18) per ricevere detto segnale di uscita filtrato (LPF $_{\rm out}$ ), e configurato in modo da eseguire un confronto tra il valore di detto segnale di uscita filtrato (LPF $_{\rm out}$ ) ed almeno una prima soglia ( $V_{\rm t1}$ ) e generare un segnale di confronto, indicativo del risultato del confronto; in cui detta unità di controllo (20) è configurata in modo da generare un segnale di controllo ( $S_{\rm c}$ ) atto a controllare detta struttura di compensazione (14a, 14b), in funzione di detto segnale di confronto.

- 4. Circuito secondo la rivendicazione 3, in cui detta prima soglia  $(V_{\text{tl}})$  è indicativa di un primo valore desiderato di offset su detto segnale di uscita  $(V_{\text{out}})$ .

- 5. Circuito secondo una qualsiasi delle rivendicazioni

- 3-4, in cui detto modulo di filtraggio passa-basso (18) presenta una frequenza di taglio di valore regolabile; ed in cui detta unità di controllo (20) è configurata in modo da modificare il valore di detta frequenza di taglio in funzione di detto segnale di confronto.

- 6. Circuito secondo la rivendicazione 5, in cui detta unità di controllo (20) è configurata in modo da incrementare/decrementare il valore di detta frequenza di taglio, in funzione di un incremento/decremento, in valore assoluto, di una distanza tra detto segnale di uscita filtrato (LPF $_{\rm out}$ ) e detta prima soglia ( $V_{\rm t1}$ ).

- 7. Circuito secondo una qualsiasi delle rivendicazioni 3-6, in cui detto modulo rilevatore di soglia (22) è configurato in modo da confrontare il valore di detto segnale di uscita filtrato (LPF<sub>out</sub>) con almeno una seconda soglia ( $V_{t2}$ ), in valore assoluto maggiore di detta prima soglia ( $V_{t1}$ ), per generare detto segnale di confronto; ed in cui detta unità di controllo (20) è configurata in modo da variare una modalità di compensazione per la generazione di detto segnale di controllo ( $S_c$ ) in funzione del valore di detto segnale di confronto.

- 8. Circuito secondo la rivendicazione 7, in cui detta unità di controllo (20) è configurata in modo da implementare: una modalità di compensazione veloce, quando detto segnale di uscita filtrato (LPF $_{\rm out}$ ) supera in valore

assoluto detta seconda soglia  $(V_{t2})$ ; ed una modalità di compensazione lenta, quando detto segnale di uscita filtrato (LPF $_{out}$ ) è compreso, in valore assoluto, tra detta prima soglia  $(V_{t1})$  e detta seconda soglia  $(V_{t2})$ .

- 9. Circuito secondo la rivendicazione 8, in cui detta modalità di compensazione veloce prevede un primo valore di detta frequenza di taglio ed una prima frequenza operativa di lavoro ( $f_{op\_fast}$ ) per detta unità di controllo (20); ed in cui detta modalità di compensazione lenta prevede un secondo valore di detta frequenza di taglio, minore di detto primo valore, ed una seconda frequenza operativa di lavoro ( $f_{op\_slow}$ ) per detta unità di controllo (20), minore di detta prima frequenza operativa di lavoro ( $f_{op\_fast}$ ).

- 10. Circuito secondo la rivendicazione 9, in cui detta unità di controllo (20) è configurata in modo da implementare inoltre una strategia di compensazione rapida, all'accensione e/o all'uscita da una condizione di standby di detto dispositivo sensore MEMS (1), ad un terzo valore di detta frequenza di taglio, maggiore di detto primo valore, e ad una terza frequenza operativa di lavoro ( $f_{op\_rec}$ ) per detta unità di controllo (20), maggiore di detta prima frequenza operativa di lavoro ( $f_{op\_fast}$ ), per riportare rapidamente detto circuito elettronico di lettura (6) in una dinamica consentita di funzionamento.

- 11. Circuito secondo la rivendicazione 10, in cui

detto segnale di controllo ( $S_c$ ) è un segnale digitale avente un numero prefissato di bit; ed in cui, durante detta strategia di compensazione rapida, detta unità di controllo (20) è configurata per eseguire una ricerca iterativa su detti bit, fino a determinare una combinazione di detti bit tale per cui detto segnale di uscita filtrato ( $LPF_{out}$ ) è compreso tra un valore minimo ed un valore massimo definiti da detta dinamica consentita.

- 12. Circuito secondo una qualsiasi delle rivendicazioni 3-11, in cui detta unità di controllo (20) è configurata per determinare iterativamente una variazione incrementale del valore assoluto di detto segnale di controllo ( $S_c$ ), fino a quando detto segnale di uscita filtrato ( $LPF_{out}$ ) scende, in valore assoluto, al di sotto di detta prima soglia ( $V_{t1}$ ).

- 13. Circuito secondo una qualsiasi delle rivendicazioni precedenti, in cui detta struttura di compensazione (14a, 14b) comprende almeno un elemento elettrico regolabile, accoppiato all'ingresso di detto circuito elettronico di lettura (6).

- 14. Circuito secondo la rivendicazione 13, in cui detta struttura micromeccanica di rilevamento (2) è di tipo capacitivo, e detto almeno un elemento elettrico regolabile è un condensatore a capacità variabile (14a, 14b).

- 15. Dispositivo sensore MEMS (1), comprendente una

struttura micromeccanica di rilevamento (2) atta a trasdurre una grandezza da rilevare in una grandezza elettrica di rilevamento, ed un circuito elettronico di lettura (6), accoppiato in ingresso alla struttura micromeccanica di rilevamento (2) e configurato in modo da elaborare detta grandezza elettrica di rilevamento per fornire un segnale di uscita (V<sub>out</sub>); comprendente inoltre un circuito di compensazione dell'offset (12) secondo una qualsiasi delle rivendicazioni precedenti.

- 16. Dispositivo secondo la rivendicazione 15, in cui detto circuito di compensazione dell'offset (12) è integrato con detto circuito elettronico di lettura (6).

- 17. Metodo di compensazione dell'offset, per un dispositivo sensore MEMS (1), dotato di una struttura micromeccanica di rilevamento (2) atta a trasdurre una grandezza da rilevare in una grandezza elettrica di rilevamento e di un circuito elettronico di lettura (6), accoppiato in ingresso alla struttura micromeccanica di rilevamento (2) e configurato in modo da elaborare detta grandezza elettrica di rilevamento per fornire un segnale di uscita ( $V_{\rm out}$ ), che è funzione di detta grandezza da rilevare; detto metodo comprendendo la fase di generare una grandezza elettrica di compensazione, di valore regolabile, atta a compensare un offset presente su detto segnale di uscita ( $V_{\rm out}$ ),

caratterizzato dal fatto di comprendere le fasi di:

leggere il segnale di uscita  $(V_{\text{out}})$  durante il funzionamento del dispositivo sensore MEMS (1);

ricavare un'informazione sull'offset presente su detto segnale di uscita ( $V_{\text{out}}$ ); e

controllare detta struttura di compensazione (14a, 14b) in funzione di detta informazione sull'offset.

18. Metodo secondo la rivendicazione 17, in cui detta fase di ricavare un'informazione sull'offset comprende:

eseguire un filtraggio passa-basso (18) di detto segnale di uscita ( $V_{\text{out}}$ ) per generare un segnale di uscita filtrato ( $LPF_{\text{out}}$ ); e

confrontare il valore di detto segnale di uscita filtrato (LPF $_{\text{out}}$ ) con almeno una prima soglia ( $V_{\text{t1}}$ ) per generare un segnale di confronto, indicativo del risultato del confronto;

in cui detta fase di controllare comprende la fase di generare un segnale di controllo  $(S_c)$  atto a controllare detta struttura di compensazione  $(14a,\ 14b)$ , in funzione di detto segnale di confronto.

p.i.: STMICROELECTRONICS S.R.L.

Lorenzo NANNUCCI

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)

p.i.: STMICROELECTRONICS S.R.L.

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)

Fig.4

p.i.: STMICROELECTRONICS S.R.L.

p.i.: STMICROELECTRONICS S.R.L.

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)