(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5309915号 (P5309915)

(45) 発行日 平成25年10月9日(2013.10.9)

(24) 登録日 平成25年7月12日(2013.7.12)

(51) Int . CL.

F I

HO3K 19/0175 (2006.01)

HO3K 19/00 1O1A HO3K 19/00 1O1F

請求項の数 2 (全 12 頁)

(21) 出願番号 特願2008-293413 (P2008-293413) (22) 出願日 平成20年11月17日 (2008.11.17)

(65) 公開番号 特開2010-124047 (P2010-124047A)

(43) 公開日 平成22年6月3日 (2010.6.3) 審査請求日 平成23年10月11日 (2011.10.11) ||(73)特許権者 000106276

サンケン電気株式会社

埼玉県新座市北野3丁目6番3号

|(74)代理人 100083806

弁理士 三好 秀和

|(74)代理人 100100712

弁理士 岩▲崎▼ 幸邦

|(74)代理人 100100929

弁理士 川又 澄雄

|(74)代理人 100095500

弁理士 伊藤 正和

(74)代理人 100101247

弁理士 高橋 俊一

|(74)代理人 100098327

弁理士 高松 俊雄

最終頁に続く

(54) 【発明の名称】 レベルシフト回路

### (57)【特許請求の範囲】

## 【請求項1】

第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、

前記第2電圧レベルの論理電圧状態を第1コンデンサを介してセットするセットレベル 回路と、

前記第2電圧レベルの論理電圧状態を第2コンデンサを介してリセットするリセットレベル回路と、

前記セットレベル回路のセット信号と前記リセットレベル回路のリセット信号とにより ローサイドスイッチに直列に接続されたハイサイドスイッチをオン / オフ駆動する駆動回 路と、

前記第1コンデンサ及び前記第2コンデンサに流れる電流の内の少なくともいずれか一方に流れる電流を検出する電流検出回路と、

前記電流検出回路が前記第 1 コンデンサ又は前記第 2 コンデンサに流れる電流を検出している期間中、前記セットレベル回路及び前記リセットレベル回路に入力される駆動信号の内の少なくともいずれか一方をマスクするマスク回路と、

を備えることを特徴とするレベルシフト回路。

### 【請求項2】

前記セットレベル回路と前記リセットレベル回路によって駆動される異なる電圧レベル の論理電圧状態は、前記セットレベル回路によるセット信号より、前記リセットレベル回

20

### 路によるリセット信号が優先されることを特徴とする請求項1記載のレベルシフト回路。

### 【発明の詳細な説明】

### 【技術分野】

### [00001]

本発明は、ハーフブリッジ構成のスイッチにおいて必要とされるレベルシフトを与える レベルシフト回路に関する。

#### 【背景技術】

### [0002]

従来のレベルシフト回路として、例えば、特許文献1に記載されたレベルシフト回路が 知られている。

# [0003]

このレベルシフト回路においては、ハーフブリッジ構成のハイサイドスイッチとローサイドスイッチとの中点におけるハイサイドグランド電位は、ハイサイドスイッチ及びローサイドスイッチのオン / オフ動作に同期して、グランド電位に対して例えばゼロボルトから最大で400Vと大きく電圧レベルが変化する。このため、ハイサイドスイッチのゲートにはハイサイドグランド電位よりも高い電位を印加するハイサイドドライバが用いられる。

### [0004]

また、2つの受動デバイスとして第1コンデンサと第2コンデンサとが設けられ、パルス信号の立ち上がりエッジが第1ドライバを介して第1コンデンサに入力され、パルス信号の立ち上がりエッジがインバータを介して立ち下がりエッジとなって第2コンデンサに入力される。第1コンデンサと第2コンデンサとは、立ち上がりエッジ及び立ち下がりエッジにより、必要とされる電流を生じさせるように機能する。

### [0005]

即ち、第1コンデンサと第2コンデンサにおいて、一時的な電流を生じさせ、その一時的な電流を利用して、ハーフブリッジドライバ又は同様なタイプの回路を適正に駆動するために必要とされる適正な時点でラッチをセット又はリセットする。ラッチからのセット信号又はリセット信号でハイサイドドライバがハイサイドスイッチをオン又はオフさせる

# [0006]

以上の構成においては、第1コンデンサ及び第2コンデンサの充電電圧がセット信号、 リセット信号によらず、外的要因によって変化すると、第1コンデンサ及び第2コンデン サに一時的な電流が流れる。

【特許文献1】特表2005-512444号公報

# 【発明の開示】

【発明が解決しようとする課題】

# [0007]

以上の構成において、ハーフブリッジ構成のハイサイドスイッチとローサイドスイッチとの中点にはトランスやリアクトルなどのインダクタンス負荷が接続される場合がある。ここで、ハイサイドスイッチとローサイドスイッチによるスイッチング動作による電圧変動、電流変動によって前記インダクタンス負荷のインダクタンス成分によって振動が発生する。

### [0008]

ハイサイドスイッチとローサイドスイッチとの中点はハイサイドドライバのハイサイドグランド電位となるため、この振動によってハイサイドドライバのハイサイド電位全体が振動する。この要因によって、第1コンデンサ及び第2コンデンサの充電電圧がセット信号、リセット信号によらず前記振動によって変化すると、第1コンデンサ及び第2コンデンサに一時的な電流が流れてしまう。このため、ラッチ回路が誤動作しハイサイドスイッチへの信号伝達不良が発生する。

### [0009]

50

10

20

30

本発明は、ハイサイドドライバのハイサイドグランド電位の振動による誤動作を防止して確実な信号伝達を行うレベルシフト回路を提供することにある。

### 【課題を解決するための手段】

### [0010]

上記課題を解決するために、請求項1の発明は、第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、前記第2電圧レベルの論理電圧状態を第1コンデンサを介してセットするセットレベル回路と、前記第2電圧レベルの論理電圧状態を第2コンデンサを介してリセットするリセットレベル回路と、前記セットレベル回路のセット信号と前記リセットレベル回路のリセット信号とによりローサイドスイッチに直列に接続されたハイサイドスイッチをオン/オフ駆動する駆動回路と、前記第1コンデンサ及び前記第2コンデンサに流れる電流の内の少なくともいずれか一方を検出する電流検出回路と、前記電流検出回路が前記第1コンデンサ又は前記第2コンデンサに流れる電流を検出している期間中、前記セットレベル回路及び前記リセットレベル回路に入力される駆動信号の内の少なくともいずれか一方をマスクするマスク回路とを備えることを特徴とする。

#### [0012]

請求項2の発明は、請求項1記載のレベルシフト回路において、前記セットレベル回路と前記リセットレベル回路によって駆動される異なる電圧レベルの論理電圧状態は、前記セットレベル回路によるセット信号より、前記リセットレベル回路によるリセット信号が優先されることを特徴とする。

### 【発明の効果】

### [0013]

本発明によれば、電流検出回路は、第1コンデンサ及び第2コンデンサに流れる電流、即ち電流の充放電期間を検出することで、ハイサイドスイッチとローサイドスイッチとの接続点におけるハイサイドグランドVSの電圧変動を検出することができる。このため、ハイサイドグランドVSの電圧がハーフブリッジ回路又はフルブリッジ回路の中点電位である場合に、中点電位の変化をコンデンサの充放電により検出することができる。

### [0014]

即ち、中点電位を検出することにより、適切なタイミングでハイサイドスイッチ、ローサイドスイッチを駆動できるとともに、中点電位の変化中に駆動信号が出力され各スイッチ素子のリカバリー電流による短絡電流がハーフブリッジ回路又はフルブリッジ回路に流れるのを防止できる。従って、異なる電圧レベルの電圧変動等の外的要因により発生するコンデンサの充放電による信号伝達不良を防止して、確実な信号伝達を行うことができる

# [0015]

また、マスク回路は、電流検出回路が第1コンデンサ<u>又は</u>第2コンデンサ<u>に流れる電流を検出して</u>いる期間中、セットレベル回路及びリセットレベル回路に入力される駆動信号をマスクするので、中点電位の電圧変動等の外的要因により発生するコンデンサの充放電による信号伝達不良を防止して、確実な信号伝達を行うことができる。

### 【発明を実施するための最良の形態】

# [0016]

以下、本発明の実施の形態のレベルシフト回路を図面を参照しながら詳細に説明する。

### [0017]

本発明は、コンデンサを介して異なる電圧レベルに信号を伝達することで、信号伝達時に発生する消費電力を低減すると同時に、異なる電圧レベルの電圧変動などによるコンデンサの充放電による信号伝達不良を電流検知回路及びマスク回路で防止することによって確実な信号伝達を行う。

# 【実施例1】

### [0018]

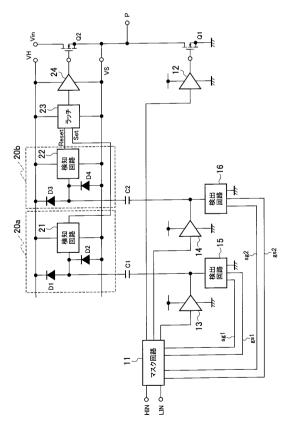

図1は本発明の実施例1のレベルシフト回路を示す回路構成図である。実施例1のレベ

10

20

30

00

40

[0019]

なお、ハーフブリッジ回路を用いる代わりに、フルブリッジ回路を用いても良い。

[0020]

マスク回路11は、LIN端子に入力されたローサイド指令信号を駆動回路12に出力する。駆動回路12は、マスク回路11からのローサイド指令信号によりローサイドスイッチQ1を駆動する。

[0021]

マスク回路11は、HIN端子に入力されたハイサイド指令信号をバッファ13,14に出力する。バッファ13の出力には第1コンデンサC1が接続され、バッファ13は、第1コンデンサC1を介してセット信号を第1ハイサイド信号検出回路20aに送出する。バッファ14の出力には第2コンデンサC2が接続され、バッファ14は、第2コンデンサC2を介してリセット信号を第2ハイサイド信号検出回路20bに送出する。

[0022]

第 1 コンデンサ C 1 の一端とバッファ 1 3 の出力とには検出回路 1 5 が接続されている。第 2 コンデンサ C 2 の一端とバッファ 1 4 の出力とには検出回路 1 6 が接続されている

[0023]

検出回路15は、本発明の電流検出回路に対応し、第1コンデンサ C 1 に流れる充放電電流を検出し、放電電流期間信号 s g 1 と充電電流期間信号 g s 1 をマスク回路11に出力する。検出回路16は、本発明の電流検出回路に対応し、第2コンデンサ C 2 に流れる充放電電流を検出し、放電電流期間信号 s g 2 と充電電流期間信号 g s 2 をマスク回路11に出力する。

[0024]

第 1 コンデンサ C 1 の他端は、第 1 ハイサイド信号検知回路 2 0 a に接続される。第 2 コンデンサ C 2 の他端は、第 2 ハイサイド信号検出回路 2 0 b に接続される。

[0025]

第1ハイサイド信号検知回路20aは、本発明のセット回路に対応し、第1コンデンサ C 1 の他端にアノードが接続され且つカソードがハイサイドグランド電位VSよりも高電位VHに接続されたダイオードD1、第1コンデンサ C 1 の他端にカソードが接続され且 つアノードがハイサイドグランド電位VSに接続されたダイオードD2、第1コンデンサ C 1 の他端に発生する信号を検知する検知回路21とで構成され、セット信号を検出し、 検知されたセット信号をラッチ23に出力する。

[0026]

第2ハイサイド信号検知回路20bは、本発明のリセット回路に対応し、第2コンデンサC2の他端にアノードが接続され且つカソードがハイサイドグランド電位VSよりも高電位VHに接続されたダイオードD3、第2コンデンサC2の他端にカソードが接続され且つアノードがハイサイドグランド電位VSに接続されたダイオードD4、第2コンデンサC2の他端に発生する信号を検知する検知回路22とで構成され、リセット信号を検出し、検知されたリセット信号をラッチ23に出力する。

[0027]

ラッチ 2 3 は、検知回路 2 1 からのセット信号によってセットされ、検知回路 2 2 からのリセット信号によってリセットされる。駆動回路 2 4 は、本発明の駆動回路に対応し、ラッチ 2 3 からの出力によりハイサイドスイッチ Q 2 を駆動する。

[0028]

ハイサイド回路は、第1ハイサイド信号検知回路20a、第2ハイサイド信号検知回路20b、ラッチ23、駆動回路24で構成され、前記ハーフブリッジ回路の中点Pをハイ

10

20

30

40

20

30

40

50

サイドグランド電位VSとしている。

## [0029]

ハイサイドグランド電位 V S は、ハイサイドスイッチ Q 2 及びローサイドスイッチ Q 1 のオン / オフ動作に同期して大きく電圧レベルが変化する。ハイサイドグランド電位 V S が変化すると、ハイサイドグランド電位 V S に合わせて第 1 及び第 2 コンデンサ C 1 , C 2 の電位が変化する。このとき、第 1 コンデンサ C 1 及び第 2 コンデンサ C 2 には充放電電流が流れる。

### [0030]

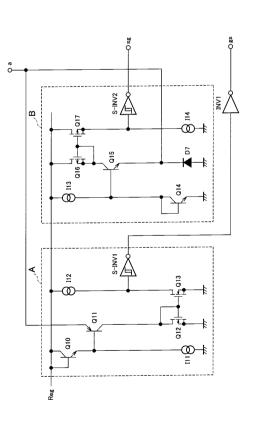

図 2 は図 1 に示す実施例 1 のレベルシフト回路内の検出回路 1 5 , 1 6 の一例を示す回路構成図である。

# [0031]

図 2 のブロック A において、NPN型のトランジスタQ 1 0 とPNP型のトランジスタQ 1 1 と電流源 I 1 1 とでプラスクランプ回路を構成する。トランジスタQ 1 0 のベースとコレクタは電源 R e g に接続され、トランジスタQ 1 0 のエミッタは電流源 I 1 1 の一端とトランジスタQ 1 1 のベースに接続され、電流源 I 1 1 の他端は、接地されている。トランジスタQ 1 1 のエミッタは、第 1 コンデンサC 1 (第 2 コンデンサC 2)に接続された a 端子に接続されている。

# [0032]

トランジスタQ 1 1 のコレクタは、N型のMOSFETQ 1 2 のドレイン及びゲートとN型のMOSFETQ 1 3 のゲートに接続され、MOSFETQ 1 2 のソースとMOSFETQ 1 3 のソースとは接地されている。MOSFETQ 1 3 のドレインは、シュミットインバータS - INV 1 の入力端に接続されると共に電流源 I 1 2 を介して電源Regに接続されている。

#### [0033]

シュミットインバータS - INV1の出力端は、インバータINV1を介して充電電流期間信号gsをマスク回路11に出力する。MOSFETQ12とMOSFETQ13とは、第1カレントミラー回路を構成する。

### [0034]

図2のブロックBにおいて、NPN型のトランジスタQ14とNPN型のトランジスタQ15と電流源I13とはマイナスクランプ回路を構成している。電源Regとグランドとの間には電流源I13とトランジスタQ14との直列回路が接続されている。トランジスタQ14は、コレクタとベースとが共通接続されている。電流源I13とトランジスタQ14との接続点にはNPN型のトランジスタQ15のベースが接続されている。

# [0035]

トランジスタQ15のコレクタは、P型のMOSFETQ16のドレイン及びゲートとP型のMOSFETQ17のゲートに接続され、MOSFETQ16のソースとMOSFETQ17のソースとは電源Regに接続されている。トランジスタQ15のエミッタは、ダイオードD7のカソードとa端子とに接続され、ダイオードD7のアノードは接地されている。

### [0036]

MOSFETQ17のドレインは、シュミットインバータS-INV2の入力端に接続されると共に電流源I14を介して接地されている。シュミットインバータS-INV2の出力端は、放電電流期間信号sgをマスク回路11に出力する。MOSFETQ16とMOSFETQ17とは、第2カレントミラー回路を構成する。

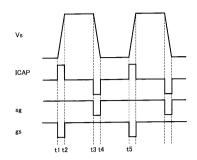

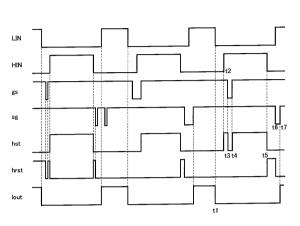

次に、図2に示す検出回路15,16の動作を図3を参照しながら説明する。図3は図2に示す検出回路の動作波形図である。図3において、VSはハイサイドグランド端子電圧、ICAPは第1コンデンサC1、第2コンデンサC2に流れる電流、SgはシュミットインバータS-INV2の出力信号、gSはインバータINV1の出力信号である。

### [0037]

まず、時刻t1~t2において、ハイサイドグランド電位VSが0Vから上昇すると、

第1及び第2コンデンサ C 1 , C 2 の電位が変化し、第1及び第2コンデンサ C 1 , C 2 に充電電流 I C A P が流れる。そして、第1コンデンサ C 1 (第2コンデンサ C 2 )に接続された a 端子の電圧が電源 R e g 電圧以上に上昇すると、トランジスタ Q 1 1 がオンし、 a 端子の電位が上昇しないようにプラスクランプ回路により電源 R e g 電圧にクランプされる。

### [0038]

プラスクランプ回路が動作し、MOSFETQ12がオンすると、第1カレントミラー回路に第1コンデンサC1(第2コンデンサC2)の充電電流ICAPがトランジスタQ11を介して入力される。

## [0039]

第1カレントミラー回路の出力電流(MOSFETQ13に流れる電流)が電流源I12の電流以上である場合には、第1カレントミラー回路の出力端電圧は、Lレベルとなる。第1カレントミラー回路の出力電流(MOSFETQ13に流れる電流)が電流源I12未満である場合には、第1カレントミラー回路の出力端電圧は、Hレベルとなる。

### [0040]

第1カレントミラー回路の出力端電圧の電圧レベルは、シュミットインバータS-INV1で反転されて、インバータINV1で反転されて、充電期間検知信号gsとしてマスク回路11に出力される。

### [0041]

即ち、プラスクランプ回路が動作している期間だけ、シュミットインバータS-INV 1の論理レベルが変化し、第1コンデンサC1(第2コンデンサC2)の充電期間を検出 することができる。

# [0042]

次に、時刻 t 3 ~ t 4 において、ハイサイドグランド電位 V S が上昇した電圧から 0 V に減少すると、第 1 及び第 2 コンデンサ C 1 , C 2 の電位が変化し、第 1 及び第 2 コンデンサ C 1 , C 2 に放電電流 I C A P が流れる。そして、第 1 コンデンサ C 1 (第 2 コンデンサ C 2)に接続された a 端子の電圧が G N D 電圧以下になると、トランジスタ Q 1 5 がオンし、 a 端子の電圧が低下しないようにマイナスクランプ回路によりグランド電圧にクランプされる。

# [0043]

マイナスクランプ回路が動作し、MOSFETQ16がオンすると、第2カレントミラー回路に第1コンデンサC1(第2コンデンサC2)の放電電流ICAPがトランジスタQ15を介して入力される。

# [0044]

第2カレントミラー回路の出力電流(MOSFETQ17に流れる電流)が電流源I14の電流以上である場合には、第2カレントミラー回路の出力端電圧は、Hレベルとなる。第2カレントミラー回路の出力電流が電流源I14未満である場合には、第2カレントミラー回路の出力端電圧はLレベルとなる。

#### [0045]

第2カレントミラー回路の出力端電圧の電圧レベルは、シュミットインバータS-IN 40 V2に入力され放電期間検知信号 Sgとしてマスク回路 1 1 に出力される。

#### [0046]

即ち、マイナスクランプ回路が動作している期間だけ、シュミットインバータS-INV2の論理レベルが変化し、第1コンデンサC1(第2コンデンサC2)の放電期間を検出することができる。

# [0047]

このように、検出回路15,16は、第1コンデンサC1、第2コンデンサC2に電流が流れると、電流の向きによってプラスクランプ回路又はマイナスクランプ回路が動作して、放電期間検知信号sg又は充電期間検知信号gsを出力することができる。

# [0048]

50

10

20

20

30

40

50

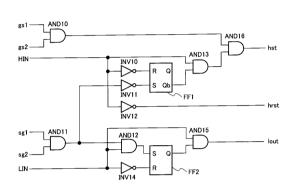

図4は本発明の第1の実施例におけるマスク回路の一実施の形態を示す回路構成図である。

### [0049]

図4において、アンド回路AND10は、検出回路15からの充電期間検知信号gs1と検出回路16からの充電期間検知信号gs2とのアンドをとってアンド回路AND16に出力する。アンド回路AND11は、検出回路15からの放電期間検知信号sg1と検出回路16からの放電期間検知信号sg2とのアンドをとってアンド回路AND12及びインバータINV11に出力する。

### [0050]

インバータINV10は、ハイサイド指令信号HINを反転してフリップフロップ回路FF1のリセット端子Rに出力する。インバータINV11は、アンド回路AND11の出力を反転してフリップフロップ回路FF1のセット端子Sに出力する。インバータINV12は、ハイサイド指令信号HINを反転してハイサイドリセット信号hrstとして出力する。

### [0051]

フリップフロップ回路 F F 1 は、Q端子の出力を反転した出力をQ b 端子からアンド回路 A N D 1 3 に出力する。アンド回路 A N D 1 3 は、ハイサイド指令信号 H I N とフリップフロップ回路 F F 1 の反転出力 Q b とのアンドをとってアンド回路 A N D 1 6 に出力する。アンド回路 A N D 1 6 は、アンド回路 A N D 1 0 の出力とアンド回路 A N D 1 3 の出力とのアンドをとってハイサイドセット信号 h s t として出力する。

### [0052]

アンド回路AND12は、アンド回路AND11の出力とローサイド指令信号LINとのアンドをとってフリップフロップ回路FF2のセット端子Sに出力する。インバータINV14は、ローサイド指令信号LINを反転してフリップフロップ回路FF2のリセット端子Rに出力する。

# [0053]

フリップフロップ回路FF2は、Q端子の出力をアンド回路AND15に出力する。アンド回路AND15は、ローサイド指令信号LINとフリップフロップ回路FF2の出力Qとのアンドをとってローサイド駆動信号1outとして出力する。

# [0054]

次に、マスク回路11の動作を図5を参照しながら説明する。図5は図4に示すマスク回路の動作波形図である。図5において、LINはローサイド指令信号、HINはハイサイド指令信号、gsはコンデンサ充電期間信号、sgはコンデンサ放電期間信号、hstはハイサイドセット信号、hrstはハイサイドリセット信号、1outはローサイド駆動信号である。

### [0055]

まず、時刻 t 1 において、ローサイド指令信号LINがLレベルになると、アンド回路AND15の出力がLレベルとなるので、ローサイド駆動信号loutは、Lレベルとなる。

### [0056]

## [0057]

次に、時刻 t 3 ~ t 4 において、充電期間検知信号 g s の L レベルにより、即ち、第 1 コンデンサ C 1、第 2 コンデンサ C 2 の充電期間中、アンド回路 A N D 1 0 の出力が L レベルとなって、 L レベルのハイサイドセット信号 h s t が出力される。このため、第 1 コンデンサ C 1、第 2 コンデンサ C 2 の充電期間中、ハイサイド指令信号 H I N をマスクすることできる。

### [0058]

次に、時刻t4において、コンデンサ充電期間検知信号gsがHレベルとなると、ハイ

サイド指令信号HINがHレベルを継続しているので、Hレベルのハイサイドセット信号hstが出力される。

### [0059]

次に、時刻 t 5 において、ハイサイド指令信号 H I N が L レベルとなると、インバータ I N V 1 2 により H レベルのハイサイドリセット信号 h r s t が出力される。

### [0060]

次に、時刻 t 6 ~ t 7 において、放電期間検知信号 s g の L レベルにより、即ち、第 1 コンデンサ C 1、第 2 コンデンサ C 2 の放電期間中、アンド回路 A N D 1 5 の出力は L レベルを保持し、 L レベルのローサイド駆動信号 1 o u t が出力される。

## [0061]

次に、時刻 t 7 において、放電期間検知信号 s g の H レベルにより、即ち、第 1 コンデンサ C 1、第 2 コンデンサ C 2 の放電期間終了信号とローサイド指令信号 L I N の H レベルとにより、アンド回路 A N D 1 5 の出力は H レベルとなるので、 H レベルのローサイド駆動信号 1 o u t が出力される。

### [0062]

このように、図4に示すマスク回路11によれば、ハイサイドセット信号 hstは、充電期間検知信号gsのLレベルにより第1コンデンサC1、第2コンデンサC2の充電期間中、ハイサイド指令信号HINをマスクし、且つ放電期間信号sgのLレベルが検出されない場合には、出力される。

## [0063]

また、ローサイド駆動信号loutは、ローサイド指令信号LINの立ち上がりと放電期間信号sgとを比較し、放電期間信号sgがローサイド指令信号LINより先に検出された場合にはローサイド駆動信号loutをマスクし、放電期間sgが終了した後、ローサイド駆動信号loutを出力する。

#### [0064]

また、一度、ローサイド指令信号LINによって、ローサイド駆動信号1out信号が出力された後、放電期間sgが検出された場合には継続してローサイド駆動信号1outを出力する。

## [0065]

このように実施例1のレベルシフト回路によれば、検出回路15,16は、第1コンデンサ C 1 及び第 2 コンデンサ C 2 に流れる電流、即ち電流の充放電期間を検出することで、ハイサイドスイッチ Q 2 とローサイドスイッチ Q 1 との接続点におけるハイサイドグランド V S の電圧変動を検出することができる。このため、ハイサイドグランド V S の電圧がハーフブリッジ回路又はフルブリッジ回路の中点電位である場合に、中点電位の変化をコンデンサの充放電により検出することができる。

# [0066]

即ち、中点電位を検出することにより、適切なタイミングでハイサイドスイッチQ2、ローサイドスイッチQ1を駆動できるとともに、中点電位の変化中に駆動信号が出力され各スイッチ素子のリカバリー電流による短絡電流がハーフブリッジ回路又はフルブリッジ回路に流れるのを防止できる。従って、異なる電圧レベルの電圧変動等の外的要因により発生するコンデンサC1,C2の充放電による信号伝達不良を防止して、確実な信号伝達を行うことができる。

## [0067]

また、マスク回路11は、検出回路15,16が電流を検出したとき、第1コンデンサ C 1 及び第2コンデンサC 2 に電流が流れている期間中、第1ハイサイド信号検知回路20 a 及び第2ハイサイド信号検知回路20 b に入力される駆動信号をマスクするので、異なる電圧レベルの電圧変動等の外的要因により発生するコンデンサの充放電による信号伝達不良を防止して、確実な信号伝達を行うことができる。

### 【実施例2】

## [0068]

10

20

30

図6は本発明の実施例2のレベルシフト回路を示す回路構成図である。図6に示す実施例2のレベルシフト回路は、実施例1のレベルシフト回路に対して、検出回路17、第3コンデンサC3、ダイオードD5,D6、バッファ18を追加し検出回路15a,16aにおける検知回路21a,22aでの信号検知方法を差動方式に変更している。

## [0069]

ダイオード D 5 とダイオード D 6 との直列回路は、電位 V H と電位 V S との間に接続されている。ダイオード D 5 とダイオード D 6 との接続点は検知回路 2 1 a , 2 2 a に接続されるとともに、第 3 コンデンサ C 3 を介して検出回路 2 0 c , 2 0 d に接続されるとともに、第 3 コンデンサ C 3 を介してバッファ 1 8 及び検出回路 1 7 に接続されている。

### [0070]

検出回路17は、第3コンデンサC3に流れる充放電電流を検出し、放電電流期間信号sg3と充電電流期間信号gs3をマスク回路11aに出力する。

#### [0071]

ここで、マスク回路11aは図示しないが、図4のマスク回路11の充電期間検知信号gs1と充電期間検知信号gs2入力へ充電期間検知信号gs3を接続し、放電期間検知信号sg1と放電期間検知信号sg2入力へ放電期間検知信号sg3を接続した回路としても良い。

# [0072]

なお、検出回路15a,16aは、第1及び第2コンデンサ C 1 , C 2 に流れる充放電電流を検出するが、充電電流期間信号gsと放電電流期間信号sgとをマスク回路11に出力しない。

#### [0073]

また、差動入力検知としたハイサイド検知回路 2 1 a , 2 2 a は基準値を C 3 信号とすることで、ハイサイドグランド V S 電圧の電圧変動などの外的要因により発生するコンデンサ C 1 , C 2 の充放電による信号伝達を同相ノイズとして判断して信号伝達不良を防止する。

このように構成された実施例2のレベルシフト回路によっても、実施例1のレベルシフト回路の効果と同様な効果が得られる。

【図面の簡単な説明】

# [0074]

【図1】本発明の実施例1のレベルシフト回路を示す回路構成図である。

【図2】図1に示す実施例1のレベルシフト回路内の検出回路の一例を示す回路構成図で ある

【図3】図2に示す検出回路の動作波形図である。

【図4】図1に示す実施例1のレベルシフト回路内のマスク回路の一例を示す回路構成図 である。

【図5】図4に示すマスク回路の動作波形図である。

【図6】本発明の実施例2のレベルシフト回路を示す回路構成図である。

## 【符号の説明】

### [0075]

11,11a マスク回路

12,24 駆動回路

13,14,18 バッファ

15,15a,16,16a 検出回路

20 a , 20 c 第1ハイサイド信号検出回路

20 b , 20 d 第2 ハイサイド信号検出回路

21,21a,22,22a 検知回路

23 ラッチ

Q 1 ローサイドスイッチ

Q 2 ハイサイドスイッチ

10

20

30

40

D 1 ~ D 7 ダイオード

AND10~16 アンド回路

C 1 第1コンデンサ

C2 第2コンデンサ

С 3 第3コンデンサ

Q 1 第1スイッチ

FF1,FF2 フリップフロップ回路

INV1, INV10~INV14 インバータ

I 1 , I 1 1 ~ I 1 4 電流源

Q 1 2 , Q 1 3 第 1 カレントミラー回路

Q 1 6 , Q 1 7 第 2 カレントミラー回路

S-INV1,S-INV2 シュミットインバータ

【図1】 【図2】

# 【図3】

# 【図4】

# 【図5】

# 【図6】

# フロントページの続き

# (72)発明者 大坂 昇平

埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内

# 審査官 宮島 郁美

# (56)参考文献 特表2005-512444(JP,A)

特表2008-535328(JP,A)

特開平04-298115(JP,A)

特開2008-263599(JP,A)

# (58)調査した分野(Int.CI., DB名)

H03K19/00,19/01-19/082,19/092-19/096