(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl.

*H01L 23/12* (2006.01)

(11) 공개번호 10-2007-0088266

(43) 공개일자 2007년08월29일

(21) 출원번호 10-2006-7016831

(22) 출원일자 2006년08월22일

심사청구일자     없음

번역문 제출일자 2006년08월22일

(86) 국제출원번호 PCT/JP2005/021686

국제출원일자 2005년11월25일

(87) 국제공개번호 WO 2006/059547

국제공개일자 2006년06월08일

(30) 우선권주장 JP-P-2004-00350882 2004년12월03일 일본(JP)

(71) 출원인

로무 가부시키가이샤

일본 교토시 우교구 사이잉 미조사카죠 21

(72) 발명자

이와타 유키

일본국 교토후 교토시 우교구 사이잉 미조사카죠 21

로무가부시키가이

샤내

(74) 대리인

한양특허법인

전체 청구항 수 : 총 8 항

(54) 반도체 장치

(57) 요약

본 발명은 복수의 기능 블록간의 신호 간섭을 저감시킨 반도체 장치를 제공한다.

CSP 구조를 갖는 반도체 장치(100)에 있어서, 반도체 기판(40)에는 복수의 기능 블록을 포함하는 집적 회로가 형성된다. 복수의 외부 전극(20)은 접속되는 기능 블록에 따라서 복수의 외부 전극군(210, 220)으로 분류되고, 또한 분류된 외부 전극군마다 복수개 영역으로 나누어 배치된다. 복수의 영역의 경계 영역에는, 저임피던스의 외부 전극(20a, 20b, 20c)에 접속된 재배선(30a, 30b, 30c)이 부설된다.

**대표도**

도 1

**특허청구의 범위**

청구항 1.

복수의 기능 블록을 포함하는 집적 회로가 형성되는 반도체 기판과,

상기 집적 회로 상에 설치된 복수의 전극 패드와 재배선을 통해 접속되어, 외부 회로와의 접속 단자가 되는 복수의 외부 전극을 구비하고,

상기 복수의 외부 전극은 접속되는 기능 블록에 따라서 복수의 외부 전극군으로 분류되고, 또한 분류된 외부 전극군마다 복수의 영역으로 나누어 배치되며,

상기 복수 영역의 경계 영역에는 저임피던스의 외부 전극에 접속된 재배선이 부설되는 것을 특징으로 하는 반도체 장치.

## 청구항 2.

청구항 1에 있어서, 상기 복수의 기능 블록 중, 적어도 1개의 기능 블록은 소신호를 취급하는 소신호 회로인 것을 특징으로 하는 반도체 장치.

## 청구항 3.

청구항 1 또는 2에 있어서, 상기 저임피던스의 외부 전극에 접속된 재배선은 외부의 접지 단자와 접속되는 접지 라인, 또는 전원 전압 단자에 접속되는 전원 라인인 것을 특징으로 하는 반도체 장치.

## 청구항 4.

청구항 1 또는 2에 있어서, 상기 저임피던스의 외부 전극에 접속된 상기 재배선은 복수이고, 서로 인접하여 부설되는 것을 특징으로 하는 반도체 장치.

## 청구항 5.

청구항 4에 있어서, 상기 저임피던스의 외부 전극에 접속된 복수의 상기 재배선 중의 2개는, 접지 라인과 전원 라인, 접지 라인과 접지 라인, 또는 전원 라인과 전원 라인 중 어느 하나의 조합인 것을 특징으로 하는 반도체 장치.

## 청구항 6.

청구항 4에 있어서, 상기 저임피던스의 외부 전극에 접속된 재배선은 접지 라인, 전원 라인, 접지 라인의 3개가 순서대로 인접하여 부설되는 것을 특징으로 하는 반도체 장치.

## 청구항 7.

청구항 1 또는 2에 있어서, 상기 저임피던스의 외부 전극에 접속된 상기 재배선은 그 양단에서 상기 저임피던스의 외부 전극에 접속되는 것을 특징으로 하는 반도체 장치.

## 청구항 8.

청구항 1 또는 2에 있어서, 상기 저임피던스의 외부 전극에 접속된 재배선은 다층인 것을 특징으로 하는 반도체 장치.

명세서

## 기술분야

본 발명은 반도체 장치에 관한 것으로, 특히 재배선을 이용한 반도체 장치에 관한 것이다.

## 배경기술

최근의 휴대전화, PDA(Personal Digital Assistance) 등의 정보 단말 기기의 소형화에 따라, 내부에 사용되는 LSI 등의 반도체 장치에 대한 소형화의 요구가 높아지고 있다. 이러한 상황에 있어서, BGA(Ball Grid Array) 구조라고 하는 설치 기술이 착안되고 있다.

BGA 구조란 종래의 QFP(Quad Flat Package) 구조와 같이, 리드 프레임에 의해 기판과 접속되는 것은 아니고, 땜납 범프 또는 땜납 볼이라 불리는 반도체 장치의 표면에 설치한 단자에 의해 기판과 접속된다. 이 BGA 구조에 의하면, 반도체 장치의 표면 전체에 외부와의 접속 단자를 구비할 수 있고, 부품 주변의 리드 프레임이 불필요해지기 때문에, 설치 면적을 대폭 줄여줄 수 있다.

이러한 BGA 구조를 이용하여 CSP(Chip Size Package) 기술이라고 하는, 반도체 칩의 면적과 설치 면적이 동일한 정도가 되는 패키지 기술이 개발되어 있다. 또한, 반도체 칩 상에 기판을 사이에 두지 않고 직접 땜납 범프를 형성하는 WL-CSP (Wafer Level CSP)라고 하는 기술도 개발되어 있고, 반도체 장치의 소형화가 진행되고 있다(특허문헌 1).

이러한 CSP 기술을 적용한 반도체 장치는, 특허문헌 1의 도 1에 도시되는 바와 같이, 땜납 범프에 의해 형성되는 외부 접속 단자가 반도체 장치의 표면에 규칙적으로 배치되고 프린트 기판과 접속되는 경우가 많다.

한편, 반도체 기판 상에는 반도체 접적 회로가 형성되어 있고, 신호의 입출력을 행하기 위한 전극 패드는, QFP 구조의 경우와 마찬가지로, 반도체 접적 회로의 외주부에 배치되어 있는 경우가 많다. 이 반도체 접적 회로 상의 외주부에 형성된 전극 패드는 재배선층에 의해 규칙적으로 배치된 땜납 범프의 위치까지 이끌려 전기적으로 접속된다.

[특허문헌 1] 일본 특허 공보 2003-297961호

## 발명의 상세한 설명

CSP 기술을 적용한 반도체 장치에 있어서는, 설치 면적을 줄여줄 수 있는 반면, 각 단자간의 거리가 근접하게 된다. 특히, WL-CSP 기술에 있어서는, 반도체 칩 표면의 전극으로부터 재배선에 의해 범프의 위치까지 신호의 이끌기를 행하고, 포스트라고 하는 전극 부분에 의해 범프와 접속되기 때문에, 각 전극간의 기생 용량의 존재를 무시할 수 없게 되고, 각 전극 단자간의 크로스토크나 노이즈의 삽입(sneaking-in) 등이 문제가 된다.

본 발명은 이러한 과제를 감안하여 이루어진 것으로, 그 목적은 복수의 기능 블록간의 신호 간섭을 저감시킨 반도체 장치의 제공에 있다.

상기 과제를 해결하기 위해서, 본 발명의 일 양태의 반도체 장치는, 복수의 기능 블록을 포함하는 접적 회로가 형성되는 반도체 기판과, 접적 회로 상에 설치된 복수의 전극 패드와 재배선을 통해 접속되어, 외부 회로와의 접속 단자가 되는 복수의 외부 전극을 구비한다. 복수의 외부 전극은 접속되는 기능 블록에 따라서 복수의 외부 전극군으로 분류되고, 또한 분류된 외부 전극군마다 복수의 영역으로 나누어 배치된다. 복수 영역의 경계 영역에는 저임피던스의 외부 전극에 접속된 재배선이 부설된다.

「접적 회로 상에 설치된 복수의 전극 패드」란, 접적 회로를 구성하는 회로 소자에 신호를 공급하고, 신호를 인출하며 또는 접지 등을 하기 위해서 설치된 전극 패드를 말한다. 또한, 「외부 전극」이란 땜납 범프, 땜납 볼 또는 포스트 등, 외부 회로와의 접속 단자로서 기능하는 전극을 말한다.

이 양태에 의하면, 집적 회로에 있어서, 신호 간섭이 요구되지 않는 복수의 기능 블록을 복수의 영역으로 나누어 형성하고, 또한 각각의 기능 블록에 접속되는 외부 전극을 복수의 영역으로 나누어 배치하며, 외부 전극끼리를 저임피던스가 되는 재배선에 의해서 전기적으로 차단함으로써 재배선으로 구획된 복수의 영역간의 신호 간섭을 저감시킬 수 있다.

복수의 기능 블록 중, 적어도 1개의 기능 블록은 소신호를 취급하는 소신호 회로이어도 된다.

또한, 복수의 기능 블록 중, 다른 기능 블록은 대신호를 취급하는 대신호 회로이어도 된다.

소신호를 취급하는 소신호 회로란, 예를 들면, 디지털 신호 처리를 행하는 회로나, 아날로그의 제어 회로 등을 말하고, 대신호를 취급하는 대신호 회로란, 파워 트랜ジ스터 등을 포함하고 대전류 또는 고전압을 취급하는 회로 등을 말하지만, 소신호 회로와 대신호 회로는 신호 레벨의 상대적인 관계로 나누어도 된다.

저임피던스의 외부 전극에 접속된 재배선은 외부의 접지 단자와 접속되는 접지 라인, 또는 전원 전압 단자에 접속되는 전원 라인으로써 된다.

복수 영역의 경계 영역에 부설되고 저임피던스의 외부 전극에 접속된 재배선을 접지 라인으로 한 경우에는, 외부의 접지 단자에 신호가 방출되기 때문에 복수 영역간의 신호 간섭을 저감시킬 수 있다. 또한, 이 재배선을 전원 라인으로 함으로써, 외부에 접속되는 바이패스 콘덴서 등을 통해 신호를 방출할 수 있기 때문에, 복수 영역간의 신호 간섭을 저감시킬 수 있다.

이 재배선은 프로세스 루이 허용하는 범위에 있어서 두껍게 형성하는 것이 바람직하다.

저임피던스의 외부 전극에 접속된 재배선은 복수이고, 서로 인접하여 부설되어도 된다. 복수의 재배선에 의해 복수의 영역을 사이에 둠으로써 신호 간섭을 보다 적합하게 저감시킬 수 있다.

저임피던스의 외부 전극에 접속된 복수의 재배선 중의 2개는 접지 라인과 전원 라인, 접지 라인과 접지 라인, 또는 전원 라인과 전원 라인 중 어느 하나의 조합이어도 된다.

저임피던스의 외부 전극에 접속된 재배선은 접지 라인, 전원 라인, 접지 라인의 3개가 순서대로 인접하여 부설되어도 된다.

저임피던스의 외부 전극에 접속된 재배선은 그 양단에서 저임피던스의 외부 전극에 접속되어도 된다.

실드 배선으로서 기능하는 재배선의 양단에 전원 전압 단자 또는 접지 단자 등을 접속함으로써, 재배선의 임피던스를 낮추고, 전위를 안정시킬 수 있으며, 복수의 영역간의 신호 간섭을 보다 적합하게 저감시킬 수 있다.

한편, 이상의 구성 요소의 임의의 조합이나 본 발명의 구성 요소나 표현을 방법, 장치, 시스템 등의 사이에서 상호 치환한 것도 또한 본 발명의 양태로서 유효하다.

#### (발명의 효과)

본 발명에 관한 반도체 장치에 의해, 상이한 기능 블록에 접속되는 외부 전극간의 신호 간섭을 저감시킬 수 있다.

#### 실시예

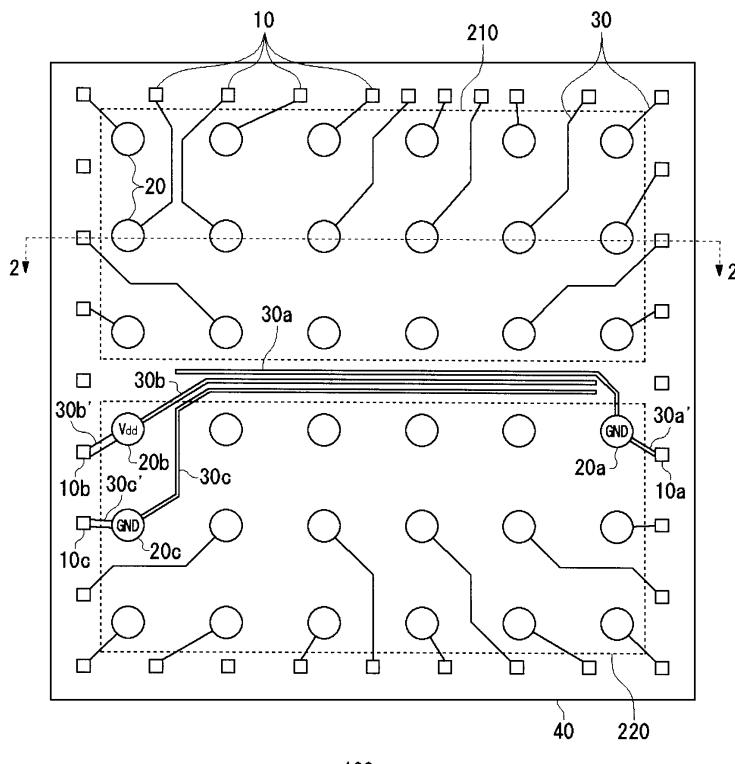

도 1은 본 발명의 실시형태에 관한 반도체 장치(100)를 전극 패드측에서 본 도면이다. 반도체 장치(100)는 CSP 구조를 갖고 있고, 동 도면에는 외부 회로와 신호의 입출력을 행하기 위해서 반도체 기판(40) 상에 설치된 복수의 전극 패드(10), 땀납 범프에 의해 형성되는 외부 전극(20), 재배선(30)이 도시되어 있다. 이후의 도면에 있어서, 동일한 구성 요소에는 동일한 부호를 붙여 적절하게 설명을 생략하는 것으로 한다.

외부 전극(20)은 반도체 장치(100)의 표면에 매트릭스 형상으로 배치된다. 또한, 전극 패드(10)는 반도체 기판(40)의 최외주에 집적 회로를 둘러싸도록 하여 배치되어 있다. 외부 전극(20)과 전극 패드(10)는 재배선(30)을 통해 접속되어 있다.

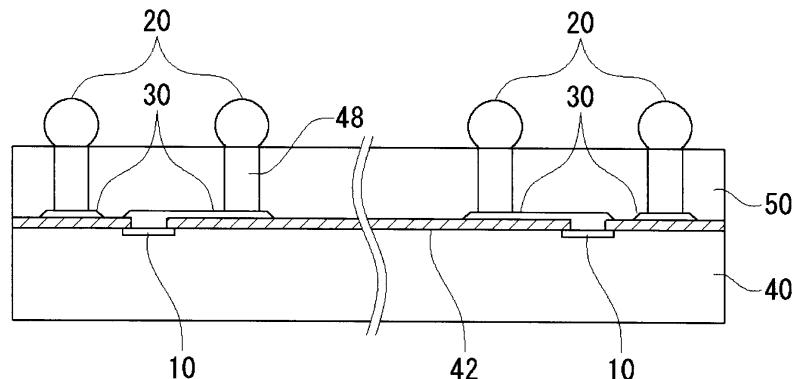

도 2는 도 1의 2-2선 단면도이다. 이 반도체 장치(100)는 반도체 기판(40) 상에 외부와의 접속 전극을 직접 형성하는 WL-CSP 구조를 갖고 있다. 반도체 장치(100)는 반도체 기판(40), 패시베이션을 위한 보호막(42), 전극 패드(10), 재배선(30), 포스트(48), 외부 전극(20), 밀봉 수지(50)를 포함한다.

반도체 기판(40)의 상면에는 트랜지스터, 저항 등의 회로 소자를 포함하는 반도체 집적 회로가 형성되어 있고, 신호의 입출력용 전극 패드(10)가 설치되어 있다. 전극 패드(10)는 통상 알루미늄 등의 재료에 의해서 형성된다.

보호막(42)은 질화 실리콘막 등이고, 전극 패드(10)의 상부가 개구되어 형성된다. 재배선(30)은 구리, 알루미늄, 금 등으로 형성되고, 전극 패드(10)로부터 최종적인 외부 인출 전극의 형성 위치가 되는 외부 전극(20)의 위치까지 신호를 이끌어 포스트(48)와 접속한다. 기둥형상의 포스트(48)는 금이나 구리 등에 의해 형성되고, 외부 전극(20)과 재배선(30)을 전기적으로 접속한다. 한편, 보호막(42)의 상층에 다시 산화막이나, 폴리이미드 등의 수지막에 의해서 절연층을 형성하고, 그 상부에 재배선(30)을 형성해도 된다.

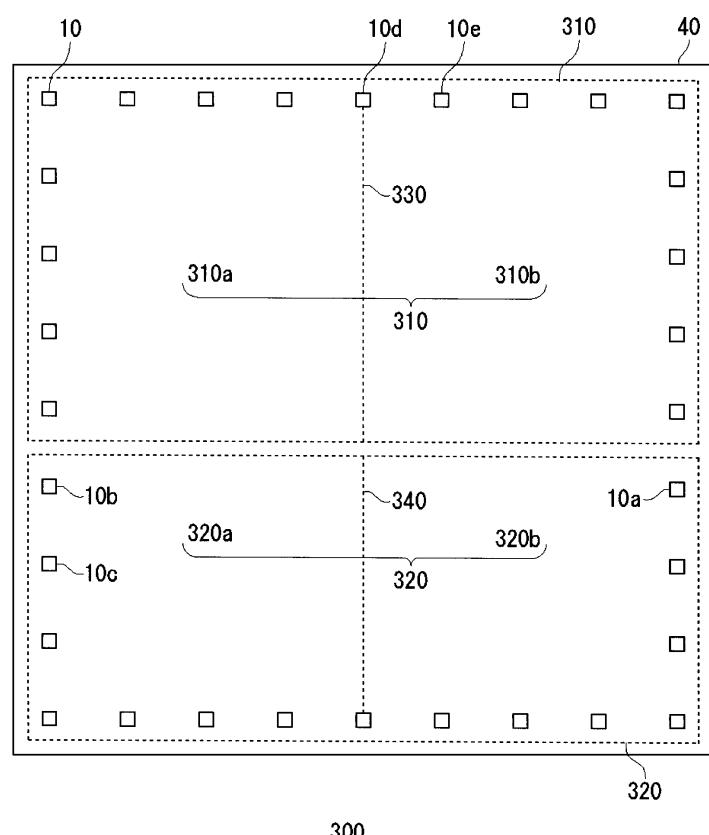

도 3은 반도체 기판(40) 상에 형성되는 반도체 집적 회로(300)의 배치를 도시하는 도면이다. 동 도면에 도시하는 바와 같이, 반도체 집적 회로(300)는 복수의 기능 블록으로서 소신호 회로(310)와, 대신호 회로(320)를 포함하고 있다. 소신호 회로(310)와 대신호 회로(320)간에 발생하는 신호 간섭은 회로의 오동작이나 반도체 집적 회로(300)에 의해 생성되는 신호의 정밀도의 악화의 원인이 되기 때문에, 소신호 회로(310)와 대신호 회로(320)는 2개의 영역으로 나누어 형성되어 있다. 예를 들면, 소신호 회로(310)는 기준 전압이나 정전류를 생성하기 위해서 이용되는 밴드 캡 레퍼런스 회로나, 디지털 아날로그 변환기 등을 포함하고 있다. 또한, 대신호 회로(320)는 부하 회로를 구동하기 위한 출력단에 설치되는 파워 트랜지스터 등을 포함하고 있다.

소신호 회로(310)와 대신호 회로(320)는 전기적인 간섭을 피하기 위해서, 전원 전압과 접지 전압이 각각에 대하여 따로따로 공급된다. 그 때문에, 소신호 회로(310) 및 대신호 회로(320)는 각각이 전원 전압 및 접지 전압을 공급하기 위한 전극 패드를 구비하고 있다.

도면 중, 전극 패드(10a, 10c)는 대신호 회로(320)에 접지 전위를 공급하기 위한 전극 패드이고, 전극 패드(10b)는 대신호 회로(320)에 전원 전압을 공급하기 위한 전극 패드이다. 또한 전극 패드(10d)는 소신호 회로(310)에 전원 전압을 공급하기 위한 전극 패드이고, 전극 패드(10e)는 소신호 회로(310)에 접지 전위를 공급하기 위한 전극 패드이다.

도 1에 되돌아간다. 복수의 외부 전극(20)은 소신호 회로(310)에 접속되는 제1 외부 전극군(210)과, 대신호 회로(320)에 접속되는 제2 외부 전극군(220)으로 나누어 2개의 영역에 배치되어 있다.

전극 패드(10)와 마찬가지로, 외부 전극(20)에 대해서도 소신호 회로(310)와 대신호 회로(320)간의 전기적인 간섭을 피하기 위해서 전원 전압 및 접지 전압은 기능 블록마다 공급된다.

외부 전극(20a)은 접지 단자(GND)로서, 반도체 장치(100)의 외부에서 접지되고, 재배선(30a')을 통해 전극 패드(10a)와 접속되며, 반도체 집적 회로(300)의 대신호 회로(320)에 접지 전압을 공급한다.

외부 전극(20b)은 전원 전압 단자(Vdd)이고, 외부의 전압원에 접속되며, 재배선(30b')에 의해서 전극 패드(10b)와 접속되고, 반도체 집적 회로(300)의 대신호 회로(320)에 전원 전압을 공급한다.

외부 전극(20c)도 외부 전극(20a)과 마찬가지로 접지 단자이고, 재배선(30c')을 통해 전극 패드(10c)와 접속되며, 대신호 회로(320)에 접지 전압을 공급한다.

또한, 본 실시형태에 관한 반도체 장치(100)는 재배선(30a~30c)을 구비한다. 이 재배선(30a~30c)은 제1 외부 전극군(210)과, 제2 외부 전극군(220)이 각각 배치되는 영역의 경계 영역에 부설되어 있다. 재배선(30a~30c)은 각각, 외부 전극(20a~20c)과 접속되어 있다.

여기에서 외부 전극(20a, 20c)은 접지 전위에 고정되고, 외부 전극(20b)은 전원 전압에 고정되는 단자이며, 모두 저임피던스가 된다. 따라서, 이들의 외부 전극(20a~20c)에 접속되는 재배선(30a~30c) 및 재배선(30a'~30c')의 임피던스도 낮게 설정되게 된다.

제1 외부 전극군(210)과 제2 외부 전극군(220)의 경계 영역에 부설되는 재배선(30a~30c) 및 재배선(30a'~30c')은 가능한 한 배선 폭을 두껍게 설계하여 재배선의 임피던스를 저하시키는 것이 바람직하다.

이상과 같이, 본 실시형태에 관한 반도체 장치(100)에 있어서는, 복수의 외부 전극(20)은 접속되는 기능 블록에 따라 제1, 제2 외부 전극군(210, 220)으로 분류되고, 또한 복수의 외부 전극(20)은 복수의 외부 전극군마다 복수의 영역으로 나누어 배치되어 있다.

또한, 제1 외부 전극군(210)과 제2 외부 전극군(220)의 경계 영역에는, 저임피던스의 외부 전극(20)에 접속된 재배선(30a~30c, 30a'~30c')이 부설되어 있다.

재배선에 의해서 제1 외부 전극군(210)과 제2 외부 전극군(220)은 전기적으로 차단되고, 소신호 회로(310) 및 대신호 회로(320)로부터 발생하는 노이즈 신호를, 저임피던스의 재배선(30a~30c) 및 외부 전극(20)을 통해 반도체 장치(100)의 외부로 방출할 수 있고, 복수의 기능 블록간의 신호 간섭을 저감시킬 수 있다.

본 실시형태에 관한 반도체 장치(100)에 의하면, 재배선(30)을 이용하여 소신호 회로(310) 및 대신호 회로(320)간을 분리하기 때문에, 반도체 접적 회로(300) 상의 다층 알루미늄 배선을 이용하여 분리하는 경우와 비교해서, 반도체 기판(40)의 면적, 즉 침 코스트를 증가시키지 않고 신호 간섭을 감소시킬 수 있다. 또한, 재배선(30)의 배선 폭은 외부 전극(20)간에 있어서 허용되는 한 두껍게 하는 것이 가능하기 때문에, 보다 효과적으로 소신호 회로(310)와 대신호 회로(320)를 분리할 수 있다.

또한, 본 실시형태에 관한 반도체 장치(100)에서는 소신호 회로(310)와 대신호 회로(320)의 전기적인 분리를 재배선(30a~30c), 재배선(30a'~30c')을 이용하여 행하기 때문에, 패키지 공정 이전, 즉 도 2에 도시하는 단면도에 있어서, 보호막(42)보다 하층에 관해서는 종래대로 설계를 행할 수 있다.

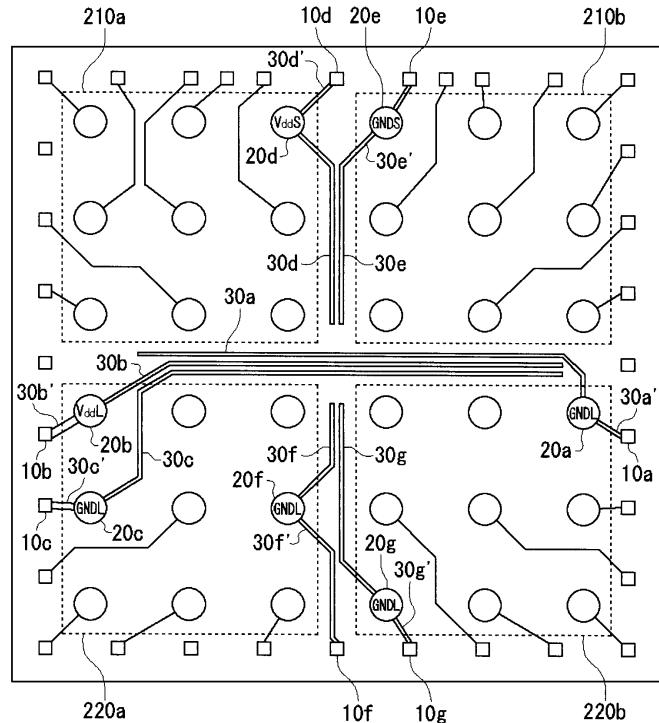

도 4는, 도 1의 반도체 장치(100)의 변형예를 도시하는 도면이다. 도 4의 반도체 장치(100)에서는, 도 3에 도시하는 소신호 회로(310)가 또한, 파선(330)에 의해서 2개의 회로 블록(310a, 310b)으로 분할되어 있다. 또한, 대신호 회로(320)도 파선(340)에 의해서 2개의 회로 블록(320a, 320b)으로 분할되어 있다.

그것에 수반하여, 도 4에 도시하는 바와 같이 각각의 회로 블록(310a, 310b)에 접속되는 외부 전극(20)도, 외부 전극군(210a)과 외부 전극군(210b)으로 나뉜다.

도 4의 반도체 장치(100)의 소신호 회로(310)에는, 재배선(30d, 30d', 30e, 30e')이 부설되어 있다. 재배선(30d')은 소신호 회로(310)에 전원 전압을 공급하기 위한 외부 전극(20d)과 접속되고, 재배선(30e')은 소신호 회로(310)에 접지 전위를 공급하기 위한 외부 전극(20e)과 접속되어 있다. 재배선(30d) 및 재배선(30e)은 외부 전극군(210a)과 외부 전극군(210b)의 경계 영역에 부설되어 있고, 양 외부 전극군(210a, 210b)간을 전기적으로 차단하고 있다.

마찬가지로, 대신호 회로(320)에 대해서도, 도 3의 파선(340)으로 나뉘어지는 2개의 회로 블록(320a, 320b)에 각각 접속되는 외부 전극군(220a, 220b)이 재배선(30f, 30f', 30g, 30g')에 의해 전기적으로 차단된다.

도 4에 도시하는 바와 같이, 본 변형예에 의하면, 2개 이상의 외부 전극군에 대해서도 저임피던스가 되는 외부 전극과 접속되는 재배선에 의해 분할함으로써 전기적으로 분리할 수 있고, 소신호 회로(310) 또는 대신호 회로(320)의 내부의 회로 블록간의 신호 간섭을 저감시킬 수 있다.

이러한 소신호 회로(310)나 대신호 회로(320)를 더욱 복수의 회로 블록으로 분할하여 재배선에 의해 전기적으로 분리하는 기술은, 동일 기능을 가지는 회로가 복수 채널 설치되는 접적 회로에 있어서 각 채널간의 신호 간섭을 방지하고자 하는 경우 등에 적합하게 이용할 수 있다.

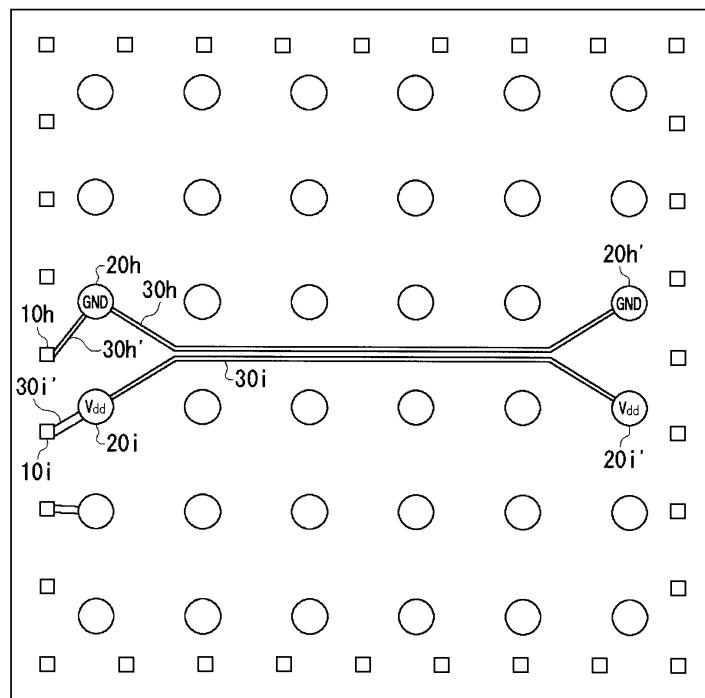

도 5는, 반도체 장치(100)의 다른 변형예를 도시하는 도면이다. 도 5에 있어서, 도 1이나 도 4와 동일한 구성 요소는 생략되어 있다. 이 반도체 장치(100)에 있어서, 외부 전극(20h, 20h')은 각각 접지용 외부 인출 전극이고, 외부 전극(20i, 20i')은 각각 전원 공급용 전극으로 되어 있다.

도 5의 반도체 장치(100)에서는, 재배선(30h)은 그 양단에서 저임피던스의 외부 전극(20h, 20h')과 접속되어 있다. 마찬가지로, 재배선(30i)에 대해서도 그 양단에서 외부 전극(20i, 20i')과 접속되어 있다.

재배선(30h 및 30i)과 같이 양단에서 외부 전극과 접속함으로써, 재배선(30h, 30i)은 각각 외부 전극(20h, 20h' 및 20i, 20i')을 통해 외부의 회로와 접속되게 된다. 그 결과, 1개의 외부 전극을 통해 외부 회로와 접속되는 경우에 비교해서 접속 저항이 1/2이 되기 때문에, 도 1이나 도 4에 도시한 반도체 장치(100)와 비교해서, 재배선의 임피던스를 더욱 낮출 수 있다. 또한, 1개의 외부 전극을 통해 외부 회로와 접속한 경우에는, 외부 전극으로부터 멀어짐에 따라서 재배선의 저항 성분 및 인덕턴스 성분이 증가하게 되어 재배선의 임피던스가 불균일하게 되지만, 양단에 외부 전극을 접속함으로써 재배선의 임피던스를 균일하게 낮출 수 있다.

그 결과, 도 5에 도시하는 반도체 장치(100)에 의하면, 소신호 회로(310) 및 대신호 회로(320)로부터 발생하는 노이즈를, 외부 전극(20h, 20h', 20i, 20i')을 통해 외부 회로에 방출할 수 있기 때문에, 소신호 회로(310)와 대신호 회로(320)간의 신호 간섭을 보다 적합하게 저감시킬 수 있다.

상기 실시형태는 예시이고, 그들의 각 구성 요소나 각 처리 프로세스의 조합에 여러 가지 변형 예가 가능한 것, 또한 그러한 변형에도 본 발명의 범위에 있는 것은 당업자에게 이해되는 바이다.

실시형태에 있어서는, 반도체 집적 회로(300)를 2개 또는 4개의 기능 블록으로 분할하고, 각 기능 블록에 접속되는 외부 전극군의 경계 영역에 재배선을 부설하는 경우에 대해서 설명하였지만, 분할하는 회로 블록의 수는 반도체 장치(100)에 요구되는 특성에 따라서 자유롭게 설정하면 된다.

또한, 실시형태에 있어서는, 소신호 회로(310) 및 대신호 회로(320)가 반도체 장치(100)의 중앙에서 분할되고, 그에 수반하여 제1, 제2 외부 전극군(210, 220)도 반도체 장치(100)의 중앙에서 분할하여 배치되는 경우에 관하여 설명하였지만, 이것에도 한정되지 않고, 각 회로의 사이즈에 따라 임의의 위치에서 분할하면 된다.

또한, 기능 블록인 소신호 회로(310)와 대신호 회로(320)가 배치되는 영역과, 각각의 기능 블록에 접속되는 제1, 제2 외부 전극군(210, 220)이 배치되는 영역은, 반드시 일치할 필요는 없다. 예를 들어, 대신호 회로(320)의 일부가 제1 외부 전극군(210)이 배치되는 영역의 일부와 겹쳐져 있어도 된다.

또한, 복수의 외부 전극군의 경계 영역에 부설되는 재배선의 개수에 대해서도, 기능 블록간의 신호 간섭을 어느 정도 저감 할 것인지를 고려하여 결정하면 된다. 또한, 재배선(30)이 다층이 되는 CSP 구조를 갖는 반도체 장치의 경우, 제1 외부 전극군과 제2 외부 전극군의 경계 영역에 부설되는 재배선을 2중으로 형성해도 되고, 재배선의 임피던스를 더욱 낮추어 신호 간섭을 더욱 저감시킬 수 있다.

또한, 실시형태에 있어서는, 제1 외부 전극군(210)과 제2 외부 전극군(220)의 경계 영역에 부설되는 재배선(30)은, 대신호 회로(320)의 전원 전압 및 접지 전압을 공급하기 위한 외부 전극(20)에 접속되는 경우에 대해서 설명하였지만, 소신호 회로(310)측의 전원 전압, 접지 전압을 공급하기 위한 외부 전극(20)이어도 되고, 또한 그들의 조합이어도 된다.

본 발명은 아날로그 회로, 디지털 회로, 아날로그 디지털 혼재 회로의 모두에 적용할 수 있고, 또한 반도체 제조 프로세스 도, 바이폴라 프로세스, CMOS 프로세스, BiCMOS 프로세스의 모두에 적용할 수 있다.

### 산업상 이용 가능성

본 발명에 관한 반도체 장치에 의해, 상이한 기능 블록에 접속되는 외부 전극간의 신호 간섭을 저감시킬 수 있다.

### 도면의 간단한 설명

도 1은 본 발명의 실시형태에 관한 반도체 장치를 전극 패드측에서 본 도면이다.

도 2는 도 1의 2-2선 단면도이다.

도 3은 반도체 기판 상에 형성되는 반도체 집적 회로의 배치를 도시하는 도면이다.

도 4는 실시형태에 관한 반도체 장치의 변형예를 도시하는 도면이다.

도 5는 실시형태에 관한 반도체 장치의 다른 변형예를 도시하는 도면이다.

<도면의 주요부분에 대한 부호의 설명>

10 : 전극 패드 20 : 외부 전극

30 : 재배선 40 : 반도체 기판

42 : 보호막 48 : 포스트

50 : 밀봉 수지 100 : 반도체 장치

210 : 제1 외부 전극군 220 : 제2 외부 전극군

300 : 반도체 접적 회로 310 : 소신호 회로

320 : 대신호 회로

도면

도면1

도면2

도면3

도면4

도면5