(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4561089号

(P4561089)

(45) 発行日 平成22年10月13日(2010.10.13)

(24) 登録日 平成22年8月6日(2010.8.6)

(51) Int.Cl.

G 11 C 11/406 (2006.01)

F 1

G 11 C 11/34 363 J

G 11 C 11/34 363 K

請求項の数 2 (全 12 頁)

(21) 出願番号 特願2003-411495 (P2003-411495)

(22) 出願日 平成15年12月10日 (2003.12.10)

(65) 公開番号 特開2005-174437 (P2005-174437A)

(43) 公開日 平成17年6月30日 (2005.6.30)

審査請求日 平成18年11月16日 (2006.11.16)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 佐藤 敏彦

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 須原 宏光

最終頁に続く

(54) 【発明の名称】記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

リフレッシュ期間毎にリフレッシュが必要な、4つのメモリバンクを有し、記憶内容の書き込みまたは読み出しが1つのメモリバンクの1つのロウアドレスを対象として行われ、リフレッシュが4つのメモリバンクのそれぞれの同じロウアドレスを対象として行われるメモリセルアレイと、

リフレッシュアドレスを発生するリフレッシュアドレス生成回路と、

前記リフレッシュ期間内における前記リフレッシュアドレスに相当するロウに対する記憶内容の書き込みまたは読み出しの有無を、前記リフレッシュアドレスと、記憶内容の書き込みまたは読み出しがあったロウアドレスとを比較することによって検知し、前記リフレッシュアドレスと、記憶内容の書き込みまたは読み出しがあったロウアドレスとの比較結果の信号を出力する比較回路と、

4つのメモリバンクのうちの、記憶内容の書き込みまたは読み出しがあったいずれか1つのメモリバンクを選択するデコーダと、

4つのメモリバンクのそれぞれに対応して設けられ、それぞれが、前記比較回路から出力された比較結果の信号と、前記デコーダにより選択された1つのメモリバンクに対する記憶内容の書き込みまたは読み出しが実行中であることを表す信号との論理積演算を行い、前記リフレッシュアドレスに相当するロウに対する記録内容の書き込みまたは読み出しが行われたことを検知した場合、一致信号を出力する4つのAND回路と、

4つのメモリバンクのそれぞれに対応して設けられ、それぞれが、前段の前記AND回路

10

20

から前記一致信号が出力された時刻から、次の前記リフレッシュ期間の開始時刻までの間、前記リフレッシュアドレスに相当するロウに対するリフレッシュ動作を抑止することを表すリフレッシュ抑止信号を出力する4つのリフレッシュ動作抑止回路と、

前記リフレッシュ動作抑止回路から前記リフレッシュ抑止信号が出力されている間、前記リフレッシュアドレスに相当するロウに対するリフレッシュ動作を抑止するタイミング発生回路と

を備える記憶装置。

【請求項2】

前記リフレッシュ動作抑止回路は、前記リフレッシュ期間内において前記リフレッシュアドレスに相当するロウおよびカラム方向のブロックに対し、記憶内容の書き込みまたは読み出しの有無を検知し、前記リフレッシュアドレスに相当するロウおよびカラム方向のブロックに対し記憶内容の書き込みまたは読み出しが実行された場合、前記リフレッシュアドレスに相当するロウおよびカラム方向のブロックに対するリフレッシュ動作を抑止する

10

請求項1に記載の記憶装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、リフレッシュを行う必要のあるダイナミック型記憶素子を用いた記憶装置において、不必要なリフレッシュ動作を抑制し、余分なリフレッシュ動作による消費電流を削減し、さらに不要なリフレッシュ動作要求回数を削減した分、記憶装置を含むシステムとしての機能の効率化を図れる記憶装置に関する。

20

【背景技術】

【0002】

従来より、2進情報を記憶し、一定時間経過するまでにリフレッシュしないと記憶内容を喪失するダイナミック型記憶素子を用いたDRAMが、コンピュータ装置などの記憶装置として用いられている。

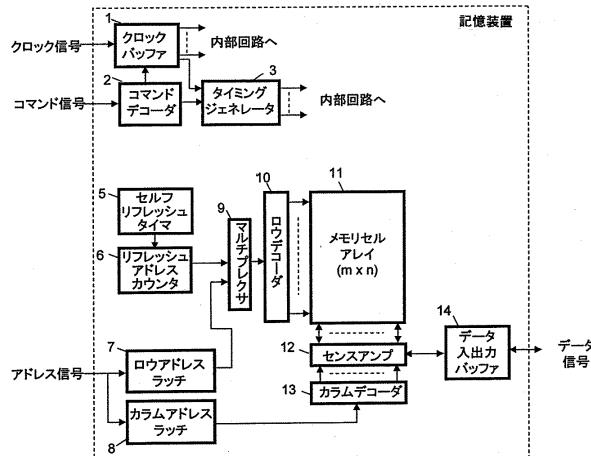

図1は、このダイナミック型記憶素子を用いた従来のDRAMの構成を示すブロック図である。このDRAMの構成は、クロックバッファ1、コマンドデコーダ2、タイミングジェネレータ3、セルフリフレッシュタイム5、リフレッシュアドレスカウンタ6、ロウアドレスラッチ7、カラムアドレスラッチ8、マルチプレクサ9、ロウデコーダ10、メモリセルアレイ11、センスアンプ12、カラムデコーダ13およびデータ入出力バッファ14を含む。

30

【0003】

クロックバッファ1は、外部から供給されたクロック信号を受信して内部回路に分配するクロック信号のバッファ回路である。コマンドデコーダ2は、外部からのコマンド信号を解読してライト、リード、オートリフレッシュなどの動作を判別する回路である。

タイミングジェネレータ3は、内部動作に必要な各種タイミング信号を発生する回路である。セルフリフレッシュタイム5は、セルフリフレッシュモード時のリフレッシュ動作間隔を決定するクロックを発生する回路である。リフレッシュアドレスカウンタ6は、外部からのオートリフレッシュおよびセルフリフレッシュ時においてリフレッシュ動作を行う毎に1インクリメントされるカウンタで、リフレッシュ時のロウアドレスを発生する回路である。ロウアドレスラッチ7およびカラムアドレスラッチ8は、外部から時分割に送られてくるアドレス信号をロウアドレスとカラムアドレスに分けて格納する。マルチプレクサ9は、リフレッシュアドレスと通常動作時のロウアドレスのいずれかを選択する回路である。ロウデコーダ10はm個のロウの1個を選択する回路である。メモリセルアレイ11は、2進情報を記憶するメモリセルをmロウ×nカラムのアレイ状に配置したもので、1個のロウが選択されるとこれに接続されているn個のメモリセルの情報がセンスアンプに出力される。センスアンプ12はメモリセルからの微小信号を増幅する回路である。カラムデコーダ13はn個のカラムの中から外部データ信号に相当する1組のデータを選

40

50

択する回路である。データ入出力バッファ14は、ライト動作時にライトデータを入力し、リード動作時にリードデータを出力する回路である。

#### 【0004】

次に動作について説明する。

図1において、外部からのクロック信号をクロックバッファ1が受信して内部回路に分配する。また、外部からのコマンド信号をコマンドデコーダ2が解読してライト、リード、オートリフレッシュなどの動作を判別し、タイミングジェネレータ3が内部動作に必要な各種タイミングを発生する。また、セルフリフレッシュモード時のリフレッシュ動作間隔を決定するクロックをセルフリフレッシュタイム5が発生し、外部からのオートリフレッシュおよびセルフリフレッシュ時に、リフレッシュアドレスカウンタ6はリフレッシュ動作を行う毎に“1”加算されてリフレッシュ時のロウアドレスを発生する。外部から時分割に送られてくるアドレス信号はロウアドレスとカラムアドレスに分けられ、それぞれロウアドレスラッチ7およびカラムアドレスラッチ8に格納される。

#### 【0005】

リフレッシュアドレスと通常動作時のロウアドレスのいずれかがマルチプレクサ9により選択され、ロウデコーダ10によりm個のロウの1個が選択される。メモリセルアレイ11は、2進情報を記憶するメモリセルをmロウ×nカラムのアレイ状に配置したもので、1個のロウが選択されるとこれに接続されているn個のメモリセルの情報がセンスアンプ12に出力される。前記メモリセルの情報として出力された微小信号はセンスアンプ12により増幅される。

#### 【0006】

カラムデコーダ13はn個のカラムの中から外部データ信号に相当する1組のデータを選択し、ライト動作時にはデータ入出力バッファ14によりライトデータが入力され、またリード動作時にはデータ入出力バッファ14を介してリードデータが出力される。

#### 【0007】

リード動作では、外部アドレス信号のロウアドレスによりメモリセルアレイ11内の1個のロウが指定され、このロウに接続されたn個のメモリセル情報がセンスアンプ12で増幅される。前記センスアンプからのリードデータは、カラムデコーダ13により1組のデータが選択され、データ入出力バッファ14を介して出力される。

#### 【0008】

また、ライト動作では、メモリセルアレイ11に記憶されている情報を読み出してセンスアンプ12で増幅した後、カラムデコーダ13で指定したカラムを外部からのライトデータで置き換えてメモリセルに書き込む。

#### 【0009】

オートリフレッシュ動作はコマンド信号により指定され、マルチプレクサ9がリフレッシュアドレスカウンタ6の出力をロウデコーダに出力してメモリセルアレイ11のロウが選択される。選択されたロウにおけるn個のカラムデータはセンスアンプ12で増幅されて、再度メモリセルに書き込まれる。

#### 【0010】

セルフリフレッシュモードにはセルフリフレッシュエントリコマンドで入り、このセルフリフレッシュモードに入るとセルフリフレッシュタイム5にもとづいて内部で自動的にリフレッシュ動作を行う。

#### 【0011】

このように、一定期間ごとにリフレッシュ動作を行なっているものとして、アクセス判別回路によりCPUあるいは他のバスマスターのアクセス対象を識別し、前記アクセス対象がDRAMでない期間に一定期間ごとにリフレッシュ動作を行い、また、DRAMのあるバンクがアクセス対象であるときにはリフレッシュ可能な他のバンクに対しリフレッシュ動作を行うDRAMのリフレッシュ方式がある（例えば、特許文献1参照）。

【特許文献1】特開平7-45073号公報

【発明の開示】

10

20

30

40

50

**【発明が解決しようとする課題】**

**【0012】**

かかる従来のDRAMのリフレッシュ方式には、以下の短所が付随している。

リフレッシュ期間内のリフレッシュアドレスカウンタ6に相当するロウアドレスに対して、既にリード動作またはライト動作が行われている場合、該ロウに対応するメモリセルのリフレッシュ動作は不要であるにもかかわらずリフレッシュ動作が行われ、前記不要なリフレッシュ動作を行うことに伴って余分な電流が消費されるという課題があった。

**【0013】**

本発明は、このような事情に鑑みてなされたものであり、不要なリフレッシュ動作を行うことに伴う余分な電流消費をなくし、また、余分なリフレッシュ動作要求をなくすことによりシステムとしての性能向上を図れる記憶装置を提供することを目的とする。10

**【課題を解決するための手段】**

**【0014】**

本発明の記憶装置は、リフレッシュ期間毎にリフレッシュが必要な、4つのメモリバンクを有し、記憶内容の書き込みまたは読み出しが1つのメモリバンクの1つのロウアドレスを対象として行われ、リフレッシュが4つのメモリバンクのそれぞれの同じロウアドレスを対象として行われるメモリセルアレイと、リフレッシュアドレスを発生するリフレッシュアドレス生成回路と、前記リフレッシュ期間内における前記リフレッシュアドレスに相当するロウに対する記憶内容の書き込みまたは読み出しの有無を、前記リフレッシュアドレスと、記憶内容の書き込みまたは読み出しがあったロウアドレスとを比較することによって検知し、前記リフレッシュアドレスと、記憶内容の書き込みまたは読み出しがあったロウアドレスとの比較結果の信号を出力する比較回路と、4つのメモリバンクのうちの、記憶内容の書き込みまたは読み出しがあったいずれか1つのメモリバンクを選択するデコーダと、4つのメモリバンクのそれぞれに対応して設けられ、それぞれが、前記比較回路から出力された比較結果の信号と、前記デコーダにより選択された1つのメモリバンクに対する記憶内容の書き込みまたは読み出しが実行中であることを表す信号との論理積演算を行い、前記リフレッシュアドレスに相当するロウに対する記録内容の書き込みまたは読み出しが行われたことを検知した場合、一致信号を出力する4つのAND回路と、4つのメモリバンクのそれぞれに対応して設けられ、それぞれが、前段の前記AND回路から前記一致信号が出力された時刻から、次の前記リフレッシュ期間の開始時刻までの間、前記リフレッシュアドレスに相当するロウに対するリフレッシュ動作を抑止することを表すリフレッシュ抑止信号を出力する4つのリフレッシュ動作抑止回路と、前記リフレッシュ動作抑止回路から前記リフレッシュ抑止信号が出力されている間、前記リフレッシュアドレスに相当するロウに対するリフレッシュ動作を抑止するタイミング発生回路とを備える。20

**【発明の効果】**

**【0015】**

本発明の記憶装置によれば、不要なリフレッシュ動作要求を記憶装置に出さないようになり、システムとしての性能向上を図れる効果がある。30

**【発明を実施するための最良の形態】**

**【0016】**

不要なリフレッシュ動作を行うことに伴う余分な電流消費を抑制し、また、余分なリフレッシュ動作要求をなくすことにより記憶装置としての性能向上を図れる記憶装置を提供するという目的を、リフレッシュアドレスをリフレッシュアドレス生成回路が発生すると、リフレッシュ動作抑止回路が、リフレッシュ期間内において前記リフレッシュアドレスに対する記憶内容の書き込みまたは読み出しの有無を検知し、前記リフレッシュアドレスに対する前記書き込みまたは読み出しがあると、前記リフレッシュアドレスに対するリフレッシュ動作を抑止することで実現した。40

また、不要なリフレッシュ動作を行うことに伴う余分な電流消費を抑制し、また、余分なリフレッシュ動作要求をなくすことにより記憶装置としての性能向上を図れる記憶装置のリフレッシュ方法を提供するという目的を、リフレッシュアドレスを発生し、前記リフ50

レッシュ期間内において前記リフレッシュアドレスに対する記憶内容の書き込みまたは読み出しの有無を検知し、前記リフレッシュアドレスに対する前記書き込みまたは読み出しがあると、前記リフレッシュアドレスに対するリフレッシュ動作を抑止することで実現した。

【実施例 1】

【0017】

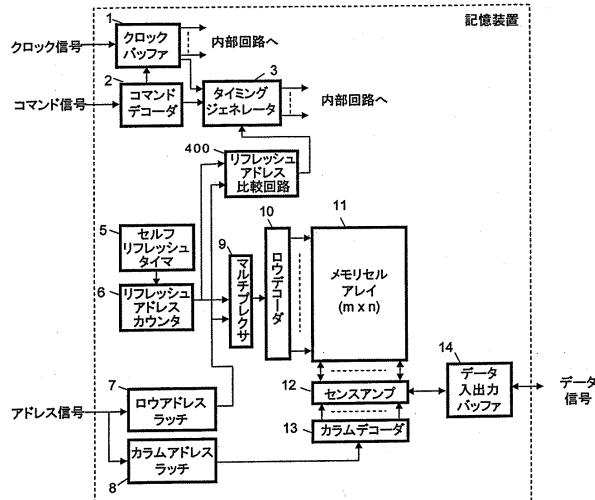

図2は、この実施例1の記憶装置の構成を示すブロック図である。なお、図2において図1と同一または相当の部分については同一の符号を付してある。この記憶装置は、2進情報を記憶し、一定時間の間にリフレッシュ動作を行わないと記憶内容を喪失するダイナミック型記憶素子を用いた記憶装置において、リフレッシュアドレスを発生する手段と、リフレッシュ期間内における前記リフレッシュアドレスに対するライト動作またはリード動作要求を検知し、前記リフレッシュ期間内の前記リフレッシュアドレスに対するライト動作またはリード動作要求を検知すると、内部動作に必要な各種タイミングを発生するタイミングジェネレータ3を制御して前記リフレッシュ期間内の前記リフレッシュアドレスに対するリフレッシュ動作を抑止する手段を含む。10

【0018】

この実施例1の記憶装置の構成は、クロックバッファ1、コマンドデコーダ2、タイミングジェネレータ3、セルフリフレッシュタイム5、リフレッシュアドレスカウンタ(リフレッシュアクセス生成回路)6、ロウアドレスラッチ7、カラムアドレスラッチ8、マルチプレクサ9、ロウデコーダ10、メモリセルアレイ11、センスアンプ12、カラムデコーダ13、データ入出力バッファ14およびリフレッシュアドレス比較回路(リフレッシュ動作抑止回路)400を含む。20

【0019】

クロックバッファ1は、外部から供給されたクロック信号を受信して内部回路に分配するクロック信号のバッファ回路である。コマンドデコーダ2は、外部からのコマンド信号を解読してライト、リード、オートリフレッシュなどの動作を判別する回路である。タイミングジェネレータ3は、内部動作に必要な各種タイミング信号を発生する回路である。セルフリフレッシュタイム5は、セルフリフレッシュモード時のリフレッシュ動作間隔を決定するクロックを発生する回路である。リフレッシュアドレスカウンタ6は、外部からのオートリフレッシュおよびセルフリフレッシュ時においてリフレッシュ動作を行う毎にその内部状態が1インクリメントされるカウンタであり、リフレッシュ時のロウアドレスを発生する回路である。ロウアドレスラッチ7およびカラムアドレスラッチ8は、外部から時分割に送られてくるアドレス信号をロウアドレスとカラムアドレスに分けて格納する。マルチプレクサ9は、リフレッシュアドレスと通常動作時のロウアドレスのいずれかを選択する回路である。ロウデコーダ10はm個のロウの1個を選択する回路である。メモリセルアレイ11は、2進情報を記憶するメモリセルをmロウ×nカラムのアレイ状に配置したもので、1個のロウが選択されるとこれに接続されているn個のメモリセルの情報がセンスアンプに出力される。センスアンプ12はメモリセルからの微小信号を増幅する回路である。カラムデコーダ13はn個のカラムの中から外部データ信号に相当する1組のデータを選択する回路である。データ入出力バッファ14は、ライト動作時にライトデータを入力し、リード動作時にリードデータを出力する回路である。30

【0020】

リフレッシュアドレス比較回路400は、リフレッシュアドレスを発生する手段であるリフレッシュアドレスカウンタ6のリフレッシュアドレスと、ライト動作、リード動作におけるロウアドレスラッチ7から供給されるアドレス情報を比較し、リフレッシュ期間ごとに該リフレッシュアドレスが示すロウに対するライト動作またはリード動作を検知し、該ロウが既にライト動作またはリード動作の対象になった場合は、タイミングジェネレータ3を制御し、リフレッシュ動作が実行されないようにするものである。40

【0021】

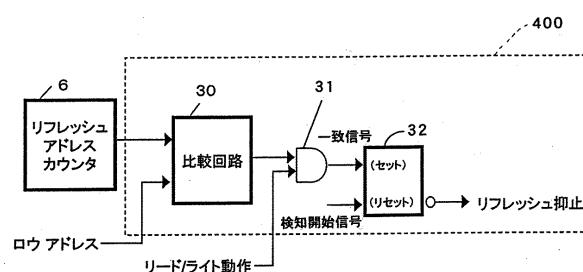

図3は、リフレッシュアドレス比較回路400の構成を示すブロック図である。50

このリフレッシュアドレス比較回路 400 は、比較回路 30、AND 回路 31、リフレッシュ抑止レジスタ 32 を含む。比較回路 30 はリフレッシュアドレスカウンタ 6 から供給されるリフレッシュアドレスと、ライト動作時やリード動作時のロウアドレスとを比較し、その比較結果を出力する回路である。AND 回路 31 は、前記比較回路 30 から出力される比較結果と、ライト動作やリード動作実行中であることを示す信号、またはライト動作要求信号やリード動作要求信号との論理積演算を行い、リフレッシュアドレスが示すロウに対するライト動作またはリード動作の実行を検知し、ライト動作またはリード動作が行われた場合には一致信号を出力する回路である。リフレッシュ抑止レジスタ 32 は検知開始信号でリセットされ、AND 回路 31 から出力される前記一致信号でセットされ、前記リフレッシュアドレスとリード動作時、ライト動作時のロウアドレスが検知期間内（検知開始信号が出力され次の検知開始信号が出力されるまでの期間であり、リフレッシュ期間に対応する）で 1 度でも一致すると前記一致信号によりセットされ、“Low” レベルのリフレッシュ抑止信号を出力するフリップフロップ回路である。

#### 【0022】

次に動作について説明する。

図 2において、外部からのクロック信号をクロックバッファ 1 が受信して内部回路に分配する。また、外部からのコマンド信号をコマンドデコーダ 2 が解読してライト、リード、オートリフレッシュなどの動作を判別し、タイミングジェネレータ 3 が内部動作に必要な各種タイミングを発生する。また、セルフリフレッシュモード時のリフレッシュ動作間隔を決定するクロックをセルフリフレッシュタイマ 5 が発生し、外部からのオートリフレッシュおよびセルフリフレッシュ時に、リフレッシュアドレスカウンタ 6 はリフレッシュ動作を行う毎に +1 されてリフレッシュ時のロウアドレスを発生する。外部から時分割に送られてくるアドレス信号はロウアドレスとカラムアドレスに分けられ、それぞれロウアドレスラッチ 7 およびカラムアドレスラッチ 8 に格納される。

#### 【0023】

リフレッシュアドレスと通常動作時のロウアドレスのいずれかがマルチプレクサ 9 により選択され、ロウデコーダ 10 により m 個のロウの 1 個が選択される。メモリセルアレイ 11 は、2 進情報を記憶するメモリセルを m ロウ × n カラムのアレイ状に配置したもので、1 個のロウが選択されるとこれに接続されている n 個のメモリセルの情報がセンスアンプ 12 に出力される。前記メモリセルの情報として出力された微小信号はセンスアンプ 12 により増幅される。

#### 【0024】

カラムデコーダ 13 は n 個のカラムの中から外部データ信号に相当する 1 組のデータを選択し、ライト動作時にはデータ入出力バッファ 14 によりライトデータが入力され、またリード動作時にはデータ入出力バッファ 14 を介してリードデータが出力される。

#### 【0025】

リード動作では、外部アドレス信号のロウアドレスによりメモリセルアレイ 11 内の 1 個のロウが指定され、このロウに接続された n 個のメモリセル情報がセンスアンプ 12 で増幅される。前記センスアンプからのリードデータは、カラムデコーダ 13 により 1 組のデータが選択され、データ入出力バッファ 14 を介して出力される。

#### 【0026】

また、ライト動作では、メモリセルアレイ 11 に記憶されている情報を読み出してセンスアンプ 12 で増幅した後、カラムデコーダ 13 で指定したカラムを外部からのライトデータで置き換えてメモリセルに書き込む。

#### 【0027】

オートリフレッシュ動作はコマンド信号により指定され、マルチプレクサ 9 がリフレッシュアドレスカウンタ 6 の出力をロウデコーダに出力し、メモリセルアレイ 11 のロウが選択される。選択されたロウにおける n 個のカラムデータはセンスアンプ 12 で増幅されて、再度メモリセルに書き込まれる。

#### 【0028】

10

20

30

40

50

セルフリフレッシュモードにはセルフリフレッシュエントリコマンドで入り、このセルフリフレッシュモードに入るとセルフリフレッシュタイム5にもとづいて内部で自動的にリフレッシュ動作を行う。

#### 【0029】

さらに、この記憶装置では、リフレッシュアドレス比較回路400において、リフレッシュアドレスカウンタ6から供給されるリフレッシュアドレスと、ライト動作時やリード動作時のロウアドレスとを図3に示す比較回路30において比較し、その比較結果をAND回路31の一方の入力端子へ出力する。AND回路31の他方の入力端子には、ライト動作やリード動作実行中であることを示す信号、またはライト動作要求信号やリード動作要求信号が入力される。この結果、AND回路31では、前記比較回路30から出力される比較結果と、前記ライト、リード動作実行中であることを示す信号、または前記ライト、リード動作要求信号との論理積演算が行われ、前記リフレッシュアドレスが示すロウに対しライト動作またはリード動作が実行されたかが検知される。そして、前記リフレッシュアドレスに対しライト動作またはリード動作が行われた場合にはAND回路31からリフレッシュ抑止レジスタ32のセット入力端子へ一致信号が出力され、リフレッシュ抑止レジスタ32はセットされて“Low”レベルのリフレッシュ抑止信号を出力する。また、リフレッシュ抑止レジスタ32のリセット入力端子には検知開始信号が入力されるため、この検知開始信号でリフレッシュ抑止レジスタ32はリセットされる。

10

#### 【0030】

この結果、前記リフレッシュアドレスとリード動作時、ライト動作時のロウアドレスが検知期間内、すなわちリフレッシュ期間内で1度でも一致すると、リフレッシュ抑止レジスタ32は前記一致信号によりセットされ、“Low”レベルのリフレッシュ抑止信号をタイミングジェネレータ3へ出力しタイミングジェネレータ3を制御し、前記リフレッシュ期間内の前記リフレッシュアドレスに対応するリフレッシュ動作を禁止して消費電流を抑制する。

20

#### 【0031】

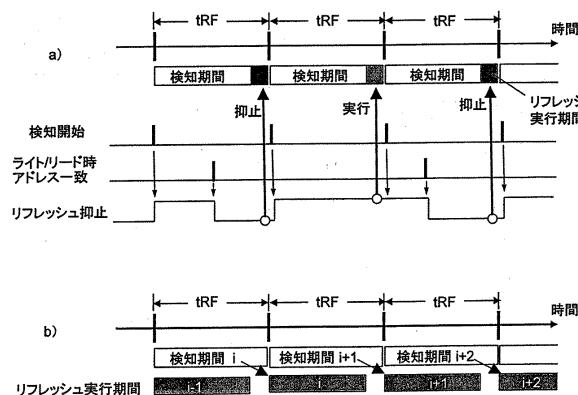

図4は、検知期間とリフレッシュ実行期間の一例を示すタイミングチャートであり、同図(a)ではリフレッシュ期間tRF内に検知期間とリフレッシュ実行期間が存在し、また、同図(b)では検知期間に対してリフレッシュ実行期間が1サイクルずれている。

30

#### 【0032】

以上のように、この実施例1によれば、リフレッシュアドレスとリード動作時、ライト動作時のロウアドレスが検知期間内で1度でも一致すると、リフレッシュアドレス比較回路400が出力するリフレッシュ抑止信号によりタイミングジェネレータ3を制御し、前記検知期間内、すなわちそのリフレッシュ期間内の前記リフレッシュアドレスに対応するリフレッシュ動作を禁止できるため、不要なリフレッシュ動作を行うことに伴う余分な電流消費を削減できる記憶装置およびそのリフレッシュ方法を提供できる効果がある。

#### 【実施例2】

#### 【0033】

この実施例2では、ダイナミック型記憶素子を用いた記憶装置は、4つのメモリバンクA、B、C、Dの4バンク構成とする。

40

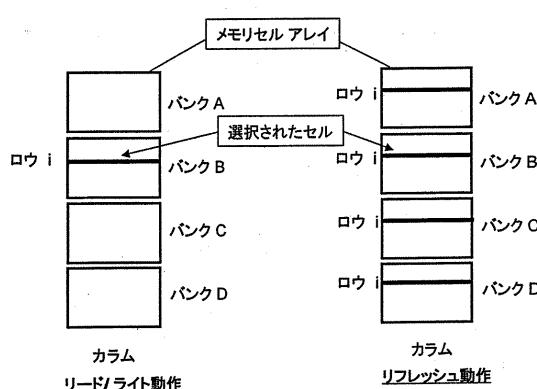

図5は、リード、ライト動作時の選択セル範囲がリフレッシュ動作時の選択セル範囲より小さい場合を示す説明図である。リード、ライト動作時は、1つのバンクに対してアクセスされるが、リフレッシュ動作時はバンクA～Dの全てのバンクに対してアクセスされる。

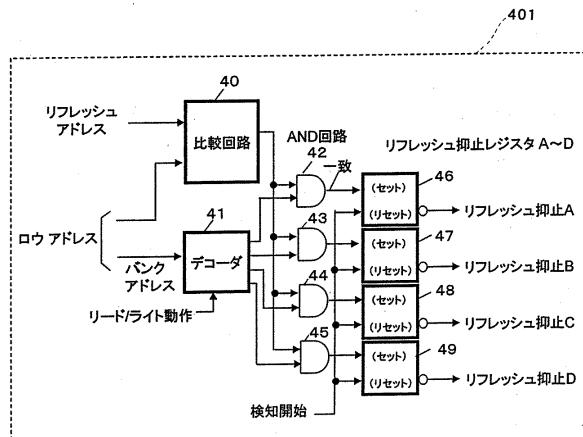

図6は、この実施例2の記憶装置のリフレッシュアドレス比較回路401の構成を示すブロック図である。なお、この実施例2の記憶装置の構成は、図2に示す前記実施例1の記憶装置の構成と同様であるが、この実施例2ではリフレッシュアドレス比較回路(リフレッシュ動作抑止回路)401の構成が図3に示した実施例1のリフレッシュアドレス比較回路の構成と異なる。

図6は、この実施例2のリフレッシュアドレス比較回路401の構成を示すブロック図

50

である。このリフレッシュアドレス比較回路 401 の構成は、比較回路 40、デコーダ 41、AND 回路 42, 43, 44, 45、リフレッシュ抑止レジスタ 46, 47, 48, 49 を含む。比較回路 40 は、前記実施例 1 で説明した図 3 における比較回路 30 と同様の機能を有している。デコーダ 41 はバンクアドレス A ~ D の中のいずれか 1 つを選択し、AND 回路 42, 43, 44, 45 とリフレッシュ抑止レジスタ 46, 47, 48, 49 はそれぞれバンク A、B、C、D に対応してリフレッシュ抑止信号 A、B、C、D を出力する。このような構成にすることでそれぞれのバンクごとにリフレッシュアドレスに対応した口ウにライトまたはリード動作があったかを検知でき、ライトまたはリード動作があった場合にはそのバンクに対するリフレッシュ動作を抑止する。

## 【0034】

10

以上のように、この実施例 2 によれば、リード、ライト動作時の選択セル範囲がリフレッシュ動作時の選択セル範囲より小さい場合でも、リフレッシュアドレスとリード動作時、ライト動作時のロウアドレスが検知期間内、すなわちリフレッシュ期間内で 1 度でも一致すると、リフレッシュアドレス比較回路 401 が出力するリフレッシュ抑止信号によりタイミングジェネレータ 3 を制御し、そのリフレッシュ期間内の前記リフレッシュアドレスに対応するバンクについてリフレッシュ動作を禁止できるため、不要なリフレッシュ動作を行うことに伴う余分な電流消費を削減できる記憶装置およびそのリフレッシュ方法を提供できる効果がある。

## 【実施例 3】

## 【0035】

20

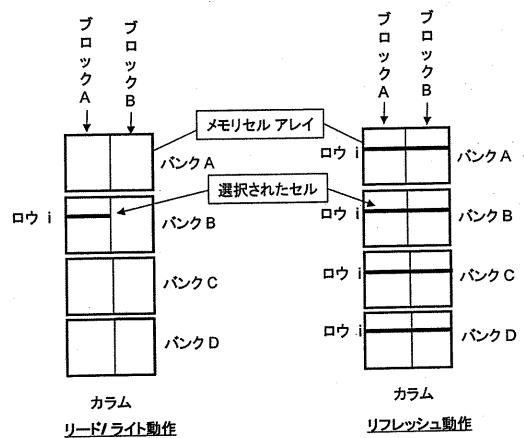

図 7 は、この実施例 3 の記憶装置を説明するためのリード、ライト動作時の選択セル範囲がリフレッシュ動作時の選択セル範囲よりさらに小さい場合を示す説明図である。このような場合には、前記実施例 2 の図 6 に示したリフレッシュアドレス比較回路 401 におけるバンクに対応する回路を、さらに各ブロック A、B に対応できるように拡張することで容易に構成できる。

## 【0036】

すなわち、この実施例 3 のリフレッシュアドレス比較回路は、記憶内容の書き込みまたは読み出しの対象となるアクセス選択セル範囲がリフレッシュ動作の対象となるリフレッシュ選択セル範囲よりも小さい場合、前記アクセス選択セル範囲ごとに前記リフレッシュアドレスに対する記憶内容の書き込みまたは読み出しの有無を検知し、前記リフレッシュアドレスに対する前記書き込みまたは読み出しがあると、前記書き込みまたは読み出しがあった前記アクセス選択セル範囲の前記リフレッシュアドレスに対するリフレッシュ動作を抑止する。そして、リフレッシュ期間内において前記リフレッシュアドレスに相当するロウおよびカラム方向のブロックに対し、記憶内容の書き込みまたは読み出しの有無を検知し、前記リフレッシュアドレスに相当するロウおよびカラム方向のブロックに対し記憶内容の書き込みまたは読み出しが実行された場合、前記リフレッシュアドレスに相当するロウおよびカラム方向のブロックに対するリフレッシュ動作を抑止する。

30

## 【0037】

この実施例 3 によれば、リード、ライト動作時の選択セル範囲がリフレッシュ動作時の選択セル範囲よりさらに小さい、ロウとカラム方向のブロックとにより規定される範囲の場合に対しても、リフレッシュアドレス比較回路が出力する前記範囲ごとのリフレッシュ抑止信号によりタイミングジェネレータ 3 を制御し、そのリフレッシュ期間内の前記リフレッシュアドレスに対する前記範囲についてリフレッシュ動作を禁止できるため、不要なリフレッシュ動作を行うことに伴う余分な電流消費を削減できる記憶装置およびそのリフレッシュ方法を提供できる効果がある。

40

## 【実施例 4】

## 【0038】

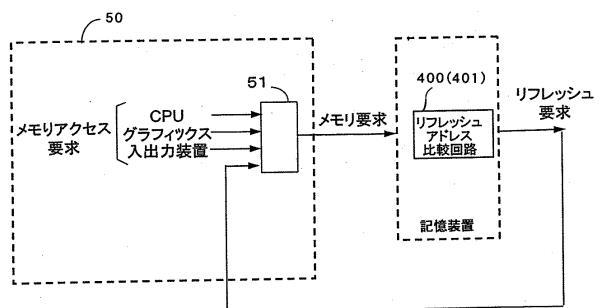

図 8 は、この実施例 4 の記憶装置を示すブロック図であり、記憶装置にリフレッシュ動作が必要な場合のみメモリ要求信号を記憶制御装置に送出する。この実施例 4 の記憶装置の構成は、記憶制御装置 50 のメモリアクセス制御回路 51 と、記憶装置のリフレッシュ

50

アドレス比較回路を含む。この記憶装置と、そのリフレッシュアドレス比較回路は、前記実施例1、実施例2、実施例3の記憶装置、リフレッシュアドレス比較回路と同等のものである。

【0039】

記憶制御装置50におけるメモリアクセス制御回路51は、CPU、グラフィックス装置、入出力装置からのメモリアクセス要求と前記記憶装置からのリフレッシュ要求とを優先順位付けして制御し、前記記憶装置にメモリ要求を送出する。前記記憶装置からのリフレッシュ要求は、前述したリフレッシュアドレス比較回路内でリフレッシュ動作要求が必要な場合にのみ送出するように構成される。

【0040】

前記実施例1、実施例2、実施例3の構成に加えてこのような構成をとることにより、不必要なリフレッシュ動作要求を記憶装置に出さないようにすることができる、この空いた時間に通常のライト動作またはリード動作要求を出すことが出来、システムとしての性能向上を図れる記憶装置およびそのリフレッシュ方法を提供できる効果がある。

【図面の簡単な説明】

【0041】

【図1】従来のDRAMの構成を示すブロック図である。

【図2】本発明の実施例1の記憶装置の構成を示すブロック図である。

【図3】本発明の実施例1の記憶装置におけるリフレッシュアドレス比較回路の構成を示すブロック図である。

【図4】検知期間とリフレッシュ実行期間の一例を示すタイミングチャートである。

【図5】本発明の実施例2の記憶装置を説明するためのリード、ライト動作時の選択セル範囲がリフレッシュ動作時の選択セル範囲より小さい場合を示す説明図である。

【図6】本発明の実施例2の記憶装置のリフレッシュアドレス比較回路の構成を示すブロック図である。

【図7】本発明の実施例3の記憶装置を説明するためのリード、ライト動作時の選択セル範囲がリフレッシュ動作時の選択セル範囲よりさらに小さい場合を示す説明図である。

【図8】この実施例4の記憶装置を示すブロック図である。

【符号の説明】

【0042】

6 ……リフレッシュアドレスカウンタ（リフレッシュアドレス生成回路）、400, 401 ……リフレッシュアドレス比較回路（リフレッシュ動作抑止回路）、50 ……記憶制御装置。

10

20

30

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開平07-057460(JP,A)

特開平02-185791(JP,A)

特開平03-283086(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 40