(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5705867号

(P5705867)

(45) 発行日 平成27年4月22日(2015.4.22)

(24) 登録日 平成27年3月6日(2015.3.6)

(51) Int.Cl.

HO3M 13/29 (2006.01)

F 1

HO3M 13/29

請求項の数 55 (全 30 頁)

(21) 出願番号 特願2012-537113 (P2012-537113)

(86) (22) 出願日 平成22年10月29日 (2010.10.29)

(65) 公表番号 特表2013-509824 (P2013-509824A)

(43) 公表日 平成25年3月14日 (2013.3.14)

(86) 國際出願番号 PCT/US2010/054703

(87) 國際公開番号 WO2011/059813

(87) 國際公開日 平成23年5月19日 (2011.5.19)

審査請求日 平成24年7月2日 (2012.7.2)

(31) 優先権主張番号 12/608,919

(32) 優先日 平成21年10月29日 (2009.10.29)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】 2次置換多項式インターバを備えたLTEターボ・デコーダのためのAPP (APR I OR I PROBABILITY:先驗確率)ストレージ設計

## (57) 【特許請求の範囲】

## 【請求項1】

競合の無いメモリ・アクセスを提供するターボ・デコーダを適用することを容易にする無線通信システムにおいて使用される方法であつて、

事後確率(APP)ランダム・アクセス・メモリ(RAM)を特定することと、

前記APP RAMを、M個のRAMファイルへ構成することと、

すべてのAPP値を、2次置換多項式(QPP)ターボ・インターバに基づいて、少なくとも2つのインターバ・サブ・グループに分割することと、ここで、前記分割は、 $n = 1, \dots, M$ のうちのn番目のインターバ・サブ・グループを、 $nL + Mk + j$ ( $j = 0, 1, 2, 3$ )のフォーマットでフォーマットすることを備え、ここで、前記Lは、前記インターバ・サブ・グループの長さであり、nは、前記M個のインターバ・サブ・グループのおおのの内のインデックスであり、前記kは、サブ・グループ・インデックスである。

10

個別のインターバ・サブ・グループを、個別のAPP RAMファイルにマップすることと、

インターバ・サブ・グループ内の第1のAPP値と、別のインターバ・サブ・グループ内の第2のAPP値とに同時にアクセスすることと、

を備える方法。

## 【請求項2】

前記ターボ・デコーダが、MAPパラレル・デコーダを備え、前記MAPパラレル・デ

コーダが、前記インタリープ・サブ・グループのうちの少なくとも1つへの読み取りまたは書き込みのうちの少なくとも1つを用いる、請求項1に記載の方法。

【請求項3】

前記ターボ・デコーダが、MAPパラレル・デコーダを備え、前記MAPパラレル・デコーダが、前記インタリープ・サブ・グループのうちの少なくとも1つへの読み取りまたは書き込みのうちの少なくとも1つを用いるように隔離された、請求項1に記載の方法。

【請求項4】

Mが2である、請求項1に記載の方法。

【請求項5】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用すること、をさらに備える請求項4に記載の方法。 10

【請求項6】

Mが4である、請求項1に記載の方法。

【請求項7】

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用すること、をさらに備える請求項6に記載の方法。

【請求項8】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用すること、をさらに備える請求項6に記載の方法。

【請求項9】

Mが8である、請求項1に記載の方法。

【請求項10】

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用すること、をさらに備える請求項9に記載の方法。

【請求項11】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用すること、をさらに備える請求項9に記載の方法。

【請求項12】

Mが16である、請求項1に記載の方法。

【請求項13】

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用すること、をさらに備える請求項12に記載の方法。

【請求項14】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用すること、をさらに備える請求項12に記載の方法。

【請求項15】

Mが32である、請求項1に記載の方法。

【請求項16】

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用すること、をさらに備える請求項15に記載の方法。 40

【請求項17】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用すること、をさらに備える請求項15に記載の方法。

【請求項18】

前記QPPターボ・インタリーバに関連するサブ・グループを持つメンバシップを保持することをさらに備え、

前記QPPターボ・インタリーバのサブ・グループに対するメンバシップは、APP RAM内のサブ・グループのメンバシップに変わる、請求項1に記載の方法。

【請求項19】

競合の無いメモリ・アクセスを提供するターボ・デコーダを適用する無線通信装置であ 50

つて、

事後確率 (APP) ランダム・アクセス・メモリ (RAM) を特定し、

前記 APP RAM を、M個のRAM ファイルへ構成し、

すべての APP 値を、2 次置換多項式 (QPP) ターボ・インターバに基づいて、少なくとも 2 つのインタリープ・サブ・グループに分割し、ここで、前記分割は、 $n = 1, \dots, M$  のうちの  $n$  番目のインタリープ・サブ・グループを、 $n L + M k + j$  ( $j = 0, 1, 2, 3$ ) のフォーマットでフォーマットすることを備え、ここで、 $n$  は、前記  $M$  個のインタリープ・サブ・グループのおのの内のインデクスであり、前記  $k$  は、サブ・グループ・インデクスである。

個別のインタリープ・サブ・グループを、個別の APP RAM ファイルにマップし、

インタリープ・サブ・グループ内の第 1 の APP 値と、別のインタリープ・サブ・グループ内の第 2 の APP 値とに同時にアクセスする、

ように構成された少なくとも 1 つのプロセッサと、

前記少なくとも 1 つのプロセッサに接続されたメモリと、

を備える無線通信装置。

【請求項 20】

前記ターボ・デコーダが、MAP パラレル・デコーダを備え、前記 MAP パラレル・デコーダが、前記インタリープ・サブ・グループのうちの少なくとも 1 つへの読み取りまたは書き込みのうちの少なくとも 1 つを用いる、請求項 19 に記載の無線通信装置。

【請求項 21】

前記ターボ・デコーダが、MAP パラレル・デコーダを備え、前記 MAP パラレル・デコーダが、前記インタリープ・サブ・グループのうちの少なくとも 1 つへの読み取りまたは書き込みのうちの少なくとも 1 つを用いるように隔離された、請求項 19 に記載の無線通信装置。

【請求項 22】

M が 2 である、請求項 19 に記載の無線通信装置。

【請求項 23】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、ように構成された少なくとも 1 つのプロセッサをさらに備える請求項 22 に記載の無線通信装置。

【請求項 24】

M が 4 である、請求項 19 に記載の無線通信装置。

【請求項 25】

同時の読み取りおよび書き込みを提供するために、デュアル・ポート RAM 設計を利用する、ように構成された少なくとも 1 つのプロセッサをさらに備える請求項 24 に記載の無線通信装置。

【請求項 26】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、ように構成された少なくとも 1 つのプロセッサをさらに備える請求項 24 に記載の無線通信装置。

【請求項 27】

M が 8 である、請求項 19 に記載の無線通信装置。

【請求項 28】

同時の読み取りおよび書き込みを提供するために、デュアル・ポート RAM 設計を利用する、ように構成された少なくとも 1 つのプロセッサをさらに備える請求項 27 に記載の無線通信装置。

【請求項 29】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、ように構成された少なくとも 1 つのプロセッサをさらに備える請求項 27 に記載の無線通信装置。

10

20

30

40

50

## 【請求項 3 0】

Mが16である、請求項19に記載の無線通信装置。

## 【請求項 3 1】

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用する、よう構成された少なくとも1つのプロセッサをさらに備える請求項30に記載の無線通信装置。

## 【請求項 3 2】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、よう構成された少なくとも1つのプロセッサをさらに備える請求項30に記載の無線通信装置。

10

## 【請求項 3 3】

Mが32である、請求項19に記載の無線通信装置。

## 【請求項 3 4】

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用する、よう構成された少なくとも1つのプロセッサをさらに備える請求項33に記載の無線通信装置。

## 【請求項 3 5】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、よう構成された少なくとも1つのプロセッサをさらに備える請求項33に記載の無線通信装置。

20

## 【請求項 3 6】

前記QPPターボ・インタリーバに関連するサブ・グループを持つメンバシップを保持するように構成された少なくとも1つのプロセッサをさらに備え、

前記QPPターボ・インタリーバのサブ・グループに対するメンバシップは、APP RAM内のサブ・グループのメンバシップに変わる、請求項19に記載の無線通信装置。

## 【請求項 3 7】

競合の無いメモリ・アクセスを提供するターボ・デコーダを適用する無線通信装置であつて、

事後確率(APP)ランダム・アクセス・メモリ(RAM)を特定する手段と、

前記APP RAMを、M個のRAMファイルへ構成する手段と、

30

すべてのAPP値を、2次置換多項式(QPP)ターボ・インタリーバに基づいて、少なくとも2つのインタリーブ・サブ・グループに分割する手段と、ここで、前記分割は、 $n = 1, \dots, M$ のうちのn番目のインタリーブ・サブ・グループを、 $nL + Mk + j$ ( $j = 0, 1, 2, 3$ )のフォーマットでフォーマットすることを備え、ここで、前記Lは、前記インタリーブ・サブ・グループの長さであり、nは、前記M個のインタリーブ・サブ・グループのうちの内のインデックスであり、前記kは、サブ・グループ・インデックスである。

個別のインタリーブ・サブ・グループを、個別のAPP RAMファイルにマップする手段と、

インタリーブ・サブ・グループ内の第1のAPP値と、別のインタリーブ・サブ・グループ内の第2のAPP値とに同時にアクセスする手段と、

40

を備える無線通信装置。

## 【請求項 3 8】

前記ターボ・デコーダが、MAPパラレル・デコーダを備え、前記MAPパラレル・デコーダが、前記インタリーブ・サブ・グループのうちの少なくとも1つへの読み取りまたは書き込みのうちの少なくとも1つを用いる、請求項37に記載の無線通信装置。

## 【請求項 3 9】

前記ターボ・デコーダが、MAPパラレル・デコーダを備え、前記MAPパラレル・デコーダが、前記インタリーブ・サブ・グループのうちの少なくとも1つへの読み取りまたは書き込みのうちの少なくとも1つを用いるように隔離された、請求項37に記載の無線通信装置

50

。

## 【請求項 4 0】

Mが2である、請求項37に記載の無線通信装置。

## 【請求項 4 1】

サブ・グループのための書込と読取との間にクロック・サイクル・オフセットを適用する手段、をさらに備える請求項40に記載の無線通信装置。

## 【請求項 4 2】

Mが4である、請求項37に記載の無線通信装置。

## 【請求項 4 3】

同時の読取および書込を提供するために、デュアル・ポートRAM設計を利用する手段、をさらに備える請求項42に記載の無線通信装置。 10

## 【請求項 4 4】

サブ・グループのための書込と読取との間にクロック・サイクル・オフセットを適用する手段、をさらに備える請求項42に記載の無線通信装置。

## 【請求項 4 5】

Mが8である、請求項37に記載の無線通信装置。

## 【請求項 4 6】

同時の読取および書込を提供するために、デュアル・ポートRAM設計を利用する手段、をさらに備える請求項45に記載の無線通信装置。

## 【請求項 4 7】

サブ・グループのための書込と読取との間にクロック・サイクル・オフセットを適用する手段、をさらに備える請求項45に記載の無線通信装置。 20

## 【請求項 4 8】

Mが16である、請求項45に記載の無線通信装置。

## 【請求項 4 9】

同時の読取および書込を提供するために、デュアル・ポートRAM設計を利用する手段、をさらに備える請求項48に記載の無線通信装置。

## 【請求項 5 0】

サブ・グループのための書込と読取との間にクロック・サイクル・オフセットを適用する手段、をさらに備える請求項48に記載の無線通信装置。 30

## 【請求項 5 1】

Mが32である、請求項45に記載の無線通信装置。

## 【請求項 5 2】

同時の読取および書込を提供するために、デュアル・ポートRAM設計を利用する手段、をさらに備える請求項51に記載の無線通信装置。

## 【請求項 5 3】

サブ・グループのための書込と読取との間にクロック・サイクル・オフセットを適用する手段、をさらに備える請求項51に記載の無線通信装置。

## 【請求項 5 4】

前記QPPターボ・インターバに関連するサブ・グループを持つメンバシップを保持する手段をさらに備え、 40

前記QPPターボ・インターバのサブ・グループに対するメンバシップは、APP RAM内のサブ・グループのメンバシップに変わる、請求項37に記載の無線通信装置。

## 【請求項 5 5】

競合の無いメモリ・アクセスを提供するターボ・デコーダを適用する無線通信のためのコンピュータ読取可能な記録媒体であって、

少なくとも1つのコンピュータに対して、事後確率(APP)ランダム・アクセス・メモリ(RAM)を特定させるためのコードと、

少なくとも1つのコンピュータに対して、前記APP RAMを、M個のRAMファイ

ルへ構成させるためのコードと、

50

少なくとも 1 つのコンピュータに対して、すべての APP 値を、2 次置換多項式 ( Q P P ) ターボ・インタリーバに基づいて、少なくとも 2 つのインタリーブ・サブ・グループに分割させるためのコードと、ここで、前記分割は、 $n = 1, \dots, M$  のうちの  $n$  番目のインタリーブ・サブ・グループを、 $n L + M k + j$  ( $j = 0, 1, 2, 3$ ) のフォーマットでフォーマットすることを備え、ここで、前記  $L$  は、前記インタリーブ・サブ・グループの長さであり、 $n$  は、前記  $M$  個のインタリーブ・サブ・グループのおのの内のインデクスであり、前記  $k$  は、サブ・グループ・インデクスである。

少なくとも 1 つのコンピュータに対して、個別のインタリーブ・サブ・グループを、個別の APP\_RAM ファイルにマップさせるためのコードと、

少なくとも 1 つのコンピュータに対して、インタリーブ・サブ・グループ内の第 1 の APP 値と、別のインタリーブ・サブ・グループ内の第 2 の APP 値とに同時にアクセスさせるためのコードと、

を備えるコンピュータ読取可能な記録媒体。

【発明の詳細な説明】

【技術分野】

【0001】

以下の記載は、一般に無線通信に関し、さらに詳しくは、メモリ・ストレージの一部におけるメモリ衝突を低減するためのストレージ設計に関する。

【背景技術】

【0002】

無線通信システムは、さまざまなタイプの通信を提供するために広く開発された。例えば、音声および / またはデータが、そのような無線通信システムによって提供されうる。一般的な無線通信システムすなわちネットワークは、複数のユーザへ、1 または複数の共有リソース（例えば、帯域幅、送信電力）に対するアクセスを提供しうる。例えば、システムは、周波数分割多重化 ( FDM ) 、時分割多重化 ( TDM ) 、符号分割多重化 ( CDM ) 、直交周波数分割多重化 ( OFDM ) のようなさまざまな多元接続技術を使用することができる。

【0003】

通常、無線多元接続通信システムは、複数のモバイル・デバイスのための通信を同時にサポートすることができる。おのののモバイル・デバイスは、順方向リンクおよび逆方向リンクによる送信を介して、1 または複数の基地局と通信することができる。順方向リンク（すなわち、ダウンリンク）は、基地局からモバイル・デバイスへの通信リンクを称し、逆方向リンク（すなわち、アップリンク）は、モバイル・デバイスから基地局への通信リンクを称する。

【0004】

無線通信システムはしばしば、有効通信範囲領域を提供する 1 または複数の基地局を使用する。一般的な基地局は、ブロードキャスト・サービス、マルチキャスト・サービス、および / またはユニキャスト・サービスのために複数のデータ・ストリームを送信することができる。これらデータ・ストリームは、モバイル・デバイスに対して興味のある独立した受信からなるデータのストリームでありうる。そのような基地局の有効範囲領域内のモバイル・デバイスは、合成ストリームによって搬送された 1 つ、複数、あるいはすべてのデータ・ストリームを受信するために使用されうる。同様に、モバイル・デバイスは、基地局あるいは別のモバイルのデバイスへデータを送信しうる。

【0005】

無線通信システム内のエリア・トラッキングによって、ユーザ機器（例えば、モバイル・デバイス、モバイル通信装置、セルラ・デバイス、スマートフォン等）のトラッキング・エリア位置が定義されるようになる。一般に、ネットワークは、ユーザ機器 ( UE ) がそのようなトラッキング・エリア位置を用いて応答する UE に対して要求またはページしうる。これによって、UE のトラッキング・エリア位置が、ネットワークへ通信され、さらに更新されるようになる。

10

20

30

40

50

## 【0006】

ターボ・コードは、しばしば、無線通信システムにおける信頼性の高い通信のために使用される。ここでは、送信機は、情報ビットを符号化するためにターボ・エンコーダを用い、受信機は、送信されたビットを、ターボ・デコーダ（T D E C）を用いて復号する。ターボ・デコーダは、ターボ・デコーダの異なる部位間で情報を交換するために、一般には、事後確率（A P P : A Posteriori Probability）ランダム・アクセス・メモリ（R A M）である、メモリの一部を含みうる。例えば、ターボ・デコーダは、A P P R A Mを共有しうる2つの最大事後（M A P : Maximum A Posteriori）デコーダを含みうる。広帯域幅および複数入力複数出力（M I M O）をサポートするための、ターボ・デコーダの高いスループット要求により、メモリ衝突および／または競合が発生しうる。例えば、M A Pデコーダ間でA P P R A Mを共有することは、A P P R A Mとの間での値のローディングまたはアンローディングに基づいて、メモリ競合および／または衝突を引き起こしうる。これは、好ましくないことに、ターボ・デコーダの処理スループットを下げる。したがって、複数のM A Pデコーダが、メモリ・アクセス競合を引き起こすことなく、A P P R A Mを共有できるようにA P P R A Mを設計する必要がある。

10

## 【発明の概要】

## 【0007】

以下は、1または複数の実施形態の基本的な理解を与えるために、そのような実施形態の簡略化された概要を示す。この概要は、考えられるすべての実施形態の広範囲な概観ではなく、すべての実施形態の重要要素や決定的要素を特定することも、何れかまたはすべての実施形態のスコープを線引きすることも意図されていない。その唯一の目的は、後に示されるより詳細な記載に対する前置きとして、簡略化された形式で1または複数の実施形態のいくつかの概念を表すことである。

20

## 【0008】

関連する態様は、競合の無いメモリ・アクセスを提供するターボ・デコーダを適用することを容易にする方法である。この方法は、事後確率（A P P）ランダム・アクセス・メモリ（R A M）を特定することを含みうる。さらに、この方法は、A P P R A Mを、少なくとも2つのファイルへ構成することを含みうる。さらに、この方法は、すべてのA P P値を、2次置換多項式（Q P P）ターボ・インタリーバに基づいて、少なくとも2つのインタリーブ・サブ・グループに分割することを備えうる。この方法はさらに、個別のインタリーブ・サブ・グループを、個別のR A Mファイルにマップすることを含みうる。

30

## 【0009】

別の態様は、無線通信装置に関する。この無線通信装置は、事後確率（A P P : A Posteriori Probability）ランダム・アクセス・メモリ（R A M）を特定し、A P P R A Mを、少なくとも2つのファイルへ構成し、すべてのA P P値を、2次置換多項式（Q P P）ターボ・インタリーバに基づいて、少なくとも2つのインタリーブ・サブ・グループに分割し、個別のインタリーブ・サブ・グループを、個別のR A Mファイルにマップする、ように構成された少なくとも1つのプロセッサを含みうる。さらに、この無線通信装置は、少なくとも1つのプロセッサに接続されたメモリを含みうる。

## 【0010】

40

さらに別の態様は、競合の無いメモリ・アクセスを提供するターボ・デコーダを適用する無線通信装置に関する。この無線通信装置は、事後確率（A P P）ランダム・アクセス・メモリ（R A M）を特定する手段を含みうる。さらに、この無線通信装置は、A P P R A Mを、少なくとも2つのファイルへ構成する手段を備えうる。さらに、この無線通信装置は、すべてのA P P値を、2次置換多項式（Q P P）ターボ・インタリーバに基づいて、少なくとも2つのインタリーブ・サブ・グループに分割する手段を備えうる。さらに、この無線通信装置は、個別のインタリーブ・サブ・グループを、個別のR A Mファイルにマップする手段を備えうる。

## 【0011】

また別の態様は、事後確率（A P P）ランダム・アクセス・メモリ（R A M）を特定す

50

ることと、APP RAMを、少なくとも2つのファイルへ構成することと、すべてのAPP値を、2次置換多項式(QPP)ターボ・インターバに基づいて、少なくとも2つのインターブ・サブ・グループに分割することと、個別のインターブ・サブ・グループを、個別のRAMファイルにマップすることと、を少なくとも1つのコンピュータにさせるコードを格納したコンピュータ読取可能な媒体を備えるコンピュータ・プログラム製品に関する。

#### 【0012】

前述した目的および関連する目的を達成するために、1または複数の実施形態は、後に十分に記載され、特許請求の範囲において特に指摘されている特徴を備える。次の記載および添付図面は、1または複数の実施形態のある実例となる態様を詳細に記載する。しかしながら、これらの態様は、さまざまな実施形態の原理が適用されるさまざまな方法のうちの僅かしか示しておらず、記載された実施形態は、そのようなすべての局面およびそれらの均等物を示すことが意図されている。

#### 【図面の簡単な説明】

#### 【0013】

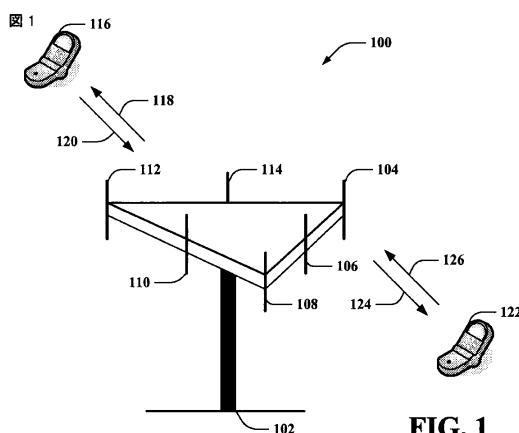

【図1】図1は、本明細書に記載されたさまざまな態様にしたがう無線通信システムの例示である。

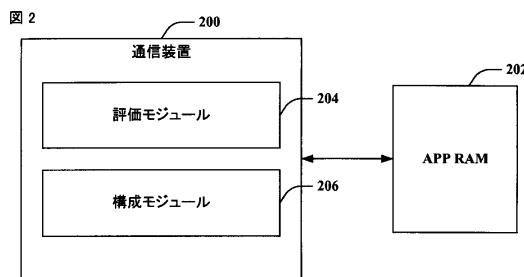

【図2】図2は、無線通信環境内で適用するための通信装置の例の例示である。

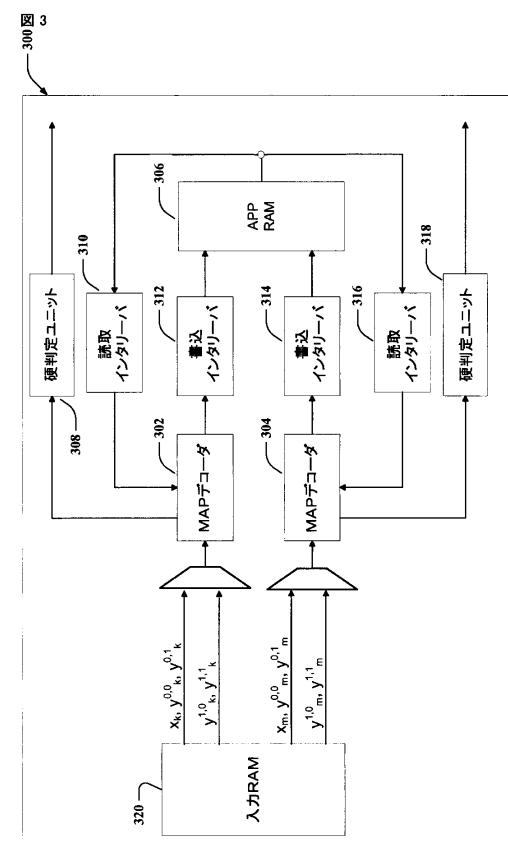

【図3】図3は、主題とするイノベーションにしたがうターボ・デコーダの例の例示である。

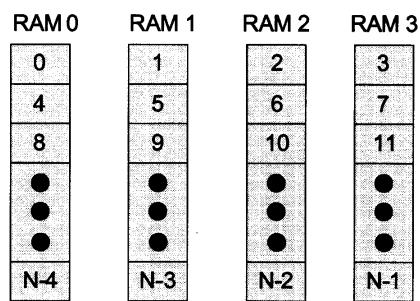

【図4】図4は、主題とするイノベーションにしたがって、4つのサブ・グループを含むA 事後確率(APP)ランダム・アクセス・メモリ(RAM)設計の例の例示である。

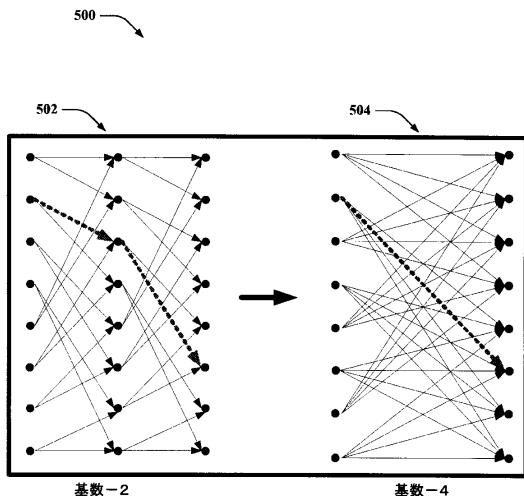

【図5】図5は、基数(radix)-2構成および基数-4構成の例示である。

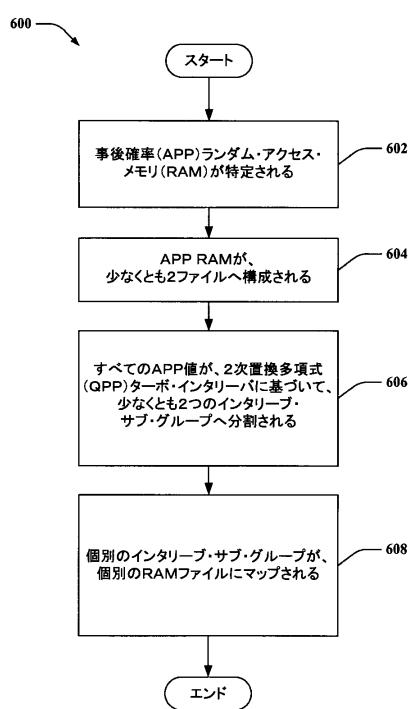

【図6】図6は、競合の無いメモリ・アクセスを提供するターボ・デコーダを適用することを容易にする方法の例の例示である。

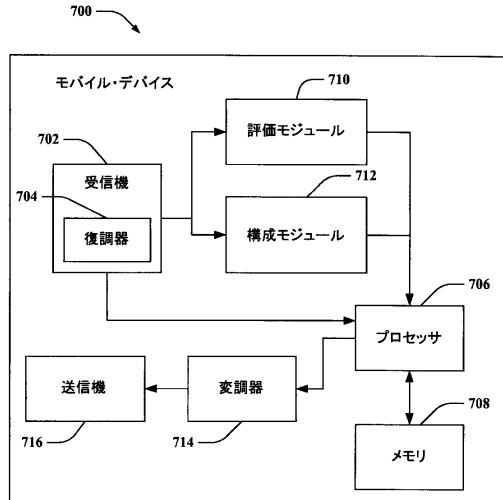

【図7】図7は、無線通信システムにおいて、メモリ衝突を回避するために、ターボ・デコーダのためのメモリの一部を構成することを容易にするモバイル・デバイスの例の例示である。

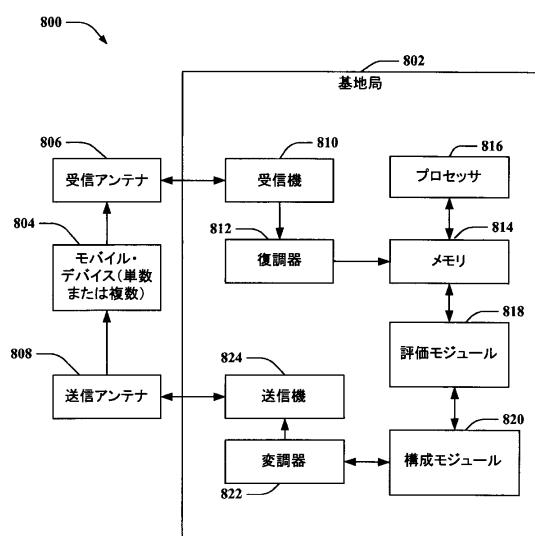

【図8】図8は、無線通信環境において、メモリ衝突を回避するために、事後確率(APP)ランダム・アクセス・メモリ(RAM)を分割することを容易にするシステムの例の例示である。

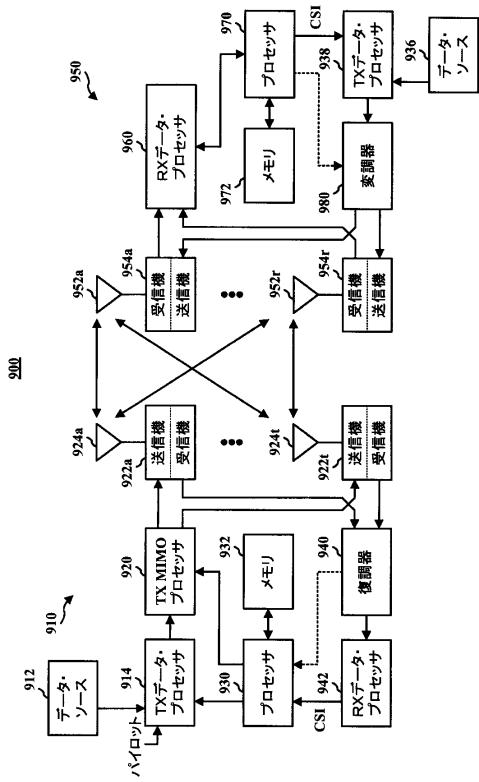

【図9】図9は、本明細書に記載されたさまざまなシステムおよび方法と共に適用される無線ネットワーク環境の実例である。

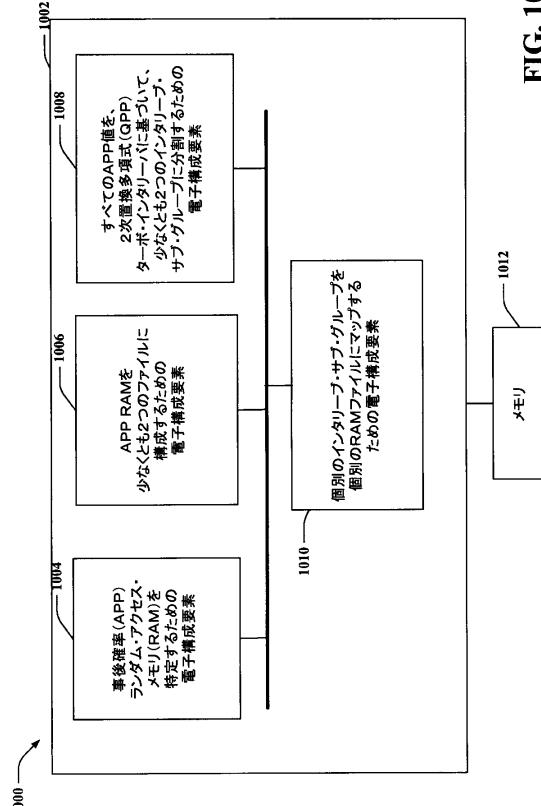

【図10】図10は、競合の無いメモリ・アクセスを提供するターボ・デコーダを適用することを容易にするシステムの例の例示である。

#### 【発明を実施するための形態】

#### 【0014】

さまざまな実施形態が、全体を通じて同一要素を示すために同一の参照番号が使用される図面を参照して説明される。

#### 【0015】

次の記載では、説明の目的のために、多数の特定の詳細が、1または複数の実施形態についての完全な理解を提供するために記載される。しかしながら、そのような実施形態は、これら具体的な詳細なしで実現されうることが明白でありうる。他の事例では、1または複数の実施形態の記載を容易にするために、周知の構成およびデバイスがブロック図形式で示される。

#### 【0016】

本願で使用されるように、用語「モジュール」、「キャリア」、「システム」、「インターバ」、「ユニット」、「デコーダ」等は、ハードウェア、ファームウェア、ハードウェアとソフトウェアとの組み合わせ、ソフトウェア、または実行中のソフトウェアの何れかであるコンピュータ関連エンティティを称することが意図される。例えば、構成要素

10

20

30

40

50

は、限定される訳ではないが、プロセッサ上で実行中のプロセス、プロセッサ、オブジェクト、実行形式、実行スレッド、プログラム、および／またはコンピュータでありうる。例示によれば、コンピューティング・デバイス上で実行中のアプリケーションと、コンピューティング・デバイスとの両方が構成要素となりうる。1または複数の構成要素は、プロセスおよび／または実行スレッド内に存在し、構成要素は、1つのコンピュータに局在化されるか、および／または、複数のコンピュータに分散されうる。さらに、これらの構成要素は、さまざまなデータ構造を格納したさまざまなコンピュータ読取可能な媒体から実行可能である。これら構成要素は、（例えば、信号によってローカル・システムや分散システム内の他の構成要素とインタラクトする1つの構成要素からのデータ、および／または、他のシステムを備えた例えばインターネットのようなネットワークを経由して他の構成要素とインタラクトする1つの構成要素からのデータのような）1または複数のデータのパケットを有する信号にしたがって、ローカル処理および／またはリモート処理によって通信することができる。

#### 【0017】

本明細書に記述された技術は、符号分割多元接続（CDMA）システム、時分割多元接続（TDMA）システム、周波数分割多元接続（FDMA）システム、直交周波数分割多元接続（OFDMA）システム、シングル・キャリア周波数分割多元接続（SC-FDMA）システム、およびその他のシステムのようなさまざまな無線通信システムに使用することができる。「システム」、「ネットワーク」という用語はしばしば置換可能に使用される。CDMAシステムは、例えばユニバーサル地上ラジオ・アクセス（UTRA）、CDMA2000等のようなラジオ技術を実現することができる。UTRAは、広帯域CDMA（W-CDMA）およびCDMAのその他の変形を含んでいる。CDMA2000は、IS-2000規格、IS-95規格、およびIS-856規格をカバーする。TDMAシステムは、例えばグローバル移動体通信システム（GSM（登録商標））のような無線技術を実現することができる。OFDMAシステムは、例えばイボルブドUTRA（E-UTRA）、ウルトラ・モバイル・ブロードバンド（UMB）、IEEE 802.11（Wi-Fi）、IEEE 802.16（WiMAX）、IEEE 802.20、フラッシュ-OFDM（登録商標）等のような無線技術を実現することができる。UTRAおよびE-UTRAは、ユニバーサル・モバイル・テレコミュニケーション・システム（UMTS）の一部である。3GPPロング・ターム・イボリューション（LTE）は、E-UTRAを使用するUMTSの最新リリースであり、ダウンリンクではOFDMAを用い、アップリンクではSC-FDMAを用いる。

#### 【0018】

シングル・キャリア周波数分割多元接続（SC-FDMA）は、シングル・キャリア変調および周波数領域等値化を用いる。SC-FDMAは、OFDMAシステムと類似の性能を有し、本質的に全体的に同等の複雑さを有する。SC-FDMA信号は、その固有のシングル・キャリア構造により、より低いピーク対平均電力比（PAPR）を有する。SC-FDMAは、例えば、より低いPAPRが送信電力効率の観点からアクセス端末に非常に役立つアップリンク通信で使用されうる。したがって、SC-FDMAは、3GPPロング・ターム・イボリューション（LTE）すなわちイボルブドUTRAにおけるアップリンク多元接続性スキームとして実施されうる。

#### 【0019】

さらに、本明細書では、さまざまな実施形態が、モバイル・デバイスに関連して記載される。モバイル・デバイスはまた、システム、加入者ユニット、加入者局、モバイル局、モバイル、遠隔局、遠隔端末、アクセス端末、ユーザ端末、端末、無線通信デバイス、ユーザ・エージェント、ユーザ・デバイス、あるいはユーザ機器（UE）とも称されうる。モバイル・デバイスは、セルラ電話、コードレス電話、セッション開始プロトコル（SIP）電話、無線ローカル・ループ（WLL）局、携帯情報端末（PDA）、無線接続機能を有する携帯型デバイス、コンピュータ・デバイス、あるいは無線モデムに接続されたその他の処理デバイスでありうる。さらに、本明細書では、さまざまな実施形態が、基地局

10

20

30

40

50

に関連して記載される。基地局はモバイル・デバイスと通信するために利用することができ、アクセス・ポイント、ノードBあるいはその他の用語で称される。

【0020】

さらに、本明細書に記載のさまざまな態様または特徴は、標準的なプログラミング技術および／またはエンジニアリング技術を用いた方法、装置、または製造物品として実現されうる。本明細書で使用される用語「製造物品」は、任意のコンピュータ読取可能なデバイス、キャリア、または媒体からアクセスすることが可能なコンピュータ・プログラムを含むことが意図される。例えば、コンピュータ読取可能な媒体は、限定される訳ではないが、磁気記憶装置（例えば、ハード・ディスク、フロッピー（登録商標）ディスク、磁気ストリップ等）、光ディスク（例えば、コンパクト・ディスク（CD）、DVD等）、スマート・カード、およびフラッシュ・メモリ・デバイス（例えば、E PROM、カード、スティック、キー・ドライブ等）を含みうる。さらに、本明細書に記載されたさまざまな記憶媒体は、情報を格納するための1または複数のデバイス、および／または、その他の機械読取可能な媒体を表すことができる。用語「機械読取可能な媒体」は、限定されることなく、無線チャネル、および、命令群および／またはデータを格納、包含、および／または搬送することができるその他任意の媒体を含みうる。

【0021】

図1に示すように、本明細書に示されたさまざまな実施形態にしたがう無線通信システム100が例示されている。システム100は、複数のアンテナ・グループを含むことができる基地局102を含む。例えば、1つのアンテナ・グループは、アンテナ104およびアンテナ106を含むことができ、別のグループはアンテナ108およびアンテナ110を備えることができ、さらに別のグループはアンテナ112およびアンテナ114を含むことができる。おののののアンテナ・グループについて2つのアンテナしか例示されていないが、2本より多いアンテナ、または2本より少ないアンテナも、各グループのために利用されうる。基地局102はさらに、送信機チェーンおよび受信機チェーンを含みうる。これらのおのののは、当業者によって理解されるように、信号の送信および受信に関連する複数の構成要素（例えば、プロセッサ、変調器、マルチプレクサ、復調器、デマルチプレクサ、アンテナなど）を備えうる。

【0022】

基地局102は、例えばモバイル・デバイス116およびモバイル・デバイス122のような1または複数のモバイル・デバイスと通信しうる。しかしながら、基地局102は、モバイル・デバイス116およびモバイル・デバイス122に類似した実質的に任意の数のモバイル・デバイスと通信しうることが理解されるべきである。モバイル・デバイス116、122は例えば、セルラ電話、スマートフォン、ラップトップ、ハンドヘルド通信デバイス、ハンドヘルド・コンピュータ・デバイス、衛星ラジオ、全地球測位システム、PDA、および／または、無線通信システム100を介して通信するのに適切なその他任意のデバイスでありうる。図示するように、モバイル・デバイス116は、アンテナ112およびアンテナ114と通信している。ここで、アンテナ112およびアンテナ114は、順方向リンク118によってアクセス端末116へ情報を送信し、逆方向リンク120によってアクセス端末116から情報を受信する。さらに、モバイル・デバイス122はアンテナ104およびアンテナ106と通信している。ここで、アンテナ104およびアンテナ106は、順方向リンク124でアクセス端末122へ情報を送信し、逆方向リンク126でアクセス端末122から情報を受信する。周波数分割デュプレクス（FDD）システムでは、例えば、順方向リンク118は、逆方向リンク120によって使用されるものとは異なる周波数帯域を使用し、順方向リンク124は、逆方向リンク126によって使用されるものとは異なる周波数帯域を使用することができる。さらに、時分割デュプレクス（TDD）システムでは、順方向リンク118と逆方向リンク120とが、共通の周波数帯域を使用し、順方向リンク124と逆方向リンク126とが、共通の周波数帯域を使用することができる。

【0023】

10

20

30

40

50

通信するように指定された領域および／またはアンテナのおののグループは、基地局102のセクタと称されうる。例えば、基地局102によってカバーされる領域のセクタ内のアクセス端末に通信するように、複数のアンテナが設計されうる。順方向リンク118および順方向リンク124による通信では、基地局102の送信アンテナは、アクセス端末116およびアクセス端末122のための順方向リンク118および順方向リンク124の信号対雑音比を改善するためにビームフォーミングを適用することができる。また、基地局102が、関連付けられた有効通信範囲にランダムに散在したモバイル・デバイス116、122に送信するためにビームフォーミングを利用している間、近隣セル内のモバイル・デバイスは、すべてのモバイル・デバイスに対して単一のアンテナによって送信している基地局に比べて、少ない干渉しか被らない。

10

#### 【0024】

基地局102（および／または基地局102のおののセクタ）は、1または複数の多元接続技術（例えば、CDMA、TDMA、FDMA、OFDMA）を使用しうる。例えば、基地局102は、対応する帯域幅においてモバイル・デバイス（例えば、モバイル・デバイス116、122）と通信するために特定の技術を利用しうる。さらに、基地局102によって、複数の技術が適用される場合、おののの技術は、それぞれの帯域幅に関連付けられうる。本明細書に記載された技術は下記を含みうる。グローバル移動体通信システム（GSM（登録商標））、汎用パケット・ラジオ・サービス（GPRS）、エンハンスト・データ・レート・フォーGSMイボリューション（EDGE）、ユニバーサル・モバイル・テレコミュニケーション・システム（UMTS）、広帯域符号分割多元接続（W-CDMA）、cdmaOne（IS-95）、CDMA2000、イボリューション・データ・オプティマイズド（EV-DO）、ウルトラ・モバイル・ブロードバンド（UMB）、ワールドワイド・インタオペラビリティ・フォー・マイクロウェーブ・アクセス（WiMAX）、MediaFL、デジタル・マルチメディア・ブロードキャスティング（DMB）、デジタル・ビデオ・ブロードキャスティング・ハンドヘルド（DVB-H）等。前述した技術のリストは、例として与えられたものであって、権利主張される主題はこれらに限定されず、実質的に任意の無線通信技術が、特許請求の範囲内にあることが意図されることが認識されるべきである。

20

#### 【0025】

基地局102は、第1の技術を用いて第1の帯域幅を利用しうる。さらに、基地局102は、第1の技術に対応するパイロットを、第2の帯域幅で送信しうる。例示によれば、第2の帯域幅は、基地局102、および／または、通信のために任意の第2の技術を利用する別の基地局（図示せず）によって導入されうる。さらに、パイロットは、第1の技術の存在を（例えば、第2の技術によって通信しているモバイル・デバイスへ）示しうる。例えば、パイロットは、第1の技術の存在に関する情報を伝送するピットを使用しうる。さらに、例えば、第1の技術を利用するセクタのセクタID、第1の周波数帯域幅を示すキャリア・インデックス等のような情報がパイロットに含まれうる。

30

#### 【0026】

別の例によれば、パイロットは、ビーコン（および／またはビーコンのシーケンス）でありうる。ビーコンは、OFDMシンボルでありうる。ここでは、電力の大部分が、1つのサブキャリアまたは少数のサブキャリア（例えば、少ない数のサブキャリア）で送信される。したがって、ビーコンは、モバイル・デバイスによって観察されうる強いピークをもたらすが、同時に、帯域幅の狭い部分において、データと干渉する（例えば、帯域幅の残りの部分は、ビーコンによって影響されない）。この例によれば、第1のセクタは、第1の帯域幅で、CDMAによって通信し、第2のセクタは、第2の帯域幅で、OFDMによって通信しうる。したがって、第1のセクタは、第2の帯域幅においてOFDMビーコン（またはOFDMビーコンのシーケンス）を（例えば、第2の帯域幅においてOFDMを利用して動作しているモバイル・デバイスへ）送信することによって、第1の帯域幅におけるCDMAの利用可能性を示しうる。

40

#### 【0027】

50

主題とするイノベーションは、クロック・サイクル内で、読み書き動作および／または書き込み動作中に、メモリ衝突を低減および／または除去するために、ターボ・デコーダ内で利用されるメモリの一部のために分割技術を適用しうる。事後確率( APP )ランダム・アクセス・メモリ( RAM )は、APP RAM のファイルへの分割および／または構成を特定するために評価されうる。この分割および／または構成の目的は、ターボ・デコーダが、何れのクロック・サイクル内でも、ファイルの何れかのうちの複数のアドレスには決してアクセス(読み書きまたは書き込み)しないようにすることである。ターボ・デコーダが、ファイルの何れかのうちの複数のアドレスにアクセスする必要がある場合、メモリ・アクセス競合が生じる。このような競合によって、ターボ・デコーダは、競合が解決されている間は、停止および待機させられる。これは、必然的に、ターボ・デコーダの処理スループットを下げるだろう。

10

### 【 0028 】

図2に移って、無線通信環境内で適用される通信装置200が例示される。通信装置200は、基地局またはその一部であるか、モバイル・デバイスまたはその一部であるか、無線通信環境で送信されたデータを受信する実質的に任意の通信装置でありうる。通信装置200は、基地局(例えば、アクセス・ポイント、ノードB、eノードB等)、および／または、ユーザ機器(例えば、移動局、モバイル・デバイス、および／または、(図示しない)任意の数の別のデバイス)でありうることが認識されるべきである。通信装置200は、順方向リンク・チャネルすなわちダウンリンク・チャネルで、情報を送信しうる。さらに、通信装置200は、逆方向リンク・チャネルすなわちアップリンク・チャネルで、情報を受信しうる。さらに、通信装置200は、逆方向リンク・チャネルすなわちアップリンク・チャネルで、情報を送信しうる。さらに、通信装置200は、順方向リンク・チャネルすなわちダウンリンク・チャネルで、情報を受信しうる。さらに、通信装置200は、MIMOシステムにおいて利用されうる。さらに、通信装置200は、OFDMA無線ネットワーク(例えば、3GPP、3GPP2、3GPP LTE等)で動作しうる。通信システムでは、通信装置200は、メモリ衝突を低減するために、事後確率( APP )ランダム・アクセス・メモリ( RAM )の評価、および、この評価に基づく、メモリの分割の生成のために、以下に説明するような構成要素を適用する。

20

### 【 0029 】

通信装置200は、APP RAM202を特定し検査しうる評価モジュール204を含みうる。APP RAM202は、通信装置200とは別に図示されているが、APP RAM202は、通信装置200に組み込まれうるか、スタンド・アロンのRAMであるか、あるいは、これらの任意の適切な組み合わせでありうることが認識されるべきである。評価モジュール204は、限定される訳ではないが、例えば、APP RAM202を共有するMAPデコーダの数、サイズ等のような情報を収集するためにAPP RAM202を評価しうる。通信装置200はさらに、APP RAM202を分割および／またはセグメント化しうる構成モジュール206を含みうる。例えば、構成モジュール206は、APP RAM202の評価に基づいて、APP RAM202をセグメント化および／または分割しうる。構成モジュール206は、APP RAM202のサイズ、および／または、MAPデコーダの数および実装に基づいて、複数のファイルを生成しうる。構成モジュール206は、すべてのAPP値を、2次置換多項式( QPP )ターボ・インタリーバに基づいて、少なくとも2つのインタリーブ・サブ・グループへ分割しうる。構成モジュール206は、個別のインタリーブ・サブ・グループを、個別のRAMファイルにマップしうる。APP RAM分割およびAPP RAM構成の評価は固定されうる。

30

### 【 0030 】

例えば、構成モジュール206は、APP RAM202を、4つのRAMファイルへ構成しうる。P[0]、P[1]、…P[4L-1]によって示される全部で4L個のAPP値があるものと仮定する。この例では、第1のファイルが、P[4i]のAPP値を含み、第2のファイルが、P[4i+1]に関するAPP値を含み、第3のファイルが、

40

50

P [ 4 i + 2 ] に関する APP 値を含み、最後のファイルが、P [ 4 i + 3 ] に関する APP 値を含みうる。ここで、i は、各ファイル内のエントリのインデクスである。インデクス i は 0 から L - 1 までの範囲を取る。ここで、L は、4 つのファイルのおのののサイズである。別の例では、構成モジュール 206 は、APP RAM 202 を、8 つの RAM ファイルに構成しうる。P [ 0 ]、P [ 1 ]、…P [ 8 L - 1 ] によって示される全部で 8 L 個の APP 値があるものと仮定する。この例では、第 1 のファイルが、P [ 8 i ] の APP 値を含み、第 2 のファイルが、P [ 8 i + 1 ] に関する APP 値を含み、第 3 のファイルが、P [ 8 i + 2 ] に関する APP 値を含み、…、最後のファイルが、P [ 8 i + 7 ] に関する APP 値を含みうる。ここで、i は、各ファイル内のエントリのインデクスである。インデクス i は 0 から L - 1 までの範囲を取る。ここで、L は、8 つのファイルのおのののサイズである。さらに、図示していないが、一例において、通信装置 200 は、事後確率 (APP) ランダム・アクセス・メモリ (RAM) を特定することと、APP RAM を、少なくとも 2 つのファイルへ構成すること等に関する命令群を保持するメモリを含みうることが認識されるべきである。さらに、通信装置 200 は、(例えば、メモリ内に保持された命令群、別のソースから取得された命令群のような) 命令群を実行することに関連して利用されるプロセッサを含みうる。

10

#### 【0031】

図 3 を参照して、主題とするイノベーションにしたがって、2 つの MAP デコーダを備えたターボ・デコーダ 300 の例が例示されている。ターボ・デコーダ 300 は、MAP デコーダ 302、MAP デコーダ 304、APP RAM 306、硬判定ユニット 308、読取インターバル 310、書込インターバル 312、書込インターバル 314、読取インターバル 316、および硬判定ユニット 318 を含みうる。MAP デコーダ 302 と MAP デコーダ 304 との両方が、APP 値の読取および/または書込のために、APP RAM 306 にアクセスしうることが認識されるべきである。主題とするイノベーションは、メモリ衝突および/またはメモリ競合を回避するために、APP RAM 306 のファイルへのセグメント化または分割を提供しうる。

20

#### 【0032】

内部 TDEC 実装は、さまざまな特徴を有しうる。2 つの MAP デコーダを備えるターボ・デコーダ 300 の例では、1 つの MAP デコーダが、トレリスの前半部 (0 から N / 2 - 1) をカバーし、他の MAP デコーダが、トレリスの後半部 (N / 2 から N - 1) をカバーする。ここで、N は、(ターボ) 符号ブロックの長さである。これは、2 つの並列の順序を与える。2 つの MAP デコーダは、逆の方式で、トレリス方向を定義する。第 1 の MAP デコーダのための順方向トレリスは、0 から N / 2 - 1 であり、逆方向トレリスは N / 2 - 1 から N である。なぜなら、ゼロにおける初期状態が既知 (全ゼロ状態) であるからである。第 2 の MAP デコーダの場合、トレリス方向は逆である。第 2 の MAP デコーダの順方向トレリスは、N - 1 から N / 2 であり、逆方向トレリスは、N / 2 から N - 1 である。なぜなら、N における終了状態が既知 (全ゼロ状態) であるからである。

30

#### 【0033】

すべての状態判定基準を格納するために膨大な量のメモリを必要としうる合計 N / 2 個のトレリスの順方向状態判定基準および逆方向状態判定基準を計算するのではなく、各 MAP デコーダの長さ N / 2 のトレリスが、おののが長さ L を持つ M 個のオーバラップしないウィンドウに分割され、順方向状態判定基準計算および逆方向状態判定基準計算がまず第 1 のウィンドウについて実行され、次に第 2 のウィンドウについてといった具合に実行されうる。さらに、MAP デコーダ 302、304 は、基数 - 4 トレリスを用いて実施されうる。すなわち、2 つの隣接する基数 - 2 トレリスが、1 つの単一基数 - 4 トレリス (図 5 参照) として集合される。

40

#### 【0034】

いくつかのオーバヘッドを無視すると、上記の例による実施は、クロック・サイクル毎に 4 つの符号トレリス移行を処理する。ここで、2 つの移行は、第 1 の基数 - 4 MAP デコーダでなされ、2 つの移行は、他の MAP デコーダでなされる。この処理機能を十分に

50

活用するために、以下の 2 つの基準が満足される必要がある。

【0035】

基準 1：入力サンプルの 4 つのセットが、メモリ・アクセス競合無しで、各クロック・サイクル毎に読み取られうる。ここで、入力サンプルの各セットは、1 またはゼロの体系的なビットのサンプル（第 1 の成分符号（C C）のための 1 と、第 2 の C C のためのゼロ）、（1 / 3 C C 符号レートによる）パリティ・ビットのために 2 つのサンプル、および、1 つの APP 値を含む。MAP 変号が、第 1 の成分符号に対応しているか、第 2 の成分符号に対応しているかに依存して、これらの 4 つのアドレスのセットは、 $m \cdot L + 2k$ 、 $m \cdot L + 2k + 1$ 、 $n \cdot L + L - 1 - 2k$ 、 $n \cdot L + L - 2 - 2k$  であるか、あるいは、 $(m \cdot L + 2k)$ 、 $(m \cdot L + 2k + 1)$ 、 $(n \cdot L + L - 1 - 2k)$ 、 $(n \cdot L + L - 2 - 2k)$  である。<sup>10</sup> ここで、 $m$ 、 $n$  は、あるスライディング・ウィンドウ・インデクスであり、 $k \in \{0, 1, \dots, L/2 - 1\}$  は、スライディング・ウィンドウ内のクロック・サイクルに関連する。最初の 2 つのアドレスは、基数 - 4 実施によって、（ターボ・インターバル無し、あるいは、ターボ・インターバル有りの何れかで）互いに隣接している。最後の 2 つのアドレスも同様である。最初の 2 つのアドレスは、第 1 の MAP デコーダに対応している。ここでは、入力サンプル・ローディングが、ウィンドウの先頭から、ウィンドウの末尾へとなされる。最後の 2 つのアドレスは、第 2 の MAP デコーダに対応している。ここでは、入力サンプル・ローディングが、逆の方式で、例えば、ウィンドウの末尾から、ウィンドウの先頭へとなされる。

【0036】

20

基準 2：4 つの APP 値が、メモリ・アクセス競合無しで、各クロック・サイクルにおいて書き込まれうる。これら APP 値のアドレスは、MAP 変号が第 1 の成分符号に対応するか、第 2 の成分符号に対応するかに依存して、 $m \cdot L + 2k$ 、 $m \cdot L + 2k + 1$ 、 $n \cdot L + L - 1 - 2k$ 、 $n \cdot L + L - 2 - 2k$  のフォーマットであるか、あるいは、 $(m \cdot L + 2k)$ 、 $(m \cdot L + 2k + 1)$ 、 $(n \cdot L + L - 1 - 2k)$ 、 $(n \cdot L + L - 2 - 2k)$  のフォーマットでありうる。 $m$ 、 $n$ 、および  $k$  は、以前に定義されている。

【0037】

上記基準を満足する APP レイアウトをどのようにして設計するかは、ターボ・インターバル構成に関連している。一例において、LTE のためのターボ・インターバルは、2 次置換多項式（QPP）を用いて定義される。QPP インタリーバは、以下のように定義される。

30

$$(i) = f_1 \cdot i + f_2 \cdot i^2 \pmod{N},$$

ここで、 $f_1$  および  $f_2$  は、2 次多項式を定義する係数であり、 $N$  は、インターバルの長さである。多項式は、 $\{0, 1, \dots, N-1\} \rightarrow \{0, 1, \dots, N-1\}$  の 1 対 1 マッピングを定義しているのであれば、置換多項式と呼ばれる。

【0038】

LTE のために定義された QPP インタリーバは、さまざまな符号ブロック・サイズのために定義されうる。LTE のために定義された合計 188 のインターバル・サイズが存在しうる。すべてのインターバル・サイズは、少なくともビットが揃えられうる。<sup>40</sup> N = 512 である場合、インターバル・サイズはすべて 8 の倍数である。512 N 1

024 である場合、インターバル・サイズはすべて 16 の倍数である。1024 K 2

048 である場合、インターバル・サイズはすべて 32 の倍数である。2048 K 6

144 である場合、インターバル・サイズはすべて 64 の倍数である。

40

【0039】

N は、

【数 1】

$$N = \prod_{i=1}^m p_i^{\eta_i}$$

50

## 【0040】

として分解されうると仮定されたい。ここで、 $p_i$  は、別個の素数であり、 $n_i$  は、対応する指數関数である。QPP がモジュロ N を伴う場合、(x) もまた、モジュロ

## 【数2】

$p_i^{n_i}$

## 【0041】

を伴う置換多項式であることが明らかになりうる。

## 【0042】

(x) はまた、任意の  $0 < m < n_i$  についての置換多項式モジュロ

## 【数3】

$p_i^m$

## 【0043】

であることが明らかになりうる。上記 2 つの要因を組み合わせると、N を分割する任意の M について、QPP インタリーバは、以下のようなサブ・グループ・インターブ特性を有することが示されうる。

## 【数4】

任意の  $0 \leq m$  の場合、 $n < N/M$ 、及び  $0 \leq k, l \leq M-1$

$\pi(m \cdot M + k) \bmod M = \pi(n \cdot M + k) \bmod M$

$\pi(m \cdot M + k) \bmod M \neq \pi(n \cdot M + l) \bmod M \quad k \neq l$  の場合

## 【0044】

上記から、0 から  $N-1$  への N 個のアドレスが、M 個のサブ・グループに分割されうる。ここで、k 番目のサブ・グループは、 $\{m \cdot M + k : 0 \leq m \leq N/M-1\}$  のアドレスを含む。その後、サブ・グループ内のすべてのアドレスが、インターブ後であっても、1 つのサブ・グループとして残る。さらに、異なるサブ・グループにおけるアドレスは、インターブ後は、異なるサブ・フレームに属する。すなわち、各サブ・グループ内では、ターボ・インターブが効果的である。

## 【0045】

サブ・グループの完全性が、インターブを用いて維持されていても、サブ・グループ内の実際のインターブ動作は、オリジナルの QPP 式を用いて計算される必要がある。そして、これは、おのののサブ・フレームについてなされる必要がある。

## 【0046】

上記の実施の例では、クロック・サイクル毎に 4 つの讀取と 4 つの書き込みを含む、インデクス  $m \cdot L + 2k$ 、 $m \cdot L + 2k + 1$ 、 $n \cdot L + L - 1 - 2k$ 、 $n \cdot L + L - 2 - 2k$ 、あるいは、 $(m \cdot L + 2k)$ 、 $(m \cdot L + 2k + 1)$ 、 $(n \cdot L + L - 1 - 2k)$ 、 $(n \cdot L + L - 2 - 2k)$  を持つ APP 値にアクセスする必要がある。同時の讀取および書き込みは、デュアル・ポート RAM 設計によって解決される。4 つの讀取または書き込みの間で競合が無いことを保証するために、一例として、全体で N 個の APP 値が、 $M = 4$  のサブ・グループに分割される。これに対応して、4 つの RAM バンクが使用される。ここで、第 1 の RAM バンクが、P[4i] の APP 値を含み、第 2 の RAM バンクが、P[4i+1] に関する APP 値を含み、第 3 の RAM バンクが、P[4i+2] に関する APP 値を含み、最後の RAM バンクが、P[4i+3] に関する APP 値を含みうる。L の典型的な値は、32/64/128 である。QPP のサブ・グループ・インターブ特性によって、 $m \cdot L + 2k$ 、 $m \cdot L + 2k + 1$ 、 $n \cdot L + L - 1 - 2k$ 、 $n \cdot L + L - 2 - 2k$

10

20

30

40

50

2 - 2 k であるか、あるいは、(m · L + 2 k)、(m · L + 2 k + 1)、(n · L + L - 1 - 2 k)、(n · L + L - 2 - 2 k) である 4 つのアドレスが常に、異なる R A M バンクに格納された異なるサブ・グループに属することを、これら L の値を用いて確認することが容易である。この結果、上述した A P P 値は常に、競合も衝突も無く、同時にアクセスされうる。

例として、

上記例におけるデュアル・ポート R A M は、A P P 値を、8 つのインタリーブ・サブ・グループへ分割することによって回避されうる。ここで、おのののサブ・グループは、個別の单一ポート R A M ファイルに格納される。单一ポート R A M は、任意の時間に、読み取りまたは書き込みされうる。クロック・サイクル毎の 4 つの読み取りおよび 4 つの書き込みは、1 つのクロック・サイクルにおいて、各 R A M ファイルからの 1 つである、8 つの値を読み取ること、および、次のクロック・サイクルにおいて、各 R A M ファイルについて 1 つである、8 つの値を書き込むこと等によって達成されうる。

#### 【 0 0 4 7 】

全ての符号ブロック・サイズが 8 の倍数であることが事実であると仮定すると、1 つの R A M バンク内に各インタリーブ・サブ・グループを備えるように、8 つの R A M バンクに A P P 値を分割することによって、最大 8 つの同時 A P P アクセスが可能である。16、32、または 64 の倍数である大きな符号ブロック・サイズの場合、A P P 値を、16、32、または 64 の R A M バンクにそれぞれ分割することによって、それぞれ最大 16、32、または 64 の同時 A P P アクセスがなされうる。ここで、各インタリーブ・サブ・グループは、1 つの R A M バンクに格納される。

#### 【 0 0 4 8 】

図 4 を参照して、主題とするイノベーションにしたがって、4 つのサブ・グループを含む事後確率 (A P P) ランダム・アクセス・メモリ (R A M) 設計 400 の例が示されている。A P P R A M 設計 400 は、(例えば、R A M 0、R A M 1、R A M 2、および R A M 3 によって示される) 4 つのファイルを含みうる。A P P 値は、おののが 1 つの R A M ファイルに格納された 4 つのインタリーブ・サブ・グループへ分割される。

#### 【 0 0 4 9 】

T D E C は、T u r b o 反復中に、インタリーバ・アドレスまたはデインタリーバ・アドレスを計算する必要がある。この計算は、Q P P に直接的に基づく。Q P P 計算ロジックは、おのののクロック・サイクル内のおのののサブ・グループについて 1 つのインタリーバ・アドレスを計算するために、おのののサブ・グループについて一度ずつ、複数回実証される必要がある。

#### 【 0 0 5 0 】

図 5 に示すように、基數 - 2 構成および基數 - 4 構成の例示 500 が図示されている。基數 - 2 502 が、基數 - 4 504 とともに示されうる。ターボ・デコーダ内の M A P デコーダは、基數 - 4 構成として実現されうることが認識されるべきである。基數 - 4 504 では、2 トレリス移行が、1 つのクロック・サイクルでなされうる。さらに、基數 - 4 504 では、より複雑な状態判定基準計算が存在する。したがって、A P P R A M からの 2 つの値は、基數 - 4 504 を用いて、おのののクロック・サイクル内でアクセスされうる。

#### 【 0 0 5 1 】

図 6 を参照して、読み取り動作または書き込み動作中の誤りを低減するために、R A M をセグメント化することに関連する方法が示されられる。説明を単純にする目的で、これら方法は、一連の動作として示され説明されているが、これら方法は、1 または複数の実施形態にしたがって、幾つかの動作が本明細書で示され記載されたものとは異なる順序で、あるいは他の動作と同時に生じうるので、動作の順序によって限定されないことが理解され認識されるべきである。例えば、当業者であれば、これら方法はその代わりに、例えば状態図におけるように、一連の相互関連する状態またはイベントとして表されうることを理解し認識するだろう。さらに、1 または複数の実施形態にしたがって方法を実現するために、必

10

20

30

40

50

すしも例示されたすべての動作が必要とされる訳ではない。

【0052】

競合の無いメモリ・アクセスを提供するターボ・デコーダを適用することを容易にする方法600を図6に示す。参照番号602では、事後確率(APP)ランダム・アクセス・メモリ(RAM)が特定されうる。参照番号604では、APP RAMが、少なくとも2ファイルへ構成されうる。参照番号606では、すべてのAPP値が、2次置換多項式(QPP)ターボ・インタリーバに基づいて、少なくとも2つのインタリーブ・サブ・グループへ分割されうる。参照番号608では、個別のインタリーブ・サブ・グループが、個別のRAMファイルにマップされうる。

【0053】

図7は、無線通信システムにおいて、メモリ衝突を回避するために、ターボ・デコーダのためのメモリの一部を構成することを容易にするモバイル・デバイス700の例の例示である。モバイル・デバイス700は、例えば(図示しない)受信アンテナから信号を受信し、受信した信号について一般的な動作(例えば、フィルタ、增幅、ダウンコンバート等)を実行し、これら調整された信号をデジタル化してサンプルを得る受信機702を備えうる。受信機702は、受信したシンボルを復調し、それらをチャネル推定のためにプロセッサ706へ提供する復調器704を備えうる。プロセッサ706は、受信機702によって受信された情報を分析すること、および/または、送信機716による送信のための情報を生成することに特化されたプロセッサ、モバイル・デバイス700の1または複数の構成要素を制御するプロセッサ、および/または、受信機702によって受信された情報を分析することと、送信機716による送信のための情報を生成することと、モバイル・デバイス700のうちの1または複数の構成要素を制御することとのすべて行うプロセッサでありうる。

【0054】

モバイル・デバイス700さらに、プロセッサ706に動作可能に接続されたメモリ708を備えうる。このメモリ708は、送信されるデータ、受信したデータ、利用可能なチャネルに関連する情報、分析された信号および/または干渉強度に関連付けられたデータ、割り当てられたチャネルや電力やレート等に関連する情報、および、チャネルの推定およびチャネルを介した通信のために適切なその他任意の情報を格納しうる。メモリ708はさらに、(例えば、パフォーマンス・ベース、キャパシティ・ベース等での)チャネルの推定および/または利用に関連付けられたアルゴリズムおよび/またはプロトコルを格納しうる。

【0055】

本明細書に記載されたデータ・ストア(例えば、メモリ708)は、揮発性メモリであるか、あるいは不揮発性メモリである。あるいは、揮発性メモリと不揮発性メモリとの両方を含みうることが認識されるだろう。限定ではなく例示によって、不揮発性メモリは、読み専用メモリ(ROM)、プログラマブルROM(PROM)、電子的プログラマブルROM(E PROM)、電子的消去可能PROM(EEPROM)、あるいはフラッシュ・メモリを含みうる。揮発性メモリは、外部キャッシュ・メモリとして動作するランダム・アクセス・メモリ(RAM)を含みうる。限定ではなく例示によって、RAMは、例えばシンクロナスRAM(SRAM)、ダイナミックRAM(DRAM)、シンクロナスSDRAM(SDRAM)、ダブル・データ・レートSDRAM(DDR SDRAM)、エンハンストSDRAM(ESDRAM)、シンクリンクDRAM(SLDRAM)、およびダイレクト・ラムバスRAM(DRRAM(登録商標))のような多くの形態で利用可能である。主題となるシステムおよび方法のメモリ708は、限定される訳ではないが、これらおよびその他任意の適切なタイプのメモリを備えることが意図される。

【0056】

プロセッサ706はさらに、評価モジュール710および/または構成モジュール712に動作可能に接続されうる。評価モジュール710は、APP RAMの一部を特定し、検査しうる。さらに、構成モジュール712は、メモリ競合および/またはメモリ衝突

10

20

30

40

50

を回避するために、セグメントがターボ・デコーダ内のMAPデコーダに対応するようにAPP RAMをセグメント化または分割しうる。構成モジュール712は、2次置換多項式(QPP)ターボ・インターバに基づいて、すべてのAPP値を、少なくとも2つのインターブ・サブ・グループへ分割しうる。構成モジュール712は、個別のインターブ・サブ・グループを、個別のRAMファイルへマップしうる。

#### 【0057】

モバイル・デバイス700はさらに、信号を変調する変調器714と、この信号を例えれば基地局、別のモバイル・デバイス等へ送信する送信機716とを備える。プロセッサ706と別に示されているが、評価モジュール710、構成モジュール712、復調器704、および/または、変調器714は、プロセッサ706または複数のプロセッサ(図示せず)の一部でありうることが認識されるべきである。10

#### 【0058】

図8は、前述したように、無線通信環境において、メモリ衝突を回避するために、事後確率(APP)ランダム・アクセス・メモリ(RAM)を分割することを容易にするシステム800の例の例示である。このシステム800は、複数の受信アンテナ806によって1または複数のモバイル・デバイス804から信号を受信する受信機810と、送信アンテナ808によって1または複数のモバイル・デバイス804へ信号を送信する送信機824とを備える、基地局802(例えば、アクセス・ポイント)を備える。受信機810は、受信アンテナ806から情報を受信する。さらに、受信した情報を復調する復調器812と動作可能に関連付けられている。復調されたシンボルは、図7に関連して上述されたプロセッサと類似のプロセッサ814によって分析される。プロセッサ814は、信号(例えばパイラット)強度および/または干渉強度を推定することに関連する情報、モバイル・デバイス804(または(図示しない)別の基地局)へ/から送信される/受信されたデータ、および/または、本明細書に記載されたさまざまな動作および機能を実行することに関連するその他任意の適切な情報を格納するメモリ816に結合されている。20

#### 【0059】

プロセッサ814はさらに、評価モジュール818および/または構成モジュール820に接続される。評価モジュール818は、APP RAMと、関連付けられたサイズとを特定しうる。構成モジュール820は、おのののファイルおよび/またはサブ・グループ間の隔離を保証するために、APP RAM内のおのののファイル内に、少なくとも2つのファイルおよびサブ・グループを生成しうる。構成モジュール820は、すべてのAPP値を、2次置換多項式(QPP)ターボ・インターバに基づいて、少なくとも2つのインターブ・サブ・グループに分割しうる。構成モジュール820は、個別のインターブ・サブ・グループを、個別のRAMファイルにマップしうる。さらに、プロセッサ814と別に示されているが、評価モジュール818、構成モジュール820、復調器812、および/または、変調器822は、プロセッサ814または複数のプロセッサ(図示せず)のうちの一部でありうることが認識されるべきである。30

#### 【0060】

図9は、無線通信システム900の例を示す。無線通信システム900は、簡潔さの目的で、1つの基地局910と1つのモバイル・デバイス950とを示している。しかしながら、システム900は、1より多い基地局、および/または、1より多いモバイル・デバイスを含むことができ、これら追加の基地局および/またはモバイル・デバイスは、以下に説明する基地局910およびモバイル・デバイス950の例と実質的に同じでも、別のものもありうることが認識されるべきである。それに加えて、基地局910および/またはモバイル・デバイス950は、本明細書に記載されたシステム(図1-3、図7-8)、技術/構成(図4-5)、および/または、方法(図56)を用いて、その間の無線通信を容易にする。40

#### 【0061】

基地局910では、多くのデータ・ストリームのためのトラフィック・データが、データ・ソース912から送信(TX)データ・プロセッサ914へ提供される。一例によれ50

ば、おのののデータ・ストリームが、それぞれのアンテナを介して送信される。TXデータ・プロセッサ914は、トライフィック・データ・ストリームをフォーマットし、このデータ・ストリームのために選択された特定の符号化スキームに基づいて符号化し、インタリープして、符号化されたデータを提供する。

【0062】

おのののデータ・ストリームの符号化されたデータは、直交周波数分割多重化(OFDM)技術を用いてパイロット・データと多重化されうる。さらに、あるいは、その代わりに、パイロット・シンボルは、周波数分割多重化(FDM)、時分割多重化(TDM)、あるいは符号分割多重化(CDM)されうる。パイロット・データは一般に、既知の方法で処理される既知のデータ・パターンであり、チャネル応答を推定するためにモバイル・デバイス950において使用されうる。おのののデータ・ストリームについて多重化されたパイロットおよび符号化されたデータは、データ・ストリームのために選択された特定の変調スキーム(例えば、バイナリ・フェーズ・シフト・キーイング(BPSK)、直交フェーズ・シフト・キーイング(QPSK)、Mフェーズ・シフト・キーイング(M-PSK)、M直交振幅変調(M-QAM)等)に基づいて変調(例えば、シンボル・マップ)され、変調シンボルが提供される。おのののデータ・ストリームのデータ・レート、符号化、および変調は、プロセッサ930によって実行または提供される命令によって決定されうる。

【0063】

データ・ストリームの変調シンボルは、(例えば、OFDMのために)変調シンボルを処理するTX MIMOプロセッサ920に提供される。TX MIMOプロセッサ920はその後、 $N_T$ 個の変調シンボル・ストリームを、 $N_T$ 個の送信機(TMTR)922a乃至922tへ提供する。さまざまな実施形態において、TX MIMOプロセッサ920は、データ・ストリームのシンボル、および、そのシンボルが送信されるアンテナへ、ビームフォーミング重みを適用する。

【0064】

おののの送信機922は、1または複数のアナログ信号を提供するために、それぞれのシンボル・ストリームを受信して処理し、さらには、MIMOチャネルを介した送信に適切な変調信号を提供するために、このアナログ信号を調整(例えば、増幅、フィルタ、およびアップコンバート)する。さらに、送信機922a乃至922tからの $N_T$ 個の変調信号は、 $N_T$ 個のアンテナ924a乃至924tそれから送信される。

【0065】

モバイル・デバイス950では、送信された変調信号が、 $N_R$ 個のアンテナ952a乃至952rによって受信され、おのののアンテナ952から受信した信号が、それぞれの受信機(RCVR)954a乃至954rへ提供される。おののの受信機954は、それぞれの信号を調整(例えば、フィルタ、増幅、およびダウンコンバート)し、この調整された信号をデジタル化してサンプルを提供し、さらにこのサンプルを処理して、対応する「受信された」シンボル・ストリームを提供する。

【0066】

RXデータ・プロセッサ960は、 $N_R$ 個の受信機954から $N_R$ 個のシンボル・ストリームを受信し、受信されたこれらシンボル・ストリームを、特定の受信機処理技術に基づいて処理して、 $N_T$ 個の「検出された」シンボル・ストリームを提供する。RXデータ・プロセッサ960は、検出されたおのののシンボル・ストリームを復調し、デインタリープし、復号して、そのデータ・ストリームのためのトライフィック・データを復元する。RXデータ・プロセッサ960による処理は、基地局910におけるTX MIMOプロセッサ920およびTXデータ・プロセッサ914によって実行されるものと相補的である。

【0067】

プロセッサ970は、上述したように、どのプリコーディング行列を使用するのかを定期的に決定する。さらに、プロセッサ970は、行列インデクス部およびランク値部を備

10

20

30

40

50

えた逆方向リンク・メッセージを規定することができる。

【0068】

逆方向リンク・メッセージは、通信リンクおよび／または受信されたデータ・ストリームに関するさまざまなタイプの情報を備えうる。逆方向リンク・メッセージは、多くのデータ・ストリームに関するトラフィック・データをデータ・ソース936から受け取るTXデータ・プロセッサ938によって処理され、変調器980によって変調され、送信機954a乃至954rによって調整され、基地局910へ送り戻される。

【0069】

基地局910では、モバイル・デバイス950からの変調信号が、アンテナ924によって受信され、受信機922によって調整され、復調器940によって復調され、RXデータ・プロセッサ942によって処理されて、モバイル・デバイス950によって送信された逆方向リンク・メッセージを抽出する。さらに、プロセッサ930は、ビームフォーミング重みを決定するためにどのプリコーディング行列を使用するかを決定するために、この抽出されたメッセージを処理する。

10

【0070】

プロセッサ930およびプロセッサ970は、基地局910およびモバイル・デバイス950それぞれにおける動作を指示（例えば、制御、調整、管理等）する。プロセッサ930およびプロセッサ970はそれぞれ、プログラム・コードおよびデータを格納するメモリ932およびメモリ972に関連付けられうる。プロセッサ930およびプロセッサ970はまた、アップリンクおよびダウンリンクそれぞれのための周波数およびインパルス応答推定値を導出する計算をも実行する。

20

【0071】

本明細書に記載された実施形態は、ハードウェア、ソフトウェア、ファームウェア、ミドルウェア、マイクロコード、あるいはこれらの任意の組み合わせで実現されうることが理解されるべきである。ハードウェアで実現する場合、処理ユニットは、1または複数の特定用途向けIC（ASIC）、デジタル信号プロセッサ（DSP）、デジタル信号処理デバイス（DSPD）、プログラム可能論理回路（PLD）、フィールド・プログラム可能ゲート・アレイ（FPGA）、プロセッサ、コントローラ、マイクロ・コントローラ、マイクロプロセッサ、本明細書に記載の機能を実行するために設計されたその他の電子ユニット、あるいはこれらの組み合わせ内に実装されうる。

30

【0072】

これら実施形態が、ソフトウェア、ファームウェア、ミドルウェアあるいはマイクロコード、プログラム・コードあるいはコード・セグメントで実現される場合、これらは、例えば記憶素子のような機械読取可能な媒体に格納されうる。コード・セグメントは、手順、機能、サブプログラム、プログラム、ルーチン、サブルーチン、モジュール、ソフトウェア・パッケージ、クラス、または、命令、データ構造、あるいはプログラム文からなる任意の組み合わせを表すことができる。コード・セグメントは、情報、データ、引数、パラメータ、あるいは記憶内容の引渡および／または受信を行うことによって、他のコード・セグメントまたはハードウェア回路に接続されうる。情報、引数、パラメータ、データなどは、メモリ共有、メッセージ引渡し、トークン引渡、ネットワーク送信などを含む任意の適切な手段を用いて引渡、転送、あるいは送信されうる。

40

【0073】

ソフトウェアで実現する場合、本明細書に記載のこれら技術は、本明細書に記載の機能を実行するモジュール（例えば、手続き、機能等）を用いて実現されうる。ソフトウェア・コードは、メモリ・ユニット内に格納され、プロセッサによって実行されうる。メモリ・ユニットは、プロセッサ内部またはプロセッサ外部に実装されうる。プロセッサ外部に実装される場合、メモリ・ユニットは、当該技術分野で周知のさまざまな手段によってプロセッサと通信可能に接続されうる。

【0074】

図10を参照して、競合の無いメモリ・アクセスを提供するターボ・デコーダを適用す

50

るシステム 1000 が例示される。例えば、システム 1000 は、基地局、モバイル・デバイスなどの中に少なくとも部分的に存在しうる。システム 1000 は、プロセッサ、ソフトウェア、またはそれらの組み合わせ（例えば、ファームウェア）によって実現される機能を表す機能ブロックでありうる機能ブロックを含むものとして示されることが認識されるべきである。システム 1000 は、連携して動作しうる電子構成要素の論理グループ 1002 を含む。論理グループ 1002 は事後確率（APP）ランダム・アクセス・メモリを特定するための電子構成要素 1004 を含みうる。さらに、論理グループ 1002 は、APP RAM を少なくとも 2 つのファイルに構成するための電子構成要素 1006 を備えうる。さらに、論理グループ 1002 は、すべての APP 値を、2 次置換多項式（QPP）ターボ・インタリーバに基づいて、少なくとも 2 つのインタリーブ・サブ・グループに分割するための電子構成要素 1008 を含みうる。さらに、論理グループ 1002 は、個別のインタリーブ・サブ・グループを個別の RAM ファイルにマップするための電子構成要素 1010 を備えうる。さらに、システム 1000 は、電子構成要素 1004、1006、1008、1010 に関連付けられた機能を実行するための命令群を保持するメモリ 1012 を含みうる。メモリ 1012 の外側にあると示されているが、電子構成要素 1004、1006、1008、1010 のうちの 1 または複数は、メモリ 1012 内に存在しうることが理解されるべきである。10

#### 【0075】

上述したものは、1 または複数の実施形態の一例を含んでいる。もちろん、上述した実施形態を説明する目的で、構成要素または方法の考えられるすべての組み合わせを記述することは可能ではないが、当業者であれば、さまざまな実施形態のさらに多くの組み合わせおよび置き換えが可能であることを認識することができる。したがって、記載された実施形態は、特許請求の範囲の精神およびスコープ内にあるそのようなすべての変更、変更、および変形を含むことが意図される。さらにまた、用語「含む」が、詳細説明あるいは特許請求の範囲のうちの何れかで使用されている限り、その用語は、用語「備える」が、請求項における遷移語として適用される場合に解釈される用語「備える」と同様に、包括的であることが意図される。20

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

#### 【C1】

競合の無いメモリ・アクセスを提供するターボ・デコーダを適用することを容易にする無線通信システムにおいて使用される方法であって、30

事後確率（APP）ランダム・アクセス・メモリ（RAM）を特定することと、

前記 APP RAM を、少なくとも 2 つの RAM ファイルへ構成することと、

すべての APP 値を、2 次置換多項式（QPP）ターボ・インタリーバに基づいて、少なくとも 2 つのインタリーブ・サブ・グループに分割することと、

個別のインタリーブ・サブ・グループを、個別の RAM ファイルにマップすることと、を備える方法。40

#### 【C2】

MAP パラレル・デコーダが、前記インタリーブ・サブ・グループのうちの少なくとも 1 つへの読み取りまたは書き込みのうちの少なくとも 1 つを用いる、C1 に記載の方法。40

#### 【C3】

MAP パラレル・デコーダが、前記インタリーブ・サブ・グループのうちの少なくとも 1 つへの読み取りまたは書き込みのうちの少なくとも 1 つを用いるように隔離された、C1 に記載の方法。

#### 【C4】

前記 APP RAM を、2 つの RAM ファイルへ構成することと、

前記 2 つの RAM ファイルのおののおののためのサブ・グループを生成することと、

をさらに備える C1 に記載の方法。

#### 【C5】

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用す50

ること、をさらに備えるC4に記載の方法。

[C6]

前記APP RAMを、4つのRAMファイルに構成することと、

前記4つのRAMファイルのおののためのサブ・グループを生成することと、

をさらに備えるC1に記載の方法。

[C7]

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用すること

、をさらに備えるC6に記載の方法。

[C8]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用す

ること、をさらに備えるC6に記載の方法。

10

[C9]

$nL + 4k$ のフォーマットで第1のサブ・グループをフォーマットすることと、ここで

、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり、k

は、サブ・グループ・インデクスである、

$nL + 4k + 1$ のフォーマットで第2のサブ・グループをフォーマットすることと、こ

こで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり

、kは、サブ・グループ・インデクスである、

$nL + 4k + 2$ のフォーマットで第3のサブ・グループをフォーマットすることと、こ

こで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり

、kは、サブ・グループ・インデクスである、

20

$nL + 4k + 3$ のフォーマットで第4のサブ・グループをフォーマットすることと、こ

こで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり

、kは、サブ・グループ・インデクスである、

サブ・グループ内の第1のAPP値と、別のサブ・グループ内の第2のAPP値とにア

クセスすることと、

をさらに備えるC6に記載の方法。

[C10]

前記APP RAMを、8つのRAMファイルへ構成することと、

前記8つのRAMファイルのおののためのサブ・グループを生成することと、

をさらに備えるC1に記載の方法。

30

[C11]

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用すること

、をさらに備えるC10に記載の方法。

[C12]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用す

ること、をさらに備えるC10に記載の方法。

[C13]

前記APP RAMを、16のRAMファイルへ構成することと、

前記16のRAMファイルのおののためのサブ・グループを生成することと、

をさらに備えるC1に記載の方法。

40

[C14]

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用すること

、をさらに備えるC13に記載の方法。

[C15]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用す

ること、をさらに備えるC13に記載の方法。

[C16]

前記APP RAMを、32のRAMファイルへ構成することと、

前記32のRAMファイルのおののためのサブ・グループを生成することと、

50

をさらに備える C 1 に記載の方法。

[ C 1 7 ]

同時の読み取りおよび書き込みを提供するために、デュアル・ポート RAM 設計を利用するこ

と、をさらに備える C 1 6 に記載の方法。

[ C 1 8 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用す

ること、をさらに備える C 1 6 に記載の方法。

[ C 1 9 ]

前記 Q P P ターボ・インターバに関連するサブ・グループを持つメンバシップを保持

することをさらに備え、

10

前記 Q P P ターボ・インターバのサブ・グループに対するメンバシップは、 A P P

R A M 内のサブ・グループのメンバシップに変わる、 C 1 に記載の方法。

[ C 2 0 ]

無線通信装置であって、

事後確率 ( A P P ) ランダム・アクセス・メモリ ( R A M ) を特定し、

前記 A P P R A M を、少なくとも 2 つの R A M ファイルへ構成し、

すべての A P P 値を、2 次置換多項式 ( Q P P ) ターボ・インターバに基づいて、少

なくとも 2 つのインターブ・サブ・グループに分割し、

個別のインターブ・サブ・グループを、個別の R A M ファイルにマップする、

ように構成された少なくとも 1 つのプロセッサと、

20

前記少なくとも 1 つのプロセッサに接続されたメモリと、

を備える無線通信装置。

[ C 2 1 ]

M A P パラレル・デコーダが、前記インターブ・サブ・グループのうちの少なくとも

1 つへの読み取りまたは書き込みのうちの少なくとも 1 つを用いる、 C 2 0 に記載の無線通信装置

。

[ C 2 2 ]

M A P パラレル・デコーダが、前記インターブ・サブ・グループのうちの少なくとも

1 つへの読み取りまたは書き込みのうちの少なくとも 1 つを用いるように隔離された、 C 2 0 に記

載の無線通信装置。

30

[ C 2 3 ]

前記 A P P R A M を、2 つの R A M ファイルへ構成し、

前記 2 つの R A M ファイルのおののおののためのサブ・グループを生成する、

ように構成された少なくとも 1 つのプロセッサをさらに備える C 2 0 に記載の無線通信装

置。

[ C 2 4 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用す

る、ように構成された少なくとも 1 つのプロセッサをさらに備える C 2 3 に記載の無線通

信装置。

40

[ C 2 5 ]

前記 A P P R A M を、4 つの R A M ファイルに構成し、

前記 4 つの R A M ファイルのおののおののためのサブ・グループを生成する、

ように構成された少なくとも 1 つのプロセッサをさらに備える C 2 0 に記載の無線通信装

置。

[ C 2 6 ]

同時の読み取りおよび書き込みを提供するために、デュアル・ポート RAM 設計を利用する、よ

うに構成された少なくとも 1 つのプロセッサをさらに備える C 2 5 に記載の無線通信装置

。

[ C 2 7 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用す

50

る、ように構成された少なくとも1つのプロセッサをさらに備えるC25に記載の無線通信装置。

[C28]

n L + 4 k のフォーマットで第1のサブ・グループをフォーマットし、ここで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり、kは、サブ・グループ・インデクスである、

n L + 4 k + 1 のフォーマットで第2のサブ・グループをフォーマットし、ここで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり、kは、サブ・グループ・インデクスである、

n L + 4 k + 2 のフォーマットで第3のサブ・グループをフォーマットし、ここで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり、kは、サブ・グループ・インデクスである、

n L + 4 k + 3 のフォーマットで第4のサブ・グループをフォーマットし、ここで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり、kは、サブ・グループ・インデクスである、

サブ・グループ内の第1のAPP値と、別のサブ・グループ内の第2のAPP値とにアクセスする、

ように構成された少なくとも1つのプロセッサをさらに備えるC25に記載の無線通信装置。

[C29]

前記APP RAMを、8つのRAMファイルへ構成し、

前記8つのRAMファイルのおののためのサブ・グループを生成する、

ように構成された少なくとも1つのプロセッサをさらに備えるC20に記載の無線通信装置。

[C30]

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用する、ように構成された少なくとも1つのプロセッサをさらに備えるC29に記載の無線通信装置。

[C31]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、ように構成された少なくとも1つのプロセッサをさらに備えるC29に記載の無線通信装置。

[C32]

前記APP RAMを、16のRAMファイルへ構成し、

前記16のRAMファイルのおののためのサブ・グループを生成する、

ように構成された少なくとも1つのプロセッサをさらに備えるC20に記載の無線通信装置。

[C33]

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用する、ように構成された少なくとも1つのプロセッサをさらに備えるC32に記載の無線通信装置。

[C34]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、ように構成された少なくとも1つのプロセッサをさらに備えるC32に記載の無線通信装置。

[C35]

前記APP RAMを、32のRAMファイルへ構成し、

前記32のRAMファイルのおののためのサブ・グループを生成する、

ように構成された少なくとも1つのプロセッサをさらに備えるC20に記載の無線通信装置。

10

20

30

40

50

## [ C 3 6 ]

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用する、よう構成された少なくとも1つのプロセッサをさらに備えるC35に記載の無線通信装置。

## [ C 3 7 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する、よう構成された少なくとも1つのプロセッサをさらに備えるC35に記載の無線通信装置。

## [ C 3 8 ]

前記QPPターボ・インターバに関連するサブ・グループを持つメンバシップを保持するように構成された少なくとも1つのプロセッサをさらに備え、

前記QPPターボ・インターバのサブ・グループに対するメンバシップは、APP RAM内のサブ・グループのメンバシップに変わる、C20に記載の無線通信装置。

## [ C 3 9 ]

競合の無いメモリ・アクセスを提供するターボ・デコーダを適用する無線通信装置であつて、

事後確率(APP)ランダム・アクセス・メモリ(RAM)を特定する手段と、

前記APP RAMを、少なくとも2つのRAMファイルへ構成する手段と、

すべてのAPP値を、2次置換多項式(QPP)ターボ・インターバに基づいて、少なくとも2つのインターブ・サブ・グループに分割する手段と、

個別のインターブ・サブ・グループを、個別のRAMファイルにマップする手段と、を備える無線通信装置。

## [ C 4 0 ]

MAPパラレル・デコーダが、前記インターブ・サブ・グループのうちの少なくとも1つへの読み取りまたは書き込みのうちの少なくとも1つを用いる、C39に記載の無線通信装置。

## [ C 4 1 ]

MAPパラレル・デコーダが、前記インターブ・サブ・グループのうちの少なくとも1つへの読み取りまたは書き込みのうちの少なくとも1つを用いるように隔離された、C39に記載の無線通信装置。

## [ C 4 2 ]

前記APP RAMを、2つのRAMファイルへ構成する手段と、

前記2つのRAMファイルのおののためのサブ・グループを生成する手段と、をさらに備えるC39に記載の無線通信装置。

## [ C 4 3 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する手段、をさらに備えるC42に記載の無線通信装置。

## [ C 4 4 ]

前記APP RAMを、4つのRAMファイルへ構成する手段と、

前記4つのRAMファイルのおののためのサブ・グループを生成する手段と、をさらに備えるC39に記載の無線通信装置。

## [ C 4 5 ]

同時の読み取りおよび書き込みを提供するために、デュアル・ポートRAM設計を利用する手段、をさらに備えるC44に記載の無線通信装置。

## [ C 4 6 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する手段、をさらに備えるC44に記載の無線通信装置。

## [ C 4 7 ]

nL + 4kのフォーマットで第1のサブ・グループをフォーマットする手段と、ここで、nは、サブ・グループ内のインデクスであり、Lは、サブ・グループの長さであり、k

10

20

30

40

50

は、サブ・グループ・インデクスである、

$n L + 4 k + 1$  のフォーマットで第 2 のサブ・グループをフォーマットする手段と、ここで、 $n$  は、サブ・グループ内のインデクスであり、 $L$  は、サブ・グループの長さであり、 $k$  は、サブ・グループ・インデクスである、

$n L + 4 k + 2$  のフォーマットで第 3 のサブ・グループをフォーマットする手段と、ここで、 $n$  は、サブ・グループ内のインデクスであり、 $L$  は、サブ・グループの長さであり、 $k$  は、サブ・グループ・インデクスである、

$n L + 4 k + 3$  のフォーマットで第 4 のサブ・グループをフォーマットする手段と、ここで、 $n$  は、サブ・グループ内のインデクスであり、 $L$  は、サブ・グループの長さであり、 $k$  は、サブ・グループ・インデクスである、

サブ・グループ内の第 1 の APP 値と、別のサブ・グループ内の第 2 の APP 値とにアクセスする手段と、

をさらに備える C 4 4 に記載の無線通信装置。

[ C 4 8 ]

前記 APP RAM を、8 つの RAM ファイルへ構成する手段と、

前記 8 つの RAM ファイルのおののためのサブ・グループを生成する手段と、

をさらに備える C 3 9 に記載の無線通信装置。

[ C 4 9 ]

同時の読み取りおよび書き込みを提供するために、デュアル・ポート RAM 設計を利用する手段、をさらに備える C 4 8 に記載の無線通信装置。

10

[ C 5 0 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する手段、をさらに備える C 4 8 に記載の無線通信装置。

[ C 5 1 ]

前記 APP RAM を、16 の RAM ファイルへ構成する手段と、

前記 16 の RAM ファイルのおののためのサブ・グループを生成する手段と、

をさらに備える C 4 8 に記載の無線通信装置。

20

[ C 5 2 ]

同時の読み取りおよび書き込みを提供するために、デュアル・ポート RAM 設計を利用する手段、をさらに備える C 5 1 に記載の無線通信装置。

30

[ C 5 3 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する手段、をさらに備える C 5 1 に記載の無線通信装置。

[ C 5 4 ]

前記 APP RAM を、32 の RAM ファイルへ構成する手段と、

前記 32 の RAM ファイルのおののためのサブ・グループを生成する手段と、

をさらに備える C 4 8 に記載の無線通信装置。

40

[ C 5 5 ]

同時の読み取りおよび書き込みを提供するために、デュアル・ポート RAM 設計を利用する手段、をさらに備える C 5 4 に記載の無線通信装置。

[ C 5 6 ]

サブ・グループのための書き込みと読み取りとの間にクロック・サイクル・オフセットを適用する手段、をさらに備える C 5 4 に記載の無線通信装置。

[ C 5 7 ]

前記 QPP ターボ・インターバに関連するサブ・グループを持つメンバシップを保持する手段をさらに備え、

前記 QPP ターボ・インターバのサブ・グループに対するメンバシップは、APP RAM 内のサブ・グループのメンバシップに変わる、C 3 9 に記載の無線通信装置。

[ C 5 8 ]

コンピュータ・プログラム製品であって、

50

少なくとも1つのコンピュータに対して、事後確率( APP )ランダム・アクセス・メモリ( RAM )を特定させるためのコードと、

少なくとも1つのコンピュータに対して、前記 APP RAM を、少なくとも2つの RAM ファイルへ構成させるためのコードと、

少なくとも1つのコンピュータに対して、すべての APP 値を、2次置換多項式( QPP )ターボ・インタリーバに基づいて、少なくとも2つのインタリーブ・サブ・グループに分割させるためのコードと、

少なくとも1つのコンピュータに対して、個別のインタリーブ・サブ・グループを、個別の RAM ファイルにマップさせるためのコードと、

を備えるコンピュータ読取可能な媒体を備える、コンピュータ・プログラム製品。

10

【図1】

FIG. 1

【図3】

FIG. 3

【図2】

FIG. 2

【図4】

図4

FIG. 4

【図5】

図5

FIG. 5

【図6】

図6

FIG. 6

【図7】

図7

FIG. 7

〔 図 8 〕

图 8

FIG. 8

【 図 9 】

四 9

FIG. 9

【 図 1 0 】

図 10

FIG. 10

---

フロントページの続き

(72)発明者 パン、ハンファン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ウェイ、ヨンビン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 岡 裕之

(56)参考文献 米国特許出願公開第2008/0172591(US, A1)

国際公開第2009/070440(WO, A1)

特開2009-095008(JP, A)

国際公開第2006/082923(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H03M 13/29

IEEE Explore

Cini