(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7054577号

(P7054577)

(45)発行日 令和4年4月14日(2022.4.14)

(24)登録日 令和4年4月6日(2022.4.6)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3233(2016.01) | F I | G 0 9 G | 3/3233       |

| G 0 9 G | 3/3291(2016.01) |     | G 0 9 G | 3/3291       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 4 2 A |

| H 0 1 L | 51/50 (2006.01) |     | G 0 9 G | 3/20 6 3 1 V |

| H 0 1 L | 27/32 (2006.01) |     | G 0 9 G | 3/20 6 4 1 P |

請求項の数 20 (全11頁) 最終頁に続く

(21)出願番号 特願2017-222649(P2017-222649)

(22)出願日 平成29年11月20日(2017.11.20)

(65)公開番号 特開2019-95504(P2019-95504A)

(43)公開日 令和1年6月20日(2019.6.20)

審査請求日 令和2年11月16日(2020.11.16)

(73)特許権者 502161508

シナティクス インコーポレイテッド

アメリカ合衆国, 95131 カリフォ

ルニア州, サンノゼ, マッケイ ドラ

イブ 1251

(74)代理人 100205350

弁理士 狩野 芳正

(74)代理人 100117617

弁理士 中尾 圭策

(74)代理人 100182187

弁理士 高岡 正之

(72)発明者 青垣 多俊

東京都中野区中野4丁目10番2号 シ

ナティクス・ジャパン合同会社内

(72)発明者 降旗 弘史

最終頁に続く

(54)【発明の名称】 表示ドライバ、表示装置及びムラ補正方法

## (57)【特許請求の範囲】

## 【請求項1】

第一のディスプレイ輝度値と第一の階調値とに対応する輝度を出力する第二のディスプレイ輝度値における第二の階調値を算出するルックアップテーブルと、前記第二の階調値と前記第二のディスプレイ輝度値におけるムラ補正データとに基づき、ムラ補正量を算出する補正量演算回路と、前記ムラ補正量を用いて、入力画像データのムラ補正を行うムラ補正回路と、を備え、

前記第一のディスプレイ輝度値は前記第二のディスプレイ輝度値と異なる表示ドライバ。

## 【請求項2】

前記ムラ補正データを記憶するメモリを備え、前記補正量演算回路は、前記メモリから前記ムラ補正データを読み出し、前記第二の階調値に応じた前記ムラ補正量を算出する請求項1に記載の表示ドライバ。

## 【請求項3】

入力される第一のディスプレイ輝度値を、変換係数に変換するルックアップテーブルと、前記変換係数と、第二の階調値と第二のディスプレイ輝度値におけるムラ補正データとに基づき、第一の階調値と前記第一のディスプレイ輝度値におけるムラ補正量を算出する補正量演算回路と、

前記ムラ補正量を用いて、入力画像データのムラ補正を行うムラ補正回路と、

を備え、

前記変換係数は、前記ムラ補正データを、前記ムラ補正量に変換する係数であり、

前記第一のディスプレイ輝度値は前記第二のディスプレイ輝度値と異なり、

前記第二のディスプレイ輝度値と前記第二の階調値とに対応する輝度は、前記第一のディスプレイ輝度値と前記第一の階調値とに対応する輝度に対応する

表示ドライバ。

【請求項 4】

前記ルックアップテーブルは、

複数のディスプレイ輝度値のそれぞれに対応づけて前記変換係数を記憶するレジスタと、

前記第一のディスプレイ輝度値が入力されたとき、前記複数のディスプレイ輝度値及び前記変換係数に基づき線形補間処理を行い、前記第一のディスプレイ輝度値に対応する変換係数を算出する演算回路と、

を備える請求項3に記載の表示ドライバ。

10

【請求項 5】

前記ルックアップテーブルには、前記変換係数の下限値が設けられ、

所定のディスプレイ輝度値以下の前記第一のディスプレイ輝度値が前記ルックアップテーブルに入力されるとき、前記下限値に変換される請求項4に記載の表示ドライバ。

【請求項 6】

前記第二のディスプレイ輝度値は、最大ディスプレイ輝度値である請求項1乃至5のいずれか一項に記載の表示ドライバ。

20

【請求項 7】

前記第一のディスプレイ輝度値は、外部から入力されるディスプレイ輝度値に対応する請求項1乃至6のいずれか一項に記載の表示ドライバ。

【請求項 8】

表示パネルと、

第一のディスプレイ輝度値と第一の階調値とに対応する輝度を出力する第二のディスプレイ輝度値における第二の階調値を算出するルックアップテーブルと、

前記第二の階調値と、前記第二のディスプレイ輝度値におけるムラ補正データとに基づき、ムラ補正量を算出する補正量演算回路と、

前記ムラ補正量を用いて、入力画像データのムラ補正を行うムラ補正回路と、

30

前記ムラ補正回路からの出力に基づき、前記表示パネルを駆動する駆動回路と、

を備え、

前記第一のディスプレイ輝度値は前記第二のディスプレイ輝度値と異なる

表示装置。

【請求項 9】

前記ムラ補正データを記憶するメモリを備え、

前記補正量演算回路は、前記メモリから前記ムラ補正データを読み出し、前記第二の階調値に応じた前記ムラ補正量を算出する請求項8に記載の表示装置。

【請求項 10】

表示パネルと、

入力される第一のディスプレイ輝度値を、変換係数に変換するルックアップテーブルと、

前記変換係数と、第二のディスプレイ輝度値と第二の階調値におけるムラ補正データとに基づき、ムラ補正量を算出する補正量演算回路と、

前記ムラ補正量を用いて、入力画像データのムラ補正を行うムラ補正回路と、

前記ムラ補正回路からの出力に基づき、前記表示パネルを駆動する駆動回路と、

を備え、

40

前記変換係数は、前記ムラ補正データを前記ムラ補正量に変換する係数であり、

前記第一のディスプレイ輝度値は前記第二のディスプレイ輝度値と異なり、

前記第二のディスプレイ輝度値と前記第二の階調値とに対応する輝度は、前記第一のディスプレイ輝度値と第一の階調値とに対応する輝度に対応する

50

表示装置。

【請求項 1 1】

前記ルックアップテーブルは、

複数のディスプレイ輝度値のそれぞれに対応づけて前記変換係数を記憶するレジスタと、前記第一のディスプレイ輝度値が入力されたとき、前記複数のディスプレイ輝度値及び前記変換係数に基づき線形補間処理を行い、前記第一のディスプレイ輝度値に対応する変換係数を算出する演算回路と、を備える請求項10に記載の表示装置。

【請求項 1 2】

前記ルックアップテーブルには、前記変換係数の下限値が設けられ、

所定のディスプレイ輝度値以下の前記第一のディスプレイ輝度値が前記ルックアップテーブルに入力されるとき、前記下限値に変換される請求項 1 1 に記載の表示装置。 10

【請求項 1 3】

前記第二のディスプレイ輝度値は、最大ディスプレイ輝度値である請求項 8 乃至 1 2 のいずれか一項に記載の表示装置。

【請求項 1 4】

前記第一のディスプレイ輝度値は、外部から入力されるディスプレイ輝度値に対応する請求項 8 乃至 1 3 のいずれか一項に記載の表示装置。

【請求項 1 5】

第一のディスプレイ輝度値と第一の階調値とに対応する輝度を出力する第二のディスプレイ輝度値における第二の階調値を算出し、 20

前記第二の階調値と、前記第二のディスプレイ輝度値における表示パネルの表示ムラの補正に用いられるムラ補正データとに基づき、ムラ補正量を算出し、

前記第一のディスプレイ輝度値は前記第二のディスプレイ輝度値と異なるムラ補正方法。

【請求項 1 6】

前記ムラ補正データをメモリに記憶し、

前記メモリから読み出された前記ムラ補正データを用いて、前記第二の階調値に応じた前記ムラ補正量が算出される請求項 1 5 に記載のムラ補正方法。

【請求項 1 7】

ルックアップテーブルに入力された第一のディスプレイ輝度値を、変換係数に変換し、前記変換係数は、第二の階調値と第二のディスプレイ輝度値におけるムラ補正データを、第一の階調値に対応するムラ補正量に変換する係数であり、 30

前記変換係数と前記ムラ補正データとが演算処理され、前記ムラ補正量を算出し、前記第一のディスプレイ輝度値は前記第二のディスプレイ輝度値と異なり、

前記第二のディスプレイ輝度値と前記第二の階調値とに対応する輝度は、前記第一のディスプレイ輝度値と前記第一の階調値とに対応する輝度に対応するムラ補正方法。

【請求項 1 8】

複数のディスプレイ輝度値のそれぞれに対応づけて前記変換係数を記憶し、

前記第一のディスプレイ輝度値が入力されたとき、前記複数のディスプレイ輝度値及び前記変換係数に基づき線形補間処理を行い、前記第一のディスプレイ輝度値に対応する変換係数を算出する請求項 1 7 に記載のムラ補正方法。 40

【請求項 1 9】

前記ルックアップテーブルには、前記変換係数の下限値が設けられ、

所定のディスプレイ輝度値以下の前記第一のディスプレイ輝度値が前記ルックアップテーブルに入力されるとき、前記下限値に変換される請求項 1 7 又は 1 8 に記載のムラ補正方法。

【請求項 2 0】

前記第二のディスプレイ輝度値は、最大ディスプレイ輝度値である請求項 1 5 乃至 1 9 のいずれか一項に記載のムラ補正方法。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

表示ドライバ、表示装置及びムラ補正方法に関する。

## 【背景技術】

## 【0002】

液晶表示パネルやOrganic Light Emitting Diode (OLED) 表示パネル等の表示パネルは、例えば、ノートブックコンピュータやデスクトップコンピュータ、スマートフォンといった電子機器に用いられている。表示パネルの表示ムラを補正する表示ドライバには、入力された階調値とムラ補正データとから補正量を算出するするものがある。

10

## 【先行技術文献】

## 【特許文献】

## 【0003】

【文献】特開2016-085344号公報

## 【概要】

## 【0004】

一の観点では、表示ドライバは、ディスプレイ特性を保持したまま、第一の輝度値と第一の階調値とに対応する輝度を出力する第二の輝度値における第二の階調値を算出するルックアップテーブルと、前記第二の階調値と前記第二の輝度値における表示パネルの表示ムラの補正に用いられるムラ補正データとに基づき、ムラ補正量を算出する補正量演算回路と、前記ムラ補正量を用いて、入力画像データのムラ補正を行うムラ補正回路と、を備える。

20

## 【図面の簡単な説明】

## 【0005】

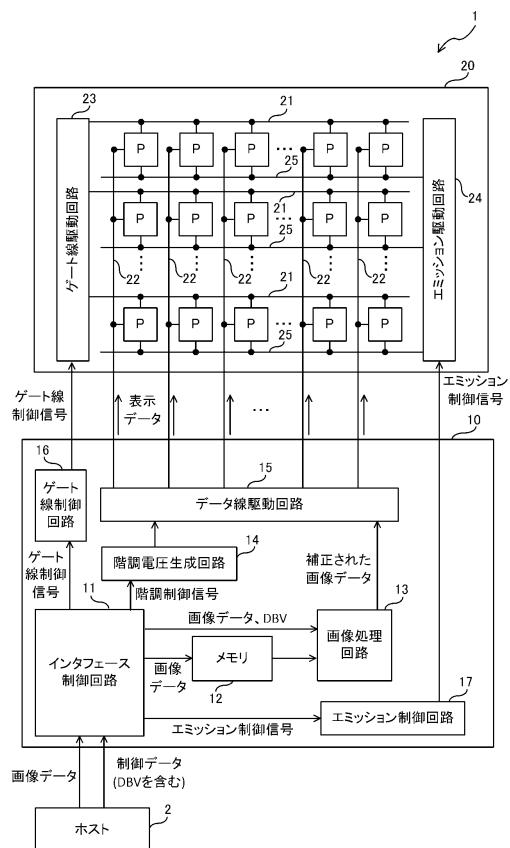

【図1A】実施形態における表示装置の構成の一例を示すブロック図である。

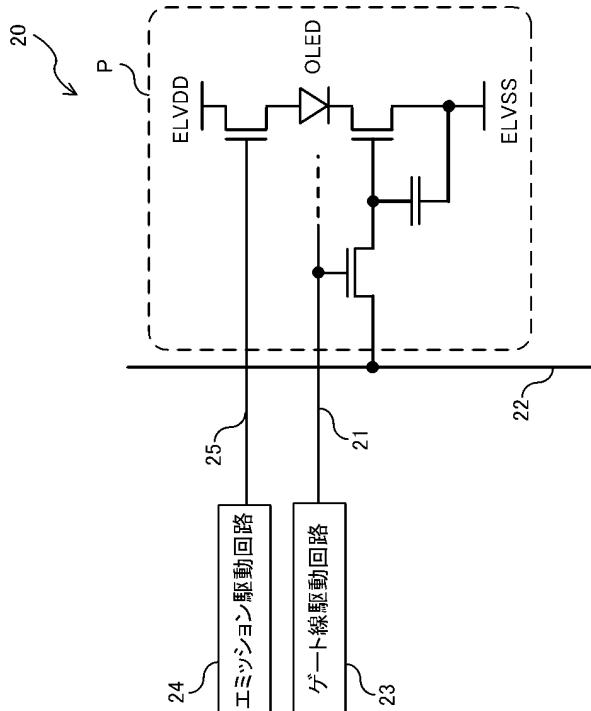

【図1B】実施形態における画素回路の構成の一例を示すブロック図である。

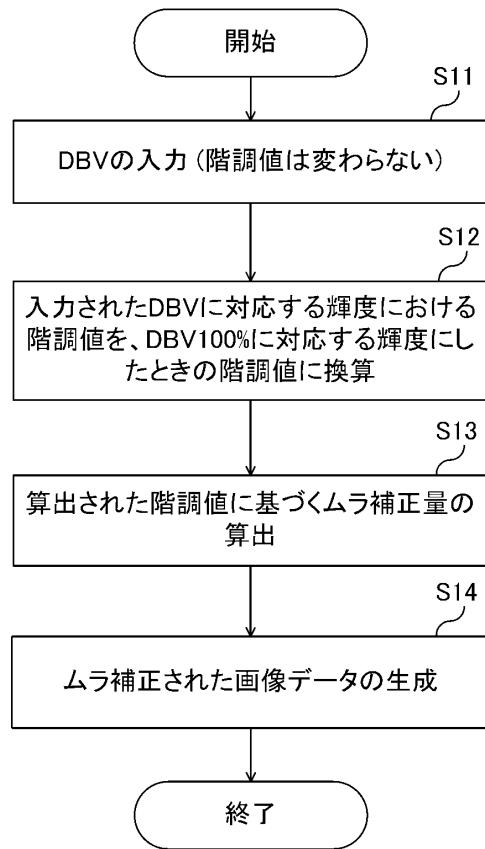

【図2】実施形態におけるムラ補正処理手順の一例を示す図である。

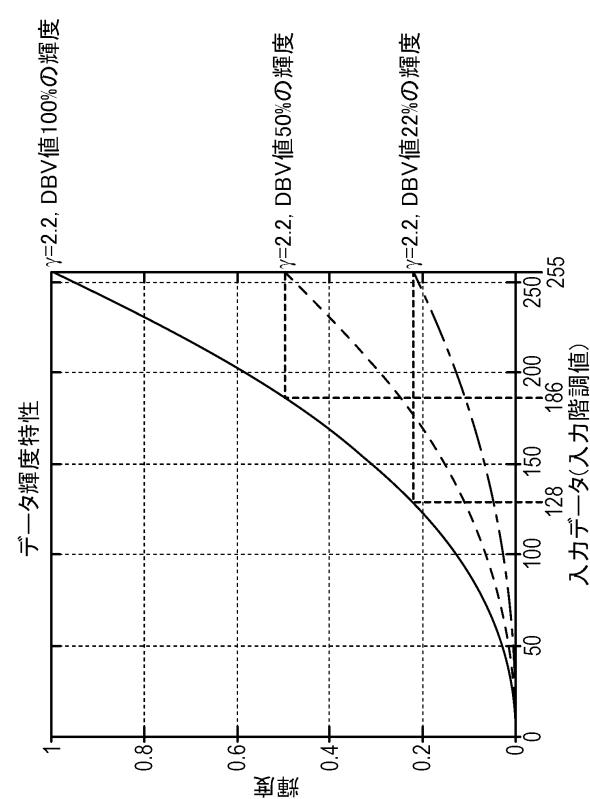

【図3】入力データと輝度との関係を表すデータ輝度特性の一例を示す図である。

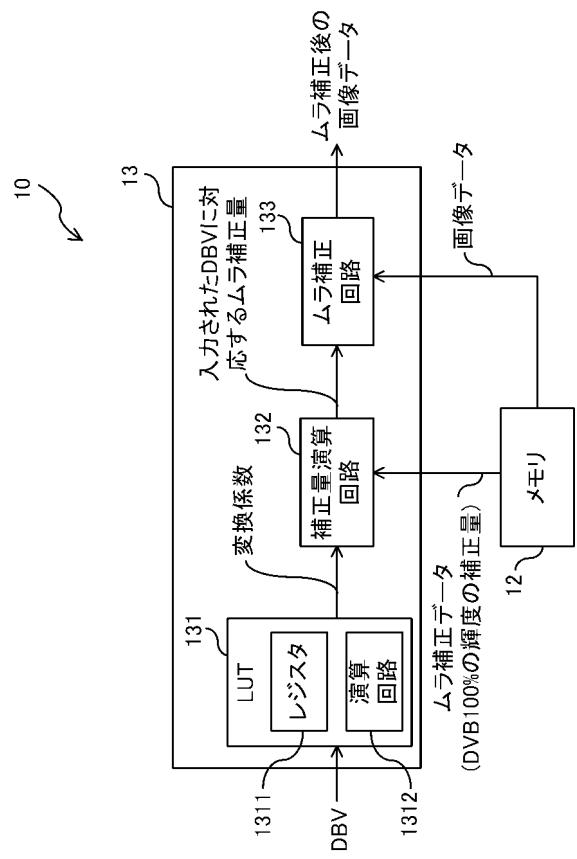

【図4】実施形態における画像処理回路の構成の一例を示すブロック図である。

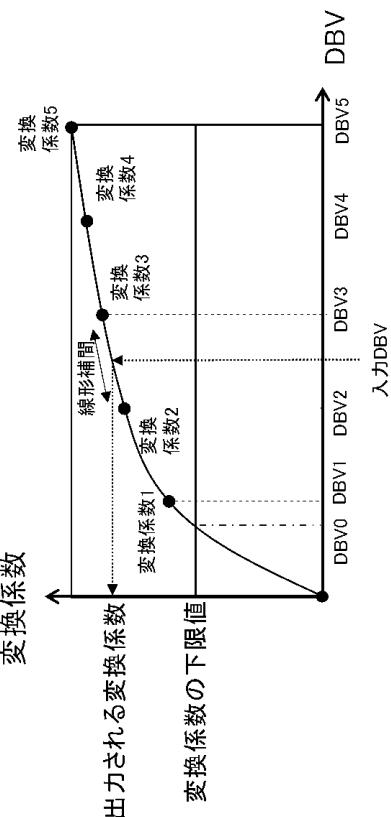

【図5】実施形態におけるLUTにおいて入力されるDBVと出力される変換係数との関係を示す図である。

30

## 【詳細な説明】

## 【0006】

以下、実施形態について、図面を参照して詳細に説明する。なお、ここに開示された技術がこれら実施形態の詳細説明がなくとも当業者により実施され得ることは明らかである。また、以下において、説明を不要に複雑にすることを避けるため、周知の特徴を詳細には説明していない。

## 【0007】

図1Aは、一実施形態における表示装置1の構成を示すブロック図である。表示装置1は、表示ドライバ10及び表示パネル20を備える。

40

## 【0008】

表示装置1は、ユーザに表示パネル20に表示される情報を提供する表示機能を有する。表示装置1は、表示パネルを備える電子機器の一例である。電子機器は、例えば、スマートフォン、ラップトップコンピュータ、ネットブックコンピュータ、タブレット、ウェブブラウザ、電子ブックリーダー、パーソナルデジタルアシスタント(PDA)といった携帯電子機器に限らない。例えば、電子機器は、表示パネルを備えるデスクトップコンピュータ又は表示パネルが用いられる自動車に搭載される表示機器等、あらゆるサイズ及び形状の機器であってもよい。また、タッチセンサを備え、指やスタイラス等の入力物体のタッチ検出が可能とされていてもよい。

50

## 【0009】

表示パネル20は、例えば、Organic Light Emitting Diode (OLED) 表示パネルや液晶表示パネルである。表示パネル20は、ゲート線21、データ線22、ゲート線駆動回路23、エミッショングループ駆動回路24、エミッショングループ25及び画素回路Pを備える。

## 【0010】

それぞれの画素回路Pは、図1Bに示すように、ゲート線21とデータ線22とが交差する位置に設けられており、赤、緑、青のいずれかの色を表示する。各画素回路Pは、エミッショングループ25に接続されている。赤を表示する画素回路Pは、Rサブピクセルとして用いられる。同様に、緑を表示する画素回路PはGサブピクセルとして用いられ、青を表示する画素回路PはBサブピクセルとして用いられる。

10

## 【0011】

表示パネル20がOLED表示パネルである場合、赤、緑、青を表示する画素回路Pはそれぞれ赤色、緑色、青色の光を発光する発光素子であるOLEDを備える。OLEDは、エミッショングループ24からのエミッショングループ信号に基づき、高電圧ELVDDと低電圧ELVSSとの電位差が生じ、ELVDDからOLEDに電流が流れることでOLEDが点灯する。

## 【0012】

図1Aに戻り、ゲート線駆動回路23は、表示ドライバ10から出力されるゲート線制御信号に応じてゲート線21を駆動する。

20

## 【0013】

エミッショングループ24は、表示ドライバ10から出力されるエミッショングループ信号に応じてエミッショングループ25を駆動する。

## 【0014】

表示ドライバ10は、ホスト2から入力された情報に基づき、表示パネル20を駆動して表示パネル20に表示データを出力する。

## 【0015】

表示ドライバ10は、インターフェース制御回路11、メモリ12、画像処理回路13、階調発生回路14、データ線駆動回路15、ゲート線制御回路16及びエミッショングループ回路17を備える。ホスト2は、例えば、アプリケーションプロセッサ、Central Processing Unit (CPU)、Digital Signal Processor (DSP) である。

30

## 【0016】

インターフェース制御回路11は、ホスト2から入力された画像データ及び制御データを各回路やメモリに出力する。

## 【0017】

画像データは、入力画像の各画素のサブピクセル毎の階調値を記述する。

## 【0018】

制御データは、表示ドライバ10を制御するためのコマンド及びパラメータを含み、例えば、輝度値であるDisplay Brightness Value (DBV) を含む。

40

DBVは、表示データの輝度を指定するパラメータであり、例えば16進数で“000”から“FFF”までの範囲内で指定される。DBVにおいて“FFF”は最も明るい状態である最大の輝度を示し、“000”は最も暗い状態である最小の輝度を示す。

## 【0019】

メモリ12は、インターフェース制御回路11から転送された画像データを格納し、例えば、Static Random Access Memory (SRAM) で構成される。

## 【0020】

画像処理回路13は、インターフェース制御回路11から受け付けた画像データに対して補正処理等の所望の画像データ処理を行い、補正された画像データをデータ線駆動回路15に出力する。実施形態における画像処理回路13の動作の詳細については後述する。

50

## 【0021】

階調電圧生成回路14は、画像データに記述されている階調値がとり得る値のそれぞれに対応する一組の階調電圧を生成する。

## 【0022】

データ線駆動回路15は、画像データの階調値に対応する階調電圧で各データ線22を駆動する。例えば、データ線駆動回路15は、階調電圧生成回路14から供給された階調電圧のうちから画像データの階調値に対応する階調電圧を選択し、その階調電圧になるよう各データ線22を駆動する。

## 【0023】

ゲート線制御回路16は、ゲート線制御回路23にゲート線制御信号を出力し、制御する。

10

## 【0024】

エミッショニン線制御回路17は、エミッショニン駆動回路24にエミッショニン制御信号を出力し、制御する。

## 【0025】

階調値に基づきムラ補正を行う場合、入力された階調値とムラ補正データとから補正量を計算し、補正後の階調値を出力する表示ドライバがある。このような表示ドライバにDBVが入力されると、DBVに応じて表示データの輝度は変化するが、階調値は変化しない。つまり、階調値が同じであってもDBVが異なると、発光素子に印加される電圧が異なる。したがって、ムラの量は、発光素子に印加される電圧に応じて変わる特性があるため、ムラ補正に用いられる補正量を変更する必要がある。

20

## 【0026】

以下、一実施形態におけるムラ補正処理方法を、図2を用いて説明する。

## 【0027】

図2に示すように、まず表示ドライバ10にDBVが入力される(ステップS11)。DBVが入力されても階調値は変わらない。

## 【0028】

ディスプレイ特性が保持されると、入力されたDBVと階調値とに対応する輝度を出力するDBV100%における階調値が算出される(ステップS12)。なお、例えば、液晶パネルやOLEDPパネル等の表示パネルでは、ガンマ値は2.2に設定される。

30

## 【0029】

図2のステップS12の演算について説明する。図3は、横軸が入力データ(入力階調値)、縦軸が輝度を表すデータ輝度特性を示すグラフの一例である。図3には、 $\gamma = 2.2$ であり、DBV100%、50%、22%に対応するデータ輝度特性のカーブが示されている。

## 【0030】

図3に示すように、輝度制御を電圧の調整により行う場合、DBV50%における255階調の輝度は、DBV100%における186階調の輝度に相当する。

## 【0031】

DBV100%における186階調は、次のように計算されてもよい。 $\gamma = 2.2$ 、DBV50%に対応する輝度は、 $0.5 * (\text{入力階調値})^{2.2} = (0.5^{1/2.2} * \text{入力階調値})^{2.2} = (186/255 * \text{入力階調値})^{2.2}$ として算出される。したがって、DBV50%における入力階調値に $186/255$ を乗算すれば、DBV50%と入力階調値とに対応する輝度を出力するDBV100%における階調値が算出される。

40

## 【0032】

同様に、DBV22%における255階調の輝度は、DBV100%における128階調の輝度に相当する。つまり、DBV22%における255階調とDBV100%における128階調とにおいて、発光素子に対して印加される電圧が同じであり、ムラ量も同じである。

## 【0033】

計算によれば、 $\gamma = 2.2$ 、DBV22%に対応する輝度は、 $0.22 * (\text{入力階調値})$

50

2 . 2 = ( 0 . 2 2 1 / 2 . 2 \* 入力階調値 ) 2 . 2 = ( 1 2 8 / 2 5 5 \* 入力階調値 )

2 . 2 として算出される。したがって、DBV22%における入力階調値に128/255を乗算すればDBV22%と入力階調値とに対応する輝度を出力するDBV100%における階調値が算出される。

【0034】

上述した例は、DBV50%における255階調とDBV100%における186階調との間及びDBV22%における255階調とDBV100%における128階調との間では、発光素子に対して印加される電圧が同じであり、ムラ量も同じであることを示している。すなわち、換算されたDBV100%における階調値に応じた補正量に基づき、入力画像に対してムラ補正を行えばよい。

10

【0035】

図2に戻り、ステップS12で算出された階調値とDBV100%の輝度におけるムラ補正データに基づき、ムラ補正量が算出され(ステップS13)、ムラ補正された画像データが生成される(ステップS14)。

【0036】

上述した一実施形態におけるムラ補正処理を実現する画像処理回路13の構成を説明する。

【0037】

図4は、一実施形態における画像処理回路13の構成を示すブロック図である。

20

【0038】

画像処理回路13は、Lookup Table (LUT)131、補正量演算回路132及びムラ補正回路133を備える。LUT131は、レジスタ1311及び演算回路1312を含む。なお、LUT131、補正量演算回路132及びムラ補正回路133は表示ドライバ10に含まれればよく、これらの回路の全て又は一部は画像処理回路13に含まれなくてもよい。

【0039】

LUT131は、入力されたDBVと階調値とに対応する輝度を出力するDBV100%における階調値を算出する。例えば、LUT131は、インターフェース制御回路11から入力されたDBVを、変換係数に変換する。変換係数は、所定の係数の一例である。実施形態における変換係数は、例えば、メモリ12に記憶されるDBV100%の輝度のムラ補正データに基づき算出されるムラ補正量を、換算されたDBV100%の輝度における階調値に対応する補正量に変換する係数である。

30

【0040】

図5は、LUT131において入力されるDBVと出力される変換係数との関係を示す図である。実施形態におけるLUT131のレジスタ1311は、所定数のDBVとそれに対応する変換係数とを記憶する。図5の例では、DBV1~5のそれぞれに対する変換係数1~5がレジスタ1311に記憶されている。LUT131にDBVが入力されると、演算回路1312は、レジスタ1311に記憶されている変換係数を用いて線形補間処理を行い、出力される変換係数を算出する。

40

【0041】

なお、変換係数は、図3を用いて説明したデータ輝度特性の関係式に、ガンマ値、入力階調値及びDBVを用いて、DBV100%における階調値を算出することにより算出してもよい。しかしながら、図4及び図5に示すLUT方式を用いることで、表示ドライバ10を、所定数のDBVの変換係数を保持するレジスタと、乗算器数個程度の小規模な回路とで実現できる。このような構成により、回路の簡略化及び必要なメモリ容量の削減を図れる。

【0042】

また、LUT設定はアナログの電圧コントロール設定に合わせて変更する必要がある。特にDBVが小さい場合、電圧の調整により階調制御を行うと階調潰れが発生するおそれがあるため、エミッションの調整だけで輝度制御を行う場合がある。この場合、DBVが変

50

わっても発光素子に印加される電圧は各階調で一定となり、ムラの量も変わらないため変換係数を一定にする必要がある。一実施形態では、図5に示すように、LUT131において、DBVが所定値であるDBV0以下の場合、変換係数が一定になるように、変換係数の下限が設定される。

【0043】

図4に戻り、LUT131は、算出した変換係数を、補正量演算回路132に出力する。

【0044】

補正量演算回路132は、メモリ12に格納されているDBV100%の輝度におけるムラ補正データと変換係数とに基づき、DBVの変化に応じたムラ補正量を算出する。補正量演算回路132は、ムラ補正量を用いて画像データにムラ補正を行い、ムラ補正画像データを生成する。

10

【0045】

以上では、限られた数の実施形態に関してのみ説明したが、本開示の利益を有する当業者は、本開示の範囲から逸脱することなく様々な他の実施形態及び変形例が考案され得ることを理解する。実施形態同士又はその変形例が組み合わせされてもよい。したがって、本明細書及び図面は、例示的開示に過ぎない。

【符号の説明】

【0046】

|         |                      |    |

|---------|----------------------|----|

| 1       | 表示装置                 | 20 |

| 1 0     | 表示ドライバ               |    |

| 1 1     | インターフェース制御回路         |    |

| 1 2     | メモリ                  |    |

| 1 3     | 画像処理回路               |    |

| 1 3 1   | LUT                  |    |

| 1 3 1 1 | レジスタ                 |    |

| 1 3 1 2 | 演算回路                 |    |

| 1 3 2   | 補正量演算回路              |    |

| 1 3 3   | ムラ補正回路               |    |

| 1 4     | 階調電圧生成回路             | 30 |

| 1 5     | データ線駆動回路             |    |

| 1 6     | ゲート線制御回路             |    |

| 1 7     | エミッショントransistor回路   |    |

| 2 0     | 表示パネル                |    |

| 2 1     | ゲート線                 |    |

| 2 2     | データ線                 |    |

| 2 3     | ゲート線駆動回路             |    |

| 2 4     | エミッショントransistor駆動回路 |    |

| 2 5     | エミッショントransistor線    |    |

| P       | 画素回路                 |    |

30

40

50

## 【図面】

## 【図 1 A】

## 【図 1 B】

10

20

30

40

## 【図 2】

## 【図 3】

50

【図4】

【図5】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

F I

G 0 9 G 3/20 6 2 3 R

H 0 5 B 33/14 A

H 0 1 L 27/32

東京都中野区中野4丁目10番2号 シナプティクス・ジャパン合同会社内

(72)発明者 土田 裕久

東京都中野区中野4丁目10番2号 シナプティクス・ジャパン合同会社内

(72)発明者 能勢 崇

東京都中野区中野4丁目10番2号 シナプティクス・ジャパン合同会社内

審査官 斎藤 厚志

(56)参考文献 特開2016-009136 (JP, A)

特開2011-227257 (JP, A)

特開2011-118361 (JP, A)

国際公開第2015/173948 (WO, A1)

特開2007-34209 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 0 9 G 3 / 3 2 3 3

G 0 9 G 3 / 3 2 9 1

G 0 9 G 3 / 2 0

H 0 1 L 5 1 / 5 0

H 0 1 L 2 7 / 3 2