(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7537882号**

**(P7537882)**

(45)発行日 令和6年8月21日(2024.8.21)

(24)登録日 令和6年8月13日(2024.8.13)

(51)国際特許分類

|         |                  |     |         |          |

|---------|------------------|-----|---------|----------|

| H 0 4 N | 25/76 (2023.01)  | F I | H 0 4 N | 25/76    |

| H 0 4 N | 25/703 (2023.01) |     | H 0 4 N | 25/703   |

| G 0 1 S | 17/32 (2020.01)  |     | G 0 1 S | 17/32    |

| H 0 1 L | 27/146 (2006.01) |     | H 0 1 L | 27/146 A |

| H 0 4 N | 25/704 (2023.01) |     | H 0 1 L | 27/146 D |

請求項の数 19 (全32頁) 最終頁に続く

(21)出願番号 特願2020-28265(P2020-28265)

(22)出願日 令和2年2月21日(2020.2.21)

(65)公開番号 特開2020-162114(P2020-162114

A)

(43)公開日 令和2年10月1日(2020.10.1)

審査請求日 令和5年2月16日(2023.2.16)

(31)優先権主張番号 10-2019-0034179

(32)優先日 平成31年3月26日(2019.3.26)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 1 2

9

1 2 9 , Samsung - ro , Yeo

n g t o n g - g u , Suw o n - s i

, Gyeonggi - do , Repub

lic of Korea

(74)代理人 110000051

弁理士法人共生国際特許事務所

金 大 允

大韓民国 京畿道 水原市 灵通区 三星路

1 2 9

最終頁に続く

(54)【発明の名称】 イメージング装置及びイメージセンサ

**(57)【特許請求の範囲】****【請求項1】**

光制御信号によって動作する光源と、

複数のピクセルを含み、前記複数のピクセルの各々が電荷に基づいて電気信号を生成するピクセル回路を含むピクセルアレイと、を備え、

前記複数のピクセルは、一般的のピクセル及び位相差検出ピクセルを含み、

前記一般的ピクセルの各々は、前記光源から出力されて被写体から反射された受信光信号に反応して第1電荷を生成するフォトダイオードを含み、

前記一般的ピクセルの各々のピクセル回路は、前記第1電荷に基づいて第1電気信号を生成し、

前記位相差検出ピクセルの各々は、前記位相差検出ピクセルの各々のピクセル回路に連結されてスイッチ制御信号によってオン／オフされるスイッチ素子、及び前記スイッチ素子に連結されて第2電荷を出力する電荷供給源を含み、

前記位相差検出ピクセルの各々のピクセル回路は、前記第2電荷に基づいて第2電気信号を生成することを特徴とするイメージング装置。

**【請求項2】**

前記ピクセル回路は、前記電荷の入力を受けるピクセルノードを含み、

前記一般的ピクセルにおいて前記フォトダイオードが前記ピクセルノードに連結され、前記位相差検出ピクセルにおいて前記スイッチ素子の一端が前記ピクセルノードに連結されることを特徴とする請求項1に記載のイメージング装置。

**【請求項 3】**

前記ピクセルアレイにおいて、

前記一般のピクセルは、ロー( r o w )方向、及び前記ロー方向に交差するカラム( c o l u m n )方向に沿ってアレイの形で配置され、

前記位相差検出ピクセルは、前記ロー方向に沿って配置されることを特徴とする請求項 1 に記載のイメージング装置。

**【請求項 4】**

前記位相差検出ピクセルは、前記カラム方向において第 1 位置に配置されることを特徴とする請求項 3 に記載のイメージング装置。

**【請求項 5】**

前記位相差検出ピクセルは、前記カラム方向において、第 1 位置、及び前記第 1 位置に隣接する第 2 位置に配置されることを特徴とする請求項 3 に記載のイメージング装置。

**【請求項 6】**

前記位相差検出ピクセルは、前記カラム方向において、第 1 位置、及び前記第 1 位置から分離された第 2 位置に配置されることを特徴とする請求項 3 に記載のイメージング装置。

**【請求項 7】**

前記ピクセルアレイにおいて、

前記一般のピクセルは、ロー( r o w )方向、及び前記ロー方向に交差するカラム( c o l u m n )方向に沿ってアレイの形で配置され、

前記位相差検出ピクセルは、互いに分離配置されて前記一般のピクセルのうちの一部によって囲まれることを特徴とする請求項 1 に記載のイメージング装置。

**【請求項 8】**

前記スイッチ制御信号は、前記光制御信号と同一であることを特徴とする請求項 1 に記載のイメージング装置。

**【請求項 9】**

前記ピクセル回路は、互いに同一の構造を有する第 1 ピクセル回路及び第 2 ピクセル回路を有し、

前記第 1 ピクセル回路は、第 1 フォト制御信号によって制御される第 1 フォトゲートを含み、

前記第 2 ピクセル回路は、前記第 1 フォト制御信号と 180 度の位相差を有する第 2 フォト制御信号によって制御される第 2 フォトゲートを含み、

前記第 1 フォトゲートがターンオンされると、前記電荷は、前記第 1 ピクセル回路に入力され、

前記第 2 フォトゲートがターンオンされると、前記電荷は、前記第 2 ピクセル回路に入力されることを特徴とする請求項 1 に記載のイメージング装置。

**【請求項 10】**

前記スイッチ制御信号は、前記第 1 フォト制御信号及び前記第 2 フォト制御信号のうちの 1 つと同一であることを特徴とする請求項 9 に記載のイメージング装置。

**【請求項 11】**

前記位相差検出ピクセルは、ロー方向に沿って配置され、

前記位相差検出ピクセルのうち、前記ロー方向に隣接する第 1 位相差検出ピクセル及び第 2 位相差検出ピクセルは、1 つのグループでグルーピングされることを特徴とする請求項 9 に記載のイメージング装置。

**【請求項 12】**

前記第 1 位相差検出ピクセルのスイッチ制御信号、及び前記第 2 位相差検出ピクセルのスイッチ制御信号は、前記第 1 位相差検出ピクセルの第 1 フォト制御信号及び第 2 フォト制御信号のうちの 1 つと同一であることを特徴とする請求項 11 に記載のイメージング装置。

**【請求項 13】**

前記位相差検出ピクセルのうちの一部は、前記ロー方向に交差するカラム方向において

10

20

30

40

50

第1位置に配置され、残りは前記カラム方向において前記第1位置に隣接する第2位置に配置され、

前記第1位置に配置された位相差検出ピクセルと前記第2位置に配置された位相差検出ピクセルとが互いに異なってグルーピングされることを特徴とする請求項11に記載のイメージング装置。

#### 【請求項14】

前記位相差検出ピクセルから獲得されたデータを用いることで前記第1フォト制御信号及び前記第2フォト制御信号の位相差エラーを補正するコントロールロジックを更に含むことを特徴とする請求項9に記載のイメージング装置。

#### 【請求項15】

前記コントロールロジックは、前記一般的ピクセルから獲得されたデータを用いることで前記一般的ピクセルの各々と前記被写体との間の距離情報を含むデプスマップ(depth map)を生成することを特徴とする請求項14に記載のイメージング装置。

#### 【請求項16】

前記光制御信号及び前記スイッチ制御信号は、PWM(Pulse Width Modulation)信号であることを特徴とする請求項1に記載のイメージング装置。

#### 【請求項17】

前記位相差検出ピクセルは、前記受信光信号を遮断する光遮断層を含むことを特徴とする請求項1に記載のイメージング装置。

#### 【請求項18】

複数のピクセルを含み、前記複数のピクセルのうちの少なくとも1つは、ピクセルノードに連結される第1フォトトランジスタを有する第1ピクセル回路、前記ピクセルノードに連結される第2フォトトランジスタを有する第2ピクセル回路、前記ピクセルノードに連結されるスイッチ素子、及び前記スイッチ素子に連結される電荷供給源を含み、前記第1フォトトランジスタは、第1フォトゲートを有し、前記第2フォトトランジスタは、第2フォトゲートを有するピクセルアレイと、

前記第1フォトゲートに第1フォト制御信号を入力し、前記第2フォトゲートに前記第1フォト制御信号と180度の位相差を有する第2フォト制御信号を入力し、前記スイッチ素子をターンオン及びターンオフさせて前記ピクセルノードに電荷を供給するコントローラと、を備えることを特徴とするイメージセンサ。

#### 【請求項19】

前記コントローラは、光信号を出力する光源を駆動するための光制御信号を生成し、前記光制御信号をスイッチ制御信号として前記スイッチ素子に入力することを特徴とする請求項18に記載のイメージセンサ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、イメージング装置及びイメージセンサに関する。

##### 【背景技術】

##### 【0002】

イメージセンサは、光を受け入れて電気信号を生成する半導体基板に形成されたセンサであって、複数のピクセルを有するピクセルアレイや、ピクセルアレイを駆動してイメージを生成するためのロジック回路などを含む。最近では、一般的のイメージセンサに加えて、特定の波長帯域の光信号を出力する光源をイメージセンサと結合させた形のイメージング装置に対する研究も活発に行われている傾向にある。

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

【文献】特開2017-011273号公報

##### 【発明の概要】

10

20

30

40

50

**【発明が解決しようとする課題】**

**【0004】**

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、受信光信号と出力光信号との位相差を用いてデプスマップ (depth map) を生成するイメージング装置及びイメージセンサを提供することにある。

**【課題を解決するための手段】**

**【0005】**

上記目的を達成するためになされた本発明の一態様によるイメージング装置は、光制御信号によって動作する光源と、複数のピクセルを含み、前記複数のピクセルの各々が電荷に基づいて電気信号を生成するピクセル回路を含むピクセルアレイと、を備え、前記複数のピクセルは、一般的のピクセル及び位相差検出ピクセルを含み、前記一般的のピクセルの各々は、前記光源から出力されて被写体から反射された受信光信号に反応して第1電荷を生成するフォトダイオードを含み、前記一般的のピクセルの各々のピクセル回路は、前記第1電荷に基づいて第1電気信号を生成し、前記位相差検出ピクセルの各々は、前記位相差検出ピクセルの各々のピクセル回路に連結されてスイッチ制御信号によってオン／オフされるスイッチ素子、及び前記スイッチ素子に連結されて第2電荷を出力する電荷供給源を含み、前記位相差検出ピクセルの各々のピクセル回路は、前記第2電荷に基づいて第2電気信号を生成することを特徴とする。

10

**【0006】**

上記目的を達成するためになされた本発明の一態様によるイメージセンサは、複数のピクセルを含み、前記複数のピクセルのうちの少なくとも1つは、ピクセルノードに連結される第1フォトトランジスタを有する第1ピクセル回路、前記ピクセルノードに連結される第2フォトトランジスタを有する第2ピクセル回路、前記ピクセルノードに連結されるスイッチ素子、及び前記スイッチ素子に連結される電荷供給源を含み、前記第1フォトトランジスタは、第1フォトゲートを有し、前記第2フォトトランジスタは、第2フォトゲートを有するピクセルアレイと、前記第1フォトゲートに第1フォト制御信号を入力し、前記第2フォトゲートに前記第1フォト制御信号と180度の位相差を有する第2フォト制御信号を入力し、前記スイッチ素子をターンオン及びターンオフさせて前記ピクセルノードに電荷を供給するコントローラと、を備えることを特徴とする。

20

**【0007】**

上記目的を達成するためになされた本発明の他の態様によるイメージセンサは、第1フォト制御ラインに沿って配置された第1ピクセル、及び第2フォト制御ラインに沿って配置された第2ピクセルを含み、電荷を生成するフォトダイオード、及び前記電荷を用いて前記第1ピクセル及び前記第2ピクセルの各々が電気信号を生成するピクセル回路を含むピクセルアレイと、第1クロック信号を出力する第1出力端、及び第2クロック信号を出力する第2出力端を有するクロックドライバと、第1フレーム周期の間に前記第2ピクセルを前記第2フォト制御ラインに連結し、第1フレーム周期の次の第2フレーム周期の間に前記第1出力を前記第2フォト制御ラインに連結し、前記第1フレーム周期及び前記第2フレーム周期で獲得されたデータに基づいて前記第1フォト制御ライン及び前記第2フォト制御ラインに入力されるクロック信号の位相を補正するコントローラと、を備えることを特徴とする。

30

**【発明の効果】**

**【0008】**

本発明のイメージング装置は、一般的のピクセル及び位相差検出ピクセルを含む複数のピクセルを有するピクセルアレイを含み、ピクセルの各々が所定のタイミングで動作して電荷から電気信号を生成するピクセル回路を含む。この構成により、ピクセル回路に入力されるクロック信号の位相差エラーを検出し、位相差エラーを補償することにより、イメージング装置の性能を改善することができる。

本発明の多様でありながらも有意義な利点及び効果は、上述した内容に限定されず、本発明の具体的な実施形態を説明する過程でより簡単に理解することができる。

40

50

**【図面の簡単な説明】****【0009】**

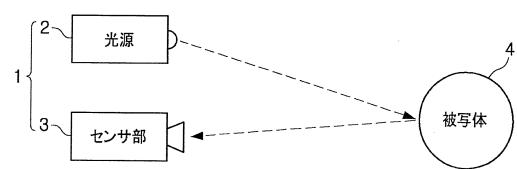

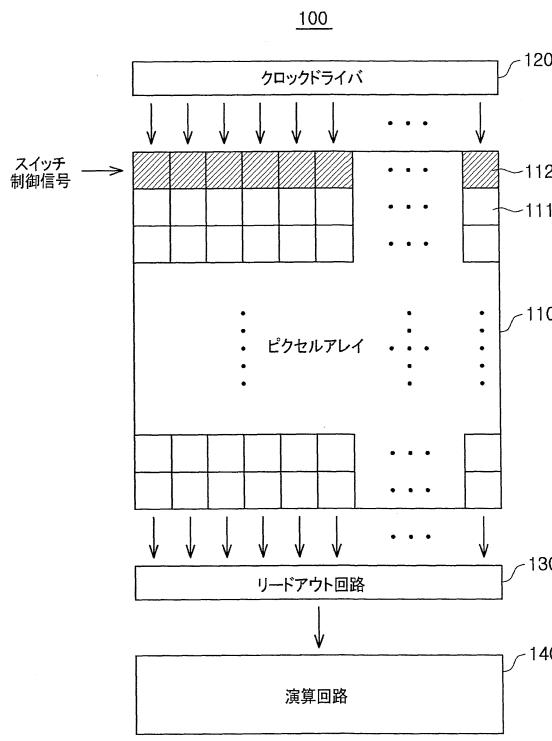

【図1】本発明の一実施形態によるイメージング装置を示す概略ブロック図である。

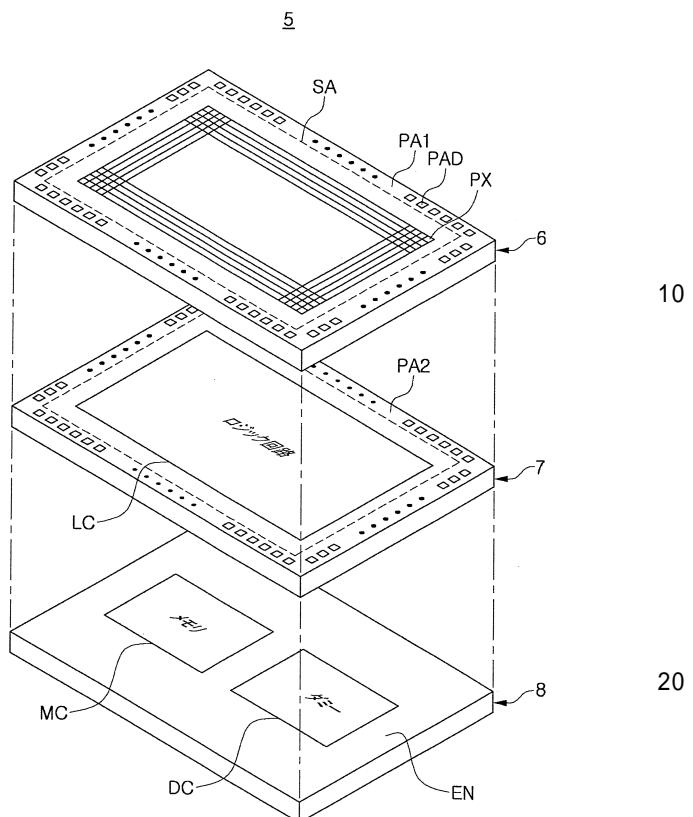

【図2a】本発明の一実施形態によるイメージセンサの一例を示す概略図である。

【図2b】本発明の一実施形態によるイメージセンサの他の例を示す概略図である。

【図3】本発明の一実施形態によるイメージング装置を示す概略ブロック図である。

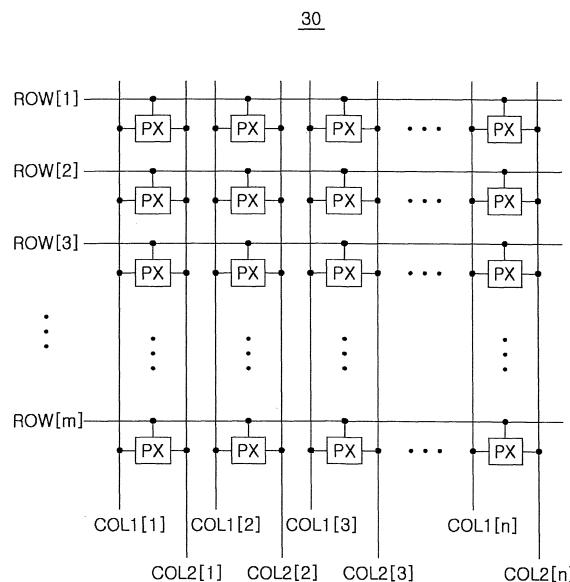

【図4】本発明の一実施形態によるイメージセンサのピクセルアレイを示す概略図である。

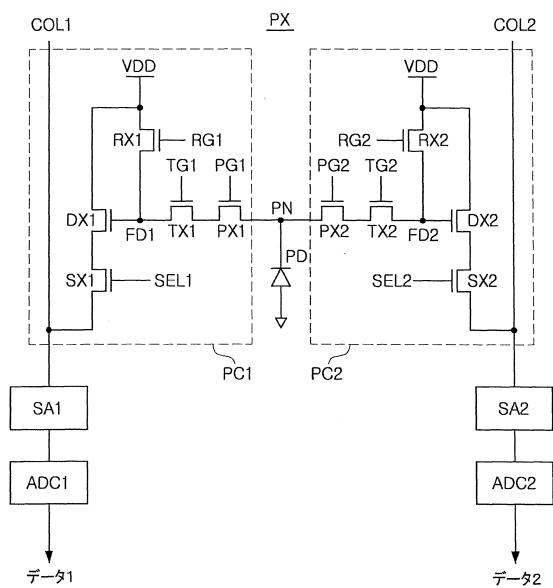

【図5】本発明の一実施形態によるイメージセンサに含まれる一般的ピクセルの一例を示す回路図である。

【図6】本発明の一実施形態によるイメージセンサに含まれる一般的ピクセルの他の例を示す回路図である。 10

【図7】本発明の一実施形態によるイメージセンサの動作を説明するために提供される図である。

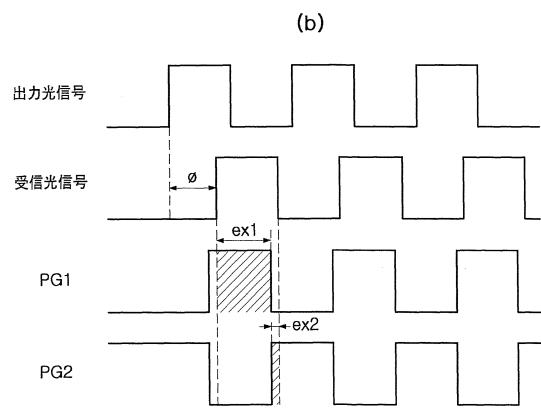

【図8】本発明の一実施形態によるイメージセンサの一例の動作を説明するために提供されるタイミング図である。

【図9】本発明の一実施形態によるイメージセンサの位相差エラーを有する場合の動作を説明するために提供されるタイミング図である。

【図10】本発明の一実施形態によるイメージセンサの他の例の動作を説明するために提供されるタイミング図である。

【図11】本発明の一実施形態によるイメージセンサの第1例を示す概略図である。

【図12】本発明の一実施形態によるイメージセンサに含まれる位相差検出ピクセルの一例を示す回路図である。

【図13】本発明の一実施形態によるイメージセンサに含まれる位相差検出ピクセルの他の例を示す回路図である。

【図14a】本発明の一実施形態によるイメージセンサに含まれる位相差検出ピクセルの一例の動作を説明するために提供されるタイミング図である。

【図14b】本発明の一実施形態によるイメージセンサに含まれる位相差検出ピクセルの位相差エラーを有する場合の動作を説明するために提供されるタイミング図である。

【図15a】本発明の一実施形態によるイメージセンサのピクセルの一例を示す概略図である。 30

【図15b】本発明の一実施形態によるイメージセンサのピクセルの他の例を示す概略図である。

【図16】本発明の一実施形態によるイメージセンサの第2例を示す概略図である。

【図17】本発明の一実施形態によるイメージセンサの第3例を示す概略図である。

【図18】本発明の一実施形態によるイメージセンサの第4例を示す概略図である。

【図19】本発明の一実施形態によるイメージセンサの第5例を示す概略図である。

【図20】本発明の一実施形態によるイメージセンサにおける位相差検出ピクセルのグループング方法の一例を説明するために提供される図である。

【図21】本発明の一実施形態によるイメージセンサにおける位相差検出ピクセルのグループング方法の他の例を説明するために提供される図である。 40

【図22】本発明の一実施形態によるイメージセンサにおける1つのグループに含まれる位相差検出ピクセルの動作を説明するために提供される図である。

【図23】本発明の一実施形態によるイメージセンサにおける1つのグループに含まれる位相差検出ピクセルの動作を説明するために提供されるタイミング図である。

【図24】本発明の一実施形態によるイメージセンサにおける一般的ピクセルを用いた位相差検出動作の第1フレーム周期を説明するために提供される図である。

【図25】本発明の一実施形態によるイメージセンサにおける一般的ピクセルを用いた位相差検出動作の第2フレーム周期を説明するために提供される図である。

【図26】本発明の一実施形態によるイメージセンサを含む電子機器を示す概略ブロック図である。 50

**【発明を実施するための形態】****【0010】**

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。

**【0011】**

図1は、本発明の一実施形態によるイメージング装置を示す概略プロック図である。

**【0012】**

先ず、図1を参照すると、本実施形態によるイメージング装置1は、光源2及びセンサ部3を含む。光源2は、特定の波長帯域の光信号を出力する発光素子を含む。一例として、光源2は、VCSEL(Vertical Cavity Surface Emitting Laser)又はLED(Light Emitting Diode)などを発光素子として含む。光源2は、アレイの形で配列された複数の発光素子を含むことができ、複数の発光素子が出力する光信号の進行経路上において光学素子が更に設けられ得る。光源2が出力する光信号は、赤外線波長帯域の光信号であり得る。

10

**【0013】**

光源2が出力する光信号は、被写体4によって反射され、センサ部3は、被写体4で反射された光信号を受信光信号として受ける。センサ部3は、受信光信号に応答して電気信号を生成するピクセルを有するピクセルアレイ、及びピクセルアレイで生成された電気信号を用いてイメージを生成するコントローラなどを含む。一例として、コントローラが生成するイメージは、被写体4及びその周辺環境の距離情報が含まれるデプスマップ( Depth Map)である。

20

**【0014】**

本実施形態において、センサ部3は、デプスマップを生成する機能に加えて、イメージング装置1に近接する被写体4の存在を感知する近接センシング機能、被写体4とイメージング装置1との間の距離を計算する距離測定機能などを提供する。センサ部3は、複数のピクセルを有するピクセルアレイや、ピクセルアレイを制御するコントローラなどを含むイメージセンサで実現される。光源2から出力されて被写体4から反射された受信光信号をセンサ部3が正確に検出するほど、上記の機能をより正確に実現することができる。

**【0015】**

一例として、複数のピクセルは、それぞれ、互いに位相差を有する複数のクロック信号で動作する。複数のピクセルに入力されるクロック信号の位相は、光源2に入力される光制御信号に基づいて決定される。複数のピクセルに入力されるクロック信号と光制御信号との間の位相差を正確に決定することにより、イメージング装置1の動作性能を改善することができる。

30

**【0016】**

例えば、複数のピクセルに入力されるクロック信号のうちの少なくとも1つは、光制御信号と同一の位相を有する。但し、実際には、いくつかの要因により、クロック信号と光制御信号との間に位相差が発生することがあり、位相差が原因となって同一の距離に位置する被写体4に対するセンサ部3が判断する距離情報がそれ異なる可能性がある。本実施形態では、複数のピクセルに入力されるクロック信号と光制御信号との間、又はクロック信号との間で発生する意図しない位相差を検出し且つ補償することにより、イメージング装置1の性能を改善することができる。

40

**【0017】**

図2a及び図2bは、本発明の一実施形態によるイメージセンサを示す概略図である。

**【0018】**

図2a及び図2bに示す実施形態によるイメージセンサ(5、5A)は、図1を参照して説明したイメージング装置1のセンサ部3として採用される。先ず、図2aを参照すると、本実施形態によるイメージセンサ5は、第1層6、第1層6の下部に設けられる第2層7、及び第2層7の下部に設けられる第3層8を含む。第1層6、第2層7、及び第3層8は、それぞれ垂直方向に積層される。一実施形態において、第1層6及び第2層7はウェハレベルで互いに積層され、第3層8はチップレベルで第2層7の下部に付着される

50

。第1層6～第3層8は、1つの半導体パッケージとして提供され得る。

#### 【0019】

第1層6は、複数のピクセルPXが設けられたセンシング領域SAと、センシング領域SAの周辺に設けられた第1パッド領域PA1と、を含む。第1パッド領域PA1には複数の上部パッドPADが含まれ、複数の上部パッドPADは、ビア(VIA、図示せず)などを介して、第2層7の第2パッド領域PA2に設けられたパッド及びロジック回路LCに連結され得る。

#### 【0020】

複数のピクセルPXは、それぞれ、光を受け入れて電荷を生成するフォトダイオードと、フォトダイオードで生成された電荷を処理するピクセル回路などと、を含む。ピクセル回路は、フォトダイオードで生成された電荷に対応する電圧を出力するための複数のトランジスタを含む。

10

#### 【0021】

第2層7は、ロジック回路LCを提供する複数の素子を含むことができる。ロジック回路LCに含まれる複数の素子は、第1層6に設けられたピクセル回路を駆動するための回路、例えばクロックドライバ、リードアウト回路、演算回路、タイミングコントローラなどを提供する。ロジック回路LCに含まれる複数の素子は、第1パッド領域PA1及び第2パッド領域PA2を介してピクセル回路に連結され得る。ロジック回路LCは、複数のピクセルPXからリセット電圧及びピクセル電圧を獲得して、ピクセル信号を生成する。

20

#### 【0022】

本実施形態において、複数のピクセルPXのうちの少なくとも1つは、同一のレベルに配置された複数のフォトダイオードを含む。複数のフォトダイオードのそれぞれの電荷から生成されたピクセル信号は、それぞれ位相差を有し、ロジック回路LCは、1つのピクセルPXに含まれる複数のフォトダイオードで生成されたピクセル信号の位相差に基づいて自動焦点機能を提供することができる。

#### 【0023】

第2層7の下部に設けられた第3層8は、メモリチップMC、ダミーチップDC、及びメモリチップMCとダミーチップDCとを密封する保護層ENを含む。メモリチップMCは、ダイナミックランダムアクセスメモリ(DRAM)又は静态ランダムアクセスメモリ(SRAM)であり、ダミーチップDCはデータを実際に記憶する機能は有しない。メモリチップMCは、バンプによって、第2層7のコントロールロジックLCに含まれる素子のうちの少なくとも1つに電気的に連結され、自動焦点機能を提供する上で必要な情報を記憶することができる。一実施形態において、バンプはマイクロバンプである。

30

#### 【0024】

次に、図2bを参照すると、本実施形態によるイメージセンサ5Aは、第1層6A及び第2層7Aを含む。第1層6Aは、複数のピクセルPXが設けられたセンシング領域SA、複数のピクセルPXを駆動するための素子が設けられたロジック回路LC、並びにセンシング領域SA及びロジック回路LCの周辺に設けられた第1パッド領域PA1を含む。第1パッド領域PA1には複数の上部パッドPADが含まれ、複数の上部パッドPADは、ビア(VIA、図示せず)などを介して、第2層7Aに設けられたメモリチップMCに連結され得る。第2層7Aは、メモリチップMC、ダミーチップDC、及びメモリチップMCとダミーチップDCとを密封する保護層ENを含む。

40

#### 【0025】

図3は、本発明の一実施形態によるイメージング装置を示す概略ブロック図である。

#### 【0026】

図3を参照すると、イメージング装置10は、コントローラ20、ピクセルアレイ30、光源ドライバ40、及び光源50などを含む。ピクセルアレイ30は、複数の行及び複数の列に沿ってアレイの形で配置される複数のピクセルPXを含む。複数のピクセルPXは、それぞれ、被写体60から入射する光信号に応答して電荷を生成するフォトダイオード、及びフォトダイオードで生成された電荷に対応する電気信号を生成するピクセル回路

50

などを含む。一例として、ピクセル回路は、フローティングディフュージョン、転送トランジスタ、リセットトランジスタ、駆動トランジスタ、及び選択トランジスタなどを含む。実施形態に応じて、ピクセルPXの構成は異なり得る。一例として、ピクセルPXは、それぞれ、シリコンフォトダイオードとは異なり、有機物質を含む有機フォトダイオードを含むか、又はデジタルピクセルで実現される。ピクセルPXがデジタルピクセルで実現される場合、ピクセルPXは、それぞれ、比較器、及び比較器の出力をデジタル信号に変換して送り出すカウンターなどを含む。

#### 【0027】

コントローラ20は、ピクセルアレイ30を制御するための複数の回路を含む。一例として、コントローラ20は、クロックドライバ21、リードアウト回路22、演算回路23、コントロールロジック24などを含む。クロックドライバ21は、ピクセルアレイ30を第1方向又は第2方向で駆動する。例えば、クロックドライバ21は、ピクセル回路の転送ゲートに入力される転送制御信号、リセットゲートに入力されるリセット制御信号、選択ゲートに入力される選択制御信号、及びフォトゲートに入力されるフォト制御信号などを生成する。第1方向及び第2方向は様々な方法で定義され、一例として、第1方向はロー(rown)方向に対応し、第2方向はカラム(column)方向に対応する。

10

#### 【0028】

リードアウト回路22は、相関二重サンプラー(Correlated Double Sampler: CDS)、及びアナログ-デジタルコンバータ(Analog-to-Digital Converter: ADC)などを含む。相関二重サンプラーは、クロックドライバ21から供給されるクロック信号によって選択されるピクセルPXにカラムラインを介して連結され、相関二重サンプリングを行ってリセット電圧及びピクセル電圧を検出する。アナログ-デジタルコンバータは、相関二重サンプラーから検出されたリセット電圧及びピクセル電圧をデジタル信号に変換して演算回路23に伝達する。

20

#### 【0029】

演算回路23は、デジタル信号を一時記憶するラッ奇又はバッファ回路及び增幅回路などを含み、リードアウト回路22から受信されたデジタル信号を処理する。クロックドライバ21、リードアウト回路22、及び演算回路23は、コントロールロジック24によって制御される。コントロールロジック24は、クロックドライバ21、リードアウト回路22、及び演算回路23の動作タイミングを制御するためのタイミングコントローラ、及びイメージデータを処理するためのイメージ信号プロセッサ(Image Signal Processor)などを含む。一実施形態において、演算回路23は、コントロールロジック24に含まれる。

30

#### 【0030】

コントロールロジック24は、リードアウト回路22及び演算回路23から出力されたデータを信号処理することでイメージデータを生成する。一例として、イメージデータはデブスマップを含む。また、コントロールロジック24は、イメージング装置10の動作モードに応じて、リードアウト回路22及び演算回路23から出力されたデータを用いることにより、被写体60とイメージング装置10との間の距離を計算し、またイメージング装置10に近接する被写体60を認識することができる。或いは、演算回路23がデブスマップを生成し、コントロールロジック24はデブスマップをイメージ処理してイメージ品質を改善することもできる。

40

#### 【0031】

イメージング装置10は、デブスマップを生成するために、被写体60に光信号を出力する光源50を含む。光源50は、少なくとも1つの発光素子を含み、一例として、複数の半導体発光素子がアレイの形で配列された半導体チップを含む。光源50は、光源ドライバ40によって動作する。光源ドライバ40は、コントローラ20によって制御される。

#### 【0032】

本実施形態において、光源ドライバ40は、パルス信号の特性を有する光制御信号を生成して光源50を駆動する。光源ドライバ40は、コントローラ20の制御命令に応答し

50

て PWM (Pulse Width Modulation) 信号で光制御信号を生成し、光制御信号の周波数、デューティ比、持続時間などを決定する。一例として、コントローラ 20 は、クロックドライバ 21 がピクセルアレイ 30 に入力するクロック信号のうちの少なくとも 1 つを、光源 50 に入力される光制御信号に同期化する。一実施形態において、光源 50 に入力される光制御信号に同期化する信号は、クロックドライバ 21 がピクセル PX のフォトゲートに入力するフォト制御信号である。

#### 【0033】

ピクセル PX は、クロックドライバ 21 に含まれる出力バッファからフォト制御信号の入力を受ける。一例として、1 つのローラインに連結されたピクセル PX、又は 1 つのカラムラインに連結されたピクセル PX は、同一のフォト制御信号の入力を受ける。理想的には、出力バッファが同時に送り出すフォト制御信号は互いに位相差を有しなくてもよいが、実際にはいくつかの要因によってフォト制御信号間に位相差エラーが発生する可能性がある。位相差エラーは、光制御信号とフォト制御信号との間にも発生することがある。

10

#### 【0034】

本発明の実施形態では、フォト制御信号間、又はフォト制御信号と光制御信号との間で意図せずに示される位相差エラーを検出して位相差エラーを補償する。従って、ピクセル PX が output するデータの精度を改善すると共にイメージング装置 10 の性能を改善することができる。

#### 【0035】

図 4 は、本発明の一実施形態によるイメージセンサのピクセルアレイを示す概略図である。

20

#### 【0036】

図 4 を参照すると、本実施形態によるピクセルアレイ 30 は、複数のピクセル PX を含み、複数のピクセル PX は、複数のローライン (ROW [1] - ROW [m]) と、複数のカラムライン (COL 1 [1] - COL 1 [n]、COL 2 [1] - COL 2 [n]) とが交差する地点に配置される。図 4 に示す実施形態において、複数のピクセル PX は、それぞれ、複数のローライン (ROW [1] - ROW [m]) のいずれかに連結される。また、複数のピクセル PX は、それぞれ、複数の第 1 カラムライン (COL 1 [1] - COL 1 [n]) のいずれかに連結され、複数の第 2 カラムライン (COL 2 [1] - COL 2 [n]) のいずれかに連結される。実施形態に応じて、複数のピクセル PX のそれに連結されるローライン (ROW [1] - ROW [m]) 及びカラムライン (COL [1] - COL [n]) の数は多様に変形することができる。また、複数のピクセル PX に連結されるローライン (ROW [1] - ROW [m])、及び複数のカラムライン (COL 1 [1] - COL 1 [n]、COL 2 [1] - COL 2 [n]) の延長方向が図 4 に示す様子と異なる場合もある。

30

#### 【0037】

複数のピクセル PX は、それぞれ、ピクセルアレイ 30 が受信する光信号に反応して電荷を生成するフォトダイオードと、フォトダイオードで生成された電荷を用いて電気信号を出力するピクセル回路と、を含む。ピクセル回路は、フォトダイオードで生成された電荷が移動するか否かを決定するフォトゲート、電荷を蓄積するフローティングディフュージョン、フローティングディフュージョンとフォトゲートとの間に連結された転送トランジスタ、フローティングディフュージョンをリセットするリセットトランジスタ、フローティングディフュージョンの電圧を増幅する駆動トランジスタ、及び駆動トランジスタとカラムライン (COL 1 [1] - COL 1 [n]、COL 2 [1] - COL 2 [n]) のいずれかと連結する選択トランジスタなどを含む。

40

#### 【0038】

光源から出力された光信号が被写体で反射されてピクセルアレイ 30 に入射すると、複数のピクセル PX のそれぞれのフォトダイオードは、入射した光信号に応答して電荷を生成する。光源から出力された光信号と、被写体から反射されてピクセルアレイ 30 に入射する受信光信号とは、所定の位相差を有する。一実施形態において、イメージング装置は

50

、位相差を用いることにより、イメージング装置と被写体との間の距離を判別し、また被写体に近接したことを感知することで、デプスマップを生成することができる。

#### 【0039】

イメージング装置は、1回のフレームの間に、複数のピクセルPXに連結された複数の第1カラムライン( COL1[1] - COL1[n] )、及び複数の第2カラムライン( COL2[1] - COL2[n] )を介して、それぞれ異なる積分時間( integration time )の間に生成された電荷に対応する電気信号を獲得することができる。一例として、イメージング装置は、180度の位相差を有する転送制御信号を用いて複数のピクセルPXのそれぞれに含まれる転送トランジスタをターンオン及びターンオフさせることにより、第1カラムライン( COL1[1] - COL1[n] )及び第2カラムライン( COL2[1] - COL2[n] )を介して電気信号を獲得する。

10

#### 【0040】

図5及び図6は、本発明の一実施形態によるイメージセンサに含まれる一般のピクセルを示す回路図である。

#### 【0041】

先ず、図5を参照すると、本実施形態によるイメージング装置のピクセルPXは、光信号に応答して電荷を生成するフォトダイオードPDと、フォトダイオードPDで生成された電荷に対応する電気信号を出力するピクセル回路( PC1、PC2 )と、を含む。ピクセル回路( PC1、PC2 )は、第1ピクセル回路PC1と、第2ピクセル回路PC2と、を含む。第1ピクセル回路PC1は第1カラムラインCOL1を介して第1サンプリング回路SA1及び第1アナログ-デジタルコンバータADC1に連結され、第2ピクセル回路PC2は第2カラムラインCOL2を介して第2サンプリング回路SA2及び第2アナログ-デジタルコンバータADC2に連結される。

20

#### 【0042】

第1ピクセル回路PC1は、フォトダイオードPDに連結された第1フォトトランジスタPX1、第1転送トランジスタTX1、フォトダイオードPDで生成された電荷を蓄積する第1フローティングディフュージョンFD1、及び複数の第1回路素子( RX1、DX1、SX1 )を含む。複数の第1回路素子( RX1、DX1、SX1 )は、第1リセットトランジスタRX1、第1駆動トランジスタDX1、及び第1選択トランジスタSX1などを含む。第2ピクセル回路PC2は、第1ピクセル回路PC1と同様の構造を有する。第1転送トランジスタTX1、第1リセットトランジスタRX1、及び第1選択トランジスタSX1を制御するための制御信号( TG1、RG1、SEL1 )は、イメージング装置のロードライバによって入力される。

30

#### 【0043】

第1リセットトランジスタRX1がターンオンされると、第1フローティングディフュージョンFD1の電圧が電源電圧VDDにリセットされ、第1選択トランジスタSX1がターンオンされて、第1サンプリング回路SA1が第1リセット電圧を検出する。第1リセットトランジスタRX1がターンオフされ、第1転送トランジスタTX1がターンオンされるまでの第1露出時間の間に、フォトダイオードPDは、光に露出して電荷を生成する。

40

#### 【0044】

第1転送トランジスタTX1がターンオンされると、フォトダイオードPDで生成され、第1フォトトランジスタPX1に蓄積された電荷が第1フローティングディフュージョンFD1に移動する。第1サンプリング回路SA1は、第1選択トランジスタSX1のターンオンに応答して第1ピクセル電圧を検出する。第1アナログ-デジタルコンバータは、第1リセット電圧と第1ピクセル電圧との差をデジタル形式の第1ロー( raw )データDATA1に変換する。

#### 【0045】

第2ピクセル回路PC2の動作は、第1ピクセル回路PC1の動作と同様である。但し、第2フォトトランジスタPX2は、第1フォトトランジスタPX1と同時にターンオン

50

されない。従って、第2ピクセル回路P C 2が第2カラムラインC O L 2を介して出力する第2ピクセル電圧は、第1露出時間と異なる第2露光時間の間にフォトダイオードP Dが光に露出して生成された電荷に対応する。第2アナログ・デジタルコンバータA D C 2は、第2リセット電圧と第2ピクセル電圧との差を第2ローデータD A T A 2に変換する。

#### 【0046】

本発明の一実施形態において、イメージング装置は、グローバルシャッター方式で動作する。一例として、イメージング装置に含まれるピクセルP Xのそれぞれに含まれる第1リセットトランジスタR X 1及び第2リセットトランジスタR X 2の両方がターンオンされてピクセルP Xが同時にリセットされた後、所定の露出時間の間にピクセルP Xに含まれるフォトダイオードP Dが光に露出して電荷を生成する。フォトダイオードP Dが光に露出する露出時間の長さは、イメージング装置の動作モードに応じて異なる。露光時間の間に、第1フォトトランジスタP X 1及び第2フォトトランジスタP X 2には互いに相補的な関係を有するクロック信号が入力され、フォトダイオードP Dで生成された電荷が第1フォトトランジスタP X 1及び第2フォトトランジスタP X 2のうちの少なくとも1つに記憶される。第1フォトトランジスタP X 1及び第2フォトトランジスタP X 2に入力されるクロック信号は、イメージング装置の光源に入力される光制御信号と同期化して制御される。

#### 【0047】

一例として、第1時間の間に、第1フォトトランジスタP X 1に入力される第1フォト制御信号P G 1は光制御信号と同一の位相を有し、第2フォトトランジスタP X 2に入力される第2フォト制御信号P G 2は光制御信号と180度の位相差を有する。また、第1時間の次の第2時間の間に、第1フォト制御信号P G 1は光制御信号と90度の位相差を有し、第2転送制御信号T G 2は光制御信号と270度の位相差を有する。イメージセンサは、第1時間の間に獲得された第1ローデータD A T A 1及び第2ローデータD A T A 2、並びに第2時間の間に獲得された第1ローデータD A T A 1及び第2ローデータD A T A 2を用いて被写体を認識し、また被写体までの距離を判断する。一例として、第1時間及び第2時間は、それぞれ、イメージセンサのフレーム周期である。

#### 【0048】

カラムライン(C O L 1、C O L 2)が延長されるカラム方向で互いに隣接するピクセルP Xは、第1フォト制御信号P G 1及び第2フォト制御信号P G 2を共有する。一実施形態において、カラム方向で互いに隣接するピクセルP Xのそれぞれに含まれる第1フォトトランジスタP X 1は、第1フォト制御ラインに連結されて同一の第1フォト制御信号P G 1の入力を受ける。同様に、カラム方向で互いに隣接するピクセルP Xのそれぞれに含まれる第2フォトトランジスタP X 2は、第2フォト制御ラインに連結されて同一の第2フォト制御信号P G 2の入力を受ける。一例として、第1フォト制御ライン及び第2フォト制御ラインは、カラム方向に延長されるラインである。

#### 【0049】

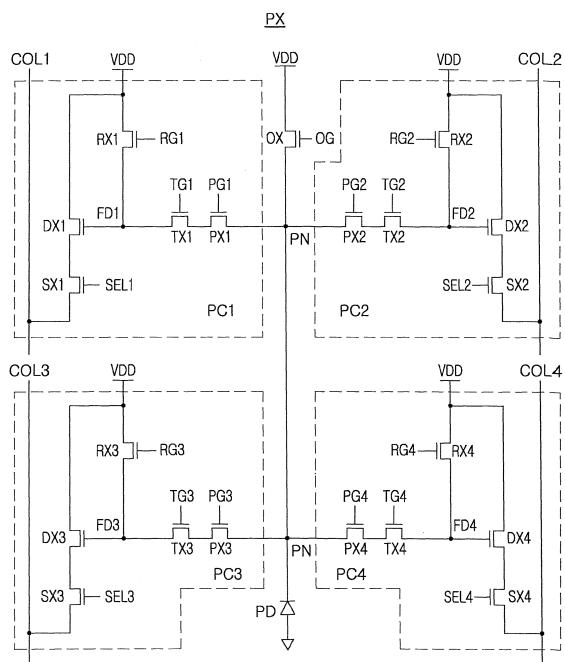

次に、図6を参照すると、本実施形態によるイメージセンサのピクセルP Xでは、1つのフォトダイオードP Dに複数のピクセル回路(P C 1、P C 2、P C 3、P C 4)が連結される。図6に示す実施形態において、フォトダイオードP Dに第1～第4ピクセル回路(P C 1、P C 2、P C 3、P C 4)が連結される様子を示したが、実施形態に応じて、上記個数は多様に変形することができる。第1～第4ピクセル回路(P C 1、P C 2、P C 3、P C 4)は、実質的にそれぞれ同一の構造を有する。

#### 【0050】

第1～第4ピクセル回路(P C 1、P C 2、P C 3、P C 4)の動作は、上記の図5を参照して説明した実施形態と同様である。フォトダイオードP Dが光に露出する間に、第1～第4ピクセル回路(P C 1、P C 2、P C 3、P C 4)に含まれる第1～第4フォトトランジスタ(P X 1、P X 2、P X 3、P X 4)は、それぞれ異なる位相で動作する。一例として、第1フォトトランジスタP X 1に入力される第1フォト制御信号P G 1と、第2フォトトランジスタP X 2に入力される第2フォト制御信号P G 2とは、180度の

10

20

30

40

50

位相差を有する。また、第3フォト制御信号PG3と第4フォト制御信号PG4も互いに180度の位相差を有し、第3フォト制御信号PG3は第1フォト制御信号PG1と90度の位相差を有する。一実施形態において、第1～第4フォト制御信号(PG1、PG2、PG3、PG4)は、光制御信号と同一の周期を有し、光制御信号よりも小さいデューティ比を有する。一例として、第1～第4フォト制御信号(PG1、PG2、PG3、PG4)のデューティ比は、光制御信号のデューティ比の1/2である。

#### 【0051】

イメージセンサは、上記のような位相差動作により、第1～第4フォトトランジスタ(PX1、PX2、PX3、PX4)に記憶された電荷から獲得されたピクセル電圧を用いてデブスマップを生成することができる。リードアウト動作では、第1カラムラインCOL1を介して第1フォトトランジスタPX1に記憶された電荷に対応する第1データが出力され、第2カラムラインCOL2を介して第2フォトトランジスタPX2に記憶された電荷に対応する第2データが出力される。また、第3カラムラインCOL3を介して第3フォトトランジスタPX3の電荷に対応する第3データが出力され、第4カラムラインCOL4を介して第4ストレージトランジスタPX4の電荷に対応する第4データが出力される。

10

#### 【0052】

一方、実施形態に応じて、第1ピクセル回路PC1と第3ピクセル回路PC3とが1つのカラムラインに連結され、第2ピクセル回路PC2と第4ピクセル回路PC4とが1つのカラムラインに連結され得る。また、上述した実施形態と同様に、ロー方向において同一の位置に配置されてカラム方向で隣接するピクセルPXは、第1～第4フォト制御信号(PG1、PG2、PG3、PG4)を互いに共有することができる。

20

#### 【0053】

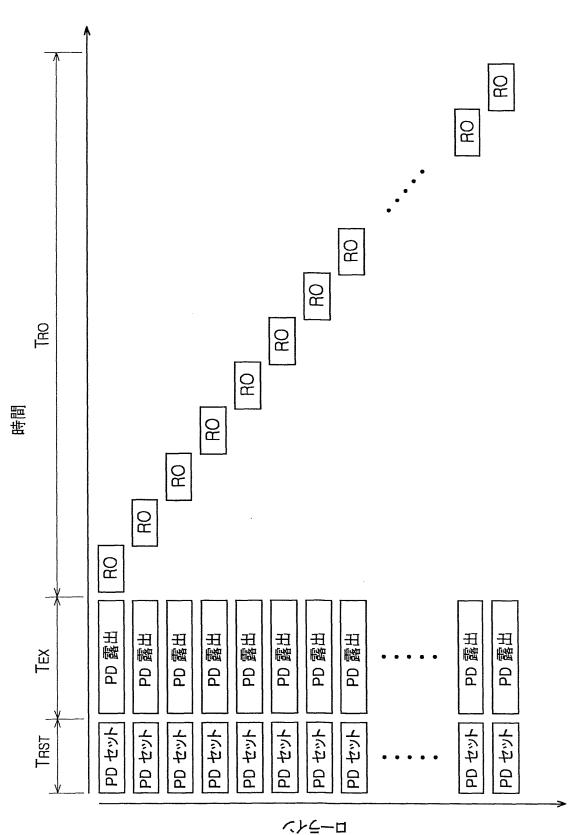

図7は、本発明の一実施形態によるイメージセンサの動作を説明するために提供される図である。

#### 【0054】

図7は、イメージセンサのグローバルシャッター動作を説明するために提供される図である。図7を参照すると、リセット時間TRSTの間に、ピクセルアレイに含まれる複数のピクセルのフォトダイオードが同時にリセットされる。一例として、クロックドライバは、ピクセル回路に含まれるリセットトランジスタをターンオンさせてフォトダイオードを所定の電源電圧に連結することにより、フォトダイオードをリセットする。

30

#### 【0055】

フォトダイオードがリセットされると、複数のピクセルに含まれるフォトダイオードが露出時間TEXの間に光に露出して電荷を生成する。一例として、露出時間TEXは、イメージセンサの動作環境、シャッタースピード、絞り値などによって決定される。

#### 【0056】

露出時間TEXが経過すると、クロックドライバが複数のピクセルに連結された複数のローラインをスキャンする。リードアウト回路は、クロックドライバが複数のローラインをスキャンする順序で複数のピクセルに対するリードアウト動作を行う。リードアウト回路は、リードアウト時間TROの間に、複数のピクセルのそれぞれからリセット電圧及びピクセル電圧を読み出す。

40

#### 【0057】

リードアウト回路がリードアウト時間TROの間にリセット電圧及びピクセル電圧を読み出すために、露出時間TEXの間にフォトダイオードで生成される電荷は、ピクセル回路のストレージ領域に記憶される。一例として、ストレージ領域は、ピクセル回路のフォトトランジスタである。ストレージ領域に記憶された電荷は、転送トランジスタのターンオンに応答して、ピクセル回路のフローティングディフュージョンに移動する。リードアウト回路は、転送トランジスタがターンオンされる前に、即ち電荷がストレージ領域に記憶されている間に、複数のピクセルのリセット電圧を読み出す。リードアウト回路は、クロックドライバによって転送トランジスタがターンオンされて、ストレージ領域の電荷が

50

フローティングディフュージョンに移動した後、複数のピクセルのピクセル電圧を読み出す。

**【 0 0 5 8 】**

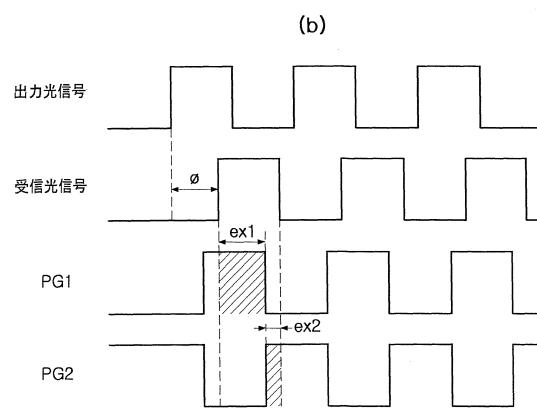

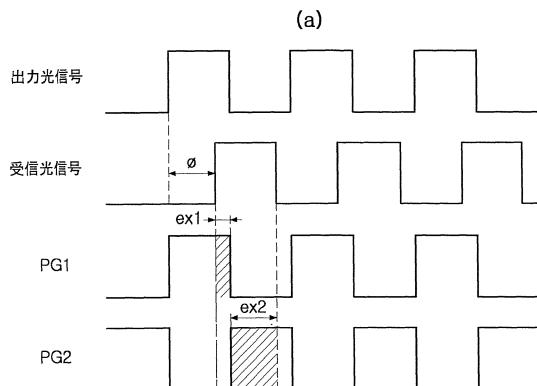

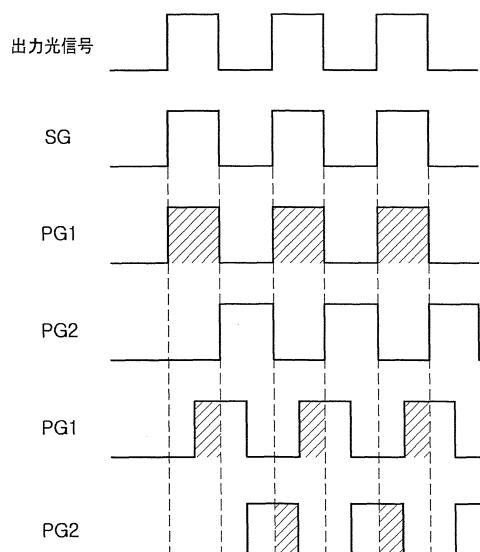

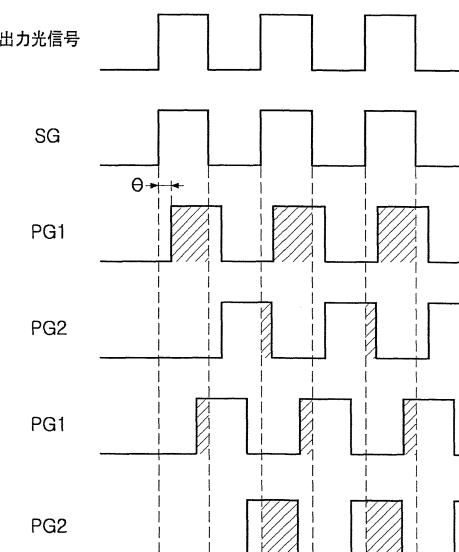

図 8 ~ 図 10 は、本発明の一実施形態によるイメージセンサの動作を説明するために提供されるタイミング図である。

**【 0 0 5 9 】**

図 8 ( a ) 及び ( b ) は、それぞれ、第 1 フレーム周期及び第 2 フレーム周期の間の、出力光信号及び受信光信号、並びに第 1 フォト制御信号 PG 1 及び第 2 フォト制御信号 PG 2 を示す図である。図 8 ( a ) 及び ( b ) に示す実施形態において、出力光信号は、 PWM 方式で動作する光源から出力される出力光信号であり、光源に入力される光制御信号と同一の周期及びデューティ比を有する信号である。図 8 ( a ) 及び ( b ) は、グローバルシャッター方式で動作するイメージング装置において、ピクセルが同時にリセットされた後、フォトダイオード PD が光に露出する露光時間の間にピクセルに入力される第 1 フォト制御信号 PG 1 及び第 2 フォト制御信号 PG 2 を示す図である。

10

**【 0 0 6 0 】**

図 8 ( a ) を参照すると、出力光信号と、被写体が出力光信号を反射させて生成された受信光信号とが所定の位相差 ( ) を有する。第 1 フレーム周期の間、第 1 フォト制御信号 PG 1 は出力光信号と 0 度の位相差を有し、第 2 転送制御信号 PG 2 は出力光信号と 180 度の位相差を有する。従って、フォトダイオード PD で第 1 露出時間  $e \times 1$  の間に生成された電荷が第 1 フォト制御信号 PG 1 によって制御される第 1 フォトトランジスタに蓄積され、フォトダイオード PD で第 2 露光時間  $e \times 2$  の間に生成された電荷は第 2 フォト制御信号 PG 2 によって制御される第 2 フォトトランジスタに蓄積される。

20

**【 0 0 6 1 】**

次に、図 8 ( b ) を参照すると、第 2 フレーム周期の間、第 1 フォト制御信号 PG 1 は出力光信号と 90 度の位相差を有し、第 2 フォト制御信号 PG 2 は出力光信号と 270 度の位相差を有する。従って、第 2 フレーム周期の間にフォトダイオード PD が光に露出する第 1 露出時間  $e \times 1$  及び第 2 露出時間  $e \times 2$  は、それぞれ、第 1 フレーム周期の間に第 1 露出時間  $e \times 1$  及び第 2 露出時間  $e \times 2$  のそれと異なる。第 2 フレーム周期の間、第 1 露出時間  $e \times 1$  は第 2 露出時間  $e \times 2$  よりも長い。

30

**【 0 0 6 2 】**

露出時間が終了すると、イメージング装置のコントローラは、ピクセルアレイに含まれるピクセルからピクセル電圧及びリセット電圧を読み出す。一例として、イメージング装置のコントローラは、ローリング方式により、ピクセルに連結された第 1 カラムライン及び第 2 カラムラインのそれからピクセル電圧及びリセット電圧を読み出し、その差を計算する。ピクセル電圧とリセット電圧との差はローデータとして用いられる。

**【 0 0 6 3 】**

イメージング装置のコントローラは、第 1 フレーム周期及び第 2 フレーム周期のそれにおいてピクセルに連結された第 1 カラムライン及び第 2 カラムラインを介して獲得されたローデータを用いることにより、ピクセルから被写体までの距離を判断することができる。また、イメージング装置のコントローラは、ピクセルのそれから被写体までの距離を用いることにより、デプスマップを生成することができる。一例として、第 1 フレーム周期の間に第 1 カラムライン及び第 2 カラムラインのそれを介して出力されるローデータを A 0 、 A 2 と定義し、第 2 フレーム周期の間に第 1 カラムライン及び第 2 カラムラインのそれを介して出力されるローデータを A 1 、 A 3 と定義する場合、ピクセルと被写体との間の距離 d は以下のように決定される。下記数学式 1 において、 c は光の速度、  $f_m$  は光源に入力される光制御信号の周波数である。

40

**【 数 1 】**

50

$$\phi = \arctan\left(\frac{A1 - A3}{A0 - A2}\right)$$

$$d = \frac{c}{2f_m} \frac{\phi}{2\pi}$$

#### 【 0 0 6 4 】

図9( a )及び( b )は、それぞれ、第1フレーム周期及び第2フレーム周期の間の、出力光信号及び受信光信号、並びに第1フォト制御信号PG1及び第2フォト制御信号PG2を示す図である。図8( a )及び( b )に示す実施形態とは異なり、図9( a )図9( b )に示す実施形態では、出力光信号と第1フォト制御信号PG1及び第2フォト制御信号PG2との間に位相差エラーが示される。一例として、図9( a )を参照すると、位相差エラーにより、第1フォト制御信号PG1と出力光信号との位相差が0度よりも大きく、第2フォト制御信号PG2と出力光信号の位相差が180度よりも大きい。従って、第1フレーム周期及び第2フレーム周期で示される第1露出時間e×1及び第2露出時間e×2も同様に、位相差エラーが存在しない場合とは異なる。

#### 【 0 0 6 5 】

位相差エラーにより、第1フレーム周期及び第2フレーム周期のそれぞれで示される第1露出時間e×1及び第2露出時間e×2が異なるため、ピクセルと被写体との間の距離も正確に測定できない場合がある。本発明の実施形態では、位相差エラーを検出すための位相差検出ピクセルをピクセルアレイに配置して位相差エラーを検出し、位相差エラーを補償するための補償データを生成する。或いは、位相差検出ピクセルを有することなく、ピクセルに入力される第1フォト制御信号PG1及び第2フォト制御信号PG2を2回のフレーム周期のそれぞれでシフトさせることにより、位相差エラーを検出す。

#### 【 0 0 6 6 】

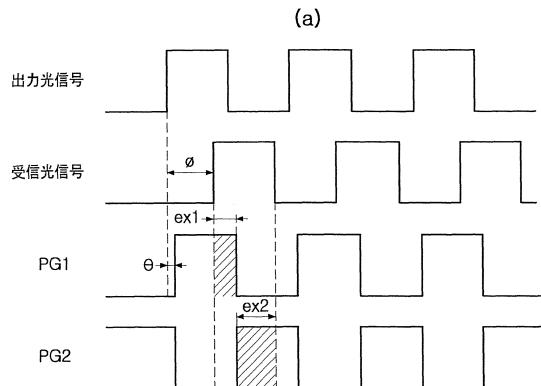

次に、図10( a )及び( b )は、1つのピクセルが4つのピクセル回路を含むイメージセンサにおける位相差エラーの有無によるタイミング図である。図10( a )は位相差エラーが存在しない場合に対応するタイミング図であり、図10( b )は位相差エラーが存在する場合に対応するタイミング図である。

#### 【 0 0 6 7 】

図10( a )及び( b )を参照すると、イメージセンサにおいて、1つのピクセルは4つのピクセル回路を含む。4つのピクセル回路に含まれる第1～第4フォトトランジスタは、第1～第4フォト制御信号(PG1～PG4)の入力を受ける。第1～第4フォト制御信号(PG1～PG4)は、それぞれ、出力光信号と所定の位相差を有し、出力光信号よりも小さいデューティ比を有する。第1フォト制御信号PG1は出力光信号と0度の位相差を有し、第2～第4フォト制御信号(PG2～PG4)は、それぞれ、第1フォト制御信号PG1と90度、180度、270度の位相差を有する。一例として、第1～第4フォト制御信号(PG1～PG4)のデューティ比は、出力光信号のデューティ比の1/2である。

#### 【 0 0 6 8 】

先ず、図10( a )を参照すると、第1フォト制御信号PG1のターンオン時間は、受信光信号がフォトダイオードに入る時間に重ならない。第2～第4フォト制御信号(PG2～PG4)のそれぞれのターンオン時間は、受信光信号がフォトダイオードに入る時間に第2～第4露出時間(e×2～e×4)のそれぞれの分だけ重なる。イメージセンサは、上記数学式1を参照して説明した方法により、ピクセルから被写体までの距離を測定することができる。従って、1回のフレーム周期の間に獲得されたデータによりピクセルから被写体までの距離を測定することができる。

10

20

30

40

50

**【 0 0 6 9 】**

図 10 ( b ) に示す実施形態では、位相差エラー が存在する。従って、第 1 ~ 第 4 フォト制御信号 ( P G 1 ~ P G 4 ) のターンオン時間に受信光信号が重なるか否かについては、図 10 ( a ) に示す実施形態とは異なる場合がある。一例として、図 10 ( b ) に示す実施形態では、位相差エラー により、第 2 フォト制御信号 P G 2 及び第 3 フォト制御信号 P G 3 のターンオン時間だけが、受信光信号がフォトダイオードに入る時間に重なる。位相差エラー により、イメージセンサが検出するピクセルと被写体との間の距離が変化することがあり、デブスマップにエラー が示される可能性がある。上述のように、本発明の実施形態では、位相差エラー を検出するための位相差検出ピクセルを用いるか、又はフォト制御信号 ( P G 1 ~ P G 4 ) を 2 回のフレーム周期のそれぞれからシフトさせてピクセルに入力することにより、位相差エラー を検出することもできる。

10

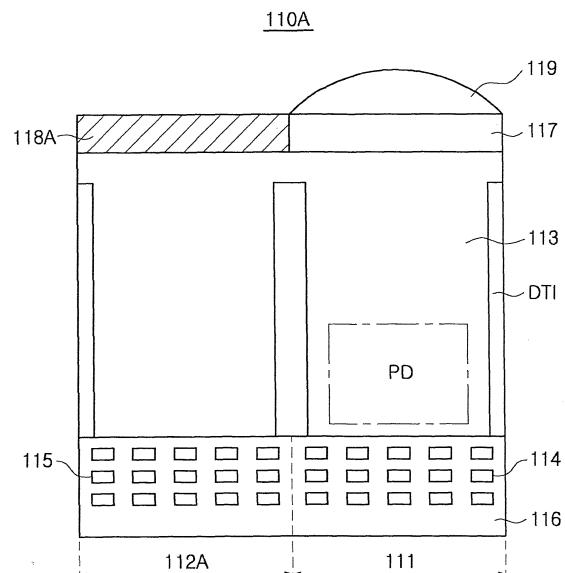

**【 0 0 7 0 】**

図 11 は、本発明の一実施形態によるイメージセンサを示す概略図である。図 12 及び図 13 は、本発明の一実施形態によるイメージセンサに含まれる位相差検出ピクセルを示す回路図である。

**【 0 0 7 1 】**

図 11 を参照すると、本発明の一実施形態によるイメージセンサ 100 は、ピクセルアレイ 110、クロックドライバ 120、リードアウト回路 130、及び演算回路 140 などを含む。ピクセルアレイ 110 は、ロー方向及びカラム方向に沿って配置された複数のピクセル ( 111、112 ) を含む。一例として、ピクセルアレイ 110 は、複数の一般的ピクセル 111 と、複数の位相差検出ピクセル 112 と、を含む。一般的ピクセル 111 は、ロー方向及びカラム方向に沿ってアレイの形で配置され、位相差検出ピクセル 112 は、ロー方向に沿って配置される。位相差検出ピクセル 112 の数及び配置形態は、実施形態に応じて多様に変更することができる。

20

**【 0 0 7 2 】**

例えば、クロックドライバ 120 は、複数のフォト制御ラインを介して複数のピクセルに連結される。複数のフォト制御ラインは、ピクセルのそれぞれにフォト制御信号を入力するラインである。リードアウト回路 130 は、ピクセルの選択トランジスタに連結された複数のカラムラインを介してピクセルに連結される。

30

**【 0 0 7 3 】**

一実施形態において、位相差検出ピクセル 112 は、一般的ピクセル 111 とは異なる構造を有する。以下、図 12 及び図 13 を参照して、位相差検出ピクセル 112 について説明する。

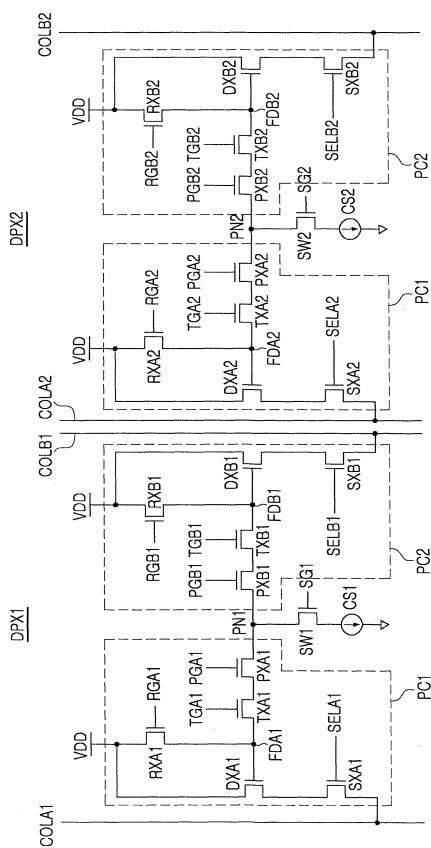

**【 0 0 7 4 】**

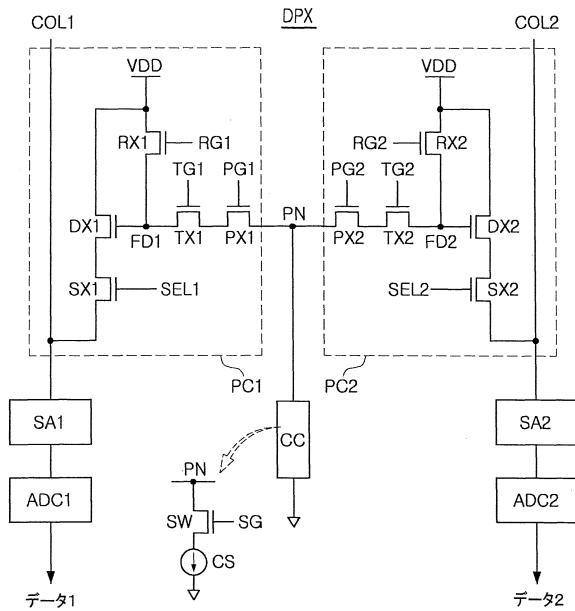

先ず、図 12 を参照すると、本発明実施形態によるイメージセンサに含まれる位相差検出ピクセル D P X は、第 1 ピクセル回路 P C 1、第 2 ピクセル回路 P C 2、及び電荷回路 C C などを含む。第 1 ピクセル回路 P C 1、第 2 ピクセル回路 P C 2、及び電荷回路 C C は、ピクセルノード P N に連結される。第 1 ピクセル回路 P C 1 及び第 2 ピクセル回路 P C 2 は、上記の図 5 を参照して説明した実施形態と類似する。即ち、位相差検出ピクセル D P X に含まれるピクセル回路は、一般的ピクセルに含まれるピクセル回路と同一の構造を有する。一例として、第 1 フォトトランジスタ P X 1 はクロックドライバに連結された第 1 フォト制御ラインを介して第 1 フォト制御信号 P G 1 の入力を受け、第 2 フォトトランジスタ P X 2 はクロックドライバに連結された第 2 フォト制御ラインを介して第 2 フォト制御信号 P G 2 の入力を受ける。

40

**【 0 0 7 5 】**

位相差検出ピクセル D P X は、ピクセルノード P N にフォトダイオードの代わりに電荷回路 C C が連結される。電荷回路 C C は、ピクセルノード P N に電荷を出力する。一例として、電荷回路 C C は、電荷を出力する電荷供給源 C S と、電荷供給源 C S とピクセルノード P N との間に連結されるスイッチ素子 S W と、を含む。スイッチ素子 S W は、スイッチ制御信号 S G によってターンオン / ターンオフされる。

50

**【 0 0 7 6 】**

次に、図13を参照すると、本実施形態によるイメージセンサに含まれる位相差検出ピクセルD P Xは、第1～第4ピクセル回路（P C 1～P C 4）及び電荷回路C Cなどを含む。第1～第4ピクセル回路（P C 1～P C 4）及び電荷回路C Cは、ピクセルノードP Nに連結される。第1～第4ピクセル回路（P C 1～P C 4）は、上記の図6を参照して説明した実施形態と類似する。位相差検出ピクセルD P Xのピクセル回路は、フォトダイオードを含む一般的なピクセルのピクセル回路と同一の構造を有する。

**【 0 0 7 7 】**

電荷回路C Cは、上記の図12を参照して説明したように、ピクセルノードP Nに電荷を供給する。電荷回路C Cは直列に連結されたスイッチ素子S Wと電荷供給源C Sとを含み、スイッチ素子S Wはスイッチ制御信号S Gによってターンオン／ターンオフされて電荷供給源C Sが出力する電荷をピクセルノードP Nに供給する。

10

**【 0 0 7 8 】**

図12及び図13に示す実施形態において、スイッチ素子S Wに入力されるスイッチ制御信号S Gは、イメージング装置の光源に入力される光制御信号と同一の信号である。以下、図14a及び図14bと共に参照して、位相差検出ピクセルD P Xの動作についてより詳細に説明する。

**【 0 0 7 9 】**

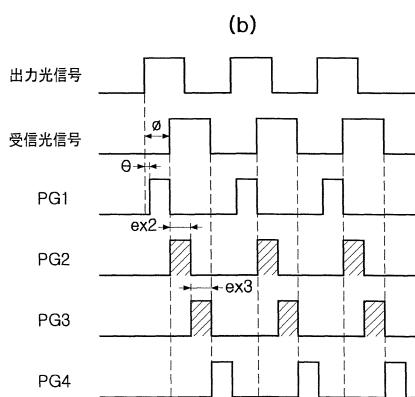

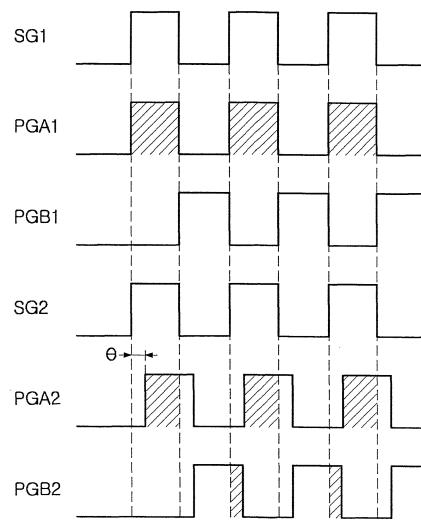

図14a及び図14bは、本発明の一実施形態によるイメージセンサに含まれる位相差検出ピクセルの動作を説明するために提供されるタイミング図である。

20

**【 0 0 8 0 】**

図14a及び図14bに示す実施形態において、出力光信号は、PWM方式で動作する光源が出力する光信号であり、光源に入力される光制御信号と同一の周期及びデューティ比を有する。スイッチ制御信号S Gは、光制御信号と同一の信号である。従って、出力光信号及びスイッチ制御信号S Gは同一の周期及びデューティ比を有し、出力光信号とスイッチ制御信号S Gとの間の位相差は0度である。

**【 0 0 8 1 】**

図14aを参照して説明する実施形態は、イメージング装置の光源に入力される光制御信号と、第1フォト制御信号P G 1及び第2フォト制御信号P G 2との間に意図しない位相差エラーが発生しない理想的な場合である。図14aを参照すると、第1フレーム周期の間、第1フォト制御信号P G 1は光制御信号との位相差が0度の信号であり、第2フォト制御信号P G 2は光制御信号との位相差が180度の信号である。従って、理想的な場合には、第1フレーム周期の間、電荷供給源C Sが出力する電荷は全て第1フォトトランジスタP X 1に記憶される。

30

**【 0 0 8 2 】**

一方、第1フレーム周期の次の第2フレーム周期において、第1フォト制御信号P G 1は光制御信号と90度の位相差を有し、第2フォト制御信号P G 2は光制御信号と270度の位相差を有する。従って、理想的な場合には、第2フレーム周期の間、電荷供給源C Sが出力する電荷は第1フォトトランジスタP X 1及び第2フォトトランジスタP X 2に1/2ずつ分けて記憶される。

40

**【 0 0 8 3 】**

一方、図14bを参照して説明する実施形態は、イメージング装置の光源に入力される光制御信号と、第1フォト制御信号P G 1及び第2フォト制御信号P G 2との間に意図しない位相差エラーが発生した場合に該当する。図14bを参照すると、第1フレーム周期の間、第1フォト制御信号P G 1と光制御信号との間に位相差エラーの分だけ位相差が発生する。位相差エラーにより、第2フォト制御信号P G 2と光制御信号との間の位相差は180度+である。従って、第1フレーム周期の間に電荷供給源C Sが出力する電荷は、第1フォトトランジスタP X 1と第2フォトトランジスタP X 2とに分けて記憶される。

**【 0 0 8 4 】**

50

第1フレーム周期の次の第2フレーム周期において、第1フォト制御信号PG1は光制御信号と90度+の位相差を有し、第2フォト制御信号PG2は光制御信号と270度+の位相差を有する。従って図14bに示す実施形態において、第2フレーム周期の間に電荷供給源CSが outputする電荷は、第1フォトトランジスタPX1よりも第2フォトトランジスタPX2に更に多く記憶される。

#### 【0085】

結果として、位相差エラーが発生した場合とそうでない場合とを比較すると、位相差検出ピクセルDPXから出力されるデータの間に差が生じる。本実施形態によるイメージング装置及びイメージセンサは、位相差検出ピクセルDPXのスイッチ素子SWに光制御信号をスイッチ制御信号SGとして入力し、位相差検出ピクセルDPXで獲得されたデータを用いることにより、位相差エラーの発生有無及びそのサイズなどを検出することができる。位相差エラーが検出されると、クロックドライバは、位相差エラーを相殺することができる補償値を、一般的のピクセルPXに入力される第1フォト制御信号PG1及び第2フォト制御信号PG2に反映する。従って、位相差エラーを除去することにより、イメージング装置及びイメージセンサの性能を改善することができる。

#### 【0086】

例えば、図14bに示す実施形態において、位相差エラーを検出するためのデータは、第1フレーム周期の間に第1フォト制御信号PG1のハッシュ領域のような第1波形領域に対応する第1データ、第1フレーム周期の間に第2フォト制御信号PG2のハッシュ領域のような第2波形領域に対応する第2データ、第2フレーム周期の間に第1フォト制御信号PG1のハッシュ領域のような第3波形領域に対応する第3データ、及び第2フレーム周期の間に第2フォト制御信号PG2のハッシュ領域のような第4波形領域に対応する第4データを含む。本実施形態において、コントローラは、第1フレーム周期の後に、図13に示す実施形態における第3ピクセル回路PC3から第1データを獲得し、第4ピクセル回路PC4から第2データを獲得する。また、第2フレーム周期の後に、第3ピクセル回路PC3から第3データを獲得し、第4ピクセル回路PC4から第4データを獲得する。その後、コントローラは、第4データと第3データとの差異値、及び第2データと予め定められた定数との合計から第1データを差分した値のうちの少なくとも1つに比例する位相差エラーを評価する。その後、コントローラは、位相差エラーに基づいて、第1フォト制御信号及び第2フォト制御信号のうちの少なくとも1つの位相を調整する。従って、位相差検出ピクセルから獲得された情報が、一般的のピクセルのクロックを改善するために用いられる。これは、イメージング装置を用いてデブスマップなどを生成する際の誤差を減らすことに寄与する。

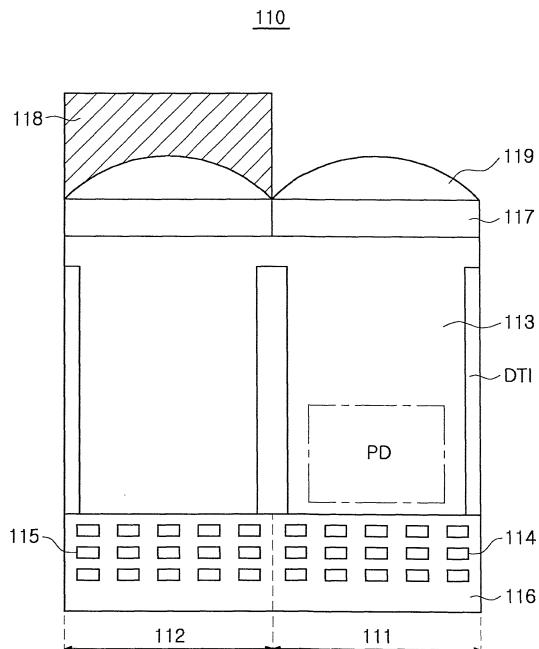

#### 【0087】

図15a及び図15bは、本発明の一実施形態によるイメージセンサのピクセルを示す概略図である。一例として、図15a及び図15bは、図11に示すイメージセンサ100のピクセルアレイ110のうちの一部を示す図である。

#### 【0088】

図15aに示す実施形態において、ピクセルアレイ110は、一般的ピクセル111と、位相差検出ピクセル112と、を含む。一般的ピクセル111及び位相差検出ピクセル112は、半導体基板113に形成され、ピクセル分離膜DTIによって互いに分離される。一般的ピクセル111及び位相差検出ピクセル112は、共通的に回路絶縁層116、光学絶縁層117、マイクロレンズ119などを含む。

#### 【0089】

図15aに示す実施形態では、位相差検出ピクセル112ではなく、一般的ピクセル111だけがフォトダイオードPDを含むものを示しているが、これとは異なり、位相差検出ピクセル112にもフォトダイオードPDが形成され得る。位相差検出ピクセル112は、光を透過させない不透明な物質で形成される光遮断層118を含む。光遮断層118は、位相差検出ピクセル112に入射する光信号を遮断する。

#### 【0090】

10

20

30

40

50

次に、図 15 b を参照すると、ピクセルアレイ 110 A の位相差検出ピクセル 112 A には、マイクロレンズ 119 及び光学絶縁層 117 が形成されない。ピクセルアレイ 110 A の製造工程では、半導体基板 113 にフォトダイオード PD 及びピクセル分離膜 DT I を形成し、ピクセル回路 (114、115) を形成した後、位相差検出ピクセル 112 A に対応する領域にのみ光遮断層 118 A を形成する。その後、一般的なピクセル 111 に対応する領域に光学絶縁層 117 及びマイクロレンズ 119 を形成する。実施形態に応じて、位相差検出ピクセル 112 A にフォトダイオード PD を形成することもできる。

#### 【0091】

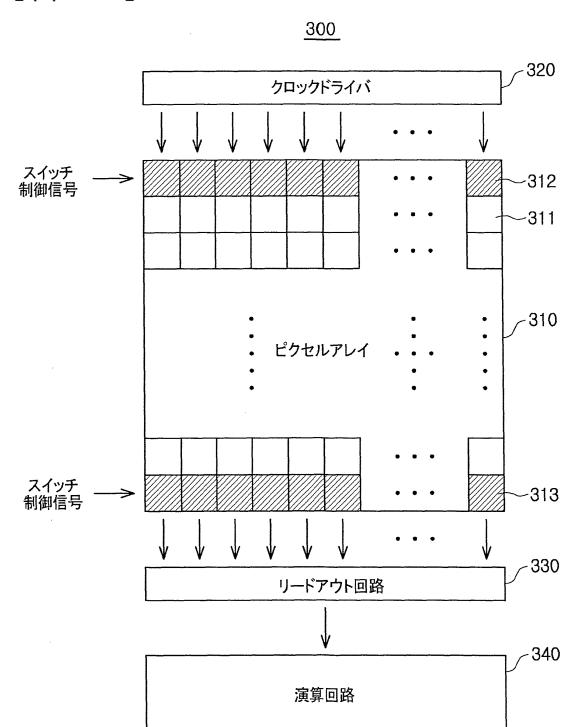

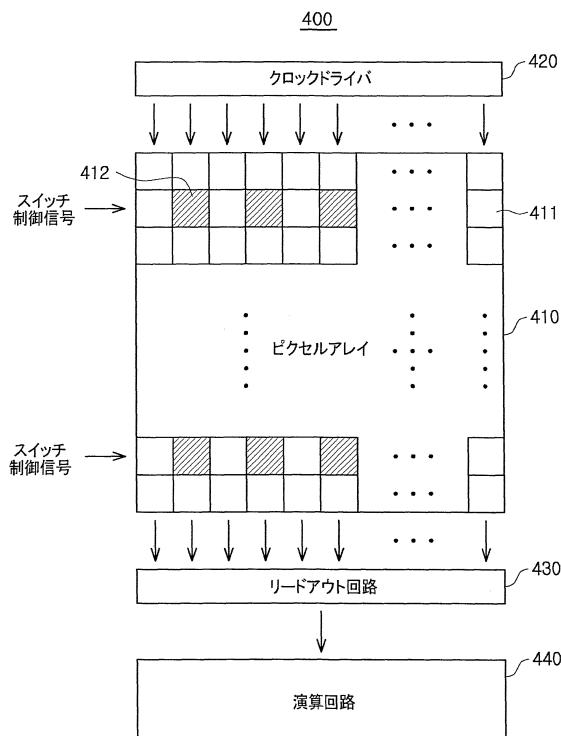

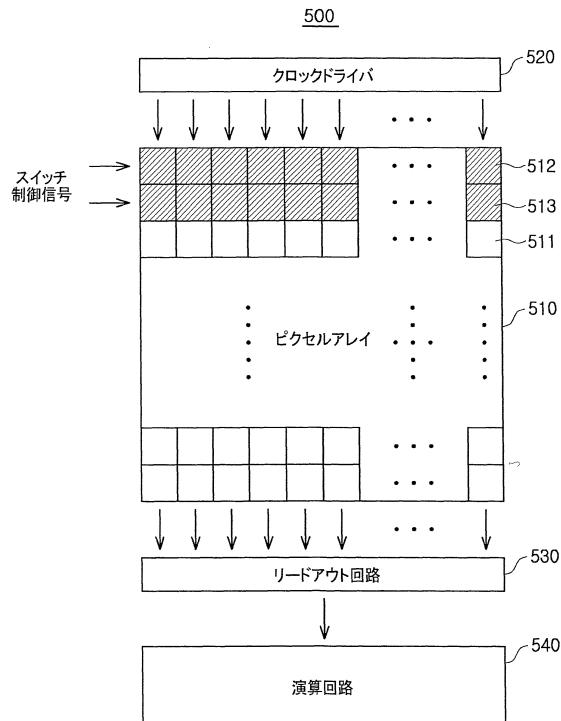

図 16 ~ 図 19 は、本発明の一実施形態によるイメージセンサの多様な例を示す概略図である。

10

#### 【0092】

先ず、図 16 を参照すると、本実施形態によるイメージセンサ 200 は、ピクセルアレイ 210、クロックドライバ 220、リードアウト回路 230、演算回路 240 などを含む。ピクセルアレイ 210 は、ロー方向及びカラム方向に沿って配置された複数のピクセル (211、212) を含む。一例として、ピクセルアレイ 210 は、複数の一般的なピクセル 211 と、複数の位相差検出ピクセル 212 と、を含む。一般的なピクセル 211 はロー方向及びカラム方向に沿ってアレイの形で配置され、位相差検出ピクセル 212 はロー方向に沿って配置される。図 16 に示す実施形態において、位相差検出ピクセル 212 は、ピクセルアレイ 210 において最下端のローラインに沿って配置される。

#### 【0093】

クロックドライバ 220、リードアウト回路 230、及び演算回路 240 の動作は、上記の図 11 を参照して説明した実施形態と同様である。一例として、クロックドライバ 220 は、フォト制御ラインを介してピクセル (211、212) のそれぞれにカラム方向にフォト制御信号を入力する。即ち、ロー方向に同一の位置でカラム方向に沿って配列されたピクセル (211、212) は、同一のフォト制御ラインに連結され、グローバルシャッター動作の露光時間の間に同一のフォト制御信号の入力を受ける。

20

#### 【0094】

次に、図 17 を参照すると、イメージセンサ 300 のピクセルアレイ 310 において、位相差検出ピクセル (312、313) が最上端のローライン及び最下端のローラインに沿って配置される。一般的なピクセル 311 は、カラム方向において位相差検出ピクセル (312、313) の間に配置される。クロックドライバ 320、リードアウト回路 330、演算回路 340 の動作は、上述の実施形態と同様である。

30

#### 【0095】

図 18 を参照すると、イメージセンサ 400 のピクセルアレイ 410 において、位相差検出ピクセル 412 は、一般的なピクセル 411 で囲まれ、互いに分離されて配置される。クロックドライバ 320、リードアウト回路 330、演算回路 340 の動作は、上述の実施形態と同様である。

#### 【0096】

図 18 に示す実施形態では、フォト制御ラインのうちの一部が位相差検出ピクセル 412 に連結されない。位相差検出ピクセル 412 に連結されないフォト制御ラインに入力されるフォト制御信号の位相差エラーを補償するために、補間方法を用いる。図 18 に示す実施形態では、位相差検出ピクセル 412 から偶数番目のフォト制御ラインに入力されたフォト制御信号の位相差エラーを獲得し、獲得された位相差エラーを用いることで、奇数番目のフォト制御ラインに入力されたフォト制御信号の位相差エラーを補間方法により推定する。

40

#### 【0097】

次に、図 19 を参照すると、イメージセンサ 500 のピクセルアレイ 510 において、位相差検出ピクセル (512、513) が最上端に位置する 2 つのローラインに沿って配列される。一般的なピクセル 511 は、カラム方向において位相差検出ピクセル (512、513) の下端に配置される。クロックドライバ 520、リードアウト回路 530、演算

50

回路 540 の動作は、上述の実施形態と同様である。

#### 【0098】

図 19 に示す実施形態において、位相差検出ピクセル (512, 513) に入力されるスイッチ制御信号は、イメージセンサ 500 及びイメージング装置を構成する光源に入力される光制御信号である。実施形態に応じて、スイッチ制御信号が光制御信号ではなく他の信号であってもよい。一例として、位相差検出ピクセル (512, 513) のそれぞれに入力されるスイッチ制御信号は、位相差検出ピクセル (512, 513) に入力されるフォト制御信号のうちの 1 つである。

#### 【0099】

位相差検出ピクセル (512, 513) に入力されるフォト制御信号のうちの 1 つをスイッチ制御信号として用いるために、ロー方向において互いに隣接する一対の位相差検出ピクセルは、1 つのグループにグルーピングされる。以下、図 20 ~ 図 23 を参照してより詳細に説明する。

10

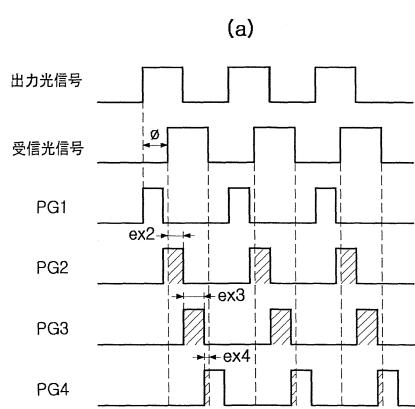

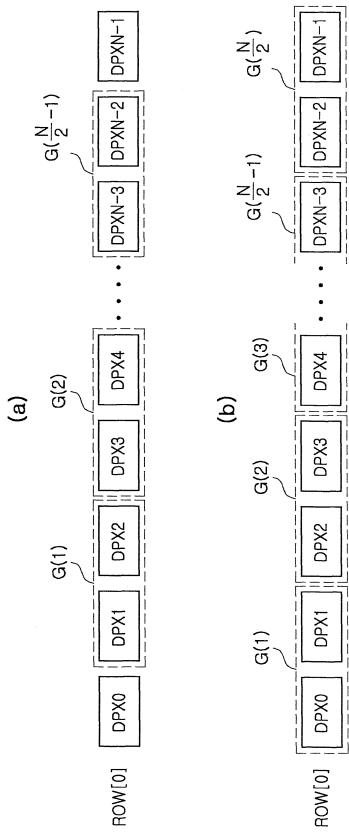

#### 【0100】

図 20 及び図 21 は、本発明の一実施形態によるイメージセンサにおける位相差検出ピクセルのグルーピング方法を説明するために提供される図である。一方、図 22 及び図 23 は、本発明の一実施形態によるイメージセンサにおける 1 つのグループに含まれる位相差検出ピクセルの動作を説明するために提供される図である。

10

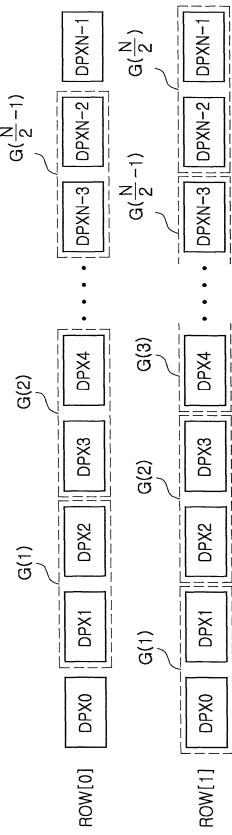

#### 【0101】

図 20 は、イメージセンサにおいて、位相差検出ピクセルが少なくとも 1 つのローラインに沿って連続的に配置される一実施形態におけるグルーピング方法を説明するための図である。図 20 (a) は第 1 フレーム周期の間ににおけるグルーピング方法を、図 20 (b) は第 2 フレーム周期の間ににおけるグルーピング方法に対応する図である。

20

#### 【0102】

先ず、図 20 (a) を参照すると、最初の位相差検出ピクセル (D P X 0) 及び最後の位相差検出ピクセル (D P X N - 1) を除いた残りの位相差検出ピクセルがグルーピングされる。ロー方向に隣接する一対の位相差検出ピクセルが 1 つのグループに結ばれ、位相差検出ピクセルの数が N 個である場合、第 1 フレーム周期の間ににおけるグループの数は (N / 2 - 1) 個である。

30

#### 【0103】

次に、図 20 (b) を参照すると、第 2 フレーム周期の間に、全ての位相差検出ピクセルがグルーピングされ。従って、位相差検出ピクセルの数が N 個である場合、第 2 フレーム周期の間ににおけるグループの数は N / 2 個である。図 20 に示す実施形態によるイメージセンサは、2 回のフレーム周期の間に位相差エラーを検出し、位相差エラーを補償するための補償データを生成する。

30

#### 【0104】

図 21 は、イメージセンサにおいて、位相差検出ピクセルが 2 つ以上のローラインに沿って連続的に配置される一実施形態におけるグルーピング方法を示す図である。図 20 を参照すると、1 番目のローライン (ROW [0]) に含まれる位相差検出ピクセルと、2 番目のローライン (ROW [1]) に含まれる位相差検出ピクセルとが互いに異なってグルーピングされる。従って、図 21 に示す実施形態によるイメージセンサは、図 20 に示す実施形態とは異なり、1 回のフレーム周期だけで位相差エラーを検出し、位相差エラーを補償するための補償データを生成することができる。

40

#### 【0105】

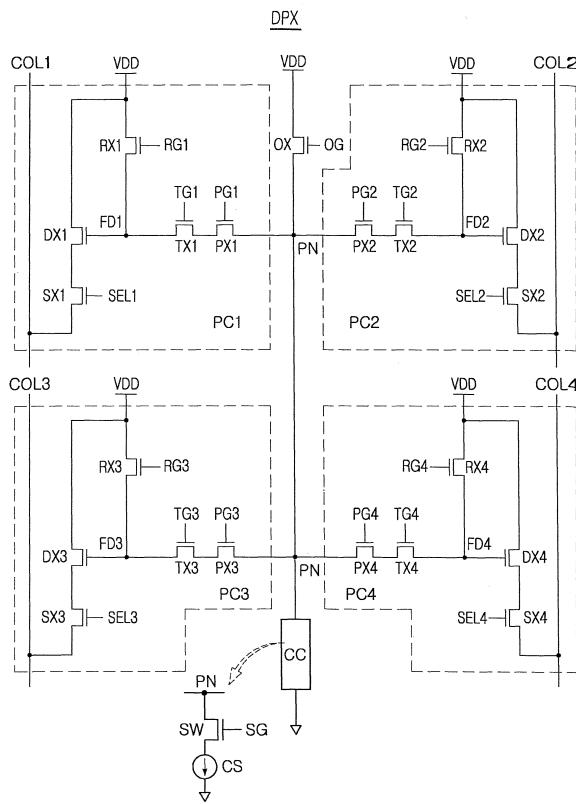

図 22 は、1 つのグループに含まれる第 1 位相差検出ピクセル D P X 1 及び第 2 位相差検出ピクセル D P X 2 を示す回路図であり、図 23 は、第 1 位相差検出ピクセル D P X 1 及び第 2 位相差検出ピクセル D P X 2 の動作を説明するためのタイミング図である。図 22 及び図 23 に示す実施形態において、第 1 位相差検出ピクセル D P X 1 及び第 2 位相差検出ピクセル D P X 2 のそれぞれの第 1 フォト制御信号 P G A 1 及び第 2 フォト制御信号 P G A 2 は互いに 180 度の位相差を有する。

50

**【 0 1 0 6 】**

第1位相差検出ピクセルD P X 1のスイッチ素子S W 1、及び第2位相差検出ピクセルD P X 2のスイッチ素子S W 2は、第1位相差検出ピクセルD P X 1の第1フォト制御信号P G A 1をスイッチ制御信号(S G 1、S G 2)として受ける。図23に示すように、第1位相差検出ピクセルD P X 1に入力されるフォト制御信号(P G A 1、P G B 1)と、第2位相差検出ピクセルD P X 2に入力されるフォト制御信号(P G A 2、P G B 2)との間に位相差エラーが存在する場合、第1位相差検出ピクセルD P X 1及び第2位相差検出ピクセルD P X 2のそれぞれで獲得されるデータが互いに異なる。

**【 0 1 0 7 】**

従って、第1位相差検出ピクセルD P X 1に入力されるフォト制御信号(P G A 1、P G B 1)のうちの1つを第1位相差検出ピクセルD P X 1及び第2位相差検出ピクセルD P X 2にスイッチ制御信号(S G 1、S G 2)として入力することにより、位相差エラーを検出する。位相差エラーは、第1位相差検出ピクセルD P X 1に連結されたフォト制御ラインと、第2位相差検出ピクセルD P X 2に連結されたフォト制御ラインとの間のエラーである。

**【 0 1 0 8 】**

再び図20を参照すると、イメージセンサにおいて位相差検出ピクセルが1つのローライン(ROW[0])に沿って配列される場合には、互いに隣接するカラムライン間の位相差エラーを検出するために、2回のフレーム周期が必要となる。2回のフレーム周期のそれぞれにおいて、位相差検出ピクセルは、互いに異なる方法でグルーピングされる。一方、図21のように、位相差検出ピクセルが2つのローライン(ROW[0]、ROW[1])に沿って配列されると、2つのローライン(ROW[0]、ROW[1])のそれぞれで位相差検出ピクセルを互いに異ならせてグルーピングすることにより、1回のフレーム周期だけで互いに隣接するフォト制御ライン間の位相差エラーを検出することができる。互いに隣接するフォト制御ライン間の位相差エラーを検出する場合、フォト制御ラインのうちの1つを基準ラインとして選択し、基準ラインを基準に各フォト制御ラインに対する位相差エラーの累積値を演算することにより、位相差エラーを補正するのに必要な補償データを計算することができる。一例として、補償データは、イメージセンサの演算回路やコントロールロジックなどにより計算する。コントロールロジックは、補償データに基づいて、クロックドライバが各フォト制御ラインに入力するフォト制御信号を決定する。

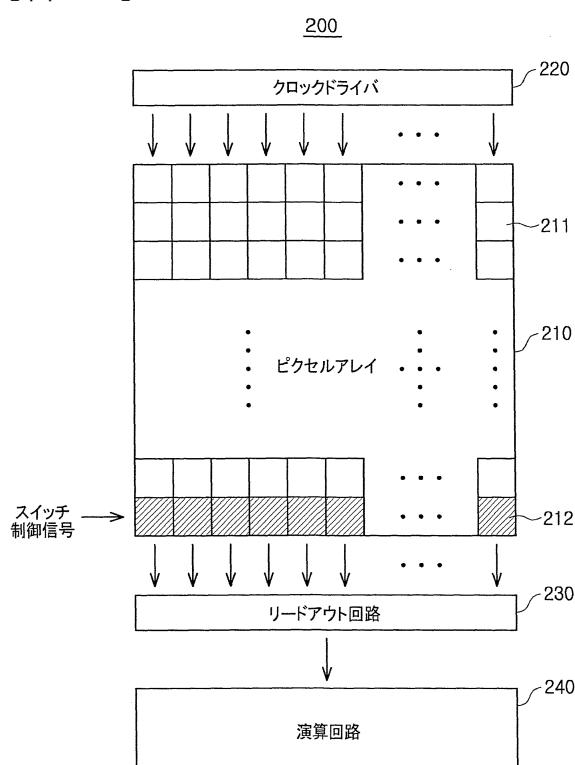

**【 0 1 0 9 】**

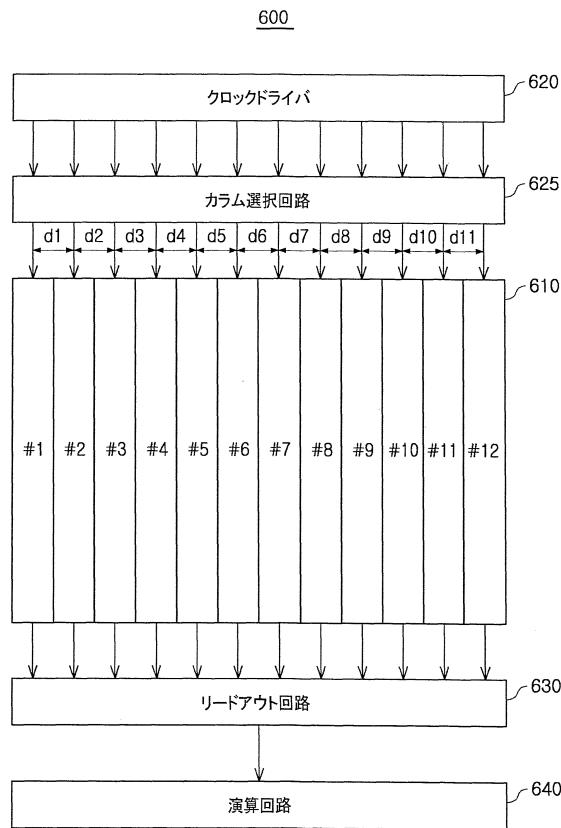

図24及び図25は、本発明の一実施形態によるイメージセンサにおける一般のピクセルを用いた位相差検出動作を説明するために提供される図である。

**【 0 1 1 0 】**

図24及び図25を参照して説明する実施形態において、イメージセンサ600は、ピクセルアレイ610、クロックドライバ620、カラム選択回路625、リードアウト回路630、演算回路640などを含む。イメージセンサ600のピクセルアレイ610は位相差検出ピクセルを含まない。即ち、ピクセルアレイ610は、一般的のピクセルだけを含む。図24及び図25は、連続的な第1フレーム周期及び第2フレーム周期のそれぞれにおけるイメージセンサ600の動作を説明するための図である。

**【 0 1 1 1 】**

ピクセルアレイ610は、ピクセルに連結された複数のフォト制御ラインを含み、複数のフォト制御ラインは、クロックドライバ620の出力端に連結されて、クロック信号の入力を受ける。クロック信号は、ピクセルの露光時間の間にフォトトランジスタをターンオン及びターンオフさせてフォトダイオードが生成する電荷をフォトトランジスタに記憶するためのフォト制御信号である。従って、1つのピクセルに一対のフォト制御ラインが連結され、一対のフォト制御ラインに入力されるクロック信号は、90度又は180度の位相差を有する。

**【 0 1 1 2 】**

それぞれ異なるカラムラインに入力されるフォト制御信号の間には位相差が存在する。

10

20

30

40

50

先ず、図 2 4 を参照すると、第 1 フレーム周期の間に、フォト制御ラインは、それぞれ、フォト制御ラインに対応するクロックドライバ 620 の出力端に連結される。一例として、第 1 フォト制御ラインはクロックドライバ 620 の第 1 出力端に連結され、第 2 フォト制御ラインはクロックドライバ 620 の第 2 出力端に連結される。

#### 【 0 1 1 3 】

クロックドライバ 620 の出力端のそれぞれで出力されるクロック信号は、所定の位相差を有する。一例として、第 1 フォト制御ラインと第 2 フォト制御ラインとの間には位相差  $d_1$  が存在する。位相差  $d_1$  は、クロックドライバ 620 の第 1 出力端で出力される第 1 クロック信号と、クロックドライバ 620 の第 2 出力端で出力される第 2 クロック信号との間の位相差である。同様に、第 2 クロック信号と第 3 クロック信号との間には位相差  $d_2$  が存在し、第 1 クロック信号と第 3 クロック信号との間の位相差は  $d_1 + d_2$  で決定される。

10

#### 【 0 1 1 4 】

次に、図 2 5 を参照すると、第 2 フレーム周期の間に、カラム選択回路 625 により、クロックドライバ 620 の出力端が 1 つずつシフトされて、フォト制御ラインに入力される。第 1 フレーム周期においてクロックドライバ 620 の  $n$  番目の出力端に連結された  $n$  番目のフォト制御ラインは、第 2 フレーム周期にクロックドライバ 620 の  $n - 1$  番目の出力端に連結される。第 2 フレーム周期において第 1 フォト制御ラインはクロックドライバ 620 の出力端に連結されないため、第 1 フォト制御ラインに連結されたピクセルはダメーピクセルとして決定される。

20

#### 【 0 1 1 5 】

第 2 フォト制御ラインは、第 1 フレーム周期の間にクロックドライバ 620 の第 2 出力端に連結され、第 2 フレーム周期の間にクロックドライバ 620 の第 1 出力端に連結される。クロックドライバ 620 の第 1 出力端及び第 2 出力端で出力される第 1 クロック信号と第 2 クロック信号との位相差は  $d_1$  である。同様に、第 1 フレーム周期及び第 2 フレーム周期において、第 3 フォト制御ラインは、クロックドライバ 620 の第 3 出力端及び第 2 出力端にそれぞれ連結される。クロックドライバ 620 の第 2 出力端及び第 3 出力端で出力される第 2 クロック信号と第 3 クロック信号との位相差は  $d_2$  である。演算回路 640 は、第 1 フレーム周期で獲得されたデータと、第 2 フレーム周期で獲得されたデータとの差を計算することにより、クロックドライバ 620 が出力端を介して出力するクロック信号、例えばフォト制御信号間の位相差を計算することができる。

30

#### 【 0 1 1 6 】

図 2 4 及び図 2 5 に示す実施形態において、位相差エラーを検出するためには 2 回のフレーム周期が必要となる。位相差エラーを検出するための 2 回のフレーム周期は、イメージセンサ 600 がウェイクアップモード (wake up mode) に転換される動作の初期に設定されるか、又はイメージセンサ 600 の動作中に所定の周期毎に挿入される。本実施形態において、所定の周期毎に 2 回のフレーム周期を割り当てて位相差エラーを検出することにより、温度及び回路素子のしきい値電圧の変化に伴う位相差エラーの変化を補償と共に、イメージセンサ 600 の性能を最適化することができる。

40

#### 【 0 1 1 7 】

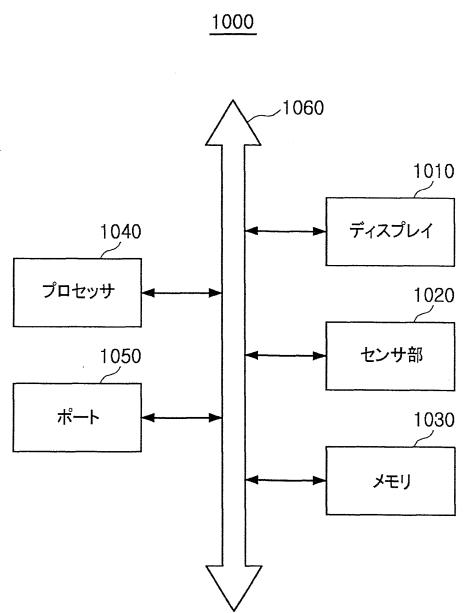

図 2 6 は、本発明の一実施形態によるイメージセンサを含む電子機器を示す概略ブロック図である。

#### 【 0 1 1 8 】

図 2 6 に示す実施形態によるコンピュータ装置 1000 は、ディスプレイ 1010、イメージセンサ (センサ部) 1020、メモリ 1030、プロセッサ 1040、及びポート 1050などを含む。その他にも、コンピュータ装置 1000 は、有線 / 無線通信装置、電源装置などを更に含むことができる。図 2 6 に示す構成要素のうち、ポート 1050 は、コンピュータ装置 1000 がビデオカード、サウンドカード、メモリカード、USB 装置などと通信するために提供される装置である。コンピュータ装置 1000 は、通常のデスクトップコンピュータやラップトップコンピュータの他に、スマートフォン、タブレッ

50

トＰＣ、スマートウェアラブル機器などを全て包括する概念である。

【0119】

プロセッサ1040は、特定の演算や命令及びタスクなどを行う。プロセッサ1040は、中央処理装置(ＣＰＵ)又はマイクロプロセッサユニット(ＭＣＵ)、システム・オン・チップ(ＳｏＣ)などであり、バス1060を介してディスプレイ1010、イメージセンサ1020、メモリ1030は勿論、ポート1050に連結された他の装置と通信することができる。

【0120】

メモリ1030は、コンピュータ装置1000の動作に必要なデータ、又はマルチメディアデータなどを記憶する記憶媒体である。メモリ1030は、ランダムアクセスメモリ(ＲＡＭ)のような揮発性メモリ、又はフラッシュメモリなどの不揮発性メモリを含む。また、メモリ1030は、記憶装置としてソリッドステートドライブ(ＳＳＤ)、ハードディスクドライブ(ＨＤＤ)、及び光学ドライブ(ＯＤＤ)のうちの少なくとも1つを含む。イメージセンサ1020は、図1～図25を参照して説明した様々な実施形態による形態であって、コンピュータ装置1000に採用される。

10

【0121】

以上、本発明の実施形態について図面を参照しながら詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的思想から逸脱しない範囲内で多様に変更実施することが可能である。

20

【符号の説明】

【0122】

- 1、10 イメージング装置

- 2、50 光源

- 3 センサ部

- 4、60 被写体

- 5、5A、100、200、300、400、500、600 イメージセンサ

- 6、6A 第1層

- 7、7A 第2層

- 8 第3層

- 20 コントローラ

- 21、120、220、320、420、520、620 クロックドライバ

- 22、130、230、330、430、530、630 リードアウト回路

- 23、140、240、340、440、540、640 演算回路

- 24 コントロールロジック

- 30、110、110A、210、310、410、510、610 ピクセルアレイ

- 40 光源ドライバ

- 111、211、311、411、511 一般的ピクセル

- 112、112A、212、312、313、412、512、513 位相差検出ピクセル

- 113 半導体基板

- 114、115 ピクセル回路

- 116 回路絶縁層

- 117 光学絶縁層

- 118、118A 光遮断層

- 119 マイクロレンズ

- 625 カラム選択回路

- 1000 コンピュータ装置

- 1010 ディスプレイ

- 1020 イメージセンサ(センサ部)

- 1030 メモリ

30

40

50

|                             |                         |    |

|-----------------------------|-------------------------|----|

| 1 0 4 0                     | プロセッサ                   |    |

| 1 0 5 0                     | ポート                     |    |

| 1 0 6 0                     | バス                      |    |

| A D C 1、A D C 2             | 第1、第2 アナログ - デジタルコンバータ  |    |

| C C                         | 電荷回路                    |    |

| C O L 1 ~ C O L 4           | 第1 ~ 第4 カラムライン          |    |

| C O L 1 [ 1 ] ~ O L 1 [ n ] | 第1カラムライン                |    |

| C O L 2 [ 1 ] ~ O L 2 [ n ] | 第2カラムライン                |    |

| C S                         | 電荷供給源                   |    |

| D C                         | ダミーチップ                  | 10 |

| D T 1                       | ピクセル分離膜                 |    |

| D P X 0 ~ D P X N - 1       | 位相差検出ピクセル               |    |

| D X 1 ~ D X 4               | 第1 ~ 第4 駆動トランジスタ        |    |

| E N                         | 保護層                     |    |

| F D 1 ~ F D 4               | 第1 ~ 第4 フローティングディフュージョン |    |

| L C                         | ロジック回路                  |    |

| M C                         | メモリチップ                  |    |

| P A 1、P A 2                 | 第1、第2 パッド領域             |    |

| P A D                       | 上部パッド                   |    |

| P C 1 ~ P C 4               | 第1 ~ 第4 ピクセル回路          | 20 |

| P D                         | フォトダイオード                |    |

| P G 1 ~ P G 4               | 第1 ~ 第4 フォト制御信号         |    |

| P G A 1、P G A 2             | 第1、第2 フォト制御信号           |    |

| P N                         | ピクセルノード                 |    |

| P X                         | ピクセル                    |    |

| P X 1 ~ P X 4               | 第1 ~ 第4 フォトトランジスタ       |    |

| R G 1 ~ R G 4               | 第1 ~ 第4 リセット制御信号        |    |

| R O W [ 1 ] ~ R O W [ m ]   | ローライン                   |    |

| R X 1 ~ R X 4               | 第1 ~ 第4 リセットトランジスタ      |    |

| S A                         | センシング領域                 | 30 |

| S A 1、S A 2                 | 第1、第2 サンプリング回路          |    |

| S E L 1 ~ S E L 4           | 第1 ~ 第4 選択制御信号          |    |

| S G                         | スイッチ制御信号                |    |

| S X 1 ~ S X 4               | 第1 ~ 第4 選択トランジスタ        |    |

| S W                         | スイッチ素子                  |    |

| T G 1 ~ T G 4               | 第1 ~ 第4 転送制御信号          |    |

| T X 1 ~ T X 4               | 第1 ~ 第4 転送トランジスタ        |    |

| V D D                       | 電源電圧                    |    |

## 【図面】

## 【図 1】

## 【図 2 a】

【図 4】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

10

20

30

40

【図 10】

【図 11】

100

120

112

113

114

115

116

117

118

119

121

130

140

40

50

【図 1 2】

【図 1 3】

【図 1 4 a】

【図 1 4 b】

10

20

30

40

50

【図 15 a】

【図 15 b】

【図 16】

【図 17】

【図 18】

【図 19】

10

20

【図 20】

【図 21】

30

40

50

【図 2 2】

【図 2 3】

10

20

【図 2 4】

【図 2 5】

30

40

50

【図 2 6】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類 F I

H 0 4 N 25/704

(72)発明者 吉 ミン ソン

大韓民国 京畿道 水原市 靈通区 三星路 129

(72)発明者 金 黎 明

大韓民国 京畿道 水原市 靈通区 三星路 129

(72)発明者 柳 賢 錫

大韓民国 京畿道 水原市 靈通区 三星路 129

(72)発明者 ペ 明 漢

大韓民国 京畿道 水原市 靈通区 三星路 129

審査官 門田 宏

(56)参考文献 特表2019-504326 (JP, A)

特表2013-516913 (JP, A)

特開2016-095298 (JP, A)

特開2008-187420 (JP, A)

国際公開第2016/009832 (WO, A1)

特開2005-214743 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 0 4 N 5 / 3 0 - 5 / 3 3

H 0 4 N 2 3 / 1 1

H 0 4 N 2 3 / 2 0 - 2 3 / 3 0

H 0 4 N 2 5 / 0 0

H 0 4 N 2 5 / 2 0 - 2 5 / 6 1

H 0 4 N 2 5 / 6 1 5 - 2 5 / 7 9

G 0 1 S 7 / 4 8 - 7 / 5 1

G 0 1 S 1 7 / 0 0 - 1 7 / 9 5

H 0 1 L 2 7 / 1 4 - 2 7 / 1 4 8

H 0 1 L 2 9 / 7 6

H 1 0 K 3 9 / 3 2 - 3 9 / 3 4