(12) 发明专利

(10) 授权公告号 CN 107833918 B

(45) 授权公告日 2021.03.16

(21) 申请号 201710377223.3

(51) Int.CI.

(22) 申请日 2017.05.25

H01L 29/78 (2006.01)

(65) 同一申请的已公布的文献号

申请公布号 CN 107833918 A

(56) 对比文件

US 2014191248 A1, 2014.07.10

(43) 申请公布日 2018.03.23

JP 2005286042 A, 2005.10.13

(30) 优先权数据

CN 105431949 A, 2016.03.23

2016-180766 2016.09.15 JP

US 2015129957 A1, 2015.05.14

(73) 专利权人 株式会社东芝

US 2015380484 A1, 2015.12.31

地址 日本东京

审查员 倪敬涵

(72) 发明人 下村纱矢 加藤浩朗 小林研也

(74) 专利代理机构 北京律盟知识产权代理有限

权利要求书3页 说明书9页 附图19页

责任公司 11287

代理人 杨林勋

(54) 发明名称

半导体装置

(57) 摘要

本发明的实施方式提供一种能够抑制寄生晶体管的动作的半导体装置。实施方式的半导体装置具有第1导电型的第1半导体区域、第2导电型的第2半导体区域、第1导电型的第3半导体区域、栅极电极、第1电极、第2绝缘部、第3绝缘部、及第2电极。栅极电极隔着第1绝缘部设置在第1半导体区域中及第2半导体区域中，且在第1方向上延伸。第1电极设置在第3半导体区域之上，且与第3半导体区域电连接。第2绝缘部在第1半导体区域中与栅极电极相隔，且在第2方向上延伸。第3绝缘部具有在第1方向上延伸的第1绝缘部分。第1绝缘部分在第2方向上位于栅极电极与第2绝缘部之间。第2电极设置在第2绝缘部及第3绝缘部之上，且与栅极电极电连接。

1.一种半导体装置,其特征在于包括:

第1导电型的第1半导体区域;

第2导电型的第2半导体区域,选择性设置在所述第1半导体区域之上;

第1导电型的第3半导体区域,选择性设置在所述第2半导体区域之上;

栅极电极,隔着第1绝缘部设置在所述第1半导体区域中及所述第2半导体区域中,且在第1方向上延伸;

第1电极,设置在所述第3半导体区域之上,且与所述第3半导体区域电连接;

第2绝缘部,在所述第1半导体区域中与所述栅极电极相隔,且仅具有在与所述第1方向交叉的第2方向上延伸的部分;

第3绝缘部,具有在所述第1方向上延伸的第1绝缘部分,且所述第1绝缘部分在所述第2方向上位于所述栅极电极与所述第2绝缘部之间,所述第3绝缘部在所述第1半导体区域中与所述栅极电极及所述第2绝缘部相隔;及

第2电极,设置在所述第2绝缘部及所述第3绝缘部之上,且与所述栅极电极电连接。

2.根据权利要求1所述的半导体装置,其特征在于:

所述栅极电极在所述第2方向上设置着多个,

所述第2绝缘部在所述第1方向上设置着多个,

所述第1绝缘部分在所述第2方向上,位于所述多个栅极电极与所述多个第2绝缘部之间。

3.根据权利要求1所述的半导体装置,其特征在于:

所述栅极电极在所述第2方向上设置着多个,

所述第2绝缘部在所述第1方向上设置着多个,

所述第3绝缘部还具有在所述第2方向上延伸的第2绝缘部分,且

所述第1绝缘部分在所述第2方向上,位于所述多个栅极电极的一部分与所述多个第2绝缘部之间,

所述第2绝缘部分在所述第1方向上,位于所述多个栅极电极的另一部分与所述多个第2绝缘部之间。

4.根据权利要求1所述的半导体装置,其特征在于还包括:

第1导电部,设置在所述第2绝缘部中;及

第2导电部,设置在所述第3绝缘部中;且

所述第1导电部在所述第2方向上延伸,

所述第2导电部具有在所述第1绝缘部分中沿着所述第1方向延伸的第1导电部分;

所述第1导电部及所述第2导电部与所述第1电极及所述第2电极电分离。

5.一种半导体装置,其特征在于包括:

第1导电型的第1半导体区域;

第2导电型的第2半导体区域,选择性设置在所述第1半导体区域之上;

第1导电型的第3半导体区域,选择性设置在所述第2半导体区域之上;

栅极电极,隔着第1绝缘部设置在所述第1半导体区域中及所述第2半导体区域中,且在第1方向上延伸;

第1电极,设置在所述第3半导体区域之上,且与所述第3半导体区域电连接;

第2绝缘部，在所述第1半导体区域中与所述栅极电极相隔，且仅具有在所述第1方向上延伸的部分；

第3绝缘部，具有在与所述第1方向交叉的第2方向上延伸的第2绝缘部分，且所述第2绝缘部分在所述第1方向上位于所述栅极电极与所述第2绝缘部之间，所述第3绝缘部在所述第1半导体区域中与所述栅极电极及所述第2绝缘部相隔；及

第2电极，设置在所述第2绝缘部及所述第3绝缘部之上，且与所述栅极电极电连接。

6. 根据权利要求5所述的半导体装置，其特征在于：

所述栅极电极在所述第2方向上设置着多个，

所述第2绝缘部在所述第2方向上设置着多个，

所述第2绝缘部分在所述第1方向上，位于所述多个栅极电极与所述多个第2绝缘部之间。

7. 根据权利要求5所述的半导体装置，其特征在于：

所述栅极电极在所述第2方向上设置着多个，

所述第2绝缘部在所述第2方向上设置着多个，

所述第3绝缘部还具有在所述第1方向上延伸的第1绝缘部分，且

所述第1绝缘部分在所述第2方向上，位于所述多个栅极电极的一部分与所述多个第2绝缘部之间，

所述第2绝缘部分在所述第1方向上，位于所述多个栅极电极的另一部分与所述多个第2绝缘部之间。

8. 根据权利要求5所述的半导体装置，其特征在于还包括：

第1导电部，设置在所述第2绝缘部中；及

第2导电部，设置在所述第3绝缘部中；且

所述第1导电部在所述第2方向上延伸，

所述第2导电部具有在所述第2绝缘部分中沿着所述第2方向延伸的第2导电部分，

所述第1导电部及所述第2导电部与所述第1电极及所述第2电极电分离。

9. 一种半导体装置，其特征在于包括：

第1导电型的第1半导体区域；

第2导电型的第2半导体区域，选择性设置在所述第1半导体区域之上；

第1导电型的第3半导体区域，选择性设置在所述第2半导体区域之上；

栅极电极，隔着第1绝缘部设置在所述第1半导体区域中及所述第2半导体区域中；

第1电极，设置在所述第3半导体区域之上，且与所述第3半导体区域电连接；

环状的第2绝缘部，在所述第1半导体区域中与所述栅极电极相隔，且包围所述第1半导体区域的一部分；

环状的第1导电部，设置在所述第2绝缘部中；及

第2电极，设置在所述第2绝缘部之上，且与所述栅极电极电连接。

10. 根据权利要求9所述的半导体装置，其特征在于还包括：

环状的第3绝缘部，与所述第2绝缘部相隔而设置在所述第1半导体区域中，位于所述第2绝缘部的内侧，且包围所述第1半导体区域的一部分；及

环状的第2导电部，设置在所述第3绝缘部中。

11. 根据权利要求10所述的半导体装置，其特征在于：

所述第1导电部及所述第2导电部与所述第1电极及所述第2电极电分离。

## 半导体装置

[0001] [相关申请]

[0002] 本申请享有以日本专利申请2016-180766号(申请日:2016年9月15日)为基础申请的优先权。本申请通过参照该基础申请而包含基础申请的全部内容。

### 技术领域

[0003] 本发明的实施方式涉及一种半导体装置。

### 背景技术

[0004] MOSFET(Metal Oxide Semiconductor Field Effect Transistor,金属氧化物半导体场效应晶体管)等半导体装置具有寄生晶体管。该寄生晶体管较理想的是难以动作。

### 发明内容

[0005] 本发明提供一种能够抑制寄生晶体管的动作的半导体装置。

[0006] 实施方式的半导体装置具有第1导电型的第1半导体区域、第2导电型的第2半导体区域、第1导电型的第3半导体区域、栅极电极、第1电极、第2绝缘部、第3绝缘部、及第2电极。所述第2半导体区域选择性设置在所述第1半导体区域之上。所述第3半导体区域选择性设置在所述第2半导体区域之上。所述栅极电极隔着第1绝缘部设置在所述第1半导体区域中及所述第2半导体区域中。所述栅极电极在第1方向上延伸。所述第1电极设置在所述第3半导体区域之上。所述第1电极与所述第3半导体区域电连接。所述第2绝缘部在所述第1半导体区域中与所述栅极电极相隔。所述第2绝缘部在与所述第1方向交叉的第2方向上延伸。所述第3绝缘部具有在所述第1方向上延伸的第1绝缘部分。所述第3绝缘部的所述第1绝缘部分在所述第2方向上位于所述栅极电极与所述第2绝缘部之间。所述第3绝缘部在所述第1半导体区域中与所述栅极电极及所述第2绝缘部相隔。所述第2电极设置在所述第2绝缘部及所述第3绝缘部之上。所述第2电极与所述栅极电极电连接。

### 附图说明

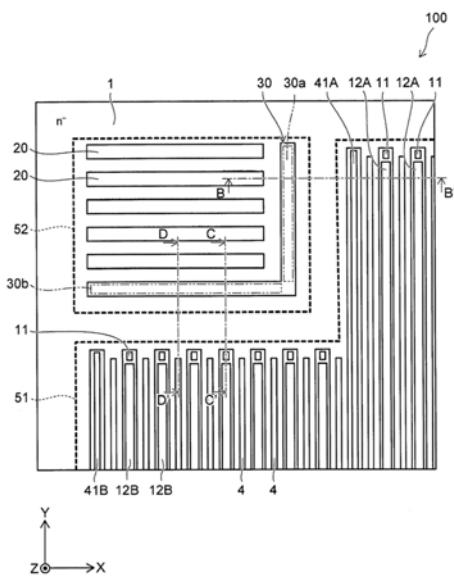

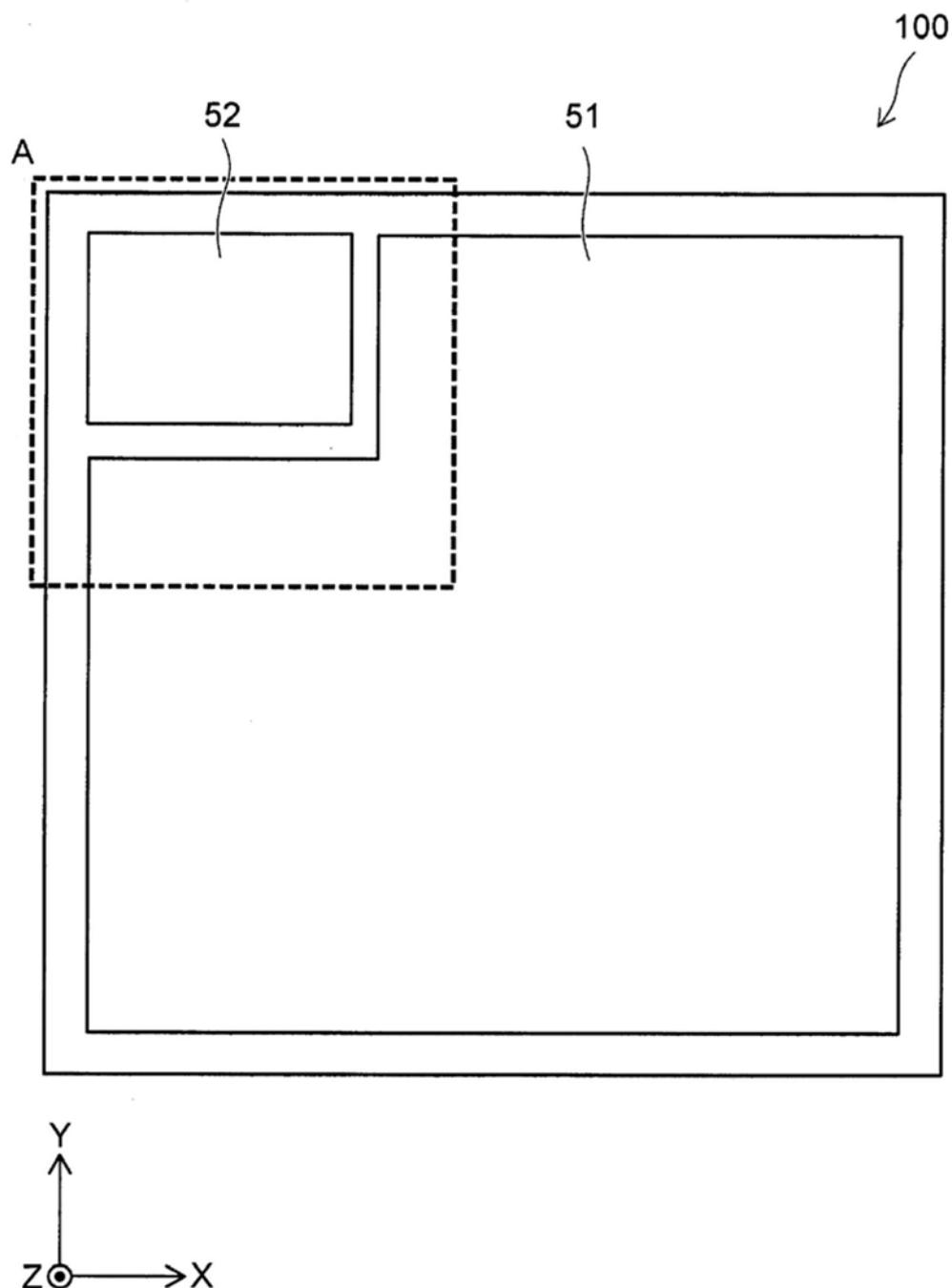

[0007] 图1是第1实施方式的半导体装置的俯视图。

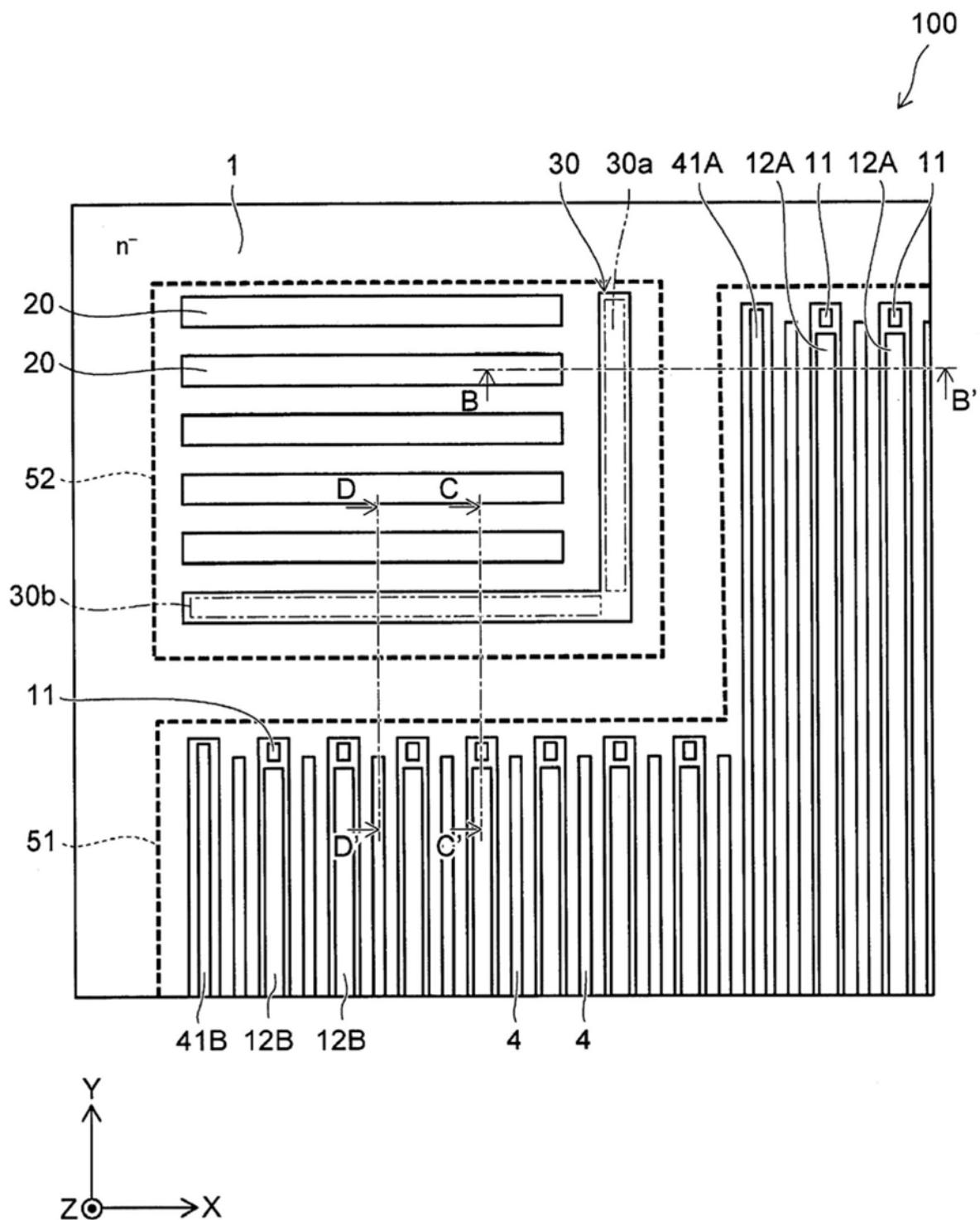

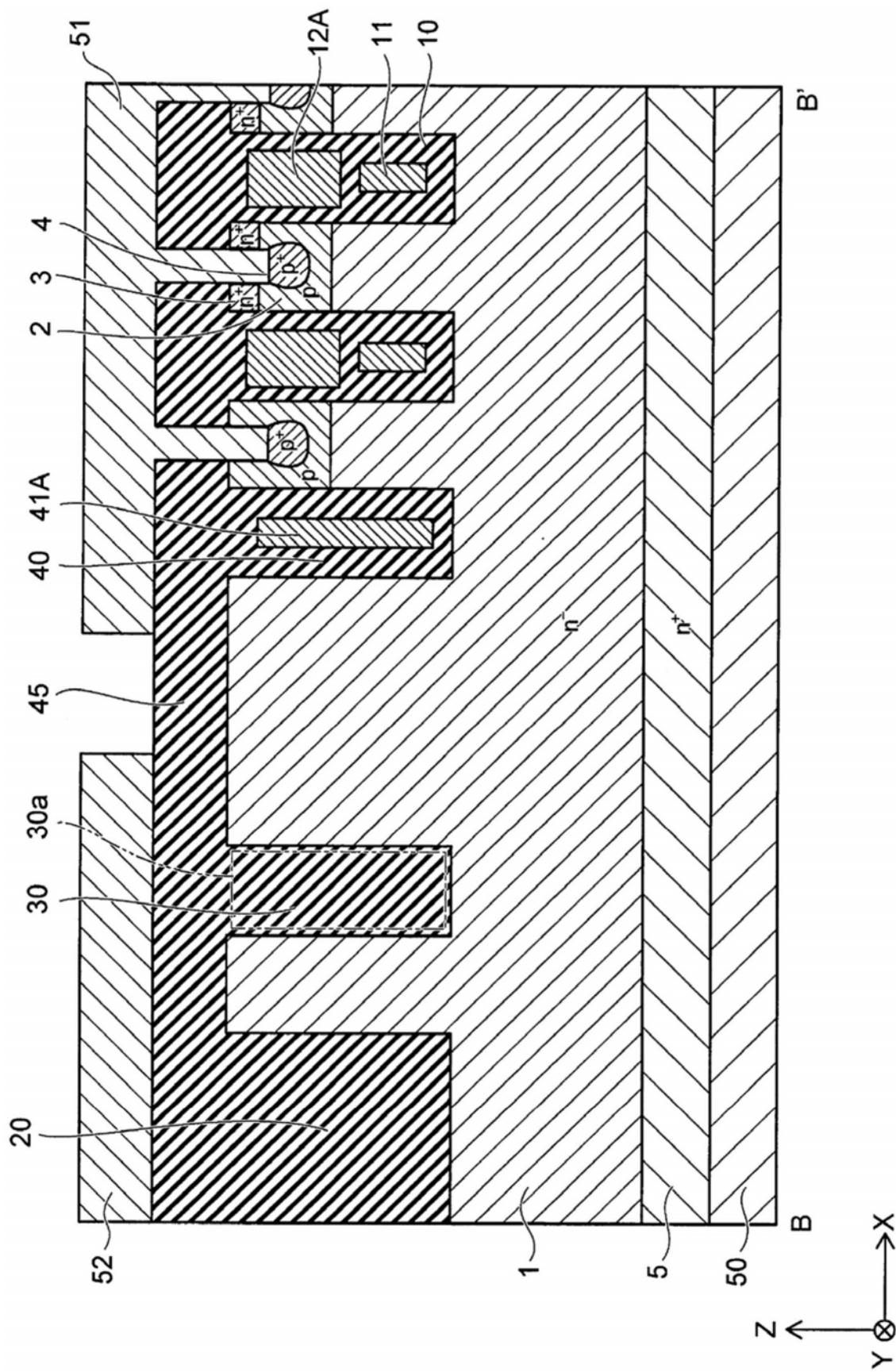

[0008] 图2是将图1的部分A放大的俯视图。

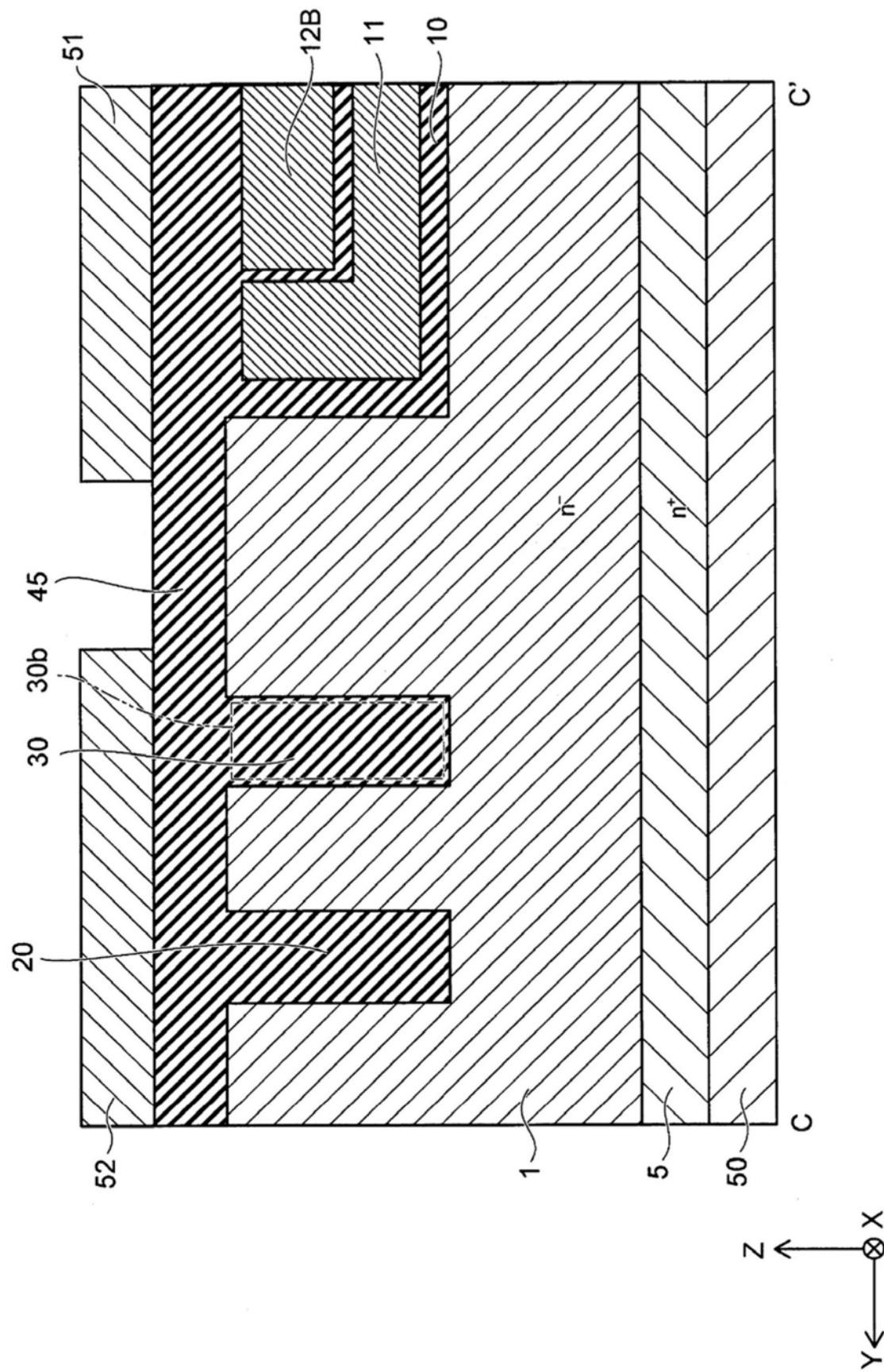

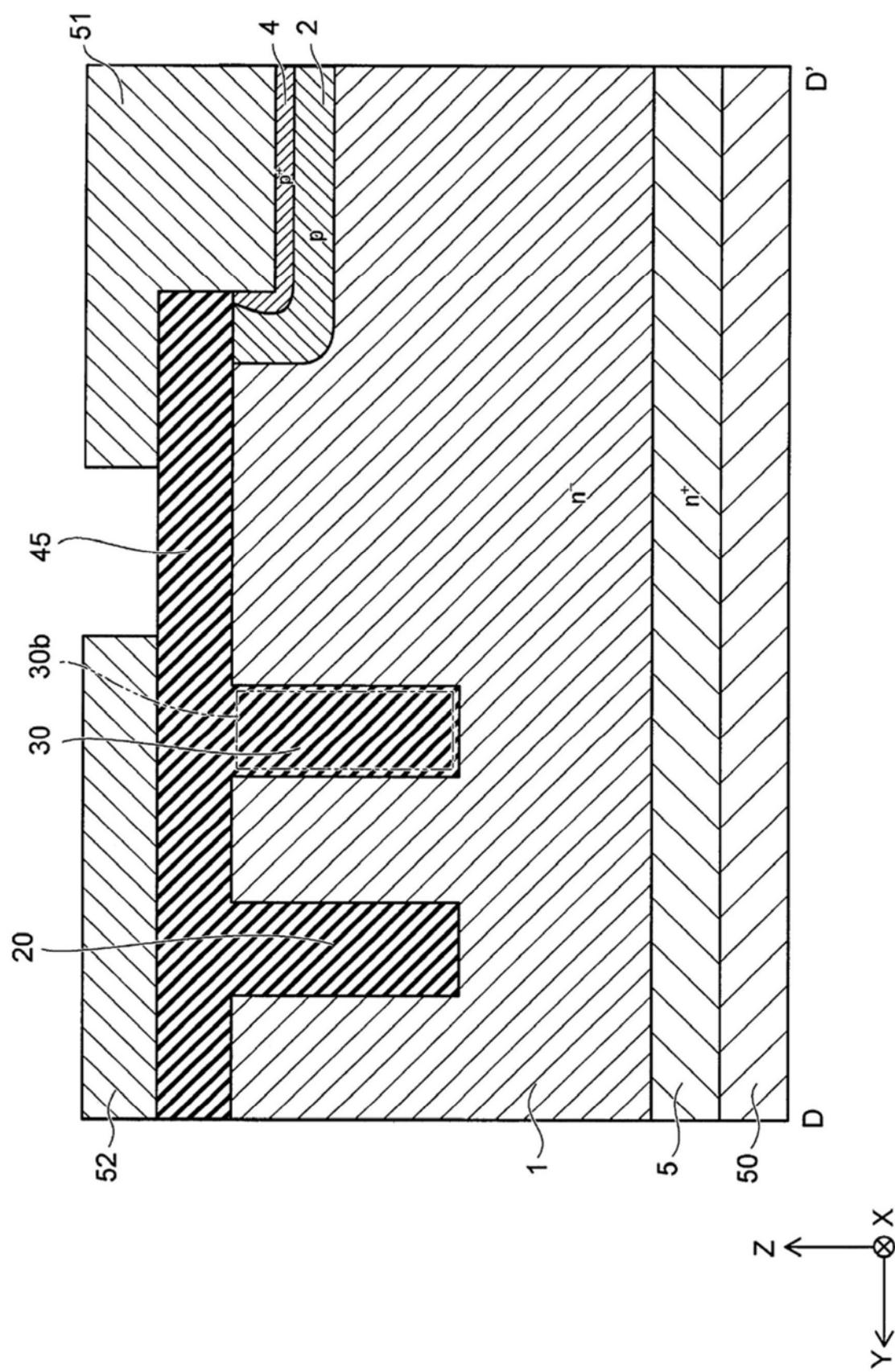

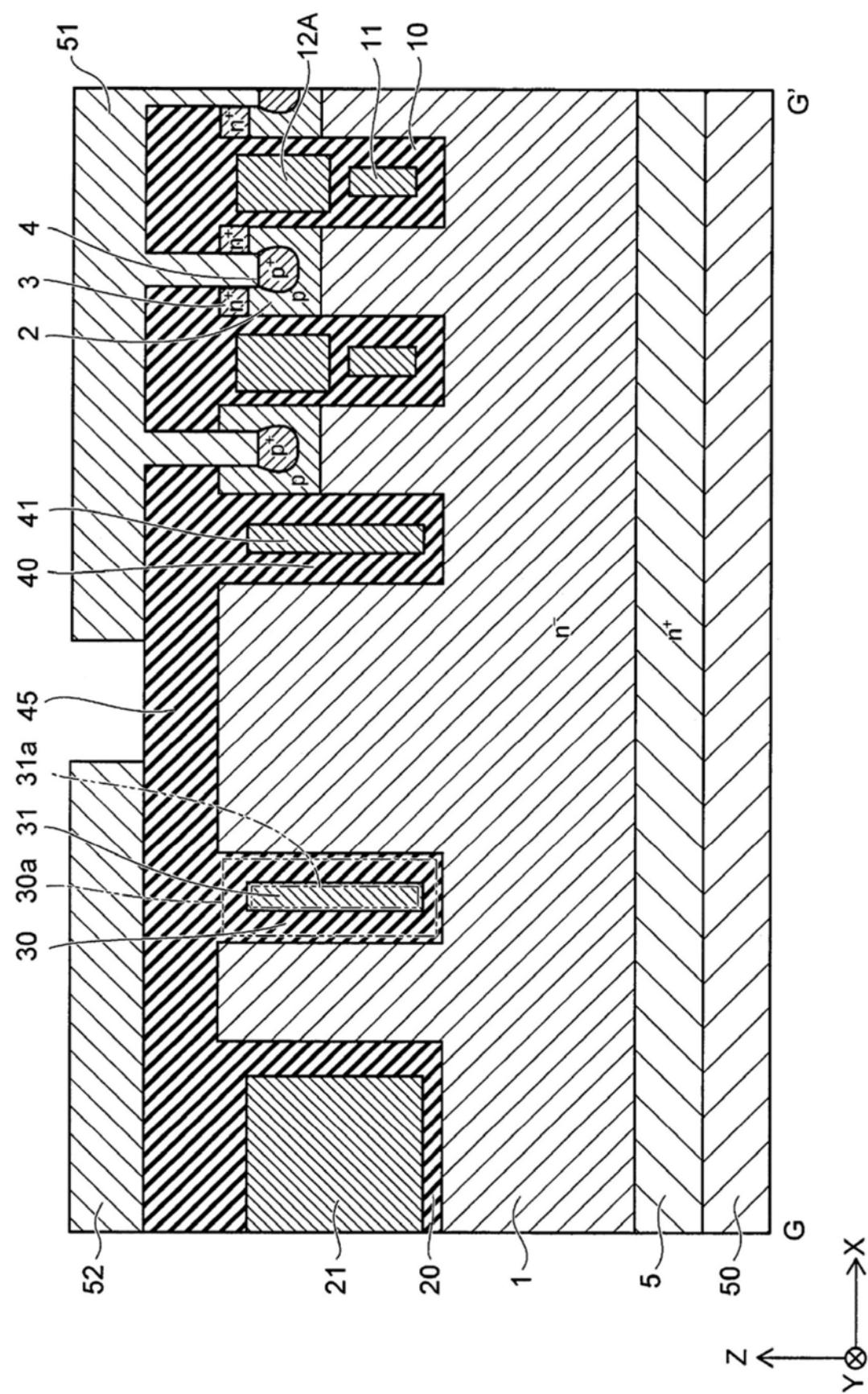

[0009] 图3是图2的B-B'剖视图。

[0010] 图4是图2的C-C'剖视图。

[0011] 图5是图2的D-D'剖视图。

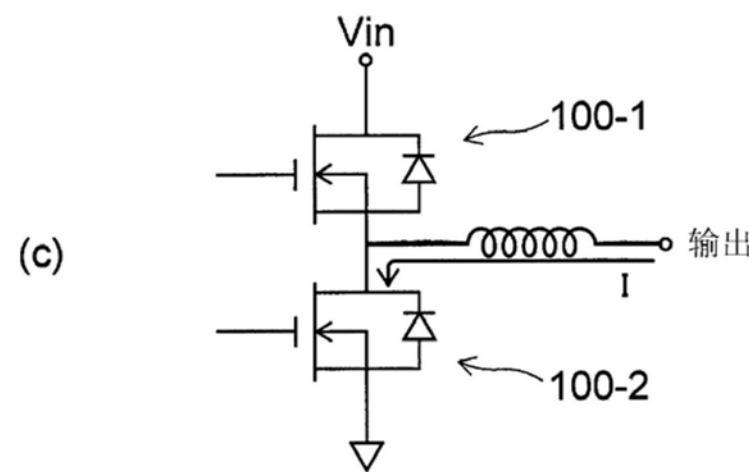

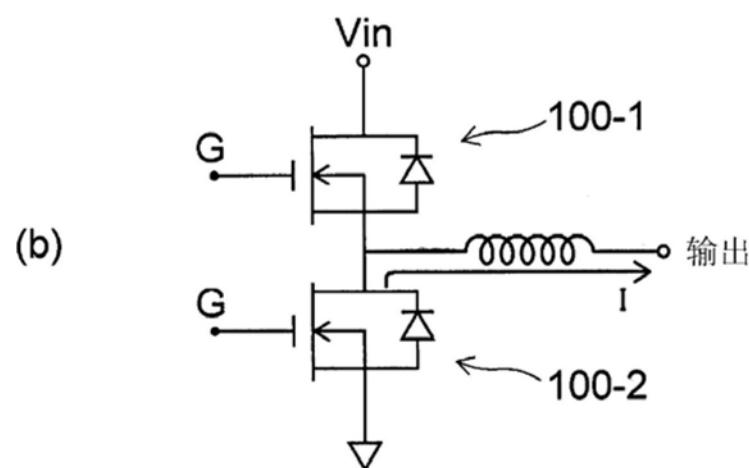

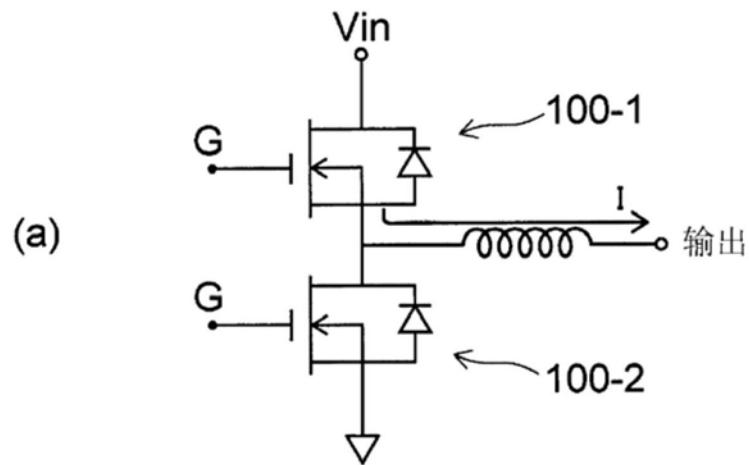

[0012] 图6(a)~(c)是表示连接着第1实施方式的半导体装置的电气电路的一例的电路图。

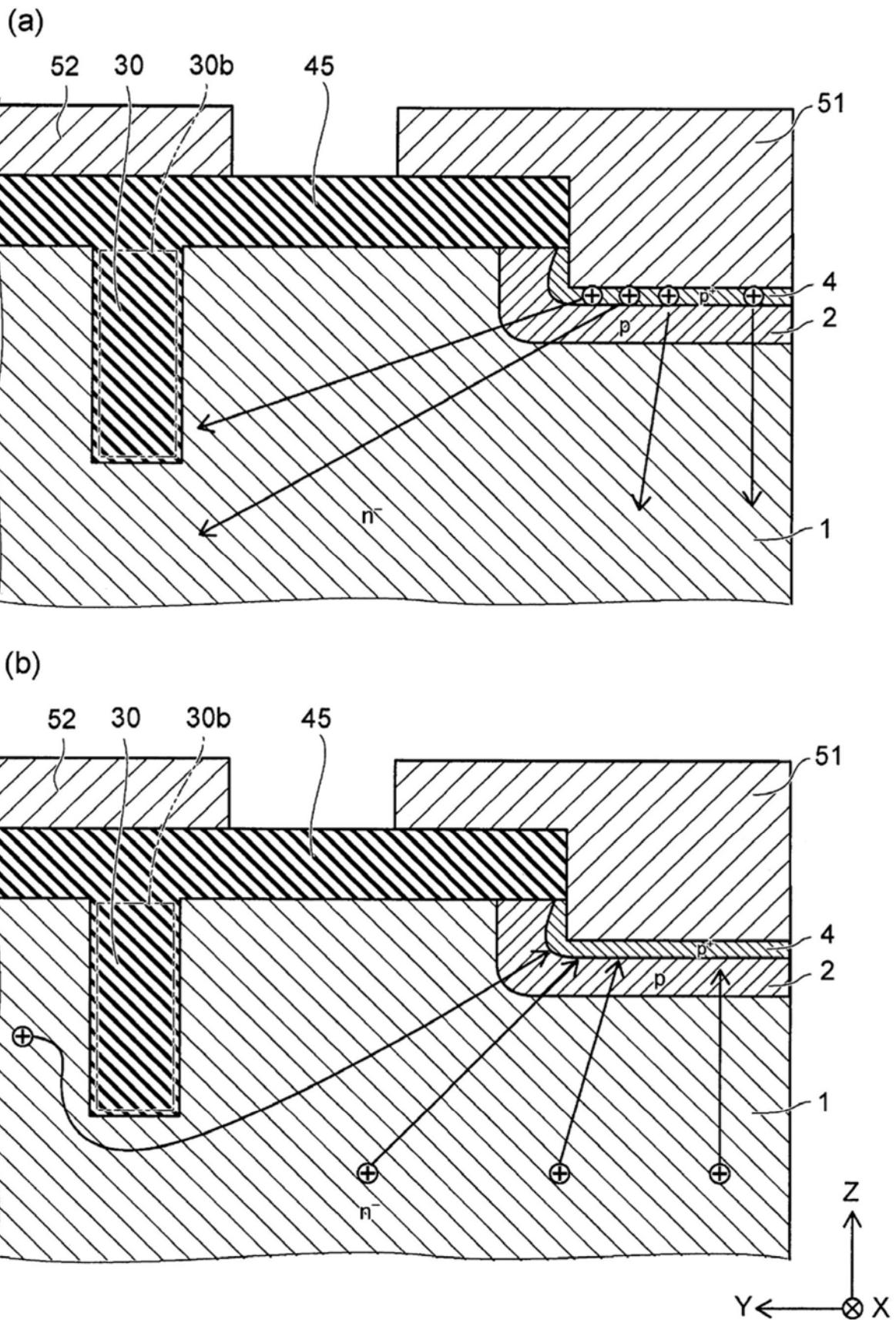

[0013] 图7(a)及(b)是表示第1实施方式的半导体装置中的载流子的流动的剖视图。

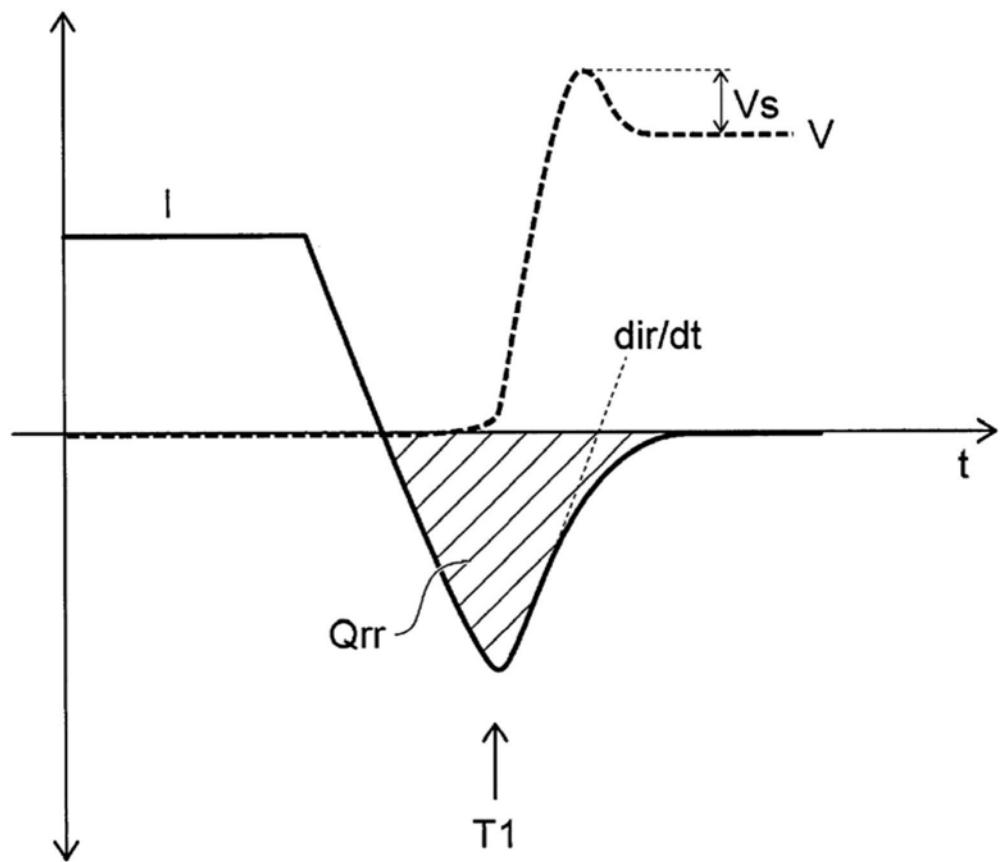

[0014] 图8是表示图6所示的电气电路中的半导体装置中的电流及电压的波形的曲线图。

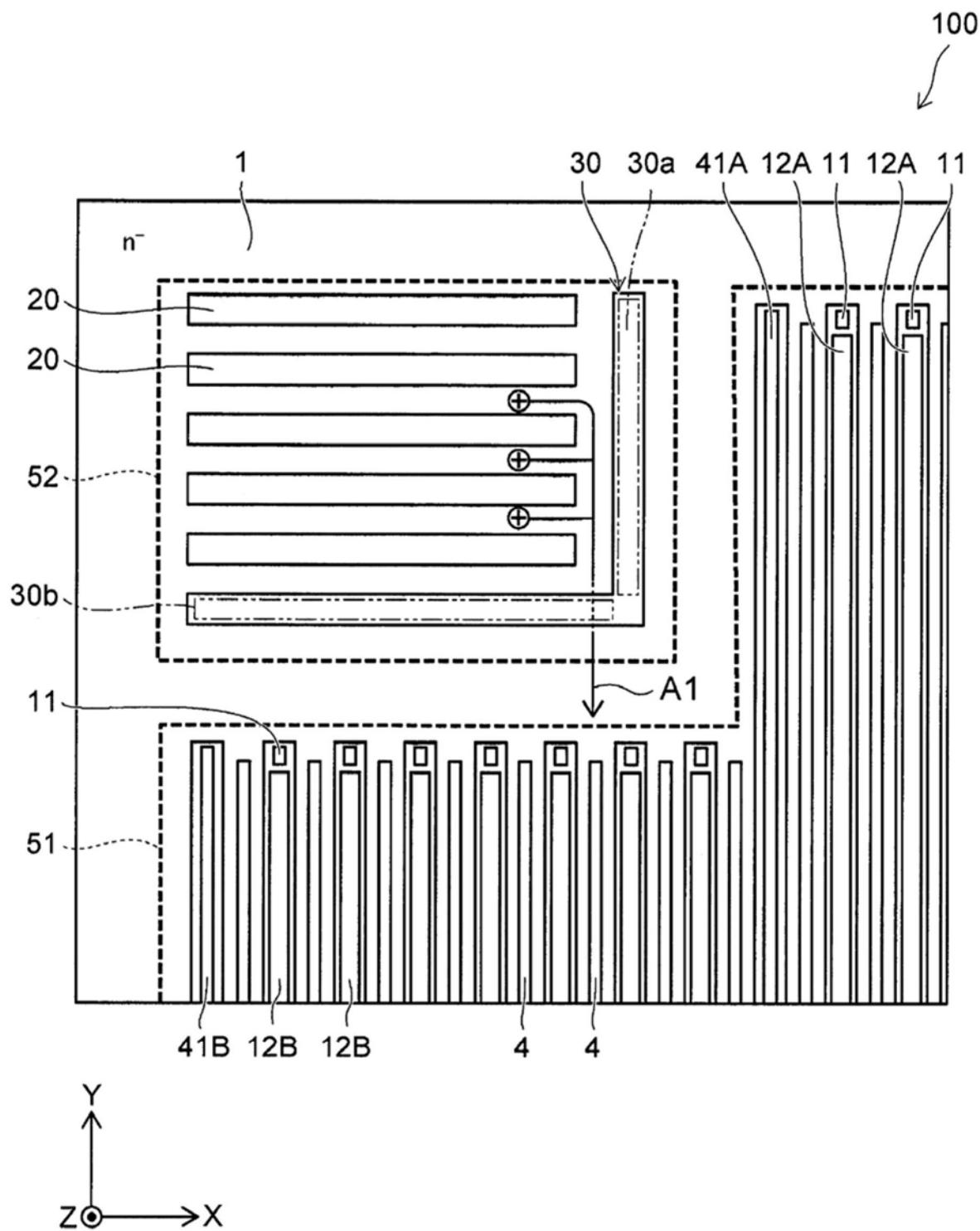

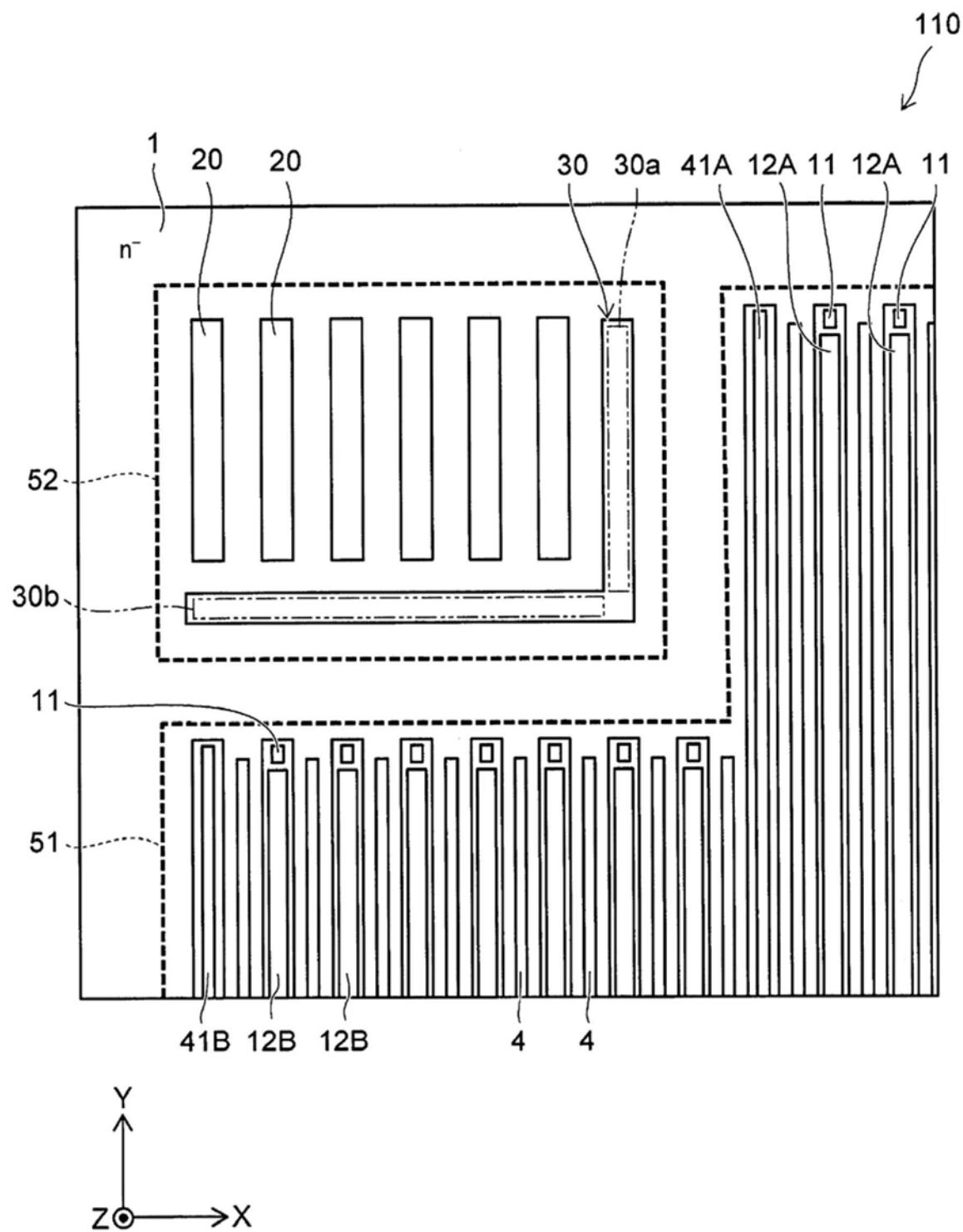

[0015] 图9是第1实施方式的半导体装置100的俯视图。

- [0016] 图10是表示第1实施方式的第1变化例的半导体装置的一部分的俯视图。

- [0017] 图11是表示第1实施方式的第2变化例的半导体装置的一部分的俯视图。

- [0018] 图12(a)是图11的E-E'剖视图,图12(b)是图11的F-F'剖视图。

- [0019] 图13(a)及(b)是表示第1实施方式的第2变化例的半导体装置的另一例的局部放大剖视图。

- [0020] 图14是表示第1实施方式的第3变化例的半导体装置的一部分的俯视图。

- [0021] 图15是图14的G-G'剖视图。

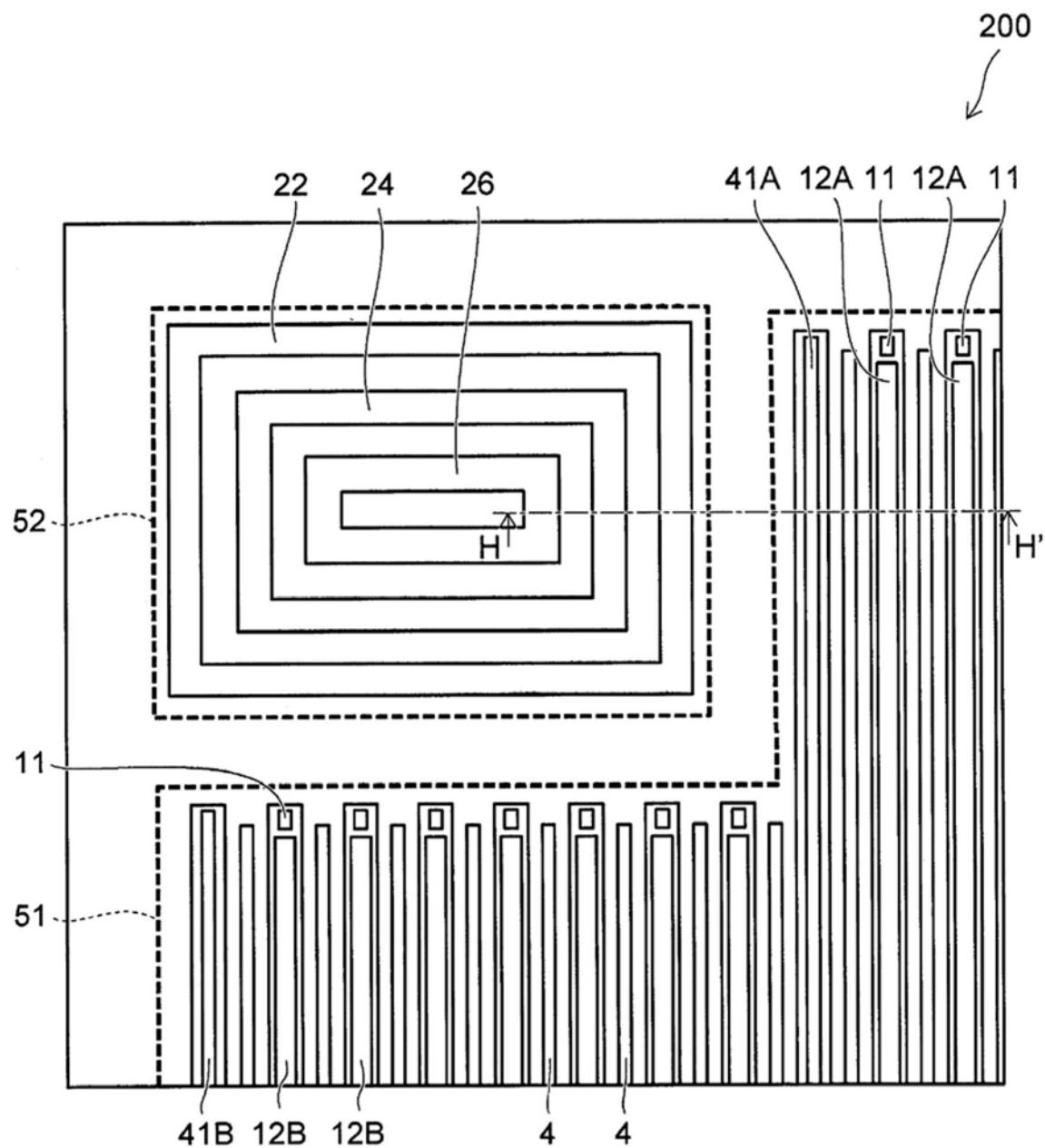

- [0022] 图16是表示第2实施方式的半导体装置的一部分的俯视图。

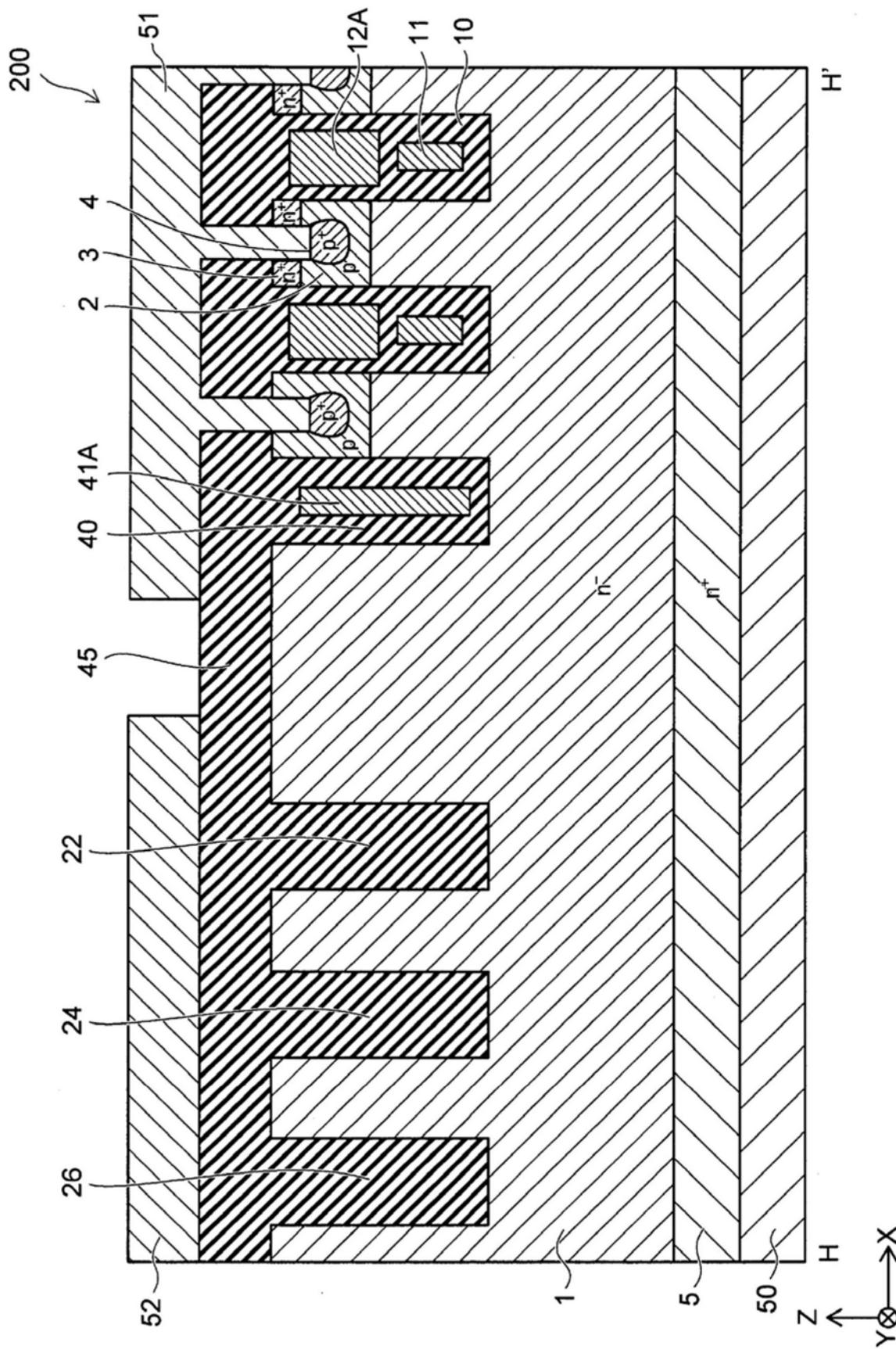

- [0023] 图17是图16的H-H'剖视图。

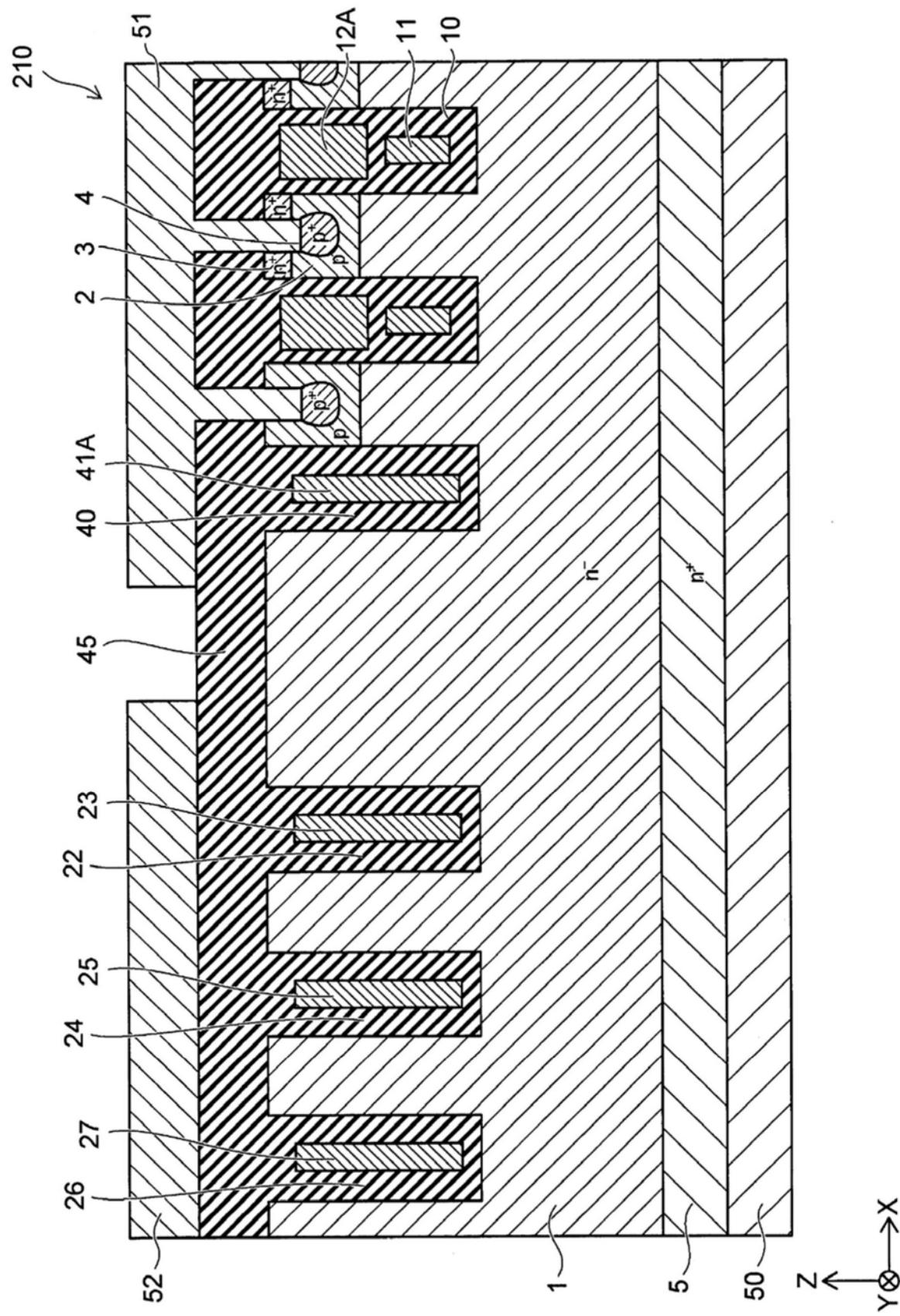

- [0024] 图18是表示第2实施方式的第1变化例的半导体装置的一部分的剖视图。

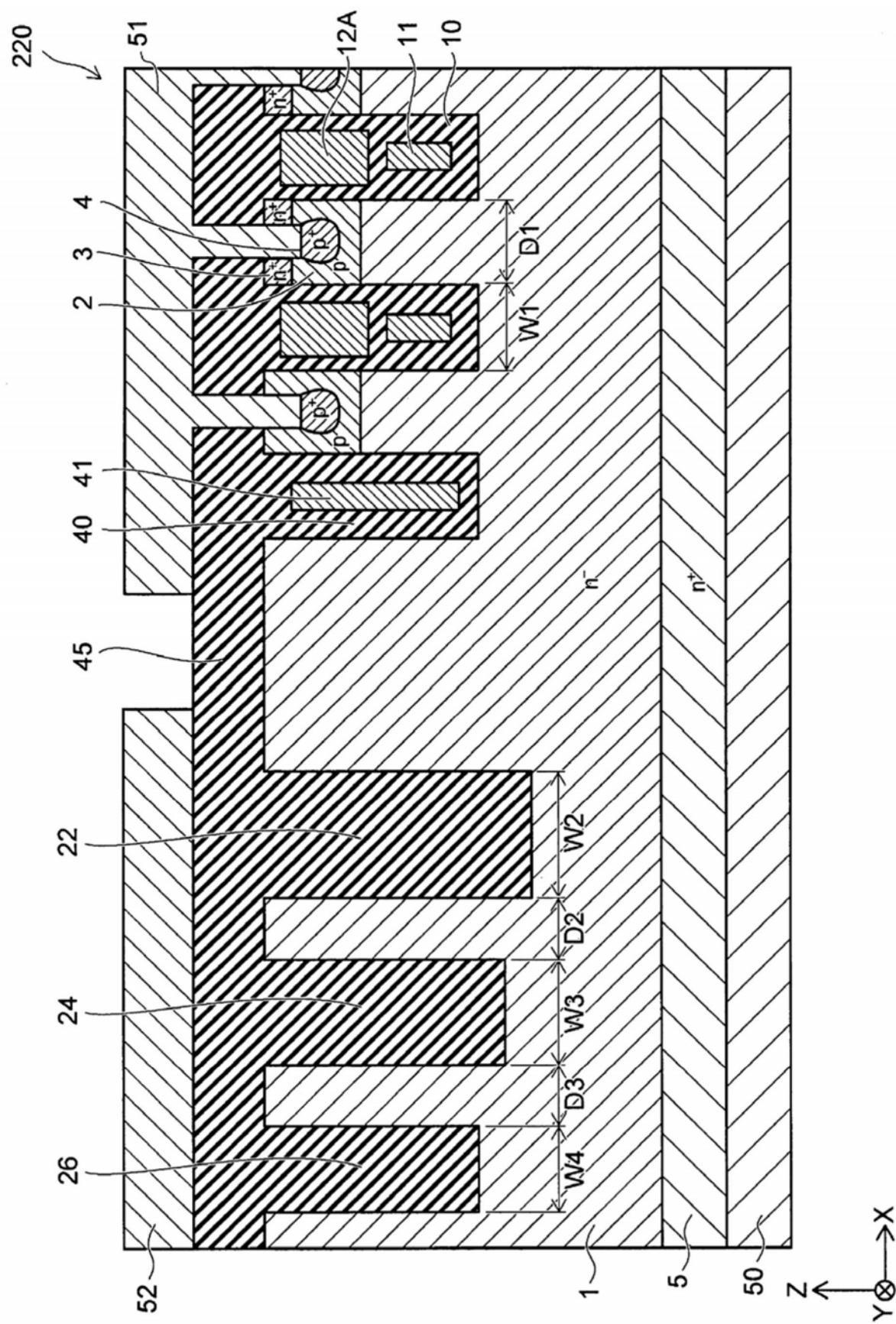

- [0025] 图19是表示第2实施方式的第2变化例的半导体装置的一部分的剖视图。

### 具体实施方式

- [0026] 以下,参照附图对本发明的各实施方式进行说明。

- [0027] 另外,附图是示意性或概念性的,各部分的厚度与宽度的关系、部分之间的大小的比率等未必与实物相同。而且,即便是在表示相同部分的情况下,也存在彼此的尺寸或比率视各附图而不同表示的情况。

- [0028] 而且,在本申请的说明书与各图中,对与已经说明过的要素相同的要素标注相同的符号,并适当省略详细的说明。

- [0029] 在各实施方式的说明中,使用XYZ正交座标系。将从漏极电极50朝向源极电极51的方向设为Z方向。另外,将与Z方向垂直且相互正交的2个方向设为X方向(第2方向)及Y方向(第1方向)。

- [0030] 在以下的说明中, $n^+$ 、 $n^-$ 及 $p^+$ 、 $p^-$ 的记法表示各导电型的杂质浓度的相对高低。即,带有“+”的记法表示比起不带“+”也不带“-”的记法,杂质浓度相对较高,带有“-”的记法表示比起不带“+”也不带“-”的记法,杂质浓度相对较低。

- [0031] 对于以下所说明的各实施方式,也可使各半导体区域的p型与n型对调而实施各实施方式。

- [0032] (第1实施方式)

- [0033] 使用图1~图5,对第1实施方式的半导体装置的一例进行说明。

- [0034] 图1是第1实施方式的半导体装置100的俯视图。

- [0035] 图2是将图1的部分A放大的俯视图。

- [0036] 图3是图2的B-B'剖视图。

- [0037] 图4是图2的C-C'剖视图。

- [0038] 图5是图2的D-D'剖视图。

- [0039] 另外,在图2中,用虚线表示源极电极51及栅极垫片52,并省略绝缘层45、p型基极区域2、及 $n^+$ 型源极区域3。

- [0040] 半导体装置100例如是MOSFET(Metal Oxide Semiconductor Field Effect Transistor)。

- [0041] 如图1~图4所示,半导体装置100具有 $n^-$ 型(第1导电型)半导体区域1(第1半导体

区域)、p型(第2导电型)基极区域2(第2半导体区域)、n<sup>+</sup>型源极区域3(第3半导体区域)、p<sup>+</sup>型接触区域4、n<sup>+</sup>型漏极区域5、绝缘部10(第1绝缘部)、场板电极(以下,称为FP电极)11、栅极电极12A及12B、绝缘部20(第2绝缘部)、绝缘部30(第3绝缘部)、绝缘部40、FP电极41A及41B、绝缘层45、漏极电极50、源极电极51(第1电极)、以及栅极垫片52(第2电极)。

[0042] 如图1所示,在半导体装置100的上表面,设置着源极电极51及栅极垫片52。源极电极51与栅极垫片52相互远离而电分离。

[0043] 如图2所示,在源极电极51之下,设置着与栅极垫片52电连接的多个栅极电极12A及多个栅极电极12B。多个栅极电极12A及多个栅极电极12B在X方向上并排,且各自在Y方向上延伸。在从Z方向观察的情况下,栅极垫片52在Y方向上,与栅极电极12B并排,而不与栅极电极12A并排。因此,栅极电极12B的Y方向上的长度比栅极电极12A的Y方向上的长度短。

[0044] 以下,就栅极电极12A及12B共通的性质,将这些栅极电极统称为“栅极电极12”而加以说明。

[0045] 在栅极垫片52之下,沿着Y方向并排着多个绝缘部20。各绝缘部20在X方向上延伸。栅极电极12A的一部分在X方向上与绝缘部20并排。另外,栅极电极12B在Y方向上与绝缘部20的一部分并排。

[0046] 绝缘部30具有在Y方向上延伸的第1绝缘部分30a、及在X方向上延伸的第2绝缘部分30b。第1绝缘部分30a在X方向上,位于多个绝缘部20与多个栅极电极12A之间。第2绝缘部分30b在Y方向上,位于多个绝缘部20与多个栅极电极12B之间。

[0047] FP电极41A及41B设置在源极电极51之下。在从Z方向观察的情况下,栅极垫片52在Y方向上,与FP电极41B并排,而不与FP电极41A并排。因此,FP电极41B的Y方向上的长度比FP电极41A的Y方向上的长度短。

[0048] FP电极41A的一部分在X方向上,位于栅极电极12A的一部分与绝缘部30之间。FP电极41B位于多个栅极电极12B的半导体装置外周侧。栅极电极12B在X方向上,设置在FP电极41A的一部分与FP电极41B之间。

[0049] 以下,就FP电极41A及41B共通的性质,将这些FP电极统称为“FP电极41”而加以说明。

[0050] 如图3~图5所示,在半导体装置100的下表面,设置着漏极电极50。

[0051] n<sup>+</sup>型漏极区域5设置在漏极电极50之上,且与漏极电极50电连接。

[0052] n<sup>-</sup>型半导体区域1设置在n<sup>+</sup>型漏极区域5之上。

[0053] p型基极区域2选择性设置在n<sup>-</sup>型半导体区域1之上。

[0054] n<sup>+</sup>型源极区域3及p<sup>+</sup>型接触区域4选择性设置在p型基极区域2之上。

[0055] FP电极11隔着绝缘部10设置在n<sup>-</sup>型半导体区域1中。

[0056] 栅极电极12隔着绝缘部10设置在n<sup>-</sup>型半导体区域1中及p型基极区域2中。栅极电极12位于FP电极11之上,且与FP电极11相隔。如图4所示,FP电极11的Y方向上的端部向Z方向转向,且在Y方向上与栅极电极12并排。

[0057] 源极电极51的一部分设置在p型基极区域2中,且与n<sup>+</sup>型源极区域3及p<sup>+</sup>型接触区域4电连接。在栅极电极12与源极电极51之间,设置着绝缘层45,这些电极电分离。

[0058] FP电极41隔着绝缘部40设置在n<sup>-</sup>型半导体区域1中及p型基极区域2中。FP电极41与栅极电极12在X方向上相隔。

[0059] FP电极11及41与源极电极51或栅极垫片52电连接。

[0060] 绝缘部20及30与p型基极区域2、绝缘部10、及栅极电极12相隔而设置在n<sup>-</sup>型半导体区域1中。另外，绝缘部20与30在n<sup>-</sup>型半导体区域1中，在X方向及Y方向上相隔。

[0061] 绝缘部20及绝缘部30周围的n<sup>-</sup>型半导体区域1被绝缘层45所覆盖，栅极垫片52与源极电极51相隔而设置在绝缘层45之上。绝缘部10、20及30通过绝缘层45而相连。绝缘部10、20及30、绝缘层45例如是形成为一体的绝缘膜。

[0062] 这里，对半导体装置100的动作进行说明。

[0063] 如果在相对于源极电极51而正的电压施加到漏极电极50的状态下，对栅极电极12施加阈值以上的电压，那么半导体装置成为接通状态。这时，在绝缘部10附近的p型基极区域2形成通道(反转层)。电子通过该通道而从n<sup>+</sup>型源极区域3流向n<sup>-</sup>型半导体区域1，并通过n<sup>+</sup>型漏极区域5而排出。

[0064] 此后，如果施加于栅极电极12的电压低于阈值，那么p型基极区域2中的通道湮灭，半导体装置成为断开状态。

[0065] 如果半导体装置100成为断开状态，那么因FP电极11与漏极电极50之间的电位差，空乏层从绝缘部10与n<sup>-</sup>型半导体区域1的界面向n<sup>-</sup>型半导体区域1扩大。利用从绝缘部10与n<sup>-</sup>型半导体区域1的界面扩大的该空乏层，能够提高半导体装置的耐压。或者，能够与半导体装置耐压的提高程度相应地，提高n<sup>-</sup>型半导体区域1中的n型杂质浓度，从而降低半导体装置的接通电阻。

[0066] 另外，半导体装置100内置有以p型基极区域2为阳极、以n<sup>-</sup>型半导体区域1为阴极的二极管。因此，在相对于漏极电极50而正的电压施加到源极电极51时，顺向电流从漏极电极50流向源极电极51。

[0067] 其次，对各构成要素的材料的一例进行说明。

[0068] n<sup>-</sup>型半导体区域1、p型基极区域2、n<sup>+</sup>型源极区域3、p<sup>+</sup>型接触区域4、及n<sup>+</sup>型漏极区域5包含硅、碳化硅、氮化镓、或砷化镓作为半导体材料。在使用硅作为半导体材料的情况下，可使用砷、磷、或锑作为n型杂质。可使用硼作为p型杂质。

[0069] FP电极11、栅极电极12、及FP电极41包含多晶硅等导电材料。

[0070] 绝缘部10、20、30及40包含氧化硅等绝缘材料。

[0071] 漏极电极50、源极电极51、及栅极垫片52包含铝等金属。

[0072] 这里，使用图6～图8对本实施方式所达成的效果进行说明。

[0073] 图6是表示连接着第1实施方式的半导体装置100的电气电路的一例的电路图。

[0074] 图7是表示第1实施方式的半导体装置中的载流子的流动的剖视图。

[0075] 图8是表示图6所示的电气电路中的半导体装置100-2中的电流及电压的波形的曲线图。

[0076] 另外，在图8中，实线表示在二极管中流动的电流，虚线表示漏极电极50相对于源极电极51的电压。横轴表示时间，二极管的电流是以顺向流动的情况为正而加以表示。

[0077] 在图6所示的例子中，使用本实施方式的2个半导体装置100-1与100-2构成了半桥电路。图6(a)表示半导体装置100-1为接通状态、半导体装置100-2为断开状态，从而电流I流向半导体装置100-1的情况。

[0078] 如果在图6(a)所示的状态下，将半导体装置100-1关闭，那么产生基于电感L的感

应电动势。由此,如图6(b)所示,顺向电流I流向半导体装置100-2的二极管。这时,如图7(a)所示,电洞通过p型基极区域2而从源极电极51注入到n<sup>-</sup>型半导体区域1。

[0079] 如果顺向电流向半导体装置100-2的二极管的流动结束,那么储存在半导体装置100-2内部的载流子排出。这时,如图7(b)所示,电洞通过p型基极区域2而向源极电极51排出。载流子从半导体装置100-2排出,由此如图6(c)所示,在半导体装置100-2中,反向恢复电流从漏极电极50向源极电极51流动。

[0080] 如图8所示,如果在时序T1反向恢复电流的流动结束,那么此后,半导体装置100-2的漏极电极50相对于源极电极51的电压V开始上升。这时,对应于反向恢复电流的减少斜率dir/dt,电压V中产生突波电压Vs。如果dir/dt较大,那么突波电压Vs也较大。如果突波电压Vs较大,那么由n<sup>+</sup>型源极区域3、p型基极区域2、及n<sup>-</sup>型半导体区域1所构成的寄生NPN型晶体管易于动作。如果寄生NPN型晶体管动作,那么大电流流经半导体装置内,而有可能破坏半导体装置,因此较理想的是dir/dt较小。

[0081] 另外,如果图8所示的储存电荷Qrr较大,且电洞集中流向一部分p型基极区域2及p<sup>+</sup>型接触区域4,那么寄生晶体管的基极电位上升,而有寄生晶体管动作的可能性。因此,与dir/dt同样地,较理想的是储存电荷Qrr也较少。

[0082] 在二极管动作时所注入的电洞的一部分也储存在栅极垫片52之下的n<sup>-</sup>型半导体区域1。储存在栅极垫片52之下的n<sup>-</sup>型半导体区域1的电洞在反向恢复动作时,移动到附近的p型基极区域2并向源极电极51排出。从而,在与栅极垫片52下的n<sup>-</sup>型半导体区域1靠近的p型基极区域2,与其他部分相比流动着更多的电洞,因此寄生NPN型晶体管更易动作。

[0083] 因此,减少储存在栅极垫片52之下的电荷Qrr、及减小储存在栅极垫片52之下的载流子而实现的反向恢复时的dir/dt对抑制寄生NPN型晶体管的动作特别有效。

[0084] 就该点来讲,如本实施方式的半导体装置100这样,在栅极垫片52下的n<sup>-</sup>型半导体区域1中设置绝缘部20,由此能够减小栅极垫片52之下的n<sup>-</sup>型半导体区域1的体积。因此,能够减少储存在栅极垫片52之下的电荷Qrr。

[0085] 而且,通过设置多个绝缘部20,可使注入到n<sup>-</sup>型半导体区域1的电洞的一部分储存在绝缘部20彼此之间。就储存在绝缘部20彼此之间的n<sup>-</sup>型半导体区域1的电洞来讲,在反向恢复动作时,其移动会受到绝缘部20的阻碍,而难以向源极电极51移动,因此能够延长反向恢复所需的时间,从而能够缩小dir/dt。

[0086] 进而,在本实施方式的半导体装置100中,绝缘部30的第1绝缘部分30a在多个绝缘部20与多个栅极电极12A之间沿着Y方向而延伸。通过采用这种构造,在反向恢复动作时,当储存在绝缘部20彼此之间的n<sup>-</sup>型半导体区域1的电洞向源极电极51移动时,其移动会受到第1绝缘部分30a的阻碍。因此,能够延长反向恢复所需的时间,从而能够进一步缩小dir/dt。

[0087] 即,根据本实施方式,通过设置绝缘部20及30,能够减少储存电荷Qrr,且能够缩小dir/dt,由此能够降低寄生NPN型晶体管动作的可能性。

[0088] 这里,参照图9,对本实施方式的半导体装置的更理想形态进行说明。

[0089] 图9是第1实施方式的半导体装置的俯视图。

[0090] 第1绝缘部分30a在X方向上与多个绝缘部20相隔。在绝缘部30仅具有第1绝缘部分30a的情况下,有如下可能性:储存在绝缘部20彼此之间的电洞如图9的箭头A1所示,流经绝

缘部20与绝缘部30的间隙，而流到p<sup>+</sup>型接触区域4。因此，有流经绝缘部20与30的间隙的电洞集中流到部分p<sup>+</sup>型接触区域4，从而寄生NPN型晶体管动作的可能性。

[0091] 通过使绝缘部30除了第1绝缘部分30a以外还具有第2绝缘部分30b，能够减少如箭头A1所示在绝缘部20与30的间隙而朝向-Y方向流动的电洞。因此，能够抑制电洞集中流到部分p<sup>+</sup>型接触区域4，从而能够更进一步降低寄生NPN型晶体管动作的可能性。

[0092] 而且，在反向恢复动作时，n<sup>-</sup>型半导体区域1的电位高于p型基极区域2的电位，也高于与源极电极51连接的FP电极41A的电位。因此，通过在绝缘部20及30与栅极电极12A之间设置FP电极41A，能够利用FP电极41A来捕获在反向恢复时通过FP电极41A附近的电洞。由此，能够减少电荷Qrr，从而能够进一步降低寄生NPN型晶体管动作的可能性。

[0093] (第1变化例)

[0094] 图10是表示第1实施方式的第1变化例的半导体装置110的一部分的俯视图。

[0095] 在图10中，用虚线表示源极电极51及栅极垫片52，并省略绝缘层45及各半导体区域。

[0096] 在图2～图4所示的半导体装置100中，栅极电极12在Y方向上延伸，绝缘部20在X方向上延伸。与此相对地，在本变化例的半导体装置110中，栅极电极12、绝缘部20都在Y方向上延伸。

[0097] 在半导体装置110中，与半导体装置100同样地，多个绝缘部20设置在栅极垫片52之下。另外，绝缘部30的第2绝缘部分30b在Y方向上，设置在多个栅极电极12B与多个绝缘部20之间。

[0098] 因此，根据本变化例，能够与半导体装置100同样地，减少二极管动作时的电洞的储存量及反向恢复动作时的电洞的排出量。

[0099] 另外，在如下方面也相同，即，通过使绝缘部30还具有在Y方向上延伸的第1绝缘部分30a，能够减少流经绝缘部20与第2绝缘部分30b的间隙的电洞。

[0100] 但是，在栅极电极12与绝缘部20相互沿着不同方向延伸的情况下，当储存在绝缘部20彼此之间的电洞沿着绝缘部20流向源极电极51时，该电洞流的移动会受到栅极电极12的阻碍。因此，在栅极电极12与绝缘部20相互沿着不同方向延伸的情况下，和栅极电极12与绝缘部20沿着相同方向延伸的情况相比，能够使电荷Qrr减少，从而能够进一步降低寄生NPN型晶体管动作的可能性。

[0101] (第2变化例)

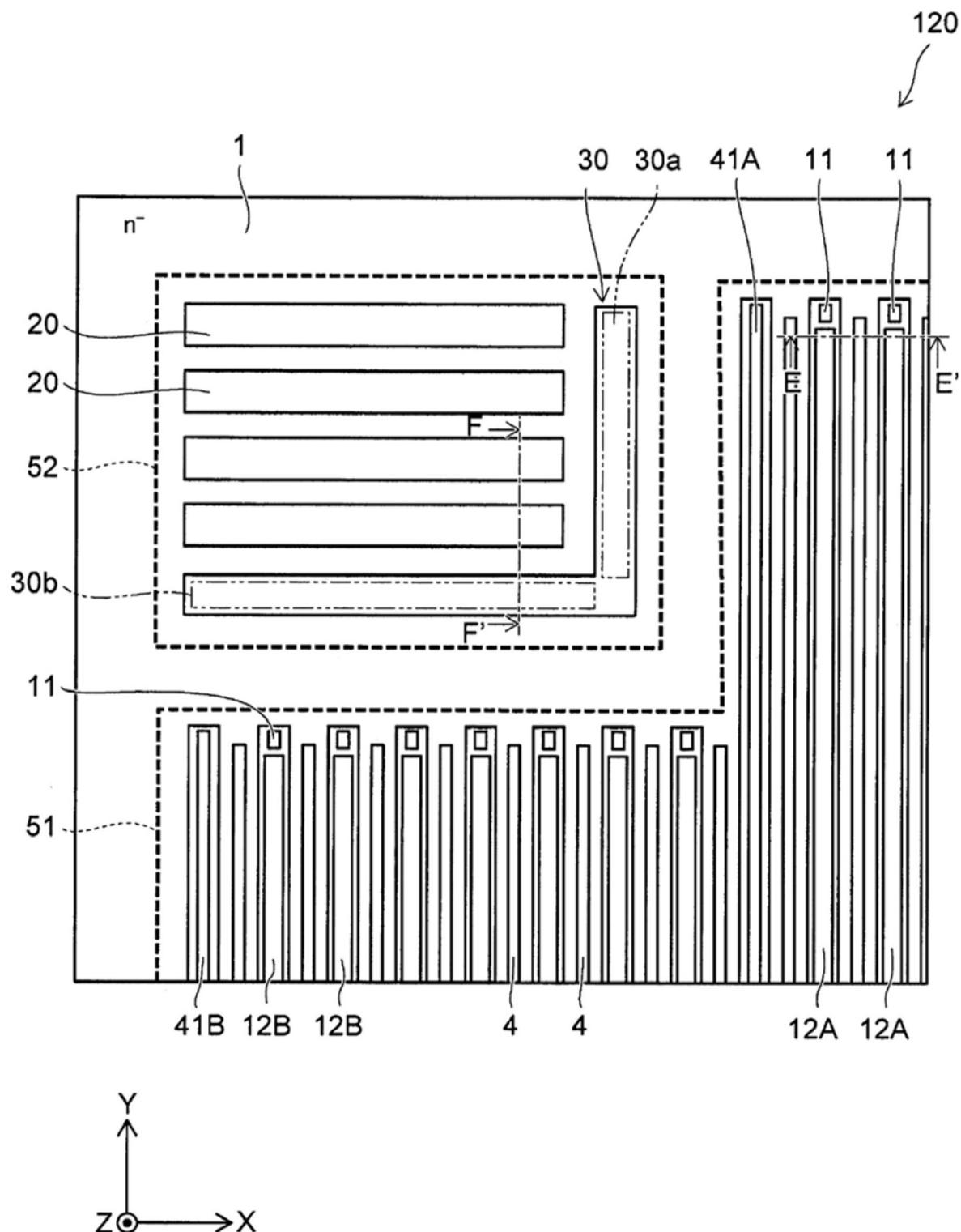

[0102] 图11是表示第1实施方式的第2变化例的半导体装置120的一部分的俯视图。

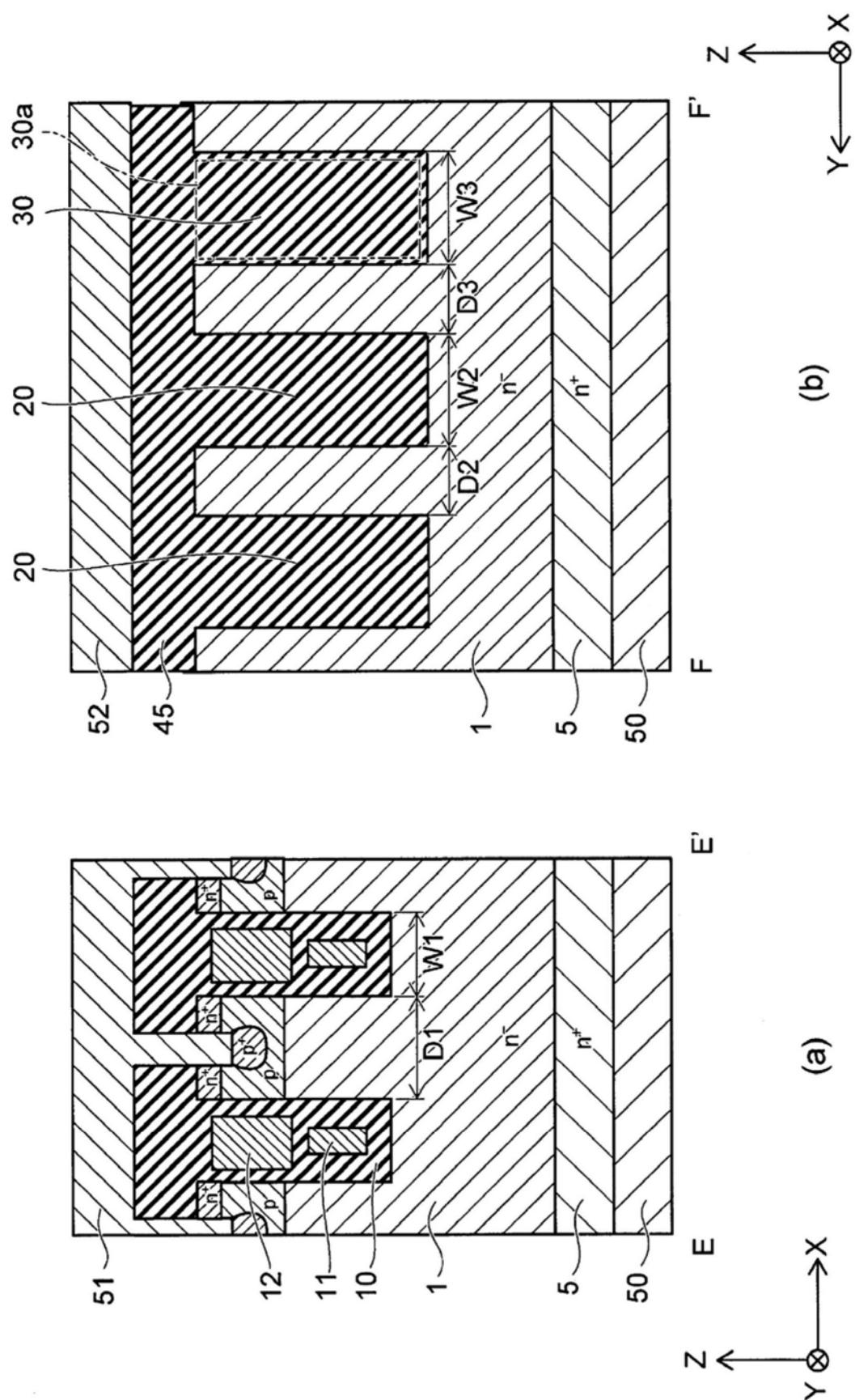

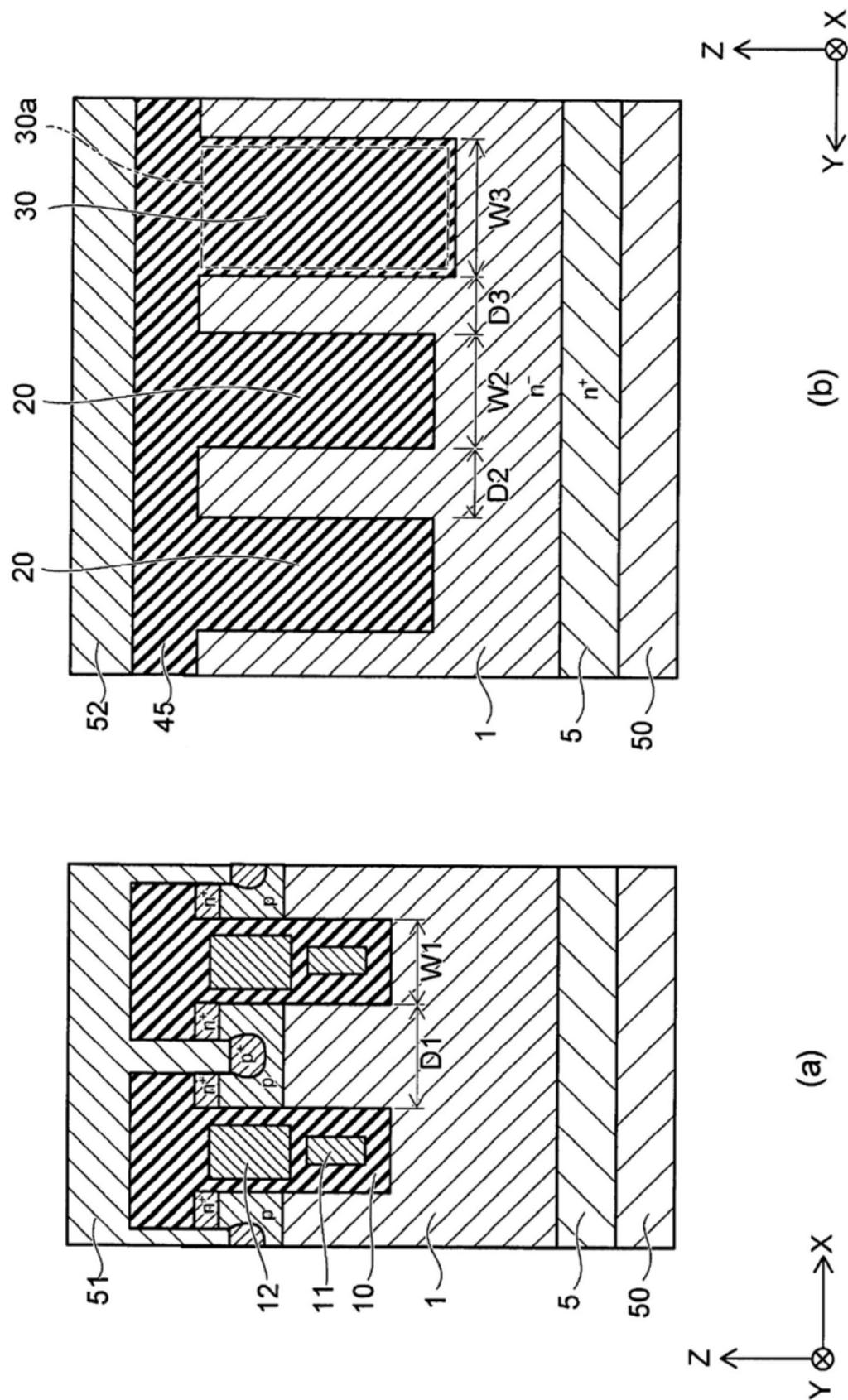

[0103] 图12(a)是图11的E-E'剖视图，图12(b)是图11的F-F'剖视图。

[0104] 图13是表示第1实施方式的第2变化例的半导体装置120的另一例的局部放大剖视图。

[0105] 另外，在图11中，用虚线表示源极电极51及栅极垫片52，并省略绝缘层45及各半导体区域。

[0106] 在本变化例的半导体装置120中，如图11所示，栅极电极12与绝缘部20相互沿着不同方向延伸。而且，如图12所示，绝缘部20的宽度W2及绝缘部30的宽度W3比绝缘部10的宽度W1宽。

[0107] 另外，这里所说的宽度表示与各个绝缘部的延伸方向垂直的方向上的、各绝缘部

的长度。

[0108] 绝缘部20彼此之间的距离D2及绝缘部20与30之间的距离D3比绝缘部10彼此之间的距离D1短。而且，绝缘部20的下端及绝缘部30的下端设置得比绝缘部10的下端靠下方。

[0109] 通过使宽度W2及宽度W3比宽度W1宽，并使距离D2及距离D3比距离D1短，而与半导体装置100相比，能够减小栅极垫片52之下的n<sup>-</sup>型半导体区域1的体积，从而减少储存在栅极垫片52之下的电洞量。

[0110] 另外，通过使绝缘部20的下端及绝缘部30的下端设置得比绝缘部10的下端靠下方，能够进一步减小栅极垫片52之下的n<sup>-</sup>型半导体区域1的体积，从而能够减少图8所示的电荷Qrr。此外，因直到储存在绝缘部20彼此之间的电洞从源极电极51排出为止的时间变得更长，所以能够进一步缩小dir/dt。

[0111] 即，根据本变化例的半导体装置120，与半导体装置100相比，能够进一步降低寄生NPN型晶体管动作的可能性。

[0112] 另外，也可如图13所示，使绝缘部30的宽度W3比宽度W2宽，并使距离D3比距离D2短。另外，也可使绝缘部30的下端的位置比绝缘部20的下端的位置深。通过这样设置，能够更进一步地减少栅极垫片52下的电洞的储存量及朝向源极电极51的电洞的排出量，从而能够降低寄生NPN型晶体管动作的可能性。

[0113] (第3变化例)

[0114] 图14是表示第1实施方式的第3变化例的半导体装置130的一部分的俯视图。

[0115] 图15是图14的G-G'剖视图。

[0116] 另外，在图14中，用虚线表示源极电极51及栅极垫片52，并省略绝缘层45及各半导体区域。

[0117] 半导体装置130在还包括导电部21及导电部31这一点上，与半导体装置100不同。导电部21设置在绝缘部20中，导电部31设置在绝缘部30中。

[0118] 导电部21沿着绝缘部20在X方向上延伸。

[0119] 导电部31具有第1导电部分31a及第2导电部分31b。第1导电部分31a设置在第1绝缘部分30a中，且在Y方向上延伸。第2导电部分31b设置在第2绝缘部分30b中，且在X方向上延伸。

[0120] 导电部21及31与源极电极51及栅极垫片52电分离，这些导电部的电位是浮动的。

[0121] 在本变化例的半导体装置130中，也与半导体装置100同样地，能够减少电荷Qrr及dir/dt，从而能够降低寄生NPN型晶体管动作的可能性。

[0122] 而且，通过将导电部21及31与源极电极51及栅极垫片52电分离，能够抑制源极电极51的电容及栅极垫片52的电容增加，从而能够抑制半导体装置的切换速度降低。

[0123] 另外，这里，对在半导体装置100中设置着导电部21及31的情况进行了说明，但本变化例并不限于此。例如，也可在半导体装置110或120的绝缘部20中及绝缘部30中设置导电部21及31。

[0124] (第2实施方式)

[0125] 图16是表示第2实施方式的半导体装置200的一部分的俯视图。

[0126] 图17是图16的H-H'剖视图。

[0127] 另外，在图16中，用虚线表示源极电极51及栅极垫片52，并省略绝缘层45及各半

体区域。

[0128] 关于半导体装置200设置在栅极垫片52之下的绝缘部的构造来讲,与半导体装置100不同。

[0129] 如图16及图17所示,半导体装置200中,在栅极垫片52之下,设置着绝缘部22(第2绝缘部)、24(第3绝缘部)及26。绝缘部22、24及26分别设定为环状,且包围n<sup>-</sup>型半导体区域1的一部分。绝缘部24设置在绝缘部22的内侧,绝缘部26设置在绝缘部24的内侧。

[0130] 在将沿着指定方向延伸的多个绝缘部设置在栅极垫片52之下的情况下,有电洞通过绝缘部彼此的间隙而在栅极垫片52下的区域与源极电极51之间移动的可能性。

[0131] 针对此,通过如本实施方式的半导体装置200这样,在栅极垫片52之下设置环状的绝缘部,能够进一步抑制栅极垫片52下的区域与源极电极51之间的电洞的移动。因此,根据本实施方式,与第1实施方式的半导体装置相比,能够使图8所示的dir/dt更小,从而能够进一步降低寄生NPN型晶体管动作的可能性。

[0132] 另外,设置在栅极垫片52之下的环状的绝缘部的数量既可少于也可多于图16所示的例子。绝缘部的数量任意,可适当变更。

[0133] (第1变化例)

[0134] 图18是表示第2实施方式的第1变化例的半导体装置210的一部分的剖视图。

[0135] 半导体装置210在还包括导电部23、25及27这一点上,与半导体装置200不同。

[0136] 如图18所示,导电部23、25及27分别设置在绝缘部22、24及26之中。导电部23、25及27分别设定为环状,且包围n<sup>-</sup>型半导体区域1的一部分。

[0137] 导电部23、25及27与源极电极51及栅极垫片52电分离,这些导电部的电位是浮动的。

[0138] 在本变化例中,也与半导体装置200同样地,能够减少电荷Qrr及dir/dt,从而能够降低寄生NPN型晶体管动作的可能性。

[0139] 而且,通过将导电部23、25及27与源极电极51及栅极垫片52电分离,能够抑制源极电极51的电容及栅极垫片52的电容增加,从而能够抑制半导体装置的切换速度降低。

[0140] (第2变化例)

[0141] 图19是表示第2实施方式的第2变化例的半导体装置220的一部分的剖视图。

[0142] 半导体装置220就绝缘部22、24及26的构造来讲,与半导体装置200不同。

[0143] 如图19所示,绝缘部22的宽度W2比绝缘部24的宽度W3宽,宽度W3比绝缘部26的宽度W4宽。宽度W2例如与绝缘部10的宽度相同,或比之宽。

[0144] 绝缘部22与24之间的距离D2比绝缘部24与26之间的距离D3窄。距离D3比绝缘部10彼此之间的距离D1窄。而且,绝缘部22的下端的位置比绝缘部24的下端的位置深,绝缘部24的下端的位置比绝缘部26的下端的位置深。绝缘部26的下端的位置例如与绝缘部10的下端的位置相同,或比之深。

[0145] 即,绝缘部22、24及26越往外侧,宽度越宽,下端的位置越深。通过加宽外侧的绝缘部的宽度,并加深下端的位置,与半导体装置200相比,能够进一步抑制栅极垫片52下的区域与源极电极51之间的电洞的移动,从而能够减小dir/dt。因此,根据本变化例,能够进一步降低寄生NPN型晶体管动作的可能性。

[0146] 另外,在半导体装置220中,也与半导体装置210同样地,可在绝缘部22、24及26中

分别设置导电部23、25及27。

[0147] 对于以上所说明的各实施方式中的、各半导体区域之间的杂质浓度的相对的高低,例如,能使用SCM(扫描型静电电容显微镜)加以确认。另外,各半导体区域中的载流子浓度可看作与在各半导体区域中活化的杂质浓度相等。因此,对于各半导体区域之间的载流子浓度的相对的高低,也能够使用SCM加以确认。

[0148] 而且,对于各半导体区域中的杂质浓度,例如能够通过SIMS(二次离子质量分析法)加以测定。

[0149] 以上,已对本发明的若干实施方式进行了说明,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些新颖的实施方式能够以其他各种方式加以实施,且能够在不脱离发明主旨的范围内,进行各种省略、替换、变更。关于实施方式中所包含的、例如n<sup>-</sup>型半导体区域1、p型基极区域2、n<sup>+</sup>型源极区域3、p<sup>+</sup>型接触区域4、n<sup>+</sup>型漏极区域5、绝缘部10、场板电极11、栅极电极12、绝缘部20、22、24及26、导电部21、23、25及27、绝缘部30、导电部31、绝缘部40、场板电极41、绝缘层45、漏极电极50、源极电极51、及栅极垫片52等各要素的具体构成,本领域技术人员能够从公知的技术中加以适当选择。这些实施方式及其变形包含在发明的范围及主旨内,且包含在权力要求书所记载的发明及其均等的范围内。而且,所述各实施方式能够相互组合而实施。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19