(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5991018号

(P5991018)

(45) 発行日 平成28年9月14日(2016.9.14)

(24) 登録日 平成28年8月26日(2016.8.26)

(51) Int.Cl.

F 1

|                    |                  |      |       |      |

|--------------------|------------------|------|-------|------|

| <b>H01L 21/338</b> | <b>(2006.01)</b> | H01L | 29/80 | H    |

| <b>H01L 29/778</b> | <b>(2006.01)</b> | H01L | 29/80 | F    |

| <b>H01L 29/812</b> | <b>(2006.01)</b> | H01L | 29/80 | E    |

| <b>H01L 27/095</b> | <b>(2006.01)</b> | H01L | 29/78 | 301B |

| <b>H01L 21/336</b> | <b>(2006.01)</b> |      |       |      |

請求項の数 11 (全 23 頁) 最終頁に続く

(21) 出願番号

特願2012-112033 (P2012-112033)

(22) 出願日

平成24年5月16日(2012.5.16)

(65) 公開番号

特開2013-239605 (P2013-239605A)

(43) 公開日

平成25年11月28日(2013.11.28)

審査請求日

平成27年1月28日(2015.1.28)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100080160

弁理士 松尾 憲一郎

(74) 代理人 100149205

弁理士 市川 泰央

(72) 発明者 光永 将宏

福岡県福岡市早良区百道浜2丁目3番2号

ソニーセミコンダクタ株式会社内

審査官 小川 将之

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ピエゾ分極を起こす半導体である  $In_xGa_{1-x}P$  ( $x = 0 . 5 1$ ) にて形成されたバッファ層と、

前記バッファ層の上に  $GaAs$  を積層して形成されたチャネル層と、

を備え、

前記チャネル層においては、前記バッファ層のピエゾ分極により前記バッファ層の厚さに応じた数で当該チャネル層に生じる2次元ホールガスをキャリアとし、

前記チャネル層の半導体には、濃度が  $1 \times 10^{17} \text{ atoms/cm}^3$  以下の C、Zn、又は Be を不純物としてドープしてあり、

前記バッファ層の半導体には、濃度が  $1 \times 10^{12} \sim 4 \times 10^{18} \text{ atoms/cm}^3$  の C、Zn、又は Be を不純物としてドープしてある半導体装置。

## 【請求項 2】

前記チャネル層は、価電子帯のエネルギーレベルが前記バッファ層よりも高い半導体にて形成されている請求項 1 に記載の半導体装置。

## 【請求項 3】

前記バッファ層は、互いに格子整合する複数の半導体層にて形成されており、

これら複数の半導体層のうち、前記チャネル層に隣接して設けられる半導体層は、前記ピエゾ分極を起こす半導体で形成されている請求項 1 又は請求項 2 に記載の半導体装置。

## 【請求項 4】

10

20

前記チャネル層は、前記ピエゾ分極を起こす半導体と格子整合する半導体を1回以上積層して形成してある請求項1～請求項3の何れか1項に記載の半導体装置。

**【請求項5】**

前記バッファ層は、化合物半導体基板の上に積層されており、

前記バッファ層と前記化合物半導体基板の間には、前記バッファ層の半導体と前記化合物半導体基板の半導体の双方に格子整合する半導体層であって、前記バッファ層の半導体と前記化合物半導体基板の半導体の双方とバンドギャップが異なる少なくとも1層の半導体層を積層してある請求項1～請求項4の何れか1項に記載の半導体装置。

**【請求項6】**

前記チャネル層の上に積層されたn型半導体により形成したゲートを備える請求項1～請求項5の何れか1項に記載の半導体装置。

10

**【請求項7】**

前記チャネル層にn型の不純物を拡散することにより形成したゲートを備える請求項1～請求項5の何れか1項に記載の半導体装置。

**【請求項8】**

前記チャネル層に接合されたショットキーメタルにより形成したゲートを備える請求項1～請求項5の何れか1項に記載の半導体装置。

**【請求項9】**

前記チャネル層上に積層したゲート酸化膜にショットキーメタルを接合して形成したゲートを備える請求項1～請求項5の何れか1項に記載の半導体装置。

20

**【請求項10】**

請求項1～請求項9の何れか1項に記載の半導体装置とn型電界効果トランジスタを同じ化合物半導体基板上に形成した相補型半導体装置。

**【請求項11】**

請求項1～請求項9の何れか1項に記載の半導体装置を用いて作成されたレベルシフト回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本技術は、バッファ層のピエゾ分極によりチャネル層に発生する2次元ホールガスを当該チャネル層のキャリアとして用いる技術に関する。

30

**【背景技術】**

**【0002】**

GaAsなどの化合物半導体層を有する化合物半導体系の電界効果トランジスタ(FET)は、電子移動度が高いため、nチャネルにおける周波数特性が良好である。現在、高周波数帯に用いられるnチャネルを用いたFETには、HEMTやJPHEMTなどがある(例えば、特許文献1参照)。HEMTは高電子移動度トランジスタの略であり、JPHEMTは接合型・擬似格子整合高電子移動度トランジスタの略である。

**【0003】**

HEMTは、半導体ヘテロ接合界面に誘起された高移動度の二次元電子ガスをチャネルとしたFETであり、JPHEMTは、ある程度の格子不整合を許容することによりHEMTよりも高い電子移動度を実現したFETであり、JPHEMTは、ゲート部にpn接合を使ってゲートの順方向電圧(ターンオン電圧)を向上させたFETである。

40

**【0004】**

このようなnチャネルを用いたFETとしては、電子供給層と電子走行層との自発分極とピエゾ分極とにより、電子供給層と電子走行層のヘテロ接合界面の電子走行層の側に発生する2次元電子ガスをキャリアとして用いるものがある(例えば、特許文献2,3参照)。

**【先行技術文献】**

**【特許文献】**

50

## 【0005】

【特許文献1】特開平11-150264号公報

【特許文献2】特開2010-074077号公報

【特許文献3】特開2010-045343号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

上述したように、nチャネルFETの高性能化が進んでいる。これに加えて、素子の高集積化のため、化合物半導体を用いた相補型（コンプリメンタリ）素子の開発が要望されている。すなわち、p型チャネルFETにおいても、キャリアの高移動度とゲートの低いオン抵抗を実現する必要がある。10

## 【0007】

ここで、エピタキシャル成長により積層されたエピタキシャル基板を選択的にエッチングして作成するpチャネルFETは、ホールを供給するために、CやZn等の不純物を添加する必要がある。しかしながら、一般に、この不純物が多いほどキャリアの移動度が低下するという関係があるため、pチャネルFETにおいて、キャリアの高移動度とゲートの低いオン抵抗を実現することは困難であった。

## 【0008】

本技術は、上記課題に鑑みてなされたもので、エピタキシャル基板を選択的にエッチングして作成するpチャネルFETにおけるキャリアの高移動度とゲートの低いオン抵抗を実現し、素子の高集積化を実現することが可能な半導体装置を提供することを目的とする。20

## 【課題を解決するための手段】

## 【0009】

本技術に係る半導体装置は、ピエゾ分極を起こす半導体であるIn<sub>x</sub>Ga<sub>1-x</sub>P（x=0.51）にて形成されたバッファ層と、前記バッファ層の上にGaAsを積層して形成されたチャネル層と、を備え、前記チャネル層においては、前記バッファ層のピエゾ分極により前記バッファ層の厚さに応じた数で当該チャネル層に生じる2次元ホールガスをキャリアとし、前記チャネル層の半導体には、濃度が1×10<sup>17</sup>atoms/cm<sup>3</sup>以下のC、Zn、又はBeを不純物としてドープしており、前記バッファ層の半導体には、濃度が1×10<sup>12</sup>~4×10<sup>18</sup>atoms/cm<sup>3</sup>のC、Zn、又はBeを不純物としてドープしてある構成としてある。30

## 【0010】

なお、本技術に係る半導体装置は、他の装置に組み込まれた状態で実施されたり他の方法とともに実施されたりする等の各種の態様を含む。また、本技術は前記半導体装置を備える各種システム、上述した装置の製造方法、上述した装置の製造方法をコンピュータに実現させるプログラム、該プログラムを記録したコンピュータ読み取り可能な記録媒体、等としても実現可能である。

## 【発明の効果】

## 【0011】

本技術によれば、ホールをキャリアとして用いた半導体装置において、アンドープにおいてもヘテロ界面に高濃度のキャリアが発生するため、キャリア（ホール）移動度を向上できる。これにより、ホールをキャリアとして用いた半導体装置について、高いキャリア濃度、高いキャリアの飽和速度、比較的高い絶縁破壊電圧を実現でき、低いオン抵抗、高速動作、高耐圧を実現できる。40

## 【図面の簡単な説明】

## 【0012】

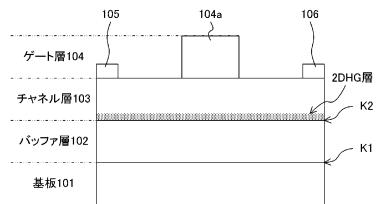

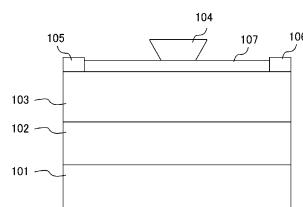

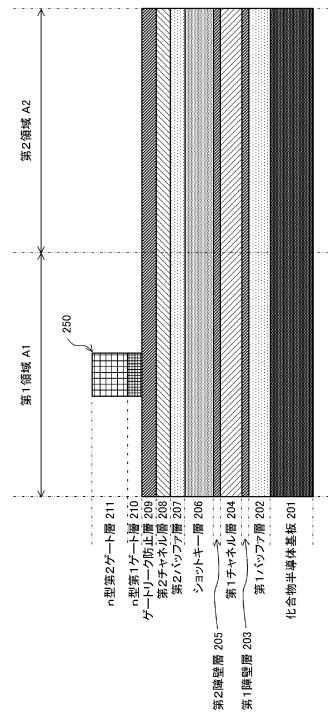

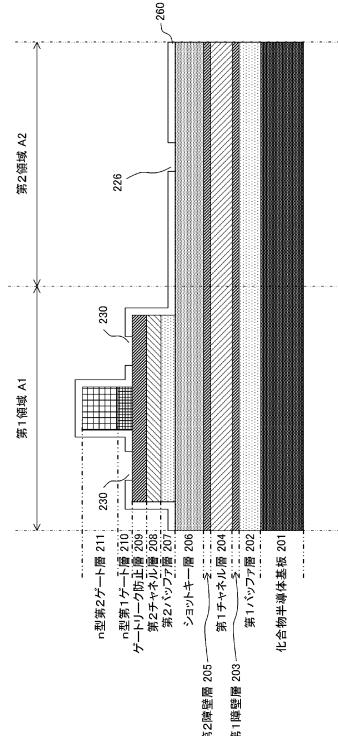

【図1】第1実施形態に係る半導体装置の断面構成の1例を示す図である。

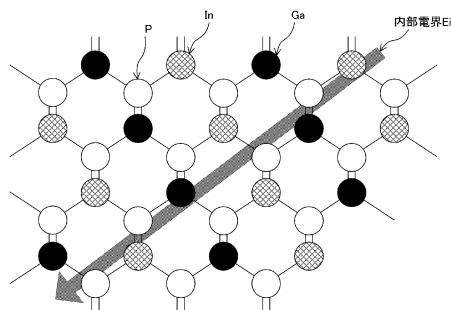

【図2】バッファ層の結晶構造を模式的に示した図である。

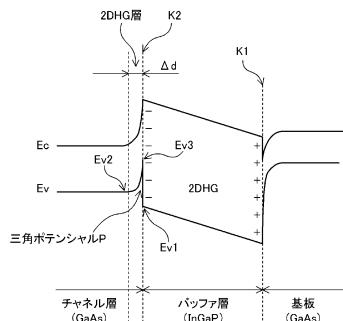

【図3】半導体装置のバンド構造を説明する図である。50

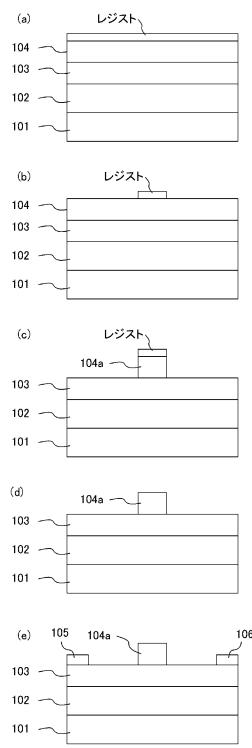

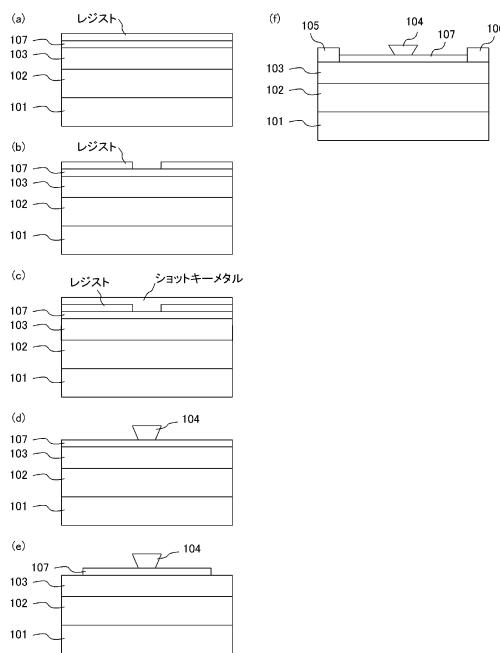

【図4】図1に係るゲート部の作成方法を説明する図である。

【図5】不純物拡散により形成したゲート部を説明する図である。

【図6】図5に係るゲート部の作成方法を説明する図である。

【図7】ショットキーメタルの蒸着により形成したゲート部を説明する図である。

【図8】図7に係るゲート部の作成方法を説明する図である。

【図9】酸化膜を介したショットキーメタルの蒸着により形成したゲート部を説明する図である。

【図10】図9に係るゲート部の作成方法を説明する図である。

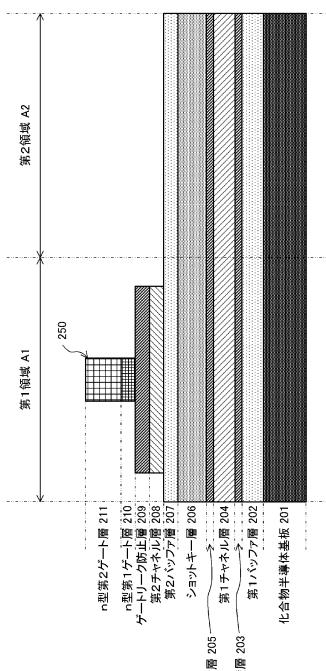

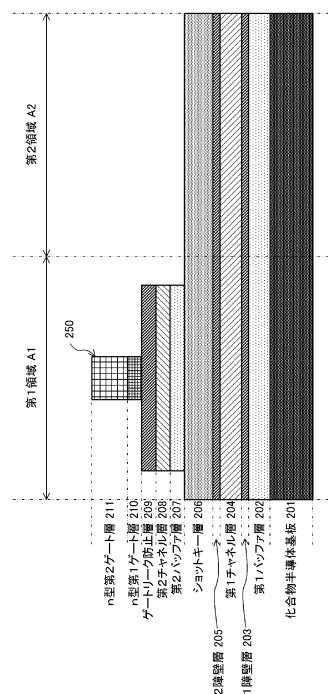

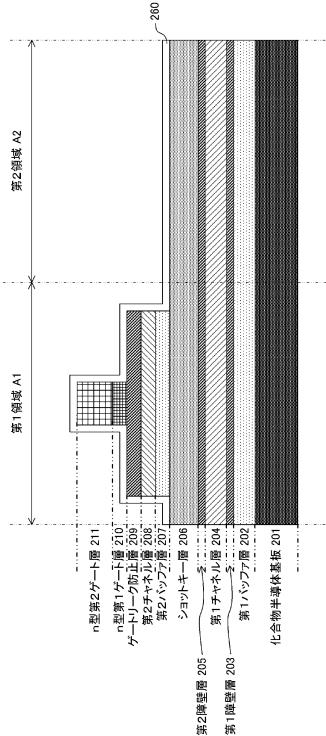

【図11】第2実施形態に係る半導体装置の断面構成の1例を示す図である。

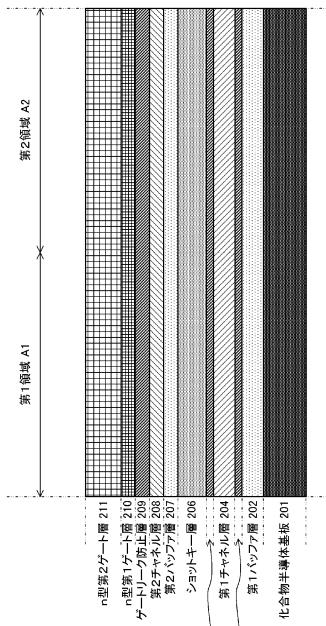

【図12】第2実施形態に係る半導体装置の作成方法を説明する図である。

10

【図13】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図14】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図15】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図16】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図17】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図18】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図19】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図20】第2実施形態に係る半導体装置の作成方法を説明する図である。

【図21】第2実施形態に係る半導体装置の作成方法を説明する図である。

【発明を実施するための形態】

20

【0013】

以下、下記の順序に従って本技術を説明する。

(1) 半導体装置の第1実施形態の構成：

(2) 半導体装置の第2実施形態の構成：

(3) 第2実施形態に係る半導体装置の製造方法：

(4) まとめ：

【0014】

(1) 半導体装置の第1実施形態の構成：

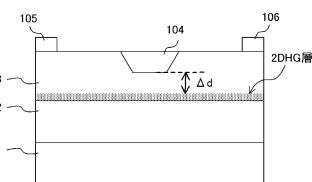

図1は、第1実施形態に係る半導体装置100の断面構成の1例を示す図である。同図に示す半導体装置100は、化合物半導体系のp型チャネル電界効果トランジスタ(以下、pFETと略す)を含む半導体装置である。

30

【0015】

半導体装置100としてのpFETは、化合物半導体のGaaS単結晶で作成された化合物半導体基板としての基板101の上に、エピタキシャル成長により形成されたエピタキシャル結晶成長層を選択的にエッチングすることにより作成してある。エピタキシャル結晶成長層は、基板101側から順に、バッファ層102、チャネル層103、及びゲート層104を積層してある。以下、各層について説明する。

【0016】

バッファ層102は、基板101上に形成され、エピタキシャル成長時に基板101とのヘテロ接合界面K1において格子整合する半導体で形成されている。ここで、格子整合とは、接合面に不整合転移等が入ることなく成長することを言い、不整合転移が入る前の臨海膜厚以下で半導体層を成長した場合の疑似格子整合であってもよい。このように、基板101とバッファ層102を格子整合させることにより、エピタキシャル成長にてバッファ層102を基板101上に形成することができる。

40

【0017】

なお、バッファ層102と基板101の間には、バッファ層102の半導体と基板101の半導体の双方に格子整合する半導体層であって、バッファ層102の半導体と基板101の半導体の双方とバンドギャップが異なる少なくとも1層の半導体層を積層してもよい。このようにバッファ層102と基板101の間に半導体層を介在させることにより、バンドギャップを大きくして耐圧を向上することができる。

50

**【0018】**

例えば、バッファ層102と基板101の間には、GaAlInPの4元混晶などを積層することが出来る。このGaAlInPのバンドギャップは、1.9~2.3eVであり、pFETの耐圧を向上することが出来る。

**【0019】**

また、バッファ層102の膜厚は、10~1000nmとし、より好適には250nm~1000nmとする。このような膜厚にバッファ層102を制御することにより、FETの耐圧を向上することができる。なお、バッファ層102の膜厚については、膜厚を厚くするほどpFETの耐性が向上する。

**【0020】**

また、バッファ層102は、GaAs基板上に形成したときにピエゾ分極が生じる半導体にて形成されている。ピエゾ分極とは、結晶構造に起因した局所的な歪みによるピエゾ効果と、陽イオンと陰イオンの電荷不均衡に起因して、巨視的に発生する自発分極である。このピエゾ分極により、バッファ層102には、マクロには一定方向の内部電界が生じる。

**【0021】**

内部電界は、本実施形態に係る半導体装置100においては、少なくとも、基板101からチャネル層103に向かう方向のベクトル成分を有する。より具体的には、このベクトル成分が、バッファ層102の内部電界のベクトルにおいて支配的である。これにより、バッファ層102は、基板101とのヘテロ接合界面K1には正に帯電し、チャネル層103とのヘテロ接合界面K2は負に帯電する。このようなピエゾ分極を生じる半導体としては、InGaPが例示される。なお、バッファ層102に用いるInGaPは、不純物を添加したものであってもよいし、不純物を添加したものであってもよい。

**【0022】**

図2は、GaAs基板上にエピタキシャル成長したInGaPにおけるピエゾ分極を説明する図である。同図に示すように、GaAs基板の(001)結晶面上にInGaPをエピタキシャル成長させると、<111>方向に自然超格子構造が形成される。このInGaP自然超格子構造は、閃亜鉛構造における<111>方向に、オーダリングベクトルを有している。

**【0023】**

このため、InGaPの結晶構造が立方晶系から三方晶系へと変化し、その結果、Ga-PとIn-Pのボンド長の違いによる局所的な歪みに起因したピエゾ効果と、陽イオンと陰イオンの電荷不均衡に起因した自発分極が発生する。このとき、図3に示すように、エピタキシャル結晶成長層内で、<111>方向にマクロな内部電界が誘発される。すなわち、バッファ層102には、基板101からチャネル層103へ向かう内部電界Eiが生じる。

**【0024】**

なお、バッファ層102にInGaPを用いる場合、インジウム(In)の組成比は、In<sub>x</sub>Ga<sub>1-x</sub>Pとすると、x=0.51とする。この組成比を採用することにより、バッファ層102のInGaPと基板101のGaAsとの間、及び、バッファ層102のInGaPと後述するチャネル層のGaAsとの間で格子整合しつつ、大きなピエゾ分極を生じさせることができる。

**【0025】**

バッファ層102の上には、pFETの主電流が流れる半導体層としてのチャネル層103が形成してある。チャネル層103は、エピタキシャル成長時にバッファ層102と格子整合する半導体で形成されている。このようにバッファ層102とチャネル層103を格子整合させることにより、エピタキシャル成長によりチャネル層103をバッファ層102の上に形成することができる。

**【0026】**

また、チャネル層103は、価電子帯のエネルギーレベルがバッファ層102に比べて

10

20

30

40

50

高い半導体を用いて形成してある。従って、ヘテロ接合界面K2には、チャネル層103の側からバッファ層102の側へのホールの移動を規制するポテンシャル障壁が形成される。

#### 【0027】

また、ヘテロ接合界面K2の価電子帯のエネルギーレベルは、バッファ層102の側のヘテロ接合界面K2近傍の価電子帯のエネルギーレベルや、チャネル層103の側のヘテロ接合界面K2の価電子帯のエネルギーレベルに比べて、高くなっている。このため、ヘテロ接合界面K2の価電子帯のエネルギーレベルは、不連続又は急峻に変化することになり、価電子帯には、ヘテロ接合界面K2において、ホール閉じ込め効果を有する上に凸の三角ポテンシャルが形成される。10

#### 【0028】

ここで、チャネル層103において発生するホールは、上述したバッファ層102の内部電界によってヘテロ接合界面K2に引き寄せられるが、このホールはヘテロ接合界面K2のチャネル層103の側の近傍に形成される三角ポテンシャルに閉じ込められて量子化する。これにより、ヘテロ接合界面K2のチャネル層103の側の近傍には、2次元ホールガス層(2DHG層)が形成される。

#### 【0029】

以上の条件を満たすチャネル層103の材料としては、バッファ層102としてInGaPを採用した場合、このInGaPと格子整合する半導体であり、例えば、GaAs、InGaAs、AlGaAs、InGaAsP、及びこれらを適宜に組み合わせたものが例示される。また、チャネル層103には、 $1 \times 10^{17} \text{ atoms/cm}^3$ 以下の不純物を添加してもよく、チャネル層103の膜厚は、30~150nmとする。より好適には、チャネル層103の膜厚は、50~100nmとする。このような膜厚にチャネル層103を制御することにより、pFETのエンハンスメント動作を保証することができる。20

#### 【0030】

図3は、半導体装置100のバンド構造を説明する図である。同図に示す例では、不純物を添加していないInGaPでバッファ層102を形成し、不純物を添加していないGaAsでチャネル層103を形成してある。このとき、価電子帯のエネルギーレベルは、バッファ層102のエネルギーレベルEv1に比べて、チャネル層103のエネルギーレベルEv2の方が高くなっている。30

#### 【0031】

また、バッファ層102とチャネル層103のヘテロ接合界面K2における価電子帯のエネルギーレベルEv3は、バッファ層102における価電子帯のエネルギーレベルEv1やチャネル層103における価電子帯のエネルギーレベルEv2に比べて高くなっている。このため、ヘテロ接合界面K2のバッファ層102の側では、エネルギーレベルEv1とエネルギーレベルEv3との間で価電子帯のエネルギーレベルが不連続になっている。

#### 【0032】

一方、ヘテロ接合界面K2のチャネル層103の側では、価電子帯のエネルギーレベルは連続的に変化するものの、ヘテロ接合界面K2の近傍(図では所定距離dの範囲内)において、エネルギーレベルがEv3からEv2へと急峻に低下している。このため、チャネル層103側のヘテロ接合界面K2の近傍には、ホールをトラップする上に凸の三角ポテンシャルPが形成される。この三角ポテンシャルPは、エネルギーレベルが高くなるほど幅狭になっている。40

#### 【0033】

ここで、チャネル層103において発生するホールは、上述したように、バッファ層102の内部電界Eiによりヘテロ接合界面K2に引き寄せられる傾向にあり、このようにして引き寄せられたホールは三角ポテンシャルPにトラップされる。そして、幅狭の三角ポテンシャルPにトラップされたホールは量子化し、ヘテロ接合界面K2のチャネル層1

10

20

30

40

50

03の側に2DHG層を形成することになる。

#### 【0034】

ここで、2DHG層の2次元ホールガスの密度は、バッファ層102としてInGaPを採用し、チャネル層103としてGaAsを採用し、バッファ層の膜厚を10~100nmとし、チャネル層の膜厚を30~150nmとしたとき、 $1 \times 10^{17} \sim 1 \times 10^{18}$  atoms/cm<sup>3</sup>であった。これは、従来のHEMTと同等もしくはそれ以上である。すなわち、従来の一般的なHEMT構造作成の際のような不純物の変調ドープを行わずに、従来のHEMTと同等もしくはそれ以上の2DHGが発生していることが分かる。

#### 【0035】

このような第1実施形態に係る半導体装置100によれば、不純物の拡散による不純物散乱の影響等が存在しないため、非常に大きなホール移動度が得られる。従って、第1実施形態に係る半導体装置100は、高いキャリア濃度、高いキャリアの飽和速度、比較的高い絶縁破壊電圧が実現され、結果として、低いオン抵抗、高速動作、高耐圧を実現できる。

#### 【0036】

なお、チャネル層103の半導体には、濃度が $1 \times 10^{17}$  atoms/cm<sup>3</sup>以下であればC、Zn、又はBeを不純物としてドープしてもよく、また、バッファ層102の半導体には、濃度が $1 \times 10^{12} \sim 4 \times 10^{18}$  atoms/cm<sup>3</sup>であればC、Zn、又はBeを不純物としてドープしてもよい。一般に、不純物の濃度が $1 \times 10^{17}$  atoms/cm<sup>3</sup>以上になると、キャリアである正孔の移動度が急激に低下することが知られているが、上述した濃度の範囲内の不純物であれば、チャネル層103における正孔の移動度を低下させることなく、正孔の濃度を更に高めることが出来る。

#### 【0037】

また、本願の発明者が行った実験によれば、チャネル層103に発生する2次元ホールの量は、チャネル層103の厚みが大きいほど多くなる傾向があった。従って、バッファ層102の厚みを大きくすると、チャネル層103に発生させるキャリア数が多くなり、バッファ層102の厚みを小さくすれば、チャネル層103に発生させるキャリア数が少なくなることになる。すなわち、バッファ層102の厚みを調整することにより、チャネル層103に生じる2次元ホールガスの量を調整することが出来る。

#### 【0038】

また、バッファ層102は、InGaP層の間に他種の半導体層を挟んで積層させた複数の半導体層で形成されても良い。InGaP層以外の半導体層には、InGaPよりも価電子エネルギーが高く、InGaP層と格子整合する材料で形成された半導体層を用いる。このような材料としては、GaAs、InGaAs、AlGaAs、InGaAsP、及びこれら材料を複合したもの等が例示される。なお、バッファ層102を複数の半導体層で形成する場合は、少なくとも、チャネル層103と接合される層については、ピエゾ分極する半導体としてのInGaP層とする。これにより、バッファ層102のピエゾ分極によって2次元ホールガスが発生することとなる。

#### 【0039】

また、バッファ層102を複数の半導体層で形成する場合は、InGaP層以外の半導体層には、InGaPよりも価電子帯のエネルギーレベルが高く、InGaP層と格子整合する材料で形成された半導体層を用いる。バッファ層102を複数の半導体層で形成することにより、バッファ層102にもある程度の導電性を持たせることが出来る。例えば、バッファ層102は、InGaP/GaAs/InGaP積層膜で形成することにより、InGaP単層膜で形成した場合に比べて導電性が向上する。

#### 【0040】

なお、多層構造を採用したバッファ層102をあっても、本願の発明者が行った実験によれば、チャネル層103に発生するキャリア数は、バッファ層102全体の厚みに応じたものとなっていた。このため、バッファ層102をInGaP層以外の半導体層を含

10

20

30

40

50

む多層構造とした場合でも、バッファ層 102 全体の厚さを調整することにより、チャネル層 103 に発生させるべきキャリア数を調整することができる。

#### 【0041】

チャネル層 103 の上には、pFET のゲートを構成するゲート部 104a が形成され、このゲート部 104a を挟んで両側にドレイン電極 105 とソース電極 106 が形成される。ここで、ゲート部 104a は、各種の方法で形成することが可能であり、例えば、エピタキシャル成長と選択的エッチングによる方法、不純物拡散、ショットキーメタルの蒸着、酸化膜を介したショットキーメタルの蒸着等、様々な方法で形成することができる。

#### 【0042】

ここで、エピタキシャル成長と選択的エッチングによる方法により作成されるゲート部のリーク電流を I1、不純物拡散により作成されるゲート部のリーク電流を I2、ショットキーメタルの蒸着により作成されるゲート部のリーク電流を I3、酸化膜を介したショットキーメタルの蒸着により作成されるゲート部のリーク電流を I4 とすると、I4 < I1 = I2 < I3、となる。リーク電流は小さい方が好ましいため、ゲート部 104a は酸化膜を介したショットキーメタルの蒸着により作成することが理想的である。ただし、化合物半導体では酸化膜の形成と制御が難しいため、実用上は、化合物半導体の場合は選択的エッチングが好ましい。

#### 【0043】

図 1 に示す例では、チャネル層 103 の上に、ゲート領域に対応する n 型の半導体層としてのゲート層 104 をエピタキシャル成長により形成し、このゲート層 104 を選択的にエッチングすることにより、ゲート部 104a を形成してある。

#### 【0044】

図 1 に示すゲート層 104 は、例えば、Si 等の n 型不純物を  $1 \times 10^{17} \sim 1 \times 10^{19}$  atoms/cm<sup>3</sup> の濃度で添加した、GaAs 層、InGaP 層、AlGaAs 層、及びこれらの複合とすることができます。ゲート層 104 に n-InGaP 層を用いる場合は、In<sub>x</sub>Ga<sub>1-x</sub>P とすると、x = 0.49 とする。これにより、チャネル層 103 とゲート層 104 が格子整合する。ゲート層 104 に n-AlGaAs 層を用いる場合は、Al<sub>x</sub>Ga<sub>1-x</sub>As とした場合、x = 0.1 ~ 0.5 とする。これにより、ゲート部 104a のリーク電流が低減する。なお、より好適には、ゲート層 104 に n-AlGaAs 層を用いる場合は、Al<sub>x</sub>Ga<sub>1-x</sub>As とした場合、x = 0.25 とする。これにより、酸化しやすい Al の比率を抑えつつ、リーク電流を低減することができる。

#### 【0045】

ゲート層 104 の膜厚は、例えば、チャネル層 103 の側から順に InGaP 層と GaAs 層を積層して形成した場合、特に限定されるものではないが、プロセス上の問題から、ストップ層として用いられる n-InGaP 層の膜厚を 10 nm ~ 50 nm とし、n-GaAs 層の膜厚を 50 ~ 200 nm とすることが現実的である。

#### 【0046】

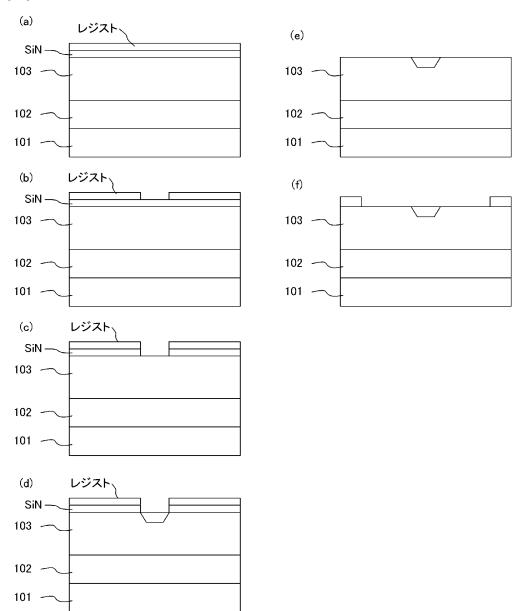

図 4 は、図 1 に示す半導体装置 100 のゲート部 104a の作成方法を説明する図である。同図において、ゲート部 104a は、ゲート層の上にレジストを塗布し(図 4(a))、ゲート部 104a が形成される領域以外のレジストを露光・現像して開口し(図 4(b))、ゲート部 104a が形成される領域以外のゲート層 104 をエッチングしてゲート部 104a のみを残した後(図 4(c))、レジストを剥離することにより形成される(図 4(d))。

#### 【0047】

その後、ゲート部 104a を挟んだ両側の位置に、それぞれチャネル層 103 とオーム接觸するドレイン電極 105 とソース電極 106 を蒸着することにより、半導体装置 100 が作成される(図 4(e))。

#### 【0048】

図 5 には、不純物拡散によりゲート部 104a を形成した半導体装置 100 を示してあ

10

20

30

40

50

る。同図に示す半導体装置 100 には、チャネル層 103 に拡散した n 型不純物により、ゲート部 104a を形成してある。このとき、ゲート部 104a は、不純物拡散の深さを調整することにより、チャネル層 103 の 2DHG 層との距離が 50 ~ 100 nm としてある。これにより、pFET の閾値電圧、すなわちゲート電圧に対する電流特性を調整することが出来る。例えば、ゲート部 104a と 2DHG 層の距離を小さくするほどエンハンスメント動作しやすくなり、ゲート部 104a と 2DHG 層の距離を大きくするほどデプレッション動作しやすくなる。また、ゲート部 104a の形成に用いる n 型不純物は、Si, S, Se, Te, Sn, Ge 等とし、これら不純物の濃度（ドナー濃度 Nd）は、 $N_d = 1 \times 10^{17} \sim 1 \times 10^{19}$  atoms/cm<sup>3</sup> とする。

## 【0049】

10

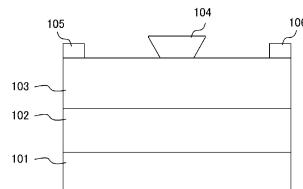

図 6 は、図 5 に示す半導体装置 100 のゲート部 104a の作成方法を説明する図である。同図において、ゲート部 104a は、チャネル層 103 の上に SiN 膜を CVD（化学蒸着）により付けて不動態化するとともに、その上にレジストを塗布し（図 6(a)）、ゲート部 104a に対応する領域のレジストのみを露光・現像して開口し（図 6(b)）、このレジストをマスクとしてゲート部 104a に対応する領域の SiN 膜をエッチングして開口させ（図 6(c)）、この SiN 膜の開口から不純物をチャネル層 103 に拡散し（図 6(d)）、レジストを剥離するとともに SiN 膜を除去することにより形成される（図 6(e)）。

## 【0050】

20

その後、ゲート部 104a を挟んだ両側の位置に、それぞれチャネル層 103 とオーミック接触するドレン電極 105 とソース電極 106 を蒸着することにより、半導体装置 100 が作成される（図 6(f)）。

## 【0051】

図 7 は、ショットキーメタルの蒸着によりゲート部 104a を形成した半導体装置 100 を示してある。同図に示す半導体装置 100 では、チャネル層 103 の上に直接にゲート電極をショットキー接合することにより、ゲート部 104a を形成してある。ゲート部 104a に用いるショットキーメタルは、Al, Zr, Hf, Gd, Fe, Nd, Sn, Yb, Au, Ti, Ni 等とする。

## 【0052】

30

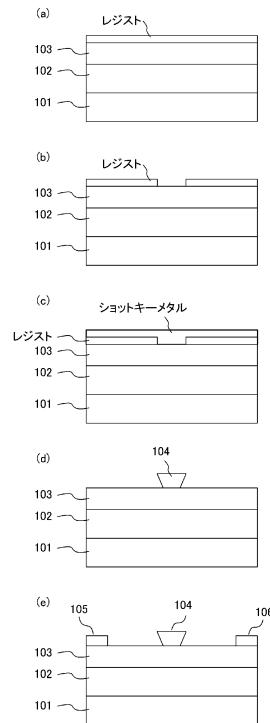

図 8 は、図 7 に示す半導体装置 100 のゲート部 104a の作成方法を説明する図である。同図において、ゲート部 104a は、チャネル層 103 の上にレジストを塗布し（図 8(a)）、ゲート部 104a が形成される領域のレジストのみを露光・現像して開口し（図 8(b)）、その上からショットキーメタルを蒸着し（図 8(c)）、レジストを剥離することによりゲート領域以外に蒸着されたショットキーメタルをリフトオフすることにより形成される（図 8(d)）。

## 【0053】

その後、ゲート部 104a を挟んだ両側の位置に、それぞれチャネル層 103 とオーミック接触するドレン電極 105 とソース電極 106 を蒸着することにより、半導体装置 100 が作成される（図 8(e)）。

## 【0054】

40

図 9 は、酸化膜を介したショットキーメタルの蒸着により形成したゲート部 104a を形成した半導体装置 100 を示してある。同図に示す半導体装置 100 では、チャネル層 103 の上に堆積した絶縁膜の上に、ショットキーメタルを蒸着することにより、ゲート部 104a を形成してある。絶縁膜は、Al<sub>2</sub>O<sub>3</sub>、HfO、Ga<sub>2</sub>O、GaON 等の酸化膜を、10 nm ~ 30 nm の厚さで形成する。また、ゲート部 104a に用いるショットキーメタルは、Al, Zr, Hf, Gd, Fe, Nd, Sn, Yb, Au, Ti, Ni 等とする。

## 【0055】

図 10 は、図 9 に示す半導体装置 100 のゲート部 104a の作成方法を説明する図である。同図において、ゲート部 104a は、チャネル層 103 の上に絶縁膜を堆積し（図

50

10(a)）、その上からレジストを塗布し(図10(b))、ゲート領域のレジストのみを露光・現像して開口し(図10(c))、その上からショットキーメタルを蒸着し(図10(d))、レジストを剥離することによりゲート領域以外に蒸着されたショットキーメタルをリフトオフすることにより形成される(図10(e))。

#### 【0056】

その後、ゲート部104aを挟んだ両側の位置をそれぞれチャネル層103に達するまでエッチングし(図10(f))、これらエッチング開口にそれぞれチャネル層103とオーム接觸するドレイン電極105とソース電極106を蒸着することにより、半導体装置100が作成される(図10(g))。

10

#### 【0057】

以上説明したように、本実施形態に係る半導体装置100のゲート部104aは、各種の方法で形成可能であり、目的に応じて最適な方法でゲート部104aを形成することが出来る。

#### 【0058】

##### (2) 半導体装置の第2実施形態の構成：

次に、上述したpFETを用いた他の実施形態について説明する。上述したpFETを用いて好適な実施形態としては、例えば、コンプリメンタリインバータや、レベルシフトロジック等がある。以下説明する第2実施形態では、コンプリメンタリインバータに上述したpFETを用いた場合を取り説明を行う。

20

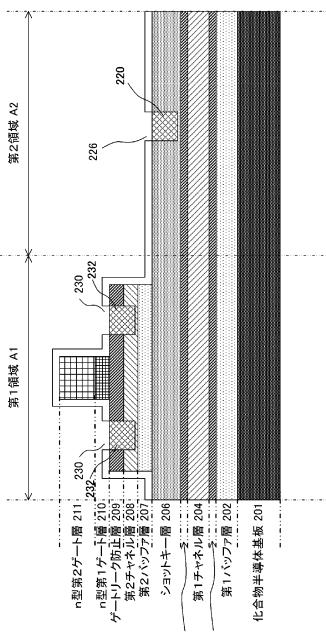

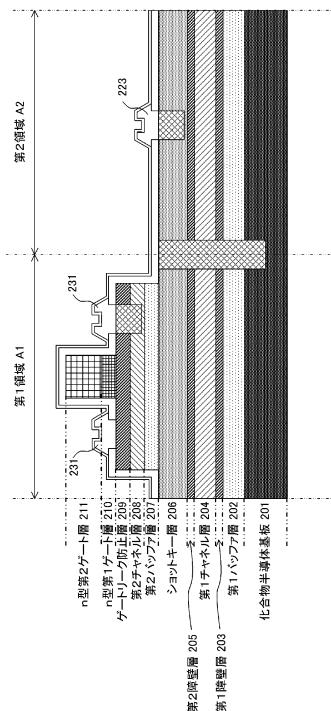

#### 【0059】

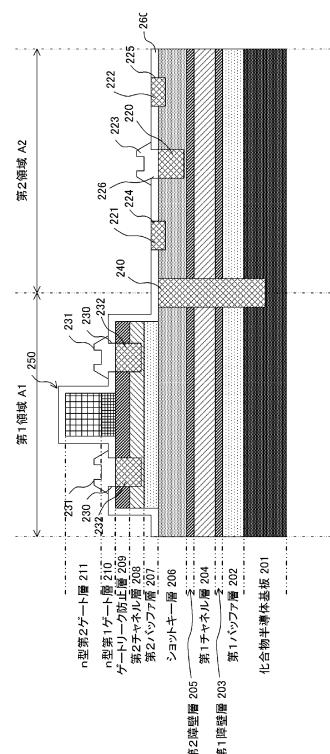

図11は、第2実施形態に係る半導体装置200の断面構成の1例を示す図である。同図に示す半導体装置200は、化合物半導体体系のpFETとNチャネル型電界効果トランジスタ(以下、nFETと略す。)を同一の基板上に形成したコンプリメンタリインバータである。このコンプリメンタリインバータに用いるpFETは、上述した第1実施形態に係るpFETに対応するものであり、以下に説明する第2実施形態のpFETは、上述した第1実施形態に係るpFETの特徴を適宜に置換したり組み合わせたりすることができる。

#### 【0060】

第2実施形態に係る半導体装置200は、GaAs単結晶基板の化合物半導体基板201上に、エピタキシャル成長により、Nチャネル電界効果トランジスタ(nFET)を形成するためのエピタキシャル層である層202～205と、Pチャネル電界効果トランジスタ(pFET)を形成するためのエピタキシャル層である層206～211を順次に積層して形成してある。

30

#### 【0061】

半導体装置200は、pFETが形成される第1領域A1、nFETが形成される第2領域A2を備えている。第1領域A1と第2領域A2は、化合物半導体基板201上にエピタキシャル成長により形成された層状のエピタキシャル基板に対して、適宜の手順で加工(エッチングやドーピング等)を施すことにより、同じ1つの化合物半導体基板上に形成される。

40

#### 【0062】

第1領域A1及び第2領域A2は、ともにnFET形成用のエピタキシャル結晶成長層を備えている。このnFET形成用のエピタキシャル結晶成長層は、図1に示すように、化合物半導体基板201の側から順に、第1バッファ層202、第1障壁層203、第1チャネル層204、及び第2障壁層205を備えている。なお、第1障壁層203と第2障壁層205は、必要に応じて何れか一方を省略することが出来る。

#### 【0063】

第1バッファ層202は、化合物半導体基板201と第1障壁層203の格子定数差を緩衝するために2層間に挿入される半導体層であり、例えば、p型不純物が添加されているA1GaAs層とする。なお、第1バッファ層202は、アンドープのGaAs層であ

50

つてもよく、その他、化合物半導体基板 201 と第1障壁層 203 の格子定数差を緩衝可能な材料であれば様々なものを採用可能である。

#### 【0064】

第1障壁層 203 は、例えば、第1キャリア供給層 203a と第1高抵抗層 203b を化合物半導体基板 201 の側から順に積層して形成してある。

#### 【0065】

第1キャリア供給層 203a は、第1チャネル層 204 にキャリアとしての電子を供給するための半導体層であり、例えば、n型不純物として Si を  $1.0 \times 10^{12} \sim 4.0 \times 10^{18}$  atoms/cm<sup>3</sup> の高濃度で添加した厚さ約 3 nm の AlGaAs 層とする。

10

#### 【0066】

第1高抵抗層 203b は、第1キャリア供給層 203a と第1チャネル層 204 の間に良好なヘテロ接合界面を得るために形成される半導体層であり、例えば、不純物が添加されていない厚さ約 3 nm の AlGaAs 層とする。

#### 【0067】

第1チャネル層 204 は、nFET の主電流が流れる半導体層であり、例えば、不純物が添加されていない厚さ 5 nm ~ 15 nm の InGaAs 層とする。

#### 【0068】

第2障壁層 205 は、例えば、第2高抵抗層 205a、及び第2キャリア供給層 205b を化合物半導体基板 201 の側から順に積層して形成してある。

20

#### 【0069】

第2高抵抗層 205a は、第1チャネル層 204 とその上に形成される第2キャリア供給層 205b との間に良好なヘテロ接合界面を得るために形成される半導体層であり、例えば、不純物が添加されていない厚さ約 3 nm の AlGaAs 層とする。

#### 【0070】

第2キャリア供給層 205b は、第1チャネル層 204 にキャリアとしての電子を供給するための半導体層であり、例えば、n型不純物として Si を  $1.0 \times 10^{12} \sim 4.0 \times 10^{18}$  atoms/cm<sup>3</sup> の高濃度で添加された厚さ約 6 nm の AlGaAs 層とする。

#### 【0071】

30

ショットキー層 206 は、第1領域 A1 において、ショットキー層 206 の上に形成される第2バッファ層 207 との間に良好なヘテロ接合界面を形成するための半導体層であり、例えば、n型不純物として Si が  $1.0 \times 10^{10} \sim 5.0 \times 10^{17}$  atoms/cm<sup>3</sup> の低濃度に添加された厚さ 70 nm ~ 200 nm の AlGaAs 層とする。

#### 【0072】

第2領域 A2 において、ショットキー層 206 は、p型不純物の Zn を拡散した p型ゲート領域 220 が形成されている。この第2領域 A2 におけるショットキー層 206 の上面には、シリコン窒化膜からなる絶縁膜 260 が形成されている。絶縁膜 260 には、半導体装置 200 の外部とショットキー層 206 とを接続するための開口部 226 が形成されており、開口部 226 にはゲート電極 223 が形成されている。

40

#### 【0073】

ゲート電極 223 は、例えば、チタン (Ti)、白金 (Pt)、金 (Au) が順次積層された金属電極により構成され、その下に形成されている p型ゲート領域 220 とオーミックコンタクトが取られている。ゲート電極 223 を挟んで両側にソース電極 221 とドレイン電極 222 が形成されており、ソース電極 221 とドレイン電極 222 は絶縁膜 260 を貫通してショットキー層 206 とオーミックコンタクトが取られている。

#### 【0074】

次に、pFET が形成される第1領域 A1 においては、第2領域 A2 に用いられる各層の階層構造の順に、第2バッファ層 207、第2チャネル層 208、ゲートリーク防止層 209、n型第1ゲート層 210、及び n型第2ゲート層 211 を備えている。

50

## 【0075】

第2バッファ層207は、ショットキー層206と第2チャネル層208の格子定数差を緩衝するために2層間に挿入される半導体層であり、例えば、不純物が添加されていない厚さ10nm～1000nmのInGaP層とする。なお、第2バッファ層207には不純物を添加してもよい。

## 【0076】

第2チャネル層208は、pFETの主電流が流れる半導体層であり、第2バッファ層207の上に形成され、例えば、不純物を添加されていない厚さ30～150nmのGaAs層、InGaAs層、AlGaAs層、InGaAsP層、又はこれらの組み合わせにより形成される層の何れかとする。むろん、これら以外にも、第2チャネル層208は、上述した第1実施形態におけるチャネル層103の場合と同様に、第2バッファ層207と格子整合し、第2バッファ層207に比べて価電子帯のエネルギーレベルが高い材料であれば、様々な材料を採用可能である。10

## 【0077】

ゲートリーク防止層209は、第2チャネル層208とn型ゲート層の間に形成されてゲートリーク電流を防止するための半導体層であり、例えば、不純物が添加されていない厚さ0nm～50nmのAlGaAs層とする。なお、ゲートリーク防止層209は、必要に応じて省略することができる。

## 【0078】

ゲートリーク防止層209の上には、第1領域A1において各層202～206の階層構造の上に形成された各層207～209の幅に比べて幅狭のn型ゲート領域250が形成されており、このn型ゲート領域250は、化合物半導体基板201の側から順にn型第1ゲート層210とn型第2ゲート層211を積層した2層構造になっている。20

## 【0079】

n型第1ゲート層210は、例えば、Siなどのn型不純物を $1 \times 10^{17} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>の濃度で添加した厚さ10nm～50nmのInGaP層とする。

## 【0080】

n型第2ゲート層211は、例えば、Siなどのn型不純物を $1 \times 10^{17} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>の濃度で添加した厚さ50～200nmのGaAs層とする。30

## 【0081】

第2バッファ層207、第2チャネル層208、ゲートリーク防止層209及びn型ゲート層の側面と、ゲートリーク防止層209及びn型ゲート層の上面には、シリコン窒化膜からなる絶縁膜260が形成されている。

## 【0082】

ゲートリーク防止層209の上面に形成された絶縁膜260には、ゲートリーク防止層209の上に積層されたn型ゲート層を挟んで両側に離間した位置に、開口部230，230が形成されている。この開口部230，230には、金属からなるソース電極231とドレイン電極231が形成されている。40

## 【0083】

ソース電極231とドレイン電極231は、チタン(Ti)、白金(Pt)、金(Au)が順次積層された金属電極により構成され、その下部に形成されるソース領域232及びドレイン領域232と、それぞれオーミックコンタクトが取られている。

## 【0084】

ソース領域232及びドレイン領域232は、開口部230，230からゲートリーク防止層209へ不純物であるZnを拡散して、ゲートリーク防止層209及び第2チャネル層208の一部領域をp型化して形成した拡散領域である。すなわち、ソース領域232及びドレイン領域232は、ゲートリーク防止層209を貫通し、第2チャネル層208の一部領域まで延在するように形成されている。

## 【0085】

10

20

30

40

50

なお、第1領域A1と第2領域A2の境界領域には、各層201～206を貫通するよう、素子分離領域240が形成されている。素子分離領域240は、例えば、B(ボロン)をイオン注入することにより形成する。

#### 【0086】

以上説明したように、第1領域A1にpn接合型ゲートを有するpFETを形成し、第2領域A2にpn接合型ゲートを有するnFETを形成してあるため、両FET、特にpFETをエンハンスマードで動作させることができ、リーク電流を低減した高速動作の相補型FETが同一基板上に形成される。

#### 【0087】

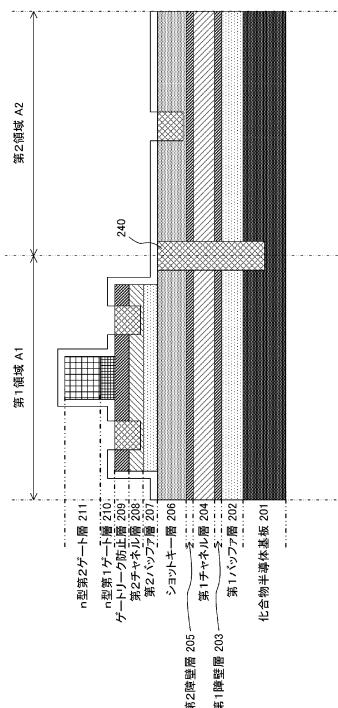

(3) 第2実施形態に係る半導体装置の製造方法：

10

次に、図12～図20を用いて第2実施形態に係る半導体装置100の製造方法を説明する。図12は、GaAs単結晶基板上にGaAs材料を主体とする各層を、例えば有機金属気相成長法(MOCVD)法によりエピタキシャル成長させた半導体装置100の積層構造を表す模式的な縦断面図である。

#### 【0088】

同図に示す積層構造を形成するには、まず、GaAs単結晶からなる化合物半導体基板201上に、不純物を添加しないGaAs層をエピタキシャル成長させて厚さ約200nm程度の第1バッファ層202を形成する。

#### 【0089】

次に、第1バッファ層202の上に、n型不純物としてSiを $1.0 \times 10^{12} \sim 4.0 \times 10^{12}$ atoms/cm<sup>3</sup>、例えば $3.0 \times 10^{12}$ atoms/cm<sup>3</sup>の高濃度で添加したAlGaAs層をエピタキシャル成長させて厚さ約3nmの第1キャリア供給層203aを形成する。

20

#### 【0090】

次に、第1キャリア供給層203aの上に、不純物を添加しないAlGaAs層をエピタキシャル成長させて厚さ約3nmの第1高抵抗層203bを形成する。これら第1キャリア供給層203aと第1高抵抗層203bは、第1障壁層203を構成する。この第1障壁層203のアルミニウム(Al)の組成比は、 $Al_{1-x}Ga_xAs$ とすると、 $x = 0.1 \sim 0.5$ とし、例えば $Al_{0.2}Ga_{0.8}As$ とする。

#### 【0091】

30

次に、第1高抵抗層203bの上に、不純物を添加しないInGaAs層をエピタキシャル成長させて厚さ5nm～15nmの第1チャネル層204を形成する。第1チャネル層204のインジウム(In)の組成比は、 $In_{1-x}Ga_xAs$ とすると、 $x = 0.51$ とし、上述した1つ目の障壁層よりもバンドギャップを狭くする。

#### 【0092】

次に、第1チャネル層204の上に、不純物を添加しないAlGaAs層をエピタキシャル成長させて厚さ約2nmの第2高抵抗層205aを形成する。

#### 【0093】

次に、第2高抵抗層205aの上に、n型不純物としてSiを $1.0 \times 10^{12} \sim 4.0 \times 10^{12}$ atoms/cm<sup>3</sup>の高濃度に添加したAlGaAs層をエピタキシャル成長させて、厚さ約6nmの第2キャリア供給層205bを形成する。

40

#### 【0094】

これら第2高抵抗層205a、第2キャリア供給層205bは、第2障壁層205を構成する。この第2障壁層205のアルミニウム(Al)の組成比は、 $Al_{1-x}Ga_xAs$ とすると、 $x = 0.1 \sim 0.5$ とし、例えば $Al_{0.2}Ga_{0.8}As$ とする。これにより2つめの障壁層は、第1チャネル層204よりもバンドギャップを広くすることができる。

#### 【0095】

次に、第2キャリア供給層205bの上に、n型不純物としてSiを低濃度に添加したAlGaAs層をエピタキシャル成長させて厚さ70nm～200nmのショットキー層

50

206を形成する。

**【0096】**

次に、不純物を添加しないInGaP層をエピタキシャル成長させて厚さ10nm～100nmの第2バッファ層207を形成する。

**【0097】**

次に、第2バッファ層207の上に、不純物を添加しないGaAs層をエピタキシャル成長させて、厚さ30nm～150nmの第2チャネル層208を形成する。

**【0098】**

次に、第2チャネル層208の上に、不純物を添加しないAlGaAs層をエピタキシャル成長させて、厚さ0～50nmのゲートリーク防止層209を形成する。厚さが0とは、ゲートリーク防止層209は必須の構成ではないためである。ゲートリーク防止層209のアルミニウム(Al)の組成比は $Al_{1-x}Ga_xAs$ とすると、 $x = 0.1 \sim 0.5$ とし、例えば $Al_{0.2}Ga_{0.8}As$ とする。

10

**【0099】**

次に、ゲートリーク防止層209又は第2チャネル層208の上に、Siなどのn型不純物を $1 \times 10^{17} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>の濃度で添加したInGaP層をエピタキシャル成長させて、厚さ10nm～50nmのn型第1ゲート層210を形成する。

**【0100】**

次に、n型第1ゲート層210の上に、Siなどのn型不純物を $1 \times 10^{17} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>添加したGaAs層をエピタキシャル成長させて、厚さ50～200nmのn型第2ゲート層211を形成する。n型第1ゲート層210とn型第2ゲート層211は、n型ゲート層を構成する。

20

なお、以上のエピタキシャル成長は、温度約600℃により行う。

**【0101】**

次に、図13に示すように、n型第2ゲート層211及びn型第1ゲート層210を、例えばフォトリソグラフィ技術及びウエットエッティング若しくはドライエッティング技術を用いて、順次に選択的にエッティング除去する。このエッティングにより、第1領域A1にn型ゲート領域250を形成する。

**【0102】**

次に、図14に示すように、ゲートリーク防止層209、第2チャネル層208を、例えばフォトリソグラフィ技術及びウエットエッティング若しくはドライエッティング技術を用いて、順次に選択的にエッティング除去する。このとき、InGaPの第2バッファ層207がエッティングストップ層の役割をするため、第2領域A2のオーバーエッティングが抑制される。これにより、エッティングによるnFETのオン抵抗とオフ容量への影響が防止できる。

30

**【0103】**

その後、図15に示すように、第2バッファ層207を、例えば、塩酸を用いて選択的にエッティングする。これらのエッティングにより、第1領域A1においては、各層207～209が除去されずに残存しつつ、各層207～209の上にn型ゲート領域250が積層された状態となり、第2領域においては、各層207～211が全てエッティング除去された状態となる。

40

**【0104】**

次に、図16に示すように、基板上面の露出した表面にプラズマCVD法によりシリコン窒化膜からなる絶縁膜260を厚さ100nm～500nm形成する。

**【0105】**

次に、図17に示すように、絶縁膜260に、第1領域A1のソース領域及びドレイン領域形成用の開口部230，230と、第2領域A2のゲート領域形成用の開口部224を形成する。開口部230，230，226はフォトリソグラフィ技術、及び、例えばRIE(Reactive Ion Etching)技術を用いた異方性エッティングにより形成する。

50

## 【0106】

次に、図18に示すように、不純物であるZnを、絶縁膜260の開口部230, 230を通してゲートリーク防止層209と第2チャネル層208の厚さ方向途中まで拡散させ、開口部226を通してショットキー層206の厚さ方向途中まで拡散させる。Znは、ジエチルジンク(Zn(C2H5)2)とアルシン(AsH3)を含むガス雰囲気中で基板を約600℃に加熱し、開口部230, 230, 226から導入拡散させる。これにより、第1領域A1にp型のソース領域232及びドレイン領域232が形成され、第2領域A2にp型ゲート領域220が形成される。

## 【0107】

なお、第2領域A2では、開口部226から拡散されるZnの拡散深さが、第1チャネル層204の上面から約10nm以上離れるように形成することが好ましい。また、Znはイオン注入法により注入することもきる。

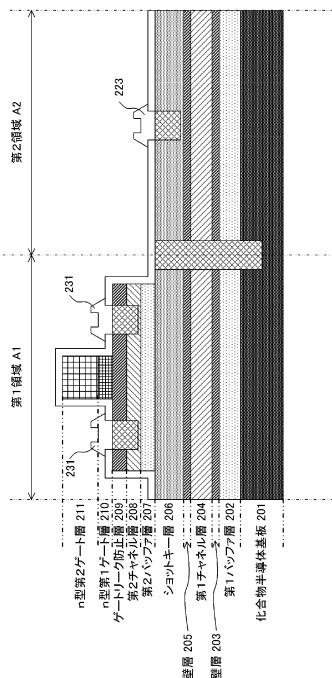

## 【0108】

次に、図19に示すように、第1領域A1, 第2領域A2を電気的に分離するための素子分離領域240を形成する。素子分離領域240は、ショットキー層206から第1キャリア供給層203aの底部に達する深さまで形成する。素子分離領域240は、例えばBイオンのイオン注入法により形成することができる。

## 【0109】

次に、図20に示すように、基板の表面に金属膜を堆積し、フォトリソグラフィ技術及びエッチング技術を用いて選択的に除去して、第1領域A1のソース電極231及びドレイン電極231と、第2領域A2のゲート電極223を同時に形成する。

## 【0110】

金属膜は、例えば電子ビーム蒸着法によりチタン(Ti)、白金(Pt)、金(Au)を例えば30nm、50nm、120nmの厚さで堆積する。これにより、Znを拡散させたp型のソース領域232とドレイン領域232、p型ゲート領域220のそれぞれにおいてオームックコンタクトをとることができる。

## 【0111】

更に、図21に示すように、基板表面に絶縁材料からなる保護膜265を堆積し、次に第2領域A2のゲート電極223を挟むように保護膜265及び絶縁膜260に開口部224, 225を形成する。

## 【0112】

そして、基板表面に抵抗加熱法により金-ゲルマニウム(AuGe)合金を厚さ約160nm、ニッケル(Ni)を厚さ約40nm堆積し、フォトリソグラフィ技術及びエッチング技術を用いて選択的に除去して、ソース電極221及びドレイン電極222を形成する。ソース電極221及びドレイン電極222は、n型のショットキー層206とオームックコンタクトがとられている。

## 【0113】

なお、保護膜265及び絶縁膜260の開口部224, 225を形成する際に、第1領域A1のn型ゲート領域250の上部にも同時に開口部を形成し、第2領域A2のソース電極221及びドレイン電極222とともに、第2領域A2のゲート電極を形成することができる。

## 【0114】

以上説明した製造方法によれば、図11に示す構造のpFET、nFETを同時に同一のエピタキシャル基板上に形成して、コンプリメンタリインバータを作成することができる。

## 【0115】

## (4)まとめ：

以上説明した半導体装置によれば、ピエゾ分極を起こす半導体にて形成されたバッファ層102と、バッファ層102の上に積層されたチャネル層103と、を備え、チャネル層103においては、バッファ層102のピエゾ分極によりチャネル層103に生じる2

10

20

30

40

50

次元ホールガスをキャリアとしている。これにより、エピタキシャル基板を選択的にエッチングして作成するpチャネルFETにおけるキャリアの高移動度とゲートの低いオン抵抗を実現し、素子の高集積化を実現することができる。

#### 【0116】

なお、本発明は上述した実施形態や変形例に限らず、上述した実施形態および変形例の中で開示した各構成を相互に置換したり組み合わせを変更したりした構成、公知技術並びに上述した実施形態および変形例の中で開示した各構成を相互に置換したり組み合わせを変更したりした構成、等も含まれる。また、本発明の技術的範囲は上述した実施形態に限定されず、特許請求の範囲に記載された事項とその均等物まで及ぶものである。

#### 【0117】

そして、本技術は、以下のような構成を取ることができる。

#### 【0118】

(1) ピエゾ分極を起こす半導体にて形成されたバッファ層と、

前記バッファ層の上に積層されたチャネル層と、

を備え、

前記チャネル層においては、前記バッファ層のピエゾ分極により当該チャネル層に生じる2次元ホールガスをキャリアとする半導体装置。

#### 【0119】

(2) 前記バッファ層においてピエゾ分極を起こす半導体は、InGaPである(1)

に記載の半導体装置。

#### 【0120】

(3) 前記チャネル層は、価電子帯のエネルギーレベルが前記バッファ層よりも高い半導体にて形成されている(1)又は(2)に記載の半導体装置。

#### 【0121】

(4) 前記チャネル層には、前記ピエゾ分極により前記バッファ層の厚さに応じた数の2次元ホールガスが発生する(1)～(3)の何れか1項に記載の半導体装置。

#### 【0122】

(5) 前記バッファ層は、互いに格子整合する複数の半導体層にて形成されており、

これら複数の半導体層のうち、前記チャネル層に隣接して設けられる半導体層は、前記ピエゾ分極を起こす半導体で形成されている(1)～(4)の何れか1項に記載の半導体装置。

#### 【0123】

(6) 前記チャネル層は、前記ピエゾ分極を起こす半導体と格子整合する半導体を1回以上積層して形成してある(1)～(5)の何れか1項に記載の半導体装置。

#### 【0124】

(7) 前記チャネル層の半導体には、濃度が $1 \times 10^{17}$ atoms/cm<sup>3</sup>以下の不純物がドープしてあり、

前記バッファ層の半導体には、不純物がドープしてある(1)～(6)の何れか1項に記載の半導体装置。

#### 【0125】

(8) 前記バッファ層は、化合物半導体基板の上に積層されており、

前記バッファ層と前記化合物半導体基板の間には、前記バッファ層の半導体と前記化合物半導体基板の半導体の双方に格子整合する半導体層であって、前記バッファ層の半導体と前記化合物半導体基板の半導体の双方とバンドギャップが異なる少なくとも1層の半導体層を積層してある(1)～(7)の何れか1項に記載の半導体装置。

#### 【0126】

(9) 前記チャネル層の上に積層されたn型半導体により形成したゲートを備える(1)～(8)の何れか1項に記載の半導体装置。

#### 【0127】

(10) 前記チャネル層にn型の不純物を拡散することにより形成したゲートを備える

10

20

30

40

50

(1) ~ (8) の何れか 1 項に記載の半導体装置。

**【0128】**

(11) 前記チャネル層に接合されたショットキーメタルにより形成したゲートを備える(1) ~ (8) の何れか 1 項に記載の半導体装置。

**【0129】**

(12) 前記チャネル層上に積層したゲート酸化膜にショットキーメタルを接合して形成したゲートを備える(1) ~ (8) の何れか 1 項に記載の半導体装置。

**【0130】**

(13) (1) ~ (12) の何れか 1 項に記載の半導体装置と n 型電界効果トランジスタを同じ化合物半導体基板上に形成した相補型半導体装置。 10

**【0131】**

(14) (1) ~ (12) の何れか 1 項に記載の半導体装置を用いて作成されたレベルシフト回路。

**【0132】**

(15) 化合物半導体の基部を形成する工程と、

前記基部の上に、前記基部の化合物半導体と格子整合し且つピエゾ分極を起こす半導体を積層してバッファ層を形成する工程と、

前記バッファ層の上に、前記バッファ層の半導体と格子整合し且つ前記バッファ層のピエゾ分極により 2 次元ホールガスが発生する半導体を積層してチャネル層を形成する工程と、 20

前記チャネル層の上にゲートを形成する工程と、

前記チャネル層の上の前記ゲートを挟んだ両側にそれぞれドレイン及びソースを形成する工程と、

を含む、半導体装置の製造方法。

**【符号の説明】**

**【0133】**

100 ... 半導体装置、101 ... 基板、102 ... バッファ層、103 ... チャネル層、104 ... ゲート層、104a ... ゲート部、105 ... ドレイン電極、106 ... ソース電極

200 ... 半導体装置、201 ... 化合物半導体基板、202 ... 第 1 バッファ層、203 ... 第 1 障壁層、203a ... 第 1 キャリア供給層、203b ... 第 1 高抵抗層、204 ... 第 1 チャネル層、205 ... 第 2 障壁層、205a ... 第 2 高抵抗層、205b ... 第 2 キャリア供給層、206 ... ショットキー層、207 ... 第 2 バッファ層、208 ... 第 2 チャネル層、209 ... ゲートリーク防止層、210 ... n 型第 1 ゲート層、211 ... n 型第 2 ゲート層 30

220 ... p 型ゲート領域、221 ... ソース電極、222 ... ドレイン電極、223 ... ゲート電極、224 ... 開口部、225 ... 開口部、226 ... 開口部

230 ... 開口部(第 1 領域の)、231 ... ソース電極、231 ... ドレイン電極、232 ... ソース領域、232 ... ドレイン領域、240 ... 素子分離領域、250 ... n 型ゲート領域、260 ... 絶縁膜、265 ... 保護膜、A1 ... 第 1 領域、A2 ... 第 2 領域、Ei ... 内部電界、Ev1 ... エネルギーレベル、Ev2 ... エネルギーレベル、Ev3 ... エネルギーレベル、K1 ... ヘテロ接合界面、K2 ... ヘテロ接合界面、P ... 三角ポテンシャル、 40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 四 8 】

【 図 9 】

【 図 1 1 】

【図10】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/78 (2006.01)

(56)参考文献 特開2011-066075(JP,A)

特開2003-258384(JP,A)

特開平10-313096(JP,A)

特開平6-168960(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/338

H 01 L 21/336

H 01 L 27/095

H 01 L 29/778

H 01 L 29/78

H 01 L 29/812