(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7652274号**

**(P7652274)**

(45)発行日 令和7年3月27日(2025.3.27)

(24)登録日 令和7年3月18日(2025.3.18)

(51)国際特許分類

|        |                  |     |        |        |

|--------|------------------|-----|--------|--------|

| H 01 L | 21/20 (2006.01)  | F I | H 01 L | 21/20  |

| H 01 L | 21/205 (2006.01) |     | H 01 L | 21/205 |

請求項の数 21 (全18頁)

(21)出願番号 特願2023-549420(P2023-549420)

(86)(22)出願日 令和4年8月22日(2022.8.22)

(86)国際出願番号 PCT/JP2022/031572

(87)国際公開番号 WO2023/047864

(87)国際公開日 令和5年3月30日(2023.3.30)

審査請求日 令和6年3月8日(2024.3.8)

(31)優先権主張番号 特願2021-152843(P2021-152843)

(32)優先日 令和3年9月21日(2021.9.21)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000190149

信越半導体株式会社

東京都千代田区大手町二丁目2番1号

(74)代理人 100102532

弁理士 好宮 幹夫

(74)代理人 100194881

弁理士 小林 俊弘

100215142

弁理士 大塚 徹

久保埜 一平

(72)発明者 群馬県安中市磯部二丁目13番1号 信

越半導体株式会社 半導体磯部研究所内

萩本 和徳

(72)発明者 群馬県安中市磯部二丁目13番1号 信

越半導体株式会社 半導体磯部研究所内

最終頁に続く

(54)【発明の名称】窒化物半導体基板及びその製造方法

**(57)【特許請求の範囲】****【請求項1】**

成長用基板と、該成長用基板上に成膜された窒化物半導体薄膜とを具備する窒化物半導体基板であって、

前記窒化物半導体薄膜は、前記成長用基板上に形成されたAlN層と、該AlN層上に形成された窒化物半導体層とを含み、かつ、

前記AlN層中の平均Y(イットリウム)濃度が、 $1 \times 10^{15} \text{ atoms/cm}^3$ 以上、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下のものであることを特徴とする窒化物半導体基板。

**【請求項2】**

前記AlN層の厚さが50~150nmであり、かつ、前記窒化物半導体薄膜中における前記成長用基板直上から薄膜成長方向に300nmまでの平均Y(イットリウム)濃度が、 $1 \times 10^{15} \text{ atoms/cm}^3$ 以上、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下のものであることを特徴とする請求項1に記載の窒化物半導体基板。

**【請求項3】**

前記窒化物半導体層は、GaN、AlN、及びAlGaNのうち1つ以上からなるものであることを特徴とする請求項1に記載の窒化物半導体基板。

**【請求項4】**

前記成長用基板は、複数の層が積層された複合基板上に単結晶シリコン層が形成されたものであり、かつ、

前記単結晶シリコン層上に前記窒化物半導体薄膜が成膜されたものであることを特徴と

する請求項1に記載の窒化物半導体基板。

**【請求項5】**

前記単結晶シリコン層が100～500nmの厚さを有するものであることを特徴とする請求項4に記載の窒化物半導体基板。

**【請求項6】**

前記複合基板は、多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層全体に積層された第2の接着層と、該第2の接着層全体に積層されたバリア層とを含むものであり、かつ、

前記単結晶シリコン層は、前記複合基板の片面のみに積層された平坦化層の上に形成されたものであることを特徴とする請求項4に記載の窒化物半導体基板。

10

**【請求項7】**

前記複合基板が、前記第1の接着層と前記第2の接着層との間に、前記第1の接着層全体に積層された導電層を有するものであることを特徴とする請求項6に記載の窒化物半導体基板。

**【請求項8】**

前記複合基板は、多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層全体に積層されたバリア層と、該バリア層の裏面に積層された第2の接着層と、該第2の接着層の裏面に積層された導電層とを含むものであり、かつ、

前記単結晶シリコン層は、前記複合基板の前記バリア層の表面に積層された平坦化層の上に形成されたものであることを特徴とする請求項4に記載の窒化物半導体基板。

20

**【請求項9】**

前記複合基板は、多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層の裏面に積層された導電層と、該導電層の裏面に積層された第2の接着層と、前記第1の接着層の表面及び側面と前記導電層の側面と前記第2の接着層の側面及び裏面に積層されたバリア層とを含むものであり、かつ、

前記単結晶シリコン層は、前記複合基板の前記バリア層の表面に積層された平坦化層の上に形成されたものであることを特徴とする請求項4に記載の窒化物半導体基板。

**【請求項10】**

前記導電層が、ポリシリコン層を含むものであることを特徴とする請求項7から請求項9のいずれか一項に記載の窒化物半導体基板。

30

**【請求項11】**

前記導電層が、150～500nmの厚さを有するものであることを特徴とする請求項7から請求項9のいずれか一項に記載の窒化物半導体基板。

**【請求項12】**

前記多結晶セラミックコアが、窒化アルミニウムを含むものであることを特徴とする請求項6から請求項9のいずれか一項に記載の窒化物半導体基板。

**【請求項13】**

前記第1の接着層及び前記第2の接着層はテトラエチルオルトシリケート(TEOS)層又は酸化ケイ素(SiO<sub>2</sub>)層を含み、前記バリア層は窒化ケイ素を含むものであることを特徴とする請求項6から請求項9のいずれか一項に記載の窒化物半導体基板。

40

**【請求項14】**

前記第1の接着層及び前記第2の接着層は50～200nmの厚さを有し、前記バリア層は100～350nmの厚さを有するものであることを特徴とする請求項6から請求項9のいずれか一項に記載の窒化物半導体基板。

**【請求項15】**

前記平坦化層はテトラエチルオルトシリケート(TEOS)又は酸化ケイ素(SiO<sub>2</sub>)を含み、かつ、500～3000nmの厚さを有するものであることを特徴とする請求項6から請求項9のいずれか一項に記載の窒化物半導体基板。

**【請求項16】**

50

成長用基板と、該成長用基板上に成膜された窒化物半導体薄膜とを具備する窒化物半導体基板の製造方法であって、

(1) Y(イットリウム)を含有する前記成長用基板を準備する工程、及び

(2) 前記成長用基板上にAlN層をエピタキシャル成長させ、さらに前記AlN層上に窒化物半導体層をエピタキシャル成長させることにより、前記窒化物半導体薄膜を成膜する工程

を含み、かつ、

前記工程(2)において、前記成長用基板中のYを拡散させて、前記AlN層中の平均Y(イットリウム)濃度を、 $1 \times 10^{15} \text{ atoms/cm}^3$ 以上、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下とすることを特徴とする窒化物半導体基板の製造方法。

10

#### 【請求項17】

前記AlN層の厚さを $50 \sim 150 \text{ nm}$ とし、かつ、前記窒化物半導体薄膜中における前記成長用基板直上から薄膜成長方向に $300 \text{ nm}$ までの平均Y(イットリウム)濃度を $1 \times 10^{15} \text{ atoms/cm}^3$ 以上、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下とすることを特徴とする請求項16に記載の窒化物半導体基板の製造方法。

#### 【請求項18】

前記成長用基板を、結合材料としてイットリア( $\text{Y}_2\text{O}_3$ )を含有する多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層全体に積層された第2の接着層と、該第2の接着層全体に積層されたバリア層とを含む複合基板と、該複合基板の片面のみに積層された平坦化層と、該平坦化層の上に形成された単結晶シリコン層により構成された成長用基板とし、かつ、前記単結晶シリコン層上に前記窒化物半導体薄膜を形成するようにし、かつ、

20

予め前記バリア層の厚さを調整することによって、前記AlN層中の平均Y(イットリウム)濃度を、 $1 \times 10^{15} \text{ atoms/cm}^3$ 以上、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下とすることを特徴とする請求項16又は請求項17に記載の窒化物半導体基板の製造方法。

#### 【請求項19】

前記複合基板を、前記第1の接着層と前記第2の接着層との間に、前記第1の接着層全体に積層された導電層を有するものとすることを特徴とする請求項18に記載の窒化物半導体基板の製造方法。

#### 【請求項20】

30

前記成長用基板を、結合材料としてイットリア( $\text{Y}_2\text{O}_3$ )を含有する多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層全体に積層されたバリア層と、該バリア層の裏面に積層された第2の接着層と、該第2の接着層の裏面に積層された導電層とを含む複合基板と、該複合基板の前記バリア層の表面に積層された平坦化層と、該平坦化層の上に形成された単結晶シリコン層により構成された成長用基板とし、かつ、前記単結晶シリコン層上に前記窒化物半導体薄膜を形成するようにし、かつ、

予め前記バリア層の厚さを調整することによって、前記AlN層中の平均Y(イットリウム)濃度を、 $1 \times 10^{15} \text{ atoms/cm}^3$ 以上、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下とすることを特徴とする請求項16又は請求項17に記載の窒化物半導体基板の製造方法。

40

#### 【請求項21】

前記成長用基板を、結合材料としてイットリア( $\text{Y}_2\text{O}_3$ )を含有する多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層の裏面に積層された導電層と、該導電層の裏面に積層された第2の接着層と、前記第1の接着層の表面及び側面と前記導電層の側面と前記第2の接着層の側面及び裏面に積層されたバリア層とを含む複合基板と、該複合基板の前記バリア層の表面に積層された平坦化層と、該平坦化層の上に形成された単結晶シリコン層により構成された成長用基板とし、かつ、前記単結晶シリコン層上に前記窒化物半導体薄膜を形成するようにし、かつ、

予め前記バリア層の厚さを調整することによって、前記AlN層中の平均Y(イットリウム)濃度を、 $1 \times 10^{15} \text{ atoms/cm}^3$ 以上、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下とす

50

ることを特徴とする請求項 1 6 又は請求項 1 7 に記載の窒化物半導体基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、窒化物半導体基板及びその製造方法に関する。

【背景技術】

【0 0 0 2】

半導体薄膜製造方法のひとつであるMOCVD法は、大口径化や量産性に優れており、均質な薄膜結晶を成膜できるため、広く用いられている。GaNに代表される窒化物半導体はSiの材料としての限界を超える次世代の半導体材料として期待されている。

10

【0 0 0 3】

GaNは飽和電子速度が大きいという特性から高周波動作可能なデバイスの作製が可能であり、また絶縁破壊電界も大きいことから、高出力での動作が可能である。また、軽量化や小型化、低消費電力化も見込める。近年、5G等に代表されるような通信速度の高速化、またそれ伴う高出力化の要求により、高周波、且つ高出力で動作可能なGaN HEMTが注目されている。

【0 0 0 4】

GaNデバイスを作製するためのGaNエピタキシャルウェーハに用いられる基板としては、Si基板が最も安価であり且つ大口径化に有利である。また、大口径で且つGaNと熱膨張係数が近いGaNエピタキシャル成長用の大口径基板（以下、GaN用支持基板）も特許文献1等に開示されている。このGaN用支持基板は、多結晶セラミックコア、第1の接着層、導電層、第2の接着層、バリア層を含む支持構造と、該支持構造の片面に積層された平坦化層、該平坦化層に積層された単結晶シリコン層により構成される。

20

【0 0 0 5】

このGaN用支持基板を用いることで、大口径で且つエピタキシャル層の厚さが厚く、且つクラックの発生しないGaNエピタキシャル基板を作製できる。また、GaNと熱膨張係数差が極めて小さい事から、GaN成長中や冷却中に反りが発生しにくいため、成膜後の基板の反りを小さく制御できるだけでなく、エピタキシャル層中に複雑な応力緩和層を設ける必要が無いため、エピタキシャル成膜時間が短くなり、エピタキシャル成長のコストを大幅に削減できる。さらに、GaN用支持基板は大部分がセラミックスであるため、基板自体が非常に硬く塑性変形しにくいため、口径の大きいGaN/Siで解決されていないウェーハ割れが発生しない。

30

【0 0 0 6】

ところで、Si基板においてもGaN成長用支持基板においても、GaNに代表されるようなIII族窒化物半導体の成膜では、エピタキシャルウェーハ表面のピットの発生がしばしば問題となる。これは、Si基板やGaN成長用基板直上に成膜するAlNの表面モフォロジーが悪いことが一因として挙げられる。エピタキシャルウェーハ表面にピットが発生すると、デバイス動作に必要なキャリアが欠損してしまうため、キラー欠陥となり歩留まりが低下する。

40

【先行技術文献】

【特許文献】

【0 0 0 7】

【文献】特表2020-505767

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 8】

本発明は上記課題を解決するためになされたもので、AlN層の表面モフォロジーを改善して窒化物半導体エピタキシャルウェーハ表面のピットの発生を抑制することができる窒化物半導体基板、及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

50

**【 0 0 0 9 】**

上記課題を解決するために、本発明では、

成長用基板と、該成長用基板上に成膜された窒化物半導体薄膜とを具備する窒化物半導体基板であって、

前記窒化物半導体薄膜は、前記成長用基板上に形成された AlN 層と、該 AlN 層上に形成された窒化物半導体層とを含み、かつ、

前記 AlN 層中の平均 Y (イットリウム) 濃度が、 $1 \times 10^{15}$  atoms/cm<sup>3</sup> 以上、 $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下のものである窒化物半導体基板を提供する。

**【 0 0 1 0 】**

AlN 層中の平均 Y 濃度をこの範囲内とすれば、AlN の表面モフォロジーが悪化することなく、よって表面のピットの発生が抑制された窒化物半導体基板とすることができます。 10

**【 0 0 1 1 】**

また、前記 AlN 層の厚さが 50 ~ 150 nm であり、かつ、前記窒化物半導体薄膜中における前記成長用基板直上から薄膜成長方向に 300 nm までの平均 Y (イットリウム) 濃度が、 $1 \times 10^{15}$  atoms/cm<sup>3</sup> 以上、 $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下のものであることが好ましい。

**【 0 0 1 2 】**

このようにすれば、窒化物半導体薄膜中において AlN 層がイットリウム含有領域で十分に覆われているため、より確実に表面モフォロジーの良好な AlN 層を形成し、窒化物半導体薄膜表面のピットの発生を抑制することができる。 20

**【 0 0 1 3 】**

また、前記窒化物半導体層は、GaN、AlN、及び AlGaN のうち 1 つ以上からなるものであることが好ましい。

**【 0 0 1 4 】**

本発明では、AlN 層の上にこのような窒化物半導体層を設けることができる。

**【 0 0 1 5 】**

また、前記成長用基板は、複数の層が積層された複合基板上に単結晶シリコン層が形成されたものであり、かつ、

前記単結晶シリコン層上に前記窒化物半導体薄膜が成膜されたものであることが好ましい。 30

**【 0 0 1 6 】**

このような成長用基板であれば、大口径で且つエピタキシャル層が厚く、且つクラックの発生しない窒化物半導体エピタキシャル成長基板を作製できる。また、窒化物半導体との熱膨張係数差が小さいため、窒化物半導体成長中や冷却中に反りが発生しにくいため、成膜後の基板の反りを小さく制御できる。

**【 0 0 1 7 】**

このとき、前記単結晶シリコン層が 100 ~ 500 nm の厚さを有するものであることが好ましい。

**【 0 0 1 8 】**

単結晶シリコン層はこのような厚さとすることができます。 40

**【 0 0 1 9 】**

また、前記複合基板は、多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第 1 の接着層と、該第 1 の接着層全体に積層された第 2 の接着層と、該第 2 の接着層全体に積層されたバリア層とを含むものであり、かつ、

前記単結晶シリコン層は、前記複合基板の片面のみに積層された平坦化層の上に形成されたものであることが好ましい。

**【 0 0 2 0 】**

このような構成であれば、成長用基板の大部分がセラミックスであるため、基板自体が非常に硬く塑性変形しにくいだけでなく、シリコン基板で解決されていないウェーハ割れも発生しない。

10

20

30

40

50

**【 0 0 2 1 】**

また、前記複合基板が、前記第1の接着層と前記第2の接着層との間に、前記第1の接着層全体に積層された導電層を有するものであってもよい。

**【 0 0 2 2 】**

複合基板には、必要に応じて導電性を付与することができる。

**【 0 0 2 3 】**

また、前記複合基板は、多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層全体に積層されたバリア層と、該バリア層の裏面に積層された第2の接着層と、該第2の接着層の裏面に積層された導電層とを含むものであり、かつ、

10

前記単結晶シリコン層は、前記複合基板の前記バリア層の表面に積層された平坦化層の上に形成されたものであってもよい。

**【 0 0 2 4 】**

このような成長用基板を用いた窒化物半導体基板であれば、成長用基板の表面側導電層によるリークパスが生じず、高周波特性に優れたものとすることができる。

**【 0 0 2 5 】**

また、前記複合基板は、多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層の裏面に積層された導電層と、該導電層の裏面に積層された第2の接着層と、前記第1の接着層の表面及び側面と前記導電層の側面と前記第2の接着層の側面及び裏面に積層されたバリア層とを含むものであり、かつ、

20

前記単結晶シリコン層は、前記複合基板の前記バリア層の表面に積層された平坦化層の上に形成されたものであってもよい。

**【 0 0 2 6 】**

このような成長用基板を用いた窒化物半導体基板であっても、成長用基板の表面側導電層によるリークパスが生じず、高周波特性に優れたものとすることができる。

**【 0 0 2 7 】**

このとき、前記導電層が、ポリシリコン層を含むものであることが好ましい。

**【 0 0 2 8 】**

また、前記導電層が、150～500nmの厚さを有するものであることが好ましい。

**【 0 0 2 9 】**

30

導電層は、このような層とすることができます。

**【 0 0 3 0 】**

このとき、前記多結晶セラミックコアが、窒化アルミニウムを含むものであることが好ましい。

**【 0 0 3 1 】**

このような複合基板とすれば、窒化物半導体との熱膨張係数差を極めて小さくできる。

**【 0 0 3 2 】**

また、前記第1の接着層及び前記第2の接着層はテトラエチルオルトシリケート(TEOS)層又は酸化ケイ素(SiO<sub>2</sub>)層を含み、前記バリア層は窒化ケイ素を含むものであることが好ましい。

40

**【 0 0 3 3 】**

また、前記第1の接着層及び前記第2の接着層は50～200nmの厚さを有し、前記バリア層は100～350nmの厚さを有するものであることが好ましい。

**【 0 0 3 4 】**

第1の接着層及び第2の接着層、及びバリア層の厚さは、このような厚さの層とすることができます。

**【 0 0 3 5 】**

また、前記平坦化層はテトラエチルオルトシリケート(TEOS)又は酸化ケイ素(SiO<sub>2</sub>)を含み、かつ、500～3000nmの厚さを有するものであることが好ましい。

**【 0 0 3 6 】**

50

平坦化層は、このような層とすることができます。

#### 【0037】

また本発明では、成長用基板と、該成長用基板上に成膜された窒化物半導体薄膜とを具備する窒化物半導体基板の製造方法であって、

(1) Y(イットリウム)を含有する前記成長用基板を準備する工程、及び

(2) 前記成長用基板上にAlN層をエピタキシャル成長させ、さらに前記AlN層上に窒化物半導体層をエピタキシャル成長させることにより、前記窒化物半導体薄膜を成膜する工程

を含み、かつ、

前記工程(2)において、前記成長用基板中のYを拡散させて、前記AlN層中の平均Y(イットリウム)濃度を、 $1E15 \text{ atoms/cm}^3$ 以上、 $5E19 \text{ atoms/cm}^3$ 以下とする窒化物半導体基板の製造方法を提供する。

#### 【0038】

このように成長用基板にY(イットリウム)が所定量含有されていれば、比較的簡単にAlN層に所定濃度のYを拡散させることができる。

#### 【0039】

また、前記AlN層の厚さを $50 \sim 150 \text{ nm}$ とし、かつ、前記窒化物半導体薄膜中ににおける前記成長用基板直上から薄膜成長方向に $300 \text{ nm}$ までの平均Y(イットリウム)濃度を $1E15 \text{ atoms/cm}^3$ 以上、 $5E19 \text{ atoms/cm}^3$ 以下とすることが好ましい。

#### 【0040】

このようにすれば、窒化物半導体薄膜中においてAlN層がイットリウム含有領域で十分に覆われているため、より確実に表面モフォロジーの良好なAlN層を形成し、窒化物半導体薄膜表面のピットの発生を抑制することができる。

#### 【0041】

また、前記成長用基板を、結合材料としてイットリア( $\text{Y}_2\text{O}_3$ )を含有する多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層全体に積層された第2の接着層と、該第2の接着層全体に積層されたバリア層とを含む複合基板と、該複合基板の片面のみに積層された平坦化層と、該平坦化層の上に形成された単結晶シリコン層により構成された成長用基板とし、かつ、前記単結晶シリコン層上に前記窒化物半導体薄膜を形成するようにし、かつ、

予め前記バリア層の厚さを調整することによって、前記AlN層中の平均Y(イットリウム)濃度を、 $1E15 \text{ atoms/cm}^3$ 以上、 $5E19 \text{ atoms/cm}^3$ 以下とすることが好ましい。

#### 【0042】

このような製造方法であれば、簡単でより確実に所定濃度のYを拡散させることができます。

#### 【0043】

また、前記複合基板を、前記第1の接着層と前記第2の接着層との間に、前記第1の接着層全体に積層された導電層を有するものとすることができる。

#### 【0044】

複合基板には、必要に応じて導電性を付与することができる。

#### 【0045】

また、前記成長用基板を、結合材料としてイットリア( $\text{Y}_2\text{O}_3$ )を含有する多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層全体に積層されたバリア層と、該バリア層の裏面に積層された第2の接着層と、該第2の接着層の裏面に積層された導電層とを含む複合基板と、該複合基板の前記バリア層の表面に積層された平坦化層と、該平坦化層の上に形成された単結晶シリコン層により構成された成長用基板とし、かつ、前記単結晶シリコン層上に前記窒化物半導体薄膜を形成するようにし、かつ、

10

20

30

40

50

予め前記バリア層の厚さを調整することによって、前記A1N層中の平均Y(イットリウム)濃度を、1E15atoms/cm<sup>3</sup>以上、5E19atoms/cm<sup>3</sup>以下とするようにしてもよい。

#### 【0046】

このような窒化物半導体基板の製造方法であれば、複合基板の表面側導電層によるリークパスが生じず、高周波特性に優れた窒化物半導体基板を製造することができる。

#### 【0047】

また、前記成長用基板を、結合材料としてイットリア(Y<sub>2</sub>O<sub>3</sub>)を含有する多結晶セラミックコアと、該多結晶セラミックコア全体に積層された第1の接着層と、該第1の接着層の裏面に積層された導電層と、該導電層の裏面に積層された第2の接着層と、前記第1の接着層の表面及び側面と前記導電層の側面と前記第2の接着層の側面及び裏面に積層されたバリア層とを含む複合基板と、該複合基板の前記バリア層の表面に積層された平坦化層と、該平坦化層の上に形成された単結晶シリコン層により構成された成長用基板とし、かつ、前記単結晶シリコン層上に前記窒化物半導体薄膜を形成するようにし、かつ、

予め前記バリア層の厚さを調整することによって、前記A1N層中の平均Y(イットリウム)濃度を、1E15atoms/cm<sup>3</sup>以上、5E19atoms/cm<sup>3</sup>以下とするようにしてもよい。

#### 【0048】

このような窒化物半導体基板の製造方法であっても、複合基板の表面側導電層によるリークパスが生じず、高周波特性に優れた窒化物半導体基板を製造することができる。

#### 【発明の効果】

#### 【0049】

以上のように、本発明であれば、A1N層の表面モフォロジーを改善して窒化物半導体エピタキシャルウェーハ表面のピットの発生を抑制することができる窒化物半導体基板、及びその製造方法を提供することができる。

#### 【図面の簡単な説明】

#### 【0050】

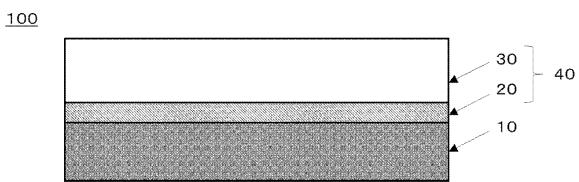

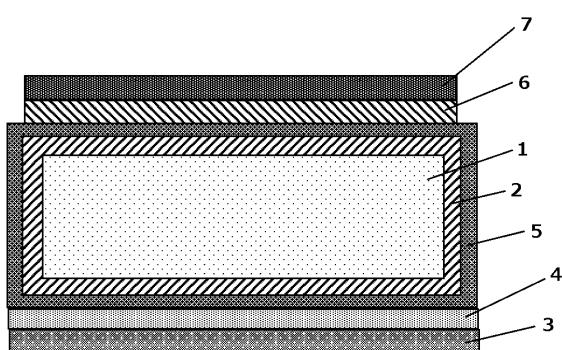

【図1】本発明の窒化物半導体基板の一例を示す概略図である。

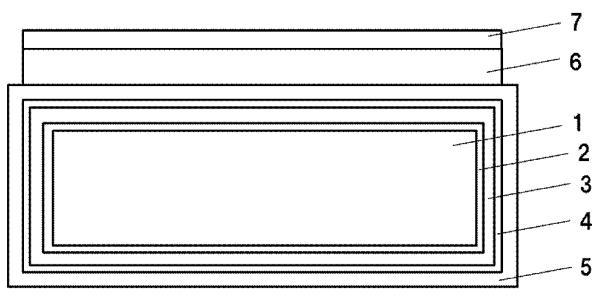

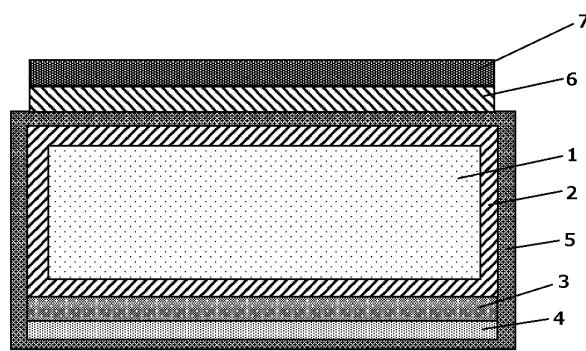

【図2】本発明に用いる成長用基板の一例を示す概略図である。

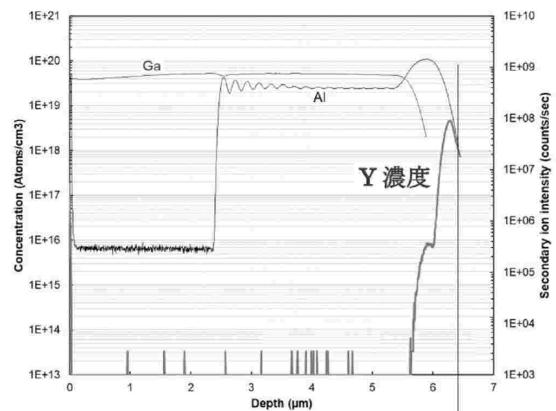

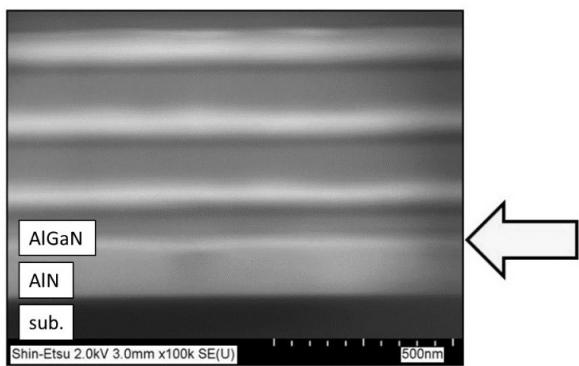

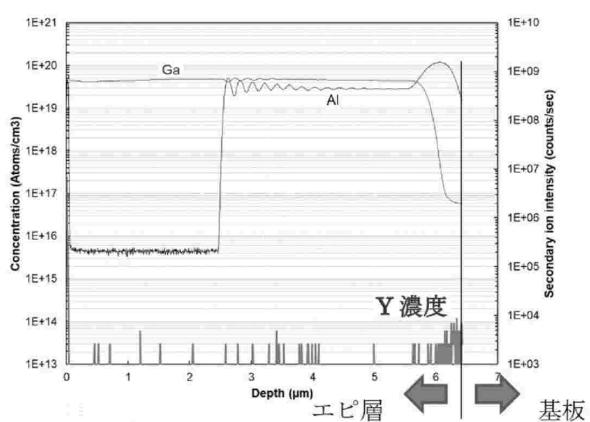

【図3】実施例1のバリア層が100nmのGaN用支持基板における、エピ構造1のSIMSプロファイルである。

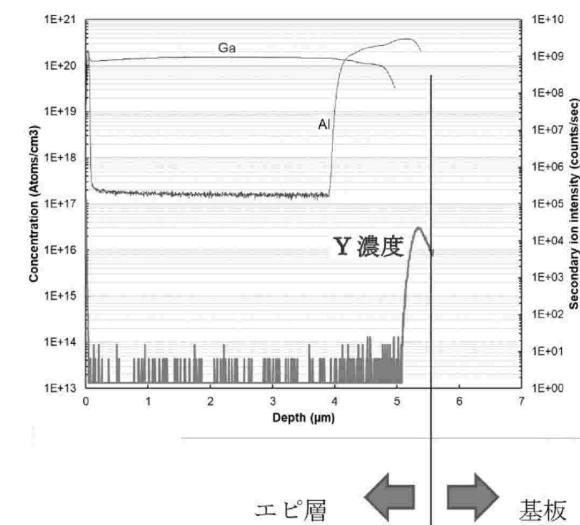

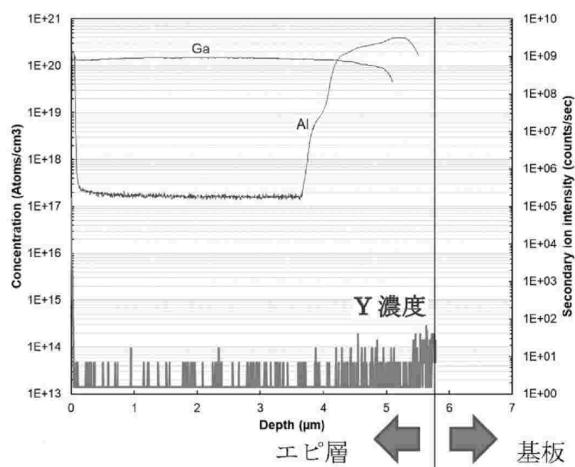

【図4】実施例1のバリア層が200nmのGaN用支持基板における、エピ構造2のSIMSプロファイルである。

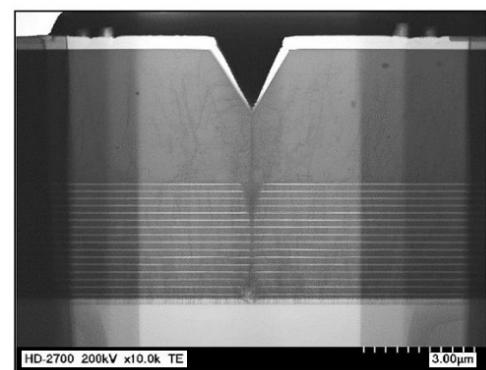

【図5】実施例で得られた窒化物半導体基板のエピタキシャル層と成長用基板界面のSEM像の一例である(エピ構造1)。

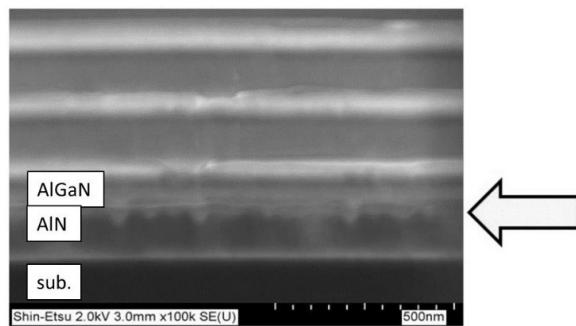

【図6】比較例1のバリア層が1000nmのGaN用支持基板における、エピ構造1のSIMSプロファイルである。

【図7】比較例1のバリア層が1000nmのGaN用支持基板における、エピ構造2のSIMSプロファイルである。

【図8】比較例2におけるエピ-基板界面のSEM像(エピ構造1)である。

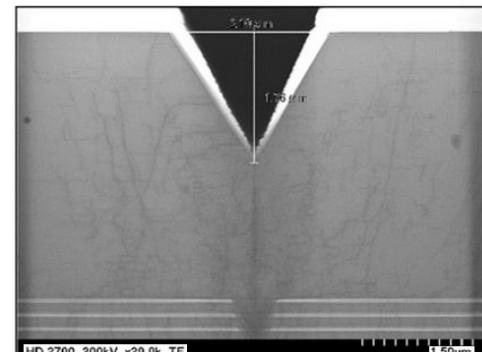

【図9】比較例2において窒化物半導体薄膜の表面に発生したピットの断面TEM像(エピ構造1)である。

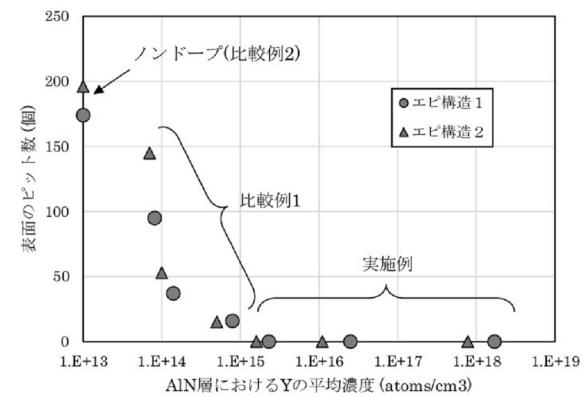

【図10】2水準のエピ構造における、A1N層中のY平均濃度とGaN層表面のピット数の関係を示すグラフである。

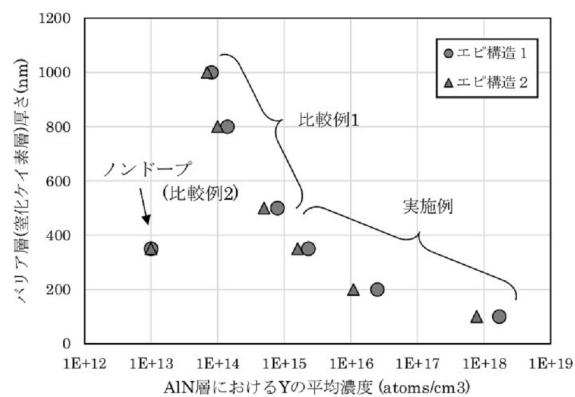

【図11】2水準のエピ構造における、A1N層中のY平均濃度とバリア層厚さの関係を示すグラフである。

【図12】本発明に用いる成長用基板の別の一例を示す概略図である。

【図13】本発明に用いる成長用基板のさらに別の例を示す概略図である。

#### 【発明を実施するための形態】

#### 【0051】

上述したように Si 基板や GaN 成長用支持基板に III 族窒化物半導体を成膜すると、エピタキシャルウェーハ表面にピットが発生し問題となる。これは、Si 基板や GaN 成長用基板直上に成膜する AlN 層の表面モフォロジーが悪いことが一因として挙げられる。

#### 【 0 0 5 2 】

本発明者らは、エピタキシャルウェーハ表面にピットが発生するのを抑制するため AlN 層の表面モフォロジーの改善について検討を重ねたところ、成長用基板上の窒化物半導体薄膜中に所定濃度のイットリウムを含有させることで AlN 層の表面モフォロジーが改善し、ピットの発生が抑制できることが判り、本発明を完成させた。

#### 【 0 0 5 3 】

即ち、本発明は、成長用基板と、該成長用基板上に成膜された窒化物半導体薄膜とを具備する窒化物半導体基板であって、前記窒化物半導体薄膜は、前記成長用基板上に形成された AlN 層と、該 AlN 層上に形成された窒化物半導体層とを含み、かつ、前記 AlN 層中の平均 Y (イットリウム) 濃度が、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下のものである窒化物半導体基板である。

#### 【 0 0 5 4 】

また本発明は、成長用基板と、該成長用基板上に成膜された窒化物半導体薄膜とを具備する窒化物半導体基板の製造方法であって、(1) Y (イットリウム) を含有する前記成長用基板を準備する工程、及び(2) 前記成長用基板上に AlN 層をエピタキシャル成長させ、さらに前記 AlN 層上に窒化物半導体層をエピタキシャル成長させることにより、前記窒化物半導体薄膜を成膜する工程を含み、かつ、前記工程(2)において、前記成長用基板中の Y を拡散させて、前記 AlN 層中の平均 Y (イットリウム) 濃度を、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下とする窒化物半導体基板の製造方法である。

#### 【 0 0 5 5 】

以下、本発明について詳細に説明するが、本発明はこれらに限定されるものではない。

#### 【 0 0 5 6 】

##### [ 窒化物半導体基板 ]

図 1 に本発明の窒化物半導体基板の一例を示す。本発明の窒化物半導体基板 100 は、成長用基板 10 の上に窒化物半導体薄膜 40 が成膜されており、窒化物半導体薄膜 40 は、成長用基板 10 の上に形成された AlN 層 20 と、AlN 層 20 の上に形成された窒化物半導体層 30 を含む。本発明の窒化物半導体基板 100 は、AlN 層 20 中にイットリウムを所定量含むことを特徴とし、AlN 層 20 中における平均 Y (イットリウム) 濃度が、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下である。

#### 【 0 0 5 7 】

AlN 層 20 における平均 Y (イットリウム) 濃度を $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下とすることによって、AlN 層の表面モフォロジーが改善し、AlN 層上に成長するエピタキシャル層 (窒化物半導体層 30) におけるピットの発生を抑制することができる。一方、AlN 层 20 における平均 Y 濃度が、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 未満ではピット抑制効果が十分に得られず、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> より高いと GaN 本来の特性が得られない。

#### 【 0 0 5 8 】

平均 Y (イットリウム) 濃度の測定方法としては特に限定はされないが、例えば、二次イオン質量分析 (SIMS) によって求めることができる。

#### 【 0 0 5 9 】

また本発明の窒化物半導体基板は、AlN 層の厚さが 50 ~ 150 nm であり、かつ、窒化物半導体薄膜中における成長用基板直上から薄膜成長方向に 300 nm までの平均 Y (イットリウム) 濃度が、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下のものであることが好ましい。このようにすれば、窒化物半導体薄膜中において AlN 層がイットリウム含有領域で十分に覆われているため、より確実に表面モフォロジーの

10

20

30

40

50

良好な AlN 層を形成し、窒化物半導体薄膜表面のピットの発生を抑制することができる。

#### 【0060】

窒化物半導体薄膜中、AlN 層の上に形成される窒化物半導体層は、GaN、AlN、及び AlGaN のうち 1 つ以上からなるものであることが好ましく、特には、AlGaN 上に GaN を積層した層、もしくは AlGaN 上に AlGaN、AlN、及び GaN からなる超格子構造が積層された層とすることがより好ましい。また、AlN 層と窒化物半導体層とを合わせた窒化物半導体薄膜の総膜厚は特に限定はされないが、例えば 0.5 ~ 2.0 μm、好ましくは 1 ~ 10 μm とすることができます。

#### 【0061】

成長用基板は、複数の層が積層された複合基板上に単結晶シリコン層が形成されたものであり、かつ、単結晶シリコン層上に窒化物半導体薄膜が成膜されたものであることが好ましい。

10

#### 【0062】

また成長用基板としては、以下に説明するような GaN 用支持基板とすることがより好ましい。GaN 用支持基板は、例えば、図 2 に示すように多結晶セラミックコア 1 と、該多結晶セラミックコア 1 全体に積層された第 1 の接着層 2 と、該第 1 の接着層 2 全体に積層された導電層 3 と、該導電層 3 全体に積層された第 2 の接着層 4 と、該第 2 の接着層 4 全体に積層されたバリア層 5 とを含む複合基板（支持構造）と、該複合基板の片面のみに積層された平坦化層 6 と、該平坦化層 6 に積層された単結晶シリコン層 7 により構成される。

20

#### 【0063】

尚、導電層 3 および第 1 の接着層 2 は必要に応じて成膜されるものであり、必ずしも存在するわけではなく、また片面のみに成膜されている場合もある。

#### 【0064】

ここで、多結晶セラミックコア 1 は窒化アルミニウムを含み、焼結助剤によって例えば 1800 の高温で焼結され、約 600 ~ 1150 μm の厚さを有することが好ましい。基本的には Si 基板の SEMI 規格の厚さで形成される場合が多い。

30

#### 【0065】

第 1 の接着層 2 および第 2 の接着層 4 は、テトラエチルオルトシリケート (TEOS) 層ないしは酸化ケイ素 (SiO<sub>2</sub>) 層、またはその両方を含む層で、LPCVD プロセスや CVD プロセス等によって堆積され、おおよそ 50 ~ 200 nm の厚さを有することが好ましい。

#### 【0066】

導電層 3 は、ポリシリコンを含み、LPCVD プロセス等によって堆積され、約 150 ~ 500 nm の厚さを有することが好ましい。これは導電性を付与するための層であり、例えばホウ素 (B) やリン (P) 等がドープされる。このポリシリコンを含む導電層 3 は、必要に応じて設けるものであって、なくても良く、また片面のみに成膜されていても良い。

#### 【0067】

バリア層 5 は、窒化ケイ素層を含み、LPCVD プロセス等によって堆積され、100 ~ 350 nm の厚さを有することが好ましい。

40

#### 【0068】

平坦化層 6 は、テトラエチルオルトシリケート (TEOS) 又は酸化ケイ素 (SiO<sub>2</sub>) を含み、LPCVD プロセス等によって堆積され、厚さは 500 nm ~ 3000 nm 程度であることが好ましい。この平坦化層は上面の平坦化のために堆積され、SiO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>、Si<sub>3</sub>N<sub>4</sub>、あるいは酸窒化珪素 (Si<sub>x</sub>O<sub>y</sub>N<sub>z</sub>) 等の通常のセラミックスの膜材等であってもよい。

#### 【0069】

単結晶シリコン層 7 は、約 100 ~ 500 nm の厚さを有することが好ましい。これは、GaN などの他のエピタキシャル成長のための成長面として利用される層であり、層転

50

写プロセス等を用いて平坦化層 6 に接合される。

【 0 0 7 0 】

尚、各層の厚さや製造方法、用いられる物質等は、上記の値に限定されず、必ずしもすべての層が存在するという訳ではない。

【 0 0 7 1 】

また、前記 G a N 用支持基板（成長用基板）の別の例としては、例えば図 1 2 に示すように多結晶セラミックコア 1 と、前記多結晶セラミックコアに全体に結合された第 1 の接着層 2 と、前記第 1 の接着層全体に結合されたバリア層 5 と、前記バリア層の裏面に結合された第 2 の接着層 4 と、前記第 2 の接着層の裏面に結合された導電層 3 とを含む複合基板と、前記複合基板の表面のみに結合された平坦化層 6 と、前記平坦化層に結合された単結晶シリコン層 7 により構成されることができる。

10

【 0 0 7 2 】

このような導電層 3 が裏面側にだけに成膜されている構造の成長用基板を用いた窒化物半導体基板であれば、高周波デバイスを作製する場合に成長用基板の表面側導電層によるリードパスが生じず、高周波特性に優れたものとすることができます。

【 0 0 7 3 】

また、前記 G a N 用支持基板（成長用基板）のさらに別の例としては、例えば図 1 3 に示すように多結晶セラミックコア 1 と、前記多結晶セラミックコアに全体に結合された第 1 の接着層 2 と、前記第 1 の接着層の裏面に結合された導電層 3 と、前記導電層の裏面に結合された第 2 の接着層 4 と、前記第 1 の接着層の表面及び側面と前記導電層の側面と前記第 2 の接着層の側面及び裏面に結合されたバリア層 5 とを含む複合基板と、前記複合基板の表面のみに結合された平坦化層 6 と、前記平坦化層に結合された単結晶シリコン層 7 により構成されることができる。

20

【 0 0 7 4 】

このような導電層 3 が裏面側にだけに成膜されている構造の成長用基板を用いた窒化物半導体基板であっても、高周波デバイスを作製する場合に成長用基板の表面側導電層によるリードパスが生じず、高周波特性に優れたものとすることができます。

【 0 0 7 5 】

[ 窒化物半導体基板の製造方法 ]

以下に、本発明の窒化物半導体基板の製造方法について説明する。

30

【 0 0 7 6 】

[ 第一の態様 ]

本発明の窒化物半導体基板の製造方法の第一の態様では、Y（イットリウム）を含有する成長用基板を準備し（工程（1））、該成長用基板上に窒化物半導体薄膜のエピタキシャル成長を行う際に成長用基板中のYを拡散させて、A l N 層中の平均 Y（イットリウム）濃度を所定範囲内とする（工程（2））。

【 0 0 7 7 】

< 工程（1）>

工程（1）は、Y（イットリウム）を含有する成長用基板を準備する工程である。

【 0 0 7 8 】

まず初めにエピタキシャル成長用の基板である、Yを含有する成長用基板を作製する。成長用基板としては、Yを含有していれば特に限定はされないが、例えば、上述した G a N 用支持基板を用いることができる。G a N 用支持基板内の多結晶セラミックコアに結合材料（例えば、焼結助剤）としてイットリア（Y<sub>2</sub>O<sub>3</sub>）を含めることで、それをY源とすることができます。

40

【 0 0 7 9 】

ここで、準備する G a N 用支持基板のバリア層（窒化ケイ素層）の厚さを予め調整しておくことで、後述の工程（2）でエピタキシャル層内に拡散するイットリウムの量を容易に制御することができ、より確実に A l N 層中の平均 Y 濃度を所定範囲内とすることができます。バリア層の厚さは、例えば、100 ~ 350 nm 以下とすることができます。

50

**【0080】**

&lt;工程(2)&gt;

工程(2)は、成長用基板上にAlN層をエピタキシャル成長させ、さらにAlN層上に窒化物半導体層をエピタキシャル成長させることにより、窒化物半導体薄膜を成膜する工程である。また本工程において、成長用基板中のYを拡散させて、AlN層中の平均Y(イットリウム)濃度を、 $1E15\text{ atoms/cm}^3$ 以上、 $5E19\text{ atoms/cm}^3$ 以下とする。

**【0081】**

工程(2)では、例えば、MOCVD反応炉において、GaN用支持基板上にAlN層(例えば、 $50\sim150\text{ nm}$ )、AlGaN層( $100\sim200\text{ nm}$ )およびGaN等のIIII族窒化物半導体薄膜のエピタキシャル成長を行う。エピタキシャル成長の際、Al源としてTMA1、Ga源としてTMGa、N源としてNH<sub>3</sub>を用いる。また、キャリアガスはN<sub>2</sub>およびH<sub>2</sub>、ないしはそのいずれかとし、プロセス温度は $900\sim1200$ 程度とする。

10

**【0082】**

このような工程を行うことで、AlN層中の平均Y濃度を、 $1E15\text{ atoms/cm}^3$ 以上、 $5E19\text{ atoms/cm}^3$ 以下の範囲とする。このようなイットリウム濃度とすることで、AlNの表面モフォロジーが改善し、ピットの発生を抑制することができる。

**【0083】****[第二の態様]**

また、本発明の窒化物半導体基板を製造する方法は、上述の第一の態様だけに限定されない。AlN層中にイットリウムを含有させる方法としては、上述のように拡散させる方法以外にAlN層のエピタキシャル成長時にY源ガスを流すようにしてもよい。

20

**【実施例】****【0084】**

以下、実施例及び比較例を用いて本発明を具体的に説明するが、本発明はこれらに限定されるものではない。

**【0085】****(実施例)**

エピタキシャル成長用の基板である、GaN用支持基板を作製した。GaN用支持基板は、多結晶セラミックコア(窒化アルミニウムコア)と、該多結晶セラミックコアに全体に積層された第1の接着層(酸化ケイ素層)と、該第1の接着層全体に積層された導電層(ポリシリコン層)と、該導電層全体に積層された第2の接着層(酸化ケイ素層)と、該第2の接着層全体に積層されたバリア層(窒化ケイ素層)とを含む複合基板と、該複合基板の片面のみに積層された平坦化層(酸化ケイ素層)と、該平坦化層の上に形成された単結晶シリコン層により構成した。バリア層の厚さは、 $100\text{ nm}$ 、 $200\text{ nm}$ 、 $350\text{ nm}$ の3水準とした。また、多結晶セラミックコア内には、Y源としてイットリア(Y<sub>2</sub>O<sub>3</sub>)を含めた。

30

**【0086】**

次に、MOCVD反応炉において、作製したGaN用支持基板上にAlN、AlGaNおよびGaN等のIIII族窒化物半導体薄膜のエピタキシャル成長を行った。GaN用支持基板はサテライトと呼ばれるウェーハポケットに載置した。エピタキシャル成長の際、Al源としてTMA1、Ga源としてTMGa、N源としてNH<sub>3</sub>を用いた。また、キャリアガスはN<sub>2</sub>およびH<sub>2</sub>とし、プロセス温度は $1200$ とした。

40

**【0087】**

サテライトの上にGaN用支持基板を載置し、エピタキシャル成長を行う際、エピタキシャル層は基板側から成長方向に向かって順にAlN、AlGaNを成膜し、その後GaNをエピタキシャル成長させた。エピタキシャル層の構造は2水準(エピ構造1、2)作製した。

**【0088】**

50

## &lt;エピ構造1&gt;

A<sub>1</sub>N層を150nm、A<sub>1</sub>GaN層を150nm製膜した後、A<sub>1</sub>GaN、A<sub>1</sub>N、GaNを数nmオーダーで繰り返し成膜するいわゆる超格子構造を3μm程度成膜した。その上にGaN層を成膜し、エピタキシャル層の合計の総膜厚は6.5μmとした。

## 【0089】

## &lt;エピ構造2&gt;

A<sub>1</sub>N層を150nm成膜後、成長方向につれてA<sub>1</sub>組成が低くなるようにA<sub>1</sub>GaNを1.5μm程度成膜した。その上にGaN層を成膜し、エピタキシャル層の合計の総膜厚は5.5μmとした。

## 【0090】

エピ構造1、2のいずれも、エピタキシャル層の表層側にはデバイス層を設けた。デバイス層は、2次元電子ガスが発生する結晶性の高いGaN層（チャネル層）を約400nm、2次元電子ガスを発生させるためのA<sub>1</sub>GaN層（バリア層）を約20nm、最表層に3nm程度のGaN層（キャップ層）を設けた構造とした。バリア層はA<sub>1</sub>組成を20%とした。

## 【0091】

エピタキシャル成長終了後、表面検査測定装置、および顕微鏡によって表面のピットの数をカウントした。また、SIMS分析（二次イオン質量分析法）によって、エピタキシャル層内のY（イットリウム）濃度を測定した。また、エピタキシャル層と成長基板界面の断面をSEM（走査型電子顕微鏡）にて観察し、A<sub>1</sub>N層のモフォロジーを確認した。

10

## 【0092】

## （比較例1）

実施例のGaN用支持基板作製の工程において、バリア層の厚さを、500nm、800nm、1000nmとした。これらの基板を用いて実施例と同様のエピタキシャル成長（2水準）、同様の評価を実施した。

20

## 【0093】

## （比較例2）

実施例のGaN用支持基板作製の工程において、多結晶セラミックコア内にイットリア（Y<sub>2</sub>O<sub>3</sub>）を含めない基板を作製した。また、バリア層の厚さは350nmとした。この基板を用いて、実施例と同様のエピタキシャル成長（2水準）、および同様の評価を実施した。また、発生したピットの断面TEM像を観察した。

30

## 【0094】

## 〔評価結果（実施例）〕

実施例で作製した、バリア層の厚さを100nmとしたときのエピ構造1の窒化物半導体基板、及びバリア層の厚さを200nmとしたときのエピ構造2の窒化物半導体基板のSIMS測定結果を図3、4に示す。これらの窒化物半導体基板はいずれもエピタキシャル層と成長用基板界面付近のエピタキシャル層内でY濃度が高くなっている、成長用基板直上のA<sub>1</sub>N層中の平均Y濃度が1E15atoms/cm<sup>3</sup>以上、5E19atoms/cm<sup>3</sup>以下の範囲内にあることが分かる。実施例で作製したその他の窒化物半導体基板も、A<sub>1</sub>N層中の平均Y濃度は上記範囲内であり、バリア層が薄いほど平均Y濃度が高くなることが確認された（図11）。

40

## 【0095】

またSEM観察の結果から、実施例で作製した窒化物半導体基板はいずれも、成膜用基板直上に形成されたA<sub>1</sub>N層が良好なモフォロジーを示していることが確認された（一例を図5に示す）。

## 【0096】

さらに、実施例で作製した窒化物半導体基板はいずれも、表面検査測定装置や顕微鏡観察によっては、表面のピットは確認されなかった（図10）。

## 【0097】

## 〔評価結果（比較例1、2）〕

50

比較例 1 で作製した、バリア層の厚さを 1 0 0 0 n m としたときのエピ構造 1 及びエピ構造 2 の窒化物半導体基板の S I M S 測定結果を図 6、7 に示す。これらの窒化物半導体基板はいずれもエピタキシャル層と成長用基板界面付近のエピタキシャル層内で Y 濃度が検出下限値以下であり、成長用基板直上の A 1 N 層中の平均 Y 濃度が  $1 E 1 5 a t o m s / c m^3$  を下回っていることが分かる。比較例 1、2 で作製したその他の窒化物半導体基板も、A 1 N 層中の平均 Y 濃度は  $1 E 1 5 a t o m s / c m^3$  を下回っており、バリア層が厚いほど平均 Y 濃度が低くなることが確認された（図 11）。

#### 【 0 0 9 8 】

また S E M 観察の結果から、比較例 1、2 で作製した窒化物半導体基板はいずれも、成膜用基板直上に形成された A 1 N 層のモフォロジーは不良であることが確認された（一例を図 8 に示す）。

10

#### 【 0 0 9 9 】

さらに、比較例 1、2 で作製した窒化物半導体基板はいずれも、表面検査測定装置や顕微鏡観察によって、表面に多数のピットが発生していることが確認された（後述の図 10 を参照）。また図 9 に、表面に発生したピットの T E M 画像を示す（図 9 中、（ a ）の画像を拡大したのが（ b ）の画像である）。

#### 【 0 1 0 0 】

#### 【 評価結果の考察 】

図 10 に示した A 1 N 層中の平均 Y 濃度と表面のピット数の関係の通り、実施例（本発明の窒化物半導体基板）はいずれも A 1 N 層中の平均 Y 濃度が  $1 E 1 5 a t o m s / c m^3$  以上、 $5 E 1 9 a t o m s / c m^3$  以下の範囲内にあるので、表面のピット発生を抑制できているが、比較例 1 のように A 1 N 層中の平均 Y 濃度が  $1 E 1 5 a t o m s / c m^3$  を少しでも下回ると、表面のピット発生を抑制できないことが分かる。

20

#### 【 0 1 0 1 】

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

10

20

30

40

50

【図 7】

【図 8】

10

【図 9】

(a)

(b)

【図 10】

20

30

40

50

【図 1 1】

【図 1 2】

10

【図 1 3】

20

30

40

50

---

フロントページの続き

審査官 佐藤 靖史

(56)参考文献 特表2019-523994 (JP, A)

特開2013-030763 (JP, A)

米国特許出願公開第2013/0048939 (US, A1)

特開2006-008416 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/20

H01L 21/205