(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3884024号

(P3884024)

(45) 発行日 平成19年2月21日(2007.2.21)

(24) 登録日 平成18年11月24日(2006.11.24)

(51) Int.C1.

F 1

|             |               |                  |             |                   |

|-------------|---------------|------------------|-------------|-------------------|

| <b>G02F</b> | <b>1/1345</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/1345</b>     |

| <b>G02F</b> | <b>1/1339</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/1339 500</b> |

| <b>G09F</b> | <b>9/30</b>   | <b>(2006.01)</b> | <b>G09F</b> | <b>9/30 321</b>   |

請求項の数 28 (全 21 頁)

(21) 出願番号 特願2004-100298 (P2004-100298)

(22) 出願日 平成16年3月30日 (2004.3.30)

(62) 分割の表示 特願平9-94606の分割

原出願日 平成9年3月27日 (1997.3.27)

(65) 公開番号 特開2004-234022 (P2004-234022A)

(43) 公開日 平成16年8月19日 (2004.8.19)

(54) 審査請求日 平成16年4月23日 (2004.4.23)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100116159

弁理士 玉城 信一

(72) 発明者 平形 吉晴

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 日夏 貴史

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第1の基板と、

前記第1の基板に対向し、対向電極が形成された第2の基板とを有し、

前記コモンコンタクト部には、

前記第1の基板に形成された第1の導電膜と、

前記第1の導電膜上に形成された絶縁膜と、

前記絶縁膜に形成された前記第1の導電膜に達する開口部と、

前記絶縁膜上に形成され、前記開口部において前記第1の導電膜に電気的に接続された第2の導電膜と、 10

前記第1の基板と前記第2の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、

前記導電性スペーサは前記絶縁膜上において、前記第2の導電膜と前記対向電極の双方に接しており、

前記画素領域において、前記絶縁膜上に前記画素電極が形成され、

前記第1の導電膜は、前記画素領域に形成された前記画素電極よりも下層の導電膜と同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とするアクティブマトリクス型表示装置。 20

**【請求項 2】**

請求項 1 において、前記第 2 の導電膜は金属薄膜であることを特徴とするアクティブマトリクス表示装置。

**【請求項 3】**

請求項 1 において、前記第 2 の導電膜は透光性を有する導電膜であることを特徴とするアクティブマトリクス表示装置。

**【請求項 4】**

請求項 3 において、前記透光性を有する導電膜は ITO 膜であることを特徴とするアクティブマトリクス型表示装置。

**【請求項 5】**

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第 1 の基板と、

前記第 1 の基板に対向し、対向電極が形成された第 2 の基板とを有し、

前記コモンコンタクト部には、

前記第 1 の基板に形成された第 1 の導電膜と、

前記第 1 の導電膜上に形成された絶縁膜と、

前記絶縁膜に形成された前記第 1 の導電膜に達する開口部と、

前記絶縁膜上に形成され、前記開口部において前記第 1 の導電膜に電気的に接続された第 2 の導電膜と、

前記第 1 の基板と前記第 2 の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、

前記導電性スペーサは前記絶縁膜上において、前記第 2 の導電膜と前記対向電極の双方に接しており、

前記第 2 の導電膜と前記画素電極とは同じ出発膜から形成され、

前記第 1 の導電膜は、前記画素領域に形成された前記画素電極よりも下層の導電膜と同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とするアクティブマトリクス型表示装置。

**【請求項 6】**

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第 1 の基板と、

前記第 1 の基板に対向し、対向電極が形成された第 2 の基板とを有し、

前記コモンコンタクト部には、

前記第 1 の基板に形成された第 1 の導電膜と、

前記第 1 の導電膜上に形成された絶縁膜と、

前記絶縁膜に形成された前記第 1 の導電膜に達する開口部と、

前記絶縁膜上に形成され、前記開口部において前記第 1 の導電膜に電気的に接続された第 2 の導電膜と、

前記第 1 の基板と前記第 2 の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、

前記導電性スペーサは前記絶縁膜上において、前記第 2 の導電膜と前記対向電極の双方に接しており、

前記第 1 の導電膜と前記薄膜トランジスタのソース電極及びドレイン電極とは同じ出発膜から形成され、前記第 2 の導電膜と前記画素電極とは同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とするアクティブマトリクス型表示装置。

**【請求項 7】**

請求項 6 において、前記第 1 の導電膜と前記ソース電極及び前記ドレイン電極とは、チタン膜、アルミニウム膜、チタン膜でなる多層膜から形成されたことを特徴とするアクティブマトリクス型表示装置。

10

20

30

40

50

**【請求項 8】**

請求項 5 乃至 7 のいずれか一項において、前記第 2 の導電膜と前記画素電極とは金属薄膜から形成されたことを特徴とするアクティブマトリクス型表示装置。

**【請求項 9】**

請求項 5 乃至 7 のいずれか一項において、前記第 2 の導電膜と前記画素電極とは透光性を有する導電膜から形成されたことを特徴とするアクティブマトリクス型表示装置。

**【請求項 10】**

請求項 9 において、前記透光性を有する導電膜は ITO 膜であることを特徴とするアクティブマトリクス型表示装置。

**【請求項 11】**

請求項 1 乃至 10 のいずれか一項において、前記第 2 の基板と前記対向電極との間の前記コモンコンタクト部と対向する箇所に、第 4 の導電膜が前記対向電極に接して形成されていることを特徴とするアクティブマトリクス型表示装置。

**【請求項 12】**

請求項 11 において、前記第 4 の導電膜には、少なくとも 1 つの開口部が形成されていることを特徴とするアクティブマトリクス型表示装置。

**【請求項 13】**

請求項 1 乃至 12 のいずれか一項において、前記薄膜トランジスタはトップゲート型薄膜トランジスタであることを特徴とするアクティブマトリクス型表示装置。

**【請求項 14】**

請求項 1 乃至 12 のいずれか一項において、前記薄膜トランジスタはボトムゲート型薄膜トランジスタであることを特徴とするアクティブマトリクス型表示装置。

**【請求項 15】**

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第 1 の基板と、

前記第 1 の基板に対向し、対向電極が形成された第 2 の基板とを有し、

前記コモンコンタクト部には、

前記第 1 の基板に形成された第 1 の絶縁膜と、

前記第 1 の絶縁膜上に形成された第 1 の導電膜と、

前記第 1 の導電膜上に形成された第 2 の絶縁膜と、

前記第 2 の絶縁膜に形成された前記第 1 の導電膜に達する開口部と、

前記第 2 の絶縁膜上に形成され、前記開口部において前記第 1 の導電膜に電気的に接続された第 2 の導電膜と、

前記第 1 の基板と前記第 2 の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、前記導電性スペーサは前記第 2 の絶縁膜上において、前記第 2 の導電膜と前記対向電極の双方に接しており、

前記画素領域には、前記第 1 の絶縁膜に前記薄膜トランジスタのソース電極及びドレイン電極が形成され、前記第 2 の絶縁膜上に前記画素電極が形成され、

前記開口部は、1 つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とするアクティブマトリクス型表示装置。

**【請求項 16】**

請求項 15 において、前記第 2 の導電膜は金属薄膜であることを特徴とするアクティブマトリクス表示装置。

**【請求項 17】**

請求項 15 において、前記第 2 の導電膜は透光性を有する導電膜であることを特徴とするアクティブマトリクス表示装置。

**【請求項 18】**

請求項 17 において、前記透光性を有する導電膜は ITO 膜であることを特徴とするアクティブマトリクス型表示装置。

**【請求項 19】**

10

20

30

40

50

薄膜トランジスタ、及び前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第1の基板と、前記第1の基板に対向し、対向電極が形成された第2の基板とを有し、

前記コモンコンタクト部には、

前記第1の基板に形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成された第1の導電膜と、

前記第1の導電膜上に形成された第2の絶縁膜と、

前記第2の絶縁膜に形成された前記第1の導電膜に達する開口部と、

前記第2の絶縁膜上に形成され、前記開口部において前記第1の導電膜に電気的に接続された第2の導電膜と、

前記第1の基板と前記第2の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、前記導電性スペーサは前記第2の絶縁膜上において、前記第2の導電膜と前記対向電極の双方に接しており、

前記画素領域には、前記第1の絶縁膜上に前記薄膜トランジスタのソース電極及びドレイン電極が形成され、前記第2の絶縁膜上に前記画素電極が形成され、

前記第1の導電膜と前記薄膜トランジスタのソース電極及びドレイン電極とは同じ出発膜から形成され、前記第2の導電膜と前記画素電極とは同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とするアクティブマトリクス型表示装置。

#### 【請求項20】

請求項19において、前記第1の導電膜と前記ソース電極及び前記ドレイン電極とは、チタン膜、アルミニウム膜、チタン膜でなる多層膜から形成されたことを特徴とするアクティブマトリクス型表示装置。

#### 【請求項21】

請求項19又は20において、前記第2の導電膜と前記画素電極とは金属薄膜から形成されたことを特徴とするアクティブマトリクス型表示装置。

#### 【請求項22】

請求項19又は20において、前記第2の導電膜と前記画素電極とは透光性を有する導電膜から形成されたことを特徴とするアクティブマトリクス型表示装置。

#### 【請求項23】

請求項22において、前記透光性を有する導電膜はITO膜であることを特徴とするアクティブマトリクス型表示装置。

#### 【請求項24】

請求項15乃至23のいずれか一項において、前記第1の絶縁膜は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜又はこれらの膜の多層膜であることを特徴とするアクティブマトリクス型表示装置。

#### 【請求項25】

請求項15乃至24のいずれか一項において、前記第2の基板と前記対向電極との間の前記コモンコンタクト部と対向する箇所に、第4の導電膜が前記対向電極に接して形成されていることを特徴とするアクティブマトリクス型表示装置。

#### 【請求項26】

請求項25において、前記第4の導電膜には、少なくとも1つの開口部が形成されていることを特徴とするアクティブマトリクス型表示装置。

#### 【請求項27】

請求項15乃至26のいずれか一項において、前記薄膜トランジスタはトップゲート型薄膜トランジスタであることを特徴とするアクティブマトリクス型表示装置。

#### 【請求項28】

請求項15乃至26のいずれか一項において、前記薄膜トランジスタはボトムゲート型薄膜トランジスタであることを特徴とするアクティブマトリクス型表示装置。

#### 【発明の詳細な説明】

10

20

30

40

50

**【技術分野】****【0001】**

本発明は対向する基板にそれぞれ形成された配線を導電性スペーサを介して電気的に接続するためのコンタクト構造に関する。特に、本発明は、液晶表示装置等の電気光学装置のコモンコンタクトに応用されるコンタクト構造に関する。

**【背景技術】****【0002】**

近年、モバイルコンピュータや携帯電話（P H S を含む）等の携帯情報端末機器（携帯機器）の表示部に液晶表示装置が広く使用されている。また液晶表示装置として、薄膜トランジスタをスイッチング素子に使用したアクティブマトリクス型の液晶表示装置が広く知られている。10

**【0003】**

液晶表示装置は2枚の基板に液晶を封入し、2枚の基板にそれぞれ形成された電極により電界を形成し、その電界強度を制御することにより表示を行っている。アクティブマトリクス型液晶表示装置においては、2枚の基板のうち、一方の基板は画素電極に電圧供給を制御するための薄膜トランジスタ（TFT）が形成されるため、TFT基板と呼ばれ、他方の基板は画素電極に対向する対向電極が形成されるため、対向基板と呼ばれている。

**【0004】**

アクティブマトリクス型表示装置においては、TFT基板上の画素電極と対向基板上の対向電極間で電界を発生して、表示を実現している。TFT基板上の画素電極の電位は薄膜トランジスタにより制御されて変動するが、対向基板上の対向電極は一定のコモン電位に固定される。対向電極をコモン電位に固定するために、対向電極は、TFT基板上に形成されたコモンコンタクトを介して取出し端子に接続され、この取出し端子は基板外部の電源に接続される。このような接続構成により、対向電極の電位は電源によりコモン電位に固定される。20

**【0005】**

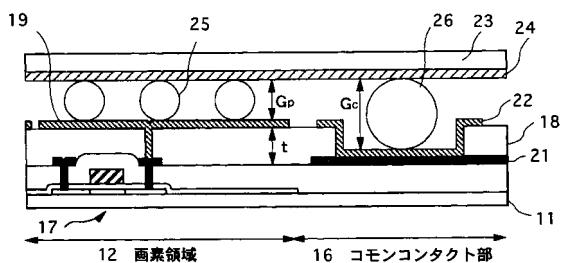

以下に、図12～図14を用いて、従来のアクティブマトリクス型表示装置のコモンコンタクトの構造を簡単に説明する。

**【0006】**

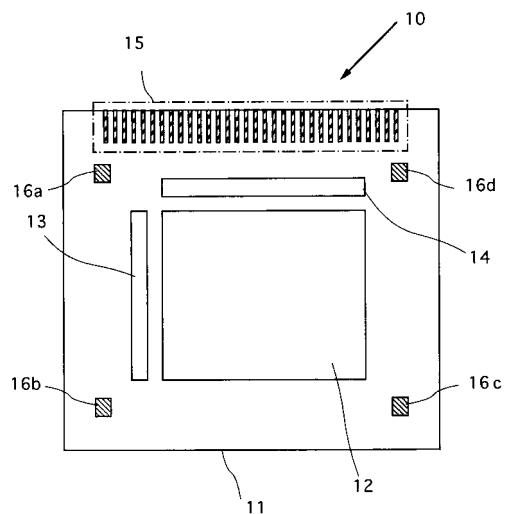

図12はTFT基板10の上面図であり、基板11上には、画素電極、画素電極に接続された薄膜トランジスタがマトリクス状に配置された画素領域12と、薄膜トランジスタのON/OFFのタイミングを制御するための走査線駆動回路13と、画素電極に画像データを供給するための信号線駆動回路14が設けられている。更に、外部から電力や制御信号を供給するための取出し端子15が設けられ、対向電極との接続部となるコモンコンタクト部16a～16dが設けられている。30

**【0007】**

図13は画素領域12及びコモンコンタクト部16の断面構成図である。図13に示すように、TFT基板11の画素領域12には、基板11上に薄膜トランジスタ17が形成され、薄膜トランジスタ17上には層間絶縁膜18が形成され、層間絶縁膜18上には、薄膜トランジスタ17のドレイン電極に接続された画素電極19が形成されている。40

**【0008】**

コモンコンタクト部16において、内部配線21が薄膜トランジスタ17のソース・ドレイン電極の出発膜をパターニングして形成されている。層間絶縁膜18には矩形状の開口部が形成され、この開口部において内部配線21に接続される導電性パッド22が形成されている。画素電極19と導電性パッド22は同じ出発膜からパターニングされている。

**【0009】**

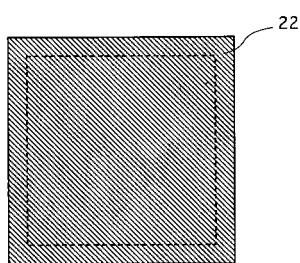

図14は従来例のコモンコンタクト部16の上面図であり、導電性パッド22の内側の点線の領域が層間絶縁膜18に形成された開口部に相当する。

**【0010】**

図13に示すように、対向基板23表面には透明導電膜でなる対向電極24が形成され、対向電極24は画素領域12において画素電極19に対向し、コモンコンタクト部16において導電性パッド22と対向する。

#### 【0011】

そして、基板11と23の間隔を保持するため、画素領域12には球状の絶縁性のスペーサ25が配置され、コモンコンタクト部16には球状の導電性スペーサ26が配置される。導電性スペーサ26により対向電極24はTFT基板の導電性パッド22に電気的に接続される。導電性パッド22は内部配線21に電気的に接続され、内部配線21は取出し端子15に電気的に接続されている。このような接続構成により、対向基板23側の対向電極24は、TFT基板11側の取出し端子15に接続されている。

10

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

従来の液晶表示装置においては、図13に示すように、コモンコンタクト部16には層間絶縁膜18に開口部が形成されるため、(コモンコンタクト部のセルギャップGc)+(画素領域のセルギャップGp)+(層間絶縁膜18の膜厚t)の関係がある。

#### 【0013】

画素領域12のセルギャップGpはスペーサ25により規定される。スペーサ25には規格品が用いられるため、スペーサ25の径が同じであれば、画素領域12のセルギャップGpは基板ごとにほぼ同じになる。しかしながら、コモンコンタクト部のセルギャップGcが基板ごとにばらつくことを避けることは、困難である。

20

#### 【0014】

コモンコンタクト部のセルギャップGcは、上記の関係からセルギャップGpが一定なため、層間絶縁膜18の膜厚tのみに依存する。よって、基板ごとにセルギャップGcを一定にするには層間絶縁膜18の膜厚tをばらつかないようにする必要があるが、この層間絶縁膜18の膜厚tは、基板ごとに同じ膜厚tになるように成膜しても、基板ごとにその膜厚tがばらつくことは避けられない。

#### 【0015】

また、液晶表示装置のコモンコンタクト部は通常2~4個形成されるが、同一基板でも層間絶縁膜18の膜厚tが場所ごとに異なる場合があり、このような場合には、同一基板であってもコモンコンタクト部ごとに膜厚tが異なるおそれもある。

30

#### 【0016】

このような層間絶縁膜18の膜厚tのばらつきため、コモンコンタクト部のセルギャップGcは基板ごと、あるいはコモンコンタクト部ごとにばらついてしまう。更に、このセルギャップGcのばらつきにより、画素領域のセルギャップGpのばらつきを生じてしまう。

#### 【0017】

このコモンコンタクト部のセルギャップGcのばらつきが画素領域のセルギャップGpに与える影響は、画素領域12の面積がコモンコンタクト部の面積より相対的に狭くなる程顕在化することになる。特に、プロジェクターなどに用いる投射用ディスプレイは、1~2inch程度の極めて高精細な小型ディスプレイであるため、上述の画素領域のセルギャップGpのばらつきの問題が顕在化してしまう。

40

#### 【0018】

また、導電性スペーサ26も規格品が用いられるが、その径は画素領域12のスペーサ25の径と設計時の層間絶縁膜18の膜厚で決定される。しかしながら、層間絶縁膜18の膜厚が設計値よりも非常に厚くなつた場合、コモンコンタクト部のセルギャップGcが非常に大きくなるため、導電性スペーサ26により、対向電極を導電性パッドに良好に接続することができなくなってしまう。このような場合には、対向電極の電位をコモン電位に固定できなくなり、表示が行えなくなる。

#### 【0019】

50

本発明の目的は、上記の問題点を解消し、層間絶縁膜の膜厚がばらついても、基板ごとの基板間隔のばらつきをなくし、かつ導電性スペーサが原因となる接触不良の発生を減少することを可能にしたコンタクト構造を提供することにある。

**【課題を解決するための手段】**

**【0020】**

上述した問題点を解消するために、本発明の構成は、

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第1の基板と、

前記第1の基板に対向し、対向電極が形成された第2の基板とを有し、

前記コモンコンタクト部には、

前記第1の基板に形成された第1の導電膜と、

前記第1の導電膜上に形成された絶縁膜と、

前記絶縁膜に形成された前記第1の導電膜に達する開口部と、

前記絶縁膜上に形成され、前記開口部において前記第1の導電膜に電気的に接続された第2の導電膜と、

前記第1の基板と前記第2の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、

前記導電性スペーサは前記絶縁膜上において、前記第2の導電膜と前記対向電極の双方に接しており、

前記画素領域において、前記絶縁膜上に前記画素電極が形成され、

前記第1の導電膜は、前記画素領域に形成された前記画素電極よりも下層の導電膜と同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とする。

**【0021】**

更に、本発明の他の構成は、

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第1の基板と、

前記第1の基板に対向し、対向電極が形成された第2の基板とを有し、

前記コモンコンタクト部には、

前記第1の基板に形成された第1の導電膜と、

前記第1の導電膜上に形成された絶縁膜と、

前記絶縁膜に形成された前記第1の導電膜に達する開口部と、

前記絶縁膜上に形成され、前記開口部において前記第1の導電膜に電気的に接続された第2の導電膜と、

前記第1の基板と前記第2の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、

前記導電性スペーサは前記絶縁膜上において、前記第2の導電膜と前記対向電極の双方に接しており、

前記第2の導電膜と前記画素電極とは同じ出発膜から形成され、

前記第1の導電膜は、前記画素領域に形成された前記画素電極よりも下層の導電膜と同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とする。

**【0022】**

更に、本発明の他の構成は、

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第1の基板と、

前記第1の基板に対向し、対向電極が形成された第2の基板とを有し、

前記コモンコンタクト部には、

10

20

30

40

50

前記第1の基板に形成された第1の導電膜と、

前記第1の導電膜上に形成された絶縁膜と、

前記絶縁膜に形成された前記第1の導電膜に達する開口部と、

前記絶縁膜上に形成され、前記開口部において前記第1の導電膜に電気的に接続された第2の導電膜と、

前記第1の基板と前記第2の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、

前記導電性スペーサは前記絶縁膜上において、前記第2の導電膜と前記対向電極の双方に接しており、

前記第1の導電膜と前記薄膜トランジスタのソース電極及びドレイン電極とは同じ出発膜から形成され、前記第2の導電膜と前記画素電極とは同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とする。

#### 【0023】

更に、本発明の他の構成は、

薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第1の基板と、

前記第1の基板に対向し、対向電極が形成された第2の基板とを有し、

前記コモンコンタクト部には、

前記第1の基板に形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成された第1の導電膜と、

前記第1の導電膜上に形成された第2の絶縁膜と、

前記第2の絶縁膜に形成された前記第1の導電膜に達する開口部と、

前記第2の絶縁膜上に形成され、前記開口部において前記第1の導電膜に電気的に接続された第2の導電膜と、

前記第1の基板と前記第2の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、前記導電性スペーサは前記第2の絶縁膜上において、前記第2の導電膜と前記対向電極の双方に接しており、

前記画素領域には、前記第1の絶縁膜に前記薄膜トランジスタのソース電極及びドレイン電極が形成され、前記第2の絶縁膜上に前記画素電極が形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とする。

#### 【0024】

更に、本発明の他の構成は、

薄膜トランジスタ、及び前記薄膜トランジスタに電気的に接続された画素電極が配置されている画素領域と、コモンコンタクト部とが設けられた第1の基板と、前記第1の基板に対向し、対向電極が形成された第2の基板とを有し、

前記コモンコンタクト部には、

前記第1の基板に形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成された第1の導電膜と、

前記第1の導電膜上に形成された第2の絶縁膜と、

前記第2の絶縁膜に形成された前記第1の導電膜に達する開口部と、

前記第2の絶縁膜上に形成され、前記開口部において前記第1の導電膜に電気的に接続された第2の導電膜と、

前記第1の基板と前記第2の基板との間に挟まれた複数の球状の導電性スペーサとが設けられ、前記導電性スペーサは前記第2の絶縁膜上において、前記第2の導電膜と前記対向電極の双方に接しており、

前記画素領域には、前記第1の絶縁膜上に前記薄膜トランジスタのソース電極及びドレイン電極が形成され、前記第2の絶縁膜上に前記画素電極が形成され、

前記第1の導電膜と前記薄膜トランジスタのソース電極及びドレイン電極とは同じ出発

膜から形成され、前記第2の導電膜と前記画素電極とは同じ出発膜から形成され、

前記開口部は、1つの前記導電性スペーサが占める面積よりも広く、前記導電性スペーサが自由に移動できる面積を有することを特徴とする。

**【発明の効果】**

**【0025】**

本発明のコモンコンタクト構造により、層間絶縁膜の膜厚がばらついても、基板ごとの基板間隔のばらつきをなくし、かつ導電性スペーサが原因となる接触不良の発生を減少することができる。

**【0026】**

即ち、本発明においては、基板間隔は導電性スペーサの大きさのみに依存することになるため、導電性スペーサの大きさが同じであれば、第1の導電膜と第2の導電膜とを絶縁している絶縁膜の厚さが基板ごとに異なっても、その対向する基板の間隔を基板ごとに同じにすることができる。

**【発明を実施するための最良の形態】**

**【0027】**

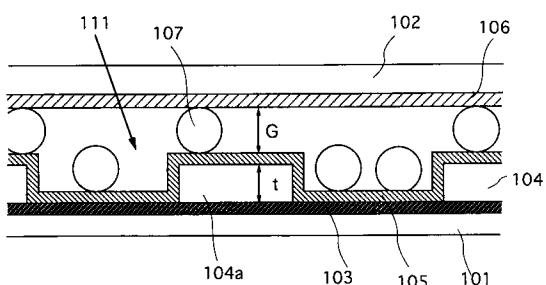

図1、図2を用いて本発明の実施の形態を説明する。

**【0028】**

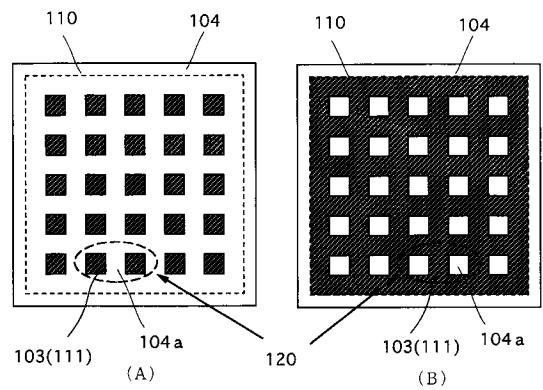

[実施の形態1] 図1は本実施の形態のコモンコンタクト部の断面構成図であり、図2はTFT基板側の上面図である。また、図2(A)に示す領域120の断面拡大図が図1に相当する。

**【0029】**

図13に示すように、従来例では画素領域12のスペーサは画素電極19を介して、層間絶縁膜18上に配置されるが、コモンコンタクト部16の導電性パッド22の下層には層間絶縁膜18が存在しない。層間絶縁膜18が存在しないことが、コモンコンタクト部のセルギャップGcが層間絶縁膜18の膜厚に依存することの原因である。

**【0030】**

そこで、本実施形態においては、コモンコンタクト部にも導電性パッドの下層に絶縁体を存在させ、絶縁体上に導電性スペーサを配置することにより、コモンコンタクト部のセルギャップGcが層間絶縁膜18の膜厚に依存しないようにするものであり、本実施形態では、層間絶縁膜18を選択的に残存するよう開口部を形成することを特徴とする。

**【0031】**

本実施形態において、第1の基板101には第1の導電膜103と、第1の導電膜103を覆う絶縁膜104と、絶縁膜104を選択的に残存して開口され第1の導電膜103を露出する開口部111と、残存された前記絶縁膜104aと開口部111とを覆う第2の導電膜105がそれぞれ形成される。

**【0032】**

第2の基板102上には第3の導電膜106が形成され、第1の基板101と第2の基板102との間には、導電性スペーサ107が挟持されている。

**【0033】**

図13に示す従来のコモンコンタクト部16であれば、開口部110においては、層間絶縁膜18はすべて除去されていたが、本実施形態では、絶縁膜104aを選択的に残存させて開口部111を形成する。この開口部111により第1の導電膜103が露出され、ここで第1の導電膜103と第2の導電膜105とが接続される。

**【0034】**

また、第1の基板101側において、残存された絶縁膜104aが最も第2の基板102に接近しているため、図1に示すように、この残存された絶縁膜104a上において、導電性スペーサ107により、第1の基板上の第2の導電膜105と第2の基板102上の第3の導電膜106が電気的に接続される。

**【0035】**

更に、開口部110では残存された絶縁膜104aが最も第2の基板に接近しているた

10

20

50

30

40

50

め、第2の導電膜105と第3の導電膜106を電気的に接続している導電性スペーサ107により、基板間隔Gが保持される。よって、この基板間隔Gは導電性スペーサ107の大きさのみに依存することになる。従って、導電性スペーサ107の大きさが同じであれば、絶縁膜104の厚さtが基板ごとに異なっても、その基板間隔Gは基板ごとに同じにすることができる。

#### 【0036】

また、本実施形態において、開口部111の面積は1つの導電性スペーサが占める面積よりも十分に広く、導電性スペーサが自由に移動できるような余裕を持たせることが好ましい。この理由は開口部111に存在する導電性スペーサ107がギャップの保持には寄与しないようにするためである。もし、この領域に導電性スペーサが自由に移動できるような余裕がないと、ここで導電性スペーサ107が複数個積み重なってしまい、基板間隔Gを基板全体で均一にすることができなくなる。

#### 【0037】

更に、本実施形態において、残存された絶縁膜104a表面の面積は1つの導電性スペーサ107が占めるよりも十分に広く、導電性スペーサ107が確実に配置されるような空間であることが好ましい。これは、絶縁膜104a上に導電性スペーサ107が確実に配置されないと、第1の基板と第2の基板間で電気的な接続を取ることができず、更にギャップを保持することもできなくなるからである。

#### 【0038】

また、本実施形態において、図2(A)に示すように開口部111を形成したが、図2(B)に示すように、残存された絶縁膜104aと開口部111の関係を逆にすることもできる。なお、図2(A)で点線で示す領域120の拡大断面図が図1に相当する。

#### 【0039】

[実施形態2] 図1、図2(A)を用いて本発明の実施の形態を説明する。図1は本実施の形態のコモンコンタクト部の断面構成図であり、図2(A)はTFT基板側の上面図である。図2(A)で点線で示す領域120の拡大断面図が図1に相当する。

#### 【0040】

本実施形態も実施形態1と同様に、コモンコンタクト部にも導電性パッドの下層に絶縁体を存在させ、絶縁体上に導電性スペーサを配置することにより、コモンコンタクト部のセルギャップGcが層間絶縁膜18の膜厚に依存しないものである。そこで、本実施形態では、層間絶縁膜18を選択的に残存するように開口部を形成することを特徴とする。

#### 【0041】

即ち、本実施形態においては、導電性パッド22の下層に絶縁体を形成し、この絶縁体上に導電性スペーサを配置することにより、コモンコンタクト部のセルギャップGcが層間絶縁膜18の膜厚に依存しないようにした。

#### 【0042】

図1に示すように、第1の基板101には、第1の導電膜103と、第1の導電膜103を覆う絶縁膜104と、絶縁膜104に形成された第1の導電膜103を露出する開口部111と、開口部111より露出された第1の導電膜103表面に選択的に形成された絶縁膜104aと、開口部111を覆う第2の導電膜105が形成されている。

#### 【0043】

第2の基板102上には第3の導電膜106が形成され、第1の基板101と第2の基板102との間には導電性スペーサ107が配置されている。

#### 【0044】

図2(A)はTFT基板側の上面図であり、第2の導電膜105が形成されていない状態を示す。図2(A)において、点線で示す開口部110は従来例の層間絶縁膜18に形成されたコモンコンタクト用の開口部に相当する。本実施形態では、この開口部110に、第1の導電膜103が露出される部分を残すように、選択的に絶縁膜104aを形成する。

10

20

30

40

50

**【0045】**

開口部110において、絶縁膜104aが形成されない領域では、第1の導電膜103が露出され、その上に形成される第2の導電膜105と接続される。

**【0046】**

また、第1の基板101側において、開口部110では絶縁膜104aが最も第2の基板に接近しているため、図1に示すように、この絶縁膜104a上において、導電性スペーサ107により、第1の基板101上の第2の導電膜105と第2の基板102上の第3の導電膜106が電気的に接続される。

**【0047】**

更に、開口部110では絶縁膜104aが最も第2の基板102に接近しているため、

10 第2の導電膜105と第3の導電膜106を電気的に接続している導電性スペーサ107により、基板間隔Gが保持される。よって、この基板間隔Gは導電性スペーサ107の大きさのみに依存することになる。従って、導電性スペーサ107の大きさが同じであれば、絶縁膜104の厚さtが基板ごとに異なっても、その基板間隔Gを基板ごとに同じにすることができる。

**【0048】**

本実施形態において、絶縁膜104aが形成されない領域の面積は1つの導電性スペーサ107が占めるよりも十分に広く、導電性スペーサ107が自由に移動できるような余裕を持たせることができが好ましい。この理由は絶縁膜104aが形成されない領域に存在する導電性スペーサ107がギャップの保持には寄与しないようにするためである。もし、この領域に導電性スペーサが自由に移動できるような余裕がないと、ここで導電性スペーサ107が複数個積み重なってしまい、基板間隔Gを基板全体で均一にすることはできなくなってしまう。

20

**【0049】**

更に、本実施形態において、絶縁膜104aの表面の面積は1つの導電性スペーサ107が占めるよりも十分に広く、導電性スペーサ107が確実に配置されるような空間であることが好ましい。これは、絶縁膜104a上に導電性スペーサ107が確実に配置されないと、第1と第2の基板間で電気的な接続を取ることができず、更にギャップを保持することができなくなるからである。

**【0050】**

また、本実施形態において、図2(A)に示すように絶縁膜104aを形成したが、図2(B)に示すように、絶縁膜104aを形成する領域と、第1の導電膜103を露出させる領域の関係を逆にすることもできる。

30

**【実施例1】****【0051】**

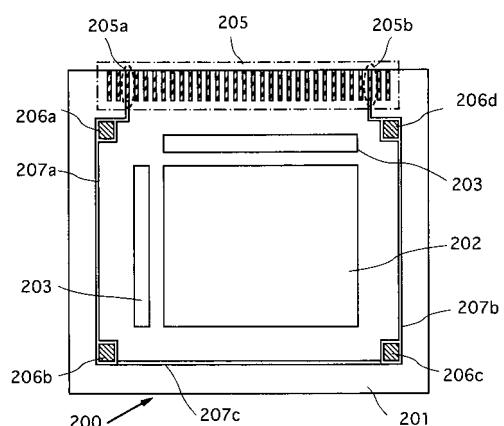

本実施例では本発明を反射型液晶表示装置のコモンコンタクト部に応用した例を示す。図3は本実施例のTFT基板の上面図であり、図4は対向基板の上面図である。

**【0052】**

図3に示すように、TFT基板200において、基板201上には、画素電極、画素電極に接続された薄膜トランジスタがマトリクス状に配置された画素領域202と、薄膜トランジスタのON/OFFのタイミングを制御するための走査線駆動回路203と、画素電極に画像データを供給するための信号線駆動回路204が設けられている。更に、外部から電力や制御信号を供給するための取出し端子205が設けられ、対向電極との接続部となるコモンコンタクト部206a～206dが設けられている。

40

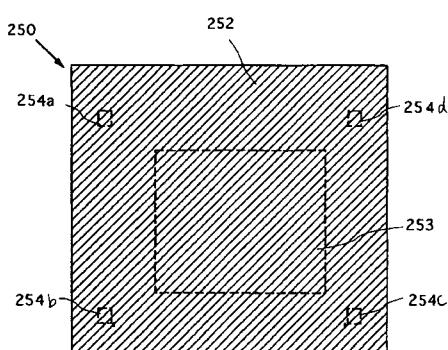

**【0053】**

図4に示すように、対向基板250は、基板上に透光性導電膜からなる対向電極252が形成されている構造を有する。中央部の矩形の領域253はTFT基板200の画素領域202と対向する領域であり、4隅の領域254a～254dはTFT基板200のコントラクト部206a～206dと電気的に接続される領域である。

**【0054】**

10

20

20

30

40

50

そして、図3に示すように、TFT基板200のコモンコンタクト部206a～206dにはそれぞれ導電性パッドが形成されている。これら導電性パッドは内部配線207a～207cによって電気的に接続されている。また、内部配線207a、207bは取出し端子205に延在し、コモン端子205a、205bに電気的に接続されている。

#### 【0055】

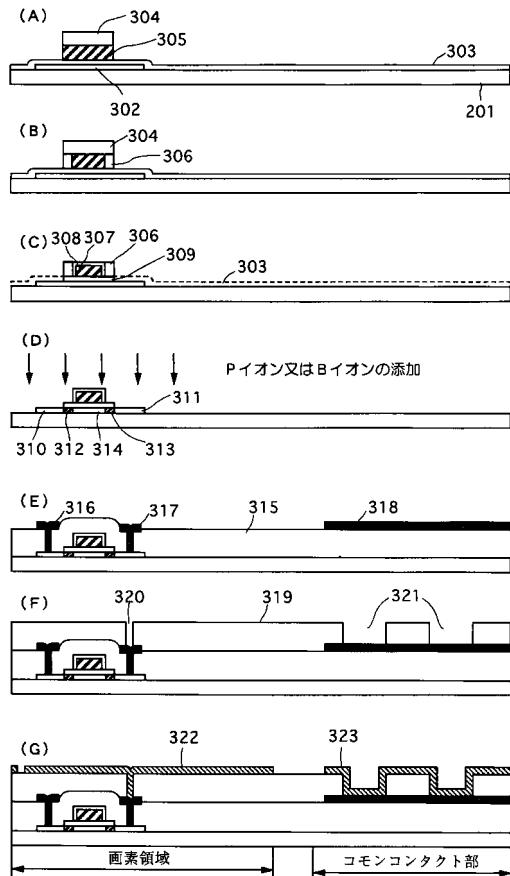

以下、TFT基板の画素領域202、及びコモンコンタクト部206を作製する工程を図5を用いて説明する。

#### 【0056】

まず、絶縁表面を有する基板201を用意する。本実施例ではガラス基板上に下地膜として酸化珪素膜を形成した。基板201の上には結晶性珪素膜でなる活性層302を形成する。なお、本実施例では1つの薄膜トランジスタのみを図示しているが、実際には、画素領域202には100万個以上の薄膜トランジスタが形成される。10

#### 【0057】

本実施例では非晶質珪素膜を熱結晶化させて結晶性珪素膜を得ている。そして、その結晶性珪素膜を通常のフォトリソ工程でパターニングして活性層302を得る。なお、本実施例では結晶化の際に結晶化を助長する触媒元素（ニッケル）を添加している。この技術については特開平7-130652号公報に詳細に記載されている。

#### 【0058】

次に、150nmの厚さの酸化珪素膜303を形成し、その上に0.2wt%のスカンジウムを含有させたアルミニウム膜（図示せず）を成膜し、レジストマスク304を用いてアルミニウム膜をパターニングし、ゲイト電極の原型となる島状パターン305を形成した（図5（A））。20

#### 【0059】

本実施例では、ここで特開平7-135318号公報に記載された陽極酸化技術を利用する。なお、詳細は同公報を参考にすると良い。

#### 【0060】

まず、上記島状パターン305上にパターニングで使用したレジストマスク304を残したまま、3%のシュウ酸水溶液中で陽極酸化を行う。この時、白金電極を陰極として2～3mVの化成電流を流し、到達電圧は8Vとする。この結果、上面にレジストマスク304が存在しているため、多孔質状の陽極酸化膜306が島状パターン305の側面に形成される（図5（B））。30

#### 【0061】

その後、レジストマスク304を除去した後に3%の酒石酸のエチレングリコール溶液をアンモニア水で中和した溶液中で陽極酸化を行う。この時、化成電流は5～6mVとし、到達電圧は100Vとすれば良い。こうして、緻密な陽極酸化膜307が形成される。

#### 【0062】

そして、上記陽極酸化工程によって、島状パターン305の陽極酸化されない部分がゲイト電極308として画定する。なお、コモンコンタクト部206c、206dを接続する内部配線207cも、上記アルミニウム膜を出発膜として、ゲイト電極308の形成と同時に形成されている。40

#### 【0063】

次に、ゲイト電極308及びその周囲の陽極酸化膜306、307をマスクとして酸化珪素膜303をエッチングし、ゲイト絶縁膜309を形成する。エッチングはCF4ガスを用いたドライエッティング法を採用した（図5（C））。

#### 【0064】

ゲイト絶縁膜309を形成した後、多孔質状の陽極酸化膜306をアルミ混酸を用いたウェットエッティングにより、除去した。

#### 【0065】

次に、イオン注入法またはプラズマドーピング法により一導電性を付与する不純物イオンを添加する。画素領域にN型薄膜トランジスタを配置するならばP（リン）イオンを、50

P型薄膜トランジスタを配置するならばB(ボロン)イオンを添加すれば良い。

#### 【0066】

本実施例では、上記不純物イオンの添加工程をイオン注入法を用いて、2度に分けて行った。1度目は80keVの高加速電圧で行い、ゲイト絶縁膜309の端部(突出部)の下に不純物イオンのピークがくるように調節した。そして、2度目は5keVの低加速電圧で行い、ゲイト絶縁膜309の端部(突出部)の下に不純物イオンが添加されないように、加速電圧を調節した。

#### 【0067】

こうして薄膜トランジスタのソース領域310、ドレイン領域311、低濃度不純物領域312、313、チャネル形成領域314が形成される。なお、ドレイン領域311側の低濃度不純物領域313はLDD領域とも呼ばれる(図5(D))。

#### 【0068】

この時、ソース、ドレイン領域310、311は300~500/ $\mu$ mのシート抵抗が得られる程度に不純物イオンを添加することが好ましい。また、低濃度不純物領域312、313は薄膜トランジスタの性能に合わせて最適化を行う必要がある。不純物イオンの添加工程が終了したら熱処理を行い、不純物イオンの活性化を行った。

#### 【0069】

次に、第1の層間絶縁膜315として酸化珪素膜を1 $\mu$ mの厚さに形成した。第1の層間絶縁膜315の膜厚を1 $\mu$ mと膜厚にしたのは第1の層間絶縁膜315の表面をできるだけ平坦にするためであり、膜厚にすることで、ゲイト電極308による突出を緩和できる。

#### 【0070】

第1の層間絶縁膜315として、酸化珪素膜の他に窒化珪素膜、酸化窒化珪素膜を形成しても良い。或いは、これら絶縁膜の多層膜としても良い。

#### 【0071】

そして、第1の層間絶縁膜315に、ソース、ドレイン領域310、311に対するコンタクトホールと、コモンコンタクト部206c、206dに内部配線207cに対するコンタクトホールをそれぞれ形成した後、ソース、ドレイン電極316、317や内部配線318の出発膜となる導電膜を形成する。

#### 【0072】

ここでは、導電膜としてチタン(Ti)膜、アルミニウム(A1)膜、チタン(Ti)膜の多層膜を、スパッタリング法で形成した。なお、チタン(Ti)膜の膜厚はそれぞれ100nmとし、アルミニウム膜の膜厚は300nmとした。この多層膜をパターニングして、ソース電極316、ドレイン電極317及び内部配線318をそれぞれ形成した(図5(E))。

#### 【0073】

図5の内部配線318は図3の内部配線207a、207bに対応する。内部配線207a、207bはコモンコンタクト部206b、206cにおいて、ゲイト電極308と同一工程を経て形成された内部配線207cに接続される。

#### 【0074】

次に、第2の層間絶縁膜319として有機性樹脂膜を1~2 $\mu$ mの厚さに形成する。有機性樹脂膜としては、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等を用いることができる。有機樹脂膜を用いるのは第2の層間絶縁膜319の表面を平坦にするためである。第2の層間絶縁膜319の表面を平坦にすることは、セルギャップの均一にするのに重要である。本実施例では、第2の層間絶縁膜319としてポリイミドを1 $\mu$ mの膜厚に形成した。

#### 【0075】

次に、第2の層間絶縁膜319にドレイン電極317、内部配線318それぞれに対するコンタクトホール320、321を開口した。内部配線318のコンタクトホール321は、図2(A)に示す開口部111のように、1.1mm×1.1mmの矩形状の領域

10

20

30

40

50

110内に、 $100\text{ }\mu\text{m} \times 100\text{ }\mu\text{m}$ の矩形状の開口を、 $100\text{ }\mu\text{m}$ の間隔で $5 \times 5$ のマトリクス状に形成した。またコンタクトホール321の他に、取出し端子205部において内部配線318(207a、207b)とコモン端子205a、205bとを接続するためのコンタクトホールも形成される(図5(F))。

#### 【0076】

後述するが、本実施例では、導電性スペーサの直径を $3.5\text{ }\mu\text{m}$ とするため、開口部を $100\text{ }\mu\text{m} \times 100\text{ }\mu\text{m}$ とし、ここに配置される導電性スペーサが移動できるような十分なゆとりを与え、開口部で導電性スペーサが積み重ならないようにした。

#### 【0077】

また、コモンコンタクト部において、第2の層間絶縁膜319の残存している領域の面積も導電性スペーサが移動できるような十分な広い領域としているため、この領域に導電性スペーサを確実に配置することができる。よって、この領域に配置された導電性スペーサにより、セルギャップの保持、電気的接続を確実に行うことができる。

#### 【0078】

そして、後に画素電極322、導電性パッド323となる金属薄膜を $100\text{ nm} \sim 400\text{ nm}$ の厚さに形成する。本実施例では金属薄膜として $1\text{ wt\%}$ のチタンを添加したアルミニウム膜を $300\text{ nm}$ の厚さに、スパッタ法で形成した。しかる後、金属薄膜をパターニングして、画素電極322、導電性パッド323をそれぞれ形成した。導電性パッド323は、コンタクトホール321を覆うように $1.1\text{ mm} \times 1.1\text{ mm}$ の矩形状に形成した。更に、取出し端子205もパターニングされる。以上によりTFT基板が完成する(図5(G))。

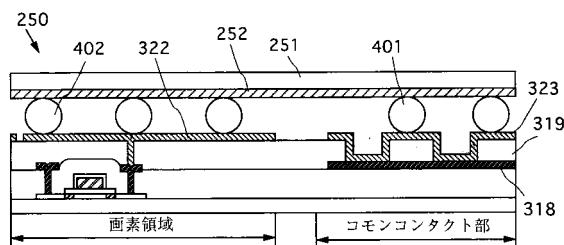

#### 【0079】

他方、図6に示すように対向基板250においては、透光性基板251上にITO膜である対向電極252を形成した。基板251には、ガラスや石英基板を用いることができる。

#### 【0080】

次にTFT基板200と対向基板250を貼り合わる。この貼り合わせ工程は公知のセル組み法に従って行えば良い。

#### 【0081】

まず、TFT基板200、対向基板250のいずれか一方の基板に、シール材を塗布する。本実施例では対向基板250側にシール材を塗布した。シール材には紫外線・熱硬化型の樹脂材料を用い、シールディスペンサー装置により、液晶注入孔を残して、基板周囲にシール材を線状に塗布した。また、図4に示す領域254a～254dには、球状の導電性スペーサ401を $3.0\text{ wt\%}$ 混入したシール材を塗布した。導電性スペーサが混入されたシール材は異方性導電膜として機能する。

#### 【0082】

導電性スペーサ401は樹脂材料でなる球体に導電膜が被覆されたものが一般的に使用されており、本実施例では金(Au)で被覆された、導電性スペーサ401を使用した。導電性スペーサ401の直径はセルギャップよりも $0.2\text{ }\mu\text{m} \sim 1\text{ }\mu\text{m}$ 程大きくすればよい。本実施例では、セルギャップを $3\text{ }\mu\text{m}$ とするため、直径 $3.5\text{ }\mu\text{m}$ の導電性スペーサ401を使用した。シール材を塗布した後、仮焼成する。

#### 【0083】

次に、TFT基板200、対向基板250のいずれか一方の基板に、セルギャップを維持するためのスペーサ402を散布する。本実施例では、スペーサ402を対向基板250側に散布した。また、セルギャップを $3\text{ }\mu\text{m}$ とするため、スペーサ402は直径 $3\text{ }\mu\text{m}$ のポリマ系材料でなる球状のスペーサを用いた。

#### 【0084】

次に、TFT基板200と対向基板250とを対向し、画素領域のセルギャップがスペーサ402の直径となるまでプレスした。プレスした状態で十数秒紫外線を照射してシール材を紫外線硬化させ、セルギャップを固定し、しかる後加圧しながら加熱してシール材の

10

20

40

50

接着強度を向上させる。

#### 【0085】

そして、液晶を封入し、封入口を封止することでセル組工程が完了する。図6に示すように、対向基板250の対向電極252は導電性スペーサ401によりTFT基板200の導電性パッド323に電気的に接続され、TFT基板側において、導電性パッド323は内部配線318を介してコモン端子に接続されている。このような接続構造により、対向基板250側の対向電極252をTFT基板側の配線によって、外部の電源と接続することが可能になる。なお、図6のコモンコンタクト部の拡大図が図1に対応する。

#### 【0086】

本実施例では、セルギャップを $3\text{ }\mu\text{m}$ とするために、画素領域に散布されるスペーサ402の直径を $3\text{ }\mu\text{m}$ とし、導電性スペーサ401の直径を $3.5\text{ }\mu\text{m}$ とした。導電性スペーサの直径をスペーサ402の直径(セルギャップ)よりも大きくするのは、対向電極252と導電性パッド323の接続を確実にするためである。基板貼り合わせ工程のプレス工程において、導電性スペーサ401はセルギャップよりも直径が大きいため、押しつぶされる。押しつぶされることにより、対向電極252、導電性パッド323との接触面積が大きくなり、電気的な接続が確実になるとともに、セルギャップを画素領域と同じに維持することができる。

#### 【0087】

また、本実施例では、内部配線318をソース、ドレイン電極316、317の出発膜で構成したが、内部配線318は画素電極322よりも下層の配線であればよい。例えば、第2の層間絶縁膜319内にチタン等の導電膜でなるブラックマトリクスを形成した場合、この導電膜で内部配線318を形成することができる。

#### 【0088】

また、本実施例ではセルギャップを均一にするため、その表面に画素電極322が形成される第2の層間絶縁膜319の表面が平坦であることが重要であると共に、内部配線318が形成される第1の層間絶縁膜315の表面の平坦性も重要になる。

#### 【0089】

表面が平坦な層間絶縁膜を得る方法として、層間絶縁膜の厚膜化による方法、有機性樹脂膜を用いたレベリングによる方法、機械的な研磨による方法、エッチバック技術による方法などが挙げられる。本実施例では、第1の層間絶縁膜315の平坦化に厚膜化による方法を採用し、第2の層間絶縁膜319の平坦化に有機性樹脂膜を用いたレベリングによる方法を採用したが、他の手法を用いて平坦化しても良い。

#### 【0090】

本実施例の液晶表示装置において、液晶層に二色性色素を分散させたり、TFT基板、対向基板に配向膜を設けたり、対向基板にカラーフィルタを設けたりすることも可能である。その様な液晶層の種類、配向膜、カラーフィルタの有無等は、駆動方法、液晶の種類等により実施者が適宜決定すれば良い。

#### 【0091】

例えば、対向基板250の側にカラーフィルタを設けた場合、カラーフィルタはコモンコンタクト部には形成されないので、対向基板において、画素領域とコモンコンタクト部に段差が生ずる。この段差を補正するため、導電性スペーサの直径をカラーフィルタの厚さ程度大きくする必要がある。

#### 【0092】

また、本実施例は反射型の液晶表示装置の例を示したが、透過型の液晶表示装置とすることもでき、この場合には、画素電極及び導電性パッドの出発膜を透光性を有するITO膜等で形成すればよい。

#### 【0093】

本実施例では代表的なトップゲイト型薄膜トランジスタであるコブレナー型薄膜トランジスタを一例として記載したが、ボトムゲイト型薄膜トランジスタであっても構わない。また、薄膜トランジスタ以外にも、薄膜ダイオード、MIM素子、バリスタ素子等を用い

10

20

20

30

30

40

40

50

ることができる。

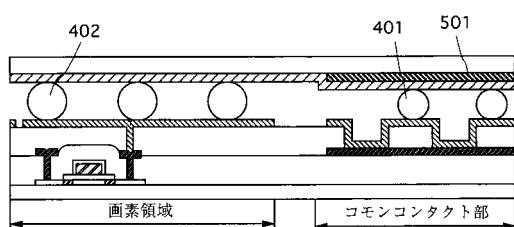

**【実施例 2】**

**【0094】**

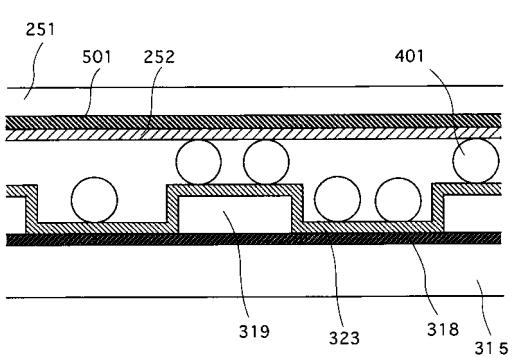

本実施例は、実施例 1 のコモンコンタクト部の変形例である。図 7 は本実施例のアクティブマトリクス型表示装置の断面構成図である。図 7 において、TFT 基板の構成は図 6 と同じであり、符号の記載を一部省略した。また図 7 において図 6 と同一の符号は同一の部材を示す。また、図 7 に示すコモンコンタクト部の拡大図を図 9 に示す。

**【0095】**

図 6 に示す実施例 1 において、対向電極 252 は透明導電膜であるITO膜で構成されているため、対向電極 252 と導電性スペーサ 401 間の電気抵抗は、金属膜と比較して大きくなる。本実施例はこの電気抵抗を低減することを目的とする。10

**【0096】**

このため、対向基板 250 側に金属膜を形成し、パターニングして、コモンコンタクト部 254a ~ 254d に導電膜でなる接続パッド 501 をそれぞれ形成する。接続パッド 501 を形成することで、対向電極 252 と導電性スペーサ 401 間の抵抗値を下げることができる。ただし、接続パッド 501 を構成する導電膜は対向電極 252 に使用される導電膜よりも電気抵抗が低いことが重要である。

**【0097】**

また、対向基板側のブラックマトリクスをクロム等の導電膜で形成した場合には、接続パッド 501 をこの導電膜で形成することができ、導電膜をパターニングしてブラックマトリクスを形成する際に、接続パッド 501 を形成すればよい。20

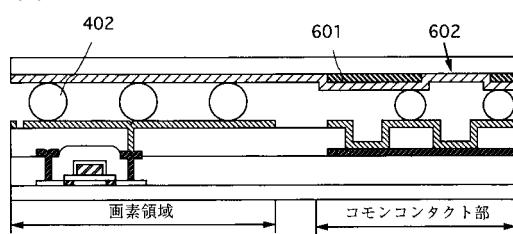

**【実施例 3】**

**【0098】**

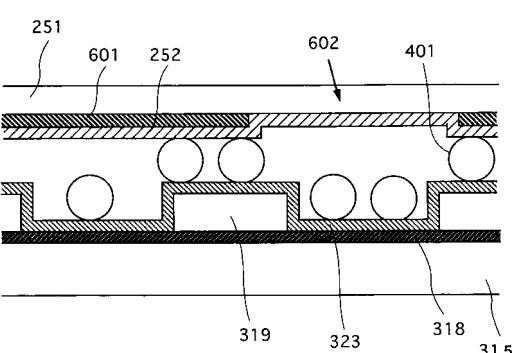

本実施例は実施例 2 の変形例であり、図 8 は本実施例のアクティブマトリクス型表示装置の断面構成図である。図 8 において、TFT 基板の構成は図 6 と同じであり、符号の記載を一部省略した。なお、図 8 において図 6 と同一の符号は同一の部材を示す。また、図 8 のコモンコンタクト部の拡大図が図 10 に対応する。

**【0099】**

実施例 1 においては、対向基板 251、対向電極 252 双方とも透光性を有するため、基板を貼り合わせた状態で、対向基板 250 側からコモンコンタクト部に導電性スペーサ 401 の分布の様子を視認することができた。しかし、実施例 2 では金属膜でなる接続パッド 501 を形成したため、導電性スペーサ 401 の分布の様子を視認することができない。30

**【0100】**

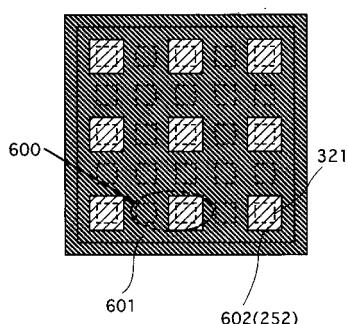

本実施例では、抵抗値を下げるための接続パッドを設けた状態で、導電性スペーサ 401 の分布の様子を視認することを可能することを目的とする。このため、接続パッド 601 に選択的に開口部を設け、この開口部を介して導電性スペーサ 401 が見えるようにした。

**【0101】**

図 11 は、本実施例のコンタクト部の上面図であり、対向基板側から見た状態を示す。また、図 10 は、図 11 の点線で囲まれた領域 600 のコモンコンタクト部の断面構成図に対応する。図 11 に示すように導電性パッド 601 には開口部 602 が形成される。開口部 602 では対向基板 251 と対向電極 252 だけが存在し、双方とも透光性を有するため、開口部 602 から導電性スペーサ 401 の分布の様子を確認することが可能になる。40

**【0102】**

開口部 602 はセルギャップを維持するため、導電性スペーサ 401 が対向電極と接しない箇所である、TFT 基板の第 2 の層間絶縁膜に開口されたコンタクトホール 321 に對峙する箇所に形成するとよい。更に、その面積を第 2 の層間絶縁膜の開口部よりも若干、数 % ~ 30 % 程度大きく形成すると良い。なお、開口部 602 の数や配置、形状等は図50

11に限定されるものではなく、実施者が適宜に設定することができる。

**【0103】**

接続パッド601の開口部602を第2の層間絶縁膜の開口部よりも若干大きく形成するには、電気的な接続に寄与している、第2の層間絶縁膜318上の導電性パッド602を視認できるようにするためである。

**【0104】**

実施例2、3においては、コモンコンタクト部のセルギャップを均一することと、導電性スペーサ401と対向電極252の接続抵抗を下げるることを同時に実現するための構成を示したが、導電性スペーサ401と対向電極252の抵抗値を下げるなどを主要な目的とする場合であれば、TFT基板側のコモンコンタクト部の構造を図13に示すような、従来のコモンコンタクト部の構成としてもよい。この場合、図13のコモンコンタクト部16において、基板23と対向電極24の間に、実施例2、3で示した接続パッド501、601を形成すればよい。

10

**【0105】**

上述した実施例1～3においては、本発明をアクティブマトリクス型液晶表示装置に応用した例を示したが、本発明のコンタクト構造は、対向する基板にそれぞれ形成された配線を導電性スペーサを介して電気的に接続するようなコンタクト構造を有する装置に応用可能であり、例えば、異なるシリコンウェハに形成されたIC等を接続することも可能である。

20

**【図面の簡単な説明】**

**【0106】**

【図1】本実施形態のコモンコンタクト部の断面構成図。

【図2】本実施形態のコモンコンタクト部の上面図。

【図3】実施例1の液晶表示装置のTFT基板の上面図。

【図4】実施例1の液晶表示装置の対向基板の上面図。

【図5】実施例1のTFT基板の作製工程を示す図。

【図6】実施例1の画素領域、コモンコンタクト部の断面構成図。

【図7】実施例2の画素領域、コモンコンタクト部の断面構成図。

【図8】実施例3の画素領域、コモンコンタクト部の断面構成図。

【図9】実施例2のコモンコンタクト部の拡大構成図。

30

【図10】実施例3のコモンコンタクト部の断面構成図である。

【図11】実施例3のコンタクト部の上面図。

【図12】従来例のTFT基板の上面図。

【図13】従来例の画素領域、コモンコンタクト部の断面構成図。

【図14】従来例のコモンコンタクト部の上面図。

**【符号の説明】**

**【0107】**

101 第1の基板

102 第2の基板

103 第1の導電膜

40

104 絶縁膜

105 第2の導電膜

106 第3の導電膜

107 導電性スペーサ

200 TFT基板

205 取出し端子

206 コモンコンタクト部

207 内部配線

250 対向基板

252 対向電極

50

- 3 1 5 第1の層間絶縁膜

3 1 8 内部配線

3 1 9 第2の層間絶縁膜

3 2 2 画素電極

3 2 3 導電性パッド

4 0 1 導電性スペーサ

4 0 2 スペーサ

5 0 1、6 0 1 接続パッド

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

(56)参考文献 特開平06-148678(JP,A)

特開平06-186579(JP,A)

特開平06-289415(JP,A)

特開平07-301815(JP,A)

特開平02-000921(JP,A)

特開平02-302730(JP,A)

特開平09-244055(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |             |

|--------|-------------|

| G 02 F | 1 / 1 3 3 9 |

| G 02 F | 1 / 1 3 4 5 |

| G 09 F | 9 / 0 0     |

|        | -           |

|        | 9 / 3 5     |