(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5410660号

(P5410660)

(45) 発行日 平成26年2月5日(2014.2.5)

(24) 登録日 平成25年11月15日(2013.11.15)

(51) Int.Cl.

F 1

H05K 3/46 (2006.01)

H01L 23/12 (2006.01)H05K 3/46

H05K 3/46

H01L 23/12

H01L 23/12 501B

請求項の数 14 (全 17 頁)

(21) 出願番号

特願2007-195674 (P2007-195674)

(22) 出願日

平成19年7月27日 (2007.7.27)

(65) 公開番号

特開2009-32918 (P2009-32918A)

(43) 公開日

平成21年2月12日 (2009.2.12)

審査請求日

平成22年5月11日 (2010.5.11)

審判番号

不服2012-21122 (P2012-21122/J1)

審判請求日

平成24年10月26日 (2012.10.26)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 大島 一宏

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 堀内 章夫

長野県長野市小島田町80番地 新光電気

工業株式会社内

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法と電子部品装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

仮基板の配線形成領域に下地層が配置され、前記下地層の大きさより大きな剥離性積層金属箔が、前記下地層の上に配置されて前記配線形成領域の外周部に部分的に接着された構造を得る工程であって、前記剥離性積層金属箔は、前記仮基板側に配置されて銅からなる第1金属箔とそれより厚みが厚い第2金属箔とが剥離できる状態で仮接着されて構成され、

前記剥離性積層金属箔の前記第2金属箔を剥離することにより、前記第1金属箔を前記仮基板に残す工程と、

前記第1金属箔の上に銅からなるビアパッドを形成する工程と、前記ビアパッドの上に絶縁層を形成する工程と、前記ビアパッドをストップ層として前記絶縁層をレーザ又はドライエッティングで加工して、前記ビアパッドに到達するビアホールを形成する工程とを含む方法により、前記第1金属箔の上にビルトアップ配線層を形成する工程と、

前記仮基板上に前記下地層、前記第1金属箔及び前記ビルトアップ配線層が形成された構造体の前記下地層の周縁に対応する部分を切断することにより、前記仮基板上の前記下地層から前記第1金属箔を分離して、前記第1金属箔の上に前記ビルトアップ配線層が形成された配線部材を得る工程と、

前記配線部材の前記第1金属箔の上に、開口部が設けられためっきレジストを形成する工程と、

前記第1金属箔をめっき給電経路に利用する電解めっきにより、前記めっきレジストの

開口部に金属めっき層を形成する工程と、

前記めっきレジストを除去する工程と、

前記金属めっき層をマスクにして前記第1金属箔をエッティングすることにより、前記ビアパッドの上に、前記ビルトアップ配線層に接続される配線層を形成する工程とを有し、

前記ビアパッドの幅は、前記ビルトアップ配線層に接続される配線層の幅より狭く設定され、

前記ビルトアップ配線層に接続される配線層の前記ビアパッド側の面の周縁部が前記絶縁層に接しており、

前記ビアパッド及び前記ビルトアップ配線層に接続される配線層が、外部との接続部を構成することを特徴とする配線基板の製造方法。 10

**【請求項2】**

前記仮基板の上に前記下地層及び剥離性積層金属箔が接着された構造を得る工程は、半硬化状態のプリプレグ上に前記下地層及び前記剥離性積層金属箔を重ねて配置し、加熱・加圧によって前記プリプレグを硬化させて前記仮基板を得ると同時に、該仮基板に前記下地層及び剥離性積層金属箔を接着する工程であることを特徴とする請求項1に記載の配線基板の製造方法。

**【請求項3】**

前記下地層は、金属箔、離型フィルム、又は離型剤からなることを特徴とする請求項1又は2に記載の配線基板の製造方法。 20

**【請求項4】**

前記仮基板の両面側に、前記下地層、前記剥離性積層金属箔及び前記ビルトアップ配線層がそれぞれ形成され、

前記仮基板の両面側から前記配線部材がそれぞれ得られることを特徴とする請求項1又は2に記載の配線基板の製造方法。

**【請求項5】**

前記第1金属箔の厚みは1乃至3μmであり、前記第2金属箔の厚みは5乃至20μmであることを特徴とする請求項1又は2に記載の配線基板の製造方法。

**【請求項6】**

前記ビルトアップ配線層に接続される前記配線層の線幅は、10乃至20μmであることを特徴とする請求項1又は2に記載の配線基板の製造方法。 30

**【請求項7】**

請求項1乃至6のいずれか一項の製造方法によって前記配線基板を得る工程と、

前記配線基板の最上又は最下の前記配線層に電子部品を接続して実装する工程とを有することを特徴とする電子部品装置の製造方法。

**【請求項8】**

請求項1乃至6のいずれか一項の製造方法の工程を含み、

前記ビルトアップ配線を形成する工程の後であって、前記配線部材を得る工程の前に、前記ビルトアップ配線層の最上の配線層に電子部品を接続して実装する工程を有することを特徴とする電子部品装置の製造方法。 40

**【請求項9】**

請求項1乃至6のいずれか一項の製造方法の工程を含み、

前記配線部材を得る工程の後であって、前記めっきレジストを形成する工程の前に、前記ビルトアップ配線層の最上の配線層に電子部品を接続して実装する工程を有することを特徴とする電子部品装置の製造方法。

**【請求項10】**

前記電子部品は半導体チップであり、前記半導体チップが前記配線層にフリップチップ接続することを特徴とする請求項7乃至9のいずれか一項に記載の電子部品装置の製造方法。

**【請求項11】**

10

20

30

40

50

請求項 1 に記載の製造方法により得られる配線基板であって、

配線層と絶縁層とが複数積層され、両面側の最表層の前記配線層に接続部がそれぞれ設けられた配線基板であって、

前記配線基板の一方の面側の前記最表層の配線層が、前記絶縁層の上に形成された銅からなる金属箔と該金属箔の上に形成された金属めっき層とから構成され、

複数の前記配線層を接続するビアが前記絶縁層に形成されたビアホール内に設けられており、

前記金属箔の前記ビアとの接続部に、銅からなるビアパッドが形成されており、

前記ビアパッドを介して前記最表層の配線層と前記ビアの底面が接続されており、

前記ビアパッドの幅は、前記最表層の配線層の幅より狭く設定されており、

前記最表層の配線層の前記ビアパッド側の面の周縁部が前記絶縁層に接してあり、

前記ビアパッド及び前記最表層の配線層が外部との接続部を構成し、

前記ビアパッドは、レーザ又はドライエッチングで前記絶縁層に前記ビアホールを形成する際のストップ層として機能し、前記ビアホールの底面として配置されており、

前記金属箔は、

仮基板と、前記仮基板の配線形成領域に配置された下地層と、前記下地層の大きさより大きな剥離性積層金属箔であって、前記下地層の上に配置されて前記仮基板の前記配線形成領域の外周部分に接着され、かつ、前記仮基板側に配置された第1金属箔とそれより厚みが厚い第2金属箔とが剥離できる状態で仮接着された剥離性積層金属箔とからなる構造体を用いて得られる金属箔であって、

前記構造体における前記剥離性積層金属箔の前記第1金属箔から前記第2金属箔を剥離し、かつ、前記構造体の前記下地層の周縁に対応する部分を切断して前記仮基板上の前記下地層から前記第1金属箔を離し、さらに、前記第1金属箔をパターニングして形成した金属箔であることを特徴とする特徴とする配線基板。

【請求項 1 2】

前記金属めっき層の厚みは、前記金属箔の厚みより厚く設定されていることを特徴とする請求項 1 1 に記載の配線基板。

【請求項 1 3】

前記最表層の配線層はパッドであることを特徴とする請求項 1 1 又は 1 2 に記載の配線基板。

【請求項 1 4】

請求項 1 1 乃至 1 3 のいずれか一項に記載の配線基板と、

前記配線基板の両面側のうち少なくとも一方の前記最表層の配線層に接続されて実装された電子部品とを有することを特徴とする電子部品装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、電子部品の実装基板に適用できる配線基板及びその製造方法とその配線基板に電子部品が実装された電子部品装置及びその製造方法に関する。

【背景技術】

【0 0 0 2】

従来、電子部品が実装される配線基板として、仮基板の上に剥離できる状態で所要のビルトアップ配線層を形成した後に、ビルトアップ配線層を仮基板から分離してコア基板をもたないコアレスタイプの配線基板を得る方法がある。

【0 0 0 3】

特許文献 1 には、樹脂基板の上に 2 枚の銅箔が剥離層で接着された構造のキャリア付銅箔を介してビルトアップ配線層を形成した後に、キャリア付銅箔の界面から剥離することにより、上側の銅箔及びビルトアップ配線層を樹脂基板から分離して配線基板を得る方法が記載されている。

【0 0 0 4】

10

20

30

40

50

また、特許文献 2 には、コア基板の上に、第 1 の金属層の外周縁の位置が第 2 の金属層の外周縁の位置よりも内側になるように積層して配置して両者を接着フィルムで接着し、第 2 の金属層の上にビルドアップ配線層を形成した後に、配線基板の第 1 の金属層の周縁部分を切断することにより第 2 の金属層及びビルドアップ配線層を第 1 の金属層及びコア基板から分離する方法が記載されている。

#### 【0005】

また、特許文献 3 には、プリプレグの上に下地層を介してそれより大きな金属箔を配置し、加熱・加圧してプリプレグから仮基板を得ると同時に仮基板上の周縁側に金属箔を接着し、金属箔の上にビルドアップ配線層を形成した後に、仮基板の周縁側を切断することにより、ビルドアップ配線層が形成された配線部材を得ることが記載されている。

10

【特許文献 1】特開 2005-236244 号公報

【特許文献 2】特開 2004-235323 号公報

【特許文献 3】特開 2007-158174 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

近年では、上記した配線基板の製造方法において、配線基板の両面側に微細な配線層（例えばライン：スペース = 20 : 20  $\mu\text{m}$ ）を形成し、両面側に配線層の接続部が露出するようにソルダレジストを形成する要求がある。

#### 【0007】

上記した特許文献 1（図 7～図 12）には、基板からビルドアップ配線層を分離した後に、ビルドアップ配線層の基板との分離面側に残された銅箔をパターニングして配線層を追加で形成する方法が記載されている。しかしながら、取り扱いを容易にするため比較的厚い（10～40  $\mu\text{m}$ ）厚みの銅箔を使用する必要があり、それをウェットエッティングによってパターン化するので、微細な配線層を形成することは困難である。

20

#### 【0008】

また、上記した特許文献 2 及び 3 では、基板からビルドアップ配線層を分離した後に、ビルドアップ配線層の下に残された銅箔を除去するようにしてあり、ビルドアップ配線層の基板との分離面側に微細な配線層を形成することに関しては考慮されていない。

#### 【0009】

30

本発明は以上の課題を鑑みて創作されたものであり、仮基板からビルドアップ配線層を分離して配線基板を得る製造方法において、ビルドアップ配線層の仮基板との分離面側に微細な配線層を形成できる配線基板の製造方法及びその配線基板に電子部品を実装するための電子部品装置の製造方法と配線基板及び電子部品装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

上記課題を解決するため、本発明は配線基板の製造方法に係り、仮基板の配線形成領域に下地層が配置され、前記下地層の大きさより大きな剥離性積層金属箔が、前記下地層の上に配置されて前記配線形成領域の外周部に部分的に接着された構造を得る工程であって、前記剥離性積層金属箔は、前記仮基板側に配置されて銅からなる第 1 金属箔とそれより厚みが厚い第 2 金属箔とが剥離できる状態で仮接着されて構成され、前記剥離性積層金属箔の前記第 2 金属箔を剥離することにより、前記第 1 金属箔を前記仮基板に残す工程と、前記第 1 金属箔の上に銅からなるビアパッドを形成する工程と、前記ビアパッドの上に絶縁層を形成する工程と、前記ビアパッドをストップ層として前記絶縁層をレーザ又はドライエッティングで加工して、前記ビアパッドに到達するビアホールを形成する工程とを含む方法により、前記第 1 金属箔の上にビルドアップ配線層を形成する工程と、前記仮基板上に前記下地層、前記第 1 金属箔及び前記ビルドアップ配線層が形成された構造体の前記下地層の周縁に対応する部分を切断することにより、前記仮基板上の前記下地層から前記第 1 金属箔を分離して、前記第 1 金属箔の上に前記ビルドアップ配線層が形成された配線部材を得る工程と、前記配線部材の前記第 1 金属箔の上に、開口部が設けられためっきレジ

40

50

ストを形成する工程と、前記第1金属箔をめっき給電経路に利用する電解めっきにより、前記めっきレジストの開口部に金属めっき層を形成する工程と、前記めっきレジストを除去する工程と、前記金属めっき層をマスクにして前記第1金属箔をエッチングすることにより、前記ピアパッドの上に、前記ビルトアップ配線層に接続される配線層を形成する工程とを有し、前記ピアパッドの幅は、前記ビルトアップ配線層に接続される配線層の幅より狭く設定され、前記ビルトアップ配線層に接続される配線層の前記ピアパッド側の面の周縁部が前記絶縁層に接してあり、前記ピアパッド及び前記ビルトアップ配線層に接続される配線層が、外部との接続部を構成することを特徴とする。

#### 【0011】

本発明の一つの好適な態様では、仮基板の材料として半硬化状態のプリプレグが使用される。プリプレグの配線形成領域に下地層（金属箔、離型フィルム又は離型剤）が配置され、下地層より大きさが一回り大きな剥離性積層金属箔がプリプレグの配線形成領域の外側の外周部に接するように、剥離性積層金属箔が下地層を介してプリプレグ上に配置される。

10

#### 【0012】

剥離性積層金属箔は、仮基板側に配置される第1金属箔とそれより厚みが厚い第2金属箔とが剥離できる状態で仮接着されて構成され、両者の界面で剥離できるようになっている。

#### 【0013】

その後に、プリプレグ、下地層及び剥離性積層金属箔を加熱・加圧することにより、プリプレグを硬化させて仮基板を得ると同時に、仮基板上に下地層及び剥離性積層金属箔の周縁部を接着させる。このとき、下地層が金属箔の場合は、金属箔同士が重なる領域では、両者が単に密着した状態となっている。あるいは、仮基板としてプリプレグを使用しない場合は、リジッド基板の上に接着層によって下地層及び剥離性積層金属箔を同様に接着してもよい。

20

#### 【0014】

次いで、剥離性積層金属箔の外面側の第2金属箔を剥離することにより、仮基板に薄膜の第1金属箔を残す。続いて、第1金属箔の上にそれに接続される所要のビルトアップ配線層を形成する。さらに、仮基板上に下地層、第1金属箔及びビルトアップ配線層が形成された構造体の下地層の周縁に対応する部分を切断する。これにより、下地層と第1金属箔とが重なる領域が得られ、下地層と第1金属箔とを容易に分離することができる。このようにして、仮基板から第1金属箔を分離することによって第1金属箔の上にビルトアップ配線層が形成された配線部材が得られる。

30

#### 【0015】

その後に、配線部材の第1金属箔（シード層）をめっき給電経路に利用するセミアディティブ法によってビルトアップ配線層に接続される配線層を形成する。このようにして、コア基板をもたないコアレスタイプの配線基板が製造される。

#### 【0016】

セミアディティブ法では、シード層をエッチングする際のエッチングシフトが配線層の出来上がりの線幅に大きく影響する。本発明では、薄膜（例えば $1 \sim 3 \mu\text{m}$ ）の第1金属箔をシード層として利用できるようにしたので、エッチングシフトを極力抑えることができ、ビルトアップ配線層に接続される微細な配線層（例えば、線幅が $10 \sim 20 \mu\text{m}$ ）を容易に形成することができる。これによって、配線基板の仮基板との分離面側にも微細な配線層を形成することができるので、狭小ピッチの電極パッドを備えた高性能な電子部品の配線基板として利用できる。

40

#### 【0017】

また、本発明の配線基板では、両面側に銅からなる微細な配線層を形成できるので、両面側にソルダレジストを安定して形成できる利点もある。これによって、フレキシブルタイプの配線基板の反りの発生を防止できると共に、一般的な方法（はんだ印刷など）によってソルダレジストの開口部内に接続端子を設けることができる。

50

## 【0018】

本発明の配線基板では、最上及び最下のいずれかの配線層に電子部品（半導体チップ）が接続されて実装され、反対側の配線層に接続端子が設けられて電子部品装置となる。

## 【0019】

電子部品を実装するタイミングは、配線基板を得た後であってもよいし、仮基板上にビルドアップ配線層が形成された後であってもよい。あるいは、第1金属箔上にビルドアップ配線層が形成された配線部材を仮基板から分離した後に電子部品を実装してもよい。

## 【発明の効果】

## 【0020】

以上説明したように、本発明では、ビルドアップ配線層の仮基板との分離面側に微細な配線層を形成できるので、高性能な電子部品の配線基板として利用できる。 10

## 【発明を実施するための最良の形態】

## 【0021】

以下、本発明の実施の形態について、添付の図面を参照して説明する。

## 【0022】

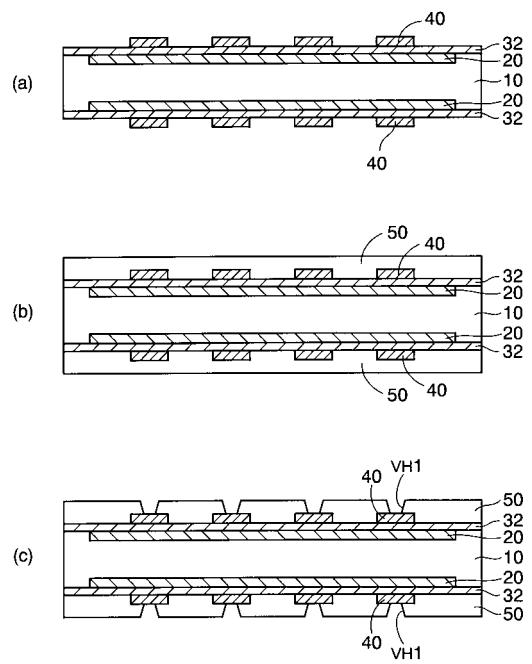

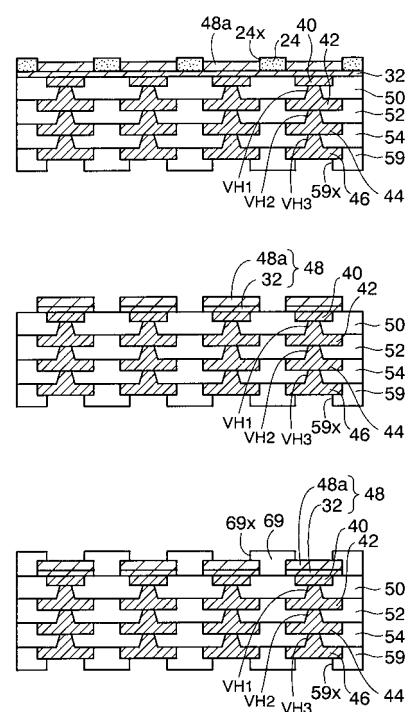

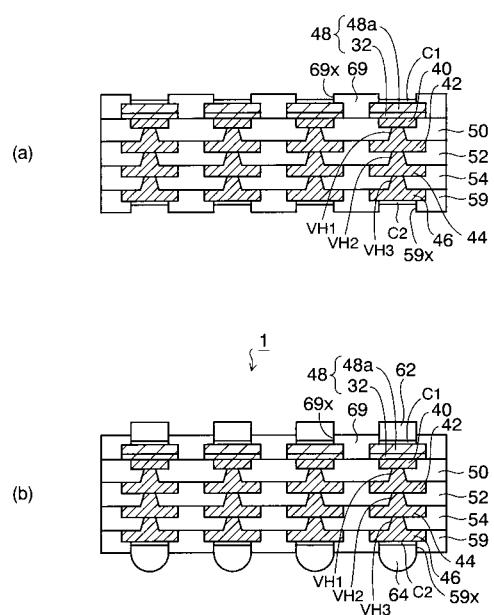

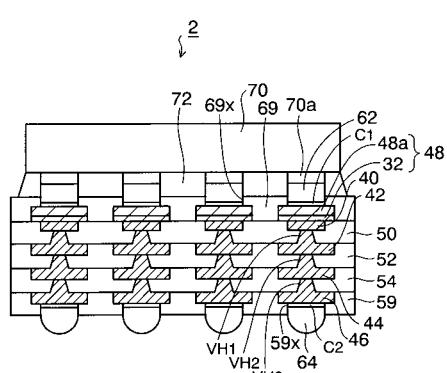

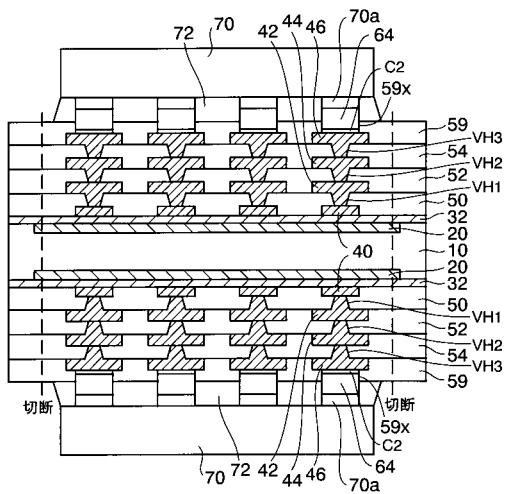

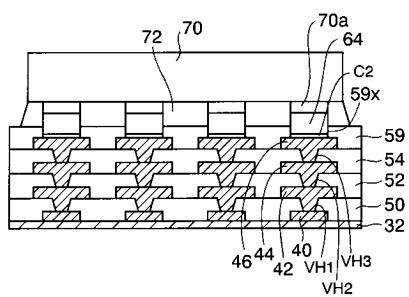

図1～図9は本発明の実施形態の配線基板の製造方法を示す断面図、図10は同じく電子部品装置を示す断面図である。

## 【0023】

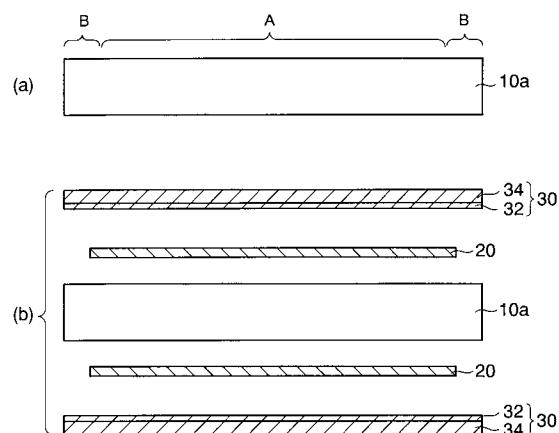

本実施形態の配線基板の製造方法では、図1(a)に示すように、まず、ガラスクロス（織布）、ガラス不織布、アラミド繊維又はアラミド不織布などにエポキシ樹脂やポリイミド樹脂などを含侵させて構成されるプリプレグ（prepreg）10aを用意する。プリプレグ10aはB-ステージ（半硬化状態）のものが使用される。 20

## 【0024】

プリプレグ10aの両面側には、配線形成領域Aとその外側の外周部Bとがそれぞれ画定されている。配線形成領域Aは、プリプレグ10aの両面側において一つずつ区画されてもよいし、複数で区画されていてもよい。

## 【0025】

その後に、図1(b)に示すように、下地層20と剥離性積層銅箔30（剥離性積層金属箔）とを用意する。下地層20としては、銅箔などの金属箔、離型フィルム又は離型剤が使用される。離型フィルムとしては、ポリエステル又はPET（ポリエチレンテレフタレート）のフィルムに薄いフッ素樹脂（ETFE）層を積層したものの、若しくは、ポリエステル又はPETのフィルムの表面にシリコーン離型処理を施したものが使用される。また、離型剤としては、シリコーン系離型剤やフッ素系離型剤が使用される。 30

## 【0026】

剥離性積層銅箔30は、薄膜の第1銅箔32の上にそれより厚みの厚い第2銅箔34が圧着されて構成される。第1銅箔32の厚みは1～3μmに設定され、第2銅箔34の厚みは5～20μmに設定される。剥離性積層銅箔30では、第1銅箔32及び第2銅箔34が仮接着された状態となっており、両者の界面から容易に剥離できるようになっている。第2銅箔34は、薄膜の第1銅箔32の取り扱いを容易にするキャリアとして機能する。 40

## 【0027】

なお、キャリアとして機能する第2銅箔34は、アルミニウム板などの各種の金属板（箔）を代替として使用することができる。

## 【0028】

下地層20はプリプレグ10aの配線形成領域Aと同等な大きさに設定される。また、剥離性積層銅箔30はプリプレグ10aの配線形成領域A及び外周部Bを覆う大きさであり、下地層20よりも一回り大きな大きさに設定される。

## 【0029】

そして、プリプレグ10aの両面側に下から順に下地層20と剥離性積層銅箔30をそれぞれ配置する。剥離性積層銅箔30は、その第1銅箔32がプリプレグ10a側になっ 50

て配置される。下地層 20 はプリプレグ 10a 上の配線形成領域 A に対応して配置され、剥離性積層銅箔 30 は下地層 20 の上に重なると共に、その周縁部がプリプレグ 10a の外周部 B に接した状態で配置される。さらに、プリプレグ 10a、下地層 20 及び剥離性積層銅箔 30 を両面側から真空雰囲気で 190 ~ 200 °C の温度で加熱・加圧する。

【0030】

これにより、図 1 (c) に示すように、プリプレグ 10a が硬化してガラスエポキシ樹脂などからなる仮基板 10 が得られると共に、プリプレグ 10a の硬化する際の接着機能によって仮基板 10 の両面に下地層 20 及び剥離性積層銅箔 30 がそれぞれ接着される。下地層 20 はその全体が仮基板 10 の配線形成領域 A に接着し、剥離性積層銅箔 30 はその周縁部が仮基板 10 の外周部 B に部分的に接着する。下地層 20 と剥離性積層銅箔 30 とが重なる領域では、両者が単に密着した状態となっており、後述するようにその領域では下地層 20 と剥離性積層銅箔 30 とを容易に分離できるようになっている。

【0031】

なお、下地層 20 として離型剤を使用する場合は、剥離性積層銅箔 30 の下面側の下地層 20 が配置される領域に上記したような離型剤を塗布や噴射によって形成し、離型剤を介して剥離性積層銅箔 30 をプリプレグ 10a 上に配置し、加熱・加圧して接着する。これにより、離型剤（下地層 20）が設けられた部分の剥離性積層銅箔 30 と仮基板 10 とが容易に分離できるようになる。

【0032】

上記した形態では、仮基板 10 としてプリプレグ 10a を使用するので、接着層を使用することなく、プリプレグ 10a を硬化させることにより、仮基板 10 上に下地層 20 及び剥離性積層銅箔 30 が接着された構造を得ることができる。

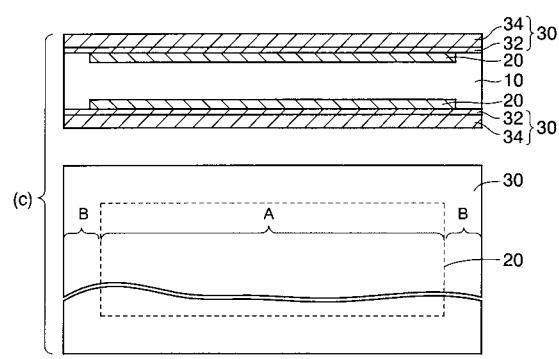

【0033】

あるいは、接着層を使用しても差し支えない場合は、図 2 に示すように、仮基板 10 の両面側に接着層 12 を介して下地層 20 及び剥離性積層銅箔 30 の周縁部をそれぞれ接着してもよい。この場合は、仮基板 10 としてプリプレグを使用する必要はなく、硬化樹脂や金属板などのリジッドタイプの仮基板を使用できる。図 2 の構造においても、図 1 (c) と同様に、下地層 20 と剥離性積層銅箔 30 とが重なる領域では、両者が単に密着した状態となって容易に分離できるようになっている。

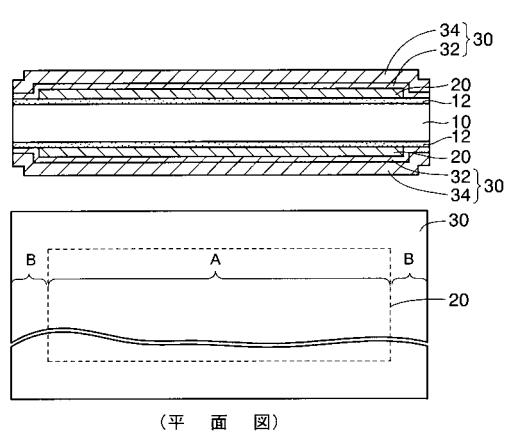

【0034】

次いで、図 3 (a) に示すように、仮基板 10 の両面側において、剥離性銅箔 30 の第 1、2 銅箔 32, 34 の界面から第 2 銅箔 34 を剥離して第 1 銅箔 32 をそれぞれ露出させる。これにより、図 3 (b) に示すように、仮基板 10 の両面側から第 2 銅箔 34 が除去されて薄膜の第 1 銅箔 32 が両面側に残された状態となる。後述するように、第 1 銅箔 32 はセミアディティブ法で配線層を形成する際の薄膜のシード層として利用される。

【0035】

このように、本実施形態では、剥離性積層銅箔 30 を使用することにより、単層では取り扱いが困難な薄膜の第 1 銅箔 32 を第 2 銅箔 34 (キャリア) で支持しておき、上記した方法によって仮基板 10 上に薄膜の第 1 銅箔 32 を形成することができる。

【0036】

続いて、図 3 (c) に示すように、仮基板 10 の両面側の第 1 銅箔 32 の上に、開口部 14x が設けられためっきレジスト 14 をそれぞれ形成する。めっきレジスト 14 は、ドライフィルムレジスト又は液状レジストを第 1 銅箔 32 の上に形成した後に、露光・現像を行うことによって得られる。

【0037】

さらに、図 3 (d) に示すように、仮基板 10 の両面側において、第 1 銅箔 32 をめっき給電経路に利用する電解めっきにより、めっきレジスト 14 の開口部 14x にパッド状の銅 (Cu) 電極を形成して第 1 配線層 40 をそれぞれ得る。第 1 配線層 40 の厚みは 5 ~ 15 μm、好適には 5 ~ 10 μm に設定され、その一例としては 10 μm である。

【0038】

10

20

30

40

50

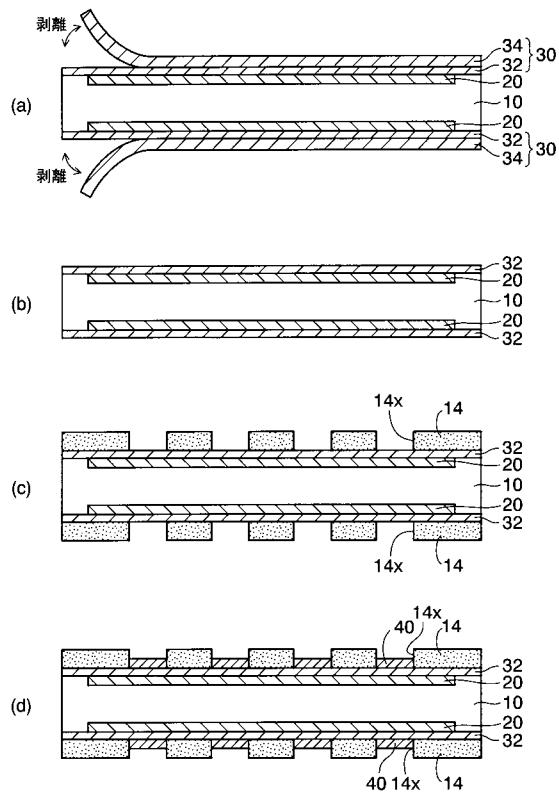

その後に、図4(a)に示すように、レジスト14が除去される。このようにして、仮基板10の両面側において、第1銅箔32の上にそれに接続される第1配線層40がそれぞれ形成される。

【0039】

なお、第1配線層40として、Cu電極の代わりに、ニッケル(Ni)層、金(Au)層及びパラジウム(Pd)層から選択される単層又は積層の電極を形成してもよい。例えば、下から順に、ニッケル(Ni)層/金(Au)層/パラジウム(Pd)層からなる電極が使用される。

【0040】

次いで、図4(b)に示すように、仮基板10の両面側の第1配線層40の上にエポキシやポリイミドなどの樹脂フィルムを貼着するなどして第1層間絶縁層50をそれぞれ形成する。さらに、図4(c)に示すように、仮基板10の両面側の第1層間絶縁層50をレーザやドライエッチングによって加工することにより、第1配線層40に到達する第1ビアホールVH1をそれぞれ形成する。第1ビアホールVH1は、第1配線層40側を底面として第1層間絶縁層50の表面に開口するように形成される。

【0041】

第1配線層40は、第1ビアホールVH1を形成する際のレーザやドライエッチングのストップ層(ビアパッド)として機能し、薄膜の第1銅箔32がそれらの処理から保護される。

【0042】

なお、第1銅箔32の保護が不要な場合は、第1配線層40を省略してもよい。

【0043】

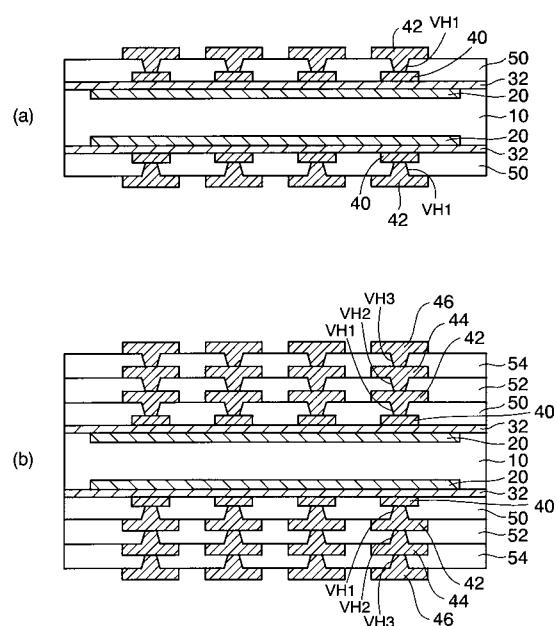

次いで、図5(a)に示すように、仮基板10の両面側の第1層間絶縁層50の上に、第1ビアホールVH1を介して第1配線層40に接続される第2配線層42をそれぞれ形成する。

【0044】

第2配線層42は例えばセミアディティブ法により形成される。詳しく説明すると、第1ビアホールVH1内及び第1層間絶縁層50上に無電解めっきなどによりシード層(不図示)を形成した後に、第2配線層42が形成される領域に開口部が設けられためっきレジスト(不図示)を形成する。続いて、シード層をめっき給電経路に利用する電解めっきにより、めっきレジストの開口部内に金属めっき層(不図示)を形成する。さらに、めっきレジストを剥離した後に、金属めっき層をマスクにしてシード層をエッチングすることにより銅などからなる第2配線層42を得る。

【0045】

なお、本実施形態の各配線層の形成方法としては、上記したセミアディティブ法の他にサブトラクティブ法などの各種の配線形成方法を採用できる。

【0046】

次いで、図5(b)に示すように、同様な工程を繰り返すことにより、仮基板10の両面側に、第2配線層42の上に第2ビアホールVH2が設けられた第2層間絶縁層52をそれぞれ形成し、第2ビアホールVH2を介して第2配線層42に接続される第3配線層44を第2層間絶縁層52の上にそれぞれ形成する。

【0047】

さらに、同様な工程を繰り返すことにより、仮基板10の両面側に、第3配線層44の上に第3ビアホールVH3が設けられた第3層間絶縁層54をそれぞれ形成し、第3ビアホールVH3を介して第3配線層44に接続される第4配線層46を第3層間絶縁層54の上にそれぞれ形成する。

【0048】

その後に、図6(a)に示すように、仮基板10の両面側の第3層間絶縁層54の上に、第4配線層46の接続部上に開口部59xが設けられたソルダレジスト59を印刷によってそれぞれ形成する。あるいは、フィルム状のレジストを貼着し、それをパターニング

10

20

30

40

50

することによりソルダレジスト 5 9 を形成してもよい。

【0049】

このようにして、仮基板 1 0 上の両面側に、4 層のビルドアップ配線層（第 1 ~ 第 4 配線層 4 0 , 4 2 , 4 4 , 4 6 と第 1 ~ 第 3 層間絶縁層 5 0 , 5 2 、5 4 ）がそれぞれ形成される。ビルドアップ配線層の層数は、n 層（n は 1 以上の整数）で任意に形成することができる。また、仮基板 1 0 の片面のみにビルドアップ配線層を形成してもよい。

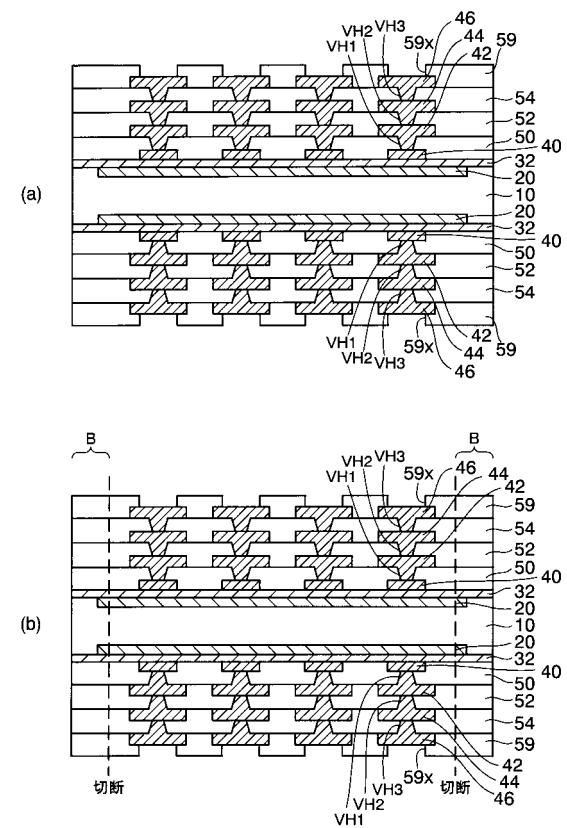

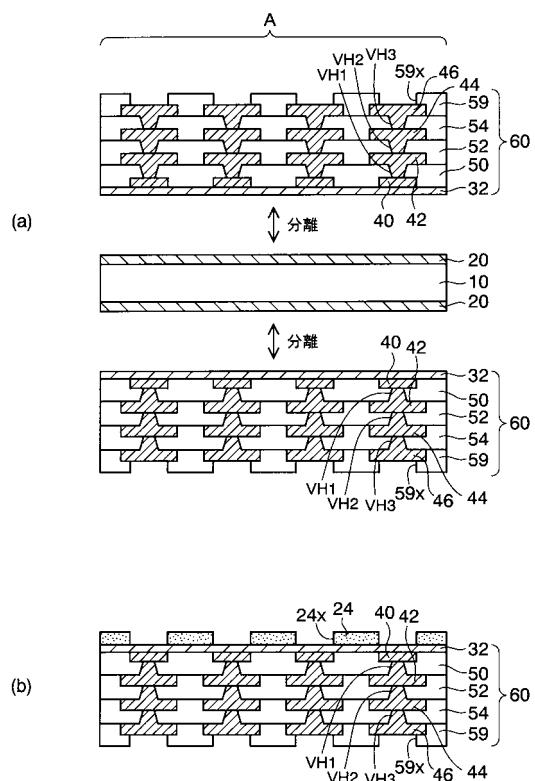

【0050】

次いで、図 6 (b) に示すように、図 6 (a) の構造体の下地層 2 0 の周縁に対応する部分を切断することにより、第 1 銅箔 3 2 の周縁部を含む外周部 B を廃棄する。これにより、図 7 (a) に示すように、下地層 2 0 と第 1 銅箔 3 2 とが単に密着した配線形成領域 A が得られ、下地層 2 0 と第 1 銅箔 3 2 とを容易に分離することができる。

10

【0051】

このようにして、下地層 2 0 と第 1 銅箔 3 2 とを分離することにより、仮基板 1 0 の両面側から第 1 銅箔 3 2 とその上に形成されたビルドアップ配線層とからなる配線部材 6 0 がそれぞれ得られる。

【0052】

本実施形態では、配線部材 6 0 は、仮基板 1 0 との分離面側に第 1 配線層 4 0 に接続された薄膜の第 1 銅箔 3 2 を備えているので、それを利用してセミアディティブ法によって第 1 配線層 4 0 に接続される微細な第 5 配線層を形成することができる。すなわち、図 7 (b) に示すように、配線部材 6 0 の第 1 銅箔 3 2 の上に、第 5 配線層が形成される領域に開口部 2 4 × が設けられためっきレジスト 2 4 をパターニングする。

20

【0053】

その後に、図 8 (a) に示すように、第 1 銅箔 3 2 をめっき給電経路に利用する電解めっきにより、めっきレジスト 2 4 の開口部 2 4 × に銅などからなる金属めっき層 4 8 a を形成する。金属めっき層 4 8 a の厚みは、5 ~ 1 5 μm、好適には 5 ~ 1 0 μm に設定され、その一例としては 1 0 μm である。

【0054】

続いて、図 8 (b) に示すように、めっきレジスト 2 4 を除去した後に、金属めっき層 4 8 a をマスクにして第 1 銅箔 3 2 をウェットエッティングすることにより、第 1 銅箔 3 2 と金属めっき層 4 8 a とにより構成される第 5 配線層 4 8 を得る。本実施形態では、薄膜（1 ~ 3 μm）の第 1 銅箔 3 2 をシード層として利用するセミアディティブ法によって第 5 配線層 4 8 を形成することから、第 1 銅箔 3 2 をウェットエッティングする際のエッティングシフトを極力抑えることができるので、ライン：スペースが 2 0 : 2 0 μm ~ 1 0 : 1 0 μm の微細な第 5 配線層 4 8 を形成することができる。

30

【0055】

第 5 配線層 4 8 の下側には、第 1 配線層 4 0 を介して同様なセミアディティブ法によって形成された微細な第 2 ~ 第 4 配線層 4 6 が設けられており、これによって配線基板の両面側に微細な第 4 配線層 4 6 と第 5 配線層 4 8 がそれぞれ内蔵される。

【0056】

なお、さらにセミアディティブ法を含むビルドアップ配線層を形成するための一連の工程を繰り返すことにより、配線基板の仮基板 1 0 との分離面側に第 5 配線層 4 8 に接続される n 層（n は 1 以上の整数）の配線層を積層することも可能である。

40

【0057】

その後に、図 8 (c) に示すように、第 5 配線層 4 8 の接続部上に開口部 6 9 × が設けられたソルダレジスト 6 9 を第 1 層間絶縁層 5 0 の上に形成する。ソルダレジスト 6 9 は、液状のソルダレジストを塗布し、露光・現像を行った後に、キュアによって硬化させることによって形成される。あるいは、フィルム状のレジストを貼着し、それをパターニングすることによりソルダレジスト 5 9 を形成してもよい。

【0058】

ここで、関連技術として第 1 銅箔 3 2 を除去して第 1 配線層 4 0 を露出させて接続電極

50

として利用する方法を挙げて本実施形態と比較してみる。この関連技術では、第1銅箔32をウェットエッティングよって除去する際に第1配線層40がエッティングで腐食されないように第1配線層40の最下にNi層などのエッティングストップ層を形成しておく必要がある。この場合、Ni層の接続部上に開口部が設けられたソルダレジストを形成する際に、Ni層上のソルダレジストが剥がれるなどして上手く形成できない場合がある。しかしながら、本実施形態では、ソルダレジスト69を形成する際に不具合が発生しない材料（銅など）から第5配線層48を形成できるので、ソルダレジストを安定して形成できるという利点もある。これにより、配線基板の両面側にソルダレジストを形成できるので、フレキシブルタイプの配線基板の反りの発生を抑えることができ、信頼性を向上させることができる。

10

#### 【0059】

続いて、図9(a)に示すように、上面側のソルダレジスト69の開口部69×内の第5配線層48の上に、無電解めっきで下から順にNi層及びAu層を形成することによって第1接続部C1を設ける。さらに、下面側のソルダレジスト59の開口部59×内の第4配線層46の上（図9では下）にも同様な第2接続部C2が設けられる。なお、Ni/Auめっき層を形成する代わりに、OSP（有機系半田付け性保護被膜）を形成して接続部C1, C2としてもよい。

#### 【0060】

続いて、図9(b)に示すように、上側の第5配線層48の第1接続部C1に、はんだを印刷したりはんだボールを搭載するなどして第1接続端子62を設ける。さらに、下側の第4配線層46の第2接続部C2に同様な第2接続端子64を設ける。

20

#### 【0061】

以上により、本実施形態のコア基板をもたないコアレスタイプの配線基板1が得られる。

#### 【0062】

本実施形態の好適な態様では、仮基板10の両面側に複数の配線形成領域Aがそれぞれ画定され、複数の配線形成領域Aからなるブロック領域に下地層20が一体的に配置された状態でその最外周部に剥離性積層銅箔30の周縁側が部分的に接着される。そして、それらの各配線形成領域Aにビルトアップ配線層がそれぞれ形成される。その後に、その構造体の下地層20の周縁に対応する部分を切断して得られる配線部材60に第5配線層48を形成する。その後に、その配線部材60を分割して個々の配線基板1が得られる。

30

#### 【0063】

以上説明したように、本実施形態の配線基板の製造方法では、まず、仮基板10の配線形成領域Aに下地層20が接着され、下地層20の大きさより大きな剥離性積層銅箔30が下地層20の上に積層されて配線形成領域Aの外周部Bに部分的に接着された構造を得る。剥離性積層銅箔30は、仮基板10側に配置される薄膜の第1銅箔32とそれより厚みが厚い第2銅箔34とが剥離できる状態で仮接着されて構成される。

#### 【0064】

次いで、第1銅箔32と第2銅箔34の界面から第2銅箔34を剥離することにより、薄膜の第1銅箔32を仮基板10に残す。本実施形態では、単層では取り扱いが困難な薄膜の第1銅箔32を厚膜の第2銅箔34で支持した状態で仮基板10上の下地層20の上に配置し、第2銅箔34を剥離することにより、薄膜の第1銅箔32のみを仮基板10の上に容易に残すことができる。

40

#### 【0065】

次いで、第1銅箔32の上にそれに電気的に接続される所要のビルトアップ配線層を形成する。さらに、仮基板10上に下地層20、第1銅箔32及びビルトアップ配線層が形成された構造体の下地層20の周縁に対応する部分を切断することにより、仮基板10から第1銅箔32を分離して、第1銅箔32の上にビルトアップ配線層が形成された配線部材60を得る。

#### 【0066】

50

その後に、薄膜の第1銅箔32をシード層として利用するセミアディティブ法によってビルドアップ配線層に接続される第5配線層48を形成する。セミアディティブ法では、シード層をエッチングする際のエッチングシフトが配線層の出来上がりの線幅に大きく影響する。本実施形態では、薄膜(1~3μm)の第1銅箔32をシード層として利用できるようにしたので、エッチングシフトを極力抑えることができ、微細な第5配線層48(線幅:10~20μm)を容易に形成することができる。

【0067】

図9(b)に示すように、そのような製造方法で得られる配線基板1では、仮基板10上に形成された4層のビルドアップ配線層(第1~第4配線層40, 42, 44, 46)が仮基板10から分離されて上下反転した状態で配置されている。そして、配線基板1の仮基板10との分離面側(上側)にも、第1配線層40に直接接続されてセミアディティブ法で形成された第5配線層48が形成されている。

【0068】

つまり、ビルドアップ配線層側だけではなく、配線基板1の仮基板10との分離面側においても、微細な配線層を自由に配置することができる。しかも、前述したように第1銅箔32を除去する場合と違って、第5配線層48の第1接続部C1上に開口部69xが設けられたソルダレジスト69を安定して形成することができる。従って、配線基板1の仮基板10との分離面側にも、一般的な方法(はんだ印刷など)によって汎用性のある第1接続端子62を設けることが可能になる。

【0069】

本実施形態の配線基板1では、図9(a)及び(b)に示すように、配線層(第1~第5配線層40, 42, 44, 46, 48)と絶縁層(第1~第3層間絶縁層50, 52, 54)とが複数積層されている。両面側の最表層の配線層(第4、第5配線層46, 48)は好適にはパッドであり、その主要部には接続部C2, C1がそれぞれ設けられている。

【0070】

配線基板の一方の面側の最表層の第5配線層48は、第1層間絶縁層50の上に形成された第1銅箔32とその上に形成された金属めっき層48aとから構成されている。

【0071】

さらに、複数の配線層(第1~第4配線層40, 42, 44, 46)を接続するビア(ビアホールVH1~VH3とそれに設けられた配線層)が各層間絶縁層50, 52, 54にそれぞれ設けられている。そして、ビアの底面(図9(b)では上面)が第1配線層40を介して第5配線層48の第1銅箔32に接続されている。第1配線層40はビアパッドとして機能する。なお、第1配線層40を省略する場合は、ビアの底面が第1銅箔32に直接接続される。

【0072】

次に、本実施形態の配線基板1に電子部品を実装する方法について説明する。図10には本実施形態の電子部品装置2が示されている、図10に示すように、図9(b)の配線基板1の上側の第1接続端子62に半導体チップ70(電子部品)のバンプ70aがフリップチップ接続される。さらに、半導体チップ70と配線基板1との間にアンダーフィル樹脂72が充填されて、本実施形態の電子部品装置2が構成される。そして、電子部品装置2の下側の第2接続端子64が実装基板(マザーボードなど)の接続パッドに接続される。

【0073】

図10では、外部接続方式をBGA(Ball Grid Array)型として使用する使用する例を示すが、第2接続端子64を省略してLGA(Land Grid Array)型としてもよい。あるいは、PGA(Pin Grid Array)型として使用する場合は、第2接続端子64としてリードピンが設けられる。

【0074】

また、本実施形態の配線基板1では、両面側の第1、第2接続端子62, 64を同一ス

10

20

30

40

50

ペック（ピッチや構造）で形成できるので、図10とは逆に、下側の第2接続端子64に半導体チップ70を実装し、上側の第1接続端子62を実装基板に接続してもよい。あるいは、両面側に半導体チップを実装し、下側の半導体チップの周囲に設けられた接続端子を実装基板に接続してもよい。電子部品として半導体チップ70を例示するが、各種の電子デバイスを実装することができる。

【0075】

本実施形態の配線基板1では、両面側に微細な第4、第5配線層46, 48が設けられているので、狭小ピッチの接続パッドを備えた高性能な半導体チップの配線基板として利用することができる。

【0076】

半導体チップ70を実装するタイミングは、配線部材60に第5配線層48を形成した後であってもよいし、第5配線層48を形成する前であってもよい。

【0077】

第5配線層48を形成した後に半導体チップ70を実装する場合は、前述した図9(b)の配線基板1において複数の配線形成領域にビルドアップ配線層が作り込まれており、各ビルドアップ配線層に接続された第1接続端子62に半導体チップ70をそれぞれ実装した後に、個々の電子部品装置2が得られるように配線基板1を分割する。

【0078】

あるいは、第5配線層48を形成する前に半導体チップ70を実装する場合は、図11に示すように、前述した図6(a)の工程（配線部材60を仮基板10から分離する前）で、両面側の第4配線層46に第2接続部C2及び第2接続端子64をそれぞれ形成した後に、半導体チップ70を両面側の第2接続端子64にそれぞれ実装し、その下側にアンダーフィル樹脂72を充填する。次いで、その構造体の下地層20の周縁に対応する部分を切断し、その後に同様な方法で第1銅箔32を利用して第5配線層48を形成する。

【0079】

仮基板10が存在する状態で半導体チップ70を実装する場合、反りの影響を受けにくくなつて搬送や取り扱いが容易になるので、半導体チップ70を信頼性よく実装できる利点がある。

【0080】

あるいは、図12に示すように、前述した図7(a)の工程（配線部材60を仮基板10から分離した後）で、第4配線層46に第2接続部C2及び第2接続端子64を形成し、次いで半導体チップ70を第2接続端子64に実装し、その下側にアンダーフィル樹脂72を充填する。その後に、同様な方法で第1銅箔32を利用して第5配線層48を形成する。

【図面の簡単な説明】

【0081】

【図1】図1(a)～(c)は本発明の実施形態の配線基板の製造方法を示す断面図（一部平面図）（その1）である。

【図2】図2は仮基板に下地層及び剥離性積層銅箔を接着する別の方法を示す断面図（一部平面図）である。

【図3】図3(a)～(d)は本発明の実施形態の配線基板の製造方法を示す断面図（その2）である。

【図4】図4(a)～(b)は本発明の実施形態の配線基板の製造方法を示す断面図（その3）である。

【図5】図5(a)及び(b)は本発明の実施形態の配線基板の製造方法を示す断面図（その4）である。

【図6】図6(a)及び(b)は本発明の実施形態の配線基板の製造方法を示す断面図（その5）である。

【図7】図7(a)及び(b)は本発明の実施形態の配線基板の製造方法を示す断面図（その6）である。

10

20

30

40

50

【図8】図8(a)～(c)は本発明の実施形態の配線基板の製造方法を示す断面図(その7)である。

【図9】図9(a)及び(b)は本発明の実施形態の配線基板の製造方法を示す断面図(その8)である。

【図10】図10は本発明の実施形態の電子部品装置を示す断面図である。

【図11】図11は本発明の実施形態の電子部品装置の製造方法における電子部品の実装のタイミングを示す断面図(その1)である。

【図12】図12は本発明の実施形態の電子部品装置の製造方法における電子部品の実装のタイミングを示す断面図(その2)である。

【符号の説明】

10

【0082】

1…配線基板、2…電子部品装置、10…仮基板、10a…プリプレグ、12…接着層、14, 24…めっきレジスト、14x, 24x, 59x, 69x…開口部、20…下地層、30…剥離性積層銅箔、32…第1銅箔、34…第2銅箔、40…第1配線層、42…第2配線層、44…第3配線層、46…第4配線層、48…第5配線層、48a…金属めつき層、50…第1層間絶縁層、52…第2層間絶縁層、54…第3層間絶縁層、59, 69…ソルダレジスト、60…配線部材、62…第1接続端子、64…第2接続端子、70…半導体チップ、70a…バンプ、A…配線形成領域、B…外周部、C1…第1接続部、C2…第2接続部、VH1, VH2, VH3…ビアホール。

【図1】

【図2】

(平面図)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

合議体

審判長 山岸 利治

審判官 富岡 和人

審判官 森川 元嗣

(56)参考文献 特開2006-19591 (JP, A)

特開2007-158174 (JP, A)

特開2007-109982 (JP, A)

特開2005-101137 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H05K3/46