## 【特許請求の範囲】

## 【請求項 1】

集積回路、特に無線周波数アプリケーションのための集積回路の製造方法であって、少なくとも1つのバイポーラ・トランジスタ及び少なくとも1つのMOS素子を含み、

シリコン基板(10、41)を提供する工程と、

バイポーラ・トランジスタの能動領域(41)とMOS素子のための能動領域(41)とを、前記シリコン基板(10)に形成する工程と、

前記能動領域の周りに、水平面において、電解絶縁領域(81)を形成する工程と、

前記MOS素子の前記能動領域上に、MOSゲート領域(111、112)を形成する工程と、

前記MOSゲート領域上と前記バイポーラ・トランジスタの前記能動領域(41)上に、電気的絶縁材料の層(141)を形成する工程と、

前記電気的絶縁層(141)に開口(143)を形成することによって、前記バイポーラ・トランジスタの前記能動領域にベース領域を画定する工程と、を含み、

前記電気的絶縁層における前記開口(143)は、電気的絶縁層(141)の残りの部分が、バイポーラ・トランジスタの前記能動領域を部分的に覆うように形成され、

前記電気的絶縁層(141)は前記MOSゲート領域上に残り、特に酸化、イオン打ち込み及び／あるいはエッチング工程を含む後続の製造工程の間、前記MOSゲート領域を密閉し保護する、前記集積回路の製造方法。

## 【請求項 2】

請求項1に記載の方法において、前記電気的絶縁層が窒化物層(141)である、前記方法。

## 【請求項 3】

請求項1あるいは請求項2に記載の方法であって、さらに、コンデンサ(41、141、151)の製造を含み、前記電気的絶縁層(141)の一部は前記コンデンサにおける誘電体として使用される、前記方法。

## 【請求項 4】

請求項1から請求項3のいずれかひとつに記載の方法において、前記MOSゲート領域は、酸化物層(111)の上のシリコン層(112)として形成される、前記方法。

## 【請求項 5】

請求項4に記載の方法において、酸化物は、前記電気的絶縁層(141)の形成に先立ち、シリコン層(112)の上に形成される、前記方法。

## 【請求項 6】

請求項4あるいは請求項5に記載の方法であって、さらに、前記電気的絶縁層(141)の形成に先立ち、バイポーラ・トランジスタのための前記能動領域(41)の上に酸化物層(111)を形成する工程を含む、前記方法。

## 【請求項 7】

請求項6に記載の方法であって、さらに、バイポーラ・トランジスタのための前記能動領域(41)の一部を露出するために、前記開口(143)を、前記能動領域(31)の上の前記酸化物層(111)を通して形成する工程を含む、前記方法。

## 【請求項 8】

請求項6あるいは請求項7に記載の方法において、前記ゲート・ポリシリコン層(112)がその上に形成される前記酸化物層(111)、及び、バイポーラ・トランジスタのための前記能動領域の上に形成される前記酸化物層(111)は、同時に形成される、好ましくは成長される、前記方法。

## 【請求項 9】

請求項1から請求項8のいずれかひとつに記載の方法において、MOS素子のための前記能動領域(41)は、前記MOSゲート領域(111、112)の形成に先立ちイオン打ち込みされる、前記方法。

## 【請求項 10】

10

20

30

40

50

請求項 1 から請求項 9 のいずれかに記載の方法において、バイポーラ・トランジスタのための前記能動領域 (41) における 2 次的埋込みコレクタ (SIC) (171)、及び、MOS 素子のための前記能動領域 (41) の背景ドーピングは、イオン打ち込み工程において同時に形成される、前記方法。

【請求項 11】

請求項 10 に記載の方法において、バイポーラ・トランジスタの外因性ベース (151) は、前記開口 (143) 内の前記電気的絶縁層 (141) の上と部分的にはバイポーラ・トランジスタの前記能動領域 (41) の上とに、形成され、それによりエミッタ開口 (162) を画定し、前記外因性ベースは、前記イオン打ち込み工程に先立ち形成され、前記イオン打ち込み工程の間フォトレジスト (161) により保護される、前記方法。

10

【請求項 12】

請求項 11 に記載の方法において、イオン打ち込み工程において同時に、前記外因性ベース (151) はドープされ、ソース及びドレイン領域 (198) は MOS 素子の前記能動領域 (41) に形成される、前記方法。

【請求項 13】

請求項 12 に記載の方法において、コンデンサ (41、141、151) の電極 (151) 及び / あるいは基板接触のための接触層もまた、前記外因性ベースがドープされるイオン打ち込み工程においてドープされる、前記方法。

20

【請求項 14】

請求項 12 あるいは請求項 13 に記載の方法において、シリコン酸化物 (200) とシリコン窒化物 (201) との 2 層は、前記ドープされたソース及びドレイン領域 (198) 上に形成され、それにより、打ち込まれた種が前記能動領域 (41) から拡散して出て行くことを防ぐ、前記方法。

【請求項 15】

請求項 1 から請求項 14 のいずれかひとつに記載の方法において、バイポーラ・トランジスタ及び MOS 素子の前記能動領域 (41) は、酸化物・窒化物 2 層を通るイオン打ち込みによって形成される、前記方法。

【請求項 16】

請求項 1 から請求項 15 のいずれかひとつに記載の方法において、前記バイポーラ・トランジスタのためのコレクタ・プラグ (192、41) を含むコレクタ (31、41、171、192) が形成され、前記コレクタ・プラグは、同じドーピング型 (n) であるが異なる拡散率を有する 2 つの異なるドーパント種類 (As, P) によるイオン打ち込みによりドープされ、低抵抗率と深いコレクタ・プラグを達成する、前記方法。

30

【請求項 17】

請求項 16 に記載の方法において、エミッタ接触 (191) が形成され、前記エミッタ接触は、前記コレクタ・プラグ打ち込みにおいて使用された前記ドーパント種類の 1 つによりドープされる、前記方法。

【請求項 18】

請求項 16 あるいは請求項 17 に記載の方法において、コレクタ・プラグの前記イオン打ち込みは、3 つの個別の工程において実行され、各工程は設定エネルギー及び設定ドーズ量におけるドーパント種のイオン打ち込みを含む、前記方法。

40

【請求項 19】

請求項 18 に記載の方法において、前記 3 工程イオン打ち込みにおいて、高抵抗及び低抵抗抵抗器 ( $R_{H1}$ 、 $R_{L0}$ ) が形成される、前記方法。

【請求項 20】

請求項 1 から請求項 19 のいずれかひとつに記載の方法において、バイポーラ・トランジスタは NPN トランジスタであり、MOS 素子は PMOS トランジスタである、前記方法。

【請求項 21】

請求項 1 から請求項 20 のいずれかひとつに記載の方法において、

50

バイポーラ・トランジスタの埋込みコレクタ領域(31)が前記基板(10)に形成され、前記埋込みコレクタ領域は、バイポーラ・トランジスタの前記能動領域(41)の下に位置し、

バイポーラ・トランジスタのための能動領域の周りに形成された電界絶縁領域が、前記シリコン基板における浅い溝(51)として形成され、前記浅い溝は基板表面から埋込みコレクタ領域(31)内(z)へと下に垂直に延び、

前記浅い溝は電気的絶縁材料(81)で満たされる、前記方法。

#### 【請求項22】

請求項21に記載の方法において、前記埋込みコレクタ領域(31)及び前記浅い溝(51、81)は、前記埋込みコレクタ領域が前記浅い溝の下に位置する領域(x)内に延びるように、相互に形成される、前記方法。

10

#### 【請求項23】

請求項22に記載の方法において、前記埋込みコレクタ領域は、好ましくは少なくとも約 $1 \times 10^9 \text{ cm}^{-3}$ の濃度に強度にnドープされ、バイポーラ・トランジスタのための前記能動領域は、約 $1 \times 10^7 \text{ cm}^{-3}$ 以下の濃度、好ましくは約 $5 \times 10^6 \text{ cm}^{-3}$ 以下、さらに好ましくは約 $1 \times 10^6 \text{ cm}^{-3}$ 以下、そして最も好ましくは約 $1 \times 10^6 \text{ cm}^{-3}$ の濃度にドープされる、前記方法。

#### 【請求項24】

請求項21から請求項23のいずれかひとつに記載の方法において、深い溝(63)が前記浅い溝(51)において形成され、特に前記浅い溝に自己整合する、前記方法。

20

#### 【請求項25】

特に無線周波数アプリケーションのための集積回路の製造における、集積回路に含まれる縦型バイポーラ・トランジスタの絶縁のための浅い溝を形成する方法であって、

第1のドーピング型の半導体基板(10)を提供する工程と、

前記基板に、前記バイポーラ・トランジスタのための第2のドーピング型の埋込みコレクタ領域(31)を形成する工程と、

前記基板上にシリコン層(41)をエピタキシャル成長させる工程と、

前記バイポーラ・トランジスタのための前記第2のドーピング型の能動領域(41)を、前記エピタキシャル成長したシリコン層に形成し、前記能動領域は埋込みコレクタ領域(31)の上に位置する工程と、

30

浅い溝(51)を前記エピタキシャル成長したシリコン層と前記シリコン基板に形成し、前記浅い溝は前記能動領域を水平面で囲み、前記基板内へ距離(z)を垂直に延ばす工程と、

前記浅い溝を電気的絶縁材料(81)で満たす工程と、

を含む前記浅い溝の形成方法。

#### 【請求項26】

請求項25に記載の方法において、前記埋込みコレクタ領域(31)及び前記浅い溝(51)は、前記埋込みコレクタ領域が前記浅い溝の下に位置する領域(x)内に延びるように、相互に形成される、前記方法。

40

#### 【請求項27】

請求項25あるいは請求項26に記載の方法において、前記浅い溝は、マスキング及びエッチングによって形成される、前記方法。

#### 【請求項28】

請求項25から請求項27のいずれかに記載の方法において、前記基板ドーピングはp型であり、前記埋込みコレクタ領域及び前記能動領域ドーピングはn型である、前記方法。

#### 【請求項29】

請求項28に記載の方法において、前記埋込みコレクタ領域は、好ましくは少なくとも約 $1 \times 10^9 \text{ cm}^{-3}$ の濃度に強度にnドープされ、前記能動領域は、約 $1 \times 10^7 \text{ cm}^{-3}$ 以下の濃度、好ましくは約 $5 \times 10^6 \text{ cm}^{-3}$ 以下、さらに好ましくは約 $1 \times 10^6 \text{ cm}^{-3}$ 以下、そ

50

して最も好ましくは約  $1 \times 10^{-16} \text{ cm}^{-3}$  の濃度にドープされる、前記方法。

【請求項 3 0】

請求項 2 5 から請求項 2 9 のいずれかひとつに記載の方法において、深い溝 (63) が前記浅い溝 (51) において形成され、特に前記浅い溝に自己整合する、前記方法。

【請求項 3 1】

集積回路、特に無線周波数アプリケーションのための集積回路は、

第 1 のドーピング型の半導体基板 (10) であって、前記基板は上部表面を有する前記半導体基板 (10) と、

前記基板に形成された縦型バイポーラ・トランジスタであって、前記トランジスタは第 2 のドーピング型の能動領域 (41) を含み、前記能動領域にはエミッタ (202) とベース (174) とが形成され、前記第 2 のドーピング型の埋込みコレクタ領域 (31) を有し、前記埋込みコレクタ領域は能動領域の下に位置する前記縦型バイポーラ・トランジスタと、

前記縦型バイポーラ・トランジスタの絶縁のための浅い溝 (51) であって、前記浅い溝は、基板の表面に沿って見られるように、前記トランジスタの能動領域を囲むと共に電気的絶縁材料 (81) で満たされた前記溝と、

前記浅い溝 (51) は、前記基板の上部表面から、前記埋込みコレクタ領域が位置する深さ (z) まで前記基板内に垂直に延びる、前記集積回路。

【請求項 3 2】

請求項 3 1 に記載の集積回路において、前記埋込みコレクタ領域 (31) は、前記浅い溝 (51) の下に位置する領域 (x) 内に延びることを特徴とする、前記集積回路。

【請求項 3 3】

請求項 3 1 あるいは請求項 3 2 に記載の集積回路において、前記埋込みコレクタ領域は、好ましくは少なくとも約  $1 \times 10^{-19} \text{ cm}^{-3}$  の濃度に強度に n ドープされ、前記能動領域は、約  $1 \times 10^{-17} \text{ cm}^{-3}$  以下の濃度、好ましくは約  $5 \times 10^{-16} \text{ cm}^{-3}$  以下、さらに好ましくは約  $1 \times 10^{-16} \text{ cm}^{-3}$  以下、そして最も好ましくは約  $1 \times 10^{-16} \text{ cm}^{-3}$  の濃度にドープされる、前記集積回路。

【請求項 3 4】

請求項 1 から請求項 2 4 のいずれかひとつに記載の方法において、縦型バイポーラ・トランジスタが、バイポーラ・トランジスタの前記能動領域に形成され、前記バイポーラ・トランジスタのドーピング・プロファイル及び熱プロセスは、2 V より大きいベース・コレクタ・バイアス電圧において、そのベース (174) からそのサブコレクタ (26) に十分空乏するトランジスタを生成する、前記方法。

【請求項 3 5】

請求項 1 から請求項 2 4 のいずれかひとつに記載の方法において、縦型バイポーラ・トランジスタが、バイポーラ・トランジスタのための前記能動領域に形成され、前記バイポーラ・トランジスタのドーピング・プロファイル及び熱プロセスは、1 V より大きいベース・コレクタ・バイアス電圧において、そのベース (174) からそのサブコレクタ (26) に十分空乏するトランジスタを生成する、前記方法。

【請求項 3 6】

請求項 3 4 あるいは請求項 3 5 に記載の方法において、コレクタは逆行ドーピング・プロファイルをもって形成される、つまり、バイポーラ・トランジスタのための能動領域の上部表面からの距離に伴いドーピング・レベルが上がるよう形成される、前記方法。

【発明の詳細な説明】

【技術分野】

【0001】

(本発明の技術分野)

本発明は一般に、シリコン IC 技術の分野、特に、バイポーラ RF - IC のために特に設計されたプロセスフローにおける能動および受動素子の集積に関する。

【背景技術】

10

20

30

40

50

## 【0002】

(本発明の関連技術および背景の記述)

改良シリコン・バイポーラ、CMOSあるいはBiCMOS回路は、今日、1-5GHzの周波数範囲における高速アプリケーションに対して使用され、以前はIII-Vに基づく技術を使用してのみ実現可能であった回路に取って代りつつある。これらの主なアプリケーション領域は、現代通信システムに対するものである。回路は、ほとんどの場合、例えば電流および電圧切替えのようなアナログ機能、および、例えば混合、増幅、および検出機能のような高周波無線機能のために使用されている。

## 【0003】

例えば通信アプリケーションに適したトランジスタを得るために、低信号通過時間( $f_T$ )が必要なだけでなく、高最大振動周波数( $f_{MAX}$ )および高い線形性が必要とされる。これらを得るために、トランジスタは、短く且つ最適化された縦型構造を持つだけでなく、主にコレクタ-ベース容量およびベース抵抗から成る内部寄生も非常に低くなければならない。電子移動度が高いので、回路設計に対する主要な構成要素はNPNトランジスタである。従ってプロセスは、NPNトランジスタが最適な特性を持つことを主要な目的として設計される。

## 【0004】

回路設計を容易にするために、ある種のp型素子もまた必要である。高性能PNPトランジスタを、前記の原理に従って設計されたプロセスに追加することができるが、このような方法は通常、付加的マスク層が必要となりプロセスが複雑となるためにコストが非常に高くなる。

## 【0005】

しかし、ほとんどの回路設計に対して、通常どんな単純なp型素子でも、ほとんどの設計上の必要性を満たすのに十分である。BiCMOSプロセスにおいては、もちろん、PMOSトランジスタを使用することができる。バイポーラRF-ICプロセスにおいては、通常、さらなる複雑なプロセスが無くても、ラテラル(横型)PNPトランジスタを得ることができる。

## 【0006】

ICプロセスの能動素子は改良され続けているけれども、素子の絶縁を改良することにより、能動素子の改良に対応する必要がある。4分の1ミクロン以下の技術に対しては、ほとんどの表面を達成するために、深い溝絶縁(STI; shallow trench Isolation)が広く使用されている。STIを使用すると、LOCOS絶縁と比較して、CMOSおよびバイポーラ回路の双方に対して、より高い実装密度、より厳密な設計規則およびより低い寄生、そしてより高い歩留りを達成することができる。ナンダクマル、A.チャタージ、S.スリンダール、K.ジョイナー、M.ロダー、およびI.-C.チェンによる“改良ULSI CMOS技術のための深い溝絶縁”、1998

IEDM Tech. Dig.、133ページ、を参照されたい。エッティングおよび再充填プロセス工程が必要とはなるが、STIは、回路構成要素間の絶縁に必要な領域をかなり小さくすることができる。化学的機械的平面化(CMP; Chemical Mechanical Planarization)は、STIを実現するためのプロセスフローにおいて広く使用されてきている。感度の高いアナログ無線回路に対する寄生および漏話をさらに減少させるために、バイポーラプロセスにおいては、深い溝(DT; Deep Trench)絶縁が、素子間の接合絶縁に代わって使用される。P.ハントおよびM.P.コークによる“プロセスHE:アナログおよびデジタルアプリケーションのための高度改良溝絶縁バイポーラ技術”、Proc. IEEE CICC 1988、816ページ、を参照されたい。DT絶縁は、バイポーラにおける程一般的ではないが、CMOSにおいても使用されている。R.D.ラング、H.モモセ、Y.ナガクボによる“深い溝絶縁CMOS素子”、1982 IEDM Tech. Dig.、237ページ、を参照されたい。高性能RF-ICに対しては、STIおよびDTを同時に使用することができる。国際特許出願公開WO 0120664(発明者H.ノルストロム、C.ビヨルマ

10

20

30

40

50

ンダ、および T. ヨハンソン) を参照されたい。

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、高性能 R F - I C に対して S T I 絶縁を使用すると、以前にはとても成功していたラテラル P N P トランジスタを得るための既存の構造は、もはや使用することができないかもしれない。構造のウェルのためのエピが  $1 \mu m$  より小さい場合、(表面からエピの中に約  $0.5 \mu m$  下まで届く) S T I 絶縁と共に使用すると、プロセスの後には、電解領域上の S T I 絶縁の下にはウェル領域が存在しなくなってしまう。代わりに、サブコレクタが電解酸化物の直接下に位置することになる。ラテラル P N P 構造を保つことはまだ可能であるが、ベースはいまや主に、多量にドープされたサブコレクタ領域から成り、従って、電流利得( )が低すぎて使用できないこととなる。適当な特性を有する p 型素子を得る他の方法を見つけなければならない。

【0008】

さらに、今日の S T I 絶縁を使用すると、異なる素子領域間の漏洩電流の問題が起こる可能性がある。さらに、バイポーラ・トランジスタにおける非常に低いベース・コレクタ容量を達成することが困難になるかもしれない、高ベータの寄生 p n p 素子(外因性ベース / n ウェル / p ウェル)は、特に n ウェルのドーピングが非常に低度の場合、問題を起すかもしれない。

【課題を解決するための手段】

【0009】

(発明の概要)

従って、本発明の目的は、集積回路、特に無線周波数アプリケーションのための集積回路の製造方法を提供することである。本方法により、バイポーラ・トランジスタおよび M O S 素子、特に P M O S トランジスタおよび他の p 型 M O S 素子を含む高品質集積回路を、最少のプロセス工程を使用して効果的に製造することができる。

【0010】

この点に関して、本発明の特別な目的は、複数の多目的プロセス工程を含む方法を提供することである。

【0011】

この目的のために、本発明は第 1 の態様により、以下の工程を含む方法を含む。

- シリコン基板を提供する。基板は、均質基板 (homogeneous substrate) あるいはウエハ上のエピ層であってもよい。

- バイポーラ・トランジスタの能動領域、および、M O S 素子の能動領域を、好ましくは、基板の 2 つの表面領域および / あるいは基板上のエピ層の 2 つの基板領域をドープすることによって、シリコン基板上に形成する。

- 電界絶縁領域を、水平面において、好ましくは浅い溝絶縁 (S T I) によって、および選択的に深い溝絶縁 (D T) によって、能動領域の周りに形成する。

- M O S ゲート・スタックを、M O S 素子の能動領域上に、好ましくはゲート酸化物層上のゲート・ポリシリコン層の形で、形成する。

- 電気的絶縁材料、好ましくは窒化物の層を、M O S ゲート・スタック上およびバイポーラ・トランジスタの能動領域上に形成する。

- バイポーラ・トランジスタの能動領域に、好ましくはエッチングにより電気的絶縁層に開口を形成することにより、ベース領域を画定する。

- 電気的絶縁層における開口は、電気的絶縁層の残りの部分がバイポーラ・トランジスタのための能動領域を部分的に、つまり能動領域の円周に沿った外側部分を覆うように、形成される。

- 電気的絶縁層は、M O S ゲート領域上に残り、特にイオン打ち込み、熱酸化、および / あるいはエッチング工程を含む後続の製造工程の間、M O S ゲート領域を密閉し保護する。

10

20

30

40

50

## 【0012】

電気的絶縁層は、バイポーラ・トランジスタのコレクタ・プラグ領域上にも残ることが都合がよい。

電気的絶縁層の一部分は、プロセスにおいて製造される並列プレート・コンデンサ内の誘電体として使用されることが好ましい。

## 【0013】

本発明のさらなる目的は、集積回路、特に無線周波数アプリケーションのための集積回路の製造における、回路内に含まれる縦型バイポーラ・トランジスタの絶縁を改良するための、浅い溝の形成方法を提供することである。

## 【0014】

この点に関して、本発明の特別な目的は、電流漏洩問題の無いバイポーラ・トランジスタを製造する方法を提供することである。

## 【0015】

この目的のために、本発明は第2の態様により、以下の方法を提供する。

- 第1のドーピング型、好ましくはp、の半導体基板が提供される。

- バイポーラ・トランジスタのための第2のドーピング型、好ましくはn、の埋込みコレクタ領域が基板に形成される。

- シリコン層が基板上にエピタキシャル成長される。

- バイポーラ・トランジスタのための第2のドーピング型の能動領域が、エピタキシャル成長シリコン層内に形成され、能動領域は埋込みコレクタ領域の上に位置する。

- 浅い溝が、エピタキシャル成長シリコン層およびシリコン基板内に形成され、浅い溝は、水平面において能動領域を囲み、基板内にある程度の距離垂直に延びる。

- 浅い溝は、電気的絶縁材料で満たされる。

## 【0016】

埋込みコレクタ領域および浅い溝は、埋込みコレクタ領域が浅い溝の下に位置する領域内に延びるように、相対的に形成されることが好ましい。

## 【0017】

本発明のさらなる目的は、特に無線周波数アプリケーションのための、新しい方法により浅い溝によって絶縁された縦型バイポーラ・トランジスタを含む集積回路を提供することであり、この新しい方法によりトランジスタの性能が改良され、それにより集積回路が改良される。

## 【0018】

この目的のために、本発明は第3の態様により、以下のものを含む集積回路を含む。

- 第1のドーピング型、好ましくはp、の半導体基板であって、基板は上面を有する。

- 基板に形成された縦型バイポーラ・トランジスタであって、トランジスタは第2のドーピング型、好ましくはn、の能動領域を含み、能動領域にはエミッタおよびベースが形成される。第2のドーピング型の埋込みコレクタ領域であって、埋込みコレクタ領域は能動領域の下に位置する。

- 縦型バイポーラ・トランジスタを絶縁するための浅い溝であって、

- 浅い溝は、基板の表面に沿って見られるように、トランジスタの能動領域を囲み、電気的絶縁材料によって満たされ、基板の上面から埋込みコレクタ領域が位置する深さまで基板内を垂直に延びる。

## 【0019】

埋込みコレクタ領域は、浅い溝の下に位置する領域内に延びることが好ましく、埋込みコレクタは、同様に浅い溝に囲まれているコレクタ・プラグに接続する。

## 【0020】

本発明のさらなる特徴および利点は、以下に説明される本発明の好ましい実施例の詳細な記述、および、付随する図面1-22から明らかになるであろう。これらの記述および図面は例示のためだけのものであり、従って本発明をこれらに制限するものではない。

## 【実施例】

10

20

30

40

50

## 【0021】

(実施例の詳細な記述)

以下の記述において、説明するためであって制限するためではなく、本発明が完全に理解されるように特定の詳細が説明される。しかし、この分野の技術者には、本発明はこれらの特定の詳細から離れた他の態様においても実施することができる事が明らかである。

## 【0022】

この記述は、NPNトランジスタと、窒化物およびMIM（Metal - Insulator - Metal；金属 - 絶縁 - 金属）コンデンサと、抵抗器とを含む、高周波アプリケーションのための集積シリコン・バイポーラ回路の製造方法を説明する。特にこの記述は、回路設計に必要な単純なp型素子を生成することを目的とする、PMOSトランジスタを回路に集積する概念を説明する。

絶縁が高度にドープされたサブコレクタ層まで達するように、STIの深さを選択することが、特に重要である。

## 【0023】

以下の素子が使用可能である。

- ・NPN

- ・PMOS

- ・準ラテラルPNP素子（PMOSから派生）

- ・窒化物コンデンサ

- ・MIMコンデンサ

- ・ポリシリコン抵抗器

## 【0024】

ここで図1-22を参照して、高性能NPNトランジスタ、PMOSトランジスタおよび受動素子を製造するためのプロセスフローの本発明による実施例の詳細を、番号を付いた22個の段落において詳細に示すこととする。

## 【0025】

## 1. 出発原料

図1は、埋設n+層（サブコレクタ）の形成前の、ホウ素ドープされた、シリコンp型ウエハの断面を示している。シリコン・ウエハは、エピ・ウエハであり、通常10mOhm cmの抵抗率を持つ高度にドープされたp+ウエハ11から成る基板10を含み、低度にドープされたp型のシリコン層12がウエハ11上に成長している。このエピ層は、通常5-10μmの厚さであり、通常10-200hm cmの抵抗率を有する。

## 【0026】

本発明の好ましい実施例においては、低度にドープされたp型シリコン層12は、図1に示されるよりもかなり厚さがあることを理解されたい。

また、p型ウエハは、通常1-200hm cmの抵抗率を有する、均質に低度にドープされたp型ウエハ（図示されていない）であってもよい。

## 【0027】

前記の概要における用語“基板”は、均質シリコン基板あるいはウエハ上にエピタキシャル層を有する構造をさすことができ、詳細な記述および請求項においても同様である。

## 【0028】

## 2. サブコレクタ埋込み

次に図2を参照すると、シリコン二酸化物の薄い保護層21が、シリコン基板10の表面上に、熱酸化により、通常20nmの厚さに形成される。この層の目的は、打ち込みの間、金属あるいは他の不純物による汚染に対するスクリーンとして機能することである。層の厚さは、後続の工程におけるイオン打ち込みを層21を通して実行することができるよう、選択される。

## 【0029】

フォトレジストの膜22がウエハ表面上に当てられ、フォトリソグラフィによってパタ

10

20

30

40

50

ーン形成される。SUBマスクとも呼ばれるこのパターン層の目的は、後続のイオン打ち込みをマスクすることにより、バイポーラ・トランジスタの埋込みコレクタのための領域23、および、PMOSトランジスタ24およびコンデンサ25それぞれのためのドープされた埋設領域を画定することである。

#### 【0030】

次に、サブコレクタのドーピングのためのイオン、好ましくは約50keVのエネルギーを使用した約 $6 \times 10^{-15} \text{ cm}^{-2}$ のドーズ量のヒ素、が打ち込みされる。ドープされた領域は、図2において26によって示されている。 $(XXEYY)$ という表記が $XX \times 10^{YY}$ の代わりに使用される。)エネルギーは、イオンが、保護されていない領域上の薄い酸化物層を通してシリコン内に到達するが、フォトレジストによって保護されている領域においてはシリコンに浸透しないように、選択される。打ち込みの後、フォトレジストは、一般的なウェットあるいはドライな化学的方法によって除去される。

#### 【0031】

他のn型ドーパント、例えばアンチモン(Sb)を、n+サブコレクタ領域を形成するために代替的に使用することができる。しかし、ヒ素を使用すると、所定の層の厚さに対して、より低い抵抗率を得ることができ、このことは素子にとって利点であり、例えばより低いコレクタ抵抗およびより低い側壁コレクタ-基板容量を得ることができる。また、ヒ素の拡散率はSbより高いので、より短いドライブ・イン時間およびより低い温度で、望ましいサブコレクタ・プロファイルを得ることができる。

#### 【0032】

### 3. サブコレクタ・ドライブ・インおよび酸化およびp型絶縁埋込み

次に、3工程熱プロセスが行われる。

最初に、打ち込み領域における損傷を再結晶化するために、600の焼きなましが使用される。

#### 【0033】

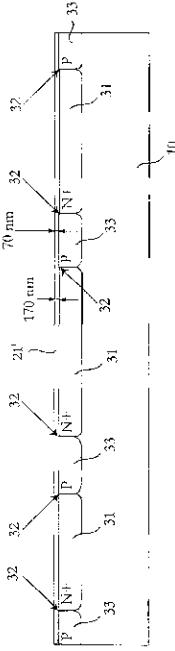

次に、図3に示されるようなドープされた領域31が得られるように、サブコレクタ内に打ち込みされたヒ素を再分布するために、約1100の高温ドライブ・インが行われる。

温度はそれから、約900に下げられ、そこで酸化が湿った空気の中で行われる。高さにドープされたn型領域はより高い酸化率を有するので、ヒ素を打ち込みされた領域においては、打ち込みされていない領域(70nmまで)よりもより厚い酸化物(170nmまで)が得られる。シリコン原子はこの酸化の間に消費されるので、酸化物を除去した後には、40-50nmの高さの段32がシリコン表面に残される。痕跡は後に、後続のリソグラフィ工程において、アライメントマークとして機能する。

#### 【0034】

従来この工程には、1100の範囲の一定の温度の酸化が使用されている。十分に高い段を生成するために、ヒ素打ち込みに先立ち、最初の酸化物をより厚く成長させなければならない。酸化物は、埋込みコレクタ領域を定義するために、パターン形成されエッチングされ、打ち込みに先立ち、薄いスクリーン酸化物がエッチングされた開口内に成長される。シリコンにおけるアライメント段に対する最大の貢献は、薄いおよび厚い酸化物領域の異なる酸化物成長率からくる。より低い酸化温度を使用することによって、Y.-B.ワン、P.ヨッソン、およびJ.V.グランによる、“ヒ素改良酸化および埋込みコレクタ工程の効果的制御”、196回電気化学協会会議(ハワイ、ホノルル、1999年10月17-22日)に記述されるように、アライメントマークを生成するための個別の層を必要としない、単純化されたプロセスフローを使用することができる。

#### 【0035】

酸化物を除去する前に、通常約120keVのエネルギーと $8 \times 10^{-12} \text{ cm}^{-2}$ のドーズ量のホウ素から成るp型イオン打ち込みが実行される。その結果のpドープされた領域は、図3において33によって示されている。打ち込みは何のマスクも使用せずに行われる。エネルギーおよびドーズ量は、n+サブコレクタのヒ素ドープされた領域31において、打ち

10

20

30

40

50

込みされたホウ素が実質的にドーピング・レベルに影響を与えない（ドナー原子の数が本質的に変化しない）ように、選択される。サブコレクタ領域間の領域においては、しかし、適度にドープされたp領域33が形成され、n領域31を互いに絶縁することになる。

【0036】

前記のp型打ち込みを省きながら、出発原料の最初のドーピング・レベルを低めのp型から適度なp型に上げることによって、機能的素子を得ることが可能であることに留意すべきである。しかしこの場合、n+サブコレクタ領域からp-基板への、コレクタ-基板間の容量は、より高くなってしまう。

【0037】

サブコレクタn+領域およびそれらの間のp領域をどのように生成するかという一般的な手順は、ハイブマンによる米国特許第5,374,845号にも示されている。しかしこの特許は、Sbドープされた層に関するものであり、アライメント段は、窒化物-酸化物2層を使用する従来の方法で生成されている。

【0038】

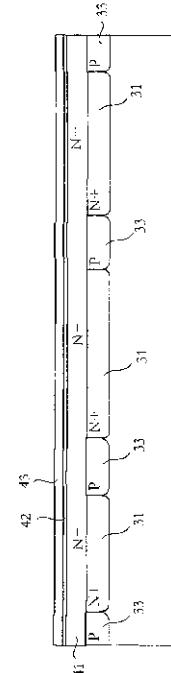

4. エピ付着およびnウェル埋込み

酸化物21は、好ましくはウェット化学（フッ化水素酸、HF）によって除去される。シリコン表面において前記の段32が現れ、約0.5から1μmの厚さのドープされていない（真性の）エピタキシャル・シリコン層41が、一般的な技術を使用して、表面上に成長される。図4aを参照されたい。層41は、エピタキシャル成長の間、代替的にn型ドープされた層であってもよい。通常のドーピング・レベルは、約1E16cm<sup>-3</sup>であろう。ハイブマンによる米国特許第5,374,845号においては、対応するエピタキシャル層は、軽度にドープされているが（抵抗率は100hmcmより高い）、まだ本質的には真性であるとみなされる。しかし、均一にドープされたn型エピタキシャル層は、プロセスフローのより後において、いわゆるトップ・ダウン接触である、基板表面接触の形成を複雑化する。

【0039】

エピタキシャル成長の間、1100の範囲の高温が使用される。p型打ち込み領域33におけるアクセプタ原子は基板内に拡散し、埋設p-領域が、エピタキシャル・シリコン41の下の、n+サブコレクタ31が存在しない領域に形成される。前記の段がエピタキシャル・シリコン層の表面上に再生成されることに、注意されたい。

【0040】

エピタキシャル層は、以下に記述するように、nおよびp型の領域（nウェルおよびpウェル）を得るために、選択された領域においてドープされる。n+サブコレクタ31の直接上に位置するn型領域において、バイポーラ・トランジスタおよびコンデンサが形成される。表面から基板への基板接触が、n型領域の間のp型領域に形成される。

【0041】

線形性の高い（つまり、信号を増幅する際にほとんど歪みを加えない）NPNトランジスタを得るために、小さい電圧変化の低いベース-コレクタ容量が有利である。エピの厚さおよびnウェルのドーピングは、本発明において、NPNトランジスタにおいて使用された場合、既に低いベース-コレクタ・バイアス電圧において、nウェルがベースからサブコレクタに十分に空乏するように選択される。従ってベース-コレクタ容量は、広いバイアス範囲に対してほとんど一定の値を示すことになる。この作用は、“パンチ・スル-”コレクタ素子に類似する。ニウその他による、IEEE BCTM会議議事録、1999年、50-53ページを参照されたい。

【0042】

浅い溝のためのハード・マスクが、次に形成される。浅い溝のためのマスク層は、シリコン表面を酸化し、通常約10nmの厚さの熱シリコン二酸化物の層42を形成することにより形成される。次に、約200nmの厚さのシリコン窒化物層43が、化学蒸着法（CVD；Chemical Vapour Deposition）により付着される。他の厚さおよび/あるいはマスク材料の組み合わせも可能である。

10

20

30

40

50

## 【0043】

ハード・マスクを通したイオン打ち込みして、前記のnウェルをエピタキシャル層に形成する。このn型打ち込みのために、好ましくはリンが、通常650keVのエネルギーにおいて9E11cm<sup>-2</sup>のドーズ量で使用される。打ち込みは、何のリソグラフィ・マスク層も使用せずに実行される。電気的 requirement およびnウェルの厚さにより、エネルギーおよびドーズ量は広い範囲において選択することができる。イオン打ち込みはまた、表面から離れるほどより高度にドープされる、より平滑なプロファイルあるいはドーピング・プロファイル、つまりいわゆる逆行プロファイルを得るために、異なるエネルギーおよびドーズ量における複数の打ち込みを含んでもよい。ウエハの全表面領域は、この時点でnウェルから成る。選択された領域におけるpウェルは、後の工程で形成される。後述の段落9を参照されたい。nウェル・プロファイルはまた、例えばリンあるいはヒ素を使用して、もとの位置においてエピ層をドープすることによっても形成することができる。

10

## 【0044】

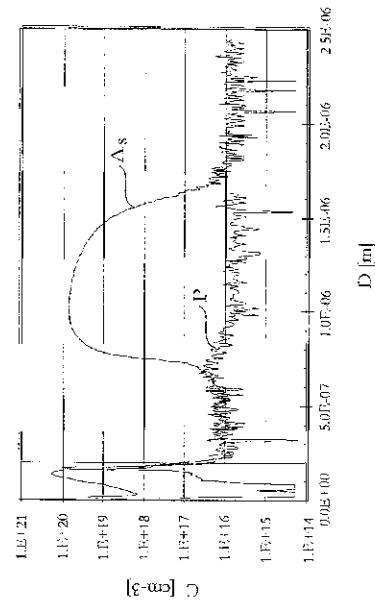

この結果の構造が図4aに示され、この時点における埋込みコレクタ構造上のnウェルのドーピング・プロファイルは、図4bのSIMS図によって示されている。

## 【0045】

段落5-8において、浅いおよび深い溝絶縁を使用した素子絶縁が記述される。絶縁構成はまた、国際公開第WO 0120664号にも記述されている。

20

## 【0046】

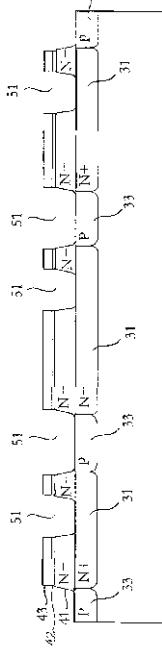

## 5. 浅い溝および能動領域の形成

ここで、浅い溝の形成を検討する。フォトレジスト(図示されていない)が窒化物層43上に塗布され、第1のマスク、いわゆるSTIマスクを使用して露光され、それにより開口が残され、そこで浅い溝がエッチングされる。エッチングは、異方性であることが好ましく、反応イオン・エッチング(RIE)によって、窒化物/酸化物層を通りシリコン基板内まで実行され、図5aに示されるように、先細り(テーパ)の(垂直な)浅い溝51を形成する。溝の好ましい深さは、シリコン層41の上面から0.2-0.7μm、あるいはさらに典型的には0.3-0.5μmである。

フォトレジストは、浅い溝のエッチングに続いて除去される。

または、酸化物/窒化物2層42、43がエッチングされ、その後にレジストが剥離される。それから段において、STIが、2層42、43をハード・マスクとして使用してエッチングされる。

30

## 【0047】

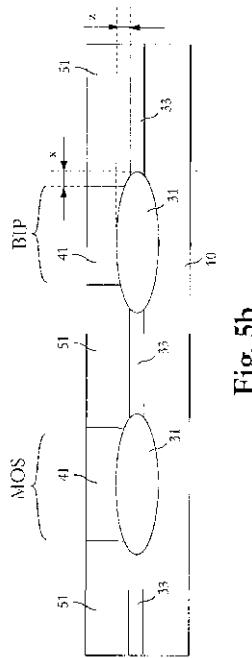

浅い溝51の代替的な好ましい設計が、図5bを参照して以下に簡潔に記述される。

浅い溝51は、それらが、シリコン表面つまり基板10上のシリコン層41の表面から、埋込みコレクタ領域31に、好ましくは埋込みコレクタ層31の深さよりさらに深くまで垂直に延びるように、形成することができる。重複する距離は、図5bにおいてzによって示されている。

さらに、埋込みコレクタ領域31および浅い溝51は、埋込みコレクタ領域31が対応する浅い溝の下に位置する領域にまで延びるように、相対的に形成することができる。浅い溝の下に位置する領域は、図5bにおいてxによって示されている。

40

## 【0048】

このような設計には数々の利点がある。異なる素子領域間の漏洩電流の問題が回避され、改良された素子絶縁が得られる。

## 【0049】

この設計は、より深い浅い溝のために、(特にバイポーラ・トランジスタに適している)低度にドープされたnウェル41を提供する。低い値のベース-コレクタ容量C<sub>bc</sub>を実現することができる。他のプロセスにより生ずるかもしれない、外因性ベース/nウェル/pウェルから成る寄生p/n/p素子は回避される。埋込みコレクタ領域もまた、浅い溝の角の下を(図5bにおいて示される距離xまで)延びるからである。接合絶縁プロセスにおいて、この寄生素子は、10より大きいベータを持つかもしれない。nウェル・ド

50

ーピングを低度にすると、本発明による浅い溝構造が使用されなければ、ベータと同様に構造のパンチ・スルーの危険性を増大させるであろう。

#### 【0050】

このような本発明によるSTI絶縁を使用することにより、以下の2つの段落において記述される深い溝絶縁はラッチ・アップ問題をなくし、ラッチ・アップ問題のない絶縁を得ることができる。

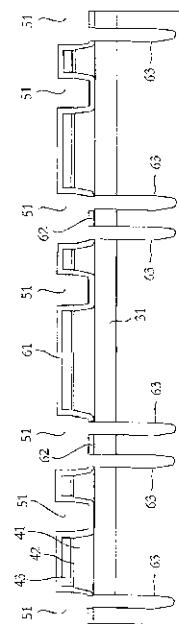

#### 【0051】

##### 6. 深い溝のためのハード・マスクの形成、および深い溝のエッチング

図6を参照して、深い溝のためのハード・マスクの形成を記述する。通常0.1-0.5μmの厚さのシリコン二酸化物層61が、例えばCVDによって、好ましくは適合的に、その構造の上部(つまり、窒化物層の残りの部分および深い溝の中)に付着される。酸化物層は適合的に付着されることが好ましい。そうでなければ後続のマスキングおよびエッチングに対するマージンを減少させるからである。フォトレジストが塗布され、第2のマスク、いわゆる深い溝マスク(図示されていない)を使用して露光される。溝マスクの開口は、深い溝領域内のどこにでも置くことができる。深い溝の幅は、異なる大きさのマスクを使用することにより選択することができる。通常、好ましくは約1μm以下の固定の横幅(厚さ)の溝を使用することが好ましい。そうでなければ、一様でないエッチングを使用することで問題が生じ、深い溝を再充填し平面化することが困難になるからである。

#### 【0052】

酸化物層は、反応イオン・エッチング(RIE)によりエッチングされ、深い溝の底面にまで延びる溝開口を画定する。窒化物層の上部においては、酸化物層がフォトレジスト・マスクにより保護され、この酸化物は後に、後続のエッチング工程の間、これらの領域のためのハード・マスクとして機能する。酸化物層は、深い溝領域の部分62において残され、そこには深い溝は形成されない。エッチングの後に、フォトレジストは除去される。

前記の国際公開第WO 0120664号において、深い溝が深い溝の端と自己整合するように、どのように付着されたシリコン二酸化物層を選択し、溝マスクを整列させるかが記述されている。

#### 【0053】

それから、深い溝63が、酸化物61をハード・マスクとして使用して、エッチングにより形成される。酸化物スペーサが生成されると、それは深い溝から能動領域への距離を画定する。深い溝の深さは、少なくとも数ミクロンであり、より好ましくは少なくとも5ミクロンである。この結果の構造が、図6に示されている。溝プロファイルは、直線的、および/あるいは先細りで、底を丸くして形成することができる。

#### 【0054】

本発明の好ましい実施例において、前記段落1において言及されたp型の厚い低度にドープされたシリコン層12を用いると、低度にドープされたシリコン層12は、図6における参照番号63の位置に実質的に対応する深さまで到達することができることに注意されたい。

深い溝のパターン形成のための酸化物ハード・マスクは、後に、例えばHFにおいて除去される。

#### 【0055】

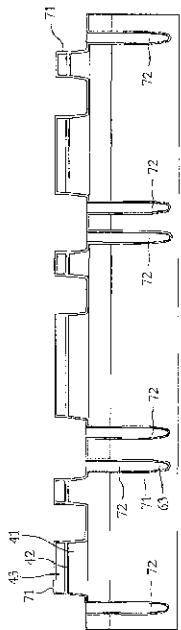

##### 7. 深い溝の充填および平面化

次に続く溝領域51、63の充填および平面化は、従来技術において知られているいくつかの方法で実行することができる。例えば、プロセスは、ライナ酸化を行うことにより続けられる。この目的は、溝の尖った端を丸い角にし、圧力および望ましくない電気的影響を減少させることである。このことは、薄い(20-30nm)熱酸化物71を高温(>1000)において成長させることにより、達成される。図7を参照されたい。溝は、従来の方法により、200nmの厚さのTEOS層および1500nmのポリシリコン

10

20

30

40

50

72で満たされる。ポリシリコンは、それから、浅い溝領域から全てのポリシリコンを除去するために、再びエッティングされる。

【0056】

または、ポリシリコンは、浅い溝領域において再びエッティングされる前に、化学的機械的研磨により、平面化される。これにより、深い溝におけるポリシリコン充填の後退が減少され、その結果、浅い溝を充填する後続の工程において、より薄い酸化物を付着することができる。

この結果の構造が、図7に示されている。

【0057】

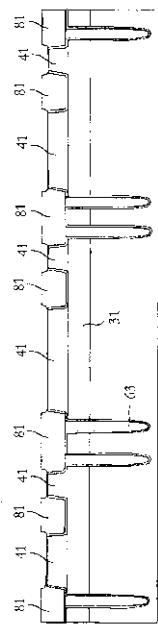

8. 浅い溝の充填および平面化；2層剥離

次に、残りの浅い溝が、例えばCVD酸化物あるいは高密度プラズマ(HDP)酸化物81で満たされ、ドライ・エッティング方法あるいは化学的機械的研磨のいずれかにより平面化される。図8を参照されたい。

このプロセスモジュールの仕上げの工程として、素子領域上の窒化物43および酸化物42(特に図7に見られる)が、好ましくはウェットな方法により、除去される。その結果の構造は、絶縁領域上の酸化物81および素子領域上の露出したシリコン41から成る。

【0058】

9. pウェルの形成

選択された領域において(図面には示されていない)、pウェルが次に形成される。BiCMOSプロセスにおいて、pウェルは主に、NMOSトランジスタおよびp型基板接触のために使用される。純粋なバイポーラプロセスにおいて、pウェル領域は主に、基板接触のために使用される。プロセスフローの後の段階において、表面に、高度にドープされたp+接触を形成することができる。pウェル領域は、pウェル領域の下にはサブコレクタn+領域は存在せず、従って、pウェル領域がp型基板と直接接触できるように、設計される。

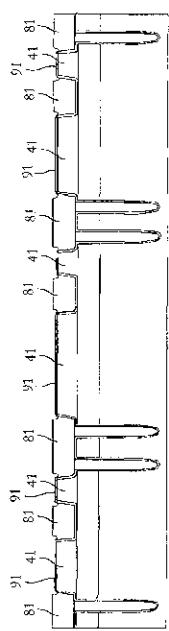

【0059】

pウェルは、最初に保護酸化物91を成長させることによって、形成される。図9を参照されたい。酸化物91はプロセスフローの後の段階において、シリコン基板と付着されたシリコン窒化物との間のパッド酸化物としても機能する。酸化物91の厚さは、通常10nmである。

【0060】

pウェル・マスクと呼ばれるフォト・マスク(図示されていない)が、それから付着されパターン形成される。ホウ素が、シリコンにイオン打ち込みされる。エネルギーおよびドーズ量は、イオンが酸化物を通りシリコン内に浸透するが、フォト・マスクは通らないように選択される。より平滑なあるいは逆行ドーピング・プロファイルを得るために、二重打ち込みを使用してもよい。特定の例においては、選択された領域における約 $1\text{E}16\text{ cm}^{-3}$ のpウェル・ドーピングを得るために、 $100\text{keV}$ のエネルギーにおける $8\text{E}12\text{ cm}^{-2}$ のドーズ量のホウ素の二重打ち込みが、 $200\text{keV}$ のエネルギーにおける $1\text{E}13\text{ cm}^{-2}$ のドーズ量の他の打ち込みと共に使用された。打ち込みの後、フォト・マスクは、従来のウェットなあるいはドライな方法を使用して除去される。

【0061】

段落10-12において、PMOS素子を生成するための、プロセスフローにおける付加的工程が記述される。PMOS素子をRF-ICプロセスフローに追加する理由は、上述の通りである。付加的工程は、ここに記述されるように、ウエハ上の他のどんな素子にも影響を与えることなく、完全に省略することができる。

【0062】

n+ゲートを有しリソグラフィ的ゲート長が約 $0.8\mu\text{m}$ の単純なPMOSトランジスタの集積の態様を、ここで説明する。例えば、S.ウルフによる“VLSI時代のためのシリコンプロセス、第2巻 - プロセス集積”、ラティス・プレス、サンセット・ビー

チ、1990年、392-397ページを参照されたい。従来のCMOS/BiCMOSプロセスにおいて、0.5-2μmのゲート長範囲において、ゲート材料に対する最も一般的な選択は、重度にドープされたn型ポリシリコンである。二重ポリ・バイポーラプロセスにおいては、重度にドープされたn+およびp+ポリシリコンが共に使用可能である。n+ゲートPMOSトランジスタは、プロセス集積問題のために、選択されていた。n+ゲート・ポリシリコンの仕事関数は、理想的にはn素子に適し、p素子に対しては、埋設チャネル素子が形成される。望ましい-0.5から-1Vの範囲への閾値電圧を調節するために、p型打ち込み(ホウ素)が使用される。このことは、ホールが空乏したp領域が形成されるように、n表面を過剰に補償する。正確なホウ素のドーズ量は、いくつかのパラメータ、例えばゲート酸化物の厚さおよびウェル・ドーピング、に依存する。

10

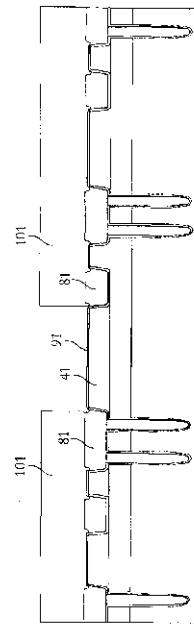

## 【0063】

## 10. PMOS素子の追加：閾値電圧調整

この時点では、ウエハ表面は、図9に示されるように、厚い酸化物81(STI)を有する電界酸化物領域、および、薄い酸化物91(10nmのpウェル酸化物)を有する素子領域から成る。

## 【0064】

PMOS素子の素子領域として機能する領域上では開いた状態にあるフォト・マスク101が、ここで当てられる。図10を参照されたい。ウエハはそれから、p型ドーパント、ホウ素を打ち込みされる。エネルギーは、ドーパントがフォト・マスクには覆われていないが薄い酸化物に覆われている領域に浸透するように、選択される。通常、20-50keVのエネルギーが使用される。ドーズ量は、閾値電圧(VTP)を-0.5から-1Vの範囲にあるよう調整するように、選択される。通常、1E12-1E13cm<sup>-2</sup>のドーズ量が使用される。正確なドーズ量、あるいはドーズ量と要素の組み合わせは、酸化物の厚さおよびPMOSゲートの下の基板の背景ドーピングに依存し、基板の背景ドーピングは、本プロセスフローにおいては、段落4および17において記述される埋込み、つまり、nウェル埋込みおよび2次的コレクタ埋込み、によって設定される。

20

続いて、フォト・マスク101が除去される。

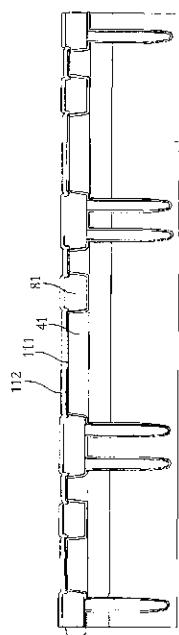

## 【0065】

## 11. PMOS素子の追加：ゲート酸化物および第1のゲート材料の形成

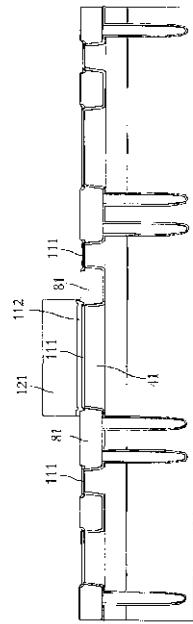

pウェル酸化物(図9-10におけるクエイ(Kooi)酸化物91としても知られる)は、HFにおけるウェット・エッティングによって除去され、熱酸化を使用して、PMOSトランジスタのためのゲート酸化物111に取って代わられる。図11を参照されたい。この酸化物の更新は、高度MOS要求によるものである。pウェル酸化物の品質は、数回のイオン打ち込みを経てきたので、通常十分でないからである。

30

通常、ゲート酸化物111の厚さに対しては、15nm以下の厚さが選択される。この特定の例においては、5Vの動作を支持しなければならないので、12nmの厚さが使用される。

## 【0066】

直ぐに続いて、第1のドープされていないシリコン層112が、LPCVDを使用して、ゲート酸化物111上に付着される。付着パラメータは、結晶質でない層(アルファ・シリコン)が形成されるように、選択される。このことは、付着温度が約550より低い場合に、達成される。この層の厚さはかなり薄く、通常100nm以内であり、好ましくは70nmである。約625の付着温度で形成されたポリシリコンを、ゲート酸化物を保護するために代替的に使用することができる。ポリシリコン材料を使用すると、ウェット・エッティング用試薬は結晶境界に浸透することができるが、代わりにほとんど均一のアルファ・シリコン材料が使用された場合、この効果は大幅に減少される。

40

この結果の構造が、図11に示されている。

## 【0067】

プロセス集積が要求される場合、この時点で、薄い酸化物層(図示されていない)をポリシリコンの上に形成することができる。薄い酸化物は、熱成長酸化物、付着酸化物、あ

50

るいは厚い自然酸化物から成っていてもよい。

【0068】

12. PMOS 素子の追加：MOSBLKエッチング

PMOS ゲートの一部を形成するのに必要とされた付着シリコン層 112 は、ここで、ウエハの他の領域から除去されなければならない。

PMOS 素子領域を覆っているフォト・マスク 121 (PMOS / VTP マスク 101 の反転マスクである MOSBLK マスク) が、ウエハに当てられる。図 12 を参照されたい。マスク 121 を使用して、シリコンは、フィールド酸化物 / ゲート酸化膜 81 / 111 をエッチング止めとして使用しながら、ドライ・エッチングによって除去される。この結果の構造が、図 12 に示されている。

10

フォト・マスクはそれから、従来の方法を使用して除去される。

【0069】

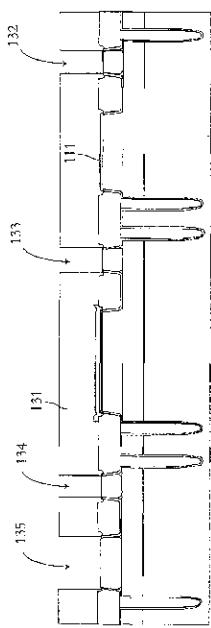

13. コレクタ接触

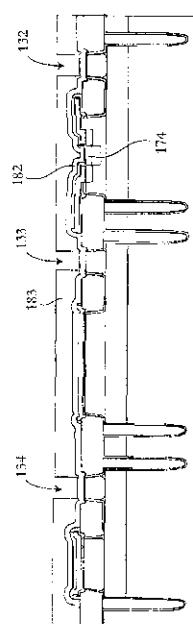

能動素子 (例えば、トランジスタ) を形成するためには、ウエハの表面からサブコレクタへの低抵抗パス (例えば、コレクタ・プラグ) が必要である。また、他の種類のこのような低抵抗パスが必要であるかもしれない。このようなパスは、フォトレジストを付着およびパターン形成して、コレクタ・プラグのようなパスが形成されるべきところに開いた領域 132、133、134、135 が生成されるような D N C A P マスク 131 を得ることによって、リソグラフィ的に画定される。図 13 を参照されたい。図示されている回路の例において、開いた領域 134 は、プラグがサブコレクタと共に、並列プレート・コンデンサにおける 1 つの電極を形成する場所にある。その結果、フォト・マスクはまた、コンデンサ領域 135 も画定する。

20

【0070】

フォトレジスト層がパターン形成された後、開口領域においてドーピングが行われる。ドーピングは、イオン打ち込み、例えば、50 keV のエネルギーおよび  $5 \times 10^{15} \text{ cm}^{-2}$  のドーズ量によるリンのイオン打ち込み、を使用して実行されることが好ましいが、代わりに、ヒ素のような他のドーパントを、単独あるいはリンと組み合わせて使用することもできる。溝絶縁が採用されている場合には、特別の注意が必要である。エネルギーおよびドーズ量の選択に関する詳細は、国際特許出願公開第 WO 9853489 号 (発明者: H. ノルストロム、A. リンドグレン、T. ラーソン、および S. - H. ホン) に記述されている。

30

【0071】

打ち込みの後、ウエハ上にはまだフォト・マスク 131 があり、薄い保護シリコン二酸化物層 111 は、好ましくはドライ・エッチングを使用して、開口領域において除去される。酸化物層 111 は、まだフォトレジストに覆われている他の領域、例えば、バイポーラ NPN トランジスタのベース領域が後に形成される素子領域の部分 (132 および 133 によって示される領域の間)、にまだ残っていることに注意されたい。

この結果の構造が、図 13 に示されている。

【0072】

フォトレジストはそれから、従来の方法により除去され、その後、シリコン・ウエハは、通常 30 分間 600 のプロセスと、それに続く、例えば  $N_2$  あるいは Ar を含む酸化作用のない空気における、30 分間 900 のプロセスの、2 工程熱プロセスを受ける。本発明のプロセスフローにおけるように薄いエピを使用している場合、熱プロセスは、コレクタ抵抗を増加させずに、省略することができる。

40

【0073】

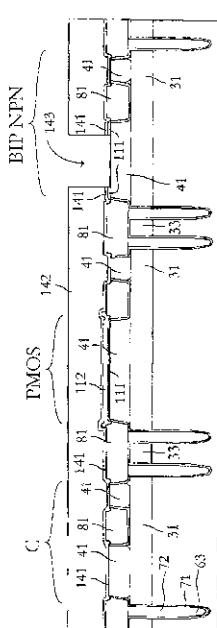

14. 室化物コンデンサ形成およびエミッタ / ベース開口の形成

熱プロセスの後、図 14 において 141 で示される薄いシリコン室化物層が、好ましくは L P C V D 技術を使用して、通常 20 nm の範囲の厚さに付着される。この層の目的は以下の 3 つである。

(i) コンデンサ領域におけるシリコン・ウエハと直接接觸している室化物層の部分が、

50

これから形成されるコンデンサにおける誘電体として機能する。シリコン窒化物は、シリコン二酸化物の誘電定数より約2倍高い誘電定数( )を有するので、酸化物の代わりに窒化物を使用すると、領域単位ごとのより高い容量を得ることができる。

(i i) 能動領域における酸化物上に付着された窒化物層の部分に、これからベース接続が形成され、この部分においてこの絶縁誘電体層が付加的に厚くなり、ベース・コレクタ接合に対する寄生容量がより低くなる。

(i i i) 窒化物層の一部は、後続のプロセスの間、PMOSトランジスタの第1のゲート材料112を密閉する。

#### 【0074】

窒化物は、酸化レジスタント・マスクとしての目的を果たす。保護窒化物フィルムがない場合、重度にドープされたコレクタ・プラグは、重度に酸化され、その結果欠陥を発生させる原因となる。従って、窒化物層がコレクタ・プラグ領域上に残ることが重要である。さらに、窒化物はまた、MOSゲート・スタックにおける第1のポリシリコン層を、望ましくない酸化から保護する。

シリコン窒化物層を付着するのに先立ち、高度にドープされたn+領域上に形成された可能性のあるシリコン二酸化物を全部除去するために、希釈したHFでウエハを短時間洗浄してもよい。

#### 【0075】

BiCMOSフローにおける単一ポリ・バイポーラ・トランジスタのためのエミッタベース容量を減少させるための異なる概念が、以下の特許に記述されている。S. H. ブレンゲルおよびR. H. エクランドによる特許第5,171,702号、および前記の、R. H. ヘイブマンによる米国特許第5,374,845号。

#### 【0076】

窒化物層141の付着に続き、ウエハは、フォトレジスト層142を付着し、これから形成されるNPNトランジスタのための、いわゆるE/Bマスク、またp型領域における任意の基板接触(図示されていない)のために、レジストを開くことによって、リソグラフィ的にパターン形成される。NPNトランジスタのための開口143は、窒化物141の下にフィールド酸化物81のない領域に置かれ、フィールド酸化物の端から適度に離れている。基板接触のための開口は、pウェル領域における、埋設p型領域(図示されていない)の上に置かれる。

#### 【0077】

開口における窒化物141および酸化物111層は、従来のエッティング、好ましくはドライ・エッティングにより、そして、好ましくは窒化物および酸化物が順次エッティングされる手順によって除去される。エッティングは、シリコン層41の表面が露出された時に終了する。NPNトランジスタに対して、前記の方法は、ベース領域を、フィールド酸化物の開口により画定されるより大きい領域ではなく、パターン形成により設定された領域に、より小さくする。このように、NPNトランジスタのベースを、より高い圧力がかかるかもしれないフィールド酸化物領域の端から離すことができる。適切に画定されたより小さい開口を生成するこのような方法は、コレクタ-ベース容量を減少させる。

この結果の構造が、図14に示されている。

窒化物141および酸化物111のシリコン層41へのエッティングに続き、フォト・マスク142が従来の方法により除去される。

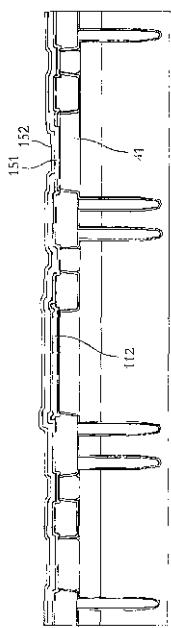

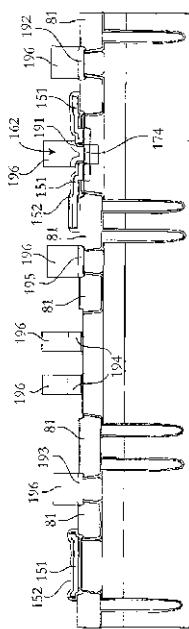

#### 【0078】

##### 15. 外因性ベース層の形成

200nmの範囲の薄いシリコン層151が次に、CVD技術を使用して構造上に付着される。図15を参照されたい。付着条件は、層151がアモルファスであるように選択されるが、微結晶あるいは多結晶シリコンを代替的に使用することもできる。この層の目的は、NPNトランジスタのための外因性ベース接触、および窒化物コンデンサの上部電極として機能することである。

#### 【0079】

10

20

30

40

50

この付着の後、イオン打ち込みが実行される。この目的は、アモルファス・シリコン層をp型に重度にドープすることである。イオン打ち込みのための選択された種類は、好ましくは、約50keVのエネルギーおよび約 $2 \times 10^{-2}$ cm<sup>-2</sup>のドーズ量におけるBF<sub>2</sub>である。ホウ素は、より低いエネルギーで代替的に打ち込みされる。エネルギーは、打ち込みされたホウ素原子が付着シリコン層151を通って到達しないように、選択される。結晶質でないシリコン層が使用された場合、打ち込みされたドーピング・プロファイルはよりよく制御される。

#### 【0080】

シリコン層151の上に、通常150nmの厚さのシリコン二酸化物層152が、PECVD技術を使用して付着される。他の型の低温酸化物、例えばLTOを、代替的に使用することもできる。PECVD技術を使用する目的は、酸化物付着の間にアモルファス・シリコンが再結晶化しないように、温度を低く保つことである。NPNトランジスタのための外因性ベース接触の形成の間、PECVDにより付着されたシリコン二酸化物層の下にBF<sub>2</sub>を打ち込みされたアモルファス・シリコン層があることの利点は、H.ノルストロムによる米国特許第6,077,752号にさらに詳しく記述されている。

この結果の構造が、図15に示されている。

#### 【0081】

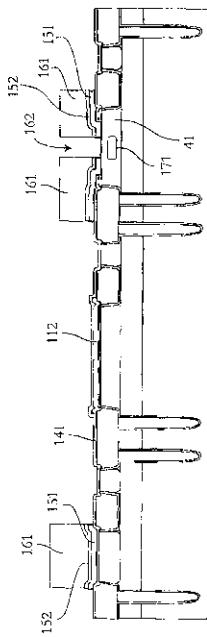

##### 16. エミッタ開口のパターン形成

次に、RFEMITマスクと呼ばれるフォト・マスク161が、構造に当てられる。図16を参照されたい。レジストは、窒化物コンデンサの上部電極、p型基板接触および、NPNトランジスタの外因性ベース領域を形成する領域を保護する。フォトレジストをマスクとして使用して、先の工程において付着されたシリコン二酸化物152およびアモルファス・シリコン151は、ここでドライ・エッチングを使用して除去される。エッチングは、シリコン窒化物層141が、開いたフィールド領域上の、コレクタ領域およびMOS素子を保護している場所で、完全に露出された時に止められる。

#### 【0082】

エッチングは、複数チャンバ・システム（クラスタ・システム）において実行されると有利である。この場合、露出したシリコンのある領域162、つまり後にNPNトランジスタの真性ベース領域として画定される領域において、シリコンが20nmオーバエッチング除去される。PMOSトランジスタの上には同様のシリコン窒化物141があり、エッチングはこの窒化物の上で止まり、窒化物はほとんどそのまま残される。

この結果の構造が、図16に示されている。

#### 【0083】

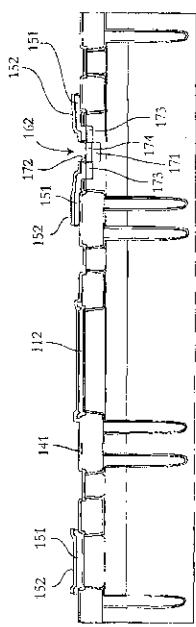

##### 17. 選択的埋込みコレクタ

次の工程は、図16および17において171で示される、NPNトランジスタのコレクタ、いわゆる2次的埋込みコレクタ（SIC）を形成する、付加的ドーピングである。この目的は、ベースの幅の広がりを最小にし、それにより、トランジスタの高周波特性を改良することである。この特定の場合において、このドーピングは、二重リン打ち込みとして実行される。第1の工程の間、 $5 \times 10^{-2}$ cm<sup>-2</sup>のリンが200keVのエネルギーにおいて打ち込みされ、第2の工程の間、 $4 \times 10^{-2}$ cm<sup>-2</sup>のリンが420keVのエネルギーにおいて打ち込みされる。これらの工程の順序は反対でもよく、正確なエネルギーおよびドーズ量は、エビの厚さ、温度駆動等の、プロセスにおける実際のプロセスパラメータに適応するよう調整されなければならないかもしれない。

#### 【0084】

工程16からのフォトレジスト161が、打ち込みがエミッタベース開口内にのみ行われるように、NPNトランジスタの一部を保護しているので、その結果、外因性ベース接触151の下においてはコレクタ・ドーピングが増加していないことに、注意されたい。これにより、NPNトランジスタの低コレクタ・ベース容量が保持される。

#### 【0085】

PMOSトランジスタは、打ち込みの間どんなフォト・マスクにも覆われず、打ち込み

10

20

30

40

50

された種類に完全に浸透され、PMOSトランジスタのためのnウェルの背景ドーピングを設定する。従って、打ち込みパラメータは、トランジスタの閾値電圧に影響を与えるが、工程11において行われた閾値電圧打ち込みドーズ量を変えることによって、補償することができる。

【0086】

打ち込みの後、レジストは従来の方法を使用して除去され、10-20nmの範囲の薄いシリコン二酸化物172が、むき出しのシリコンが露出しているウエハ表面上、つまり、真性ベース開口162(図17)において、熱的に成長される。成長は、湿った空気において、800の比較的低い温度において行われる。この工程の間、外因性ベース電極151の上の残りのPECVD付着酸化物層152は、結果的に密度が高くなる。構造の側壁上では、熱酸化物が、露出したシリコンの上に成長する。熱プロセスの間に、アモルファス・シリコン151は多結晶シリコンに変化し、同時に、先に打ち込みされたホウ素がポリシリコン内で再分布され、p型ベース接触バス173を形成する。

【0087】

18. 真性ベース形成

次の工程において、ホウ素が構造内に打ち込まれ、NPNトランジスタの真性ベース領域174を形成する。この特定の例において、約1.5E14cm<sup>-2</sup>のドーズ量のホウ素が約6keVのエネルギーにおいて打ち込まれる。先の工程において形成された薄い酸化物の厚さが変化すると、打ち込みパラメータを変更する必要があるかもしれない。打ち込みは、ベース領域におけるシリコンにのみ浸透する。他のシリコン領域は、窒化物層141によって保護されているからである。

打ち込みの後、構造は、好ましくは800の湿った空気においてさらに酸化され、シリコン/シリコン二酸化物表面におけるホウ素原子の集中を減少させる。

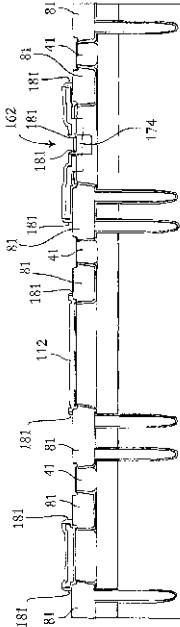

【0088】

それから、図18aを参照すると、約120nmの厚さのシリコン窒化物の層が、LPCVD技術によって適合的に付着される。窒化物層は、特別な異方性エッティングによって、NPNトランジスタの真性ベース開口162におけるように(内部スペーサ)、表面における大きな段が存在する、シリコン窒化物の側壁スペーサ181が残っているところまで、エッティングされる。このスペーサの形成の後、真性ベースの開口は、今後、エミッタ開口162と呼ばれる。最近付着された窒化物が除去されるだけでなく、フィールド81およびコレクタ接触領域41およびPMOSゲート構造112の上の、(工程14において付着された)薄い窒化物141も、このエッティングにおいて同時に除去される。

【0089】

エミッタ開口162の中央には熱酸化物が残っているが、これもまた除去される。酸化物は、ウェットあるいはドライ・エッティングによって除去してもよい。この特定の例においては、2工程ドライ・エッティングが使用される。第1のエッティング工程は、Ar/CHF<sub>3</sub>/CF<sub>4</sub>プラズマにおけるRIE(反応イオン・エッティング)を使用した酸化物除去であり、第2のエッティング工程は、先のRIEエッティングからの残留物および放射線損傷を除去するための、Ar/NF<sub>3</sub>におけるもとの場所における軽度の等方性シリコン・エッティングである。第2のエッティング工程は、約10nmのシリコンを、エミッタ開口の露出した領域から除去する。このエッティングは真性ベース・プロファイルに影響を与えるので、エッティングの深さは、製造されるNPNトランジスタの電流利得(ベータあるいはh<sub>FE</sub>)における要求によって、制御されるかもしれない。

【0090】

この第2のエッティングはまた、PMOSトランジスタ上の第1のゲート材料112として使用されたシリコンの一部も除去する。ゲート材料の最初の厚さは、PMOSトランジスタに対して何の問題も起こさないような範囲で、選択されていた。

この結果の構造が、図18aに示されている。

【0091】

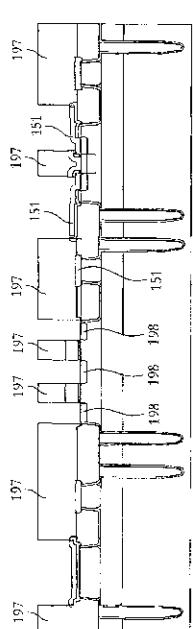

エッティングの後、通常220nmの厚さのポリシリコン層182が、LPCVD技術を

使用して付着される。図18bを参照されたい。層182は続いて、好ましくはヒ素および/あるいはリンによるイオン打ち込みによって、ドープされる。

#### 【0092】

この好ましい実施例において、ドーピングは、3つの個別の工程において実行される。

第1に、ウエハの全表面に、約50keVのエネルギーにおいて $3E15\text{cm}^{-2}$ のドーズ量のヒ素が打ち込みされる。

第2に、低値( $R_{L0}$ )および高値( $R_{H1}$ )を有する抵抗器の領域上にレジストを残すために、パターン形成されたフォトレジスト・マスク(図示されていない)を使用して、約150keVのエネルギーにおいて $1.2E16\text{cm}^{-2}$ のドーズ量のヒ素打ち込みが行われる。レジスト・マスクは、続いて、除去される。

第3に、低値抵抗器( $R_{L0}$ )のための領域および接触プラグ領域132、133、134のための領域を画定する他のマスク層183、図18cを参照、がパターン形成され、約25keVのエネルギーにおいて $4E15\text{cm}^{-2}$ のドーズ量のリンが打ち込みされる。レジスト・マスク183は、この後、除去される。

#### 【0093】

こうして得られた高値抵抗器( $R_{H1}$ )は、単位面積当たり約5000hm/sのシート抵抗率を有し、低値抵抗器( $R_{L0}$ )は、単位面積当たり約1000hm/sのシート抵抗率を有する。これらの抵抗値は、ドーズ量およびエネルギーを調整することによって、変更することができる。

#### 【0094】

重要な特徴は、エミッタ・ウィンドウと接触するポリシリコンが、異なるエネルギーにおける2回連続してヒ素打ち込みを受けることである。どんなリンもエミッタ・ポリシリコン182に入ることはできない。図18cを参照されたい。

しかし、コレクタと接触しているポリシリコンは、通常ヒ素とリンの組み合わせを使用して打ち込みされる。同じドーピング型であるが異なる拡散率を有する2つの異なるドーパント種類を使用することによって、低い抵抗率および深いコレクタ接触が達成される。

#### 【0095】

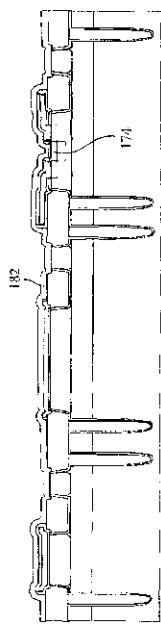

##### 19. エミッタ・エッチング

ドープされたポリシリコン182(図18cにおける)は、次に、リソグラフィおよびドライ・エッチングを使用してパターン形成される。図19aを参照されたい。この工程において、NPNトランジスタのエミッタ191およびコレクタ192への接触領域、窒化物コンデンサのより深い電極193、PMOSトランジスタのゲート194、PMOSトランジスタの基板接触195、および、低値および高値抵抗器(図19aにおいては明示的には図示されていない)、が画定される。図示されているPMOS素子は、(準ラテラルPNP素子を製造するために)2つのPMOSトランジスタを含み、従って2つのゲート領域194を有することに留意されたい。

#### 【0096】

ポリシリコンがエミッタ開口162内で単結晶シリコン表面と直接接触している場所において、ポリシリコンは、後のプロセス工程において、真性ベース領域174におけるエミッタのドライブ・インの間、ドーピング源として機能する。EMIポリ・マスクと呼ばれるフォトレジスト・マスク196を使用して、ドープされたポリシリコンのある部分が、電界酸化物領域81が露出するまで除去される。このエッチングは、 $\text{Cl}_2/\text{HBr}/\text{O}_2$ プラズマを使用したRIEを使用して行われることが好ましい。

この結果の構造が、図19aに示されている。

このエッチングの後、レジストは従来の方法を使用して除去される。

#### 【0097】

p型ポリシリコン層151の上部の酸化物層152を、ここで除去しなければならない(図示されていない)。このことは、ドライ・エッチングによって、ウエハ全体にわたって、あるいは、BASE OXREMマスクと呼ばれるフォト・マスク197を使用して局所的に、行うことができる。図19bを参照されたい。フォト・マスクを使用する方法

10

20

30

40

50

は、本実施例においては好ましい方法である。フォト・マスクは、開口が p + ポリシリコン層の上に形成されるように、パターン形成される。それから、酸化物は、Ar / CHF<sub>3</sub> / CF<sub>4</sub> プラズマを使用した RIE を使用して除去される。エッティングは、ポリシリコンがレジスト開口において露出した時に止められる。全体的エッティングの代わりにフォト・マスクを使用することの利点は、電界酸化物領域 81 がフォトレジストによって保護され、侵食を免れることである。

#### 【0098】

エッティングの後、レジストがまだ残存しているので、PMOS のそれぞれのソースおよびドレイン領域 198 にドープするために、付加的なホウ素打ち込みが行われる。図 19b を参照されたい。バイポーラ・トランジスタの外因性ベース 151、コンデンサの上部プレート 151、および p 型基板接触（図示されていない）のためのポリシリコン、が同時に打ち込みを受ける。エッティングおよび打ち込みが完了すると、フォトレジストは除去される。

#### 【0099】

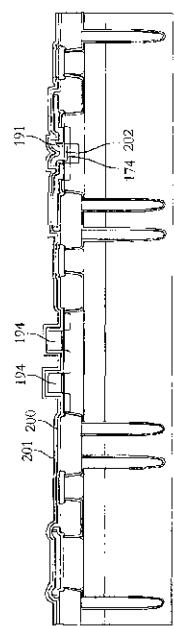

##### 20. エミッタ活性およびドライブ・イン

約 30 nm の薄い酸化物層 200 が、ウエハ上に付着される。TEOS が使用されることが好ましいが、LTO あるいは PECVD のような他の酸化物を代替的に使用することもできる。

酸化物 200 の上に、約 100 nm の厚さのシリコン窒化物層 201 が、LPCVD 技術を使用して適合的に付着される。その結果の構造が、図 20a に示されている。

#### 【0100】

付着の後に、先に打ち込みされたドーパントを活性化しドライブ・インするために、ウエハは高温にさらされる。

好ましい実施例において、熱プロセスは、2 工程手順において実行される。ウエハは、第 1 に、約 30 分の間、850 の電気炉において焼きなまされる。この目的は、打ち込みを受けた層において、ドーパントをより均一に再分布することである。この第 1 の工程は、実際、本発明のプロセスフローにおいては省略することができる。半導体ウエハは、通常約 790 において 3 時間以上行われる、シリコン酸化物 / 窒化物 200 / 201 の付着の間に、既に十分な熱プロセスを受けているからである。

#### 【0101】

第 2 に、RTA（高速熱焼きなまし）装置を使用した、約 1075 における 16 秒間の、窒素における別の熱プロセスが行われる。この焼きなましの目的は、打ち込み種 (implanted species) を電気的に活性化し、NPN トランジスタのエミッタベース接合の最終的ドーピング・プロファイル、および、PMOS 素子のプロファイルを設定することである。

#### 【0102】

先に付着されたシリコン酸化物 200 およびシリコン窒化物 201 層は、ウエハ上に残っていることに注意されたい。これらの層の目的は、熱プロセスの間に打ち込みされたドーパントが周囲に拡散して出ていくことを、止めることである。

#### 【0103】

熱プロセスの間に、上部 n 多層 191 に打ち込みされたヒ素は、拡散により真性ベースに浸透し、エミッタベース接合を形成する。本実施例に対しては、エミッタ 202 の深さは約 50 nm であり、エミッタの下に残っている真性ベース 174 の厚さは約 50 nm である。エミッタ開口内の、単結晶シリコン層の表面と多結晶層との間の接合におけるヒ素の濃度は、通常、5E20 原子 / cm<sup>-3</sup> である。真性ベース内のエミッタ - ベース接合における、対応するホウ素の濃度は、通常、1E18 原子 / cm<sup>-3</sup> である。

#### 【0104】

同時に、外因性ベース接触多層に打ち込みされたホウ素は、拡散して真性ベースに結合する。ここに記述される製造プロセスに対して、外因性ベースの深さは約 200 nm であり、外因性ベース・ポリシリコンと単結晶シリコンとの間のインターフェースにおける、対

10

20

30

40

50

応するホウ素の濃度は、通常、 $1 \times 10^{20}$  原子 /  $\text{cm}^{-3}$  である。この高度にドープされた p 型領域は、外因性ベースと呼ばれる。

p 型ポリシリコン層からのホウ素の外方拡散により、基板接触が対応する方法で形成される。

#### 【 0 1 0 5 】

PMOSトランジスタ構造のゲート 194 は、n+多層（図 18b における 182）つまりエミッタ・ポリ、および、ドープされていないポリシリコンである第 1 のゲート材料（図 11 における 112）の残留物から成る。熱プロセスの間、n+型ドーパントは、拡散によりゲート層内において再分布され、ゲートはここで n+ 材料で均一的にドープされ、従って、PMOSトランジスタのための n+ ゲート 194 が形成される。

PMOSトランジスタのソース／ドレイン領域もまた、熱プロセスによって活性化される。

この結果の構造が、図 20a に示されている。

#### 【 0 1 0 6 】

焼きなましの後、抵抗器は、フォトレジストの保護層が抵抗器本体（図示されていない）の上にのみ残るよう、リソグラフィ的に画定される。抵抗器の終端部分は、露出される。パターン形成の後、シリコン窒化物層 201 およびシリコン酸化物層 200 は、フォトレジスト層によって覆われていない表面部分において、エッティングによって除去される。スペーサ 203 が N+ 型のポリシリコン層 194 の端に沿って形成されるように、エッティングは異方性である。

#### 【 0 1 0 7 】

薄いシリコン酸化物層の上のシリコン窒化物のいわゆるスペーサの製造に関してここに記述されるプロセスは、かなりの部分、H. ノルストロムその他のによる米国特許第 4,740,484 号に記述されている製造プロセスに類似している。それから、フォトレジスト層は除去される。

#### 【 0 1 0 8 】

フォトレジスト層を除去した後に、N+ 型のポリシリコン層 194 および P+ 型のポリシリコン層 151 には、これから製造される構成要素の異なる電極領域に対する導体の抵抗を減少させるために、薄いシリサイド層を与えることができる。これらの導体は、それから、このようなシリサイド層によって分路される。このシリサイド層は、例えば PtSi、CoSi<sub>2</sub> あるいは TiSi<sub>2</sub> によって構成することができる。好ましい実施例において、二珪化チタン TiSi<sub>2</sub> が使用され、これは、いわゆる“自己整合方法”を使用して、露出したシリコン表面の上に形成される。抵抗器本体は露出せず、シリコン窒化物層 201 の残っている部分によって保護されているので、そこではシリサイドは得られない。

#### 【 0 1 0 9 】

このような自己整合シリサイド化（“サリサイド”）において、ウエハの表面上に、薄い金属層、この場合約 50 nm の厚さのチタン層が、好ましくはスパッタリングによって付着される。ブライトンその他のによる米国特許第 4,789,995 号、および、シバタによる米国特許第 4,622,735 号を参照されたい。金属層はそこで、RTA 装置における窒素ガス内で、約 715 °C の高温において、露出したシリコンと約 20 秒の短時間反応させられる。ある場合には、酸素ガスとアンモニア・ガスの混合を使用することもできる。その後、シリコンと反応していない、つまり金属付着に先立ちシリコン表面が露出していないかった部分におけるチタンが、ウェットな化学的方法によって溶解される。このエッティング工程は、反応していないチタンを選択的に除去し、チタン・シリサイド自身にはわずかしか影響を与えない。ウェットな化学的エッティングプロセスの後に、プレートは、約 875 °C において約 30 秒の間焼きなましされ、低抵抗形式の二珪化チタンが形成される。このように生成されたシリサイド層は、単位面積当たり約 2 - 50 hms の表面抵抗を有し、プレートの、先に露出されたシリコン表面上にのみ存在する。つまり、これらの表面と自己整合している。

#### 【 0 1 1 0 】

10

20

30

40

50

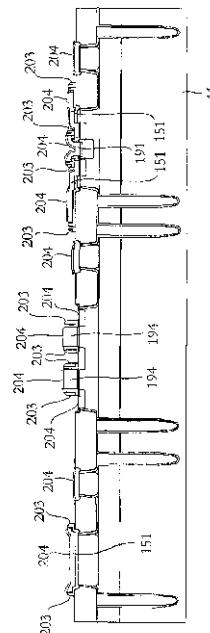

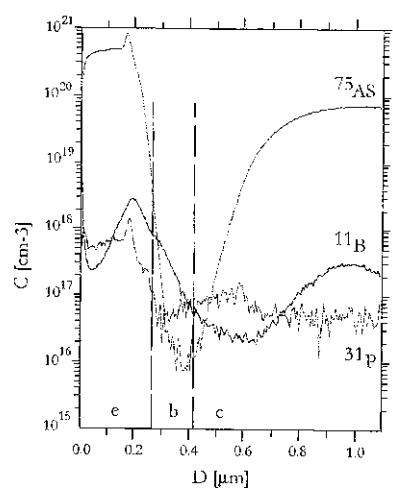

外部スペース 203 の形成およびサリサイド（自己整合シリサイド）204 の形成の後の構造が、図 20b に示され、図 20c においては、前記のプロセスフローにおいて製造された NPN トランジスタに対する SIMS プロファイルが示されている。

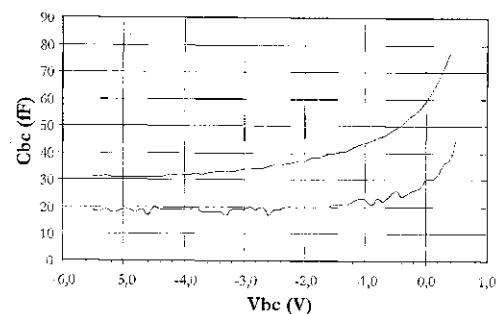

図 20d は、ベース - コレクタ電圧の作用としての、NPN トランジスタのベース - コレクタ容量を示している。下部曲線は、ここに記述される本発明の製造プロセスに従って製造された NPN に対する容量を示し、上部曲線は、より厚いエピおよびより高度なウェル・ドーピングを使用した従来技術のプロセスにより製造された NPN トランジスタに対する容量を示している。（0 V Vbc における Cbc によって表わされる）合計容量値が得られ、全範囲において変化がより少なくなる。本発明により製造されたトランジスタは、約 1V のバイアス電圧において既に完全に空乏することに、注意されたい。

ヨハンソンおよびアルンボルグによる米国特許第 6,198,156 号に記述されるように、逆行プロファイルを慎重に調整することにより、トランジスタの線形性をさらに高めることができる。

#### 【0111】

##### 21. マスク設計、第 1 の金属層への接触ホール

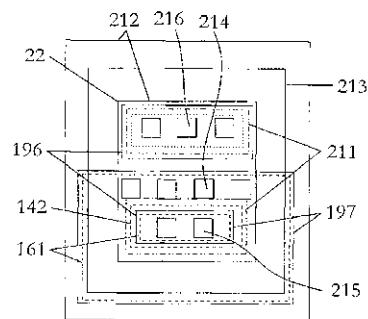

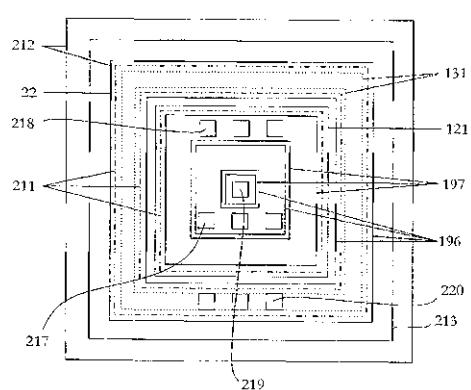

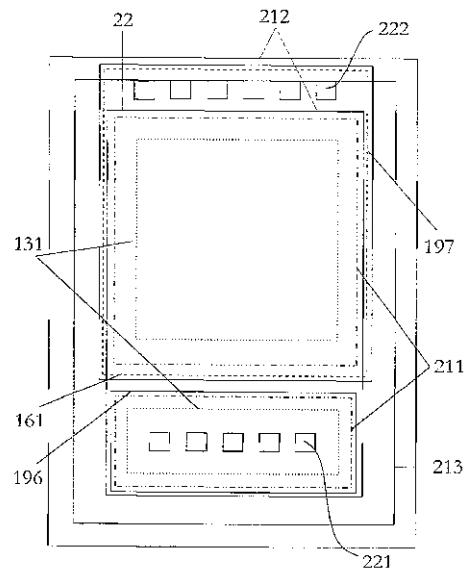

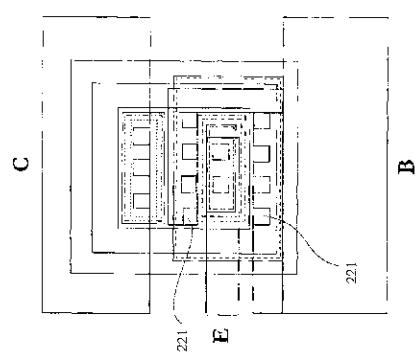

図 21a - c は、前記段落において説明した、3 つの主要な素子（NPN トランジスタ、準ラテラル PNP（つまり、PMOS 素子）および窒化物コンデンサ）のマスク設計図を示している。第 1 の金属層に対する（格子縞にパターン形成された）接触ホールも、示されている。

#### 【0112】

図 21a においては、NPN トランジスタのためのマスクが示され、22 は SUB マスクであり、211 は STI マスク（段落 5 参照）であり、212 は深い溝マスク（段落 6 参照）であり、213 は p ウェル・マスク（段落 9 参照）であり、142 は E/B マスクであり、161 は REFEMIT マスクであり、196 は EMIPOLY マスクであり、そして、197 は BASE OXREM マスクである。

さらに、接触ホールは、ベース 214 に対して、エミッタ 215 に対して、そしてコレクタ 216 に対してそれぞれ図示されている。

#### 【0113】

図 21b においては、準ラテラル PNP トランジスタのためのマスクが示され、22 は SUB マスクであり、211 は STI マスク（段落 5 参照）であり、212 は深い溝マスク（段落 6 参照）であり、213 は p ウェル・マスク（段落 9 参照）であり、121 は MOSBLK マスクであり、131 は DNCAP マスクであり、196 は EMIPOLY マスクであり、そして、197 は BASE OXREM マスクである。この構成要素の設計は、断面図とは異なり、基板接触が環状型に形成されていることに注意されたい。

さらに、接触ホールは、ゲート 217（接地）に対して、ソース 218（コレクタ）およびドレイン 219（エミッタ）に対して、そして基板接触 220（ベース）に対してそれぞれ図示されている。

#### 【0114】

図 21c においては、窒化物コンデンサのためのマスクが示され、22 は SUB マスクであり、211 は STI マスク（段落 5 参照）であり、212 は深い溝マスク（段落 6 参照）であり、213 は p ウェル・マスク（段落 9 参照）であり、131 は DNCAP マスクであり、161 は REFEMIT マスクであり、196 は EMIPOLY マスクであり、そして、197 は BASE OXREM マスクである。

さらに、接触ホールは、上部 222 および下部 221 電極に対して図示されている。

#### 【0115】

##### 22. 第 1 の金属層への接続

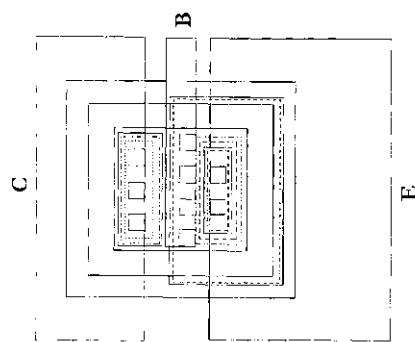

図 22a - b は、トランジスタを第 1 の金属層に接続する時の、NPN トランジスタの付加的特徴を示している。

（最良の周波数性能に対応する）最も低いベース抵抗を得るために、ベース接続 221 は、図 22a に示されるように、エミッタ E の両側に置かれる。厳密な設計規則のために

10

20

30

40

50

、このことは、トランジスタの大きさを変えることなく達成することができる（このことは、従来技術のプロセス方法においては、通常可能ではない）。

#### 【0116】

しかし、1つの回路設計におけるいくつかのトランジスタは、高電流を出力するためには使用することができる。図22aにおける設計は、その場合、エミッタEに接触している金属の幅（エミッタ接続における電流密度）によって制限されるかもしれない。外因性ベースは、エミッタを完全に囲み、ベース抵抗をさらに低くするために $TiSi_2$ によって覆われているので、金属接続は図22bに示されるように置かれ、ベース抵抗はほんの少ししか増加しない。

さらに、同じトランジスタ設計を、二重および単一のベース接触のために使用することができる（接触ホールおよび金属層を異なるように生成しなければならないだけである）。

#### 【0117】

プロセスは続いて、国際特許出願公開第WO 9903151号（発明者 H. ノルストロム、S. ナイグレンおよびO. タイルステッド）に記述されるプロセスフローに実質的に従う。

このプロセスにおいてN MOS素子が製造される場合、通常、4つのさらなるプロセス工程を追加しなければならない：N MOSゲート領域のマスキングおよびイオン打ち込み、および、N MOSソースおよびドレイン領域のマスキングおよびイオン打ち込み）。

さらに、米国特許第6,100,133号（発明者 H. ノルストロムおよびS. ナイグレン）として公開されている国際特許出願において記述されるように、MIMコンデンサをフローに追加することができる。

#### 【0118】

本発明は様々に変更することができることは、明らかであろう。このような変更は、本発明の範囲からの逸脱とみなされるべきではない。このようなすべての修正は、この分野の技術者には明らかなように、付随する請求項の範囲内に含まれるよう意図されている。

#### 【図面の簡単な説明】

#### 【0119】

【図1】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図2】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図3】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図4a】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図4b】本発明の好ましい実施例により製造された埋込みコレクタ構造上のnウェルのドーピング・プロファイルを示すSIMS（2次イオン質量分折計）図である。

【図5a】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図5b】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図6】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図7】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図8】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図9】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

10

20

30

40

50

【図10】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図11】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図12】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図13】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図14】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図15】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図16】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図17】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図18a】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図18b】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図18c】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図19a】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図19b】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図20a】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図20b】本発明の好ましい実施例によるプロセスの間の、半導体構造の一部分の高倍率拡大断面図である。

【図20c】本発明の好ましい実施例により製造されたNPNトランジスタのドーピング・プロファイルを示すSIMS(2次イオン質量分折計)図である。

【図20d】本発明の製造工程により製造された(下の曲線)および従来技術の製造工程により製造された(上の曲線)NPNトランジスタに対するベース-コレクタ・バイアス電圧の関数としてのベース-コレクタ容量を示す図である。

【図21a】本発明により製造された、主要構成要素の構成要素領域への最も重要なマスク設計を示す図である。

【図21b】本発明により製造された、主要構成要素の構成要素領域への最も重要なマスク設計を示す図である。

【図21c】本発明により製造された、主要構成要素の構成要素領域への最も重要なマスク設計を示す図である。

【図22a】本発明により製造された、主要構成要素の構成要素領域への電気的接続を示す図である。

【図22b】本発明により製造された、主要構成要素の構成要素領域への電気的接続を示す図である。

10

20

30

40

【 図 1 】

Fig. 1

【 図 2 】

Fig. 2

【図3】

Fig. 3

【 図 4 a 】

Fig. 4a

【図 4 b】

Fig. 4b

【図 5 a】

Fig. 5a

【図 5 b】

Fig. 5b

【図 6】

Fig. 6

【 四 7 】

Fig. 7

【 図 8 】

Fig. 8

【図9】

Eig 9

【 図 1 0 】

Fig. 10

【図 1 1】

Fig. 11

【図 1 2】

Fig. 12

【図 1 3】

Fig. 13

【図 1 4】

Fig. 14

【図15】

Fig. 15

【図16】

Fig. 16

【図17】

Fig. 17

【図18a】

Fig. 18a

【図 18 b】

Fig. 18b

【図 18 c】

Fig. 18c

【図 19 a】

Fig. 19a

【図 19 b】

Fig. 19b

【図20a】

Fig. 20a

【 図 2 0 b 】

Fig. 20b

【図20c】

Fig. 20c

【 図 2 0 d 】

Fig. 20d

【図21a】

Fig. 21a

【図 2 1 b】

Fig. 21b

【図 2 1 c】

Fig. 21c

【図 2 2 a】

Fig. 22a

【図 2 2 b】

Fig. 22b

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/SE 02/00838

## A. CLASSIFICATION OF SUBJECT MATTER

**IPC7: H01L 21/8222, H01L 29/732**

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

**IPC7: H01L**

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

**SE,DK,FI,NO classes as above**

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

**EPO-INTERNAL, WPI DATA, PAJ**

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                            | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 6177717 B1 (ALAIN CHANTRE ET AL),<br>23 January 2001 (23.01.01), column 4,<br>line 47 - column 7, line 45, figures 1-6                     | 25, 31                |

| A         | ---                                                                                                                                           | 26-30, 32-36          |

| A         | EP 1094514 A2 (NEC CORPORATION), 25 April 2001<br>(25.04.01), column 3, line 49 - column 4, line 30;<br>column 8, line 31 - column 10, line 4 | 1-24                  |

| A         | US 6027962 A (TAKAYUKI IGARASHI ET AL),<br>22 February 2000 (22.02.00), column 11,<br>line 30 - column 17, line 44                            | 1-24                  |

|           | ---                                                                                                                                           |                       |

Further documents are listed in the continuation of Box C. See patent family annex.

\* Special categories of cited documents:

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier application or patent but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance: the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance: the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&amp;" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

**10 Sept 2002****12 -09- 2002**Name and mailing address of the ISA/

Swedish Patent Office

Box 5055, S-102 42 STOCKHOLM

Facsimile No. + 46 8 666 02 86

Authorized officer

**Stig Edhborg/MN**

Telephone No. + 46 8 782 25 00

## INTERNATIONAL SEARCH REPORT

|                                                  |

|--------------------------------------------------|

| International application No.<br>PCT/SE 02/00838 |

|--------------------------------------------------|

## C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                               | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | PATENT ABSTRACTS OF JAPAN<br>Vol. 1996, no. 4,<br>30 April 1996 (1996-04-30)<br>& JP 07 335774 A (SONY CORP),<br>22 December 1995 (1995-12-22)<br>abstract<br>-- | 1-24                  |

| A         | US 5266504 A (JEFFREY L. BLOUSE ET AL),<br>30 November 1993 (30.11.93), see whole document<br>--                                                                 | 25-36                 |

| A         | US 5731623 A (KAZUNARI ISHIMARU), 24 March 1998<br>(24.03.98), see whole document<br>--                                                                          | 25-36                 |

| A         | US 5960272 A (KAZUNARI ISHIMARU), 28 Sept 1999<br>(28.09.99), see whole document<br>--                                                                           | 25-36                 |

| A         | US 6043130 A (HAYDN JAMES GREGORY), 28 March 2000<br>(28.03.00), see whole document<br>--<br>-----                                                               | 25-36                 |

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/SE02/00838

## Box I Observations where certain claims were found unsearchable (Continuation of item 1 of first sheet)

This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.:

because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.:

because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

3.  Claims Nos.:

because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

## Box II Observations where unity of invention is lacking (Continuation of item 2 of first sheet)

This International Searching Authority found multiple inventions in this international application, as follows:

**see next page**

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fee, this Authority did not invite payment of any additional fee.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

## Remark on Protest

The additional search fees were accompanied by the applicant's protest.

No protest accompanied the payment of additional search fees.

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/SE02/00838

## Group I (claims 1-24, 34-36):

A method in the production of an integrated circuit, including at least one bipolar transistor and at least one MOS device where an electrically insulating layer is formed to define a base region and protect the gate region during subsequent manufacturing steps.

## Group II (claims 25-33):

In the production of an integrated circuit a method for forming a shallow trench for isolation of a vertical bipolar transistor in said circuit, said trench extending vertically from the upper surface of the substrate and down into the substrate to a depth where the buried collector region is located, and an integrated circuit so produced.

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No.

PCT/SE 02/00838

| Patent document cited in search report | Publication date | Patent family member(s) |          |  | Publication date |

|----------------------------------------|------------------|-------------------------|----------|--|------------------|

| US 6177717 B1                          | 23/01/01         | EP 0962966 A            | 08/12/99 |  |                  |

|                                        |                  | FR 2779572 A            | 10/12/99 |  |                  |

|                                        |                  | JP 2000031155 A         | 28/01/00 |  |                  |

| EP 1094514 A2                          | 25/04/01         | JP 2001118858 A         | 27/04/01 |  |                  |

| US 6027962 A                           | 22/02/00         | JP 11008326 A           | 12/01/99 |  |                  |

| US 5266504 A                           | 30/11/93         | NONE                    |          |  |                  |

| US 5731623 A                           | 24/03/98         | EP 0647968 A            | 12/04/95 |  |                  |

|                                        |                  | JP 7106412 A            | 21/04/95 |  |                  |

|                                        |                  | KR 169278 B             | 01/02/99 |  |                  |

| US 5960272 A                           | 28/09/99         | JP 9115998 A            | 02/05/97 |  |                  |

| US 6043130 A                           | 28/03/00         | NONE                    |          |  |                  |

## フロントページの続き

|                          |              |            |

|--------------------------|--------------|------------|

| (51)Int.Cl. <sup>7</sup> | F I          | テーマコード(参考) |

| H 01 L 27/04             | H 01 L 27/06 | 1 0 1 D    |

| H 01 L 27/06             | H 01 L 29/72 | P          |

| H 01 L 29/732            | H 01 L 21/76 | L          |

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,CH,CY,DE,DK,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,OM,PH,P,L,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VN,YU,ZA,ZM,ZW

(72)発明者 ヨハンソン、テッド

スウェーデン国 デュルスホルム、スヴェアヴェーゲン 6 6

(72)発明者 ノルストレム、ハンス

スウェーデン国 ソルナ、モールドスティゲン 3

(72)発明者 アルゴトソン、パトリク

スウェーデン国 ストックホルム、スリプガタン 1 6

F ターム(参考) 5F003 AP05 BA13 BA25 BA97 BC02 BC05 BC08 BG03 BJ03 BJ15

BJ18 BJ20 BN01 BP02 BP12 BP94

5F032 AA13 AA35 AA44 AA67 BA01 CA01 CA03 CA14 CA17 CA18

DA23

5F038 AC05 AC15 AR09 DF12 EZ12 EZ13 EZ14 EZ15 EZ16 EZ17

EZ20

5F048 AA10 AC05 AC10 BA05 BA12 BB06 BB08 BB12 BB14 BD04

BF06 BF16 BG13 BG14 CA03 CA04 CA07 DA25 DA27 DA30

5F082 AA25 BA04 BA05 BA11 BA22 BA23 BA27 BA32 BA47 BC01

BC04 BC09 BC13 BC15 CA08 DA03 DA10 EA08 EA13 EA15

GA02