(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-218611

(P2008-218611A)

(43) 公開日 平成20年9月18日(2008.9.18)

(51) Int. Cl.

F

### テーマコード（参考）

HO 1 L 27/04 (2006.01)

HO 1 L 29/78 (2006.01)

HO 1 L 21/822 (2006.01)

HO 1 L 29/739 (2006.01)

HO 1 L 27/06 (2006.01)

HO 1 L 29/78

HO 1 L 27/04

HO 1 L 29/78

HO 1 L 29/78

HO 1 L 27/04

6570

H

653A

6552

A

5F038

5F048

5J055

審査請求 未請求 請求項の数 4 O.L. (全 14 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2007-52411 (P2007-52411)

平成19年3月2日 (2007.3.2)

(71) 出願人 000003207

トヨタ自動車株式会社

愛知県豊田市トヨタ町1番地

(74) 代理人 110000110

特許業務法人快友國際特許事務所

(72) 発明者 加納 教夫

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

|          |       |      |      |      |      |      |

|----------|-------|------|------|------|------|------|

| Fターム(参考) | 5F038 | AV03 | BB05 | BH02 | BH06 | BH16 |

|          |       | CA02 | CA08 | CD16 | EZ20 |      |

|          | 5F048 | AB07 | AB10 | AC08 | AC10 | BB20 |

|          |       | BC03 | BC18 | BD07 | CC01 | CC18 |

|          | 5J055 | AX15 | BX16 | CX07 | DX09 | EX12 |

|          |       | EY01 | FX05 | FX12 | GX01 |      |

(54) 【発明の名称】 半導体装置

(57) 【要約】

【課題】 半導体装置の温度変化に対応して半導体装置のゲート電極に印加される電圧が自律的に調整される半導体装置を提供する。

【解決手段】 半導体装置 6 は、バイポーラトランジスタ 30 と、半導体装置 6 外のゲート駆動回路 2 に接続されるゲート端子 4 と、半導体装置 6 外の定電圧点 20 に接続される接続端子 16 と、ゲート端子 4 とトランジスタ 30 内のゲート電極 12 を接続している第 1 内部配線 10 と、ゲート電極 12 と接続端子 16 を接続している第 2 内部配線 14 を備えており、第 1 内部配線 10 に正の抵抗温度係数を有する第 1 ゲート抵抗 8 が挿入されている。半導体装置 6 の温度が上昇すると、第 1 ゲート抵抗 8 の抵抗値が上昇し、ゲート電極 12 に印加される印加電圧が下降する。半導体装置 6 の通電電力量と発熱量が抑制され、半導体装置 6 の過熱が避けられる。

### 【選択図】 図 1

## 【特許請求の範囲】

## 【請求項 1】

過熱防止機能を有する半導体装置であり、

第1導電型の第1半導体領域と、

第1導電型の第3半導体領域と、

前記第1半導体領域と前記第3半導体領域を分離している第2導電型の第2半導体領域と、

前記第1半導体領域から前記第2半導体領域を経て前記第3半導体領域に達する範囲に存在している半導体に絶縁膜を介して対向しているゲート電極と、

半導体装置外のゲート駆動回路に接続されるゲート端子と、

半導体装置外の定電圧点に接続される接続端子と、

前記ゲート端子と前記ゲート電極を接続している第1内部配線と、

前記ゲート電極と前記接続端子を接続している第2内部配線を備えており、

前記第1内部配線に正の抵抗温度係数を有する第1ゲート抵抗が挿入されているか、あるいは、前記第2内部配線に負の抵抗温度係数を有する第2ゲート抵抗が挿入されていることを特徴とする半導体装置。

## 【請求項 2】

請求項1に記載の半導体装置の複数個が集積されている半導体チップであり、

複数個の半導体装置の各々が、共通ゲート端子と共通接続端子に接続されていることを特徴とする半導体チップ。

## 【請求項 3】

請求項2に記載の半導体チップであり、

第1ゲート抵抗の各々、および／または、第2ゲート抵抗の各々が、抵抗値を調整可能な抵抗パターンで形成されていることを特徴とする半導体チップ。

## 【請求項 4】

電界効果型トランジスタと、

一定電圧に調整されているオン電圧とオフ電圧の間で変化する電圧を出力するゲート駆動回路と、

前記電界効果型トランジスタのゲート電極と前記ゲート駆動回路の間に挿入されており、前記電界効果型トランジスタに熱的に接合されているとともに、正の抵抗温度係数を有するゲート抵抗と、

前記電界効果型トランジスタのゲート電極と定電圧点の間に挿入されている一定の抵抗値を有する抵抗を備えていることを特徴とする電界効果型トランジスタの過熱防止機能を有する回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体装置の温度変化に対応して半導体装置のゲート電極に印加する電圧が自律的に調整される半導体装置に関する。

## 【背景技術】

## 【0002】

IGBT (Insulated Gate Bipolar Transistor) やMOSFET (Metal Oxide Silicon Field Effect Transistor) などの半導体装置の開発が進められている。これら半導体装置では、ゲート電極に印加する電圧を切り換えることによって、半導体装置を導通状態と非導通状態の間で切り換える。

この種の半導体装置の小型化が進んでおり、半導体装置を高密度に集積して利用することが多くなっている。あるいは、この種の半導体装置でオン・オフする電力量が大きくなっている。このために、この種の半導体装置が過熱する可能性が高まっている。

## 【0003】

10

20

30

40

50

半導体装置が過熱することを防止するために、半導体装置の導通状態と非導通状態を切り換える回路（ゲート駆動回路）に保護回路を組み込む技術が提案されており、特許文献1に開示されている。この技術では、半導体装置の温度を検出する温度検出回路と、温度検出回路からの出力信号に基づいてゲート駆動回路の出力電圧を増減調整する回路を備えている。ゲート駆動回路は、半導体装置を導通状態とするゲートオン電圧と半導体装置を非導通状態とするゲートオフ電圧の間で変化するパルス電圧を出力する。特許文献1に開示されているゲート駆動回路は、検出温度が上昇するとゲート駆動回路が出力するゲートオン電圧を低下させる。この結果、半導体装置の通電電力量が抑制され、半導体装置の発熱量が抑制され、半導体装置の過熱が避けられる。

【0004】

10

【特許文献1】特開2000-124781号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

従来の技術では、温度検出回路と、その検出結果に基づいてゲート駆動回路が出力するゲートオン電圧を増減調整する回路を別々に用意する必要がある。

本発明は、温度検出回路と、ゲート駆動回路が出力するゲートオン電圧を調整する回路を別々に用意する必要がなく、半導体装置の温度が上昇したことを検知する回路が、ゲート電極に印加するゲートオン電圧を調整する回路を兼用する技術を提案する。

【課題を解決するための手段】

20

【0006】

従来の技術では、ゲート電極とゲート端子を内部配線で接続しておき、ゲート駆動回路の出力電圧をゲート端子に入力する。この技術では、過渡的な状態を除くと、ゲート駆動回路が出力するゲートオン電圧と、ゲート端子に入力されるゲートオン電圧と、ゲート電極に印加されるゲートオン電圧が等しい。そのため、ゲート電極に印加するゲートオン電圧を低下させることによって半導体装置の通電電力量を抑制して発熱量を抑制するためには、ゲート駆動回路が出力するゲートオン電圧自体を増減調整する必要があり、ゲート駆動回路が出力するゲートオン電圧を調整する回路が必要とされていた。

【0007】

30

本発明では、ゲート駆動回路が出力するゲートオン電圧を調整する回路を利用しない。一定のゲートオン電圧を出力するゲート駆動回路であれば足りる。

本発明の半導体装置は、少なくとも、第1半導体領域と、第2半導体領域と、第3半導体領域と、ゲート電極を備えている。第1半導体領域は、第1導電型である。第2半導体領域は、第1半導体領域と第3半導体領域を分離しており、第2導電型である。第3半導体領域は、第1導電型である。ゲート電極は、第1半導体領域から第2半導体領域を経て第3半導体領域に達する範囲に存在している半導体に絶縁膜を介して対向している。

本発明の半導体装置は、さらに、ゲート端子と、接続端子と、第1内部配線と、第2内部配線を備えている。ゲート端子は、半導体装置外に存在するゲート駆動回路に接続される。接続端子は、半導体装置外にあって一定の電圧に維持されている点（定電圧点）に接続される。第1内部配線は、ゲート端子とゲート電極を接続している。第2内部配線は、ゲート電極と接続端子を接続している。本発明の半導体装置では、第1内部配線に正の抵抗温度係数を有する第1ゲート抵抗が挿入されている。あるいは、第2内部配線に負の抵抗温度係数を有する第2ゲート抵抗が挿入されている。あるいは、第1内部配線に正の抵抗温度係数を有する第1ゲート抵抗が挿入されるとともに、第2内部配線に負の抵抗温度係数を有する第2ゲート抵抗が挿入されている。

【0008】

40

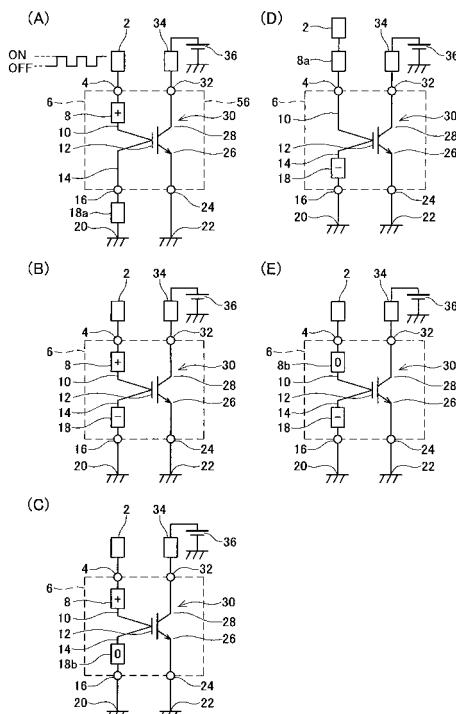

図1は、本発明の半導体装置6とそれを利用する場合の回路構成を例示している。図1において、参照番号30はトランジスタであり、直流電源36と接地点22の間に、負荷34とともに直列に接続されている。トランジスタ30が導通状態となると、負荷34に電流が流れる。トランジスタ30が非導通状態となると、負荷34に電流が流れない。ト

50

ランジスタ30は、負荷34の通電電流をオン・オフ制御する。負荷34を流れる電流はトランジスタ30にも流れる。トランジスタ30は発熱し、過熱する可能性にさらされている。

【0009】

参照番号2はゲート駆動回路であり、(A)に示すように、トランジスタ30を導通状態とするゲートオン電圧と、トランジスタ30を非導通状態とするゲートオフ電圧の間で変化するパルス電圧を出力する。ゲート駆動回路2が出力するゲートオン電圧は一定であって、増減調整されることはない。

参照番号4は、ゲート駆動回路2に接続されるゲート端子であり、第1内部配線10によってトランジスタ30のゲート電極12に接続されている。参照番号16は、一定電圧に維持されている点20に接続される接続端子であり、第2内部配線14によってトランジスタ30のゲート電極12に接続されている。図1では、定電圧点20が接地されている状態が図示されているが、一定電圧に維持されればよく、必ずしも接地されている必要はない。

【0010】

本発明では、第1内部配線10に正の抵抗温度係数を有する第1ゲート抵抗8が挿入されている場合、第2内部配線14に第2ゲート抵抗が挿入されていなくてもよいし、第2内部配線14に第2ゲート抵抗が挿入されていてもよい。

(A)に示すように、第2内部配線14に第2ゲート抵抗が挿入されていない場合、接続端子16と定電圧点20の間に第2ゲート抵抗18aを挿入すればよい。この場合、第2ゲート抵抗18aの抵抗温度係数は制約されない。第2内部配線14に第2ゲート抵抗が挿入されている場合、(B)に示すように、第2ゲート抵抗18が、負の抵抗温度係数を有するか、あるいは(C)に示すように、第2ゲート抵抗18bが、第1ゲート抵抗8の抵抗温度係数に比して無視できる程度に小さな抵抗温度係数を持っていればよい。図1において、+は正の抵抗温度係数を有することを示し、-は負の抵抗温度係数を有することを示し、0は抵抗温度係数の絶対値が小さいことを示している。

第2内部配線14に負の抵抗温度係数を有する第2ゲート抵抗18が挿入されている場合、第1内部配線10に第1ゲート抵抗が挿入されていなくてもよいし、第1内部配線10に第1ゲート抵抗が挿入されていてもよい。

(D)に示すように、第1内部配線10に第1ゲート抵抗が挿入されていない場合、ゲート駆動回路2とゲート端子4の間に第1ゲート抵抗8aを挿入すればよい。この場合、第1ゲート抵抗8aの抵抗温度係数は制約されない。第1内部配線14に第1ゲート抵抗が挿入されている場合、(B)に示すように、第1ゲート抵抗8が、正の抵抗温度係数を有するか、あるいは(E)に示すように、第1ゲート抵抗8bが、第2ゲート抵抗18の抵抗温度係数の絶対値に比して無視できる程度に小さな抵抗温度係数を持っていればよい。

【0011】

本発明の場合、ゲート駆動回路2が出力するゲートオン電圧と、ゲート端子4に入力されるゲートオン電圧と、ゲート電極12に印加されるゲートオン電圧が必ずしも等しくならない。そこで、以下では、ゲート駆動回路2が出力するゲートオン電圧を「出力電圧」といい、ゲート端子4に入力されるゲートオン電圧を「入力電圧」といい、ゲート電極12に実際に印加されるゲートオン電圧を「印加電圧」という。

【0012】

最初に、図1(A)～(C)に示すように、第1内部配線10に正の抵抗温度係数を有する第1ゲート抵抗8が挿入されている場合を説明する。この場合、ゲート駆動回路2とゲート端子4の間に実質的な電圧降下がなく、出力電圧と入力電圧はほぼ等しい。出力電圧と入力電圧は、半導体装置6の温度によらず、一定である。上記の場合、ゲート端子4と、第1ゲート抵抗8と、ゲート電極12と、第2ゲート抵抗18(または18a, 18b)と、定電位点20が直列に接続された回路が形成されるために、ゲート電極12に印加される印加電圧は、入力電圧に等しくならない。すなわち、印加電圧は、入力電圧を第

10

20

30

40

50

1ゲート抵抗8と第2ゲート抵抗18（または18a, 18b）で分圧した電圧に等しくなる。

【0013】

第1ゲート抵抗8は、正の抵抗温度係数を持っているために、半導体装置6の温度が上昇すると、第1ゲート抵抗8の抵抗値が上昇する。第1ゲート抵抗8の抵抗値が上昇すると、第1ゲート抵抗8の抵抗値と第2ゲート抵抗18（または18a, 18b）の抵抗値で分圧される電圧が下降し、ゲート電極12に印加される印加電圧が下降する。印加電圧が下降すると、半導体装置6の通電電力量と発熱量が抑制され、半導体装置6の過熱が避けられる。正の抵抗温度係数を有する第1ゲート抵抗8が、半導体装置6の温度を検知する機能と、ゲート電極12に実際に印加される印加電圧を調整する機能の両機能を実現する。ゲート駆動回路2が出力するターンオン電圧を増減調整しないでも、半導体装置6の過熱が避けられる。本発明によると、ゲート駆動回路2が出力するターンオン電圧を増減調整する回路が必要とされない。出力電圧を増減調整しなくて印加電圧は増減調整される。このことを本明細書では、自律的な調整作用という。

10

【0014】

図1(A)に示すように、第2ゲート抵抗18が半導体装置6外にあって半導体装置6の温度の影響を受けない場合、第2ゲート抵抗18aの抵抗温度係数に制約はない。

図1(B)に示すように、第2ゲート抵抗18が半導体装置6内にあって、半導体装置6の温度の影響を受ける場合、第2ゲート抵抗18が負の抵抗温度係数を持っていれば、印加電圧の自律的な調整作用が得られる。第2ゲート抵抗18aが負の抵抗温度係数を持つ場合、印加電圧の自律的な調整作用が強調される。

20

図1(c)に示すように、第2ゲート抵抗18が半導体装置6内にあって、半導体装置6の温度の影響を受ける場合、第2ゲート抵抗18bの抵抗温度係数が第1ゲート抵抗8の抵抗温度係数よりも格段に小さいものであれば、前記した印加電圧の自律的な調整作用が得られる。

20

【0015】

次に、図1(D)(B)(E)に示すように、第2内部配線14に負の抵抗温度係数を有する第2ゲート抵抗18が挿入されている場合を説明する。この場合、接続端子16と定電圧点20の間に実質的な電圧降下がなく、接続端子16の電圧は定電圧に維持される。

30

上記の場合、ゲート駆動回路2と、第1ゲート抵抗8（または8a, 8b）と、ゲート電極12と、第2ゲート抵抗18と、定電位点20が直列に接続された回路が形成されるために、ゲート電極12に印加される印加電圧は、出力電圧に等しくならない。すなわち、印加電圧は、ゲート駆動回路駆動2の出力電圧を第1ゲート抵抗8（または8a, 8b）と第2ゲート抵抗18で分圧した電圧に等しくなる。

【0016】

第2ゲート抵抗18は、負の抵抗温度係数を持っているために、半導体装置6の温度が上昇すると、第2ゲート抵抗18の抵抗値が下降する。第2ゲート抵抗18の抵抗値が下降すると、第1ゲート抵抗8（または8a, 8b）の抵抗値と第2ゲート抵抗18の抵抗値で分圧される電圧が下降し、ゲート電極12に印加される印加電圧が下降する。印加電圧が下降すると、半導体装置6の通電電力量と発熱量が抑制され、半導体装置6の過熱が避けられる。負の抵抗温度係数を有する第2ゲート抵抗18が、半導体装置6の温度を検知する機能と、ゲート電極12に実際に印加される印加電圧を調整する機能の両機能を実現する。ゲート駆動回路2が出力するターンオン電圧を増減調整しないでも、半導体装置6の過熱が避けられる。本発明によると、ゲート駆動回路2が出力するターンオン電圧を増減調整する回路が必要とされない。出力電圧を増減調整しなくても印加電圧は増減調整される。このことを本明細書では、自律的な調整作用という。

40

【0017】

図1(D)に示すように、第1ゲート抵抗8aが半導体装置6外にあって半導体装置6の温度の影響を受けない場合、第1ゲート抵抗8aの抵抗温度係数に制約はない。

50

図1(B)に示すように、第1ゲート抵抗8が半導体装置6内にあって、半導体装置6の温度の影響を受ける場合、第1ゲート抵抗8が正の抵抗温度係数を持っていれば、印加電圧の自律的な調整作用が得られる。第1ゲート抵抗8が正の抵抗温度係数を持つ場合、印加電圧の自律的な調整作用が強調される。

図1(E)に示すように、第1ゲート抵抗8bが半導体装置6内にあって、半導体装置6の温度の影響を受ける場合、第1ゲート抵抗8bの抵抗温度係数が第2ゲート抵抗18の抵抗温度係数よりも格段に小さいものであれば、前記した印加電圧の自律的な調整作用が得られる。

【0018】

抵抗温度係数を利用する印加電圧の自律的な調整作用は、バイポーラトランジスタ(例えばIGBT)でも得られるし、ユニポーラトランジスタ(例えばMOSFET)でも得られる。バイポーラトランジスタの場合、第1半導体領域がエミッタ領域であり、第2半導体領域がボディ領域であり、第3半導体領域がドリフト領域となる。ユニポーラトランジスタの場合、第1半導体領域がソース領域であり、第2半導体領域がボディ領域であり、第3半導体領域がドリフト領域(あるいはドレイン領域)となる。

【0019】

印加電圧の自律的な調整作用は、ゲート電極がトレンチ型であっても得られるし、ブレーナー型であっても得られる。いずれの場合でも、半導体装置の温度に対応してゲート電極に実際に印加される印加電圧が自律的な調整され、半導体装置の過熱が避けられる。

【0020】

本発明の半導体装置は、半導体チップ内に集積することができる。この場合、複数個の半導体装置の各々が、共通ゲート端子と共に接続されればよい。

【0021】

半導体装置を集積して用いる場合、周辺に配置されている半導体装置は放熱しやすいのに対し、中心近傍にある半導体装置は放熱しづらいために過熱しやすい。従来の技術によると、中心近傍にある半導体装置に対してはゲート駆動回路が出力するゲートオン電圧を下げ、発熱量を低減する必要がある。温度環境が相違する範囲ごとに、温度検出回路とゲート電圧の調整回路を必要とする。

本発明によると、半導体装置の配置位置に無関係に共通ゲート端子と共に接続すればよい。中心近傍にあって過熱しやすい半導体装置の温度が上昇すると、その半導体装置に対応する第1ゲート抵抗の抵抗値が上昇するか、あるいは、その半導体装置に対応する第2ゲート抵抗の抵抗値が下降し、その半導体装置のゲート電極に印加される印加電圧が下げられる。個々の半導体装置の温度に対応して印加電圧が自律的に調整される。半導体チップ内の温度のばらつきを小さくすることができる。

【0022】

第1ゲート抵抗および/または第2ゲート抵抗は、個々の半導体装置に対応して設けてもよいし、チップ内の複数個の半導体装置を温度環境によってグループ化し、各々のグループに対して第1ゲート抵抗および/または第2ゲート抵抗を用意してもよい。温度環境が類似するグループ内の複数個の半導体装置には、共通の第1ゲート抵抗および/または第2ゲート抵抗を利用してもよい。

【0023】

各々の半導体装置の第1ゲート抵抗が、抵抗値を調整可能な抵抗パターンで形成されていることが好ましい。あるいは、各々の半導体装置の第2ゲート抵抗が、抵抗値を調整可能な抵抗パターンで形成されていることが好ましい。

ここでいう調整可能とは、印刷等の技術によって抵抗パターンを作成した後に、例えばレーザなどを照射することによって抵抗値を調整可能なことをいう。

各々の第1ゲート抵抗および/または第2ゲート抵抗を調整することによって、チップ内での不均一な温度分布を抑制することができる。

【0024】

本発明は、電界効果型トランジスタの過熱防止機能を有する回路をも提供する。本発明

10

20

30

40

50

の回路は、電界効果型トランジスタと、一定電圧に調整されているオン電圧とオフ電圧の間で変化する電圧を出力するゲート駆動回路と、電界効果型トランジスタのゲート電極とゲート駆動回路の間に挿入されており、電界効果型トランジスタに熱的に接合されているとともに、正の抵抗温度係数を有するゲート抵抗と、電界効果型トランジスタのゲート電極と定電圧点の間に挿入されている一定の抵抗値を有する抵抗を備えている。

#### 【0025】

ゲート抵抗は、正の抵抗温度係数を持っており、電界効果型トランジスタに熱的に接合しているので、電界効果型トランジスタの温度が上昇すると、ゲート抵抗の抵抗値が上昇する。ゲート抵抗の抵抗値が上昇すると、ゲート抵抗の抵抗値と一定の抵抗値を有する抵抗の抵抗値で分圧される電圧が下降し、電界効果型トランジスタのゲート電極に印加される印加電圧が下降する。印加電圧が下降すると、電界効果型トランジスタの通電電力量と発熱量が抑制され、電界効果型トランジスタの過熱が避けられる。正の抵抗温度係数を有するゲート抵抗が、電界効果型トランジスタの温度を検知する機能と、電界効果型トランジスタに実際に印加される印加電圧を調整する機能の両機能を実現する。ゲート駆動回路が output するオン電圧を増減調整しなくとも、電界効果型トランジスタの過熱が避けられる。オン電圧を増減調整する必要がなく、一定のオン電圧を出力するゲート駆動回路を利用すれば足りる。

#### 【発明の効果】

#### 【0026】

本発明によると、ゲート駆動回路が output するゲートオン電圧を半導体装置の温度に対応して増減調整する必要がない。すなわち、出力電圧の調整回路が必要とされない。半導体装置の温度が上昇したことを検知する回路が、ゲート電極に実際に印加される印加電圧を調整する回路をも兼用する。ゲート駆動回路の構成を単純化することができる。

本発明は、複数の半導体装置を半導体チップ内に集積する場合に特に有用であり、半導体チップ内の温度のばらつきを小さく抑えることができる。過熱の発生を防止できる範囲内で、各々の半導体装置を駆動することができる。

#### 【発明を実施するための最良の形態】

#### 【0027】

下記に説明する実施例の好ましい特徴を列記する。

(第1特徴) 第1ゲート抵抗を半導体装置内に設け、第2ゲート抵抗を半導体装置外に設ける。

(第2特長) 第1ゲート抵抗を半導体装置外に設け、第2ゲート抵抗を半導体装置内に設ける。

(第3特徴) 第1ゲート抵抗と第2ゲート抵抗の双方を半導体装置内に設ける。

(第4特長) 第1ゲート抵抗と第2ゲート抵抗の合計抵抗値に対して、温度に対応して変化する抵抗値の変化幅が、5%～50%の範囲である。

#### 【実施例】

#### 【0028】

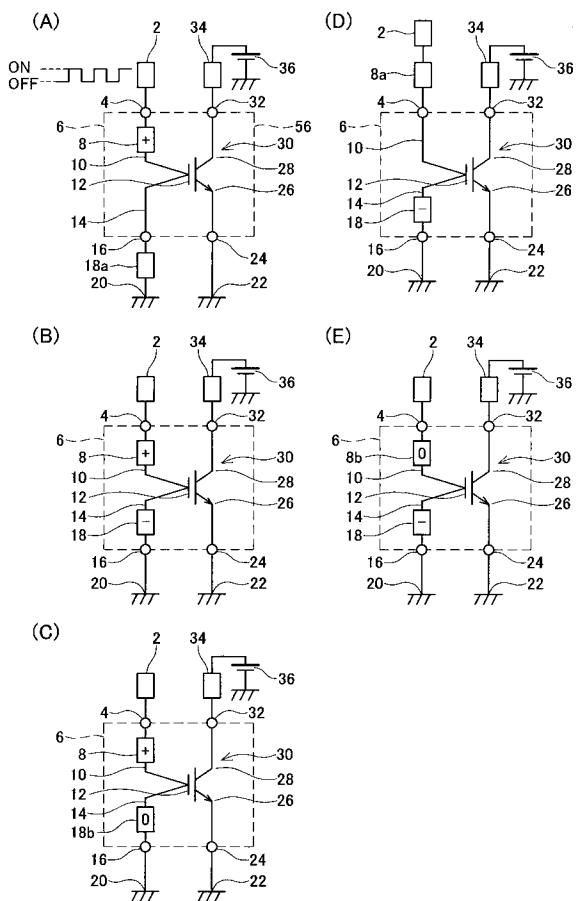

図1(A)に、本発明の第1実施例である半導体装置6と、その半導体装置6を利用する場合の回路図を示す。半導体装置6は、半導体チップ56内に形成されているバイポーラトランジスタ30を備えている。図2は、バイポーラトランジスタ30の断面構造を示している。バイポーラトランジスタ30は、n型のエミッタ領域26(第1導電型の第1半導体領域の実施例)と、n型のドレイン領域50(第1導電型の第3半導体領域の実施例)と、エミッタ領域26とドレイン領域50を分離しているp型のボディ領域48(第2導電型の第2半導体領域の実施例)を備えている。バイポーラトランジスタ30は、その他に、p型のボディコンタクト領域40、n型のバッファ領域52、p型のコレクタ領域28を備えている。バイポーラトランジスタ30は、IGBTの構造を備えている。

#### 【0029】

バイポーラトランジスタ30は、エミッタ領域26からボディ領域48を経てドレイン領域50に達する範囲に存在している半導体に対して、ゲート絶縁膜44を介して対向し

ているトレンチゲート電極 12 を備えている。

またバイポーラトランジスタ 30 は、エミッタ電極 24 とコレクタ電極 32 を備えている。エミッタ電極 24 は、エミッタ領域 26 とボディコンタクト領域 40 に接しており、層間絶縁膜 42 によってトレンチゲート電極 12 から絶縁されている。コレクタ電極 32 は、コレクタ領域 28 に接している。トレンチゲート電極 12 は、エミッタ電極 24 が存在しない位置において半導体チップ 56 の表面に露出している。

#### 【0030】

図 1 (A) に示すように、バイポーラトランジスタ 30 のエミッタ電極 24 は、接地されて用いられる。バイポーラトランジスタ 30 のコレクタ電極 32 は、負荷 34 を介して直流電源 36 に接続されて用いられる。

バイポーラトランジスタ 30 のゲート電極 12 は、第 1 ゲート抵抗 8 を介して半導体チップ 56 の表面に形成されているゲート端子 4 に接続されている。第 1 ゲート抵抗 8 は、半導体チップ 56 の表面に形成されている。第 1 ゲート抵抗 8 を介してゲート電極 12 とゲート端子 4 を接続する配線 10 (第 1 内部配線の実施例) も、半導体チップ 56 の表面に形成されている。ゲート電極 12 は、半導体チップ 56 の表面に形成されている配線 14 (第 2 内部配線の実施例) によって、半導体チップ 56 の表面に形成されている接続端子 16 にも接続されている。

#### 【0031】

半導体装置 6 を利用する場合、ゲート端子 4 にゲート駆動回路 2 が接続される。接続端子 16 は第 2 ゲート抵抗 18a を介して定電圧点 20 に接続されて用いられる。第 1 ゲート抵抗 8 は正の抵抗温度係数を有しており、トランジスタ 30 の温度とほぼ同じ温度をなる位置に配置されている。第 2 ゲート抵抗 18a は、トランジスタ 30 の温度の影響を受けない位置に配置されており、抵抗温度係数は正であってもよいし、負であってもよい。

#### 【0032】

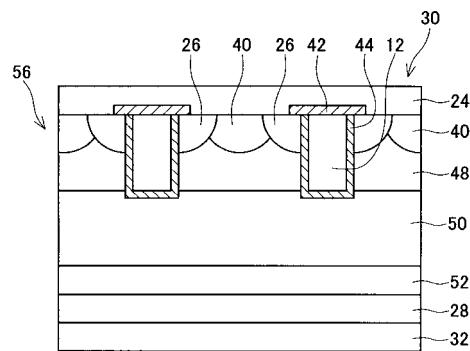

図 3 に、第 1 ゲート抵抗 8 の温度と抵抗値の関係を表しているグラフを示す。横軸はトランジスタ 30 の温度 ( ) を示し、縦軸は第 1 ゲート抵抗 8 の抵抗値 ( ) を示している。トランジスタ 30 の温度が上昇するにつれて、第 1 ゲート抵抗 8 の抵抗値は大きくなる。

#### 【0033】

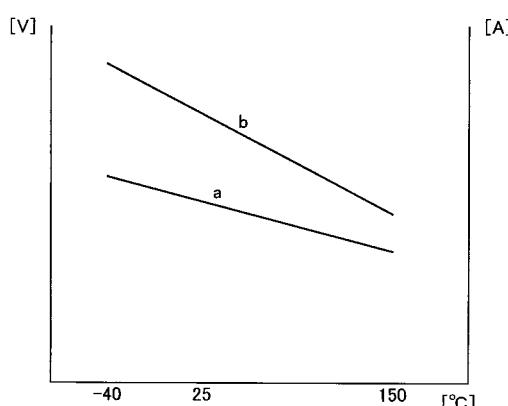

図 4 のグラフ a に、トランジスタ 30 の温度 ( ) と、ゲート電極 12 に印加される印加電圧の関係を示す。横軸はトランジスタ 30 の温度であり、左横軸は印加電圧 (V) を示している。

印加電圧は、ゲート駆動回路 2 が output するゲートオン電圧を、第 1 ゲート抵抗 8 の抵抗値と第 2 ゲート抵抗 18 の抵抗値で分圧した電圧であり、第 1 ゲート抵抗 8 の抵抗値が増大すれば、印加電圧は下降する関係にある。なお、第 1 ゲート抵抗 8 の抵抗値が増大すれば印加電圧が下降する関係は、トランジスタ 30 の温度によって第 2 ゲート抵抗 18 の抵抗値が変化しない場合、あるいは、トランジスタ 30 の温度の上昇によって第 2 ゲート抵抗 18 の抵抗値が下降する場合にも得られる。図 1 (A) の場合、第 2 ゲート抵抗 18 は半導体装置 6 の外部にあり、トランジスタ 30 の温度が変化しても、第 2 ゲート抵抗 18 の温度は変化しない。したがって、トランジスタ 30 の温度が変化しても、第 2 ゲート抵抗 18 の抵抗値は変化しない。図 1 (B) の場合、トランジスタ 30 の温度変化に追従して第 2 ゲート抵抗 18 の温度も変化する。第 2 ゲート抵抗 18 の抵抗値は温度上昇に伴って下降する。トランジスタ 30 の温度が上昇すると、第 2 ゲート抵抗 18 の抵抗値は下降し、印加電圧は下降する。図 1 (C) の場合、トランジスタ 30 の温度変化に追従して第 2 ゲート抵抗 18 の温度も変化するが、第 2 ゲート抵抗 18 の抵抗温度係数は小さいために、温度変化があっても抵抗値はさほど変化しない。トランジスタ 30 の温度が上昇すると、印加電圧は下降する。

#### 【0034】

図 4 のグラフ b に、トランジスタ 30 の温度と、トランジスタ 30 のエミッタ電極 24 とコレクタ電極 32 間に流れる電流の関係を示す。横軸はトランジスタ 30 の温度 ( )

であり、右横軸はエミッタ - コレクタ間に流れる電流 (A) を示している。エミッタ - コレクタ間に流れる電流は、印加電圧に依存して変化し、印加電圧が下降すればエミッタ - コレクタ間に流れる電流も下降する。グラフからわかるように、トランジスタ 30 の温度が上昇すると、印加される電圧は低下し、エミッタ - コレクタ間に流れる電流も下降し、トランジスタ 30 の発熱量が絞られる。トランジスタ 30 の温度が上昇すれば、トランジスタ 30 の発熱量が絞られるために、トランジスタ 30 が過熱することがない。

#### 【0035】

トランジスタ 30 の許容上限温度での抵抗値と常温での抵抗値の差と、第1ゲート抵抗と第2ゲート抵抗の合計抵抗値の比率が、5%～50%の範囲であることが好ましい。この比率にあると、トランジスタ 30 の温度が上昇すれば、印加電圧が下降し、トランジスタ 30 の発熱量が絞られるという自律的調整作用が適切に得られる。前記比率が5%以下であると、自律的調整作用が弱すぎ、前記比率が50%以上であると、自律的調整作用が強く働きすぎる。

10

#### 【0036】

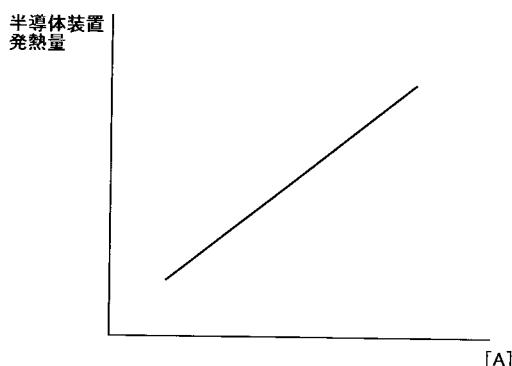

図5に、エミッタ - コレクタ間に流れる電流と、トランジスタ 30 の発熱量の関係を示す。横軸はエミッタ - コレクタ間に流れる電流 (A) であり、縦軸はトランジスタ 30 の発熱量を示す。エミッタ - コレクタ間に流れる電流が制限されると、トランジスタ 30 の発熱量が絞られる。

#### 【0037】

トランジスタ 30 の温度が上昇すれば、印加電圧が下降し、トランジスタ 30 の発熱量が絞られるという自律的調整作用が得られるので、ゲート駆動回路 2 が output するゲートオン電圧は一定であれば足りる。温度に対応してゲートオン電圧を調整する回路を設ける必要はない。

20

#### 【0038】

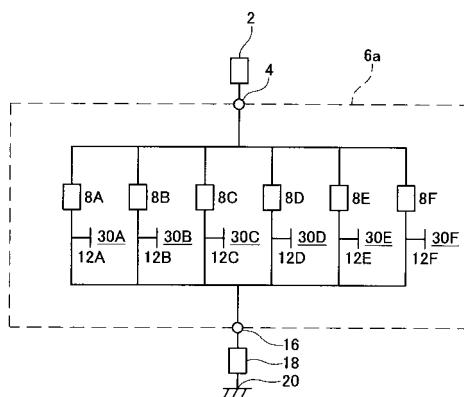

図6に、複数の半導体装置 6 が同一チップ内に集積されている様子を示す。この場合、図示の明瞭化のために、トランジスタ 30 のゲート電極 12 のみを示す。図6は、チップ内に6個のトランジスタ 30 A～30 F が集積されている場合を示す。トランジスタの個数は、6個に限られない。

図6の場合、トランジスタ 30 A～30 F の各々に対して第1トランジスタ 8 A～8 F が形成されており、共通のゲート端子 4 に接続されている。トランジスタ 30 A～30 F の各々のゲート電極 12 A～12 F は、共通の接続端子 16 に接続されている。また、トランジスタ 30 A～30 F に対しての共通の第2ゲート抵抗 18 が接続されている。

30

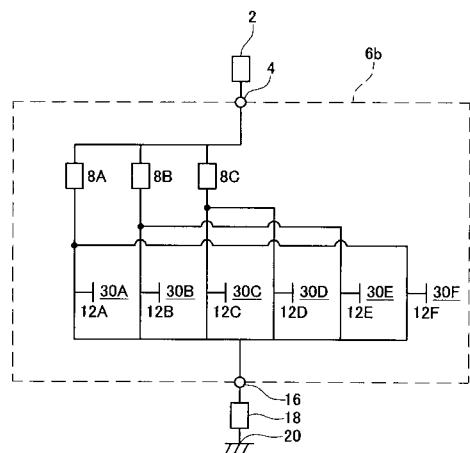

#### 【0039】

図7に、図6の半導体チップの変形例を示す。この場合、チップ内のトランジスタ 30 が、熱環境によって3つにグループ化されている。トランジスタ 30 A, 30 F は、チップ 6b の外側に位置しており、放熱しやすく、過熱しにくい。トランジスタ 30 C, 30 D は、チップ 6b の中心に位置しており、放熱しづらく、過熱しやすい。トランジスタ 30 B, 30 E は、中間的な特性を備えている。この場合、過熱しやすいトランジスタ 30 A, 30 F は、トランジスタ 30 A から熱的影響を受けやすい第1ゲート抵抗 8 A に共通に接続されている。過熱しやすいトランジスタ 30 C, 30 D は、トランジスタ 30 C から熱的影響を受けやすい第1ゲート抵抗 8 C に共通に接続されている。トランジスタ 30 B, 30 E は、トランジスタ 30 B から熱的影響を受けやすい第1ゲート抵抗 8 B に共通に接続されている。

40

熱的環境によってグループ化し、グループ毎に第1ゲート抵抗を利用してもよい。

#### 【0040】

図6、図7では、正の抵抗温度係数を持つ第1ゲート抵抗をチップ内に設ける例を説明している。負の抵抗温度係数を持つ第2ゲート抵抗を利用する場合には、第2ゲート抵抗をチップ内に設ければよい。

#### 【0041】

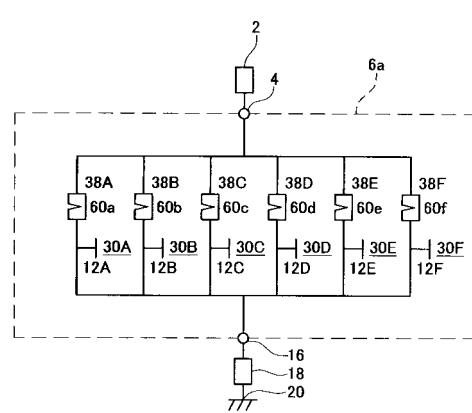

図8に、図6の半導体チップにおいて、第1ゲート抵抗の各々に抵抗値を調整可能な抵

50

抗パターンが形成されている図を示す。第1ゲート抵抗38A～38Fのそれぞれは、抵抗パターンが形成されている。抵抗パターンは、半導体チップ6aの表面に物理的、化学的堆積法によって形成することができる。半導体チップ6aの表面に形成されている抵抗パターン60a～60fにレーザを照射することによって切れ目60a～60fを入れることができる。切れ目60a～60fの位置および／または大きさを調整することによって、第1ゲート抵抗38A～38Fのそれぞれの抵抗値を調整することができる。抵抗値の大きさを調整することによって、ゲート電極に印加するゲート電圧の自律的調整作用の大きさを適当なレベルの調整することができる。

#### 【0042】

負の抵抗温度係数を持つ第2ゲート抵抗を、トリミング可能な抵抗パターンで形成してもよい。グループ化されている半導体装置ごとにゲート抵抗が用意されている場合、各グループのためのゲート抵抗ごとに抵抗値を適値に調整することができる。チップ内の不均一な温度分布を抑制することができる。

10

#### 【0043】

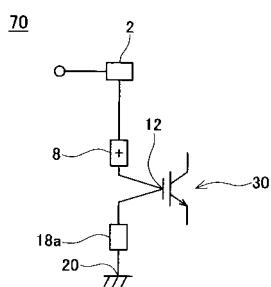

図9に、本実施例の半導体装置を利用して実現される過熱防止機能を有する回路70の図を示す。回路70は、電界効果型トランジスタ30の過熱を防止する自律的な調整機能を備えている回路である。回路70を実現するためには、電界効果型トランジスタ30のゲート電極12を、正の温度抵抗係数を有するゲート抵抗8を介してゲート駆動回路2に接続する。さらにゲート電極12を、一定の抵抗値を有する抵抗18aを介して定電圧点20に接続する。

20

#### 【0044】

ゲート抵抗8は、電界効果型トランジスタ30と熱的に接合しており、ゲート抵抗8の抵抗値は電界効果型トランジスタ30の温度の影響を受ける。抵抗18aは、電界効果型トランジスタ30の温度の影響を受ける位置に配置されていてもよいし、温度の影響を受けない位置に配置されていてもよい。ゲート抵抗8は、正の抵抗温度係数を持っており、電界効果型トランジスタ30に熱的に接合しているので、電界効果型トランジスタ30の温度が上昇すると、ゲート抵抗8の抵抗値が上昇する。ゲート抵抗8の抵抗値が上昇すると、ゲート抵抗8の抵抗値と一定の抵抗値を有する抵抗18aの抵抗値で分圧される電圧が下降し、電界効果型トランジスタ30のゲート電極12に印加される印加電圧が下降する。印加電圧が下降すると、電界効果型トランジスタ30の通電電力量と発熱量が抑制され、電界効果型トランジスタ30の過熱が避けられる。

30

#### 【0045】

本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

#### 【図面の簡単な説明】

#### 【0046】

【図1】(A)～(E)は、第1実施例の半導体装置6と、それを利用する場合の回路を示す。

40

【図2】バイポーラトランジスタ30の断面構造を示す。

【図3】半導体装置6の第1ゲート抵抗8の温度と抵抗値の関係を表す。

【図4】aは、半導体装置6の温度と印加電圧の関係を表し、bは、温度とエミッタ-コレクタ間電流の関係を表す。

【図5】半導体装置6のエミッタ-コレクタ間電流と発熱量の関係を表す。

【図6】半導体装置6が同一チップ内に集積されている図を示す。

【図7】図6の半導体チップの変形例を示す。

【図8】図6の半導体チップの第1ゲート抵抗の各々が、抵抗値を調整可能な抵抗パターンで形成されている場合を示す。

【図9】電界効果型トランジスタ30の過熱防止機能を有する回路70を示す。

50

## 【符号の説明】

## 【0 0 4 7】

- 2 : ゲート駆動回路

4 : ゲート端子

6 : 半導体装置

8、8a、8b、8A～8F、38A～38F : 第1ゲート抵抗

10 : 第1内部配線

12、12A～12F : ゲート電極

14 : 第2内部配線

16 : 接続端子

18、18a、18b : 第2ゲート抵抗

20 : 定電圧点

22 : 接地点

24 : エミッタ電極

26 : エミッタ領域

28 : コレクタ領域

30、30A～30F : パワートランジスタ

32 : コレクタ電極

34 : 負荷

36 : 直流電源

40 : ボディコンタクト領域

42 : 層間絶縁膜

44 : ゲート絶縁膜

48 : ボディ領域

50 : ドレイン領域

52 : n型バッファ領域

56 : 半導体チップ

60a～60e : 切れ目

70 : 回路

10

20

【図1】

【 図 2 】

【 図 4 】

〔 四 6 〕

( 5 )

【図7】

【図8】

【図9】

## フロントページの続き

| (51) Int.Cl.             | F I          | テーマコード(参考) |

|--------------------------|--------------|------------|

| H 01 L 21/8234 (2006.01) | H 01 L 27/04 | V          |

| H 01 L 27/088 (2006.01)  | H 01 L 27/06 | 3 1 1      |

| H 03 K 17/08 (2006.01)   | H 01 L 27/08 | 1 0 2 E    |

|                          | H 03 K 17/08 | Z          |