### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5967912号 (P5967912)

(45) 発行日 平成28年8月10日(2016.8.10)

(24) 登録日 平成28年7月15日(2016.7.15)

| (51) Int.Cl. |               |           | F 1  |       |     |

|--------------|---------------|-----------|------|-------|-----|

| HO4N         | <i>5/3</i> 57 | (2011.01) | HO4N | 5/335 | 570 |

| HO4N         | 5/374         | (2011.01) | HO4N | 5/335 | 740 |

| HO4N         | 5/378         | (2011.01) | HO4N | 5/335 | 780 |

請求項の数 12 (全 19 頁)

(21) 出願番号 特願2011-264512 (P2011-264512) (22) 出願日 平成23年12月2日 (2011.12.2) (65) 公開番号 特開2013-118475 (P2013-118475A) (43) 公開日 平成25年6月13日 (2013.6.13) 審査請求日 平成26年11月28日 (2014.11.28)

||(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

|(74)代理人 100090273

弁理士 國分 孝悦

(72) 発明者 菊池 伸

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 松永 隆志

最終頁に続く

### (54) 【発明の名称】 固体撮像装置

### (57)【特許請求の範囲】

### 【請求項1】

光電変換を行う光電変換素子を含む複数の画素と、

前記複数の画素の信号が出力される複数の信号線と、

前記複数の信号線に定電流を流すための第1の定電流回路と、

定電流を流すための第2の定電流回路とを有し、

前記第1の定電流回路は、

複数の第1のトランジスタと、

前記<u>複数の</u>第1のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間に共通に接続される1個の第1の抵抗と、

ドレイン端子又はコレクタ端子が前記<u>複数の</u>信号線に接続され、ソース端子又はエミッタ端子が<u>抵抗を介することなく</u>前記<u>複数の</u>第1のトランジスタのドレイン端子又はコレクタ端子に接続される複数の第3のトランジスタとを有し、

前記複数の第1のトランジスタのソース端子又はエミッタ端子は、前記1個の第1の抵抗に直接接続され、

前記第2の定電流回路は、

ゲート端子又はベース端子が前記<u>複数の</u>第1のトランジスタのゲート端子又はベース端子に接続される第2のトランジスタと、

前記第2のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間に接続される第2の抵抗と、

ゲート端子又はベース端子が前記<u>複数の</u>第3のトランジスタのゲート端子又はベース端子に接続され、ソース端子又はエミッタ端子が前記第2のトランジスタのドレイン端子又はコレクタ端子に接続される第4のトランジスタと、

前記第2のトランジスタのゲート端子又はベース端子及び前記第4のトランジスタのドレイン端子又はコレクタ端子に接続される第1の定電流源とを有することを特徴とする固体撮像装置。

#### 【請求項2】

前記第2の定電流回路を流れる電流は、前記第1の定電流回路を流れる電流のM倍であり、

前記第2の抵抗の値は、前記第1の抵抗の値の1/M倍であることを特徴とする請求項1記載の固体撮像装置。

#### 【請求項3】

さらに、前記第4のトランジスタのゲート端子又はベース端子に接続される定電圧源を 有することを特徴とする請求項1又は2記載の固体撮像装置。

#### 【請求項4】

さらに、第2の定電流源と、

ドレイン端子又はコレクタ端子が前記第2の定電流源に接続され、ゲート端子又はベース端子が前記第2の定電流源及び前記第4のトランジスタのゲート端子又はベース端子に接続される第5のトランジスタと、

前記第5のトランジスタのソース端子又は<u>エミッタ</u>端子と前記基準電位ノードとの間に接続される第3の抵抗とを有することを特徴とする請求項1~3のいずれか1項に記載の固体撮像装置。

### 【請求項5】

前記複数の画素は、行列状に配列され、

前記複数の信号線は、前記複数の画素の列毎に接続される複数の信号線であり、

前記複数の第1のトランジスタは、ソース端子又はエミッタ端子が相互に接続され、

前記第1の抵抗は、前記相互に接続されたソース端子又はエミッタ端子と前記基準電位 ノードとの間に接続されることを特徴とする請求項1~4のいずれか1項に記載の固体撮 像装置。

# 【請求項6】

光電変換を行う光電変換素子を含む複数の画素と、

前記複数の画素の信号が出力される複数の信号線と、

前記複数の信号線に定電流を流すための第1の定電流回路と、

定電流を流すための第2の定電流回路とを有し、

前記第1の定電流回路は、

複数の第1のトランジスタと、

前記<u>複数の</u>第1のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間に共通に接続される1個の第1の抵抗と、

ドレイン端子又はコレクタ端子が前記<u>複数の</u>信号線に接続され、ソース端子又はエミッタ端子が<u>抵抗を介することなく</u>前記<u>複数の</u>第1のトランジスタのドレイン端子又はコレクタ端子に接続される複数の第3のトランジスタとを有し、

前記複数の第1のトランジスタのソース端子又はエミッタ端子は、前記1個の第1の抵 抗に直接接続され、

前記第2の定電流回路は、

ゲート端子又はベース端子が前記<u>複数の</u>第1のトランジスタのゲート端子又はベース端子に接続される第2のトランジスタと、

前記第2のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間に接続される第2の抵抗と、

ゲート端子又はベース端子が前記<u>複数の</u>第3のトランジスタのゲート端子又はベース端子に接続され、ソース端子又はエミッタ端子が前記第2のトランジスタのドレイン端子又

10

20

30

40

はコレクタ端子及びゲート端子又はベース端子に接続される第4のトランジスタと、

前記第4のトランジスタのゲート端子又はベース端子及びドレイン端子又はコレクタ端子に接続される第1の定電流源とを有することを特徴とする固体撮像装置。

#### 【請求項7】

光電変換を行う光電変換素子を含む複数の画素と、

前記複数の画素の信号を増幅する複数のアンプと、

前記複数のアンプに定電流を流すための第1の定電流回路と、

定電流を流すための第2の定電流回路とを有し、

前記第1の定電流回路は、

複数の第1のトランジスタと、

前記<u>複数の</u>第1のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間に共通に接続される1個の第1の抵抗と、

ドレイン端子又はコレクタ端子が前記<u>複数の</u>アンプに接続され、ソース端子又はエミッタ端子が<u>抵抗を介することなく</u>前記<u>複数の</u>第1のトランジスタのドレイン端子又はコレクタ端子に接続される複数の第3のトランジスタとを有し、

前記複数の第1のトランジスタのソース端子又はエミッタ端子は、前記1個の第1の抵抗に直接接続され、

前記第2の定電流回路は、

ゲート端子又はベース端子が前記<u>複数の</u>第1のトランジスタのゲート端子又はベース端子に接続される第2のトランジスタと、

前記第2のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間に接続される第2の抵抗と、

ゲート端子又はベース端子が前記<u>複数の</u>第3のトランジスタのゲート端子又はベース端子に接続され、ソース端子又はエミッタ端子が前記第2のトランジスタのドレイン端子又はコレクタ端子に接続される第4のトランジスタと、

前記第2のトランジスタのゲート端子又はベース端子及び前記第4のトランジスタのドレイン端子又はコレクタ端子に接続される第1の定電流源とを有することを特徴とする固体撮像装置。

### 【請求項8】

前記第2の定電流回路を流れる電流は、前記第1の定電流回路を流れる電流のM倍であり、

前記第2の抵抗の値は、前記第1の抵抗の値の1/M倍であることを特徴とする請求項7記載の固体撮像装置。

### 【請求項9】

さらに、前記第4のトランジスタのゲート端子又はベース端子に接続される定電圧源を 有することを特徴とする請求項7又は8記載の固体撮像装置。

# 【請求項10】

さらに、第2の定電流源と、

ドレイン端子又はコレクタ端子が前記第2の定電流源に接続され、ゲート端子又はベース端子が前記第2の定電流源及び前記第4のトランジスタのゲート端子又はベース端子に接続される第5のトランジスタと、

前記第 5 のトランジスタのソース端子又はエミッタ端子と前記基準電位ノードとの間に接続される第 3 の抵抗とを有することを特徴とする請求項 $\frac{7}{2}$  ~  $\frac{9}{2}$  のいずれか 1 項に記載の固体撮像装置。

#### 【請求項11】

前記複数の画素は、行列状に配列され、

前記複数のアンプは、前記複数の画素の列毎に接続される複数のアンプであり、

前記複数の第1のトランジスタは、ソース端子又はエミッタ端子が相互に接続され、

前記第1の抵抗は、前記相互に接続されたソース端子又はエミッタ端子と前記基準電位ノードとの間に接続されることを特徴とする請求項7~10のいずれか1項に記載の固体

10

20

30

40

#### 撮像装置。

### 【請求項12】

光電変換を行う光電変換素子を含む複数の画素と、

前記複数の画素の信号を増幅する複数のアンプと、

前記複数のアンプに定電流を流すための第1の定電流回路と、

定電流を流すための第2の定電流回路とを有し、

前記第1の定電流回路は、

複数の第1のトランジスタと、

前記複数の第1のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間 に共通に接続される1個の第1の抵抗と、

10

ドレイン端子又はコレクタ端子が前記複数のアンプに接続され、ソース端子又はエミッ 夕端子が抵抗を介することなく前記複数の第1のトランジスタのドレイン端子又はコレク タ端子に接続される複数の第3のトランジスタとを有し、

前記複数の第1のトランジスタのソース端子又はエミッタ端子は、前記1個の第1の抵 抗に直接接続され、

前記第2の定電流回路は、

ゲート端子又はベース端子が前記複数の第1のトランジスタのゲート端子又はベース端 子に接続される第2のトランジスタと、

前記第2のトランジスタのソース端子又はエミッタ端子と基準電位ノードとの間に接続 される第2の抵抗と、

20

30

ゲート端子又はベース端子が前記複数の第3のトランジスタのゲート端子又はベース端 子に接続され、ソース端子又はエミッタ端子が前記第2のトランジスタのドレイン端子又 はコレクタ端子及びゲート端子又はベース端子に接続される第4のトランジスタと、

前記第4のトランジスタのゲート端子又はベース端子及びドレイン端子又はコレクタ端 子に接続される第1の定電流源とを有することを特徴とする固体撮像装置。

【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、固体撮像装置に関する。

#### 【背景技術】

[0002] 近年、固体撮像装置として、撮像領域の画素内部に増幅素子を有するCMOS型固体撮 像装置が普及してきている。CMOS型固体撮像装置は、マトリクス状に配列された画素

の各々が光電変換素子と増幅素子を有し、増幅された光電変換信号を列毎に共通化された 垂直信号線で読み出すように構成されている。各垂直信号線は定電流源を有し、通常はM OSトランジスタである増幅素子がソースフォロワ動作をすることで信号が増幅される。 特許文献1には、その一例が開示されている。

【先行技術文献】

#### 【特許文献】

[0003]

40

【特許文献 1 】特開 2 0 0 4 - 1 6 5 8 2 5 号公報

### 【発明の概要】

【発明が解決しようとする課題】

### [0004]

しかしながら、特許文献1には、以下のような課題がある。第一に、各垂直信号線に接 続された定電流回路は水平方向に1次元状に配列されている。列数分の定電流回路に流れ る電流がバイアスの基準となるグランド電位に向かって流れ、グランド線の配線抵抗によ リ本来はOVであるグランド電位が上昇する。この電位上昇により定電流を流しているM OSトランジスタのゲートバイアス電圧が変化し、画素ソースフォロワの動作点がずれて しまう。それにより回路動作のリニアリティがずれ、画像のシェーディングなどが発生す

る。

### [0005]

第二に、定電流のゲートバイアス線(以下、ゲートバイアス線という)は画面水平方向に長く延びている。そのために、例えばこの固体撮像装置がデジタルカメラ、デジタルビデオカメラに実装された場合、撮像装置の近傍にあるレンズ駆動用のモーターが動作した時に発生する磁気が原因となる電磁誘導による電流がゲート線を流れる。この誘導電流により、ゲート電位が変動し、画素出力が変化し、その結果、画像に"横筋"と呼ばれるノイズが発生することがわかってきた。

### [0006]

この現象は、近年、デジタルカメラ、デジタルビデオカメラの高感度化の目覚ましい進展とともに顕著になってきている。すなわち、微小なゲートバイアス線の電位変動が、特に高感度設定時に画質の劣化として見えやすくなってきている。

#### [0007]

本発明の目的は、画質の劣化を防止することができる固体撮像装置を提供することである。

【課題を解決するための手段】

### [0008]

本発明の固体撮像装置は、光電変換を行う光電変換素子を含む複数の画素と、前記複数 の画素の信号が出力される複数の信号線と、前記複数の信号線に定電流を流すための第1 の定電流回路と、定電流を流すための第2の定電流回路とを有し、前記第1の定電流回路 は、複数の第1のトランジスタと、前記複数の第1のトランジスタのソース端子又はエミ ッタ端子と基準電位ノードとの間に共通に接続される1個の第1の抵抗と、ドレイン端子 又はコレクタ端子が前記複数の信号線に接続され、ソース端子又はエミッタ端子が抵抗を 介することなく前記複数の第1のトランジスタのドレイン端子又はコレクタ端子に接続さ れる複数の第3のトランジスタとを有し、前記複数の第1のトランジスタのソース端子又 はエミッタ端子は、前記1個の第1の抵抗に直接接続され、前記第2の定電流回路は、ゲ ート端子又はベース端子が前記複数の第1のトランジスタのゲート端子又はベース端子に 接続される第2のトランジスタと、前記第2のトランジスタのソース端子又はエミッタ端 子と基準電位ノードとの間に接続される第2の抵抗と、ゲート端子又はベース端子が前記 複数の第3のトランジスタのゲート端子又はベース端子に接続され、ソース端子又はエミ ッタ端子が前記第2のトランジスタのドレイン端子又はコレクタ端子に接続される第4の トランジスタと、前記第2のトランジスタのゲート端子又はベース端子及び前記第4のト ランジスタのドレイン端子又はコレクタ端子に接続される第1の定電流源とを有すること を特徴とする。

### 【発明の効果】

#### [0009]

第1のトランジスタのゲートバイアス線が電磁誘導などの外乱によって電位変動しにくくなり、基準電位ノードの電位上昇によって第1のトランジスタに流れる定電流が変動することを抑制出来る。その結果、画像のシェーディング、横筋発生などを軽減する事が出来る。

【図面の簡単な説明】

[0010]

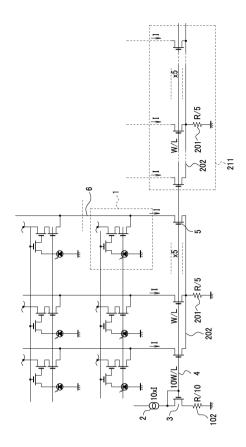

- 【図1】本発明の第1の実施形態の概念を説明するための図である。

- 【図2】本発明の第1の実施形態の固体撮像装置の回路構成図である。

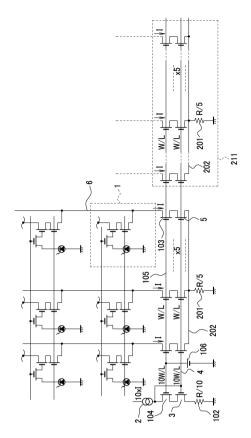

- 【図3】本発明の第2の実施形態の固体撮像装置の回路構成図である。

- 【図4】本発明の第2の実施形態の概念を説明するための図である。

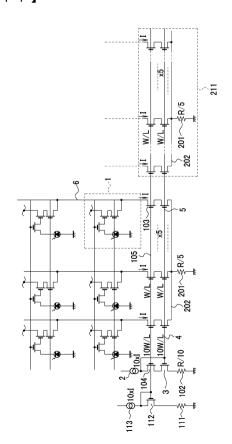

- 【図5】本発明の第3の実施形態の固体撮像装置の回路構成図である。

- 【図6】本発明の第4の実施形態の固体撮像装置の回路構成図である。

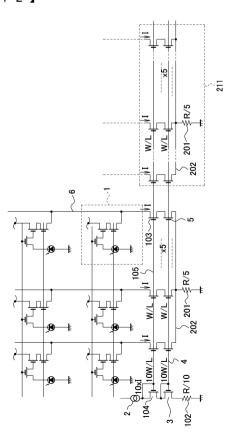

- 【図7】本発明の第5の実施形態の固体撮像装置の回路構成図である。

- 【図8】本発明の第6の実施形態の概念を説明するための図である。

20

10

30

40

【図9】本発明の第6の実施形態の固体撮像装置の回路構成図である。

【図10】本発明の第7の実施形態の固体撮像装置の回路構成図である。

【図11】本発明の第8の実施形態の固体撮像装置の回路構成図である。

【図12】本発明の第9の実施形態の固体撮像装置の回路構成図である。

【図13】本発明の第10の実施形態の固体撮像装置の回路構成図である。

【図14】本発明の第11の実施形態の固体撮像装置の回路構成図である。

【図15】本発明の第12の実施形態の固体撮像装置の回路構成図である。

【発明を実施するための形態】

[0011]

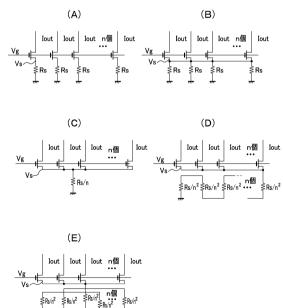

(第1の実施形態)

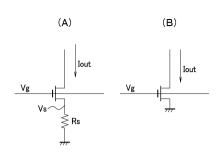

図1(A)及び(B)を用いて、定電流回路におけるソース抵抗Rsの効果を確認し、それに基づく第1の実施形態を述べる。図1(A)にソース抵抗Rsを有する定電流回路、図1(B)にソース抵抗Rsのない定電流回路を示す。ここで、Rsは、ソースに付加される抵抗(ソース抵抗)である。ioutは、出力電流Ioutの交流成分である。vgは、カレントミラーMOSトランジスタのゲート電位Vgの交流成分である。Vthは、MOSトランジスタの閾値電圧である。gmは、相互コンダクタンスである。

### [0012]

ソース抵抗 R s がある場合、図 1 (A)のように、定電流回路に流れる電流 I o u t の交流成分 i o u t は、次式 (1)で表される。

[0013]

【数1】

$$i_{out} = v_g \frac{1}{\frac{1}{g_m} + R_s} \cdots (1)$$

### [0014]

ソース抵抗 R s がない場合、図 1 (B) のように、定電流回路に流れる電流 I o u t の交流成分 i o u t は、次式 (2) で表される。

[0015]

【数2】

$$i_{out} = v_g g_m \cdots (2)$$

### [0016]

「交流成分」は小信号振幅の入出力を記述したものであるから、「電流の変化分」「電圧の変化分」と言い換えてもよい。式(1)及び(2)を比べると、ゲート電圧Vgの変動に対しての定電流回路に流れる電流Ioutの交流成分iout、すなわちゲート電位Vgの変動は、式(1)でソース抵抗Rsが大きいほど、小さい事がわかる。このようにソース抵抗Rsを有する定電流回路は、その抵抗Rsがない場合と比較して、ゲート電位Vg、グランド電位の変動に対して流れる電流Ioutの変動が少ない、という利点がある。式(1)の定電流回路の考え方を固体撮像装置に適用した場合の第1の実施形態を、図2に示す。

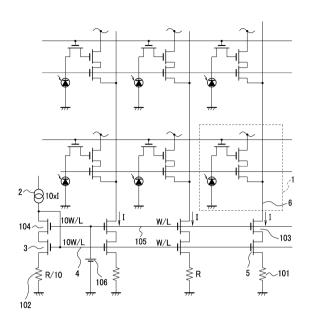

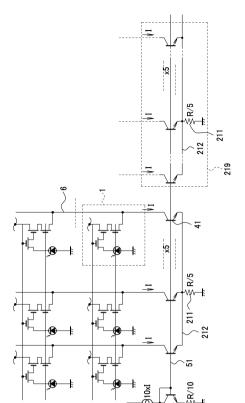

#### [0017]

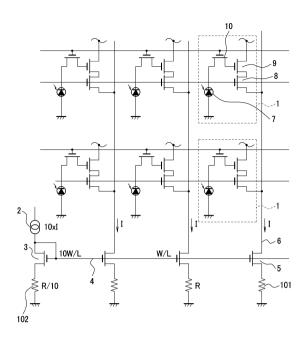

図2は、本発明の第1の実施形態の固体撮像装置の画素領域と、画素領域の画素列方向に延在する垂直信号線に接続されている定電流源を示している。説明の便宜上、複数の画素1は2列×3行分だけを記載しているが、実際の固体撮像装置では列数及び行数は数百から数千を数える。また、固体撮像装置は、図2に記載された回路以外に、垂直信号線から出力された信号を増幅する回路、共通の水平出力線へ転送する回路、垂直水平方向に信号を走査する回路などを有する。

10

20

40

30

20

30

40

50

#### [0018]

複数の画素1は、2次元行列状に配列される。画素1の内部において、7は光電変換を 行う光電変換素子(フォトダイオード)、8は行選択MOSトランジスタ、9は画素ソー スフォロワMOSトランジスタ、10は画素電荷を転送するMOSトランジスタである。 光電変換素子7は、光電変換により信号を生成する。MOSトランジスタ10は、光電変 換素子7により生成された信号をMOSトランジスタ9のゲート端子に転送する。行選択 MOSトランジスタ8が列方向に一斉にオンすると、ソースフォロワMOSトランジスタ 9のゲート電位に応じた出力が垂直信号線6に現われる。複数の垂直信号線6は、複数の 画素1の列毎に、各列の画素1に接続され、複数の画素1の信号が出力される。その際の 駆動電流をIとする。第1の定電流源2を流れる電流は、駆動電流Iの10倍の電流10 ×Iである。第2のトランジスタ3は、定電流源を構成するN型MOSトランジスタであ る。4は定電流バイアス線である。第1のトランジスタ5は、各画素1に対応した定電流 動作を行うN型MOSトランジスタである。N型MOSトランジスタ3及び5はカレント ミラー回路を構成しており、画素1の垂直信号線6に流れる電流は第2のトランジスタ3 と第1のトランジスタ5のサイズ比で決定される。この場合、サイズ比は10:1である ので、第1の定電流源2の1/10の電流Ⅰが第1のトランジスタ5に流れ、各画素ソー スフォロワMOSトランジスタ9に相当するソースフォロワの駆動電流となる。

#### [0019]

第1の定電流回路は、第1のトランジスタ5及び第1の抵抗101を有し、垂直信号線6に定電流Iを流す。第1のトランジスタ5は、ドレインが垂直信号線6に接続される。第1の抵抗101は、第1のトランジスタ5のソース端子と基準電位ノード(グランド電位ノード)との間に接続される。第2の定電流回路は、第1の定電流源2、第2のトランジスタ3及び第2の抵抗102を有し、定電流を流す。第2のトランジスタ3は、ゲート端子が第1のトランジスタ5のゲート端子に接続される。第2の抵抗102は、第2のトランジスタ3のソース端子と基準電位ノードとの間に接続される。第1の定電流源2は、第2のトランジスタ3のドレイン端子及びゲート端子に接続される。

### [0020]

ここで、第1の抵抗101は、本実施形態の特徴であるソース端子に付加されたソース抵抗であり、第2の102はそれに対応する定電流源部分のソース端子に接続されたソース抵抗である。第1の抵抗101は、第1のトランジスタ5のソース端子及び基準電位ノード間に接続されるソース抵抗である。第2の抵抗102は、第2のトランジスタ3のソース端子及び基準電位ノード間に接続されるソース抵抗である。抵抗102,101を付加した場合でも、カレントミラー回路のミラー性は成立し、ミラー比は流れる電流のの抵抗102及び101の抵抗比は、第2の抵抗102の抵抗値:第1の抵抗101の抵抗値:第1のに設定する。すなわち、第2のトランジスタ(第1の定電流回路)5を流れる電流は、第1のトランジスタ(第1のの値の1/M倍である。これは、第2のトランジスタ3及び第1のトランジスタ5のソース電位を同一にし、N型MOSトランジスタ3、5のソース及びドレイン間電圧を同一にするためである。第1の抵抗101と第2の抵抗102の比は上記のように、カレントミラー比の逆数にするのが望ましい。この値にずれがあっても、ゲート電位Vgが変動した時の電流変動を小さくする効果は依然としてある。

### [0021]

第1の抵抗101の抵抗値は、垂直信号線6に接続される基準電位線(グランド線)が列方向に延在することにより生じる配線抵抗の値より充分大きいことが必要である。グランド線の列方向の抵抗値は、固体撮像装置の画素数、画素領域の寸法、設計により異なるが、例えば、配線抵抗が1k であれば、第1の抵抗101は10k ~100k 程度が望ましい。垂直信号線6を流れる定電流Iの大きさも、第1の抵抗101の値に影響を与える。例えば、垂直信号線6を流れる定電流Iは5μA~20μAであるが、この電流Iと第1の抵抗101の値の積で計算される電圧値が0.2V程度を超えないことが望ま

しい。何故なら、画素1の回路の電源電圧が2.5~5.0 Vであるのに対して、第1の抵抗101の両端の電位降下が0.2 V程度以上あると、回路の信号振幅に影響が出始めるからである。

[0022]

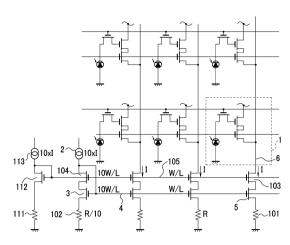

(第2の実施形態)

図3は、本発明の第2の実施形態の固体撮像装置であり、第1の実施形態と同じく、画 素領域と垂直信号線6の定電流回路の一部を示したものである。図中、参照符号1、2、 4、5、6は、第1の実施形態と同じであるので説明を割愛する。本実施形態では、定電 流回路を構成する駆動トランジスタをバイポーラトランジスタとしている。第1の定電流 回路は、第1のトランジスタ41及び第1の抵抗111を有する。第2の定電流回路は、 第1の定電流源2、第2のトランジスタ31及び第2の抵抗112を有する。トランジス タ111及び112はバイポーラトランジスタであり、抵抗111及び112はエミッタ 抵抗である。第1のトランジスタ41は、コレクタ端子が垂直信号線6に接続される。第 1の抵抗111は、第1のトランジスタ41のエミッタ端子と基準電位ノードとの間に接 続される。第2のトランジスタ31は、ベース端子が第1のトランジスタ41のベース端 子に接続される。第2の抵抗112は、第2のトランジスタ31のエミッタ端子と基準電 位ノードとの間に接続される。第1の定電流源2は、第2のトランジスタ31のコレクタ ン端子及びゲート端子に接続される。第2のトランジスタ31及び第2の抵抗112は第 2の定電流回路を構成し、第1の定電流源2に応じて生成された電圧を、バイアス線51 を通じて第1のトランジスタ41に伝えている。トランジスタ31及び抵抗112とトラ ンジスタ41及び抵抗111はバイポーラ型のカレントミラー回路を構成し、バイポーラ トランジスタ41及び31のエミッタの面積の比率、抵抗値の比率の逆数に比例して電流 が流れる。図3においては、第1の定電流源2の電流=10×I、素子比率=10倍、で あるので垂直信号線6にはIの電流が流れる。

[0023]

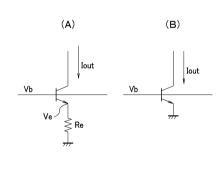

図4(A)及び(B)を用いて、エミッタ抵抗の効果を説明する。図4(A)はエミッタ抵抗Reを付加した定電流回路、図4(B)はエミッタ抵抗Reのない定電流回路である。MOSトランジスタの場合と同様に、vbはベース電位Vbの交流成分、veはエミッタ電位Veの交流成分、Eeはエミッタ抵抗、Eioutはバイポーラトランジスタの電流Ioutの交流成分である。図4(B)のエミッタ抵抗Reのない場合、電流Ioutの交流成分ioutは、次式(3)となる。ここで、Egmb=Eq/KTである。

[0024]

【数3】

$$i_{out} = g_{mb}v_b \cdots (3)$$

[0025]

また、図4(A)のエミッタ抵抗Reのある場合は、ベース電位の交流成分vbは次式(4)で表される。

[0026]

【数4】

$$v_b = v_{be} + v_e = \frac{i_{out}}{g_{out}} + R_e i_{out} \cdots (4)$$

[0027]

式(4)より、電流Ioutの交流成分ioutは、次式(5)で表される。

[0028]

10

20

30

- -

20

30

40

50

### 【数5】

$$i_{out} = \frac{v_b}{\frac{1}{g_{mb}} + R_e} \cdots (5)$$

#### [0029]

これは、式(1)と同様に、ベース電位 V b の変動がエミッタ抵抗 R e により抑制される事を表している。すなわち、バイポーラトランジスタを用いた定電流回路においても、エミッタ抵抗 R e を用いた定電流回路はバイアス線 5 1 の電位変動による電流変動を抑制するのに有用である。抵抗 1 1 1 と 1 1 2 の抵抗比率の考え方、抵抗 1 1 1 と定電流回路のグランド線の抵抗との大小関係の設計手法は第 1 の実施形態と同じである。

### [0030]

### (第3の実施形態)

図5は、本発明の第3の実施形態の固体撮像装置の回路構成図であり、参照符号1、2、4、5、6、101、102は第1の実施形態と同じであるため説明を割愛する。図中、第2のトランジスタ3は定電流源のN型MOSトランジスタであり、ゲート接地用N型MOSトランジスタ104のドレイン電極にゲート電極4が接続されている。受け側のカレントミラーも同様なゲート接地用N型MOSトランジスタ103が挿入されていることで、第1のトランジスタ5のドレイン電圧の変動が抑制され、定電流性、出力変動耐性が向上する。N型MOSトランジスタ103とN型MOSトランジスタ104ゲート幅Wは1:10の比率で構成されている。106は定電圧源であり、N型MOSトランジスタ103及び104のゲート線105を駆動する電源である。

### [0031]

以下、本実施形態が第1の実施形態と異なる点を説明する。第1の定電流回路は、第1のトランジスタ5及び第1の抵抗101の他、第3のトランジスタ103を有する。第3のトランジスタ103は、ドレイン端子が垂直信号線6に接続され、ソース端子が第1のトランジスタ5のドレイン端子に接続される。第2の定電流回路は、第1の定電流源2、第2のトランジスタ3及び第2の抵抗102の他、第4のトランジスタ104を有する。第4のトランジスタ104は、ゲート端子が第3のトランジスタ103のゲート端子に接続され、ソース端子が第2のトランジスタ3のドレイン端子に接続される。第1の定電流源2は、第2のトランジスタ3のゲート端子及び第4のトランジスタ104のドレイン端子に接続される。定電圧源106は、第4のトランジスタ104のゲート端子に接続される。

### [0032]

N型MOSトランジスタ104の役割は、画素1からの出力信号の電位が低くなり、定電流回路の駆動トランジスタのドレイン電圧が低下した時に、駆動トランジスタが3極管動作から5極管動作に遷移することで定電流性が損なわれる現象を軽減することである。本実施形態の効果である「ゲート線の電位変動による定電流回路の電流変動を抑制する効果」と類似する。しかし、本実施形態がある信号レベルでの微小な電位変動を対象としているのに対して、ゲート接地トランジスタは、垂直信号線6に現れる信号電位の大きな変動を対象としている。両者を組み合わせることで、全体として、ゲート線の電位変動に対して定電流回路がより変動しにくい回路を構成することができ、固体撮像装置の画質向上に寄与する。

### [0033]

#### (第4の実施形態)

図6は、本発明の第4の実施形態の固体撮像装置の回路構成図であり、参照符号1、2、3、4、5、6、101、102、103、104、105は第3の実施形態と同じであるため説明を割愛する。以下、本実施形態が第3の実施形態と異なる点を説明する。図5の定電圧源106は削除される。第5のトランジスタ112は、ドレイン端子が第2の

定電流源113に接続され、ゲート端子が第2の定電流源113及び第4のトランジスタ104のゲート端子に接続されるN型MOSトランジスタである。第3の抵抗111は、第5のトランジスタ112のソース端子と基準電位ノードとの間に接続される。第5のトランジスタ112は、第4のトランジスタ104のゲート接地電圧を生成するためのN型MOSトランジスタである。ゲート接地トランジスタ103のゲート電圧をN型MOSトランジスタ112で構成することで、ゲート接地電圧がN型MOSトランジスタの閾値電圧を動作が可能となる。

[0034]

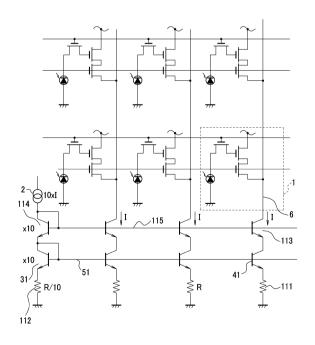

(第5の実施形態)

10

20

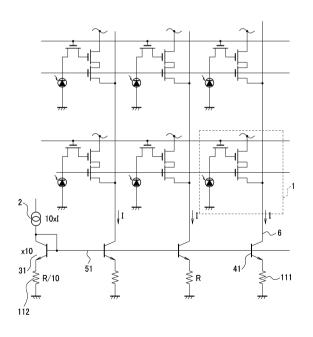

図7は、本発明の第5の実施形態の固体撮像装置の回路構成図であり、参照符号1、 - 4、5、6は第1の実施形態と同じであるため説明を割愛する。また、バイポーラトラ ンジスタ31及び41、エミッタ抵抗111及び112、バイアス線51は、第2の実施 形態と同じである。以下、本実施形態が第2の実施形態と異なる点を説明する。第1の定 電流回路は、第1のトランジスタ41及び第1の抵抗111の他、第3のトランジスタ1 13を有する。第3のトランジスタ113は、コレクタ端子が垂直信号線6に接続され、 エミッタ端子が第1のトランジスタ41のコレクタ端子に接続されるバイポーラトランジ スタである。第2の定電流回路は、第1の定電流源2、第2のトランジスタ31及び第2 の抵抗112の他、第4のトランジスタ114を有する。第4のトランジスタ114は、 ベース端子が第3のトランジスタ113のベース端子に接続され、エミッタ端子が第2の トランジスタ31のコレクタ端子に接続されるバイポーラトランジスタである。第1の定 電流源2は、第4のトランジスタ114のコレクタ端子及びベース端子に接続される。第 2 のトランジスタ 3 1 は、ベース端子及びコレクタ端子が相互に接続される。定電流生成 部にバイポーラトランジスタ114、画素定電流部にバイポーラトランジスタ113を付 加、すなわちベース接地回路を付加することでバイポーラトランジスタ41のコレクタ電 位の変動を抑制し、より安定な定電流回路を実現している。その際にも、抵抗111,1 12によりグランド線の影響を緩和、抑制し、所望の電流を得ることができる。

[0035]

(第6の実施形態)

い 30 効 お

式(1)で示す通り、定電流回路のソース側に付加した抵抗 R s の抵抗値は値が大きいほど、定電流の安定化に大きな効果が得られる。より大きな抵抗を付加した場合と同じ効果を、より小さいレイアウト面積で実現することを第6の実施形態で示す。式(1)において、式(6)とおくと、ゲート電圧 V g の交流成分 v g は、ソース抵抗 R s の電圧 V s の交流成分 v s とゲート・ソース電圧 V g s の交流成分 v g s とに分解することができる

[0036]

【数6】

$$v_g = v_{gs} + v_s \cdots (6)$$

40

【0037】

ソース抵抗Rsの電圧Vsの交流成分vsは、次式(7)で表される。

[0038]

【数7】

$$v_s = R_s i_{out} \cdots (7)$$

[0039]

また、ゲート・ソース電圧Vgsの交流成分vgsは、次式(8)で表される。

[0040]

30

40

50

【数8】

$$v_{gs} = \frac{i_{out}}{g_m} \cdots (8)$$

[0041]

図8(A)は第1~第5の実施形態で用いた定電流回路を再掲したものである。式(6)によれば、グランド及びゲート間の電位差 V g はゲート・ソース電圧 V g s とソース抵抗 R s の電圧 V s に分割されている。そのため、外乱などでゲート電位 V g が変化した際にも、1/g m に対して R s が加わったことで、電流変動が緩和される。図8(A)の様に定電流回路が複数(n個)並列に存在している場合、その全てのソース電位は V s である。これより図8(B)で示すように、複数のN型MOSトランジスタのソース同士を接続しても、その電圧関係は変化がない。これは、等価的に図8(C)と置くことができる

[0042]

すなわち、ソース電圧Vsの交流成分vsは、次式(9)で表される。

[0043]

【数9】

$$v_s = (n \cdot i_{out})(R_s / n) = R_s i_{out} \cdots (9)$$

[0044]

式(9)のように、ソース電圧Vsが保存されていれば、動作上、図8(A)と同等の効果が得られる。このようにソース抵抗Rsを有する定電流回路が複数本ある場合は抵抗Rsの部分をまとめても同様の効果がある事がわかる。その抵抗値は単独のものと比較し、統合数に反比例して小さくできる。例えば、第1の実施形態で10列分の20k の抵抗Rsを統合したとすれば、Rsが1/10の2k となり、レイアウト面積を小さくできる。

[0045]

さらに、図8(D)のように、ソース抵抗Rsを各列に割りつけて配置し、直列接続することで、各列の抵抗Rsは1/10²の200 でよい。ソース端子のバランスを考えて、中央にソース抵抗の端子を接続する図8(E)の方法も良い方法である。いずれもソース抵抗は統合列数の2乗に反比例して小さくすることができる。抵抗をまとめる際に、まとめるための配線の抵抗が、付加する抵抗より充分小さいことが必要である。固体撮像装置全列を1つにまとめる必要はなく、ひとまとめにした複数列を1つのブロックとして、このブロックを複数個配置しても構わない。

[0046]

図9は、図8で示した抵抗値の設計を固体撮像装置に適用した、本発明の第6の実施形態である。図中、201は統合されたソース抵抗であり、202は共通ソース電極であり、211は統合された定電流プロックである。第1のトランジスタ5は、5個毎に相互にソース端子が接続される。相互に接続されたソース端子は、共通ソース電極202に接続される。第1の抵抗201は、共通ソース電極202と基準電位ノードとの間に接続される。本実施形態では、全列を5列毎に分割して定電流を統合しているが、定電流回路の第2のトランジスタ3及び第2の抵抗102に対して整合の取れたものであれば、その数は適宜選択可能である。第1のトランジスタ5の大きさは第1、第3及び第4の実施形態の同じくW/Lである。しかし、ソース抵抗201はR/5となり、第1~3の実施形態の1/5の値である。これは、ソース電極202の電位が第2のトランジスタ3のソース電位と同一とするためである。

[0047]

すなわち、第2のトランジスタ3のソース電位は、次式(10)で表される。

20

30

40

50

【 0 0 4 8 】 【数 1 0 】

$$10I \bullet \frac{R}{10} = IR \cdots (10)$$

[0049]

また、抵抗201には、5個の第1のトランジスタ5から5×Iの電流が流れるため、 ソース電位をIRとするには、ソース抵抗201は、次式(11)で表され、前述のよう に統合数に反比例して抵抗値を小さくできる。

[0050]

【数11】

$$\frac{I \bullet R}{5I} = \frac{R}{5} \cdots (11)$$

[0051]

例えば、通常、外乱、変動に耐性のあるソース抵抗での電位は 0 . 2 V以上である、とすると、図中、 I は 1 0 μ A 程度とすると、ソース抵抗 2 0 1 は 4 k である。

[0052]

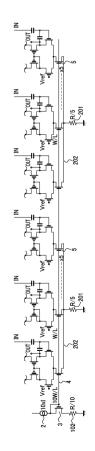

(第7の実施形態)

図10は、本発明の第7の実施形態の固体撮像装置の回路構成図であり、図5に対し、第6の実施形態を適用したものである。第1のトランジスタ5は、5個毎に相互にソース端子が接続される。相互に接続されたソース端子は、共通ソース電極202に接続される。第1の抵抗201は、共通ソース電極202と基準電位ノードとの間に接続される。ゲート接地電圧源106及びゲート接地電流源N型MOSトランジスタ104で生成されたバイアスをN型MOSトランジスタ103にて受け、各定電流性を向上させている。

[0053]

(第8の実施形態)

図11は、本発明の第8の実施形態の固体撮像装置の回路構成図であり、図6に対し、第6の実施形態を適用したものである。第1のトランジスタ5は、5個毎に相互にソース端子が接続される。相互に接続されたソース端子は、共通ソース電極202に接続される。第1の抵抗201は、共通ソース電極202と基準電位ノードとの間に接続される。電圧生成部は、図6と同様に、定電流源113、N型MOSトランジスタ112及びソース抵抗111により構成される。この様な回路構成にすることで、閾値変動、温度変動などの各変動に対し、耐性が向上する。

[0054]

(第9の実施形態)

図12は、本発明の第9の実施形態の固体撮像装置の回路構成であり、図10に対し、別なゲート接地回路の電圧生成部を追加したものである。図7と同様に、N型MOSトランジスタ3及び104は、それぞれ、ドレイン及びゲートが相互に接続される。第1の定電流回路は、第1のトランジスタ5及び第1の抵抗201の他、第3のトランジスタ103は、ドレイン端子が垂直信号線6に接続され、ソース端子が第1のトランジスタ5のドレイン端子に接続されるN型MOSトランジスタである。第2の定電流回路は、第1の定電流源2、第2のトランジスタ3及び第2の抵抗102の他、第4のトランジスタ104を有する。第4のトランジスタ104は、ゲート端子が第3のトランジスタ103のゲート端子に接続され、ソース端子が第2のトランジスタ3のドレイン端子に接続されるN型MOSトランジスタである。第1のアランジスタ5は、ゲート端子及びドレイン端子が相互に接続される。第1のトランジスタ5は、ゲート端子及びドレイン端子が相互に接続される。第1のトランジスタ5は、

5個毎に相互にソース端子が接続される。相互に接続されたソース端子は、共通ソース電極 2 0 2 に接続される。第 1 の抵抗 2 0 1 は、共通ソース電極 2 0 2 と基準電位ノードとの間に接続される。本実施形態は、第 8 の実施形態に比べ、動作する電圧範囲は狭くなるが、電流源での消費電流が小さくなる。

### [0055]

#### (第10の実施形態)

図13は、本発明の第10の実施形態の固体撮像装置の回路構成図であり、図3に対応する。定電流回路がバイポーラトランジスタ31及び41の場合でも、エミッタ抵抗211を統合することで、小さな抵抗値で大きな効果が得られる。図中、参照符号2、31、51、112、41、6は、第2の実施形態と同一であり、説明を割愛する。第1のトランジスタ41は、5個毎に相互にエミッタ端子が接続される。相互に接続されたエミッタ端子は、共通エミッタ電極212に接続される。第1の抵抗211は、共通エミッタ電極212と基準電位ノードとの間に接続される。定電流ブロック219で5系統の統合にい、バイポーラトランジスタ41のエミッタを共通エミッタ電極212で共通化する。共通エミッタ電極212で共通化する。共通エミッタ電極212で共通化する。共通エミッタ電極212で共通化する。共通エミッタ電極212で共通化する。共通エミッタ電極212で共通化する。共のエミッタ抵抗の1/5である。バイポーラトランジスタの場合はエミッタ電位が0.1 Vもあれば十分にその抑圧効果がある。そのため、垂直信号線6に流れる電流Iが同様に10µAとすると、エミッタ抵抗の抵抗値Reは、統合なしの場合はRe=10k 、統合した場合はRe(211)=2k である。

### [0056]

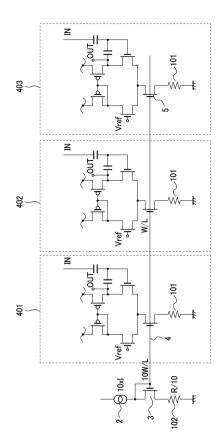

#### (第11の実施形態)

第1~第11の実施形態は全て画素ソースフォロワの負荷の定電流に関してであったが、配列したオペアンプなどにも適用できる。図14は、本発明の第11の実施形態の1次元又は2次元に配列されたオペアンプ401~403を有する固体撮像装置の回路構成図である。図中、401、402、403は、1次元に配列されたオペアンプである。オペアンプ401~403の入力端子INは、それぞれ図2の複数の垂直信号線6に接続される。

### [0057]

図2のように、複数の画素1は、光電変換を行う光電変換素子7を含む。オペアンプ401~403は、複数の画素1の信号を増幅する。第1の定電流回路は、第1のトランジスタ5及び第1の抵抗101を有し、オペアンプ401~403に定電流を流す。第2の定電流回路は、第1のトランジスタ5及び第2の抵抗102を有し、定電流を流す。第1のトランジスタ5は、ドレイン端子がオペアンプ401~403に接続されるN型MOSトランジスタである。第1の抵抗101は、第1のトランジスタ5のソース端子と基準電位ノードとの間に接続される。第2のトランジスタ3は、ゲート端子が第1のトランジスタ5のゲート端子に接続されるN型MOSトランジスタである。第2の抵抗102は、第2のトランジスタ3のソース端子と基準電位ノードとの間に接続される。第1の定電流源2は、第2のトランジスタ3のドレイン端子及びゲート端子に接続される。第1の定電流源2は、第2のトランジスタ3のドレイン端子及びゲート端子に接続される。第2のトランジスタ(第2の定電流回路)3を流れる電流は、第1のトランジスタ(第1の定電流回路)5を流れる電流のM倍であり、第2の抵抗102の値は、第1の抵抗101の値の1/M倍である。

#### [0058]

複数の第1のトランジスタ5及び第1の抵抗101は、オペアンプ401~403の動作電流を流す定電流回路である。2は定電流源である。第2のトランジスタ3は、第1のトランジスタ5のカレントミラーの元の10倍サイズのN型MOSトランジスタである。第2の抵抗102は、第2のトランジスタ3のソース抵抗である。第1のトランジスタ5のゲート電圧は、第1の定電流源2に応じて決まり、バイアス線4を通じて第1のトランジスタ5に伝達される。同一の回路が同一のバイアス線により駆動されている場合、その揺らぎが同時刻に発生し、線状のキズとなる場合があり、画像上好ましくない。本実施形態を用いると、その揺らぎが、大きく抑圧され、線キズが軽微となる。

10

20

30

40

#### [0059]

### (第12の実施形態)

図15は、本発明の第12の実施形態の固体撮像装置の回路構成図である。本実施形態は、第11の実施形態でのオペアンプの定電流回路を5個統合した実施形態である。第1のトランジスタ5は、5個毎に相互にソース端子が接続される。相互に接続されたソース端子は、共通ソース電極202に接続される。第1の抵抗201は、共通ソース電極202と基準電位ノードとの間に接続される。固体撮像装置は、各列にオペアンプを用いた増幅器を配置する場合が多く、その際には本実施形態が有効である。図中、参照符号2、3、4、102は、第12の実施形態と同一であるので説明を割愛する。図9と同様に、5個のオペアンプの定電流回路の第1のトランジスタ5のソースを共通ソース電極202により統合して共通ソース抵抗201により接地させる。これにより、比較的小さな抵抗にて大きなソース抵抗を有する定電流回路と同等の効果が得られ、画像上の線キズなどを抑制でき、良好な画像を得ることができる。

### [0060]

以上、説明したように、固体撮像装置は、CMOSセンサーなど各画素にソースフォロワを有する1次元もしくは2次元の光センサーである。本実施形態は、その定電流回路にソース抵抗を用いた定電流源を用いる事、さらにそのソース部分を接続したブロックを構成し、そこにソース抵抗を付加することにより、外乱による誘導、グランド電位の上昇に対する耐性を向上する事が出来る。これにより、横筋などの画像の不安定を抑圧する事が出来、より良い画像を得る事が出来る。すなわち、垂直信号線6の定電流回路のゲートバイアス線5が電磁誘導などの外乱によって電位変動しにくくなり、定電流回路のグランド電位の上昇によって駆動電流が変動することを抑制する事が出来る。その結果、固体撮像装置が取得する画像のシェーディング、横筋発生などの課題を軽減する事が出来る。

#### [ 0 0 6 1 ]

なお、第1~第12の実施形態において、トランジスタはMOSトランジスタであっても、バイポーラトランジスタであってもよい。その場合、MOSトランジスタのゲート端子、ドレイン端子及びソース端子は、それぞれバイポーラトランジスタのベース端子、コレクタ端子及びエミッタ端子に対応する。また、第11及び第12の実施形態のオペアンプ401~403に接続される定電流回路についても、第2~第10の実施形態を適用することができる。

### [0062]

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

### 【符号の説明】

# [0063]

1 画素、6 垂直信号線、5 第1のトランジスタ、101 第1の抵抗

10

20

【図1】 【図2】

【図3】

【図5】 【図6】

【図7】 【図8】

【図9】 【図10】

【図11】 【図12】

【図13】

【図14】

【図15】

# フロントページの続き

# (56)参考文献 米国特許出願公開第2008/0210848(US,A1)

特開平09-148853(JP,A)

特開平02-244309(JP,A)

特開平11-266399(JP,A)

米国特許出願公開第2006/0125566(US,A1)

# (58)調査した分野(Int.CI., DB名)

H04N 5/357

H04N 5/374

H04N 5/378