US 20030114075A1

### (19) United States

# (12) **Patent Application Publication** (10) **Pub. No.: US 2003/0114075 A1** Moll et al. (43) **Pub. Date: Jun. 19, 2003**

## (54) TOY VEHICLE WIRELESS CONTROL SYSTEM

(76) Inventors: Joseph T. Moll, Prospect Park, PA

(US); James M. Dickinson, Haddon

Township, NJ (US); Frank W.

Winkler, Mickleton, NJ (US); David V.

Helmlinger, Mt. Laurel, NJ (US);

Charles S. McCall, San Francisco, CA

(US); Stephen N. Weiss, Philadelphia,

Correspondence Address:

PA (US)

AKIN GUMP STRAUSS HAUER & FELD L.L.P. ONE COMMERCE SQUARE 2005 MARKET STREET, SUITE 2200 PHILADELPHIA, PA 19103-7013 (US)

(21) Appl. No.: 10/284,046

(22) Filed: Oct. 30, 2002

#### Related U.S. Application Data

(60) Provisional application No. 60/340,591, filed on Oct. 30, 2001.

#### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> | А63Н 30/04 |

|------|-----------------------|------------|

| (52) | U.S. Cl.              |            |

(57) ABSTRACT

A toy vehicle remote control transmitter unit wirelessly controls the movements of a programmable toy vehicle. The toy vehicle includes a motive chassis having a plurality of steering positions. A microprocessor in the transmitter unit emulates manual transmission operation of the toy vehicle by being in any one of a plurality of different gear states selected by an operation of manual input elements on the transmitter unit. Forward propulsion control signals representing different toy vehicle speed ratios associated with each of the gear states are transmitted from the transmitter unit to the toy vehicle. The motive chassis has a steering feedback sensor with a plurality of defined steering positions to vary rate of steering position change to avoid overshoot.

## **PWM**

FIG.2

FIG.7E

FIG.7H

FIG.7I

FIG.7J

FIG. 8D

FIG. 10B

FIG. 11

#### TOY VEHICLE WIRELESS CONTROL SYSTEM

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of U.S. Provisional Application No. 60/340,591, filed Oct. 30, 2001, entitled "Toy Vehicle Wireless Control System," which is incorporated herein by reference in its entirety.

#### BACKGROUND OF THE INVENTION

[0002] This invention relates to toy vehicles and, in particular, to remotely controlled, motorized toy vehicles.

#### SUMMARY OF THE INVENTION

[0003] The invention is in a toy vehicle remote control transmitter unit including a housing, a plurality of manual input elements mounted on the housing for manual movement, a microprocessor in the housing operably coupled with each manual input element on the housing, and a signal transmitter operably coupled with the microprocessor to transmit wireless control signals generated by the microprocessor to a toy vehicle. The invention is characterized in that the microprocessor is configured for at least two different modes of operation. One of the modes emulates manual transmission operation of the toy vehicle by being in any one of a plurality of different gear states and transmitting through the transmitter forward propulsion control signals representing different speed ratios for each of the plurality of different gear states. The microprocessor is further configured to consecutively advance through the different gear states in response to successive manual operations of at least one of the manual input devices.

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

[0004] The following detailed description of preferred embodiments of the invention, will be better understood when read in conjunction with the appended drawings. For the purpose of illustrating the invention, there is shown in the drawings embodiments which are presently preferred. It should be understood, however, that the invention is not limited to the precise arrangements and instrumentalities shown. In the drawings:

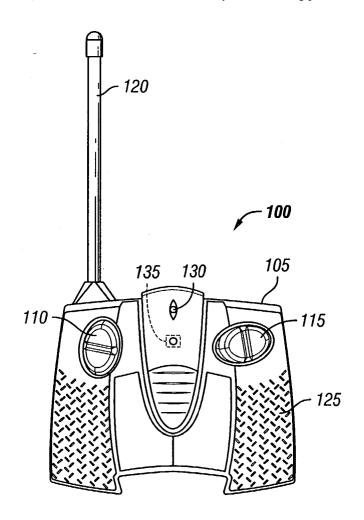

[0005] FIG. 1A is a top plan view of an exemplary remote control/transmitter used in accordance with the present invention;

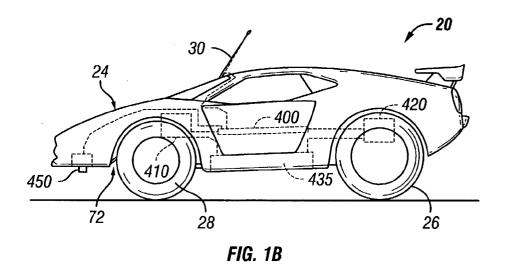

[0006] FIG. 1B is an exemplary toy vehicle remotely controlled by the remote control/transmitter of FIG. 1A;

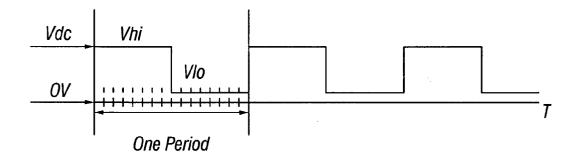

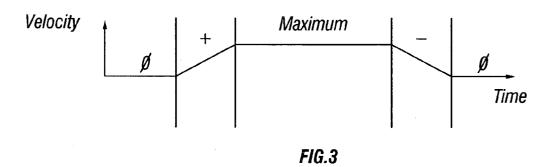

[0007] FIG. 2 is a timing diagram showing an analog output of a control circuit used to drive different motor speeds of the toy vehicle of FIG. 1B in accordance with a preferred embodiment of the present invention;

[0008] FIG. 3 is a diagram showing a trapezoidal velocity profile of a steering function of the toy vehicle of FIG. 1B;

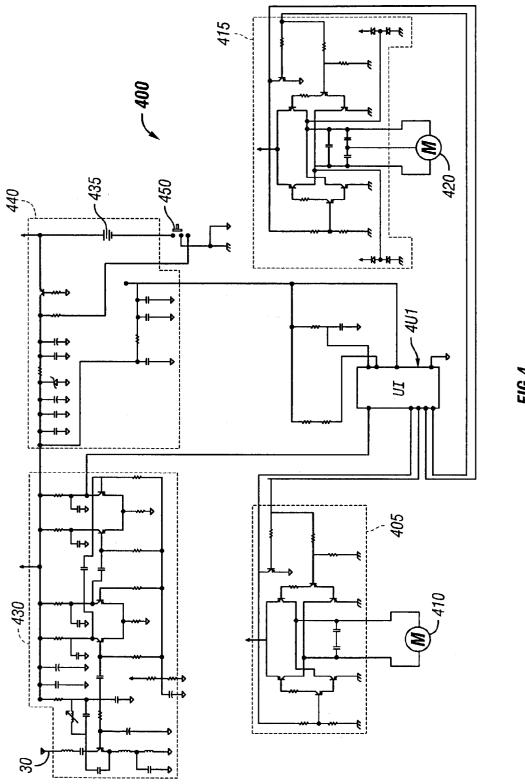

[0009] FIG. 4 is a schematic diagram of a control circuit in the toy vehicle of FIG. 1B, which is directly responsive to steering commands received in accordance with the present invention;

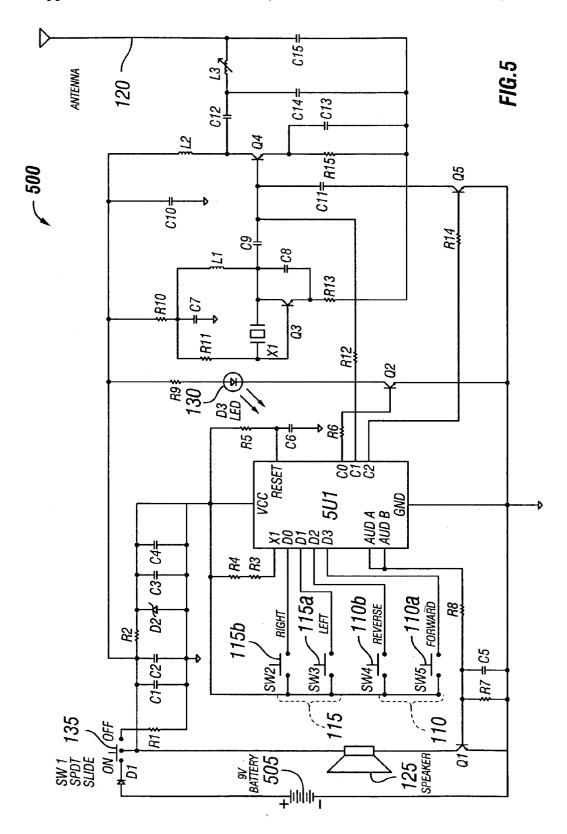

[0010] FIG. 5 is a schematic diagram of a speed shifter remote control/transmitter circuit which sends steering commands to the control circuit of FIG. 4:

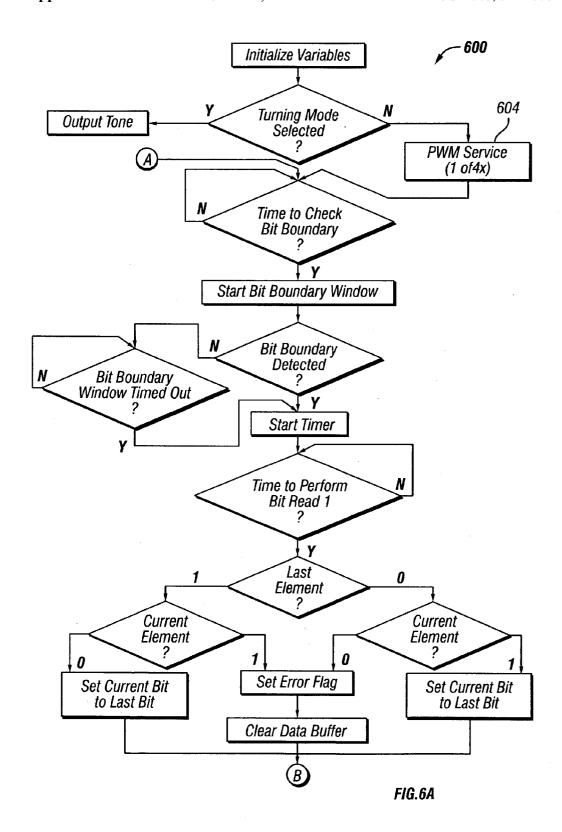

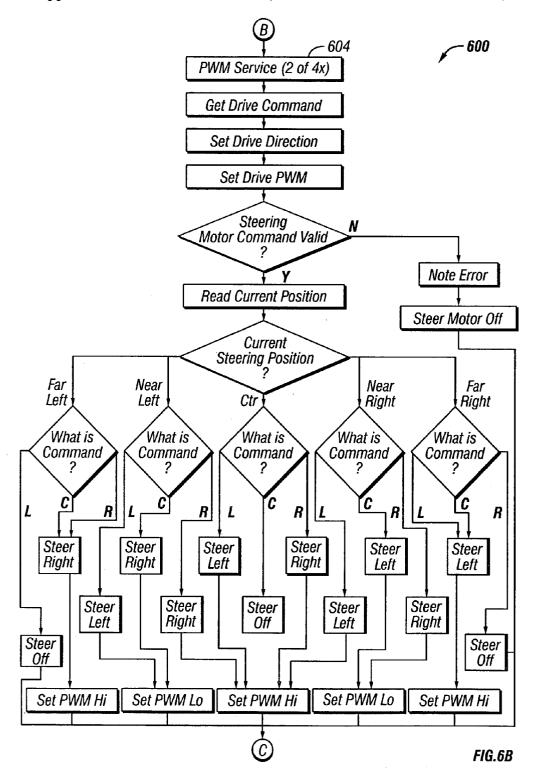

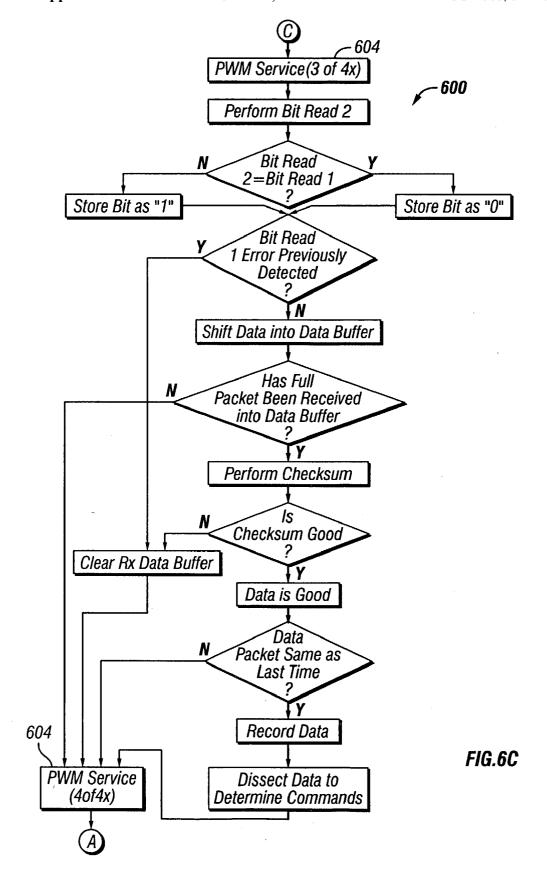

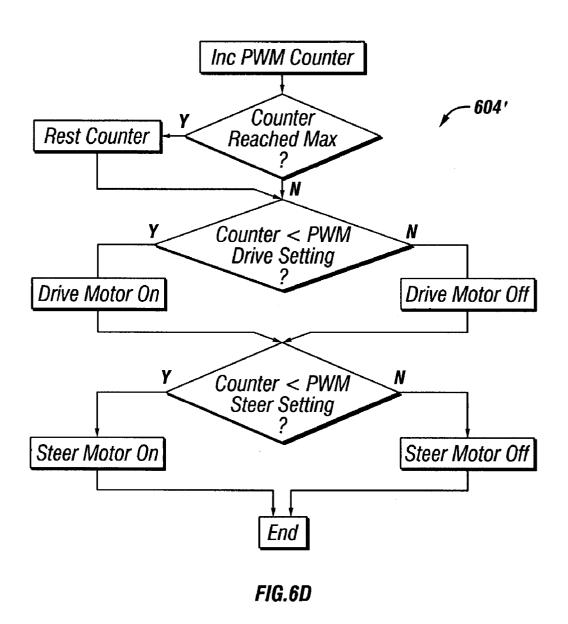

[0011] FIGS. 6A, 6B, 6C and 6D, taken together, is a flow chart illustrating the operation of the vehicle control circuit of FIG. 4;

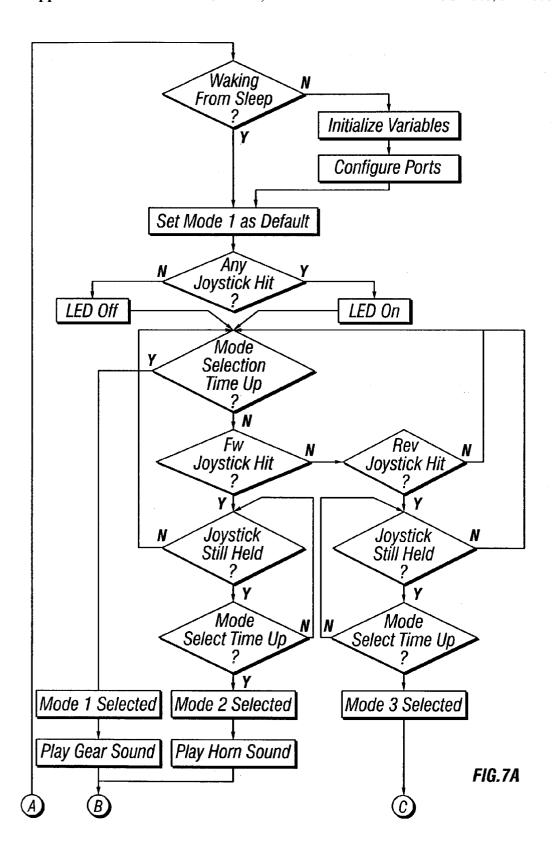

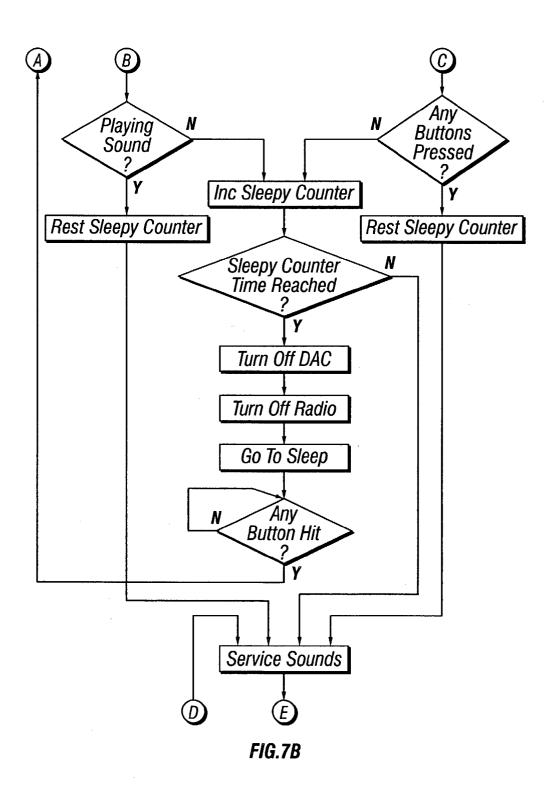

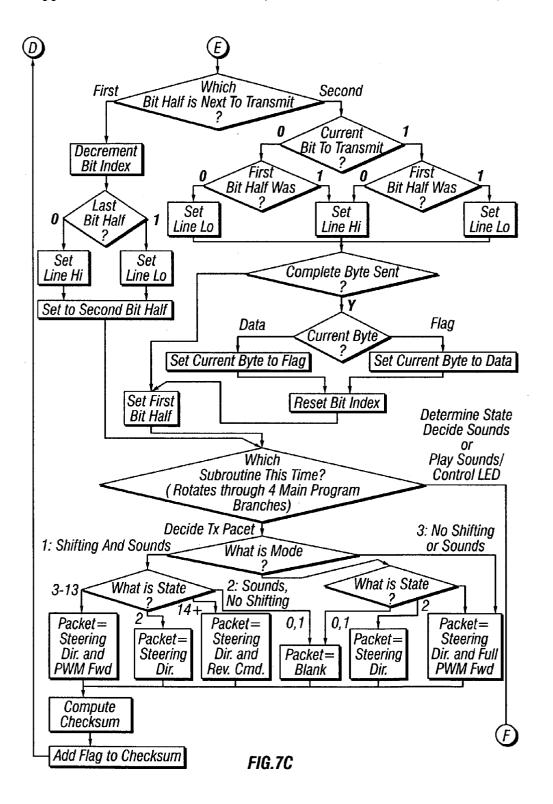

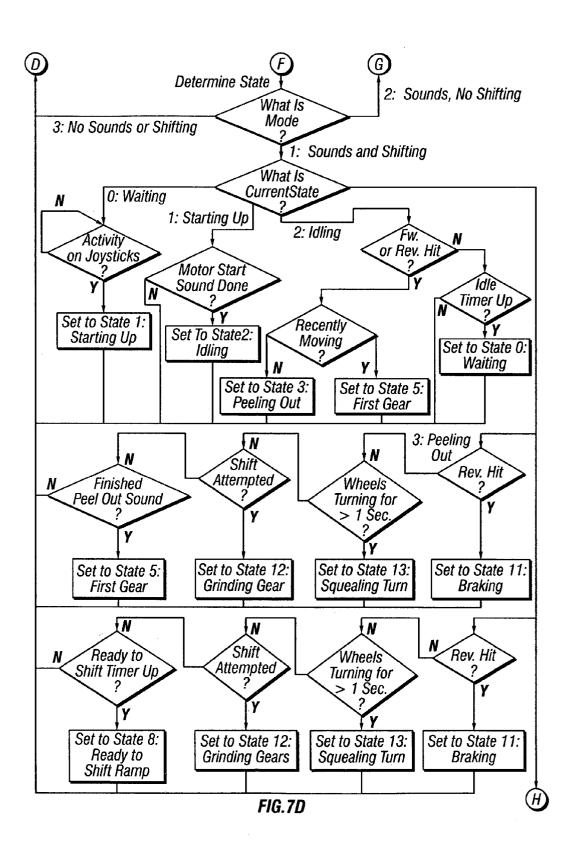

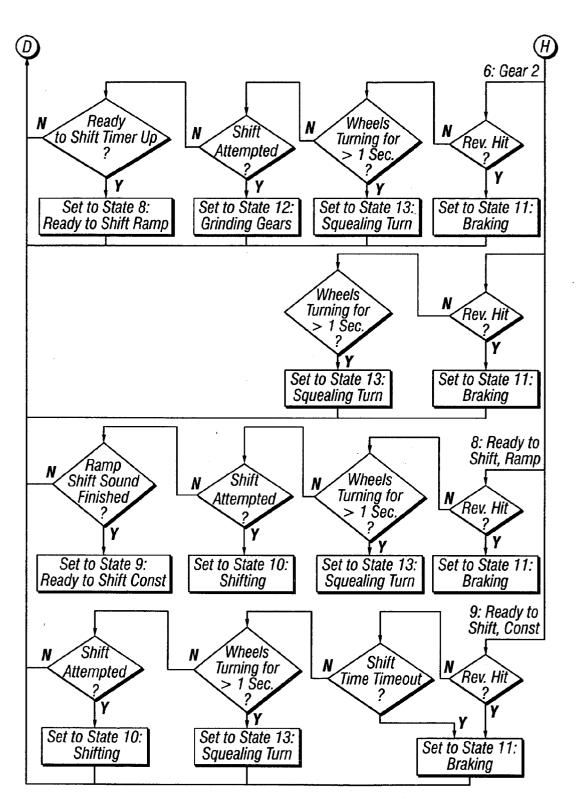

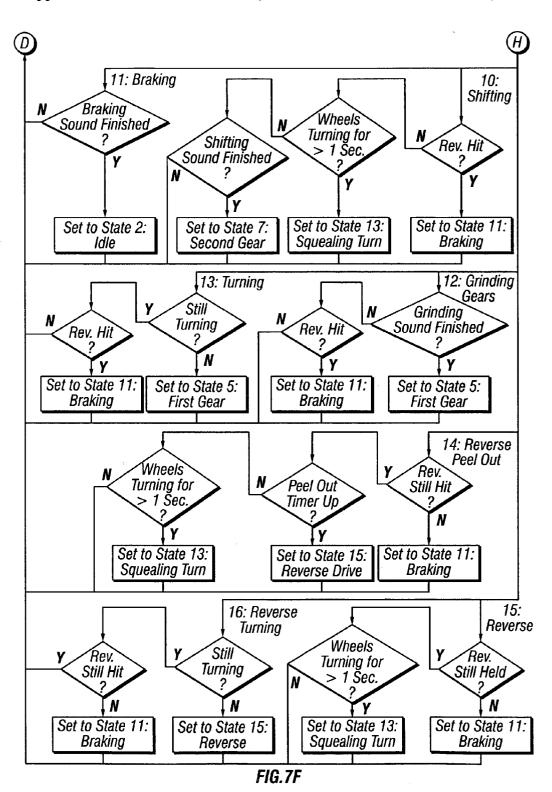

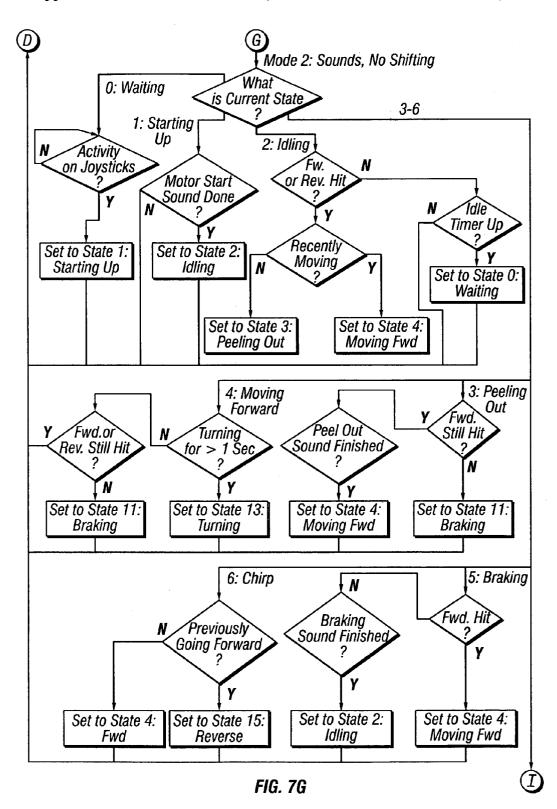

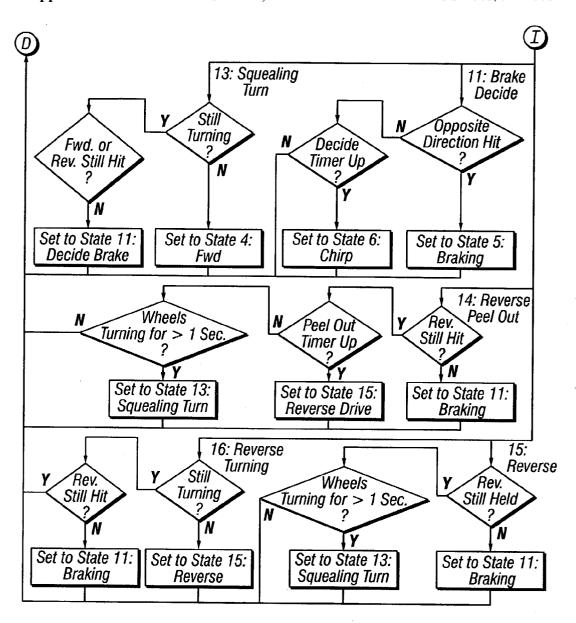

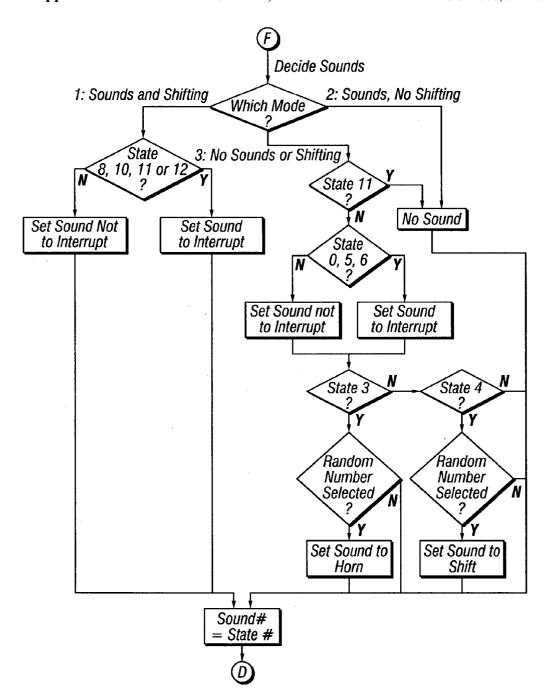

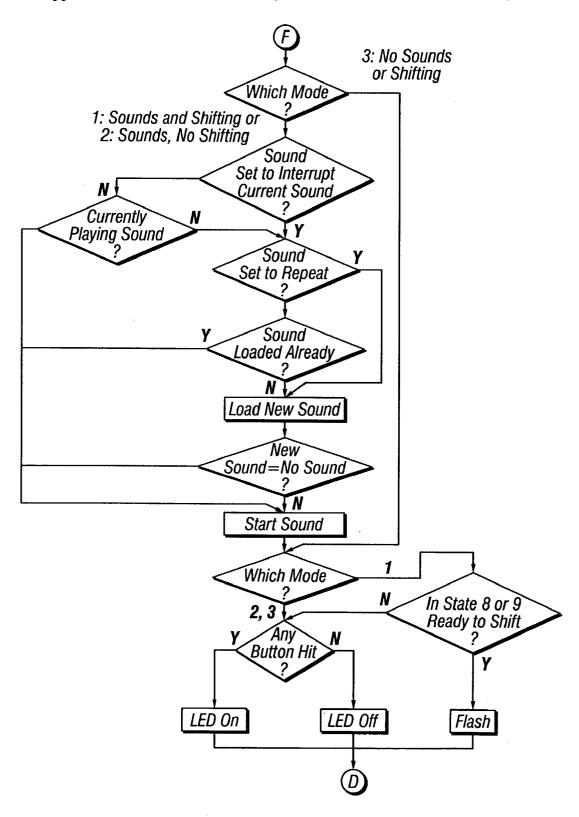

[0012] FIGS. 7A, 7B, 7C, 7D, 7E, 7F, 7G, 7H, 7I and 7J, taken together, is a flow chart illustrating the operation of the speed shifter remote control/transmitter circuit of FIG. 5;

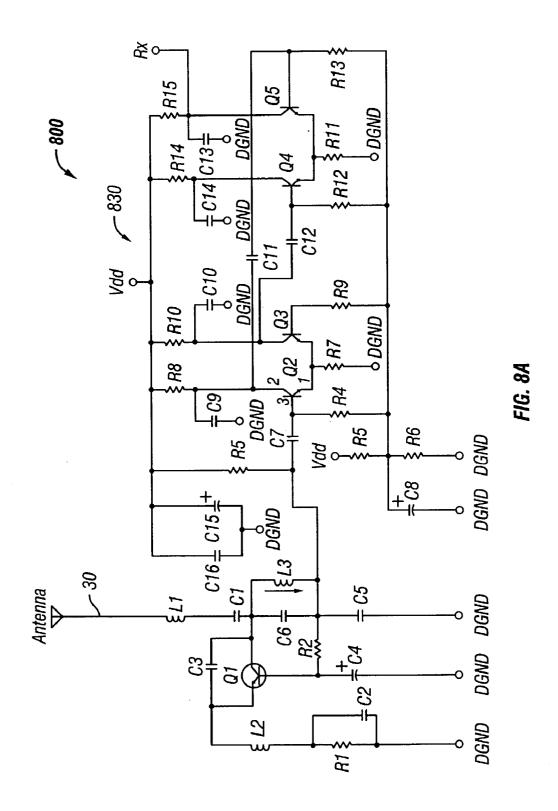

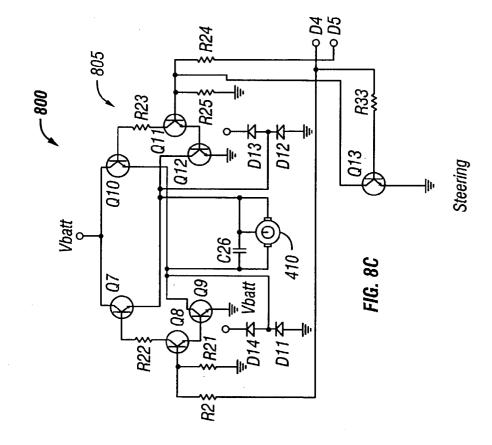

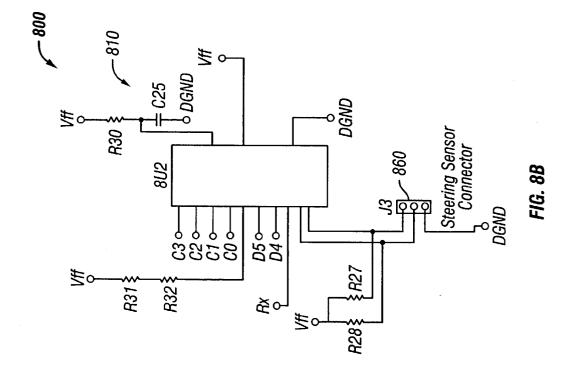

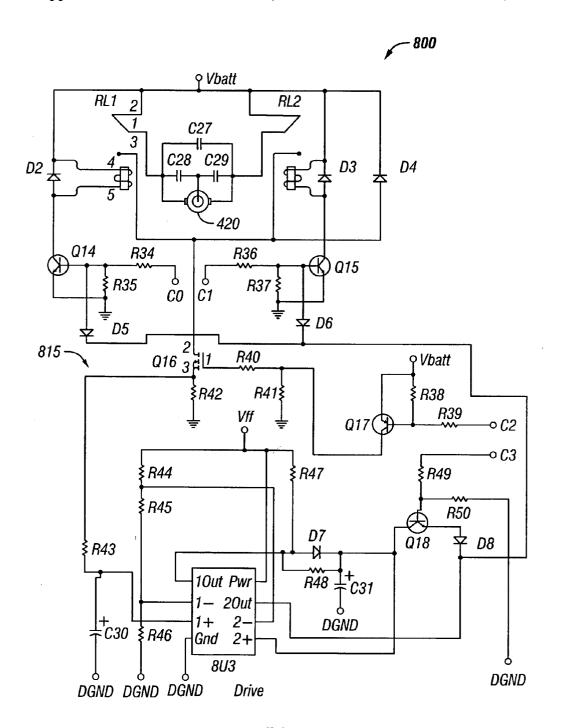

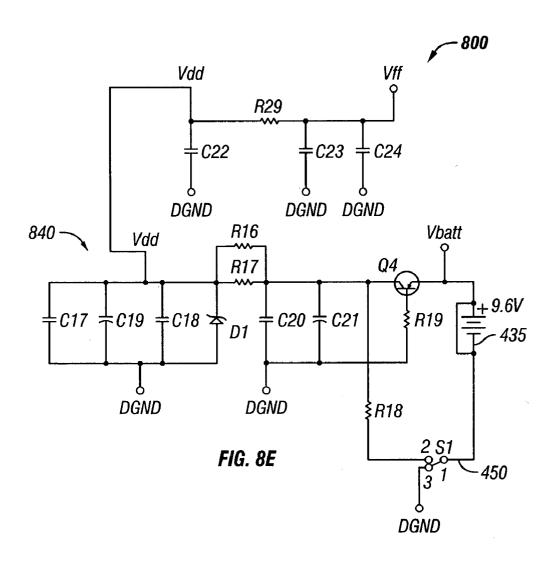

[0013] FIGS. 8A, 8B, 8C, 8D and 8E, taken together, is a schematic diagram of a toy vehicle control circuit which processes received steering commands based on current steering position of the toy vehicle in accordance with an alternate embodiment of the present invention;

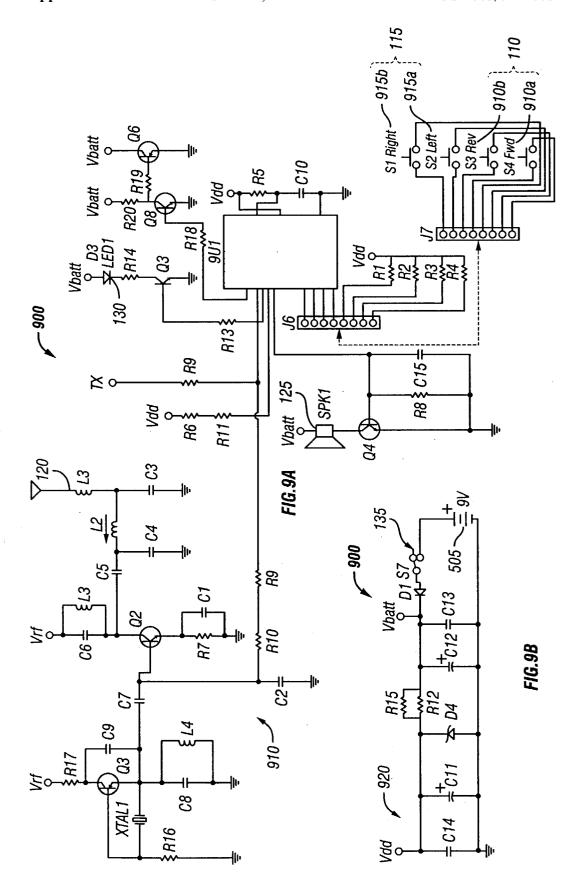

[0014] FIGS. 9A and 9B, taken together, is a schematic diagram of a speed shifter remote control/transmitter circuit in accordance with an alternate embodiment of the present invention;

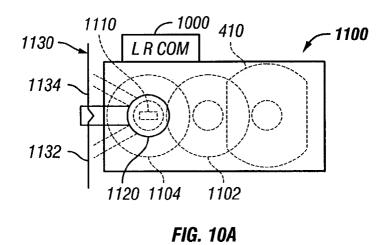

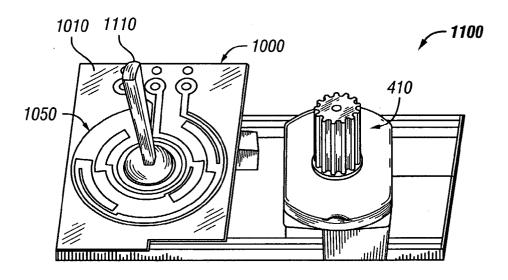

[0015] FIG. 10A depicts a steering output assembly;

[0016] FIG. 10B depicts the assembly of FIG. 10A with the output member and reduction gearing removed; and

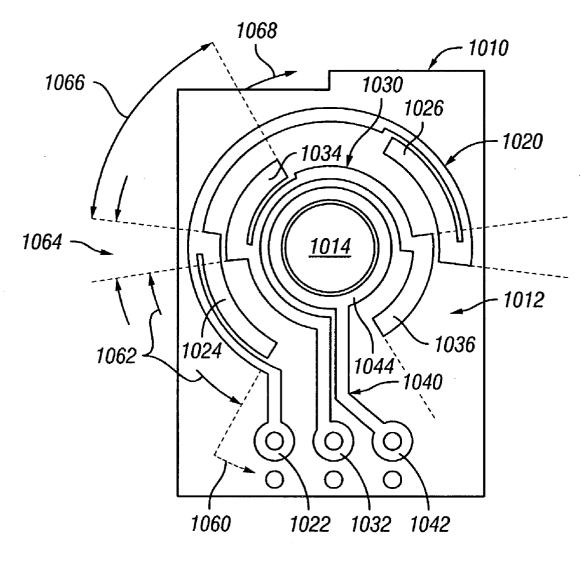

[0017] FIG. 11 depicts the stationary portion or contact member of a steering sensor.

## DETAILED DESCRIPTION OF THE INVENTION

[0018] Related U.S. Application No. 60/340,591 filed Oct. 30, 2001 is incorporated by reference herein. The present invention is a toy vehicle wireless control system which includes a remote control/transmitter 100 (FIG. 1A) with a speed shifter remote control/transmitter circuit 500 (see FIG. 5) or 900 (see FIGS. 9A, 9B), and a remotely controlled toy vehicle 20 (FIG. 1B) with a receiver/microprocessor based toy vehicle control circuit 400 (see FIG. 4) or 900 (see FIGS. 9A-9E), also hereinafter referred to as a speed shifter receiver circuit.

[0019] The remote control/transmitter 100 depicted in FIG. 1A includes a housing 105 and a plurality of manual input elements 110, 115 mounted on housing 105 and used for controlling the manual movement of a toy vehicle 20. The manual input elements 110, 115 are conventionally used to supply propulsion or movement commands and steering commands, respectively. They also enable selection among three different modes of operation or usage (hereinafter referred to as "Mode 1," "Mode 2," and "Mode 3"), each having a different play pattern. Power is selectively provided to circuitry in the remote control/transmitter 100 via ON/OFF switch 135 (in phantom in FIG. 1A).

[0020] Car 20 is shown in FIG. 1B and includes a chassis 22, body 24, rear drive wheels 26 operably coupled to drive/propulsion motor 420 (phantom) and front free rotating wheels 28 operably coupled with steering motor 410 (phantom). An antenna 30 receives command signals from remote control/transmitter 10 and carries those signals to the vehicle control circuit 400 (phantom) or 800 (not shown in FIG. 1B). An on-off switch 450 turns the circuit 400 on and off, and a battery power supply 435 provides power to the circuit 400 and motors 410, 420.

[0021] FIG. 4 shows a schematic diagram of a vehicle control circuit 400 in the toy vehicle 20. The vehicle control circuit 400 includes a steering motor control circuit 405 which controls steering motor 410, and a propulsion motor control circuit 415 which controls drive motor 420. Microprocessor 4U1 is in communication with steering motor and drive motor control circuits 405, 415, and controls all other functions executed within the toy vehicle 20. A vehicle receiver circuit 430 receives control signals sent by remote control/transmitter 100 and amplifies and sends the control signals to microprocessor 4U1 for processing. A power supply circuit 440 powers the vehicle control circuit 400 in toy vehicle 20 and the steering and propulsion motors 410, 420, respectively.

[0022] FIG. 5 shows a transmitter circuit 500 in the remote control/transmitter 100 (see FIG. 1A) that is powered by a battery 505 in communication with a two-position switch 135 that is used to turn the device 100 on and off and for selecting one of the modes. The transmitter circuit 500 also includes a microprocessor 5U1. The microprocessor 5U1 is operably coupled with each of the manual input elements 110, 115. The remote control/transmitter 100 must first be turned off via switch 135 to change the mode used. Manual input element 110 is preferably a center biased rocker button operating momentary contact switches 110a and 110b, as shown in FIG. 5. When pressed, the manual input element 110 causes one of contact switches 110a and 110b to change states. This is sensed by the microprocessor 5U1 which responds by transmitting a signal via antenna 120 to cause remotely controlled toy vehicle 20, which includes receiver/microprocessor 4U1, to move forward or backward. Manual input element 115 is also preferably a center biased rocker button operating momentary contact switches 115a and 115b in FIG. 5 which, when pressed, causes the remote control/transmitter 100 to transmit via antenna 120 a command to receiver/microprocessor 4U1 causing the toy vehicle 20 to steer to the left or to the right. When manual input element 115 is not pressed (i.e. in center position), the toy vehicle 20 travels in a straight path. When the manual input element 110 is not pressed, the vehicle 20 stons.

[0023] Mode 1, a first mode of operation or usage, is the default mode achieved when the remote control/transmitter 100 is activated from a deactivated state by moving on-off switch 135 in FIG. 5 from an "off" position to an "on" position. This mode has a multiple-speed (3-speed in the present embodiment) manual gear-shifting play pattern in which the microprocessor 5U1 emulates a manual transmission operation of the toy vehicle 20 and in which corresponding sounds are generated by the microprocessor 5U1 and played on a speaker 125 in the remote control/transmitter 100. Mode 1 has the following features and characteristics:

[0024] (1) The motionless toy vehicle 20 is put into motion by pressing manual input element 110 to a "forward" button position, closing or otherwise changing the nominal state of switch 110a on the remote control/transmitter 100. The microprocessor 5U1 is configured (i.e., programmed) to respond to the depressions of manual input element 110 by entering a first gear state of operation and generating a first forward movement command signal transmitted to the toy vehicle 20. Initially, the toy vehicle 20 responds to the first signal and moves forward at a first top speed which is less

than a maximum speed the toy vehicle 20 is capable of running. The microprocessor 5U1 generates a first sound, which is outputted by speaker 125, to simulate first gear operation of the toy vehicle 20.

[0025] (2) Once the toy vehicle 20 is moving forward for a while in a first gear state (as timed by microprocessor 5U1), a visual indication (e.g., red flashing LED 130) and/or an audible sound (e.g., single horn beep) can be outputted by the microprocessor 5U1 from the remote control/transmitter 100 to signal to a user that it is OK to shift to the second gear. Shifting into a higher gear is performed by momentarily releasing and re-engaging the forward button position of manual input element 110, which closes switch 110a within a predetermined time window. If the time window elapses, the toy vehicle 20 will return to first gear state when the forward button position of manual input element 110 is activated (i.e., switch 110a is closed). Once in the second gear state, the microprocessor 4U1 commands the vehicle 20 to move forward at a second top speed that is faster than the first top speed but less than maximum speed, and preferably the microprocessor 5U1 generates a second sound which is outputted by speaker 125 to simulate second gear operation of the toy vehicle 20. Once the toy vehicle 20 is moving forward for a while in a second gear state, a visual indication (e.g., red flashing LED 130) and/or an audible sound (e.g., single horn beep) can be outputted by microprocessor 5U1 from speaker 125 of the remote control/transmitter 100 to signal to a user that it is OK to shift to the third gear. The forward button position of input element 110 closing switch 110a is again momentarily released and re-engaged within a predetermined time window. If the time window elapses, the toy vehicle 20 will return to first gear when the forward button position of manual input element 110 is activated. Once in the third gear state, the toy vehicle 20 moves forward at a third top speed that is faster than the second top speed, and preferably the microprocessor 5U1 generates a third sound that is outputted by speaker 125 to simulate third gear operation of the toy vehicle 20. The movement of the toy vehicle 20 is terminated by releasing the forward button position of manual input element 110 closing switch 110a or by pressing and then releasing reverse button position of manual input element 110 closing switch 110b.

[0026] (3) In the three-speed embodiment, preferably the top speed of the toy vehicle 20 may be 62.5% of maximum speed when in the first gear state, 75% of maximum speed when in the second gear state, and 100% of maximum speed when in the third gear state. Other ratios and/or additional ratios to provide four, five, six or more speeds can be used to simulate other car and truck shifting.

[0027] (4) If the gear state of the toy vehicle 20 is changed before the toy vehicle 20 reaches its top speed for the previous gear by momentarily releasing and re-engaging the forward button position of manual input element 110, before the microprocessor 5U1 opens the predetermined time window to shift, the microprocessor 5U1 generates a different audible sound (e.g., grinding noise), which is preferably outputted by the speaker 125 of the remote control/transmitter 100, to signal that the user shifted too early. Top speed is not increased.

[0028] (5) Various audible sounds (e.g., peel out, squealing tire, hard braking, accelerating motor, etc.) are preferably outputted by the remote control/transmitter 100 in

response to activating the manual input elements 110, 115 on the remote control/transmitter 100. For example, transmitting a steering command by causing manual input element 115 to close switch 115a while the toy vehicle 20 is moving (e.g., forward position of manual input element 110 being pressed changing the state of switch 110a) causes the microprocessor 5U1 to output an audible sound (e.g., the squealing of tires) through speaker 125. There is a small delay in producing the audible sound so that small steering corrections do not cause the audible sound to be outputted by speaker 125. Releasing either the forward and reverse position of manual input element 110 preferably causes the microprocessor 5U1 to output an audible sound (e.g., hard breaking, tire screeching) through speaker 125. An "idling" sound is then preferably outputted by microprocessor 5U1 through speaker 125 until a next propulsion/drive command is transmitted.

[0029] (6) Speed of the toy vehicle 20 is controlled by the remote control/transmitter 100 outputting propulsion control signals having PWM (Pulse Width Modulation) characteristics with duty cycles approximate for the speed ratios selected, e.g., 56%, 75%, and 100% (see FIG. 2). Preferably, the remote control/transmitter 100 outputs a binary signal with two or more values allocated to propulsion commands. Two binary bits can be used to identify stop and three forward speed values (e.g., first, second and third speeds). The vehicle microprocessor 4U1 is preferably programmed to power each motor 410, 420 according to a duty cycle identified by the binary bits. Referring to FIG. 2, a fixed time period (e.g. sixteen milliseconds) can be broken up into fractions (e.g., sixteen, one millisecond parts) and power (V hi) supplied to the motor for the fraction of the time period (e.g., %16, 10/16, 12/16, 16/16) commanded by the two binary bits. An %16 duty cycle is depicted, with V hi provided for eight parts and V low (i.e. 0 Volts) provided for the remaining eight parts of the period constituting the cycle. If three bits are allocated to propulsion commands, a stop command and seven different forward and reverse speed commands can be encoded. Preferably, reverse speed is at a ratio of less than 100% for ease of vehicle control and realism.

[0030] Mode 2 is achieved by turning on switch 135 of the remote control/transmitter 100 while holding manual input element 110 in a "forward" movement position (changing the state of switch 110a) on the remote control/transmitter 100 until the microprocessor 5U1 acknowledges the command by causing the speaker 125 to output an audible sound (e.g., horn beeps) and/or the red LED 130 to flash. This mode allows the user to maneuver the toy vehicle 20 in the usual manner with sounds being generated but no gear shifting operation. The microprocessor 5U1 is preferably preprogrammed for a desired default speed, e.g., 100% forward and 50% or 100% reverse.

[0031] Mode 3 is achieved by turning on switch 135 of the remote control/transmitter 100 while holding manual input element 110 in a "reverse" movement position (i.e. changing state of the switch 110b) on the remote control/transmitter 100 until the microprocessor 5U1 causes speaker 125 to output an audible sound (e.g., horn beeps) and/or the red LED 130 to flash. This mode allows the user to maneuver the toy vehicle 20 in the usual manner with no sound generation by microprocessor 5U1 or gear shifting operation. The microprocessor 5U1 is preprogrammed for a desired default speed, e.g., 100% forward and 50% or 100% reverse.

[0032] A "Try Me Mode" may be provided, if desired, allowing only sound effects of the remote control/transmitter 100 to be produced while still in its packaging. Sound effects are generated by pressing any button on the transmitter. Pushing the manual input element 110 to the "forward" position can cause the start-up sound to play followed by a peel-out sound with both motor and shifting sounds. Pushing the manual input element 110 to the "reverse" position can cause the horn sound to play with the motor running sound. Pushing the manual input element 15"left" and "right" can activate the squealing tire sound accompanied by the engine downshift sound. The "Try Me Mode" preferably is deactivated automatically when the toy is taken out of its packaging and a pull-tab is removed from the remote control/transmitter 100, allowing the transmitter 100 and toy vehicle 20 to be operated in one of the three modes described

[0033] FIGS. 7A-7J depict the various steps of an operating program 700 contained by the transmitter circuit 500, such as by firmware or software in the microprocessor 5U1, to operate the remote control/transmitter 100 in the multiple modes of operation and in the different shift states in the first mode of operation. Again, the microprocessor 5U1 is preferably configured to transmit commands in binary form with propulsion and/or steering commands encoded as binary bits or sets of such bits.

[0034] FIGS. 6A-6C depict the various steps of an operating program 600 contained by the vehicle control circuit 400, such as by firmware or software in the microprocessor 4U1, to operate the toy vehicle 20 in the multiple modes and in the different shift states in the first mode of operation. FIG. 6D depicts the steps of a subroutine 604' which is entered four different times at steps 604 in the main program 600 (FIGS. 6A-6C) to increment and test the state of a pulse width modulator (PWM) timer (i.e. counter) to power or turn off power to either motor 410, 420. The operating program 600 must be cycled through four times to increment the PWM counter a total of sixteen times to complete one PWM power cycle (sixteen parts) for either motor 410, 420.

[0035] FIGS. 8A-8E collectively represent a schematic diagram for a second embodiment toy vehicle control circuit indicated generally at 800 in the Figure in which FIG. 8A depicts a vehicle receiver circuit 830 which receives control signals sent by the remote control/transmitter 100 and amplifies and sends those signals to microprocessor 8U2 in FIG. 8B. Outputs D4 and D5 from the microprocessor 8U2 are sent to a steering motor control circuit 805 depicted in FIG. 8C while outputs C0-C3 are transmitted from the microprocessor 8U2 to a propulsion motor control circuit 815 depicted in FIG. 8D. Circuit element 8U3 is a dual operating amplifier chip. Power is supplied to both the steering motor 410 in FIG. 8C and drive motor 420 in FIG. 8D as well as the other components of circuit 800 via a power supply sub circuit 430 depicted in FIG. 8E which include both the ON/OFF switch and a battery powered supply 435. One difference between circuit 800 and circuit 400 is the provision of a steering feedback through connector 860 in FIG. 8B to the vehicle microprocessor 8U2. The purpose of this will be described shortly.

[0036] FIGS. 9A and 9B collectively depict a second embodiment remote control/transmitter circuit indicated generally at 900 which is shown essentially in FIG. 9A and

indicated at 910. The only missing element is a power supply circuit 920 shown in FIG. 9B which provides two outputs Vdd and Vbatt. Again, manual input elements 110 and 115 control momentary contacts switches 910a, 910b and 915a, 915b respectively. These switches are located on a board separate from the board supporting a microprocessor 9U1 and are mechanically and electrically coupled together through connectors J6 and J7.

[0037] FIG. 10A depicts part of a steering sensor indicated generally at 1000 in a steering output assembly indicated generally at 1100. Output assembly 110 includes a housing 1102 containing steering motor 410, a plurality of compound reduction gears indicated in phantom generally at 1102, 1104 driving a shaft 1110 (phantom) keyed with a rotary output member 1120 on the housing 1102. Output member 1120 rotates in an arc, moving from side to side a wire member 1130 defining a pair of steering arms 1132, 1134 operably coupled with separate ones of the pair of front wheels 28 of the vehicle 20 to pivot those wheels side to side about vertical axes in a conventional manner to steer wheel 20. FIG. 10B shows the output assembly 1100 with the gears 1102, 1104 and a top cover carrying the rotary output member 1120 removed. The left side of assembly 1100 includes steering sensor 1000 while the right side includes steering motor 420. Sensor 1000 includes a stationary member or portion, which is indicated generally at 1010 and seen separately in FIG. 11, and a rotary member or rotating portion indicated generally at 1050. The rotary member 1050 includes a plurality of connected concentric ring portions 1052, 1054, 1056 each containing one or more dimples 1052a, 1054a and 1056a, 1056b for the innermost ring. These dimples ride over the upper surface of the stationary portion 1010. Referring to FIG. 11, the stationary portion 1010 includes a circuit board 1012 on which are mounted three electrically conductive, generally concentric tracks 1020, 1030 and 1040. Each track includes an output terminal 1022, 1032, 1042, respectively on one edge of the board 1012. These three terminals connect via a suitable electrical connection (e.g. connector 860 in FIG. 8B) to microprocessor 8U2. Each track 1020, 1030, 1040 is continuous around a central opening 1014 in the circuit board 1012 through which the output shaft 1110 extends. Rotating portion 1050 is keyed with shaft 1110 to rotate with the shaft. Rotating portion 1050 is a continuous piece of electrically conductive material such as metal and electrically couples one or more of the two outer tracks 1020 and 1030 with the innermost track 1040. A high level voltage is applied by the microprocessor 8U2 through the connecter 860 to the terminals 1022 and 1032. Terminal 1042 is connected to common or ground. The contacting dimples 1056a 1056b are in constant contact with the ring portion 1044 of innermost track 1040. In contrast, dimples 1054a of ring portion 1054 only contact wiper portions 1034 and 1036 of central track 1030 at certain angular positions of rotating portion 1050. Similarly, dimples 1052a of ring 1052 only contact wiper portions 1024 and 1026 of the outermost track 1020.

[0038] Referring to FIG. 1, dimples 1052a, 1054a, 1056a, 1046b of rotating contact member 1050 come in contact with the tracks 1020, 1030, 1040 in five different steering positions (far left indicated at 1060, near left 1062, center 1064, near right 1066, far right 1068) on printed circuit board 1010 as member 1050 turns clockwise from far left to far right. When the rotating member 1050 is turned fully left or right, dimples 1052a, 1054a loose contact with tracks

1020, 1030 and logic bits "1,1" are outputted from electrical contacts 1022, 1032. When the rotating member 1050 is turned clockwise from far left to left of center 1062, logic bits "0,1" are outputted from electrical contacts 1022, 1032. When the rotating member is in the center position 1064, logic bits "0,0" are outputted from electrical contacts 1022, 1032. When the rotating member is turned to the right of center but not fully right, logic bits "1,0" are outputted from electrical contacts 1022, 1032. When fully right, logic bits "1,1" are again output from contacts 1022, 1032.

[0039] The states of electrical contacts 1022, 1032 are monitored by processor 8U2 and the speed of steering motor 410 is preferably controlled based on the outputted logic bits (i, i) which indicate the position of the front wheels 28. Normally the steering motor 410 operates at top speed (100%). However, with feedback provided by sensor 1000, the motor 410 can be operated to prevent overshoot. FIG. 3 shows a trapezoidal velocity profile of speed versus time for the steering function of a toy vehicle 20 according to a preferred embodiment of the present invention. Steering motor 410 may be controlled like propulsion motor 420 by a PWM duty cycle to prevent overshoot of the steering system. For example, the steering motor 410 may be driven by microprocessor 8U2 (or 4U1) at a higher duty cycle when going from a left or right turn to a turn in the other direction (e.g., from far left to far right) and at a lesser duty cycle when going from a center position to right or left and vice versa. When logic bits "0, 1" are detected as the rotating member 1120 turns from center position (0,0) to the left and passes the near left wipers 1024, 1026, or when logic bits "1, 0" are detected as the output member 1120 and rotary member 1050 turn to the right and pass the near right wipers 1034, 1036, the rate of the steering motor and front wheel rotation is reduced to 50% to avoid overshooting its destination (far left or far right). Preferably too, the speed of the propulsion motor 420 can further be reduced automatically by the processor 8U2 when the processor 8U2 detects that a turn of the toy vehicle 20 is in progress to automatically slow the vehicle to a speed less than maximum while making the

[0040] With a start and end point considered in a closed loop system, speed of the steering motor 410 in the toy vehicle 20 can be varied so that steering follows a trapezoidal profile as shown in FIG. 3, i.e. start from zero and reach a maximum turning rate, and then slowed to reduce its rate of rotation so that steering system momentum is dissipated and the steering system does not overshoot its target. When the command to steer to a new position is given, firmware operating in conjunction with microprocessor 8U2 (or 4U1) will identify the current steering position and move at a higher rate and duty cycle (e.g., 100% duty cycle) when the commanded steering position is more than one steering position away from (i.e., other than adjacent to) its current position. For example, in going from a left turn to a right turn through consecutive outputs (1, 1), (0, 1), (1, 1), (1, 0) to (1, 1), (1, 1), (1, 0)1), the motor 410 may be driven at high speed (100% duty cycle) until center position (0, 0) or near right (1, 0) is encountered and the motor 410 then driven at a lower speed (e.g., 50% duty cycle) until far right (1, 1) is sensed.

[0041] Steering control can be further refined if the steering function is spring centered, i.e. a single torsion spring or pair of compression or tension springs (none depicted) used to drive the rotary output member 1120 to the straight

forward position. Then the microprocessor 8U2 (or 4U1) can be configured by programming to account for action of the spring(s). For example, turning from left to right, the microprocessor 8U2 may drive at high level and low level in moving more than one steering position (e.g. left-right) or only one steering position (e.g. center left/right), respectively, from the present position and at different speeds if moving with or against a spring. For example, movement left to right or vice versa can begin at full speed (100% duty cycle) and transfer to first low speed (e.g. 50% duty cycle) from the center position (0, 0) to the far right position to drive against the centering spring in the latter part of the movement. In going from right or left to center with spring assistance, the motor 410 is operated at a second, lower speed (e.g., 37.5% duty cycle), whereas, while going from center to left or right against a spring, the motor 410 is operated at the first low speed (e.g., 50%).

[0042] A spring loaded steering function of the toy vehicle 20 may also incorporate a target pad timeout period which monitors the time it takes for the sensor 1000 to reach a particular steering position (center, near left, far left, near right, far right). If the position is not reached within a predetermined period of time, the power to the motor 410 is turned off and the spring(s) will return the steering output number 1120 to the center position. If the steering position does not return to the center position, the microprocessor 8U2 (or 4U1) is alerted that the steering is misaligned and electromechanically re-centers the steering.

[0043] Preferred transmitter code used in a remote control/transmitter 100 operating in accordance with the present invention is located on pages A-1 through A-53 of the attached Appendix incorporated by reference herein. Preferred receiver code used in a toy vehicle 20 operating in accordance with the present invention is located on pages A-54 through A-77 of the Appendix.

[0044] In addition to duty cycle control in the vehicle 20, speed control of the vehicle 20 could be performed by the remote control/transmitter 100 by duty cycle transmission of a propulsion or steering signal (i.e. transmit the signal(s) several times followed by a period with no signal) or by varying the rate at which the propulsion signal is transmitted (e.g., every 10, 15 or 20 millisecond). Of course, the microprocessor of the toy vehicle 20 would also have to be appropriately configured to operate with such a duty cycle arrangement.

[0045] It will be appreciated by those skilled in the art that changes could be made to the embodiments described above without departing from the broad inventive concept thereof. It is understood, therefore, that this invention is not limited to the particular embodiments disclosed, but it is intended to cover modifications within the spirit and scope of the present invention.

# **APPENDIX**

### **Transmitter Code**

```

.LINKLIST

.SYMBOLS

· CODE

; /**** System parameters *****

Systemclock:

EQU

2000000

SPC41A:

EQU

1

; select body (hardware.inh)

/**** sound details (ver3.42a or later)

ADPCM_TABLE_65:

_ADPCM_H_:

;If use ADPCM65 or later

EQU

\frac{1}{1}

;If no limit

EQU

.Include

Hardware.Inh

; **** Addresses SunPlus forgot *****

P_MultiPhase

EQU

$37

; register that controls Multi Phase

settings on 81A

***** CONSTANTS/DEFINES *****

sound stuff

;If CurrentDAC->00H, PWM->80H

;number of speech pieces

;number of melodies

;number of rhythms

;should be 6 for 8KHz or 0 for 6 Khz

D_RampDownValue:

EQU

00н

D_MaxWord:

EQU

16

D_MaxMelody:

EQU

1

D_MaxRhythm:

EQU

0

D_SamplePreload:

ŎОН

EOU

; my sounds

;D_Snd_Accel

EQU

01234589

D_Snd_Braking

D_Snd_Chirp

D_Snd_Dnshift

D_Snd_Eng_Strt

EQU

EQU

EQU

EQU

D_Snd_Gear

D_Snd_Grind

ΕQU

EQU

D_Snd_Horn

EOU

D_Snd_Idle

10

EQU

D_Snd_Peelout

D_Snd_Squeel

11

12

ΕQU

ΕQŪ

D_Snd_Upshift

D_Snd_Whine_C

13

14

ΕQU

EQU

D_Snd_Whine_R

D_Snd_None

ī5

ffh

EOU

EQU

; within loop timiers

; Sound Service Timers

D_TmBH_SS0

EQU

00h

```

```

Shft96Tx.ASM

; 75 uS

D_TmBL_SS0

EQU

96h

D_TmBH_SS1

EQU

D_TmBL_SS1

EQU

d0h

; 232 us

D_TmBH_SS2

EQU

D_TmBL_SS2

EQU

f6h

; 379us

D_TmBH_SS3

EQU

04h

D_TmBL_SS3

EQU

4ah

; 549us

D_TmBH_SS4

EQU

05h

D_TmBL_SS4

; 705us

EOU

82h

D_TmBH_SS5

EQU

06h

D_TmBL_SS5

ΕQU

bch

; 862uS

D_TmBH_SS6

EQU

07h

D_TmBL_SS6

ΕQU

f8h

; 1020us

D_TmBH_SS7

EQU

09h

; 1177uS

D_TmBL_SS7

EQU

32h

; only for standby horn sound ; 2 ms

D_TmBH_SS8

D_TmBL_SS8

EQU

0Fh

EQU

D5H

D_TmBH_Tx0

EQU

09h

D_TmBL_Tx0

D8h

; 1260 us

EQU

D_TmBH_Tx1

EQU

02h

D_TmBL_Tx1

EQU

76h

; 315 us

D_TMBH_Tx2

EQU

04h

; 630 us

D_TmBL_Tx2

EQU

ech -

D_TmBH_Tx3

EQU

07h

; 945 us

D_TmBL_Tx3

EQU

62h

large timers-small timer ticks each loop. (1260 uS). Large timer ticks every .32

D_Small_Squeel_Timer_Preload

D_Large_Squeel_Timer_Preload

EOU

#8ch

EOU

#01h

; 018ch = 0.5 seconds

; for prototyping a short medium or long shift time can be selected D_Small_Shift_Timer_Preload EQU #33h ; 0633=2.0 seconds D_Large_Shift_Timer_Preload EQU #06h ;

D_Small_Fwd_Release_Timer_Preload

EQU

#19h

D_Large_Fwd_Release_Timer_Preload

ΕQU

#03h

; 0319h = 1 second

D_Small_Sound_Check_Timer_Preload

EQU

#8ch

D_Large_Sound_Check_Timer_Preload

EQU

#03h

D_Small_Idle_Timer_Preload

D_Large_Idle_Timer_Preload

#80h

EQU

EQU

#2eh

; 2e80h=15 seconds

D_Small_Chirp_Timer_Preload

EQU

#c6h

00c6h = 0.25 seconds

D_Small_LED_Timer_Preload

EQU

#ffh

; ffh =.3 seconds

D_Peelout_Time

EQU

#28h

; when idle timer has gotten here

```

### shft96Tx.ASM ; 2eh-28h=2 seconds

```

; Timers which run off of interrupts (interrupts used only during mode selection); both run off of clock/65536 interrupt. For 2 Mhz clock this is 31 hz D_Mode_Check_Timeout EQU #93 ; 93=3 seconds D_Mode_Select_Time EQU #62 ; 62=seconds D_LED_Flash_Timer EQU #8

; Inputs

; buttons

D_Pin_Fwd:

D_Pin_Rev:

; PortD bit of motor pin output

00001000b

EOU

00000100b

EQU

D_Pin_Left:

D_Pin_Right:

00000010b

ΕQU

EQU

; outputs

D_Pin_Tx:

EQU

00000010b

; Port C

D_Pin_LED:

D_Pin_Tx_Enable

00000001b

EOU

ΕQŪ

00000100b

; PACKET BITS

00110000b

00001100b

00000010b

; 2 bit pwm level

; 2 bit pwm level

D_Fwd_Bits

EQU

D_Rev_Bits

D_Left_Bit

EQU

EQU

00000001b

00000011b

D_Right_Bit

EQU

D_Turns_Bit

EQU

D_PWM_Lo

D_PWM_Med

00001000b

EQU

00010000b

00011000b

EQU

EQU

D_PWM_Hi

D_TX_Flag

; mode selection

D_Mode_2_Command

D_Mode_3_Command

EQU

01111100b

; first six bits are the flag

; fw pull down

; rev pull down

00000111b

EQU

00001011b

EOU

; ***** VARIABLES *****

.PAGEO

D_RamTop

; variables used in all modes

; interrupts related

R_IntFlags:

DS

1

R_IntTemps:

R_TempA:

DS

DS

1

1

1

R_TempX:

; sound related

R_SongNo:

DS

R_Volume:

DS

11

R_Temp1:

DS

1

; sound to be played next ; sound being played

R_Next_Sound

DS

R_Current_Sound DS

R_Sounds_Array DS

R_Sound_Interrupt

1

```

| R_Sound_Repeat DS                                                                                                                                                                                                                                         | 1                                                                               |                                                                                             | Shf  | t96Tx.ASM             |           |         |           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|-----------------------|-----------|---------|-----------|

| R_Mode<br>R_Mode_Timer<br>R_Mode_Check_Timer<br>R_Command_To_Check<br>R_Mode_To_Check                                                                                                                                                                     | DS<br>DS<br>DS<br>DS<br>DS                                                      | ; m<br>1<br>1<br>1<br>1                                                                     | ode  | related<br>; 3 modes- | shifting, | sounds, | no sounds |

| R_State                                                                                                                                                                                                                                                   | DS                                                                              | 1                                                                                           |      |                       |           |         |           |

| R_Tx_Flag_And_Ck<br>R_Tx_Commands                                                                                                                                                                                                                         | DS<br>DS                                                                        | i t<br>1                                                                                    | x re | lated                 |           |         |           |

| R_Tx_Data_Current<br>R_Current_Tx_Byte_Num<br>R_Tx_Bit_Index                                                                                                                                                                                              | DS<br>DS<br>DS                                                                  | 1<br>1<br>1                                                                                 |      |                       |           |         |           |

| R_Second_Tx_Bit_Half<br>R_First_Tx_Bit_Half<br>R_Bit_Half                                                                                                                                                                                                 | DS<br>DS<br>DS                                                                  | 1<br>1<br>1                                                                                 |      |                       |           |         |           |

| ; Variables Specific to<br>R_Gear                                                                                                                                                                                                                         | Mode 1<br>DS                                                                    | 1                                                                                           |      |                       |           |         |           |

| R_Shift_Legal                                                                                                                                                                                                                                             | DS                                                                              | 1                                                                                           |      |                       |           |         |           |

| ; Variables Specific to                                                                                                                                                                                                                                   | Mode 2                                                                          |                                                                                             |      |                       |           |         |           |

| R_Turning R_Dir R_Peelout_Enable R_Large_Shift_Timer R_Small_Shift_Timer R_Large_Gear_Timer R_Small_Gear_Timer R_Small_Idle_Timer R_Small_Idle_Timer R_Small_Chirp_Timer R_Large_Squeel_Timer R_Small_ED_Timer R_Small_LED_Timer R_Small_Fwd_Release_Time | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>D | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |      | 1<br>1                |           |         |           |

| R_Fwd_Ack_Ok<br>R_Rev_Ack_Ok                                                                                                                                                                                                                              | DS<br>DS                                                                        | 1<br>1                                                                                      |      |                       |           |         |           |

| R_Gear_Bits R_First_Start R_SS_Time_H R_SS_Time_L R_Tx_Time_H R_TX_Time_L R_Wait_Time_H R_Wait_Time_L R_Horn_Plays R_Small_Sound_Check_Time R_Sound_Check_Time                                                                                            | r                                                                               | 1<br>8<br>8<br>4<br>4<br>1<br>1<br>DS<br>DS                                                 |      | 1<br>1<br>1           |           |         |           |

```

shft96Tx.ASM

R_Peeled_Out

R_Shifted

DS

1

DS

1

R_Sleepy_Counter

R_Standby_Counter

DS

1

R_MS_Timer_Hi

R_MS_Timer_Lo

DS

1

R_Sound_Wait_Index

DS

1

.PAGEO

.Include

Channel.Inh

.CODE

ORG

DB

000н

FFH

ORG

600н

; **************** Begin Main Code **********

; V_{\perp} is by convention a vector. The reset vector is where the code goes when the micro is reset V_{\perp} Reset :

SEI

;(From Demo Code)

LDX #FFH

; load ff into the x reg (H means hex) ; transfer x reg contents to stack

;wake from sleep stuff

;lda #C0h

;sta $0D

;lda $08

;ldx #00

;stx $08

; turn off and clear all interrupt

; disable watchdog

; Acc <- Wake up status

and

#01

L_Init_Variables ; if starting from power up

L_wake_Up ; if starting from sleep

;beq

;jmp

; ***** Initialize variables

1da

#0

R_IntFlags

sta

R_IntTemps

R_TempA

R_TempX

R_SongNo

sta

sta

sta

sta

R_SongNo

R_Volume

R_Temp1

R_Sounds_Array

R_Sound_Interrupt

R_Sound_Repeat

R_Mode

R_Mode_Timer

R_Mode_Check_Timer

sta

sta

sta

sta

sta

sta

sta

sta

sta

R_Command_To_Check

R_Mode_To_Check

R_State

R_Tx_Flag_And_Ck

sta

sta

sta

```

US 2003/0114075 A1 Jun. 19, 2003

```

shft96Tx.ASM

```

```

R_Tx_Commands

sta

R_Tx_Data_Current

sta

R_Current_Tx_Byte_Num

R_Tx_Bit_Index

R_Second_Tx_Bit_Half

R_First_Tx_Bit_Half

R_Bit_Half

sta

sta

sta

sta

sta

sta

R_Gear

R_Shift_Legal

sta

sta

R_Turning

sta

R_Dir

R_Horn_Plays

sta

R_Large_Shift_Timer

R_Small_Shift_Timer

sta

sta

R_Large_Gear_Timer

R_Small_Gear_Timer

sta

sta

K_Small_Gear_Timer

R_Large_Idle_Timer

R_Small_Idle_Timer

R_Small_Chirp_Timer

R_Large_Squeel_Timer

R_Small_Squeel_Timer

R_Gear_Bits

R_First_Start

R_Shifted

R_Peeled_Out

sta

sta

sta

sta

sta

sta

sta

sta

R_Peeled_Out

sta

R_Sleepy_Counter

R_Standby_Counter

R_Fwd_Ack_Ok

sta

sta

sta

sta

R_Rev_Ack_Ok

1da

R_Peelout_Enable

sta

1dx

#0

1da

#D_TmBH_SSO

#D_IMBH_330

R_SS_Time_H,X

#D_TMBL_SS0

R_SS_Time_L,X

sta

1da

sta

1dx

#1

#D_TmBH_SS1

lda

R_SS_Time_H,X

sta

1da

#D_TmBL_SS1

R_SS_Time_L,X

sta

1dx

1da

#D_TmBH_SS2

sta

R_SS_Time_H,X

1da

#D_TmBL_SS2

sta

R_SS_Time_L,X

1dx

#3

#D_TmBH_SS3

R_SS_Time_H,X

#D_TmBL_SS3

1da

sta

lda

sta

R_SS_Time_L,X

ldx

1da

#D_TmBH_SS4

```

sta

R\_SS\_Time\_H,X

```

Shft96Tx.ASM

1da

#D_TmBL_SS4

sta

R_SS_Time_L,X

1dx

#D_TmBH_SS5

lda

sta

lda

R_SS_Time_H,X

#D_TmBL_SS5

R_SS_Time_L,X

sta

1dx

#6

1da

#D_TmBH_SS6

sta

1da

R_SS_Time_H,X

#D_TmBL_SS6

R_SS_Time_L,X

sta

1dx

1da

#D_TmBH_SS7

R_SS_Time_H,X

#D_TmBL_SS7

sta

1da

sta

R_SS_Time_L,X

ldx

#0

#D_TmBH_Tx0

R_TX_Time_H,X

#D_TmBL_Tx0

1da

sta

1da

R_TX_Time_L,X

sta

1dx

#D_TmBH_Tx1

R_Tx_Time_H,X

1da

sta

#D_TmBL_Tx1

R_Tx_Time_L,X

lda

sta

ldx

#D_TmBH_Tx2

R_Tx_Time_H,X

#D_TmBL_Tx2

1da

sta

1da

R_Tx_Time_L,X

sta

ldx

#D_TmBH_Tx3

R_Tx_Time_H,X

lda

sta

lda

#D_TmBL_Tx3

R_Tx_Time_L,X

sta

1da

#D_Snd_None

R_Current_Sound

sta

R_Next_Sound

sta

; ***** External initializations %ChannelPlayerInitial

; in Channel.inh

lda

P_Stop

; set volume

#%11110000

and

nop

nop

nop

nop

P_Stop

sta

```

sei

```

Shft96Tx.ASM

; all off (low)

LDA

#0000000b

P_PortC

STA

1da

#0

P_PortB

sta

P_PortA

sta

; ***** Port configuration

#10111111b

LDA

; D-C-B-A, high-low, 1=output

STA

P_PortIO_Ctrl

#00000000b

LDA

; outputs buffer;

DL pull down

STA

P_Port_Attrib

#00000010b

LDA

; turn off multi-phase on A2, but set 1/3

P_MultiPhase

STA

duty

; in case it does turn on for diagnosis

***** Configure interrupts

ida

; disable watchdog

#%11000010

disable nmi

enable TimerA interrupt

enable TimerB interrupt

disable 4 khz interrupt

disable 500 Hz and

enable 62.5 Hz interrupts

disable external interupt

; store interrupt settings

; store interrupt settings here, too

STA

P_Ints

R_IntFlags

STA

SEI

; disable interrupts

: ***** Preload Timers

LDA

#00h

STA

P_TmAL

preload: D58h = 315 \text{ us}

LDA

#00h

, above and mode bits

P_TmAH

STA

#00h

LDA

P_TmBL

#00h

STA

LDA

P_TmBH

STA

L_Main:

JSR

F_Get_Mode

F_Init_Mode

jsr

L_Wake_Up:

1da

P_PortC

; enable radio

#.NOT.D_Pin_Tx_Enable

and

sta

P_PortC

L_Main_Loop:

```

JSR

F\_IntCh1Service

```

; tx line should be serviced every 315 us, sound every 157 uS

; preload timers

LDA

#00h

P_TmBL

#00h

STA

LDA

P_TmBH

STA

jsr

F_Check_Time_To_Standby

L_Set_Tx_Line:

JSR

F_Set_Tx_Line

F_IntCh1Service

F_Decide_Packet

JSR

JSR

1dx

F_Wait_Sound_Service

jsr

F_IntCh1Service

ĴSR

1dx

F_Wait_Tx_Line

jsr

JSR

1dx

F_Set_Tx_Line #2

F_Wait_Sound_Service

jsr

JSR

F_IntCh1Service

jsr

F_Determine_State

; state determines packet, sounds

ldx

#3

F_Wait_Sound_Service

jsr

JSR

F_IntCh1Service

1dx

#2

F_Wait_Tx_Line

F_Set_Tx_Line

#4

jsr

ĴSR

1dx

jsr

F_Wait_Sound_Service

JSR

F_IntCh1Service

JSR

JSR

ldx

F_ServiceChannelPlayer

F_Decide_Sounds

#5

F_Wait_Sound_Service

jsr

JSR

F_IntCh1Service

ldx

#3

F_Wait_Tx_Line

F_Set_Tx_Line

#6

jsr

JSR

1dx

F_Wait_Sound_Service

jsr

```

L\_CSt\_Clear\_Standby\_Counter:

```

Shft96Tx.ASM

JSR

F_Play_Sounds

jsr

ldx

F_Control_LED #7

jsr

F_Wait_Sound_Service

F_IntChlService

JSR

1dx

F_Wait_Tx_Line

L_Main_Loop

jsr

; as an alternate to sleeping, the micro remains on, but shuts off radio

transmission

; and the DAC when nothing is doing

F_Check_Time_To_Standby:

1da

R_Mode

cmp

L_CSt_Mode_3

beq

; in modes 1 or 2 (these modes have sound)

%TestSpeechCh1 ; sets carry if pl

eechCh1 ; sets carry if playing

L_CSt_Clear_Standby_Counter

bcs

L_CSt_Mode_3:

1da

P_PortD

#0Fh

and

cmp

#0Fh

L_CSt_Clear_Standby_Counter

bne

; button pressed

inc

R_Standby_Counter

; getting sleepier

1da

R_Standby_Counter

cmp

bne

L_CSt_Done

L_CSt_Prepare_To_Standby:

lda

; clear standby counter

"_Standby_Counter

sta

P_PortC

#.NOT.D_Pin_Tx_Enable

1da

; turn off radio transmission

and

P_PortC

sta

1da

#0

;turn off dac

sta

R_DacCh1

sta

P_DacCh1

1da

R_Sound_Wait_Index

sta

jsr

F_Standby

```

```

1da

sta

R_Standby_Counter

L_CSt_Done:

rts

; wait until a button is hit. In the meantime play a sound occasionally ; to suggest to user that he turn off device. F_Standby:

L_S_Start:

1da

#0

; clear timer A

P_TMBH

P_TMBL

R_MS_Timer_Hi

R_MS_Timer_Lo

sta

sta

sta

; clear

sta

sta

R_Sound_Wait_Index

L_S_Loop:

; checks to see if any button hit or

F_ServiceChannelPlayer ; if waiting time has expired.

jsr

R_Sound_wait_Index

F_wait_Sound_Service

F_IntCh1Service

1dx

jsr

jsr

1da

P_PortD

; check button

#0fh

and

#0fh

L_S_Done

CMD

bne

; button hit

; no button hit

R_Sound_Wait_Index

R_Sound_Wait_Index

inc

1 da

cmp

bne

#09

L_S_Loop

finished hw timer loop

O_____; clear hw timers for next time

1da

P_TmBH

P_TmBL

sta

sta

#U ; reset index for next time

R_Sound_Wait_Index

1da

sta

R_MS_Timer_Lo

R_MS_Timer_Lo

#ffh

inc

1da

cmp

beq

L_S_Inc_MS_Timer_Hi

jmp

L_S_Loop

; MS_Timer_Lo not at max, keep looping

L_S_Inc_MS_Timer_Hi:

1da

R_MS_Timer_Lo

sta

R_MS_Timer_Hi

inc

R_MS_Timer_Hi

#ffh

1da

cmp

```

```

Shft96Tx.ASM; MS_Timer_Hi not at max, keep looping

bne

L_S_Loop

L_S_Set_Sound:

#0

R_Sound_Interrupt

#0

lda

sta

1da

sta

R_Sound_Repeat

L_Playing_Sound:

1da

#3

R_Current_Sound

#9

sta

1da

R_Next_Sound

jsr

F_Play_Sounds

jmp

L_S_Start

L_S_Done:

rts

P_PortB

#0000001b

P_PortB

ora

sta

1da

P_PortB

#11111110b

and

sta

P_PortB

rts

F_Blip_B1:

1da

P_PortB

#00000010b

P_PortB

ora

sta

P_PortB

#11111101b

1da

and

sta

P_PortB

rts

F_Get_Mode:

1da

#1

R_Mode

sta

; set mode 1 as new default

; disable ints momentarily since were

sei

fooling

; with a variable that's changed in the int

1da

R_Mode_Timer

{\tt L\_GM\_Check\_Modes\_Loop:}

```

```

Shft96Tx.ASM

```

```

1da

P_PortD

#0fh

and

cmp

#0fh

beq

L_GM_CK_LED_Off

1da

P_PortC

#D_Pin_LED

P_PortC

ora

sta

jmp

L_GM_Check_Timer

L_GM_CK_LED_off:

P_PortC

#.NOT.D_Pin_LED

and

sta

P_PortC

L_GM_Check_Timer:

sei

lda

R_Mode_Timer

cli

; 3 seconds

cmp

#D_Mode_Check_Timeout

L_GM_Store_Mode_1; use default

bcs

1da

P_PortD

#Ofh

#D_Mode_2_Command

L_GM_Check_Mode_3

and

cmp

bne

;mode 2 selected initially--keys need to be held

1da

P_PortC

ora

#D_Pin_LED

P_PortC

sta

1da

#D_Mode_2_Command

R_Command_To_Check

sta

Ida

#2

R_Mode_To_Check

L_GM_Wait_Modes

sta

jmp

L_GM_Check_Mode_3:

#D_Mode_3_Command

L_GM_Check_Modes_Loop

bne

; mode 3 selected--keys need to be held

1da

P_PortC

#D_Pin_LED

P_PortC

ora

sta

#D_Mode_3_Command

R_Command_To_Check

1da

sta

1da

#3

R_Mode_To_Check

L_GM_Wait_Modes

sta

jmp

; wait to see if the buttons are pressed long enough for either mode 2 or 3 to be

selected

L_GM_Wait_Modes:

sei

; start timer

```

```

Shft96Tx.ASM

lda

R_Mode_Check_Timer

sta

cli

L_GM_Wait_Mode_Loop:

P_PortD

#0fh

1da

; see if buttons still pressed

and

R_Command_To_Check

L_GM_Still_Pressed

cmp

beq

P_PortC

#.NOT.D_Pin_LED

P_PortC

1da

; turn led off

and

sta

jmp

L_GM_Check_Modes_Loop

; button no longer pressed

L_GM_Still_Pressed:

lda

R_Mode_Check_Timer

cli

#D_Mode_Select_Time

L_GM_Wait_Mode_Loop

L_GM_Store_Mode

cmp

bcc

jmp

L_GM_Store_Mode_1:

lda #1

R_Mode_To_Check

sta

; mode selected L_GM_Store_Mode:

1da

R_Mode_To_Check

sta

R_Mode

cmp

#1

L_GM_Setup_Shift_Sound

beq

cmp

L_GM_Setup_Horn_Sound

beq

jmp

L_GM_Wait_For_Joystick_Release

L_GM_Setup_Shift_Sound:

#D_Snd_Upshift

L_GM_Setup_Sound

1da

jmp

L_GM_Setup_Horn_Sound:

#D_Snd_Horn

L_GM_Setup_Sound

1da

jmp

L_GM_Setup_Sound:

R_Current_Sound

R_Next_Sound

sta

sta

#D_SamplePreload

F_PlaySpeechCh1

; the setting for sample frequency ; play

LDX

JSR

L_GM_Wait_For_Joystick_Release:

sei

Ida

#0

```

```

Shft96Tx.ASM

sta

cli

R_Mode_Timer

L_GM_Wait_For_Release:

sei

Ida

R_Mode_Timer

#D_LED_Flash_Timer

L_GM_Check_Release

cmp

; flash led

P_PortC

#D_Pin_LED

P_PortC

#0

1da

eor

sta

lda

R_Mode_Timer

sta

cli

L_GM_Check_Release:

cli

1da

P_PortD

#0fh

#0fh

and

CMD

bne

L_GM_Wait_For_Release

jmp

L_GM_Done

L_GM_Done:

; disable interrupts

; disable clk/65536 interrupt

; store interrupt settings

; store interrupt settings here, too

sei

lda

STA

#%11000000

P_Ints

R_IntFlags

STA

F_Init_Mode:

lda

R_Mode

cmp

#1

L_IM_1

beq

cmp

L_IM_2

beq

L_IM_3

jmp

L_IM_1:

jsr

F_Load_Shared_Sounds

; several sounds are shared by modes 1 and 2

; setup the sound array

L_LD_SND:

1dx

; acceleration mode no longer exists

#D_Snd_Gear

R_Sounds_Array,X

1da

sta

#5

#D_Snd_Gear

ldx

lda

```

```

Shft96Tx.ASM

sta

R_Sounds_Array,X

ldx

#D_Snd_Gear

R_Sounds_Array,X

1da

sta

#7

#D_Snd_Gear

1dx

1da

R_Sounds_Array, X

sta

1dx

#D_Snd_Horn

R_Sounds_Array,X

1da

sta

1dx

#D_Snd_Gear

R_Sounds_Array,X

lda

sta

1dx

#D_Snd_Braking

R_Sounds_Array,X

1da

sta

1dx

#12

#D_Snd_Grind

1da

sta

R_Sounds_Array, X

rts

L_IM_2:

;setup the sound array

jsr F_Load_Shared_Sounds

; several sounds are shared by modes 1 and 2

1dx

#D_Snd_Gear

R_Sounds_Array,X

lda

sta

1dx

#5

#D_Snd_Braking

R_Sounds_Array,X

1da

sta

1dx

1da

#0_Snd_Chirp

R_Sounds_Array,X

sta

1dx

#D_Snd_Horn

R_Sounds_Array,X

1da

sta

1dx

#D_Snd_Gear

R_Sounds_Array,X

lda

sta

rts

L_IM_3:

1da

;turn off dac so we're not leaking current

R_DacCh1

P_DacCh1

sta

sta

rts

```

```

Shft96Tx.ASM

F_Load_Shared_Sounds:

ldx

#D_Snd_None

lda

sta

R_Sounds_Array,X

1dx

#D_Snd_Eng_Strt

R_Sounds_Array,X

1da

sta

ldx

lda

#D_Snd_Idle

R_Sounds_Array, X

sta

ldx

1da

#D_Snd_Peelout

sta

R_Sounds_Array, X

1dx

; shift plays occasional when in mode2,

state 4

#D_Snd_Upshift

R_Sounds_Array,X

1da

sta

ldx

lda

#D_Snd_Squee1

sta

R_Sounds_Array,X

ldx

#D_Snd_Peelout

R_Sounds_Array,X

1 da

sta

ldx

#0fh

#D_Snd_Gear

R_Sounds_Array,X

1da

sta

1dx

1da

#D_Snd_Squee1

R_Sounds_Array, X

sta

; set the tx line; 2 Bytes are sent. The first contains the flag and the checksum. The second; contains the actual data.; every bit has 2 halves they will either be the same (0) or different (1).; The first bit half will always be different than the previous second bit half; (that is the tx line state always changes at the Bit boundry

*******************

;********

F_Set_Tx_Line:

P_PortB

#02h

P_PortB

1da

ora

sta

1da

P_PortB

#.NOT.02h

and

sta

P_PortB

1da

R_Bit_Half

bne

L_ST_Second_Half

```

; first bit half

```

dec

R_Tx_Bit_Index

; c.

check to see start of packet (for debugging)

da     R_Current_Tx_Byte_Num

ne     L_ST_Check_Last_Second_Half

bne

doing flag/checksum byte currently

Ìda

R_Tx_Bit_Index

#7

cmp

L_ST_Check_Last_Second_Half

bne

; blip AO to show start of packet

P_PortA

#0000001b

1da

ora

P_PortA

sta

1da

P_PortA

#11111110b

and

P_PortA

sta

L_ST_Check_Last_Second_Half:

R_Second_Tx_Bit_Half

; last was hi, we'll set next to lo s.t.; there's change across the bit boundary

bne

L_ST_Lo_First_Half

; last was no, we'll set to hi

lda P_PortC

ora #D_Pin_Tx

sta

P_PortC

lda

R_First_Tx_Bit_Half

L_ST_Done_First_Half

șta

jmp

L_$T_Lo_First_Half:

lda P_P

P_PortC

#.NOT.D_Pin_TX

and

P_PortC

sta

lda

R_First_Tx_Bit_Half

sta

L_ST_Done_First_Half:

; set flag to do second half of bit next

lda

time f_ is called

R_Bit_Half

sta

jmp

L_ST_Done

; Second half of bit

L_ST_Second_Half:

rol

; shifts bit of interest into carry bit

R_Tx_Data_Current

L_ST_Tx_Zero

bcc

; We want to transmit a "1"

Îda

R_First_Tx_Bit_Half

```

```

Shft96Tx.ASM

beq L_ST_TX_Hi_Second_Half; since first half was lo, making second half hi will make a "1"

jmp L_ST_TX_Lo_Second_Half; since first half was hi, making second half lo will make a "1"

; We want to transmit a "O"

L_ST_Tx_Zero:

lda

R_First_Tx_Bit_Half

beq L_ST_Tx_Lo_Second_Half; since first half was lo, making second half lo will make a "0"

L\_ST\_Tx\_Hi\_Second\_Half: ; since first half was hi, making second half hi will make a "1"

1da

P_PortC

#D_Pin_Tx

ora

sta

P_PortC

1da

;record

R_Second_Tx_Bit_Half

L_ST_Check_Finished_Byte

jmp

L_ST_Tx_Lo_Second_Half:

1da

P_PortC

and

#.NOT.D_Pin_Tx

P_PortC

sta

1da

R_Second_Tx_Bit_Half

; check to see if all bits of current byte have been sent L_ST_Check_Finished_Byte:

lda            R_TX_Bit_Index

R_Tx_Bit_Index

L_ST_Done_Second_Half

bne

index is zero...all bits have been sent in current data byte

da #8

ida

sta

R_Tx_Bit_Index

lda

R_Current_Tx_Byte_Num

bne

L_ST_Set_Tx_Flag_And_Ck

; current byte is flag+ck --> set to commands

R_Tx_Commands

R_Tx_Data_Current

#1

1da

sta

Īda

R_Current_Tx_Byte_Num

L_ST_Done_Second_Half

sta

jmp

; long name, I know. It sets the byte to the flag and ck byte L_ST_Set_Tx_Flag_And_Ck:

lda

R_Tx_Flag_And_Ck

sta

Ida

R_Tx_Data_Current

#0

R_Current_Tx_Byte_Num

sta

```

L\_ST\_Done\_Second\_Half:

```

Shft96Tx.ASM

#0

R_Bit_Half

1da

sta

L_ST_Done:

************

F_Determine_State:

1da

R_Mode

L_Get_State_MO

beq

cmp

L_Get_State_M1

beq

L_Get_State_M2_Dummy

beq

jmp

L_Get_State_M3

L_Get_State_M2_Dummy:

L_Gét_State_M2

jmp

L_Get_State_MO:

rts

****************

Determine state for Mode 1

L_Get_State_M1:

1da

beq

cmp

#1

L_GS1_State_1_Dummy

beq

; same for modes 1 and 2

cmp

beq

L_GS1_State_2_Dummy

; same for modes 1 and 2

cmp

beq

L_GS1_State_3

cmp

beq

L_GS1_State_4_Dummy

cmp

beq

L_GS1_State_5_Dummy

cmp

L_GS1_State_6_Dummy

beq

#7

L_GS1_State_7_Dummy

cmp

beq

cmp

L_GS1_State_8_Dummy

beq

cmp

L_GS1_State_9_Dummy

beq

```

#10 cmp beq L\_GS1\_State\_10\_Dummy cmp beq L\_GS1\_State\_11\_Dummy cmpbeq L\_GS1\_State\_12\_Dummy cmp#13 beq L\_GS1\_State\_13\_Dummy cmp beq L\_GS1\_State\_14\_Dummy cmpbeq L\_GS1\_State\_15\_Dummy jmp L\_GS\_State\_16 L\_GS1\_State\_0\_Dummy: L\_GS\_State\_0 jmp L\_GS1\_State\_1\_Dummy: L\_GS\_State\_1 jmp L\_GS1\_State\_2\_Dummy: L\_GS\_State\_2 jmp L\_GS1\_State\_4\_Dummy: L\_GS1\_State\_4 L\_GS1\_State\_5\_Dummy: L\_GS1\_State\_5 jmp L\_GS1\_State\_6\_Dummy: L\_GS1\_State\_6 jmp L\_GS1\_State\_7\_Dummy: L\_GS1\_State\_7 jmp L\_GS1\_State\_8\_Dummy: L\_GS1\_State\_8 jmp L\_GS1\_State\_9\_Dummy: jmp L\_GS1\_State\_9 L\_GS1\_State\_10\_Dummy: jmp L\_GS1\_State\_10 L\_GS1\_State\_11\_Dummy: L\_GŚ1\_State\_11 jmp L\_GS1\_State\_12\_Dummy: L\_GS1\_State\_12 jmp L\_GS1\_State\_13\_Dummy: jmp L\_GS1\_State\_13 L\_GS1\_State\_14\_Dummy: L\_GS\_State\_14 jmp

```

L_GS1_State_15_Dummy:

jmp L_GS_State_15

;*****Model State 3*************************

Peelin' out

;General:

Gear

Sound:

Peel Out

Peel Out

State 4 (Accel): Peel Out sound complete

State 11(Braking): Rev Hit

State 12(Grind Gears): trying to shift too soon (Fwd Only)

State 13 (Squeeling): Turning for a long time

;To Change State:

L_GS1_State_3:

jsr

F_GS1_Check_Fw_Still_Pressed

jsr

F_GS1_Check_Fwd_Ack_Ok

1da

R_Peeled_Out

sta

jsr

F_GS1_Check_Shift_Legal

R_Sound_Check_Delay_Complete

L_GS1_3_Sound_Check

1da

bne

; decrement timer

dec R_Small_Sc

lda R_Small_Sc

R_Small_Sound_Check_Timer

R_Small_Sound_Check_Timer

L_GS1_3_Dec_Big_Sound_Check_Timer

beq

; if small timer has run to

jmp

L_GS1_3_Check_Squee1

L_GS1_3_bec_Big_Sound_Check_Timer:

lda  #ffh ; reload small timer

sta    R_Small_Sound_Check_Timer

Dec

R_Large_Sound_Check_Timer

R_Large_Sound_Check_Timer

L_GS1_3_Check_Squeel

; not yet

Bne

1da

R_Sound_Check_Delay_Complete

sta

L_GS1_3_Sound_Check:

; which will set the Carry if actively

%TestSpeechCh1

playing

bcs

L_GS1_3_Check_Squee1

; still playing

jsr

jmp

F_GS1_Set_State_5

L_GS_Done

L_GS1_3_Check_Squeel:

jsr F_GS_Check_Squeel

```

```

Shft96Tx.ASM

;jsr

isr

F_GS1_Check_Premature_Shift

F_GS1_Check_Braking

jmp

L_GS_Done

;*****Model State 4****************************

;General:

it was eliminated

Just jumps to state 5. Used to be accellerating state, but

It is kept to avoid excessive rework in the code. Also,

śeems possible

that client might ask for it back.

;Gear:

Sound:

;To Change State:

State 5 (gear1). instantly, more or less

; going fwd. or reverse plays motor running sound, or occasionally gear shift-allow car to move.

L_GS1_State_4:

%TestSpeechCh1

L_GS1_4_Done

bcs

F_GS1_Set_State_5

jsr

L_GS1_4_Done:

L_GS_Done

jmp

;*****Mode1 State 5*****************************

General:

Gear 1

Geal I

Fwd possibly turning

Gear 1

State 8 (ready to shift) Timeout (Fwd Only)

State 11(Braking): Rev Hit if going fwd, or rev released if

; Movement:

;Sound:

;To Change State:

going rev

State 12(Grind Gears): trying to shift too soon

State 13 (Squeeling): Turning for a long time (Fwd Only)

L_GS1_State_5:

jsr

F_GS1_Check_Fw_Still_Pressed

F_GS1_Check_Fwd_Ack_Ok

F_GS1_Check_Squeel

F_GS1_Check_Premature_Shift

F_GS1_Check_Shift_Legal

F_GS1_Check_Braking

jsr

jsr

jsr

jsr

jsr

;General:

Gear 2

Gear 2

Fwd, possibly turning

Gear 2

State 8 (ready to shift) Timeout

State 11(Braking): Rev Hit

State 12 (Grind Gears): trying to shift too soon

State 13 (Squeeling): Turning for a long time

; Movement:

Sound:

;To Change State:

L_G51_State_6:

```

```

Shft96Tx.ASM

; traveling fwd currently

F_GS1_Check_Fw_Still_Pressed

F_GS1_Check_Fwd_Ack_Ok

F_GS_Check_Squeel

F_GS1_Check_Premature_Shift

F_GS1_Check_Shift_Legal

jsr

jsr

jsr

jsr

jsr

F_GS1_Check_Braking

jsr

******<u>*</u>Mode1 State 7*******************************

Gear 3

Fwd, possibly turning

Gear 3

;General:

;Movement:

;Sound:

;To Change State:

State 11(Braking): Rev Hit State 13 (Squeeling): Turning for a long time {\bf r}

L_GS1_State_7

; traveling fwd currently

jsr

jsr

F_GS1_Check_Fw_Still_Pressed

F_GS_Check_Squeel

F_GS1_Check_Braking

jsr

*****Model State 8************************

;General:

ready to shift ramp whining noise

:Movement:

Fwd

Sound:

ramp whining noise

To Change State:

State 9 (Ready to shift, const sound),

State 10 (Shifting) Fwd hit legally

State 11(Braking): Rev Hit or timeout

State 13 (Squeeling): Turning for a long time

L_GS1_State_8:

F_GS1_Check_Fw_Still_Pressed

F_GS1_Check_Fwd_Ack_Ok

; a delay in the sound check timer is apparently necessary. If I try to check the ; sound right away, it doesn't think a sound is playing. So you wait some arbitrary ; amount of time (maybe half a second), then check to see if the sound is playing. ; at the time of writing this, I don't understand why this is necessary.

R_Sound_Check_Delay_Complete

L_GS1_8_Sound_Check

lda

bne

; decrement timer

,

R_Small_Sound_Check_Timer

R_Small_Sound_Check_Timer

L_GS1_8_Dec_Big_Sound_Check_Timer

dec

lda

; if small timer has run to

beq

0

jmp

L_GS1_8_Check_Squee1

L_GS1_8_Dec_Big_Sound_Check_Timer:

#ffh ; reload small timer

R_Small_Sound_check_Timer

sta

R_Large_Sound_Check_Timer

R_Large_Sound_Check_Timer

Dec

LDA

```

```

Shft96Tx.ASM

L_GS1_8_Check_Squee1

Rne

; not yet

1da

R_Sound_Check_Delay_Complete

sta

L_GS1_8_Sound_Check:

%TestSpeechCh1

L_GS1_8_Check_Squee1

BCS

done playing ramping whining noise

sr F_GS1_Set_State_9

mp L_GS_Done

jsr

jmp

L_GS1_8_Check_Squee1:

jsr

jsr

F_GS_Check_Squeel

F_GS1_Check_Shift

F_GS1_Check_Braking

јmр

L_GS_Done

;******Model State 9******************************

:General:

ready to shift

:Movement:

Fwd

; Sound:

constant whining noise

;To Change State:

State 10 (Shifting) Fwd hit legally

State 11(Braking): Rev Hit or timeout

State 13 (Squeeling): Turning for a long time

L_GS1_State_9:

F_GS1_Check_Fw_Still_Pressed

F_GS1_Check_Fwd_Ack_Ok

F_GS_Check_Squeel

F_GS1_Check_Shift

F_GS1_Check_Braking

jsr

jsr

jmp

L_GS_Done

;*****Model State 10***********************

;General:

;Movement:

shifting

Fwd

;Sound:

;To Change State:

shifting

State 6, 7 (Gear 2,3) Sound finishes

State 11(Braking): Rev Hit

State 13 (Squeeling): Turning for a long time

L_GS1_State_10:

F_GS1_Check_Fw_Still_pressed

F_GS1_Check_Fwd_Ack_Ok

F_GS1_Check_Shift_Legal

jsr

jsr

%TestSpeechCh1

; which will set the Carry if actively

playing

BCS

L_GS1_10_Check_Squee1

; still playing shift

1da

R_Gear

cmp

#3

; shifting into gear 3

```

```

Shft96Tx.ASM

L_GS1_10_Set_State_7

beq

jsr

jmp

F_GS1_Set_State_6

; shifting from gear 1 to 2

L_GS_Done

L_GS1_10_Set_State_7:

F_GS1_Set_State_7

L_GS_Done

; shifting from gear 2 to 3

jsr

jmp

L_GS1_10_Check_Squee1:

F_GS_Check_Squeel

F_GS1_Check_Braking

jsr

jsr

jmp

L_GS_Done

;*****Model State 11***************************

;General:

braking

:Movement:

none

braking

State 2 (idle) braking sound finishes

;Sound:

;To Change State:

L_GS1_State_11:

%TestSpeechCh1

; which will set the Carry if actively

playing

bcs

L_GS1_11_Done

; still playing braking

jsr

L_GS1_11_Done:

F_GS_Set_State_2

L_GS_Done

jmp

;*****Mode1 State 12**************************

grinding gears

unchanged

General:

; Movement:

;Sound:

grinding gears

State 5 (gear 1) braking sound finishes

State 11 (braking) hit rev

;To Change State:

L_GS1_State_12:

jsr

F_GS1_Check_Fw_Still_Pressed

%TestSpeechCh1

; which will set the Carry if actively

playing

L_GS1_12_Check_Braking ; still playing squeeling

BCS

F_GS1_Set_State_5

L_GS_Done

jsr

àmp

L_GS1_12_Check_Braking:

F_GS1_Check_Braking

L_GS_Done

jsr

jmp

;*****Model State 13***********************

;General:

squeel

; Movement:

turning, and going forward

Sound:

squeel State 11 (braking) hit rev State 5 (gear 1) no longer turning

To Change State:

L_GS1_State_13:

1da

#n

R_Shifted

sta

```

```

Shft96Tx.ASM

jsr

F_GS1_Check_Fw_Still_Pressed

check to see if turning

; cii

P_PortD

#D_Pin_Left

L_GS1_13_Check_Braking ; still turning

and

beg

; check right turn

lda P_H

P_PortD

#D_Pin_Right

L_GS1_13_Check_Braking ; still turning

and

beq

; no longer turning

F_GS1_Set_State_5

L_GS_Done

L_GS1_13_Check_Braking:

jsr F_GS1_Check_Braking

jmp L_GS_Done

*****************

F_GS1_Check_Braking:

; checks braking when moving fwd

; see if rev hit (Causes braking)

lda P_PortD

and #D_Pin_Rev

bne

L_GS1CB_Done

jsr

jmp

F_GS_Set_State_11

L_GS_Done

; braking

L_GS1CB_Done:

rts

· ****************

F_GS1_Check_Premature_Shift:

R_Fwd_Ack_Ok

L_GS1PS_Done

1da

beq

; has returned to neutral

lda

P_PortD

#D_Pin_Fwd

L_GS1PS_Done

and

bne

; fwd not hit

jsr

jmp

F_GS1_Set_State_12

L_GS_Done

L_GS1PS_Done:

rts

```

\*\*\*\*\*\*\*\*

R\_Small\_Shift\_Timer

F\_GS1\_Check\_Shift\_Legal:

; decrement timer

dec

```

Shft96Tx.ASM

R_Small_Shift_Timer

L_DS_Dec_Big_Shift_Timer

L_CSL_Done

1da

; if small timer has run to 0

beq

jmp

L_CSL_Done

L_DS_Dec_Big_Shift_Timer:

#ffh ; reload small timer

R_Small_Shift_Timer

sta

R_Large_Shift_Timer

R_Large_Shift_Timer

L_CSL_Done

Dec

LDA

Bne

; not legal yet

; shift is legal

jsr

jmp

F_GS1_Set_State_8

L_GS_Done

L_CSL_Done:

rts

P_PortD

#D_Pin_Fwd

lda

and

bne

L_GS1CS_Done

; i.e. fwd pin is hi

shift

; sł

jsr

F_GS1_Set_State_10

L_GS1CS_Done:

rts

; checks if joystick has rtned to neutral position. It must return here before a new fwd (or rev.) is acknowledged

F_GS1_Check_Fwd_Ack_Ok:

1da

R_Fwd_Ack_Ok

bne

L_GS1CF_Done

;already okay

1da

P_PortD

#D_Pin_Fwd

L_GS1CF_Done

and

beq

; button pressed

; not pressed

1da

R_Fwd_Ack_Ok

sta

L_GS1CF_Done:

rts