(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4918928号

(P4918928)

(45) 発行日 平成24年4月18日(2012.4.18)

(24) 登録日 平成24年2月10日(2012.2.10)

(51) Int.Cl.

H03M 3/02 (2006.01)

F 1

H03M 3/02

請求項の数 2 (全 10 頁)

(21) 出願番号 特願2009-6162 (P2009-6162)

(22) 出願日 平成21年1月14日 (2009.1.14)

(65) 公開番号 特開2010-166268 (P2010-166268A)

(43) 公開日 平成22年7月29日 (2010.7.29)

審査請求日 平成23年9月27日 (2011.9.27)

(73) 特許権者 000006220

ミツミ電機株式会社

東京都多摩市鶴牧2丁目11番地2

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 阿部 真喜男

東京都多摩市鶴牧2丁目11番地2 ミツ

ミ電機株式会社内

審査官 北村 智彦

最終頁に続く

(54) 【発明の名称】デルタ・シグマA D変換回路

## (57) 【特許請求の範囲】

## 【請求項1】

アナログ信号をパルス密度変調してパルス密度変調データを得る変調部と、高速動作と低速動作を含む複数の動作速度で処理を行ひ前記パルス密度変調データをパルスコード変調データに変換するC P Uを有し、アナログ信号をデジタル信号に変換するデルタ・シグマA D変換回路であつて、

前記変調部は、

パルス密度変調データをクロックによりシフトして保持するシフトレジスタと、

前記シフトレジスタの保持するパルス密度変調データを分割して保持し、保持内容を前記C P Uから読み出される複数のレジスタと、

前記シフトレジスタが前記パルス密度変調データをシフトするビット数を前記C P Uの動作速度に応じ前記高速動作時には第1の値であり前記低速動作には前記第1の値より大きい第2の値である所定値だけカウントして前記複数のレジスタの格納指示信号と、前記C P Uに前記レジスタの読み出しを要求する読み出し要求信号を生成するカウンタと、を有することを特徴とするデルタ・シグマA D変換回路。

## 【請求項2】

請求項1記載のデルタ・シグマA D変換回路において、

前記変調部は、

前記C P Uからの設定に応じて、前記カウンタから読み出し要求信号を供給されたときに前記カウンタの動作を指示する変換開始信号をリセットするリセット手段を

10

20

有することを特徴とするデルタ・シグマ A/D 変換回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はデルタ・シグマ A/D 変換回路に関し、アナログ信号をデジタル信号に変換するデルタ・シグマ A/D 変換回路に関する。

【背景技術】

【0002】

近年、リチウムイオン電池を用いたバッテリパックがデジタルカメラなどの携帯機器に搭載されている。リチウムイオン電池は、一般に、その電圧により電池残量を検出することが難しいとされている。このため、マイコンなどにより電池の充放電電流を検出し、検出した充放電電流を積算することにより、電池残量を測定する方法がとられている。

【0003】

このようにして電池残量を測定するためのフェュエルゲージ IC には、高精度 A/D 変換回路などのアナログ回路と、計測した電流値を積算する CPU やタイマなどのデジタル回路とが、1 チップの半導体集積回路装置に搭載されている。

【0004】

上記アナログ回路において、アナログ信号をデジタル信号に変換する A/D 変換回路に一つとしてデルタ・シグマ A/D 変換回路がある（例えば特許文献 1 参照）。

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開平 9 - 307451 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

フェュエルゲージ IC では、バッテリパックが携帯機器に接続されて放電する場合や、バッテリパックを充電する場合には CPU が高速動作を行うが、バッテリパックが携帯機器に接続されていない場合には CPU は低速動作となる。

【0007】

デルタ・シグマ A/D 変換回路は、アナログ信号をパルス密度変調してパルス密度変調データを出力する変調部と、パルス密度変調データをデジタル信号であるパルスコード変調データに変換するフィルタ処理部とに分かれ、このフィルタ処理部の処理を CPU で実行することが考えられる。

【0008】

CPU が高速動作を行っている場合にはデルタ・シグマ A/D 変換回路の変調部からフィルタ処理を行う CPU に供給するパルス密度変調データのビット数を小さくし、CPU が低速動作を行っている場合には変調部からフィルタ処理を行う CPU に供給するパルス密度変調データのビット数を大きくする必要がある。

【0009】

本発明は上記の点に鑑みてなされたもので、CPU の動作速度に応じて変調部から CPU に供給するパルス密度変調データのビット数を可変できるデルタ・シグマ A/D 変換回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の一実施態様によるデルタ・シグマ A/D 変換回路は、アナログ信号をパルス密度変調してパルス密度変調データを得る変調部（10）と、高速動作と低速動作を含む複数の動作速度で処理を行い前記パルス密度変調データをパルスコード変調データに変換する CPU（30）を有し、アナログ信号をデジタル信号に変換するデルタ・シグマ A/D 変換回路であって、

10

20

30

40

50

前記変調部(10)は、

パルス密度変調データをクロックによりシフトして保持するシフトレジスタ(18)と

、

前記シフトレジスタ(18)の保持するパルス密度変調データを分割して保持し、保持内容を前記CPU(30)から読み出される複数のレジスタ(21, 22)と、

前記シフトレジスタ(18)が前記パルス密度変調データをシフトするビット数を前記CPUの動作速度に応じ前記高速動作時には第1の値であり前記低速動作には前記第1の値より大きい第2の値である所定値だけカウントして前記複数のレジスタ(21, 22)の格納指示信号と、前記フィルタ処理部(30)に前記レジスタの読み出しを要求する読み出し要求信号を生成するカウンタ(19)と、を有する。

10

#### 【0012】

好ましくは、前記変調部(10)は、

前記CPU(30)からの設定に応じて、前記カウンタ(19)から読み出し要求信号を供給されたときに前記カウンタ(19)の動作を指示する変換開始信号をリセットするリセット手段(13)を

有することを特徴とするデルタ・シグマA/D変換回路。

#### 【0013】

なお、上記括弧内の参照符号は、理解を容易にするために付したものであり、一例にすぎず、図示の態様に限定されるものではない。

20

#### 【発明の効果】

#### 【0014】

本発明によれば、CPUの動作速度に応じて変調部からCPUに供給するパルス密度変調データのビット数を可変することができる。

#### 【図面の簡単な説明】

#### 【0015】

【図1】本発明のデルタ・シグマA/D変換回路の一実施形態のブロック構成図である。

【図2】デルタ・シグマ変調器の一実施形態のブロック図である。

【図3】32ビットモードにおける信号タイミングチャートである。

【図4】16ビットモードにおける信号タイミングチャートである。

【図5】フェューエルゲージICを適用したバッテリパックの一実施形態のブロック図である。

30

#### 【発明を実施するための形態】

#### 【0016】

以下、図面に基づいて本発明の実施形態について説明する。

#### 【0017】

<デルタ・シグマA/D変換回路の一実施形態>

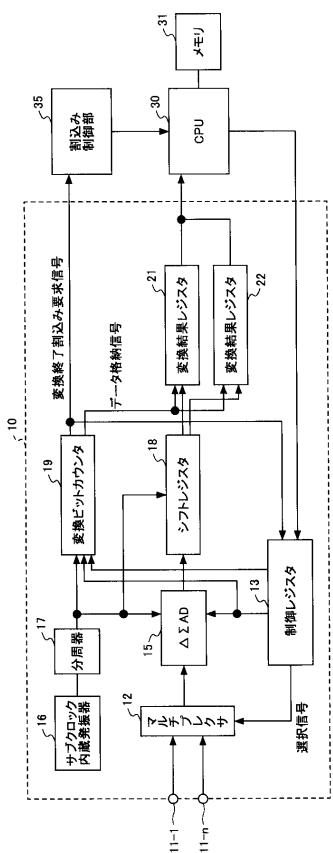

図1は、本発明のデルタ・シグマA/D変換回路の一実施形態のブロック構成図を示す。同図中、デルタ・シグマA/D変換回路は、変調部10とCPU30とメモリ31と割込み制御部35を有している。CPU30がフィルタ処理部に相当する。

#### 【0018】

変調部10の端子11-1~11-nから入力されるアナログ信号はマルチプレクサ12に供給される。マルチプレクサ12は制御レジスタ13からの選択信号に基づいて端子11-1~11-nの入力のうちいずれか一つのアナログ信号を選択してデルタ・シグマ変調器15に供給する。

40

#### 【0019】

サブクロック内部発振器16は例えば周波数38.4kHzのサブクロックを発生し、このサブクロックは分周器17で1/4分周されて周波数9.6kHzのクロックとされてデルタ・シグマ変調器15、シフトレジスタ18、変換ビットカウンタ19に供給される。

#### 【0020】

50

デルタ・シグマ変調器15は、制御レジスタ13から変換開始信号を供給されると、マルチプレクサ12から供給されるアナログ信号のパルス密度変調(PDM)を行って、1ビットデジタル変調した信号を出力し、デルタ・シグマ変調器15の出力する信号はシフトレジスタ18に供給する。

#### 【0021】

変換ビットカウンタ19は、制御レジスタ13から変換開始信号と32ビットモード又は16ビットモードを指示するモード信号を供給され、変換開始信号が例えハイレベルであるとカウンタ動作を開始し、モード信号に応じて32パルス又は16パルスのクロックをカウントしたとき読み出し要求信号としての変換終了割込み要求信号と、データ格納信号を生成する。変換ビットカウンタ19は変換終了割込み要求信号を制御レジスタ13及び割込み制御部35に供給し、また、データ格納信号を変換結果レジスタ21, 22に供給する。10

#### 【0022】

制御レジスタ13はCPU30から32ビットモード又は16ビットモード、及び、変換開始信号のリセットの有無等を設定され、32ビットモード又は16ビットモードと変換開始信号のリセットの有無に応じて、変換開始信号とモード信号をデルタ・シグマ変調器15, 変換ビットカウンタ19それぞれに供給する。

#### 【0023】

また、制御レジスタ13は変換ビットカウンタ19から変換終了割込み要求信号を供給されたとき、変換開始信号のリセット有を設定されている場合は変換開始信号をリセットし、変換開始信号のリセット無を設定されている場合は変換開始信号のリセットを行わない。20

#### 【0024】

シフトレジスタ18は、32ビット構成であり、デルタ・シグマ変調器15からの1ビットのデジタル信号をクロックにてシフトし、上位16ビットをパラレルに変換結果レジスタ21に供給し、上位16ビットをパラレルに変換結果レジスタ22に供給する。

#### 【0025】

変換結果レジスタ21, 22それぞれはCPU30から読み出しを要求されると、保持している16ビットのパルス密度変調データを16ビット幅のバスを介してCPU30に供給する。30

#### 【0026】

CPU30は、高速動作を行っている場合には制御レジスタ13に16ビットモードを指示する設定を行い、低速動作を行っている場合には制御レジスタ13に32ビットモードを指示する設定を行う。

#### 【0027】

また、CPU30は割込み制御部35から変換終了割込み要求が供給されると、32ビットモードでは変換結果レジスタ21, 22の保持するパルス密度変調データを順に読み取り(合計32ビット)、16ビットモードでは変換結果レジスタ21の保持するパルス密度変調データ(16ビット)を読み取り、パルス密度変調データをデジタル信号であるパルスコード変調データに変換するフィルタ処理、つまり、デシメーションフィルタ処理を実行する。なお、メモリ31にCPU30が実行するデシメーションフィルタ処理プログラムが格納されている。40

#### 【0028】

割込み制御部35は、変換ビットカウンタ19からの変換終了割込み要求信号の他に複数の割込み要求信号を供給されており、同時に複数の割込み要求がある場合には優先度の高い割込み要求を選択してCPU30に割込み要求を行う。

#### 【0029】

<デルタ・シグマ変調器>

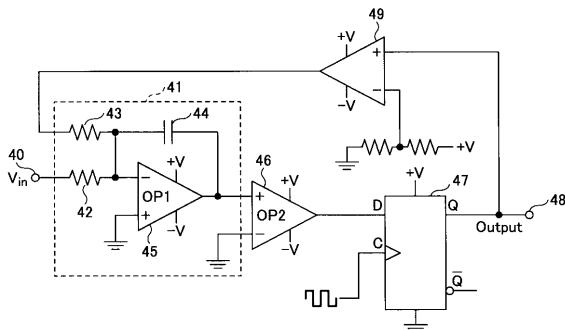

図2は、デルタ・シグマ変調器15の一実施形態のブロック図を示す。同図中、端子40にアナログ電圧V<sub>in</sub>が供給されて積分回路41に供給される。積分回路41は入力抵50

抗 4 2 , 帰還抵抗 4 3 , 積分容量 4 4 , 演算増幅器 4 5 から構成されており、アナログ電圧 V<sub>in</sub> から演算増幅器 4 9 の出力電圧を減算して得られる差分を積分する。

#### 【 0 0 3 0 】

積分回路 4 1 の出力信号は、演算増幅器 4 6 で構成されるコンパレータで量子化され、D型フリップフロップ 4 7 で 1 クロック分遅延された後、端子 4 8 から出力される。また、端子 4 8 の出力は 1 ビットの D A コンバータを構成する演算増幅器 4 9 を介して積分回路 4 1 に帰還される。

#### 【 0 0 3 1 】

< 信号タイミングチャート >

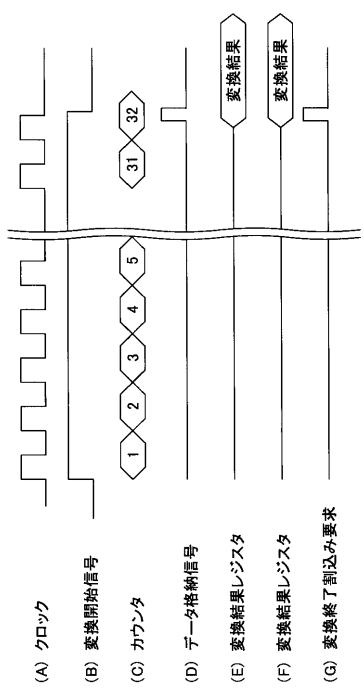

図 3 は、3 2 ビットモードにおける信号タイミングチャートを示す。図 3 ( B ) に示す変換開始信号はハイレベルとなった後、変換ビットカウンタ 1 9 は図 3 ( A ) に示すクロックをカウントし、図 3 ( C ) に示すように 3 2 パルスをカウントした時点で、図 3 ( D ) に示すデータ格納信号と、図 3 ( G ) に示す変換終了割込み要求信号を生成する。

10

#### 【 0 0 3 2 】

これにより、図 3 ( E ) , ( F ) に示すように変換結果レジスタ 2 1 , 2 2 それぞれにシフトレジスタ 1 8 の上位 1 6 ビット、下位 1 6 ビットが格納される。また、図 3 ( G ) に示す変換終了割込み要求信号により C P U 3 0 は変換結果レジスタ 2 1 , 2 2 からパルス密度変調データを読み取る。

#### 【 0 0 3 3 】

なお、図 3 の例では、制御レジスタ 1 3 に変換開始信号のリセット有が設定されているため、変換終了割込み要求信号によって図 3 ( B ) に示す変換開始信号はローレベルとされる。変換開始信号のリセット無が設定されているには、変換終了割込み要求信号が供給されても変換開始信号はハイレベルを維持し、変換ビットカウンタ 1 9 は再び 1 からカウントを開始する。

20

#### 【 0 0 3 4 】

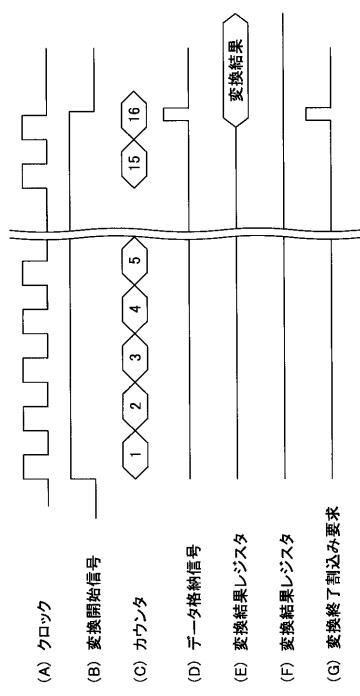

図 4 は、1 6 ビットモードにおける信号タイミングチャートを示す。図 4 ( B ) に示す変換開始信号はハイレベルとなった後、変換ビットカウンタ 1 9 は図 4 ( A ) に示すクロックをカウントし、図 4 ( C ) に示すように 1 6 パルスをカウントした時点で、図 4 ( D ) に示すデータ格納信号と、図 4 ( G ) に示す変換終了割込み要求信号を生成する。

#### 【 0 0 3 5 】

これにより、図 4 ( E ) に示すように変換結果レジスタ 2 1 にシフトレジスタ 1 8 の上位 1 6 ビットが格納される。また、図 4 ( G ) に示す変換終了割込み要求信号により C P U 3 0 は変換結果レジスタ 2 1 からパルス密度変調データを読み取る。

30

#### 【 0 0 3 6 】

なお、図 4 の例では、制御レジスタ 1 3 に変換開始信号のリセット有が設定されているため、変換終了割込み要求信号によって図 4 ( B ) に示す変換開始信号はローレベルとされる。変換開始信号のリセット無が設定されているには、変換終了割込み要求信号が供給されても変換開始信号はハイレベルを維持し、変換ビットカウンタ 1 9 は再び 1 からカウントを開始する。

#### 【 0 0 3 7 】

このようにして、C P U 3 0 が高速動作を行っている場合にはデルタ・シグマ A D 変換回路の変調部 1 0 から C P U 3 0 に供給するパルス密度変調データのビット数を小さくし、C P U 3 0 が低速動作を行っている場合には変調部 1 0 から C P U 3 0 に供給するパルス密度変調データのビット数を大きくすることができる。

40

#### 【 0 0 3 8 】

< バッテリパック >

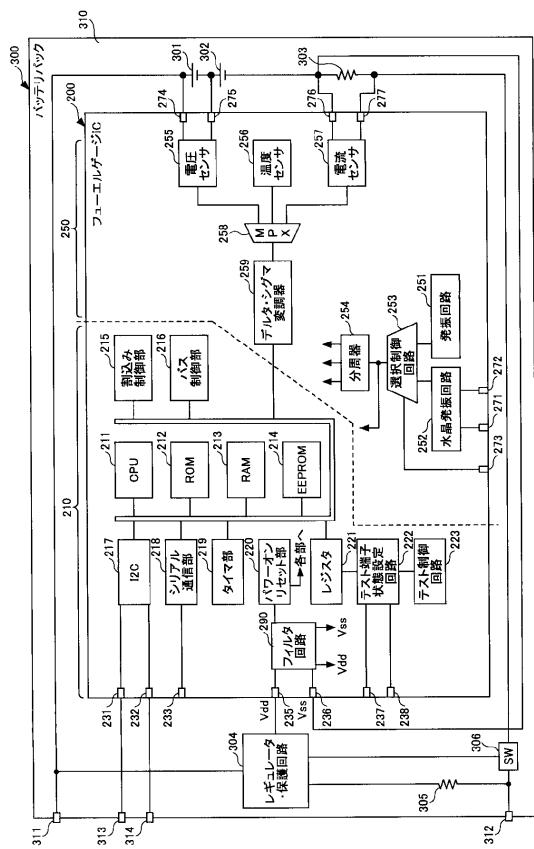

図 5 は、フューエルゲージ I C を適用したバッテリパックの一実施形態のブロック図を示す。同図中、フューエルゲージ I C 2 0 0 は、デジタル部 2 1 0 とアナログ部 2 5 0 とから大略構成されている。

#### 【 0 0 3 9 】

50

デジタル部 210 内には、CPU211、ROM212、RAM213、EEPROM214、割込み制御部215、バス制御部216、I2C部217、シリアル通信部218、タイマ部219、パワーオンリセット部220、レジスタ221、テスト端子状態設定回路222、テスト制御回路223、フィルタ回路290が設けられている。上記のCPU211、ROM212、RAM213、EEPROM214、割込み制御部215、バス制御部216、I2C部217、シリアル通信部218、タイマ部219、レジスタ221は内部バスにて相互に接続されている。

#### 【0040】

なお、CPU211は図1のCPU30に相当し、ROM212は図1のメモリ31に相当し、割込み制御部215は図1の割込み制御部35に相当する。

10

#### 【0041】

CPU211は、ROM212に記憶されているプログラムを実行してフューエルゲージIC200全体を制御し、バッテリの充放電電流を積算してバッテリ残量を算出する処理等を実行する。この際にRAM213が作業領域として使用される。EEPROM214にはトリミング情報等が記憶される。

#### 【0042】

割込み制御部215は、フューエルゲージIC200の各部から割込み要求を供給され、各割込み要求の優先度に応じて割込みを発生しCPU211に通知する。バス制御部216は、どの回路部が内部バスを使用するかの制御を行う。

#### 【0043】

I2C部217はポート231, 232を介して通信ラインに接続されて2線式のシリアル通信を行う。シリアル通信部218はポート233を介して図示しない通信ラインに接続されて1線式のシリアル通信を行う。

20

#### 【0044】

タイマ部219はシステムクロックをカウントし、そのカウント値はCPU211に参照される。パワーオンリセット部220はフィルタ回路290を介して接続されているポート235に供給される電源Vddが立ち上がったことを検出してリセット信号を発生しフューエルゲージIC200の各部に供給する。

#### 【0045】

レジスタ221にはEEPROM214からの情報が転送される。テスト端子状態設定回路222はレジスタ221に保持された情報に応じてテスト端子237, 238とテスト制御回路223との間を接続し、また、テストポート237, 238に対応するテスト制御回路223の入力を所定のレベルに設定する。

30

#### 【0046】

テスト制御回路223は、テストポート237, 238の入力を供給されると、その入力に応じて内部回路の状態を変化させて、フューエルゲージIC200の内部回路のテストが可能となる。

#### 【0047】

アナログ部250内には、発振回路251、水晶発振回路252、選択制御回路253、分周器254、電圧センサ255、温度センサ256、電流センサ257、マルチブレクサ258、デルタ・シグマ変調器259が設けられている。なお、デルタ・シグマ変調器259は図1の変調部10に相当する。

40

#### 【0048】

発振回路251はPLLを持つ発振器であり数MHzの発振信号を出力する。水晶発振回路252はポート271, 272に水晶振動子を外付けされて発振を行い、数MHzの発振信号を出力する。水晶発振回路252の発振周波数は発振回路251に対し高精度である。

#### 【0049】

選択制御回路253はポート273から供給される選択信号に基づいて発振回路251と水晶発振回路252のいずれか一方の出力する発振周波信号を選択しシステムクロック

50

としてフューエルゲージ I C 2 0 0 の各部に供給すると共に分周器 2 5 4 に供給する。また、選択制御回路 2 5 3 はリセット信号 R S T と制御信号 C N T を生成している。ところで、選択制御回路 2 5 3 はポート 2 7 3 から選択信号が供給されない場合には例えば発振回路 2 5 1 の出力する発振周波信号を選択する。分周器 2 5 4 はシステムクロックを分周して各種クロックを生成しフューエルゲージ I C 2 0 0 の各部に供給する。

#### 【 0 0 5 0 】

電圧センサ 2 5 5 はポート 2 7 4 , 2 7 5 それぞれに外付けされるバッテリ 3 0 1 , 3 0 2 の電圧を検出し、アナログの検出電圧をマルチプレクサ 2 5 8 に供給する。温度センサ 2 5 6 はフューエルゲージ I C 2 0 0 の環境温度を検出しアナログの検出温度をマルチプレクサ 2 5 8 に供給する。

10

#### 【 0 0 5 1 】

ポート 2 7 6 , 2 7 7 には電流検出用の抵抗 3 0 3 の両端が接続されており、電流センサ 2 5 7 はポート 2 7 6 , 2 7 7 それぞれの電位差から抵抗 3 0 3 を流れる電流を検出しアナログの検出電流をマルチプレクサ 2 5 8 に供給する。

#### 【 0 0 5 2 】

マルチプレクサ 2 5 8 は、アナログの検出電圧、アナログの検出温度、アナログの検出電流を順次選択してデルタ・シグマ変調器 2 5 9 に供給する。デルタ・シグマ変調器 2 5 9 は各検出値をデルタ・シグマ変換することでパルス密度変調データを内部バスを通して C P U 2 1 1 に供給し、C P U 2 1 1 にてデジタルフィルタ処理を行って検出電圧、検出温度、検出電流それぞれのデジタル化を行う。また、C P U 2 1 1 は、バッテリの充放電電流を積算することによりバッテリ残量を算出する。この際検出温度は温度補正のために使用される。

20

#### 【 0 0 5 3 】

上記のフューエルゲージ I C 2 0 0 は、バッテリ 3 0 1 , 3 0 2 、電流検出用の抵抗 3 0 3 、レギュレータ・保護回路 3 0 4 、抵抗 3 0 5 及びスイッチ 3 0 6 と共に筐体 3 1 0 に収納されてバッテリパック 3 0 0 が構成されている。バッテリパック 3 0 0 の端子 3 1 1 にバッテリ 3 0 1 の正電極及びレギュレータ・保護回路 3 0 4 の電源入力端子が接続され、レギュレータ・保護回路 3 0 4 の電源出力端子がフューエルゲージ I C 2 0 0 の電源 V d d のポート 2 3 5 が接続されている。端子 3 1 2 は抵抗 3 0 5 を介してレギュレータ・保護回路 3 0 4 の接地端子に接続されると共に、スイッチ 3 0 6 を介して電流検出用の抵抗 3 0 3 のポート 2 7 7 との接続点に接続されている。レギュレータ・保護回路 3 0 4 は、端子 3 1 1 , 3 1 2 間の電圧を安定化すると共に、この電圧が所定範囲外となった場合にスイッチ 3 0 6 を遮断して保護を行う。

30

#### 【 0 0 5 4 】

また、電流検出用の抵抗 3 0 3 のポート 2 7 6 との接続点はフューエルゲージ I C 2 0 0 の電源 V s s のポート 2 3 6 が接続される。バッテリパック 3 0 0 の端子 3 1 3 , 3 1 4 にはフューエルゲージ I C 2 0 0 のポート 2 3 1 , 2 3 2 が接続されている。

#### 【 符号の説明 】

#### 【 0 0 5 5 】

1 1 - 1 ~ 1 1 - n 端子

40

1 2 マルチプレクサ

1 3 制御レジスタ

1 5 デルタ・シグマ変調器

1 6 サブクロック内部発振器

1 7 分周器

1 8 シフトレジスタ

1 9 変換ビットカウンタ

2 1 , 2 2 変換結果レジスタ

3 0 C P U

3 1 メモリ

50

## 3.5 割込み制御部

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平06-028313(JP,A)

特開2007-240523(JP,A)

特開2007-243620(JP,A)

特開平01-314023(JP,A)

特開2007-243931(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M3/00-11/00