(12)发明专利

(10)授权公告号 CN 105393453 B

(45)授权公告日 2019.06.28

(21)申请号 201480034272.1

(72)发明人 O·皮本施托克 G·舒佩纳

(22)申请日 2014.04.16

F·盖尔豪森 U·沙赫特

(65)同一申请的已公布的文献号

申请公布号 CN 105393453 A

(74)专利代理机构 北京纪凯知识产权代理有限公司 11245

(43)申请公布日 2016.03.09

代理人 徐东升 赵蓉民

(30)优先权数据

13/863,429 2013.04.16 US

(51)Int.Cl.

H03F 1/36(2006.01)

H03G 3/30(2006.01)

(85)PCT国际申请进入国家阶段日

2015.12.16

(56)对比文件

JP 2006-261866 A, 2006.09.28,

US 005432389 A, 1995.07.11,

CN 1494763 A, 2004.05.05,

(86)PCT国际申请的申请数据

PCT/US2014/034433 2014.04.16

审查员 李佳曦

(87)PCT国际申请的公布数据

W02014/172505 EN 2014.10.23

(73)专利权人 德克萨斯仪器股份有限公司

权利要求书3页 说明书7页 附图4页

地址 美国德克萨斯州

(54)发明名称

具有宽输入电流范围的跨阻抗放大器的装置和方法

(57)摘要

本申请公开一种用于将单端输入电流信号(12)转换为差分输出电压信号(14a、14b)的改进的前置放大器电路(10)，其包括具有根据来自偏置电路(10c)的偏置电流(I1、I2)操作的输入晶体管(Q1、Q2)的第一和第二跨阻抗放大器(10a、10b)、使用自动增益控制(AGC)电路(30)改变的输出晶体管和可调节的反馈阻抗(RF, MRF)以及基准电路(20)，所述基准电路(20)根据板上基准电流(Iref)和来自跨阻抗放大器(10a、10b)的差分输出电压信号(14a、14b)控制偏置电流(I1、I2)。

1. 一种用于将输入电流转换为输出电压的前置放大器电路，所述前置放大器电路包括：

第一跨阻抗放大器，所述第一跨阻抗放大器接收表示所述输入电流的输入信号并提供第一电压输出信号；

第二跨阻抗放大器，所述第二跨阻抗放大器与所述第一跨阻抗放大器匹配并提供第二电压输出信号；

偏置电路，所述偏置电路至少部分地根据基准电流将第一偏置电流和第二偏置电流提供给相应的所述第一跨阻抗放大器和所述第二跨阻抗放大器；

基准电路，所述基准电路至少部分地根据偏移信号控制提供至所述偏置电路的所述基准电流；以及

偏移电路，所述偏移电路根据源自所述第一电压输出信号和第二电压输出信号的差分电压输出信号向所述基准电路提供所述偏移信号；

所述前置放大器电路还包括自动增益控制电路，所述自动增益控制电路至少部分地根据源自所述第一电压输出信号和第二电压输出信号的所述差分电压输出信号控制所述第一跨阻抗放大器和第二跨阻抗放大器的增益；

其中所述第一跨阻抗放大器包括：

第一输入晶体管，所述第一输入晶体管包括接收所述输入信号的基极端子、通过第一电阻器耦合至所述偏置电路的集电极端子和耦合至电路接地节点的发射极端子，所述第一输入晶体管的所述集电极端子提供所述第一电压输出信号，

第一输出晶体管，所述第一输出晶体管具有连接至所述第一输入晶体管的所述集电极端子的基极端子和连接至电压供给节点的集电极端子，

第一反馈电阻器，所述第一反馈电阻器连接在所述第一输出晶体管的发射极端子和所述第一输入晶体管的所述基极端子之间，以及

与所述第一反馈电阻器并联连接的第一增益控制场效应晶体管；

其中所述第二跨阻抗放大器包括：

第二输入晶体管，所述第二输入晶体管包括通过第二电阻器耦合至所述偏置电路的集电极端子和耦合至所述电路接地节点的发射极端子，

第二输出晶体管，所述第二输出晶体管具有连接至所述第二输入晶体管的所述集电极端子的基极端子和连接至所述电压供给节点的集电极端子，第二反馈电阻器，所述第二反馈电阻器连接在所述第二输出晶体管的发射极端子和所述第二输入晶体管的基极端子之间，以及

与所述第二反馈电阻器并联连接的第二增益控制场效应晶体管；并且

其中所述自动增益控制电路至少部分地根据所述差分电压输出信号向所述第一增益控制场效应晶体管和第二增益控制场效应晶体管提供门控信号，以减小所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便增大差分电压输出信号幅度，或者以增大所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便减小差分电压输出信号幅度。

2. 根据权利要求1所述的前置放大器电路，进一步包括DC消除电路，以根据所述偏移信号选择性地除去所述输入信号的DC含量的至少一部分。

3. 根据权利要求2所述的前置放大器电路，其中所述基准电路至少部分地根据所述偏

移信号的幅度的倒数控制所述基准电流以减小所述第一偏置电流和第二偏置电流,并且由此减小所述第一跨阻抗放大器和第二跨阻抗放大器的增益,以便增大差分电压输出信号幅度,或者以增大所述第一偏置电流和第二偏置电流,并且由此增大所述第一跨阻抗放大器和第二跨阻抗放大器的增益,以便减小差分电压输出信号幅度。

4. 一种集成电路装置,其包括:

偏置电路,所述偏置电路包括第一P沟道FET和第二P沟道FET,所述第一P沟道FET和第二P沟道FET具有彼此耦合的栅极端子、耦合至电压供给节点的源极端子和根据在所述栅极端子处的控制电压分别提供第一偏置电流和第二偏置电流的漏极端子;

第一跨阻抗放大器和第二跨阻抗放大器,各自包括:

NPN输入晶体管,所述NPN输入晶体管包括被耦合以通过对应的电阻器接收来自所述偏置电路的所述第一偏置电流和第二偏置电流的集电极端子和耦合至电路接地节点的发射极端子,所述输入晶体管的所述集电极端子提供差分电压输出信号,

NPN输出晶体管,所述NPN输出晶体管具有连接至所述输入晶体管的所述集电极端子的基极端子和连接至所述电压供给节点的集电极端子,以及

反馈电阻器,所述反馈电阻器连接在所述输出晶体管的发射极端子和所述输入晶体管的基极端子之间;

其中所述第一跨阻抗放大器的所述输入晶体管的所述基极端子被连接以接收输入信号,并且所述跨阻抗放大器提供表示所述输入信号的幅度的所述差分电压输出信号;以及

基准电路,所述基准电路提供基准电流输出,以至少部分地根据所述差分电压输出信号并且根据在所述集成电路中产生的基准电流改变提供给所述偏置电路的所述控制电压,从而控制所述第一偏置电流和第二偏置电流。

5. 根据权利要求4所述的集成电路装置,进一步包括N沟道FET,所述N沟道FET耦合在所述第一跨阻抗放大器的所述输入晶体管的所述基极端子和所述电路接地节点之间,并且该N沟道FET具有栅极端子,所述栅极端子至少部分地根据所述差分电压输出信号来控制,以选择性地去除所述输入信号的DC含量的至少一部分。

6. 根据权利要求5所述的集成电路装置,进一步包括自动增益控制电路,所述自动增益控制电路至少部分地根据所述差分电压输出信号控制所述第一跨阻抗放大器和第二跨阻抗放大器的增益。

7. 根据权利要求6所述的集成电路装置,其中各个跨阻抗放大器包括与对应的反馈电阻器并联连接的增益控制场效应晶体管,并且其中所述自动增益控制电路至少部分地根据所述差分电压输出信号向所述增益控制场效应晶体管提供门控信号,以减小所述第一跨阻抗放大器和第二跨阻抗放大器的增益,以便增大差分电压输出信号幅度,或者以增大所述第一跨阻抗放大器和第二跨阻抗放大器的增益,以便减小差分电压输出信号幅度。

8. 根据权利要求7所述的集成电路装置,其中所述基准电路至少部分地根据所述差分电压输出信号的幅度的倒数控制所述基准电流输出,以减小所述第一偏置电流和第二偏置电流,并且由此减小所述第一跨阻抗放大器和第二跨阻抗放大器的增益,以便增大差分电压输出信号幅度,或者以增大所述第一偏置电流和第二偏置电流,并且由此增大所述第一跨阻抗放大器和第二跨阻抗放大器的增益,以便减小差分电压输出信号幅度。

9. 根据权利要求4所述的集成电路装置,进一步包括自动增益控制电路,所述自动增益

控制电路至少部分地根据所述差分电压输出信号控制所述第一跨阻抗放大器和第二跨阻抗放大器的增益；

其中各个跨阻抗放大器包括与对应的反馈电阻器并联连接的增益控制场效应晶体管；并且

其中所述自动增益控制电路至少部分地根据所述差分电压输出信号向所述增益控制场效应晶体管提供门控信号，以减小所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便增大差分电压输出信号幅度，或者以增大所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便减小差分电压输出信号幅度。

10. 根据权利要求9所述的集成电路装置，其中所述基准电路至少部分地根据所述差分电压输出信号的幅度的倒数控制所述基准电流输出，以减小所述第一偏置电流和第二偏置电流，并且由此减小所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便增大差分电压输出信号幅度，或者以增大所述第一偏置电流和第二偏置电流，并且由此增大所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便减小差分电压输出信号幅度。

11. 根据权利要求4所述的集成电路装置，其中所述基准电路至少部分地根据所述差分电压输出信号的幅度的倒数控制所述基准电流输出，以减小所述第一偏置电流和第二偏置电流，并且由此减小所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便增大差分电压输出信号幅度，或者以增大所述第一偏置电流和第二偏置电流，并且由此增大所述第一跨阻抗放大器和第二跨阻抗放大器的增益，以便减小差分电压输出信号幅度。

12. 根据权利要求4所述的集成电路装置，其中所述第一跨阻抗放大器和第二跨阻抗放大器是匹配的。

13. 一种用于将单端输入电流信号转换为差分输出电压信号的前置放大器，其包括：

信号跨阻抗放大器，所述信号跨阻抗放大器包括第一输入晶体管和第一输出晶体管，所述第一输入晶体管具有接收所述单端输入电流信号的基极端子；

虚拟跨阻抗放大器，所述虚拟跨阻抗放大器匹配所述信号跨阻抗放大器，并且包括第二输入晶体管和第二输出晶体管，所述第二输入晶体管不接收输入信号；

其中所述信号跨阻抗放大器和所述虚拟跨阻抗放大器至少部分地根据所述单端输入电流信号并且根据偏置电流源和自动增益控制电路输出信号提供所述差分输出电压信号，所述偏置电流源来源于在所述前置放大器中实现的基准电流源。

## 具有宽输入电流范围的跨阻抗放大器的装置和方法

### 技术领域

[0001] 本发明涉及前置放大器或前置放大电路,更具体地涉及用于将输入电流信号转换成输出电压信号的前置放大器。

### 背景技术

[0002] 前置放大器用于多种应用例如以将从光电二极管输入的信号电流转换成电压信号,以便后续处理,诸如在光纤接收器系统中。诸如这些提供一个或多个跨阻抗放大器或TIA的前置放大器电路,其中两个TIA可用于将单端输入电流信号转换为差分输出电压信号。对于给定应用和相关联的输入电流灵敏度水平,跨阻抗放大器相对于各种性能参数来设计,性能参数包括带宽、增益、增益峰化、群延时和输入参考噪声。然而,需要较宽范围输入电流的应用可能受到饱和效益,潜在地导致一个或多个性能参数的显著劣化,以及在信号路径输出处高脉冲宽度失真(PWD)和确定性抖动(DJ)。因此,仍然需要具有对宽范围的输入电流信号幅度进行可接受的性能参数操作能力的改进的前置放大器和集成电路。

### 发明内容

[0003] 本文涉及前置放大器拓扑结构,所述前置放大器拓扑结构基于输入电流信号的幅度(amplitude)或大小(magnitude)提供跨阻抗放大器操作条件的调节,以促进满足宽输入电流范围的设计参数。不同于传统的设计,本公开的各种概念可被成功地使用,以允许在其中输入信号可以广泛地变化,而无带宽、增益、增益峰化、群延迟、输入参考噪声显著下降和无高脉宽失真或确定性抖动的情况下,应用使用一个或多个跨阻抗放大器的给定的前置放大器设计。

[0004] 本文提供一种前置放大电路,其包括接收输入信号并提供第一电压输出信号的第一跨阻抗放大器,以及与第一跨阻抗放大器匹配的第二跨阻抗放大器,所述第二互阻提供第二电压输出信号。偏置电路至少部分地基于基准电流将第一偏置电流和第二偏置电流提供给相应的跨阻抗放大器。前置放大电路进一步包括基准电路,所述基准电路至少部分地根据偏移信号控制提供给偏置电路的基准电流;和偏移(offset)电路,所述偏移电路根据从第一电压输出信号和第二电压输出信号得到的差分电压输出信号提供偏移信号。使用偏移信号以控制跨阻抗放大器偏置电流可成功地被采用,以有利地促进在宽输入电流范围内进行操作,同时保持可接受的性能参数,从而表现出超过传统前置放大器设计的明显进步。

[0005] 某些前置放大电路进一步包括DC消除电路,以基于偏移信号选择性地有效消除输入信号的直流含量(content)的全部或一部分。在某些实施例中,自动增益控制(AGC)电路可被包括以至少部分地根据差分输出电压信号控制跨阻抗放大器增益。跨阻抗放大器可包括反馈电阻器和与反馈电阻器并联连接的增益控制晶体管,AGC电路向增益控制晶体管提供门控信号以降低跨阻抗传感器增益,以便增大差分电压输出信号幅度,并且反之亦然。此外,在某些实施例中,基准电路至少部分地根据偏移信号幅度的倒数控制基准电流以减小跨阻抗放大器偏置电流,并且由此减小跨阻抗放大器增益,以便增大差分电压输出信号幅

度,并且反之亦然。

[0006] 本公开的进一步的方面提供一种集成电路装置,其包括偏置电路,所述偏置电路具有第一MOSFET和第二MOSFET,所述第一MOSFET和第二MOSFET具有彼此耦合的栅极端子、耦合至电压供给节点的源极端子和根据在所述栅极端子处的控制电压分别提供第一偏置电流和第二偏置电流的漏极端子。集成电路装置还包括第一跨阻抗放大器和第二跨阻抗放大器,其各自包括通过相应的电阻器接收相应的偏置电流的输入晶体管、发射极输出器晶体管(emitter follower transistor)以及连接在发射极输出器晶体管的发射极和输入晶体管的基极端子之间的反馈电阻器。第一跨阻抗放大器的输入晶体管的基极被连接以接收输入信号,并且跨阻抗放大器提供代表输入信号幅度的差分电压输出。在某些实施例中,第一跨阻抗放大器和第二跨阻抗放大器相互匹配。集成电路装置还包括基准电路,所述基准电路提供基准电流输出以至少部分地基于差分电压输出和根据在所述集成电路中产生的基准电流改变偏置电路控制电压,从而控制第一偏置电流和第二偏置电流。这个结构有利地采用了差分电压输出来相应地改变跨阻抗放大器偏置,从而针对输入信号水平的改变自我调节操作,以满足上面提到的设计参数,同时保持低的PWD和DI值,从而便于降低针对高输入信号水平的功率消耗。

[0007] 在某些实施例中,MOSFET耦合在第一放大器输入晶体管的基极端子和电路接地之间,并且至少部分地根据差分电压输出信号被控制以选择性地除去输入信号直流含量的至少一部分。集成电路装置的某些实施例包括AGC电路,所述AGC电路至少部分地根据差分电压输出信号控制第一跨阻抗放大器和第二跨阻抗放大器的增益。此外,在某些实施例中,基准电路至少部分地根据差分电压输出信号幅度的倒数控制基准电流输出,使得减小跨阻抗放大器偏置电流并且因此减小跨阻抗放大器增益,以便增大差分电压输出信号幅度,并且反之亦然。

[0008] 根据本公开的其他方面,提供用于将单端输入电流信号转换为差分输出电压信号的前置放大器。所述前置放大器包括接收单端输入电流信号的信号跨阻抗放大器以及虚拟(dummy)跨阻抗放大器,所述虚拟跨阻抗放大器匹配信号跨阻抗放大器,并且不接收输入信号。所述信号跨阻抗放大器和所述虚拟跨阻抗放大器至少部分地根据输入电流信号和根据偏置电流源以及根据自动增益控制电路信号来提供差分输出电压信号,所述偏置电流源来源于在前置放大器中实现的基准电流源。

## 附图说明

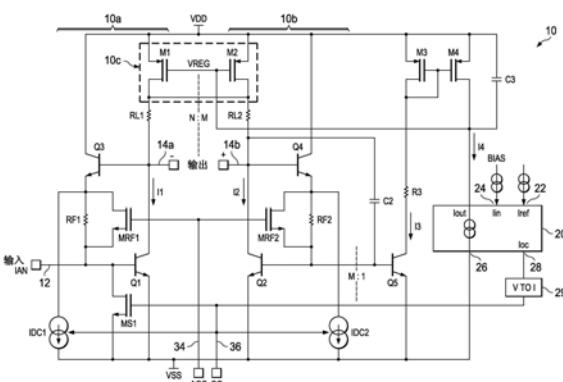

[0009] 图1是根据本公开的某些方面示出具有两个跨阻抗放大器、自动增益控制和偏移消除电路以及基准电路的示例性前置放大器的示意图,其中一个跨阻抗放大器接收单端输入电流信号,自动增益控制和偏移消除电路根据放大的差分电压输出信号提供输出,基准电路至少部分地根据差分电压输出控制TIA偏置电流;

[0010] 图2是进一步示出示例性前置放大器电路实施方式的细节的示意图,其中的基准电路根据偏移消除输入信号经由受控制的基准电流控制偏置电路控制电压,并且增益控制场效应晶体管根据AGC输入信号控制跨阻抗放大器增益,所述AGC输入信号根据差分电压输出得到;

[0011] 图3是示出在图1和2的前置放大器中的示例性自动增益控制和偏移消除电路的示

意图;以及

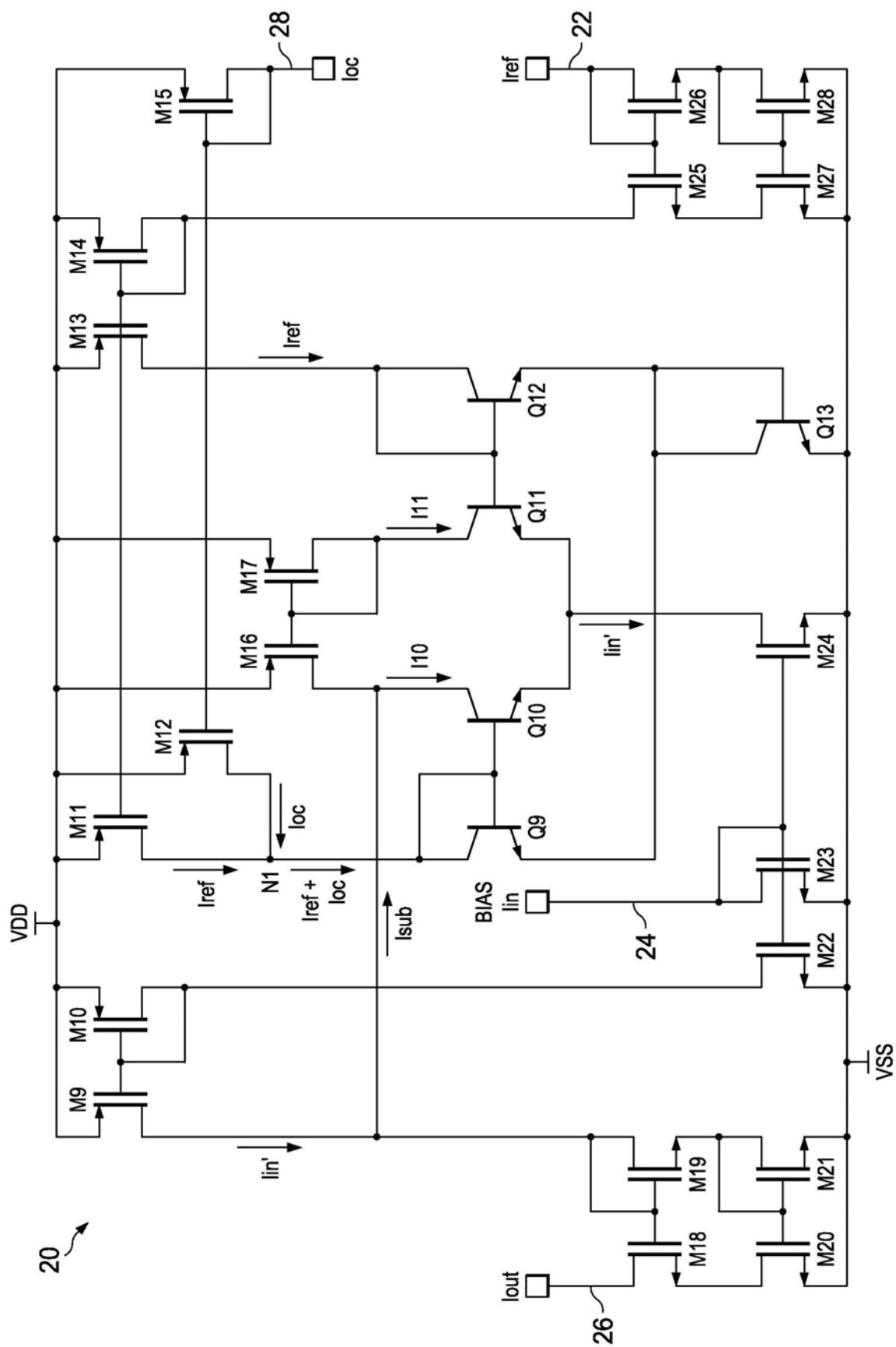

[0012] 图4是进一步详细示出在图1和2的前置放大器中的基准电路细节的示意图。

### 具体实施方式

[0013] 本文提供用于将输入电流信号转换为输出电压信号的同时基于输出电压反馈有利地采用自动增益控制和偏移调节的前置放大器拓扑结构和装置,其可以被实现为在宽范围的输入信号幅度内提供操作,同时维持性能参数在可接受限度内。本文提供了超过现有前置放大器电路设计的显著改进,现有前置放大器电路设计的示例在指派给本公开的受让人的编号7,233,209的美国专利中被说明和描述,其整体通过引用并入本文。

[0014] 图1示出在一个可能的应用中的前置放大器电路装置10,其中输入电流信号IAN接收自光电二极管2,所述光电二极管2连接在前置放大器输入端12和偏置源BIAS之间,其中该图将光电二极管2的电容表示为在输入端12处的光电二极管2的阳极和接地之间连接的电容器C1。在一个非限制性示例中,前置放大器电路10是经由光电二极管2接收光信号的光纤通信系统接收器的一部分,并且前置放大器10提供代表接收自光电二极管2的电流信号的差分电压输出,以便进一步由主机系统(未示出)处理。

[0015] 如图1所示,前置放大器10具有单端输入12和被表示为放大器16的双跨阻抗放大器体系结构,所述双跨阻抗放大器体系结构包括经由端子12接收输入信号的第一跨阻抗放大器或信号跨阻抗放大器或TIA 10a和不接收输入信号的第二跨阻抗放大器或“虚拟”跨阻抗放大器10b。跨阻抗放大器10a和跨阻抗放大器10b在节点14a和节点14b处提供代表从光电二极管2接收的输入电流信号幅度的差分输出电压信号。此外,在该示例中,电压放大器4接收来自节点14a和节点14b的差分输出电压信号,并且将在节点4a和节点4b处放大的差分电压作为输入提供给50 Ω输出缓冲器6。缓冲器6的输出作为整体前置放大器的差分输出在节点8a和8b处被提供,其可以由主机系统诸如光纤接收器(未示出)来使用。在某些实施例中,前置放大器10被构造为单个集成电路(IC),其可以但不必包括电压放大器4和/或输出缓冲器6。在其他实施方式中,前置放大器10作为独立的集成电路来实现,电压放大器4和缓冲器6被单独实现。此外,前置放大器10可能作为功能块被实现在硅上系统(例如,收发器IC)中。

[0016] 电压放大器4的输出还被提供为差分电压输入被提供给自动增益控制(AGC)和偏移消除(OC)电路30。电路30在节点34处提供AGC输出,用于第一TIA 10a和第二TIA 10b的自动增益控制。如图1所示,AGC信号34用作到与TIA反馈电阻器RF1和RF2并联连接的N沟道增益控制MOSFET MRF1和MRF2的栅极驱动信号,使得信号34分别改变TIA 10a和TIA 10b的增益。

[0017] 此外,电路30在节点36处提供由DC消除电路用作输入的偏移消除或OC输出,所述DC消除电路包括耦连在电流信号输入端12和电流接地节点VSS之间的N沟道MOSFET晶体管MS1。在操作中,消除电路晶体管MS1根据至少部分基于OC输出36并且由此基于来自电压放大器4的差分电压输出信号14a、14b的偏移信号36选择性地除去在端子12处的输入信号的DC含量的一部分。这样,输入电流信号的DC含量经由来自AGC/OC电路30的反馈而被减小或消除。

[0018] 此外,如图1中所示,偏移信号36(OC)也经由电压到电流(V至I)电路29作为电流信

号28 (Ioc) 提供给基准电路20。基准电路20控制基准电流I4 (Iout) , 基准电流I4 (Iout) 被用于基于接收的电流信号28以及BIAS电流输入24 (Iin) 和在输入22处接收到的基准电流Iref控制跨阻抗放大器10a和跨阻抗放大器10b的偏置。此外, 提供到输入22的基准电流Iref在前置放大器10的集成电路(未示出)中被生成, 以便跟踪任何过程、电压和/或温度(PVT)变化。此外, 如图1所示, 基准电流I4还可以被用于偏置电压放大器4, 尽管不是本公开的严格需要。

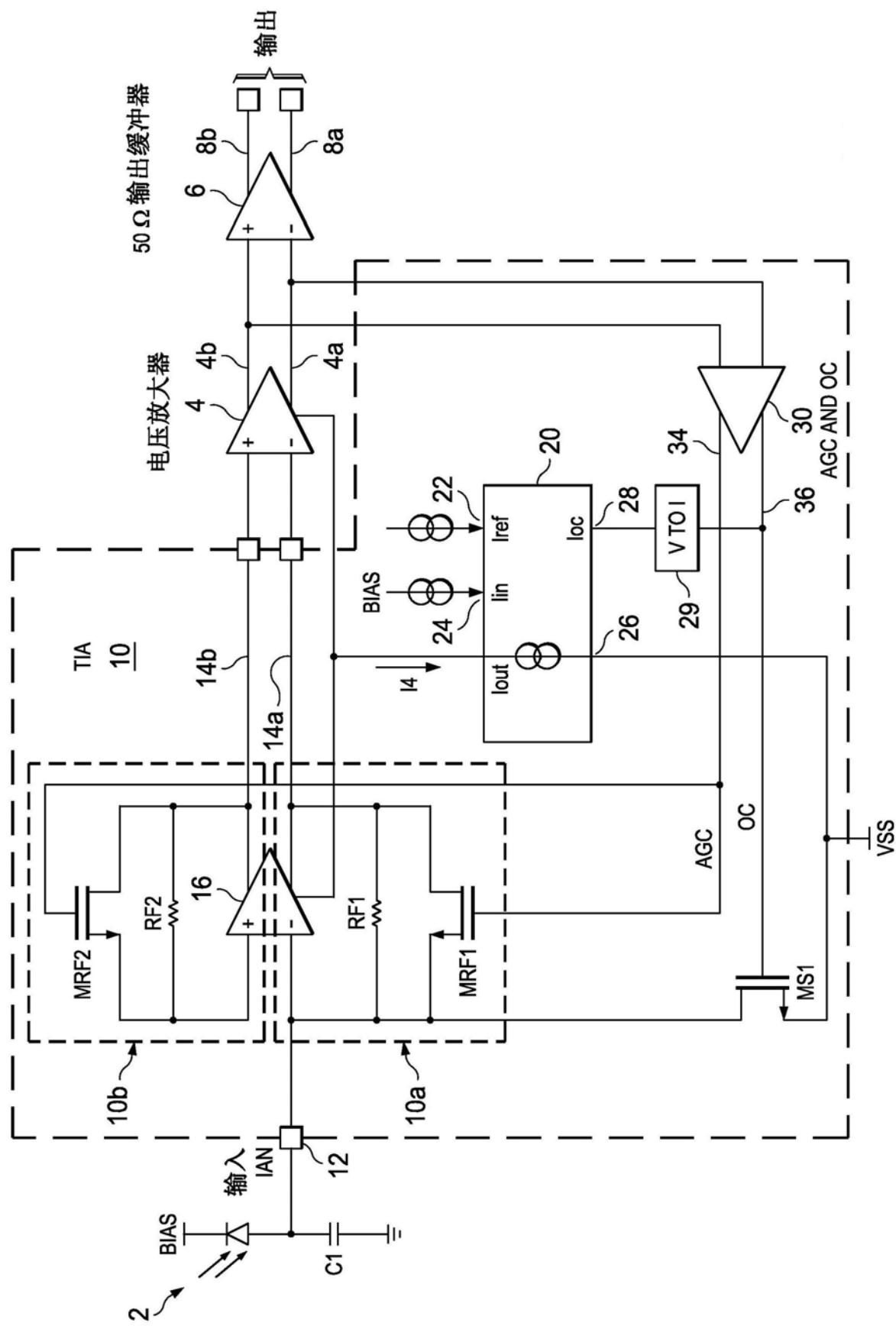

[0019] 图2示出前置放大器电路10的一个可能的非限制性实施例, 其包括第一TIA 10a和第二TIA 10b以及偏置电路10c, 偏置电路10c将第一偏置电流I1和第二偏置电流I2提供给相应的TIA 10a和TIA 10b。在该实施方式中, 第一(信号)TIA 10a包括第一输入晶体管Q1, 所述第一输入晶体管Q1具有接收输入信号12的基极端子, 以及通过第一电阻器RL1耦合到偏置电路10c的集电极和耦合到VSS的发射极端子, 其中Q1的集电极在节点14a处提供第一输出电压信号。此外, 第一TIA 10a包括发射极输出器晶体管Q3以及连接在Q3的发射极和Q1的基极之间的反馈电阻器RF1, 发射极输出器晶体管Q3具有连接到Q1的集电极的基极端子和连接到电源电压节点VDD的集电极。此外, 第一电流源IDC1连接在Q3的发射极和VSS之间。在操作中, Q1的共发射极配置和共集电极输出晶体管Q3基于在Q1的基极处接收的输入电流信号在节点14a处提供输出, 其中反馈电阻器RF1设置跨阻抗增益。此外, 如以上图1所示, 增益控制MOSFET MRF1根据AGC控制信号34操作以选择性地改变Q3的发射极和Q1的基极之间的阻抗, 从而通过RF1的并联反馈阻抗和MRF1的漏极-源极电阻选择性地改变第一跨阻抗放大器10a的增益。

[0020] 在这种配置中, 在没有输入电流的情况下, 在Q3的发射极处的电压等于Q1的基极-发射极电压, 并且Q1的集电极的电压大约为Q3的发射极电压的两倍, 从而反馈电阻器RF1两端的电压近似为零。在这种状况下, 通过Q1的集电极-发射极电流I1约为在偏置电路FET M1和M2的漏极处的电压减去2Vbe后除以RL1的电阻, 并且Q3的集电极电流由DC电流源IDC1设置。以这种方式, 该电路是由偏置电路10c (PVT) 的操作改变的依赖于工艺 (Vbe, RL1)、温度 (温度影响Vbe) 和电源电压VDD而自偏置的。然而, 偏置电路10c的操作及其控制利用根据提供输入22和24的片上基准电流的基准电路20根据差分输出电压14a和14b允许在存在此PVT影响的情况下, 定制(tailoring) 偏置电流I1以维持运行参数在可接受的范围内。因此, 在操作中, 信号TIA 10a在节点14a处提供代表在节点12处所接收的输入电流信号幅度的电压输出。

[0021] 如图2进一步所示, 第二或虚拟TIA 10b包括输入晶体管Q2、发射极输出器晶体管Q4、第二反馈电阻器RF2和耦合在Q4的发射极和Q2的基极之间的相关联的增益控制MOSFET MRF2, 其中输入晶体管Q2具有被耦合以通过第二电阻器RL2接收来自偏置电路10c的偏置电流I2的集电极以及耦合至VSS的发射极, 发射极输出器晶体管Q4包括耦合至VDD的集电极、耦合至在Q2的集电极处的第二输出节点14b的基极和通过第二DC电流源IDC2耦合至VSS的发射极。因此, 如所连接的, 第二TIA 10b没有接收输入信号, 但双TIA结构10a、10b接收单端输入电流信号并且在节点14a和14b处相应地提供差分电压输出。此外, 信号TIA 10a是倒置的(inverting), 由此输入端14a是阴极(-)输出, 且第二输出端14b是阳极(+)输出。第二输出端14b也经由电容器C2电容性耦合至Q2的基极。

[0022] 偏置电路10c包括一对P沟道MOSFET器件M1和M2, 它们的栅极端子相互连接, 并且

它们的漏极端子连接在一起,用于根据栅极电压VREG操作。M1和M2的栅极通过电容器C3被连接至电源电压VDD,从而偏置电路控制电压VREG根据电容器C3两端的电压被设置。虽然M1和M2被示出为并联连接,但是其他实施例是可能的,其中使用单个FET替代,其中栅极根据电压VREG被控制。在操作中,晶体管Q1的集电极电流I1和Q2的集电极电流I2根据晶体管Q1和Q2的相对尺寸相互成比例(scaled)。在示出的示例中,集电极电流I1和I2的这种比例缩放(scaling)对应于下面进一步描述的N:M的比率。

[0023] 偏置电路控制电压VREG通过操作基准电路20来改变,所述基准电路20控制基准电流I4从偏置FET的栅极端子通过基准电路20流向基准电流20的电流输出端子Iout 26到VSS或接地。在操作中,基准电路20根据电流输入信号28和基准电流输入22和24来控制基准电流I4的幅度,如以下结合图4进一步所描述。此外,如图2所示,前置放大器10也包括由P沟道MOSFET M3和M4形成的电流镜,M4的漏极根据流经M3和电阻器R3到晶体管Q5的集电极的电流I3提供电流I4,晶体管Q5的基极端子连接到Q2的基极并且晶体管Q5的发射极连接至所示的VSS。

[0024] 此外,在某些非限制性实施方式中,第一TIA 10a和第二TIA 10b的元件根据比例缩放因子相互匹配。在一个示例中,第一TIA 10a和第二TIA 10b匹配的比例缩放因子被设置为N:M(N>M),以降低功率消耗。然而,在其他实施方式中可使用1:1匹配,或其他实施例中M可以大于N。AGC信号34控制连接在反馈电阻器RF1和RF2两端的增益控制MOSFET MRF1和MRF2以控制双TIA前置放大器的增益,并且OC信号36控制偏移消除电路MS1,以完全地或至少部分地消除在输入12处接收的输入信号IAN的DC含量。由偏移电路30(结合图3在下面进一步描述)提供的OC信号36由电压到电流转换电路29转换,以向基准电路20提供相应的基准电流输入信号28(Ioc)。

[0025] 在图2的实施例中,晶体管Q5产生作为I2的复制的电流I3,其中I3\*M=I2。在一个示例中,电流镜晶体管M3和M4以1:1匹配率匹配,且电流I4是基于I3产生的,其中M4被连接至基准电路20的Iout端。到基准电路20的Iout连接如所示被耦合到偏置电路MOSFET M1和M2的栅极端子并且代表高增益(超镜输出(super mirror output))输出节点以控制在M1和M2的栅极处的偏置电路控制电压VREG,其中电容器C3补偿该控制电压VREG以便稳定。此外,在该配置中,基准电流I4因此被控制等于Iout。

[0026] 通过根据基于前置放大器的差分电压输出的OC信号36操作基准电路20,针对在节点12处接收的小的输入电流IAN,Ioc是非常小的,并且14将等于在BIAS输入24处到基准电路20的偏置电流输入Iin。当输入电流信号IAN增加时,Ioc28也将增加并且将增大偏置电路控制电压VREG,从而减小偏置电流I1和I2。因此,增大的输入电流水平减小TIA 10a和TIA 10b的增益,从而电路10可以既适应小的输入电流信号水平或范围又适应大的输入电流信号水平或范围。此外,AGC反馈回路在整个输入电流范围内保持TIA-级的带宽几乎为常数。因此,TIA 10a和TIA 10b的传递函数质量(transfer function quality)(量级和相位)不随在输入12处所接收的不同的输入电流IAN而显著变化,并且前置放大器增益被自动调节以适应输入信号水平。此外,前置放大器10保持TIA输出幅度适当地小,从而避免或缓解在信号路径晶体管阶段的深度饱和(deep saturation)情况。这有利地促进在宽输入电流范围内的高带宽、低PWD和DJ,并且额外地节省在过载情况下的大量功率。

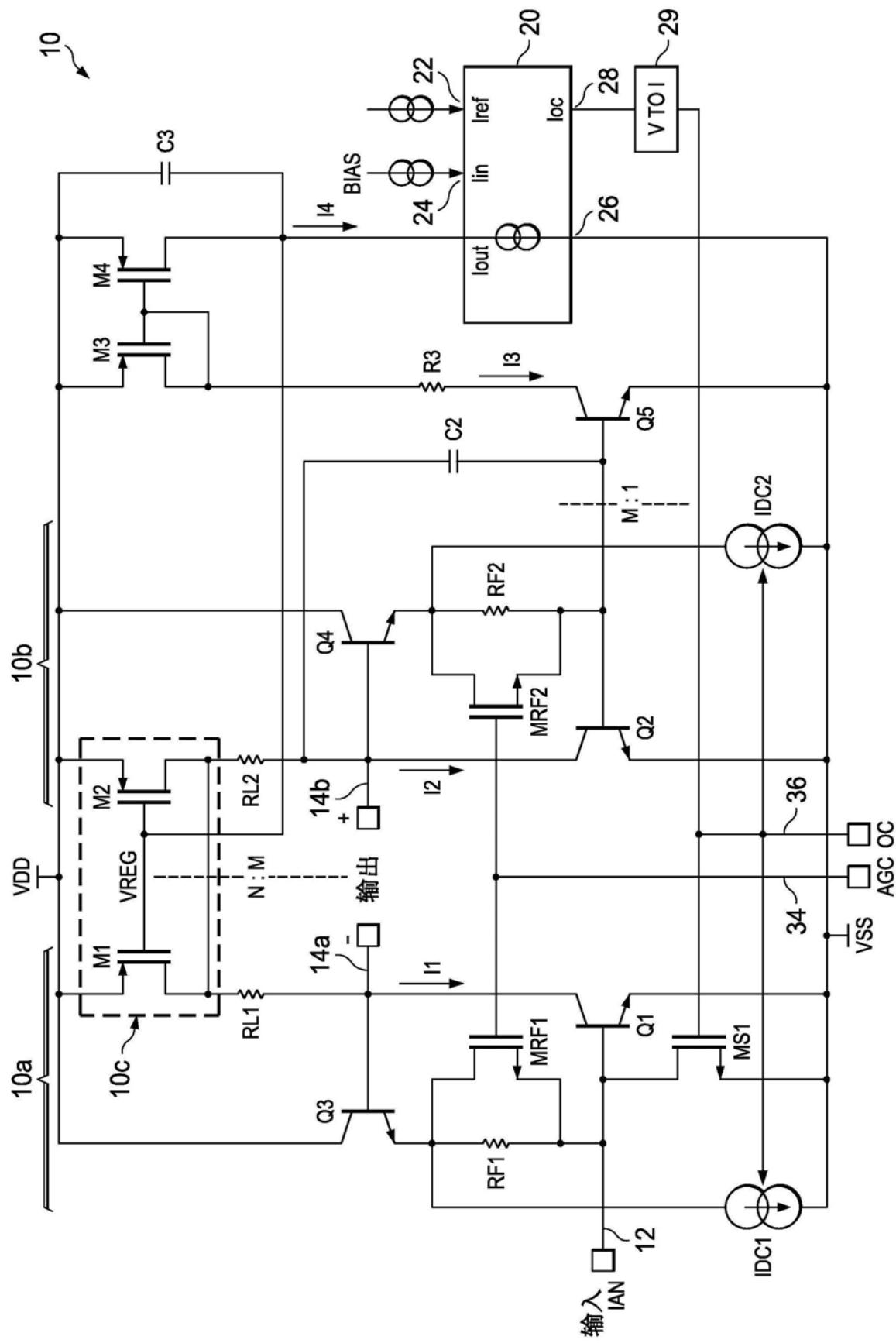

[0027] 图3示出自动增益控制(AGC)和偏移消除(OC)电路(本文也称为偏移电路30)的非

限制性实施方式。如图3所示,电路30接收来自电压放大器4的放大的差分电压输出(图1),但是其他实施方式也是可能的,其中到偏移电路30的输入直接或间接地被提供自由第一TIA 10a和第二TIA 10b提供的差分电压输出端14a和14b。此外,虽然例示的实施例利用对差分输出电压信号幅度做出反应的AGC拓扑结构,但是其他实施方式是可能的,其中AGC电路(例如,电路30)被耦合以接收输入电流信号或更直接地从其衍生(derived)的信号。

[0028] 除AGC输出34之外,偏移电路30提供如上述所使用的OC输出36。在一个示例中,偏移电路30包括偏移消除电路30a,其具有输入电阻器R4和R5以及使用电源电压VDD操作的运算放大器(op amp)32和接地VSS。运算放大器32的输出被提供为OC信号36并且由所示的电容器C4进行稳定,并且运算放大器32的输出还提供由AGC电路部分30b使用的信号。

[0029] AGC电路30b将来自运算放大器输出的信号通过电阻器R2提供给N沟道MOSFET M7和M8的栅极,MOSFET M7和M8的源极端子如图所示连接至VSS。在M8的栅极处的信号控制NPN型晶体管Q7的基极-发射极电压,Q7的集电极通过电阻器R1连接至VDD,并且在Q7的集电极处的电压控制电阻器Q6的基极-发射极电压以设置提供给由M5和M6形成的电流镜的电流。该电流流经M5和晶体管Q8,Q8的基极发射极电压由M7的漏极-源极电压控制,并且因此由运算放大器输出电压控制,电阻器R0和晶体管M7和Q8相应地提供AGC输出电压34。

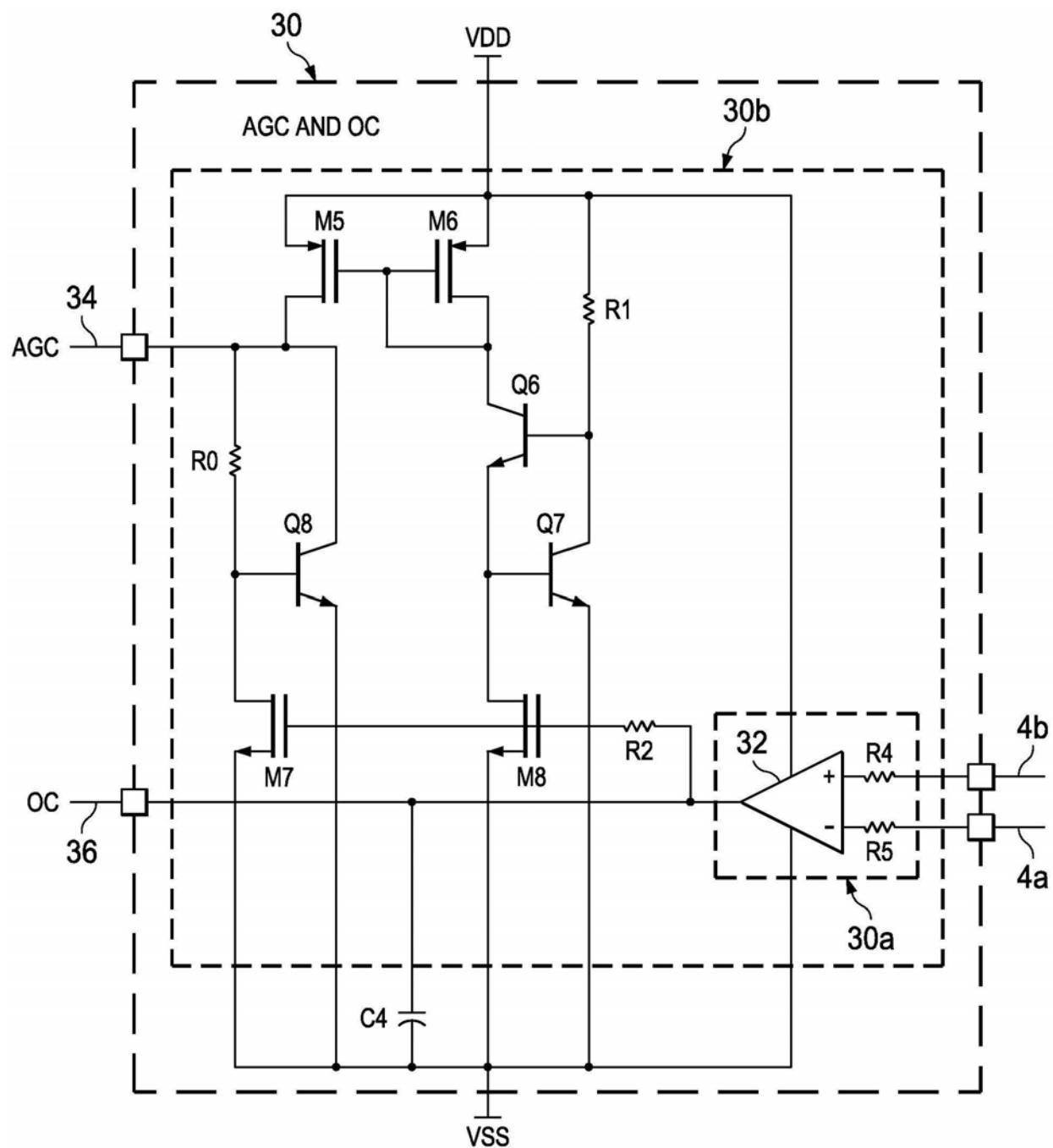

[0030] 现在参考图1、2和4,基准电路20的一个可能的实施方式在图4中示出,其如上所述接收来自端子28的电流输入信号Ioc,接收在端子22处的基准电流、在端子24处的偏置电流输入Iin(BIAS),以及经由端子26控制基准电流I4(Iout)。基准电路20包括由NPN型晶体管Q9-Q12形成的两个象限电流倍增器,Q10和Q11形成共发射极对,所述共发射极对具有由电流源产生的电流Iin',所述电流源由晶体管M23和M24形成。晶体管Q12由恒定电流Iref供应,所述恒定电流Iref基于来自端22的接收的基准电流由电流镜M13和M14产生,并且晶体管Q9由由晶体管M11产生的此电流Iref和由电流镜M12和M15产生的可变电流Ioc供应,所述电流Iref和所述可变电流Ioc在第一节点N1处加和。在操作中,电流I10、I11、Iin'、Iref和Ioc根据以下公式(1)和(2)关联:

[0031]  $I_{10} + I_{11} = I_{in}'$  (1), 和

[0032]  $I_{10}/I_{11} = (I_{ref} + I_{oc})/I_{ref} = K$  (2),

[0033] 其中K是常数。从公式(1)和(2)可以推导出以下公式(3)和(4):

[0034]  $I_{10} = K * I_{11}$  (3), 和

[0035]  $I_{11} = I_{in}' / (K+1)$  (4)。

[0036] 在两个象限电流倍增器Q9-Q12的上方是由晶体管M16和M17形成的电流镜,通过所述电流镜产生差电流Isub或减去的电流Isub,Isub等于电流I10和I11之间的差,根据以下公式(5):

[0037]  $I_{sub} = I_{10} - I_{11}$  (5)。

[0038] 差电流Isub可以通过将根据公式(3)和(4)的电流I10和I11代到公式(5)由以下公式(6)来表征:

[0039]  $I_{sub} = I_{in}' * (K-1) / (K+1)$  (6)。

[0040] 如图4进一步所示,电流源M22引导电流Iin',并且由晶体管M9和M10形成的电流镜产生由M18、M19、M20和M24形成的电流镜的输入电流,从而提供输出电流Iout,Iout等于Iin'和Isub之间的差,如以下公式(7)所示:

- [0041]  $I_{out} = I_{in'} - I_{sub}$  (7)。

- [0042] 将根据公式(6)的 $I_{sub}$ 代入公式(7),产生以下公式(8):

- [0043]  $I_{out} = I_{in'} * 2 / (K+1); K = (I_{ref} + I_{oc}) / I_{ref}$  (8)。

- [0044] 在一个可能的实施例中,  $I_{oc}$ 与TIA输入电流信号 $I_{AN}$ 线性成比例(图1),而 $I_{ref}$ 相对于TIA输入电流保持恒定。因此,在某些实施例中,  $I_{out}$ 是如上述公式(8)所示的 $I_{oc}$ 的倒数,当将 $I_{out}$ 用于偏置TIA输入级时,这是尤其有利的。因此,如上所述,根据在节点12处所接收的电流输入信号 $I_{AN}$ (图1)以及根据偏置电流源10c通过改变偏置电流 $I_1$ 和 $I_2$ 来提供TIA 10a和TIA 10b的差分输出电压。此外,基准电路20至少部分地根据偏移信号36控制提供至偏置电路10c的基准电流 $I_4$ 。偏移信号OC 36进而根据差分电压输出信号来提供,所述差分电压输出信号自身与输入电流信号水平成比例。此外,如图4所示,至少部分地根据在与前置放大器10相同的集成电路中实现的基准电流源 $I_{ref}$ ,并且也根据自动增益控制电路输出信号34,通过操作基准电路20来控制偏置电流 $I_1$ 和 $I_2$ 。

- [0045] 由于 $I_{out}$ 是 $I_{oc}$ 的倒数,基准电路20根据偏移信号36的幅度的倒数控制基准电流 $I_4$ 。这种操作提高了偏置电路控制电压 $V_{REG}$ ,从而降低了偏置电流 $I_1$ 和 $I_2$ ,使得相应地降低了跨阻抗放大器10a和跨阻抗放大器10b的增益,以便增大差分电压输出信号幅度(并且因此以便增大输入电流信号水平)。相反的情况也是正确的,即减小差分输出电压(并且因此减小输入电流信号水平)导致增大的偏置电路控制电压 $V_{REG}$ ,并且因此增加到偏置电流 $I_1$ 和 $I_2$ ,并且相应地增大跨阻抗放大器增益。

- [0046] 因此,本公开通过根据电流输入信号改变TIA偏置(例如,上述偏置电流 $I_1$ 和 $I_2$ )呈现超过现有前置放大器拓扑结构(诸如在编号7,233,209的美国专利中所示的那些)的进步,如经由差分电压输出信号间接地所感测。因此,AGC和偏移消除电路30的使用扩大输入电流信号范围,同时保持了关于带宽、增益、增益峰化、群延时和输入参考噪声的电路性能以及抑制了脉冲宽度失真和确定性抖动。因此,电路10可以适应宽输入信号范围,同时仍通过保持诸如以上提到的那些关键参数在可接受的范围内并且保持PWD和DJ值相对较低来保持优异的电路性能,从而降低针对高输入电流水平的功率消耗。

- [0047] 其他实施例也是可能的,例如,其中AGC电路更直接地测量输入电流信号水平,用于产生信号来相应地调节TIA偏置和/或增益。例如,AGC电路30可以连接到TIA的输入12,以感测在输入12和VSS之间的电压并且相应地提供AGC输出信号34和OC输出信号36。在其他可能的实施方式中,偏移和AGC电路30可以连接到基于TIA输入信号产生控制信号的电路,例如,接收信号强度指示(RSSI)电路(未示出)。此外,如上所述,AGC和偏置消除电路30可替代地直接从节点14a和节点14b接收TIA差分电压输出信号,而不是使用来自电压放大器电路4的输出。

- [0048] 本领域技术人员将认识到,在本发明的范围之内,可以对所描述的实施例进行修改,并且还认识到许多其他实施例是可能的。

图3

图4