(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6495911号

(P6495911)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

(51) Int.Cl.

H05B 37/02 (2006.01)

F 1

H05B 37/02

J

請求項の数 15 (全 11 頁)

(21) 出願番号 特願2016-536244 (P2016-536244)

(86) (22) 出願日 平成26年12月5日 (2014.12.5)

(65) 公表番号 特表2016-539477 (P2016-539477A)

(43) 公表日 平成28年12月15日 (2016.12.15)

(86) 國際出願番号 PCT/EP2014/076660

(87) 國際公開番号 WO2015/082661

(87) 國際公開日 平成27年6月11日 (2015.6.11)

審査請求日 平成29年11月29日 (2017.11.29)

(31) 優先権主張番号 13195842.3

(32) 優先日 平成25年12月5日 (2013.12.5)

(33) 優先権主張国 歐州特許庁 (EP)

(73) 特許権者 516043960

シグニファイ ホールディング ビー ヴ

イ

オランダ国 5656 アーエー アイン

トホーフェン ハイ テク キャンパス

48

(74) 代理人 100163821

弁理士 柴田 沙希子

(72) 発明者 ボーネン パウル テオドラス ヤコブス

オランダ国 5656 アーエー アイン

トホーフェン ハイ テク キャンパス

5

最終頁に続く

(54) 【発明の名称】 LEDの調光を改善するためのブリーダ

(57) 【特許請求の範囲】

【請求項 1】

発光ダイオード回路と、

前記発光ダイオード回路の調光動作を改善するためのブリーダ回路であって、

—電流の振幅の値を検出するための検出回路、及び

—ブリーダ電流を導入するための導入回路であって、前記ブリーダ電流の振幅の値が、前記検出回路からの検出結果に応じて規定される導入回路を含むブリーダ回路と、

—饋電電流を供給するための変換器とを有する装置であって、前記検出回路が、前記変換器によって供給される前記饋電電流を検出するよう構成され、前記饋電電流が、前記発光ダイオード回路の少なくとも一部を流れるよう構成され、前記ブリーダ回路と、前記発光ダイオード回路とが、熱的に結合されている装置。

【請求項 2】

前記饋電電流の前記振幅の相対的に大きい値は、前記ブリーダ電流の前記振幅の相対的に小さい値をもたらし、前記饋電電流の前記振幅の相対的に小さい値は、前記ブリーダ電流の前記振幅の相対的に大きい値をもたらす請求項 1 に記載の装置。

【請求項 3】

前記検出回路が、第1抵抗器回路を有し、前記導入回路が、第1トランジスタ回路を有する請求項 1 に記載の装置。

【請求項 4】

前記第1トランジスタ回路が、単一のトランジスタを有する、又はダーリントン構成の

2つのトランジスタを有する請求項3に記載の装置。

【請求項5】

前記検出回路が、前記第1トランジスタ回路を前記第1抵抗器回路に結合するための第2抵抗器回路を更に有し、前記第2抵抗器回路が、前記第1トランジスタ回路の第1主電極に結合される請求項3に記載の装置。

【請求項6】

前記検出回路が、前記第1トランジスタ回路を制御するための演算増幅器を更に有する請求項5に記載の装置。

【請求項7】

前記検出回路が、前記第1トランジスタ回路を制御するための第2トランジスタ回路を更に有する請求項5に記載の装置。

10

【請求項8】

前記第2トランジスタ回路が、単一のトランジスタを有する請求項7に記載の装置。

【請求項9】

前記第2トランジスタ回路が、差動増幅器構成の2つのトランジスタと、カレントミラー構成の2つのトランジスタとを有する請求項7に記載の装置。

【請求項10】

前記検出回路が、前記第1トランジスタ回路を制御するための第2トランジスタ回路を更に有し、前記第2抵抗器回路が、前記第2トランジスタ回路の電極を介して前記第1トランジスタ回路の第1主電極に結合される請求項5に記載の装置。

20

【請求項11】

前記第2トランジスタ回路が、カレントミラー構成の2つのトランジスタを有する請求項10に記載の装置。

【請求項12】

前記ブリーダ回路の休止中に前記検出回路の少なくとも一部をバイパスするためのバイパス回路を更に有する請求項1に記載の装置。

【請求項13】

前記バイパス回路が、前記検出回路の第1抵抗器回路に対して並列に結合されるダイオード回路を有する請求項12に記載の装置。

30

【請求項14】

前記ブリーダ電流及び前記饋電電流を供給するための変換器を更に有し、一方の前記変換器と、他方の前記ブリーダ回路及び前記発光ダイオード回路とが、熱的に切り離されている請求項1に記載の装置。

【請求項15】

請求項1乃至14のいずれか一項に記載の装置における使用のためのブリーダ回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光ダイオード回路の調光動作を改善するためのブリーダ回路に関する。本発明は、更に、前記ブリーダ回路を有する装置に関する。このような装置の例は、1つ以上の発光ダイオードを有するランプ又は照明器具である。

40

【背景技術】

【0002】

US 2012 / 0268040 A1は、調光器に入る又は調光器を出る電力の電力エンベロープのエッジをモニタ及び追跡するブリーダ回路を開示している(§0031、§0035)。

【0003】

US 2010 / 0090604 A1は、調光器のオフ状態において漏れ電流を検出及びバイパスする回路を開示している。LEDドライバ回路の電流制限器と調光器との間の接続部において検出回路によって電流が検出される。電流制限器とLEDとの間に、LEDに対して並列に接続され、検出回路によって制御される能動素子が、調光器からの漏れ電流をバイパス

50

し得る。この構成は、検出回路及び能動素子のために幾つかの付加的な接続を必要とすることから、複雑である。

#### 【0004】

WO2013 / 011924 A1は、検出ユニットを具備するバイパス回路を開示している。検出ユニットは、調光器から受け取られる電流をモニタする。検出ユニットによって検出される電流が所定の値を超えるとき、バイパス回路を流れる電流が遮断される。この構成は、調光器との接続を必要とする。

#### 【発明の概要】

##### 【発明が解決しようとする課題】

#### 【0005】

本発明の目的は、改善されたブリーダ回路を提供することである。本発明の他の目的は、装置を提供することである。

10

##### 【課題を解決するための手段】

#### 【0006】

第1の態様によれば、発光ダイオード回路の調光動作を改善するためのブリーダ回路であって、前記ブリーダ回路が、

- 電流の振幅の値を検出するための検出回路と、

- ブリーダ電流を導入するための導入回路とを有し、前記ブリーダ電流の振幅の値が、前記検出回路からの検出結果に応じて規定され、前記検出回路が、変換器によって供給される饋電電流を検出するよう構成され、前記饋電電流が、前記発光ダイオード回路の少なくとも一部を流れるよう構成されるブリーダ回路が提供される。

20

#### 【0007】

発光ダイオード回路の調光動作を改善するためのブリーダ回路には、前記発光ダイオード回路（の少なくとも一部）を流れるよう構成される饋電電流の振幅の値を検出するための検出回路が設けられる。この饋電電流は、前記発光ダイオード回路（の少なくとも一部）に給電するよう構成される。前記ブリーダ回路には、更に、前記ブリーダ電流を導入するための導入回路が設けられる。前記検出回路は、前記ブリーダ電流の振幅の値が、前記検出回路からの検出結果に応じて規定されるように、前記導入回路に通知する、且つ／又は前記導入回路を制御する。換言すれば、前記発光ダイオード回路（の少なくとも一部）を流れるよう構成される饋電電流の振幅の値が、ブリーダ電流の振幅の値を導き出すために用いられる。通常、前記ブリーダ電流は、給電目的のために前記発光ダイオード回路（の少なくとも一部）を流れる饋電電流とは違って、前記発光ダイオード回路を流れない。結果として、ブリーダ回路は、前記ブリーダ回路と調光器との間、及び／又は前記ブリーダ回路と変換器との間で如何なる（付加的な）接続もなされる必要なしに、発光ダイオード回路の近くに位置することができる。前記ブリーダ回路は、前記ブリーダ電流の前記振幅の値を規定するために前記饋電電流の前記振幅の値しか用いない。このようなブリーダ回路は、例えば、前記発光ダイオード回路と一緒に組み込まれることができ、前記ブリーダ回路及び前記発光ダイオード回路は、例えば、同じヒートシンクを用いることができる。これらは大きな利点である。

30

#### 【0008】

発光ダイオード回路は、何らかの種類の、何らかの組み合わせの1つ以上の発光ダイオードを有する。通常、前記饋電電流の前記振幅のより小さい値に対して、前記ブリーダ電流の前記振幅は、非ゼロ値を持ち、前記饋電電流の前記振幅のより大きい値に対して、前記ブリーダ電流の前記振幅は、ゼロ値を持つだろう。饋電電流は、前記発光ダイオードの他の部分が作動しないようにされている場合、又は前記他の部分が別の方法で給電される場合に、前記発光ダイオード回路の一部にしか流れない。

40

#### 【0009】

前記ブリーダ回路の実施例は、前記饋電電流の前記振幅の相対的に大きい値は、前記ブリーダ電流の前記振幅の相対的に小さい値をもたらし、前記饋電電流の前記振幅の相対的に小さい値は、前記ブリーダ電流の前記振幅の相対的に大きい値をもたらすことによって

50

、規定される。前記饋電電流の前記振幅の50mAから100mAまでのような相対的に大きい値に対して、前記ブリーダ電流の前記振幅は、例えば、ゼロ値を持ち得る。前記饋電電流の前記振幅の0mAから20mAまで及び20mAから50mAまでのような相対的に小さい値に対して、前記ブリーダ電流の前記振幅は、例えば、線形に及び／又は非線形に、各々、0mAから10mAへ増加し得る、及び10mAから0mAへ減少し得る。他の値も除外されるべきではない。

【0010】

前記ブリーダ回路の実施例は、前記検出回路が、第1抵抗器回路を有し、前記導入回路が、第1トランジスタ回路を有することによって規定される。前記ブリーダ回路のこの実施例は、前記発光ダイオード回路と一緒に容易に組み込まれることができる。

【0011】

前記ブリーダ回路の実施例は、前記第1トランジスタ回路が、単一のトランジスタを有する、又はダーリントン構成の2つのトランジスタを有することによって規定される。1つのトランジスタの形態の第1トランジスタ回路は、単純で、低コストで、ロバストな実施例である。ダーリントン構成の2つのトランジスタの形態の第1トランジスタ回路は、より大きな増幅を供給する。

【0012】

前記ブリーダ回路の実施例は、前記検出回路が、前記第1トランジスタ回路を前記第1抵抗器回路に結合するための第2抵抗器回路を更に有し、前記第2抵抗器回路が、前記第1トランジスタ回路の第1主電極に結合されることによって規定される。前記検出回路内の第2抵抗器回路は、他の回路を介して間接的に、又は間に他の回路がないようにして直接、前記第1抵抗器回路を前記第1トランジスタ回路の第1主電極に結合する。

【0013】

前記ブリーダ回路の実施例は、前記検出回路が、前記第1トランジスタ回路を制御するための演算增幅器を更に有することによって規定される。演算增幅器は、内部基準供給源を持っていてもよく、又は外部基準供給源を用いてもよい。

【0014】

前記ブリーダ回路の実施例は、前記検出回路が、前記第1トランジスタ回路を制御するための第2トランジスタ回路を更に有することによって規定される。第2トランジスタ回路は、1つ以上のトランジスタを有し得る。

【0015】

前記ブリーダ回路の実施例は、前記第2トランジスタ回路が、単一のトランジスタを有することによって規定される。1つのトランジスタの形態の第2トランジスタ回路は、単純で、低コストで、ロバストな実施例である。

【0016】

前記ブリーダ回路の実施例は、前記第2トランジスタ回路が、差動増幅器構成の2つのトランジスタと、カレントミラー構成の2つのトランジスタとを有することによって規定される。差動増幅器構成及びカレントミラー構成を有する第2トランジスタ回路は、前記1つのトランジスタの実施例と比べて、より良い性能を発揮するだろう。

【0017】

前記ブリーダ回路の実施例は、前記検出回路が、前記第1トランジスタ回路を制御するための第2トランジスタ回路を更に有し、前記第2抵抗器回路が、前記第2トランジスタ回路の電極を介して前記第1トランジスタ回路の第1主電極に結合されることによって規定される。前記検出回路内の第2抵抗器回路は、第2トランジスタ回路の形態の他の回路を介して間接的に、前記第1抵抗器回路を前記第1トランジスタ回路の第1主電極に結合する。

【0018】

前記ブリーダ回路の実施例は、前記第2トランジスタ回路が、カレントミラー構成の2つのトランジスタを有することによって規定される。カレントミラー構成を有する第2トランジスタ回路は、良好な熱安定性を供給するだろう。

【0019】

10

20

30

40

50

前記ブリーダ回路の実施例は、前記ブリーダ回路の休止中に前記検出回路の少なくとも一部をバイパスするためのバイパス回路を更に有することによって規定される。前記ブリーダ回路の休止中に前記検出回路の少なくとも一部をバイパスするとき、電力消費は減らされる。

【0020】

前記ブリーダ回路の実施例は、前記バイパス回路が、前記検出回路の第1抵抗器回路に対して並列に結合されるダイオード回路を有することによって規定される。例えば1つ以上のダイオードを有するダイオード回路の形態のバイパス回路は、単純で、低成本で、ロバストな実施例である。

【0021】

第2の態様によれば、上で規定されているようなブリーダ回路を有すると共に、発光ダイオード回路を更に有する装置であって、前記ブリーダ回路と、前記発光ダイオード回路とが、熱的に結合されている装置が提供される。好ましくは、前記ブリーダ回路と、前記発光ダイオード回路とが、熱的に結合されている。それらのうちの一方が、相対的に多くの電力を放散しているとき、通常、他方は、相対的に少ない電力しか放散しないだろう。

【0022】

前記装置の実施例は、前記ブリーダ電流及び前記饋電電流を供給するための変換器を更に有し、一方の前記変換器と、他方の前記ブリーダ回路及び前記発光ダイオード回路とが、熱的に切り離されていることによって規定される。好ましくは、一方の前記変換器と、他方の前記ブリーダ回路及び前記発光ダイオード回路とが、両ユニットを熱的に十分に分離するよう、熱的に切り離されるだろう。

【0023】

洞察は、ブリーダ回路は、好ましくは、発光ダイオード回路の近くに位置するだろうというものである。基本的なアイデアは、ブリーダ電流の振幅の値は、前記ブリーダ回路と調光器との間、及び／又は前記ブリーダ回路と変換器との間の（付加的な）接続を回避するよう、前記発光ダイオード回路の少なくとも一部を流れるよう構成される饋電電流の振幅の値の検出に応じて規定されるべきであるというものである。

【0024】

改善されたブリーダ回路を提供する課題は解決された。他の利点は、前記ブリーダ回路は、前記発光ダイオード回路と一緒に組み込まれることができる、並びに前記ブリーダ回路及び前記発光ダイオード回路は、同じヒートシンクを用いることができる、である。

【0025】

下記の実施例を参照して、本発明のこれら及び他の態様を説明し、明らかにする。

【図面の簡単な説明】

【0026】

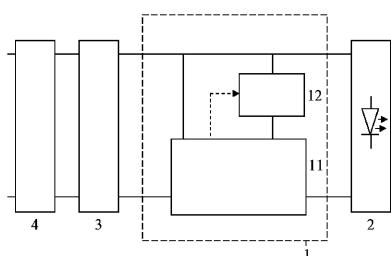

【図1】概観を示す

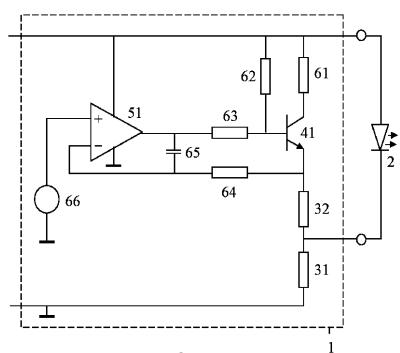

【図2】ブリーダ回路の第1実施例を示す。

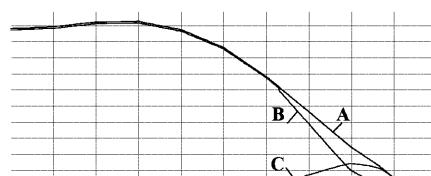

【図3】第1実施例の波形を示す。

【図4】ブリーダ回路の第2実施例を示す。

【図5】ブリーダ回路の第3実施例を示す。

【図6】ブリーダ回路の第4実施例を示す。

【発明を実施するための形態】

【0027】

図1においては、概観が示されている。発光ダイオード回路2の調光動作を改善するためのブリーダ回路1は、発光ダイオード回路2の少なくとも一部を流れるよう構成される饋電電流の振幅の値を検出回路11を有すると共に、ブリーダ電流を導入するための導入回路12を有する。ブリーダ電流の振幅の値は、検出回路11からの検出結果に応じて規定される。ブリーダ回路1の入力端子は、例えば、スイッチモード電源などであるが、他の種類の変換器を除外しない変換器3の出力端子に結合される。変換器3の入力端子は、

10

20

30

40

50

例えば、従来のトライアック調光器などであるが、他の種類の調光器を除外しない（フェーズカット）調光器4の出力端子に結合される。調光器4の入力端子は、主電源に結合される。

【0028】

好ましくは、饋電電流の振幅の相対的に大きい値は、ブリーダ電流の振幅の相対的に小さい値をもたらし、饋電電流の振幅の相対的に小さい値は、ブリーダ電流の振幅の相対的に大きい値をもたらすだろう。発光ダイオード回路2が相対的に多くの電力を放散しているとき、ブリーダ回路1は、通常、相対的に少ない電力しか放散せず、逆の場合も同じであるだろう。

【0029】

図2においては、ブリーダ回路1の第1実施例が示されている。ブリーダ回路1の第1入力端子は、ブリーダ回路1の第1出力端子に結合される。ブリーダ回路1の第2入力端子は、ここでは、単一の抵抗器の形態であるが、1つより多くの抵抗器を備える実施例も除外されるべきではない第1抵抗器回路31を介して、ブリーダ回路1の第2出力端子に結合される。ブリーダ回路1は、ここでは、単一のトランジスタの形態であるが、例えばダーリントン構成において2つ以上のトランジスタを備える実施例も除外されるべきではない第1トランジスタ回路41を有する。第1トランジスタ回路41の第1主電極は、第2抵抗器回路32を介して、ブリーダ回路1の第2出力端子及び第1抵抗器回路31に結合される。第2抵抗器回路32は、ここでは、単一の抵抗器を有するが、1つより多くの抵抗器を備える実施例も除外されるべきではない。第1トランジスタ回路41の第2主電極は、抵抗器61を介して、ブリーダ回路1の第1出力端子に結合される。抵抗器61は、第1トランジスタ回路41における電力放散を減らすが、ブリーダ回路1の基本動作に影響を及ぼさずに省略され得る。第1トランジスタ回路41の制御電極は、抵抗器62を介してブリーダ回路1の第1出力端子に結合されると共に、抵抗器63を介して演算增幅器51の出力部に結合される。抵抗器62は、制御電極電流を第1トランジスタ回路41の制御電極に送ることを可能にする。第1トランジスタ回路41の第1主電極は、抵抗器64を介して演算增幅器51の反転入力部に結合される。演算增幅器51の非反転入力部は外部基準供給源66を介してアースに結合され、ブリーダ回路1の第2入力端子もアースに結合される。他の例においては、内部（内蔵）基準供給源を備える演算增幅器が用いられてもよい。演算增幅器51の出力部は、コンデンサ65を介して演算增幅器51の反転入力部に結合される。

【0030】

ブリーダ回路1の出力端子に結合される発光ダイオード回路2を流れる饋電電流の振幅が、小さすぎる値をとるや否や、抵抗器回路31の両端の電圧の振幅は、小さすぎる値をとり、演算增幅器51は、ブリーダ電流を導入するよう第1トランジスタ回路41を制御する。結果として、発光ダイオード回路2の出力強度が相対的に小さい場合でも、調光器4はトラブルを起こさないだろう。通常、第1抵抗器回路31及び第2抵抗器回路32及び演算增幅器51が、検出回路11の一部を形成し、第1トランジスタ回路41が、導入回路12の一部を形成する。

【0031】

図3においては、図2に示されている第1実施例の波形が示されており、垂直軸は、電力（0ワット乃至8ワット）又は電流（0mA乃至500mA）であり、水平軸は、調光器の導通角（180°乃至0°）である。波形Aは、変換器2を介して伝達される電力（又は変換器3を流れる電流）を示しており、波形Bは、発光ダイオード回路2において放散される電力（又は発光ダイオード回路2を流れる饋電電流）を示しており、波形Cは、ブリーダ回路1において放散される電力（又はブリーダ電流）を示している。この例によれば、ブリーダ回路1なしでは、20%を下回る減光は不可能である。ブリーダ回路1によって、3%までの減光が可能になっている（波形Aと波形Bと間の差）。明らかに、ブリーダ回路1が、所謂深い調光を可能にする。これは、大きな利点である。深い調光における正確な利得は、変換器3の伝達関数に依存する。

10

20

30

40

50

## 【0032】

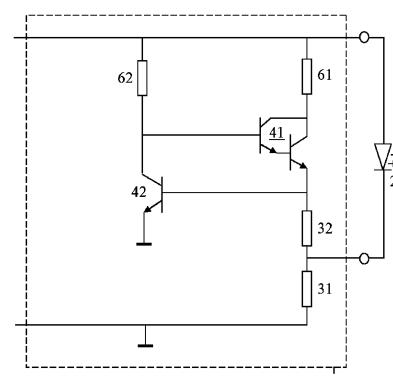

図4においては、ブリーダ回路1の第2実施例が示されている。ブリーダ回路1の第1入力端子は、ブリーダ回路1の第1出力端子に結合される。ブリーダ回路1の第2入力端子は、ここでは、単一の抵抗器の形態であるが、1つより多くの抵抗器を備える実施例も除外されるべきではない第1抵抗器回路31を介して、ブリーダ回路1の第2出力端子に結合される。ブリーダ回路1は、ここでは、ダーリントン構成の2つのトランジスタの形態であるが、3つ以上のトランジスタを備える実施例も除外されるべきではない第1トランジスタ回路41を有する。第1トランジスタ回路41の第1主電極は、第2抵抗器回路32を介して、ブリーダ回路1の第2出力端子及び第1抵抗器回路31に結合される。第2抵抗器回路32は、単一の抵抗器を有するが、1つより多くの抵抗器を備える実施例も除外されるべきではない。第1トランジスタ回路41の第2主電極は、抵抗器61を介して、ブリーダ回路1の第1出力端子に結合される。抵抗器61は、第1トランジスタ回路41などにおける電力放散を減らす。第1トランジスタ回路41の制御電極は、抵抗器62を介してブリーダ回路1の第1出力端子に結合されると共に、ここでは、単一のトランジスタの形態であるが、2つ以上のトランジスタを備える実施例も除外されるべきではない第2トランジスタ回路42の第2主電極に結合される。第2トランジスタ回路42の第1主電極はアースに結合され、ブリーダ回路1の第2入力端子もアースに結合される。第2トランジスタ回路42の制御電極は、第1トランジスタ回路41の第1主電極に結合される。

10

## 【0033】

20

ブリーダ回路1の出力端子に結合される発光ダイオード回路2を流れる電流の振幅が、小さすぎる値をとるや否や、抵抗器回路31の両端の電圧の振幅は、小さすぎる値をとり、第2トランジスタ回路42は、ブリーダ電流を導入するよう第1トランジスタ回路41を制御する。結果として、発光ダイオード回路2の出力強度が相対的に小さい場合でも、調光器4はトラブルを起こさないだろう。通常、第1抵抗器回路31及び第2抵抗器回路32及び第2トランジスタ回路42が、検出回路11の一部を形成し、第1トランジスタ回路41が、導入回路12の一部を形成する。

## 【0034】

30

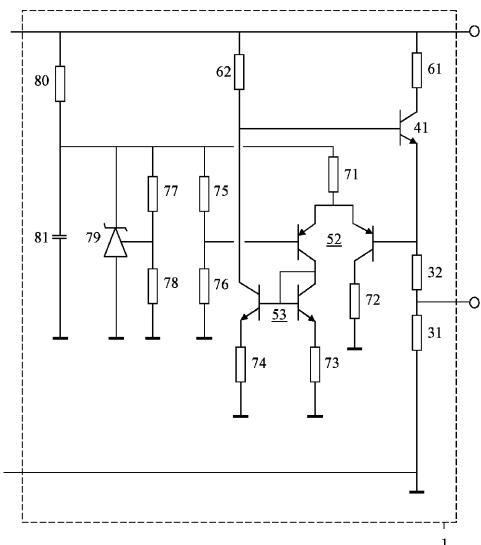

図5においては、ブリーダ回路1の第3実施例が示されている。ブリーダ回路1の第1入力端子は、ブリーダ回路1の第1出力端子に結合される。ブリーダ回路1の第2入力端子は、ここでは単一の抵抗器などの形態の第1抵抗器回路31を介して、ブリーダ回路1の第2出力端子に結合される。ブリーダ回路1は、ここでは単一のトランジスタなどの形態の第1トランジスタ回路41を有する。第1トランジスタ回路41の第1主電極は、第2抵抗器回路32を介して、ブリーダ回路1の第2出力端子及び第1抵抗器回路31に結合される。第2抵抗器回路32は、単一の抵抗器などを有する。第1トランジスタ回路41の第2主電極は、抵抗器61を介して、ブリーダ回路1の第1出力端子などに結合される。第1トランジスタ回路41の制御電極は、抵抗器62を介してブリーダ回路1の第1出力端子に結合されると共に、2つのトランジスタを有するカレントミラー構成53の第1入力部に結合される。カレントミラー構成53の第1出力部は抵抗器74を介してアースに結合され、ブリーダ回路1の第2入力端子もアースに結合される。カレントミラー構成53の第2入力部は、2つのトランジスタを有する差動増幅器構成52の第1出力部に結合される。カレントミラー構成53の第2出力部は、抵抗器73を介してアースに結合される。

40

## 【0035】

差動増幅器構成52の第2出力部は、抵抗器72を介してアースに結合される。差動増幅器構成52の給電入力部は、抵抗器71を介して、抵抗器80とコンデンサ81との間の相互接続部に結合される。抵抗器80は、更に、ブリーダ回路1の第1入力端子に結合され、コンデンサ81は、更に、アースに結合される。差動増幅器構成52の第1制御入力部は、抵抗器75を介して前記相互接続部に結合されると共に、抵抗器76を介してアースに結合される。前記相互接続部は、更に、電圧基準素子79を介してアースに結合さ

50

れ、電圧基準素子 7 9 の制御電極は、抵抗器 7 7 を介して前記相互接続部に結合されると共に、抵抗器 7 8 を介してアースに結合される。差動増幅器構成 5 2 の第 2 制御入力部は、第 1 パワートランジスタ回路 4 1 の第 1 主電極に結合される。図 5 に示されているブリーダ回路 1 の第 3 実施例は、図 4 に示されているブリーダ回路 1 の第 2 実施例と比べると、差動増幅器構成 5 2 及びカレントミラー構成 5 3 のために、より良い性能を発揮するだろう。通常、差動増幅器構成 5 2 及びカレントミラー構成 5 3 は、検出回路 1 1 などの一部を形成するだろう。

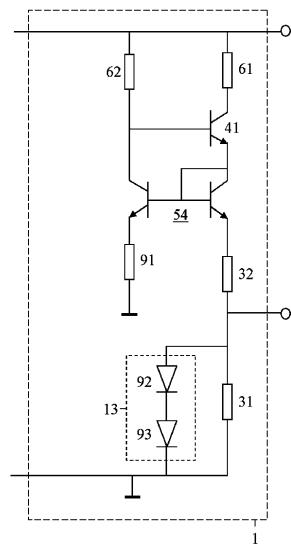

#### 【 0 0 3 6 】

図 6 においては、ブリーダ回路 1 の第 4 実施例が示されている。ブリーダ回路 1 の第 1 入力端子は、ブリーダ回路 1 の第 1 出力端子に結合される。ブリーダ回路 1 の第 2 入力端子は、ここでは単一の抵抗器などの形態の第 1 抵抗器回路 3 1 を介して、ブリーダ回路 1 の第 2 出力端子に結合される。ブリーダ回路 1 は、ここでは単一のパワートランジスタなどの形態の第 1 パワートランジスタ回路 4 1 を有する。第 1 パワートランジスタ回路 4 1 の第 1 主電極は、第 2 パワートランジスタ回路 5 4 及び第 2 抵抗器回路 3 2 を介して、ブリーダ回路 1 の第 2 出力端子及び第 1 抵抗器回路 3 1 に結合される。第 2 抵抗器回路 3 2 は、単一の抵抗器などを有し、第 2 パワートランジスタ回路 5 4 の電極を介して第 1 パワートランジスタ回路 4 1 の第 1 主電極に結合される。第 2 パワートランジスタ回路 5 4 は、ここでは、カレントミラー構成の 2 つのパワートランジスタを有する。第 1 パワートランジスタ回路 4 1 の第 2 主電極は、抵抗器 6 1 を介して、ブリーダ回路 1 の第 1 出力端子などに結合される。第 1 パワートランジスタ回路 4 1 の制御電極は、抵抗器 6 2 を介してブリーダ回路 1 の第 1 出力端子に結合されると共に、カレントミラー構成 5 4 の第 1 入力部に結合される。カレントミラー構成 5 4 の第 1 出力部は、抵抗器 9 1 を介して、アースに結合される。カレントミラー構成 5 4 の第 2 入力部及び第 2 出力部は、前記電極を形成する。通常、カレントミラー構成 5 4 は、検出回路 1 1 などの一部を形成するだろう。このカレントミラー構成 5 4 は、良好な熱安定性を供給する。

#### 【 0 0 3 7 】

好ましくは、ブリーダ回路 1 の第 4 実施例に示されているように、ブリーダ回路 1 は、電力消費を減らすためにブリーダ回路 1 の休止中に検出回路 1 1 の少なくとも一部をバイパスするためのバイパス回路 1 3 を更に有し得る。バイパス回路 1 3 は、例えば、検出回路 1 1 の第 1 抵抗器回路 3 1 に対して並列に結合されるダイオード回路 9 2、9 3 を有し得る。このようなダイオード回路 9 2、9 3 は、1 つのダイオードを有してもよく、又は例えば直列に結合される 2 つ以上のダイオードを有してもよい。

#### 【 0 0 3 8 】

2 つの素子は、第 3 の素子を介して間接的に結合されてもよく、又は間に第 3 の素子が結合されずに直接結合されてもよい。示されている前記実施例において、前記実施例のうちの或る実施例の一部は、前記実施例のうちの別の実施例に付加されてもよく、前記実施例のうちの或る実施例の一部は、前記実施例のうちの別の実施例の別の一部に取って代わってもよい。

#### 【 0 0 3 9 】

要約すると、ブリーダ回路 1 は、発光ダイオード回路 2 に給電するための饋電電流の振幅の値を検出するための検出回路 1 1 を有すると共に、ブリーダ電流を導入するための導入回路 1 2 を有する。ブリーダ電流の振幅の値は、前記検出回路 1 1 からの検出結果に応じて規定される。結果として、前記ブリーダ回路 1 と調光器 4 との間の不利な接続は回避され、前記ブリーダ回路 1 は、前記発光ダイオード回路 2 の近くに位置することができ、それらは、同じヒートシンクを用いることができる。前記検出回路 1 1 は、第 1 抵抗器回路 3 1 を有してもよく、前記導入回路 1 2 は、第 1 パワートランジスタ回路 4 1 を有してもよい。前記検出回路 1 1 は、前記第 1 パワートランジスタ回路 4 1 を前記第 1 抵抗器回路 3 1 に結合するための第 2 抵抗器回路 3 2 を更に有してもよく、前記第 1 パワートランジスタ回路 4 1 を制御するための演算増幅器 5 1 又は第 2 パワートランジスタ回路 4 2 を有してもよい。

#### 【 0 0 4 0 】

本発明を、図面において図示し、上記の説明において詳細に説明しているが、このよう

10

20

30

40

50

な図及び説明は、説明的なもの又は例示的なものとみなされるべきであって、限定するものとみなされるべきではない。本発明は、開示されている実施例に限定されない。請求項に記載の発明を実施する当業者は、図面、明細及び添付の請求項の研究から、開示されている実施例に対する他の変形を、理解し、達成し得る。請求項において、「有する」という用語は、他の要素又はステップを除外せず、単数形表記は、複数の存在を除外しない。単に、特定の手段が、相互に異なる従属請求項において引用されているという事実は、これらの手段の組み合わせが有利になるように用いられることができないことを示すものではない。請求項におけるいかなる参照符号も、範囲を限定するものとして解釈されてはならない。

【図 1】

Fig. 1

【図 2】

Fig. 2

【図 3】

Fig. 3

【図 4】

Fig. 4

【図5】

Fig. 5

【図6】

Fig. 6

---

フロントページの続き

(72)発明者 ホンテーレ ベルトランド ヨハン エドワード

オランダ国 5656 ア-エ- アイントホーフェン ハイ テク キャンパス 5

審査官 山崎 晶

(56)参考文献 特開2011-003467 (JP, A)

国際公開第2013/094700 (WO, A1)

特表2012-520562 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H05B 37/02 - 39/10

F21V 23/00 - 99/00