(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3952271号

(P3952271)

(45) 発行日 平成19年8月1日(2007.8.1)

(24) 登録日 平成19年5月11日(2007.5.11)

(51) Int.C1.

F 1

|                     |                  |            |   |

|---------------------|------------------|------------|---|

| <b>H01L 21/82</b>   | <b>(2006.01)</b> | H01L 21/82 | F |

| <b>H01L 23/52</b>   | <b>(2006.01)</b> | H01L 21/88 | M |

| <b>H01L 21/3205</b> | <b>(2006.01)</b> | H01L 21/88 | S |

請求項の数 10 (全 18 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2002-23995 (P2002-23995)    |

| (22) 出願日  | 平成14年1月31日 (2002.1.31)        |

| (65) 公開番号 | 特開2003-229483 (P2003-229483A) |

| (43) 公開日  | 平成15年8月15日 (2003.8.15)        |

| 審査請求日     | 平成16年12月9日 (2004.12.9)        |

|           |                                                    |

|-----------|----------------------------------------------------|

| (73) 特許権者 | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号  |

| (74) 代理人  | 100090273<br>弁理士 國分 孝悦                             |

| (72) 発明者  | 佐藤 元伸<br>愛知県春日井市高蔵寺町二丁目1844番<br>2 富士通ヴィエルエスアイ株式会社内 |

| (72) 発明者  | 鍵渡 裕志<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内        |

| (72) 発明者  | 澤田 豊治<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内        |

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

少なくともCuを含有する材料からなる配線及びWを材料とするヒューズを含む配線構造を備えてなる半導体装置であつて、

前記ヒューズは、当該ヒューズの切断部位と高電圧印加側との間の所定部位のみが蛇行状構造とされていることを特徴とする半導体装置。

## 【請求項2】

前記蛇行状構造は多層に形成されていることを特徴とする請求項1に記載の半導体装置。

## 【請求項3】

少なくともCuを含有する材料からなる配線及びWを材料とするヒューズを含む配線構造を備えてなる半導体装置であつて、

前記ヒューズは、当該ヒューズの切断部位と高電圧印加側との間の所定部位のみが分岐構造とされていることを特徴とする半導体装置。

## 【請求項4】

前記分岐構造は、多層に形成されていることを特徴とする請求項3に記載の半導体装置。

## 【請求項5】

少なくともCuを含有する材料からなる配線及びWを材料とするヒューズを含む配線構造を備えてなる半導体装置であつて、

10

20

前記ヒューズは、当該ヒューズの切断部位と高電圧印加側との間の所定部位のみが幅広構造、厚膜構造、又は、幅広構造及び厚膜構造とされていることを特徴とする半導体装置。

**【請求項 6】**

前記Wを材料とするヒューズに代えて、A1を含有する金属又は多結晶シリコンからなるヒューズとすることを特徴とする請求項1～5のいずれか1項に記載の半導体装置。

**【請求項 7】**

少なくともCuを含有する材料からなる配線を所定形状に形成する工程と、切断部位と高電圧印加側との間の所定部位のみが蛇行状構造となる、Wを材料とするヒューズを形成する工程と

を含むことを特徴とする半導体装置の製造方法。

10

**【請求項 8】**

前記蛇行状構造を多層に形成することを特徴とする請求項7に記載の半導体装置の製造方法。

**【請求項 9】**

少なくともCuを含有する材料からなる配線を所定形状に形成する工程と、切断部位と高電圧印加側との間の所定部位のみが幅広構造、厚膜構造、又は、幅広構造及び厚膜構造となる、Wを材料とするヒューズを形成する工程と

を含むことを特徴とする半導体装置の製造方法。

**【請求項 10】**

前記Wを材料とするヒューズに代えて、A1を含有する金属又は多結晶シリコンからなるヒューズとすることを特徴とする請求項7～9のいずれか1項に記載の半導体装置の製造方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、配線及び冗長用のヒューズを有する配線構造を備えてなる半導体装置及びその製造方法、並びにヒューズの切断方法に関し、特に配線が少なくとも銅(Cu)を含有する材料からなる配線構造を備えた半導体装置に適用して好適である。

**【0002】**

**【従来の技術】**

近年では、半導体素子の高集積化とチップサイズの縮小化に伴い、配線の微細化及び多層配線化が加速的に進められている。こうした多層配線を有するロジックデバイスにおいては、配線遅延がデバイス信号遅延の支配的要因の1つになりつつある。デバイスの信号遅延は配線抵抗値と配線容量の積に比例しており、従って配線遅延の改善のためには、配線抵抗値や配線容量の軽減が重要である。

**【0003】**

そこで、配線抵抗を低減するため、Cu配線を形成することが検討されている。特に、配線遅延に大きく影響を及ぼすグローバル配線部分において、低誘電率膜とCu配線を組み合わせることによりデバイス性能向上に大きく寄与する。

**【0004】**

ところで、通常の半導体デバイスにおいては、配線等の冗長性を持たせるために、冗長用のヒューズが設けられる。ヒューズは通常、配線に用いる金属と兼ねて形成することが便宜に資するが、Cuを材料として配線を形成する場合、耐湿性の観点からヒューズにもCuを材料に用いることは困難である。そこでこの場合、ヒューズの材料には、耐湿性に優れた金属、例えばタンゲステン(W)が用いられている。

**【0005】**

**【発明が解決しようとする課題】**

しかしながら、冗長用ヒューズの材料に耐湿性を考慮してWを用いた場合、ヒューズ切断の有無を確認するためのバイアス電圧の印加により当該ヒューズの切断箇所から腐食(コ

10

20

30

40

50

ロージョン)が進行し易く、最終的には切断したヒューズに短絡が生じるという問題がある。

#### 【0006】

この問題は、電源投入時以外にはバイアス電圧の印加されない、いわゆるノンバイアス回路の形態に比して、特に電源投入後には常にバイアス電圧が印加されるバイアス回路の形態に顕著である。ノンバイアス回路にはその性質上、当然に余分な構成要素が多く、チップ面積の増大を招来する不都合があり、従ってバイアス回路の形態が好ましいことから、冗長用ヒューズの切断によるコロージョン発生の問題を無視することはできない。

#### 【0007】

そこで本発明は、前記問題に鑑みてなされたものであり、配線(特にCuを含有する配線)と共に配線構造を構成するヒューズについて、当該ヒューズのコロージョン耐性を高め、切断によるコロージョンの発生を抑制して、将来の更なる大規模集積化に十分対応することを可能とする半導体装置及びその製造方法、並びにヒューズの切断方法を提供することを目的とする。10

#### 【0008】

##### 【課題を解決するための手段】

本発明者は、鋭意検討の結果、以下に示す発明の諸態様に想到した。

#### 【0009】

本発明は、少なくともCuを含有する材料からなる配線に適用して好適であり、当該配線及び、Wを材料とするヒューズを含む配線構造を備えてなる半導体装置及びその製造方法を対象とし、前記ヒューズが、当該ヒューズの切断部位と高電圧印加側との間の所定部位のみが蛇行状構造とされている。20

また、前記ヒューズが、当該ヒューズの切断部位と高電圧印加側との間の所定部位のみが分岐構造とされている。

また、前記ヒューズが、当該ヒューズの切断部位と高電圧印加側との間の所定部位のみが幅広構造、厚膜構造、又は、幅広構造及び厚膜構造とされている。

#### 【0012】

##### 【発明の実施の形態】

###### - 本発明の作用原理的説明 -

先ず初めに、本発明の作用原理について説明する。

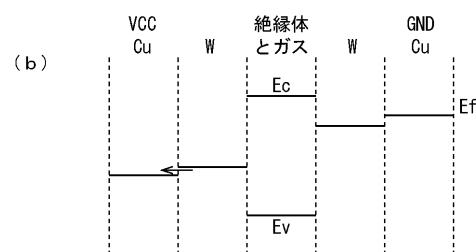

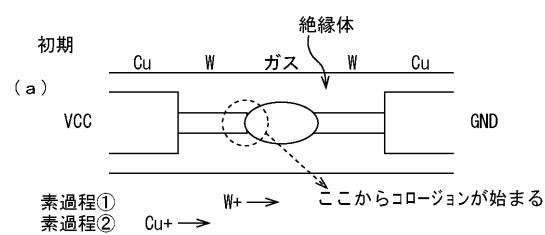

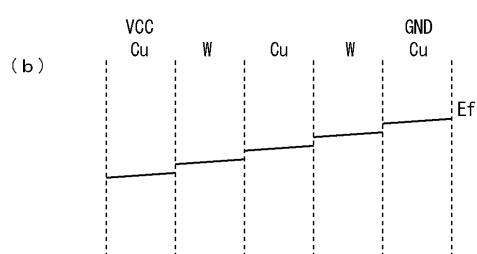

図1及び図2は、冗長用ヒューズの切断により腐食(コロージョン)が発生するメカニズムを説明するための模式図であり、図1が初期状態、図2が末期状態を表し、更に各々の図について(a)が冗長用ヒューズ近傍の様子を示す平面図、(b)が(a)に対応したエネルギー bandwidth図である。30

#### 【0013】

図1(a)に示すように、切断初期の冗長用ヒューズにバイアス電圧を印加すると、図1(b)のようなエネルギー bandwidthが形成される。このように、CuとWのフェルミレベルは階段状となる。なお切断部位は、雰囲気ガスや周辺の層間絶縁膜を介して接続されると見なせることから、図1(b)では当該切断部位を絶縁体として表している。

#### 【0014】

接地(GND)側のCuとWは、常に電子供給があるために酸化しない。一方、高電圧印加(Vcc)側のCuとWは、GND側からの電子供給がないために酸化反応が生じ易い状態となる。ここで、「高電圧印加側」とは、冗長用ヒューズの両端のうち電圧の高い側のことを言う。特に、Vcc側のWはCuに電子を取られるため、酸化反応は先ず電子供給のないWの切断端から生じる(W → W<sup>n+</sup> + n<sup>e-</sup>)。

#### 【0015】

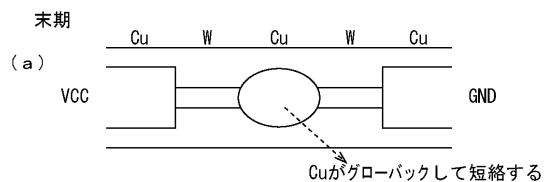

そして、Wの酸化が進行してCuまで達すると、WからCuへの電子供給がなくなり、Cuの酸化反応が生じる(Cu → Cu<sup>n+</sup> + n<sup>e-</sup>)。ここで生じたCu<sup>n+</sup>は電界によってGND方向へ力が働きグローバックする。グローバックしたCu<sup>n+</sup>はGND側のWや雰囲気ガスから電子供給がなされて還元され、ヒューズの切断部位に析出する。最終的には、多量

10

20

30

40

50

に析出したCuにより、図2(a)のようにヒューズに短絡が生じることになる。このとき、図2(b)のようにエネルギー・バンドにおける絶縁体に相当する障壁は消失する。

#### 【0016】

本発明では、上記のメカニズムによる短絡の発生を遅延させ、装置の保証寿命を確保する観点から、ヒューズの所定部位、具体的には当該ヒューズの切断部位と高電圧印加側との間に形状的な腐食遅延構造を設けるか、または当該ヒューズを耐腐食性材料で構成する。前者の腐食遅延構造としては、後述するように、蛇行状構造や幅広・厚膜構造、分岐構造等が考えられる。後者の耐腐食性材料としては、A1を含有する金属や不純物を添加した多結晶シリコン等が好適である。このようにヒューズを構成することにより、切断部位から高電圧印加側の端まで間のヒューズ長を大きくしたり、その間のヒューズ体積を増加させることができが可能となり、Cuを含有する配線材料を用いた場合では、Cu<sup>n+</sup>のグローバック開始時間を大幅に遅延させることができ、保証寿命の確保が実現する。

#### 【0017】

##### - 具体的な実施形態 -

以下、上述した本発明の作用原理を踏まえ、本発明を適用した好適な諸実施形態について、図面を参照しながら詳細に説明する。

#### 【0018】

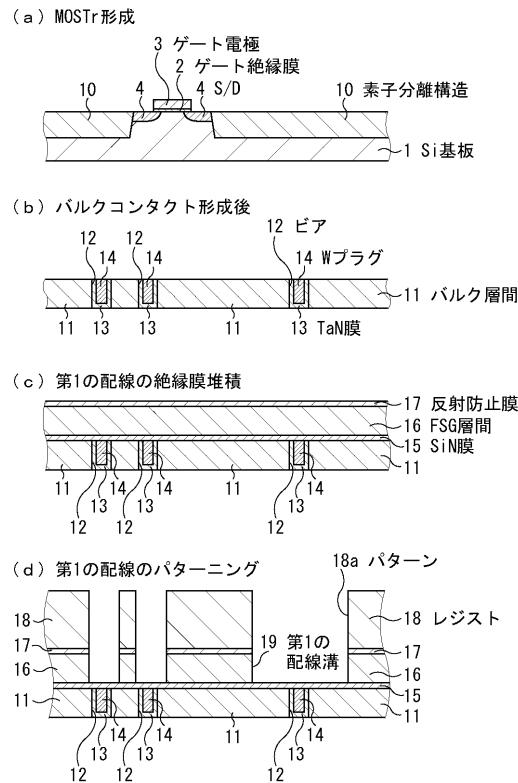

##### (MOSトランジスタ構造の形成)

先ず、半導体基板上にMOSトランジスタ構造を形成する。

具体的には、図3(a)に示すように、シリコン半導体基板1上でLOCOS法やSTI法等により素子分離を行う。ここではSTI法等により、半導体基板1に形成された溝内を絶縁物で充填してなる素子分離構造10を形成し、素子活性領域を画定する。

#### 【0019】

次に、半導体基板1上にSiO<sub>2</sub>またはSiONからなる薄いゲート絶縁膜2を形成した後、この上に多結晶シリコン膜を形成し、多結晶シリコン膜及びゲート絶縁膜2をパターニングして、半導体基板1上にゲート絶縁膜2を介したゲート電極3を形成する。そして、ゲート電極3をマスクとしてゲート電極3の両側における半導体基板1の表層に不純物をイオン注入してソース/ドレイン4を形成し、MOSトランジスタ構造とする。

#### 【0020】

##### (配線構造の形成)

続いて、配線構造を形成する。

なお便宜上、以下の図3(b)～図10(b)では、上記した半導体基板1及びMOSトランジスタ構造の図示を省略する。

#### 【0021】

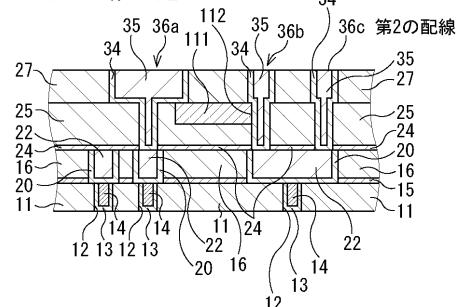

先ず、図3(b)に示すように、半導体基板1を覆うように層間絶縁膜11を堆積形成した後、層間絶縁膜11に下層配線と通じるビアホール12を開孔形成する。次に、ビアホール12の内壁を覆うようにTiN等の下地膜13を形成し、ビアホール12を埋め込む膜厚にW膜を堆積形成して、このW膜を化学機械研磨(CMP)してビアホール12のみにWが充填されてなるWプラグ14を形成する。

#### 【0022】

続いて、図3(c)に示すように、層間絶縁膜11及びWプラグ14上にSiN膜15を膜厚30nm程度に形成する。次に、SiN膜15上にFSG(fluoro-silicate glass)からなる層間絶縁膜16を膜厚500nm程度に堆積形成した後、フォトリソグラフィーの露光に対する反射防止膜17を形成する。

#### 【0023】

続いて、図3(d)に示すように、フォトレジスト18を塗布し、フォトリソグラフィーによりフォトレジスト18を加工して、各Wプラグ14上で開口する配線溝パターン18aを形成する。次に、フォトレジスト18をマスクとし、SiN膜15をエッティングストップとして、反射防止膜17及び層間絶縁膜16をドライエッティングする。

#### 【0024】

10

20

30

40

50

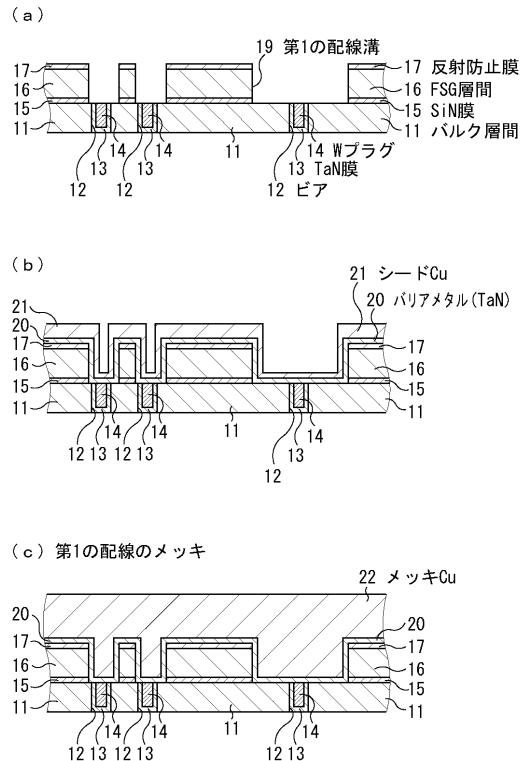

続いて、図4(a)に示すように、フォトレジスト18を灰化処理等により除去した後、更にSiN膜15をドライエッチングして層間絶縁膜11及び各Wプラグ14の表面を露出させ、配線溝パターンに倣った第1の配線溝19を形成する。

#### 【0025】

続いて、図4(b)に示すように、TaNからなるバリアメタル膜20を膜厚25nm程度に、更にシード金属膜としてCu膜21を膜厚200nm程度にクラスター化されたスピッタ装置により真空中で連続的に堆積形成する。ここで、RF処理とバリアメタル膜20及びCu膜21の形成は真空中で連続的に行なうことが望ましい。

#### 【0026】

続いて、図4(c)に示すように、バリアメタル20を電極として、メッキ法により第1の配線溝19内を埋め込む膜厚、ここでは1μm程度にCu膜22を形成する。10

#### 【0027】

続いて、図5(a)に示すように、ダマシン法によるCu膜22の分離のため、CMP法によりCu膜22(21)及びバリアメタル膜20を研磨して第1の配線溝19内のみにCu膜22を残し、第1の配線23を形成する。

#### 【0028】

続いて、図5(b)に示すように、第1の配線23の表面の拡散バリア(パッシベーション)となるSiN膜24を膜厚70nm程度に堆積形成した後、SiN膜24上にFGSからなる層間絶縁膜25を膜厚700nm程度に形成する。

#### 【0029】

そして、層間絶縁膜25にタンゲステン(W)からなる冗長用ヒューズ111を形成する。20

具体的には、層間絶縁膜25にヒューズ溝112を深さ700nm程度、幅0.50μm程度にパターン形成する。ここでヒューズ溝112は、その上面形状として、所定部位が蛇行形状となるように形成される。

#### 【0030】

続いて、このヒューズ溝112を埋め込むように層間絶縁膜25上にW膜を堆積した後、CMP法によりW膜を研磨して平坦化する。これにより、ヒューズ溝102のみをW膜で充填してなり、その上面形状の所定部位が蛇行形状とされた冗長用ヒューズ111が形成される。なお、この冗長用ヒューズの材料としては、Wに限定されるものではなく、Cu以外で耐湿性に優れた金属(導電材料)であれば良い。30

#### 【0031】

続いて、冗長用ヒューズ111の形成された層間絶縁膜25上にFGSからなる層間絶縁膜27を膜厚700nm程度に形成し、更に反射防止膜28を形成する。

#### 【0032】

続いて、図5(c)に示すように、フォトレジスト29を塗布し、フォトリソグラフィーによりフォトレジスト29を加工して、各第1の配線23上で開口する開孔パターン29aを形成する。

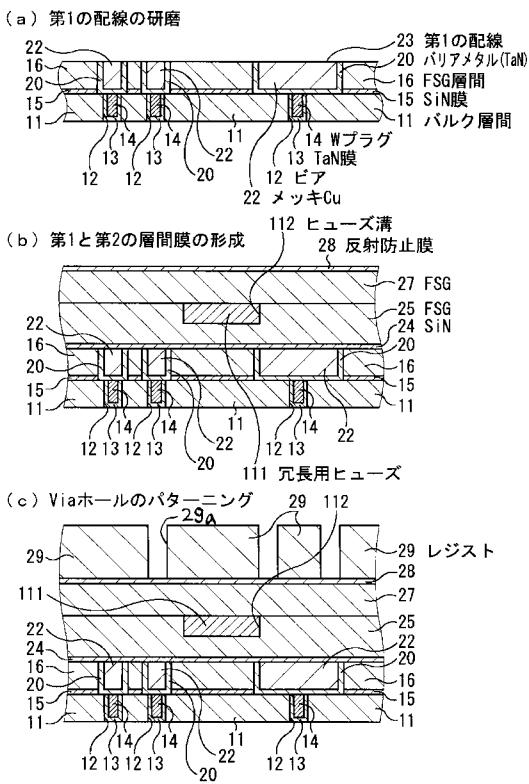

#### 【0033】

続いて、図6(a)に示すように、フォトレジスト29をマスクとし、SiN膜24をエッチングストッパーとして、反射防止膜28、層間絶縁膜27、SiN膜26及び層間絶縁膜25をドライエッチングして、開孔パターン29aの形状に倣ったビアホール30を形成する。次に、フォトレジスト29を灰化処理等により除去する。40

#### 【0034】

続いて、図6(b)に示すように、形成されたビアホール30の下方部位に、第1の配線23の表面酸化を防止する処置としてレジスト等からなる保護材料31を埋め込む。

#### 【0035】

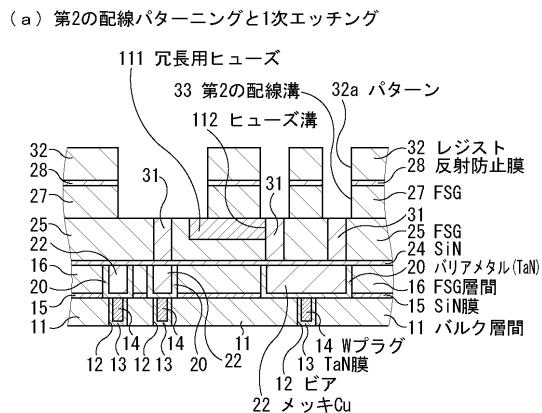

続いて、図7(a)に示すように、フォトレジスト32を塗布し、フォトリソグラフィーによりフォトレジスト32を加工して、各ビアホール30上で開口する配線層パターン32aを形成する。次に、フォトレジスト32をマスクとし、反射防止膜28及び層間絶縁膜25をドライエッチングして、開孔パターン32aの形状に倣ったビアホール33を形成する。50

膜 27 をドライエッチングして、配線層パターン 32a の形状に倣った第 2 の配線溝 33 を形成する。このとき第 2 の配線溝 33 を、隣接する当該第 2 の配線溝 33 の一端部位から冗長用ヒューズ 111 の表面の一部が露出するように形成する。

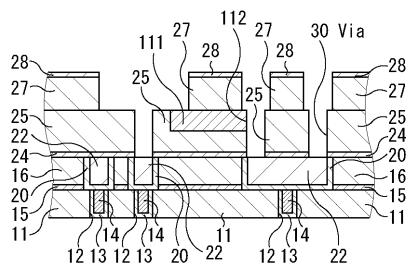

#### 【0036】

続いて、図 7 (b) に示すように、フォトレジスト 32 及び保護材料 31 を灰化処理等により除去した後、ピアホール 30 の底部に残る SiN 膜 24 及び第 2 の配線溝 33 の底部に残る SiN 膜 26 を全面ドライエッチングにより除去する。このとき、第 2 の配線溝 33 とピアホール 30 とが一体となる。

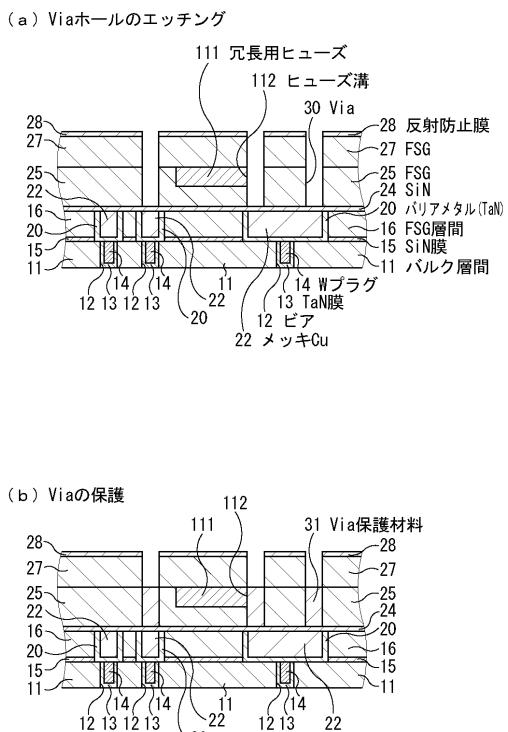

#### 【0037】

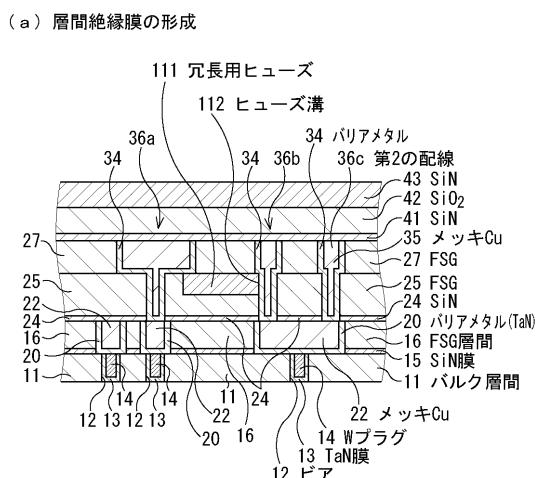

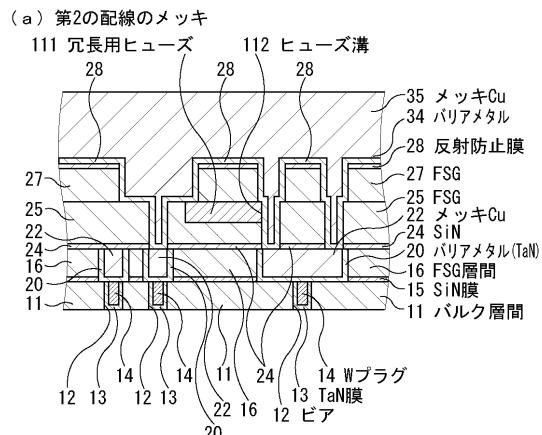

続いて、図 8 (a) に示すように、TaN からなるバリアメタル膜 34 を膜厚 25 nm 程度に、更にシード金属膜として Cu 膜 (不図示) を膜厚 200 nm 程度にスパッタ装置により真空中で連続的に堆積形成する。次に、バリアメタル 34 を電極として、メッキ法により第 2 の配線溝 33 及びピアホール 30 内を埋め込む膜厚、ここでは 1 μm 程度に Cu 膜 35 を形成する。

10

#### 【0038】

続いて、図 8 (b) に示すように、ダマシン法による Cu 膜 22 の分離のため、CMP 法により Cu 膜 35 及びバリアメタル膜 34 を研磨して第 2 の配線溝 35 及びピアホール 30 内のみに Cu 膜 35 を残した後、ウェット処理により洗浄して第 2 の配線 36a, 36b, 36c を形成し、第 1 の配線 23 及び第 2 の配線 36a, 36b, 36c からなる配線を完成させる。このとき、隣接する下層配線、図示の例では第 2 の配線 36a, 36b がバリアメタル膜 34 を介して冗長用ヒューズ 111 と接続され、前記配線及び冗長用ヒューズ 111 を含む配線構造が完成する。

20

#### 【0039】

しかる後、図 9 に示すように、カバー膜として SiN 膜 41、SiO<sub>2</sub> 膜 42 及び SiN 膜 43 をそれぞれ膜厚 100 nm 程度、400 nm 及び 300 nm 程度に形成し、前記配線構造を有する半導体装置を完成させる。

#### 【0040】

##### (冗長用ヒューズの具体的構成)

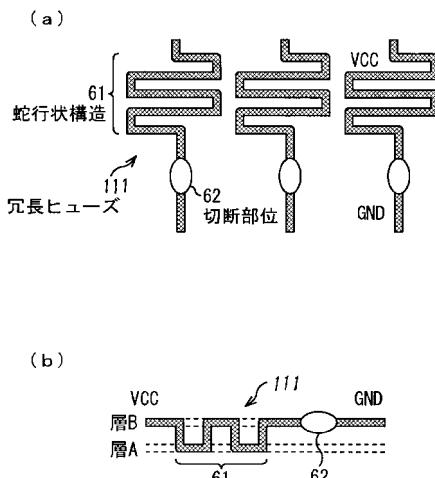

本実施形態では、図 10 (a) に示すように、W からなる冗長用ヒューズ 111 には、その一端側、ここでは高電圧 (Vcc) が印加される第 2 の配線 36a 側の近傍に形状的な腐食遅延構造、ここでは蛇行状構造 61 が設けられている。この場合、冗長用ヒューズ 111 の他端側、ここでは接地電位 (GND) となる第 2 の配線 36b 側と蛇行状構造 61 との間に、切断部位 62 が設けられている。

30

#### 【0041】

このように、冗長用ヒューズ 111 に蛇行状構造 61 を設けることにより、切断部位 62 から高電圧印加側の端まで間のヒューズ長を実質的に大きくし、当該部位のヒューズ体積を増加することができ、Cu<sup>n+</sup> のグローバック開始時間を大幅に遅延させることができとなり、装置の保証寿命の確保が実現する。

#### 【0042】

更に、図 10 (b) に示すように、冗長用ヒューズ 111 を蛇行状構造 61 の部位で多層、図示の例ではヒューズ層を 2 層に形成し、2 層間にわたって更に上下方向に蛇行するよう、当該冗長用ヒューズ 111 を構成してもよい。このように冗長用ヒューズ 111 を多層化することにより、多層配線構造を利用して、上下のヒューズ層を相互に接続し、ヒューズ材料を上下方向 (縦方向) に湾曲させることができる。この多層化により、切断部位 62 から高電圧印加側の端 (第 2 の配線 36a) まで間のヒューズ長及びヒューズ体積を更に大きくすることが可能となり、小さい面積で所望のヒューズ長が得られ、装置の保証寿命の確保に資する。

40

#### 【0043】

##### (冗長用ヒューズの切断による不良発生試験)

ここで、図 10 (a) に示す冗長用ヒューズ 111 について、比較例 1 ~ 3 との比較に基

50

づき、ノンバイアス回路構成及びバイアス回路構成の両者について耐湿性加速試験を行った結果を説明する。

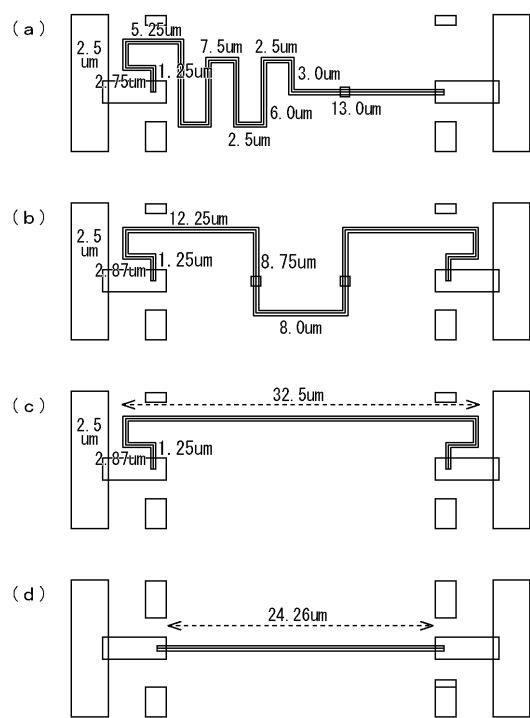

#### 【0044】

この耐湿性加速試験では、本実施形態の冗長用ヒューズをサンプル1(図11(a))、比較例1~3の冗長用ヒューズをサンプル2~4(図11(a)~(d))とし、各々について温度85℃、湿度85%、印加電圧2Vの条件でレーザ光照射による切断時からの蓄積時間を約2000時間として、各サンプルにおける不良発生率を算出した。

#### 【0045】

各比較例としては、サンプル4(図11(d))が従来用いられている直線形状の冗長用ヒューズであり、サンプル3(図11(c))が両端部位にそれぞれ1回の小さな蛇行状構造を設けたもの、サンプル2(図11(b))が両端部位にそれぞれ1回の小さな蛇行状構造を設け、更に中央部位に1回の蛇行状構造を設けたものである。

#### 【0046】

各冗長用ヒューズの切断部位については、本実施形態の冗長用ヒューズであるサンプル1が切断部位62と同様に蛇行状構造61と高電圧印加側の端との間の1箇所とし、サンプル2~4が中心部位近傍の2箇所とする。なお、従来の冗長用ヒューズでは一般的に、切断部位を2箇所設けることにより、切断の確実性が担保され、装置寿命を延ばすことができる。

#### 【0047】

バイアス回路構成の試験結果を表1に示す。

#### 【0048】

#### 【表1】

| 切断部位から高電圧印加側までの<br>長さ(μm) 幅(μm) 厚み(μm) 体積(μm³) |      |     |     |       | 不良発生率 |

|------------------------------------------------|------|-----|-----|-------|-------|

| サンプル1                                          | 54.7 | 0.5 | 0.7 | 19.15 | 0.19  |

| サンプル2                                          | 23.6 | 0.5 | 0.7 | 8.26  | 0.79  |

| サンプル3                                          | 15.3 | 0.5 | 0.7 | 5.36  | 0.97  |

| サンプル4                                          | 7.4  | 0.5 | 0.7 | 2.59  | 1     |

#### 【0049】

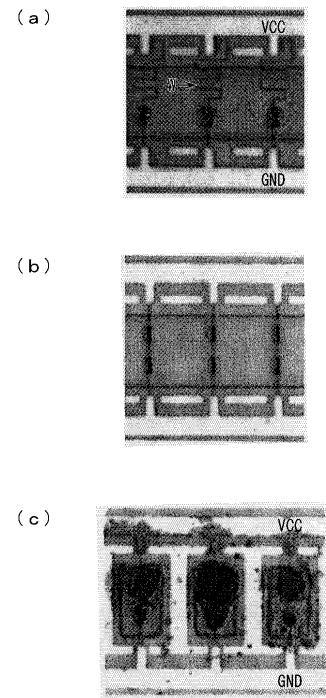

図12は、サンプル1とサンプル4について実際に耐湿性加速試験を行った様子を示す顕微鏡写真である。(a)がサンプル1の累積時間経過後の状態、(b)がサンプル4の切断直後の状態、(c)がサンプル4の累積時間経過後の状態をそれぞれ示す。

#### 【0050】

なお、ノンバイアス回路構成の場合には、サンプル1~4の全てについて不良発生は見られなかった。

これに対して、バイアス回路構成の場合には、表1に示すように、サンプル4の不良発生率を1として相対的に評価したところ、サンプル3が0.97、サンプル2が0.79、サンプル1が0.19となり、サンプル1が傑出して優れた結果を示した。このように、本実施形態のサンプル1の冗長用ヒューズを用いることにより、特にバイアス回路構成を採った場合に冗長用ヒューズの不良発生率を抑える効果が顕著であることが判った。

#### 【0051】

以上説明したように、本実施形態の半導体装置、特にその構成要素である冗長用ヒューズ111によれば、当該ヒューズ111のコロージョン耐性を高め、切断によるコロージョンの発生を抑制して、半導体装置における将来の更なる大規模集積化に十分対応することが可能となる。

10

20

30

40

50

**【0052】****- 第1の実施形態の変形例 -**

次いで、第1の実施形態の諸変形例について説明する。これら変形例では、本実施形態と同様に、Cu多層配線及び冗長用ヒューズを有する配線構造を備えた半導体装置を例示するが、冗長用ヒューズの形状がそれぞれ異なる点で相違する。なお、各変形例において冗長用ヒューズの材料には第1の実施形態と同様にタンゲステン(W)を用い、また、第1の実施形態で説明した構成部材等については同符号を記して説明を省略する。

**【0053】****(変形例1)**

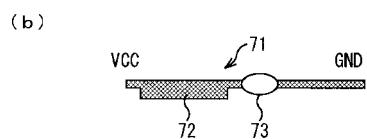

図13は、第1の実施形態の変形例1における冗長用ヒューズの構成を示す模式図であり、(a)が平面図、(b)が断面図である。10

この変形例1の冗長用ヒューズ71は、図13(a)に示すように、高電圧(Vcc)が印加される第2の配線36a側の近傍に形状的な腐食遅延構造、ここでは幅広構造72が設けられている。この場合、冗長用ヒューズ71の他端側、ここでは接地電位(GND)となる第2の配線36b側と幅広構造72との間に、切断部位73が設けられている。

**【0054】**

このように、冗長用ヒューズ71に幅広構造72を設けることにより、切断部位73から高電圧印加側の端まで間のヒューズ体積を実質的に大きくすることができ、Cu<sup>n+</sup>のグローバック開始時間を大幅に遅延させることができとなり、装置の保証寿命の確保が実現する。また、切断しない冗長用ヒューズ71の電気抵抗を低減する効果もある。20

**【0055】**

更に、図13(b)に示すように、冗長用ヒューズ71の幅広構造72の部位を上下方向に厚い厚膜構造としてもよい。これにより、切断部位73から高電圧印加側の端(第2の配線36a)まで間のヒューズ体積を更に大きくすることができ、装置の保証寿命の確保に資する。

**【0056】**

変形例1の半導体装置、特にその構成要素である冗長用ヒューズ71によれば、当該ヒューズ71のコロージョン耐性を高め、切断によるコロージョンの発生を抑制して、半導体装置における将来の更なる大規模集積化に十分対応することができる。

**【0057】****(変形例2)**

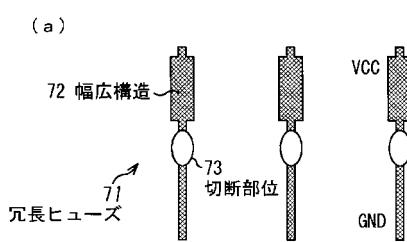

図14は、第1の実施形態の変形例2における冗長用ヒューズの構成を示す模式図であり、(a)が平面図、(b)が断面図である。

この変形例2の冗長用ヒューズ81は、図14(a)に示すように、高電圧(Vcc)が印加される第2の配線36a側の近傍に形状的な腐食遅延構造、ここでは分岐構造82が設けられている。この場合、冗長用ヒューズ81の他端側、ここでは接地電位(GND)となる第2の配線36b側と分岐構造82との間に、切断部位83が設けられている。

**【0058】**

このように、冗長用ヒューズ81に分岐構造82を設けることにより、切断部位83から高電圧印加側の端まで間のヒューズ長を実質的に大きくし、当該部位のヒューズ体積を増加することができ、Cu<sup>n+</sup>のグローバック開始時間を大幅に遅延させることができとなり、装置の保証寿命の確保が実現する。また、切断しない冗長用ヒューズ81の電気抵抗を低減する効果もある。40

**【0059】**

更に、図14(b)に示すように、冗長用ヒューズ81を分岐構造82の部位で多層、図示の例では2層に形成し、2層間にわたって更に上下方向に分岐するように、当該冗長用ヒューズ81を構成してもよい。これにより、切断部位83から高電圧印加側の端(第2の配線36a)まで間のヒューズ長及びヒューズ体積を更に大きくすることができ、装置の保証寿命の確保に資する。

**【0060】**1020304050

変形例 2 の半導体装置、特にその構成要素である冗長用ヒューズ 8 1 によれば、当該ヒューズ 8 1 のコロージョン耐性を高め、切斷によるコロージョンの発生を抑制して、半導体装置における将来の更なる大規模集積化に十分対応することが可能となる。

#### 【 0 0 6 1 】

##### ( 変形例 3 )

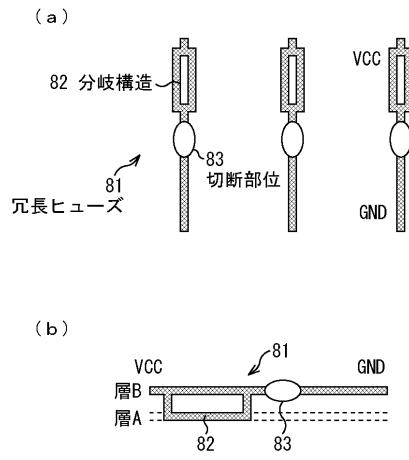

図 15 は、第 1 の実施形態の変形例 3 における冗長用ヒューズの構成を示す模式図であり、( a ) が当該変形例 3 における冗長用ヒューズの平面図、( b ) が当該変形例 3 の比較例として示す平面図である。

この変形例 3 の冗長用ヒューズ 121 は、図 15 ( a ) に示すように、形状的には従来と同様に直線形状であるが、隣接する各冗長用ヒューズ 121 の各々が、高電圧 ( Vcc ) の印加される第 2 の配線 36a の一端側から離れた他端側、ここでは接地電位 ( GND ) となる第 2 の配線 36b の近傍に切断部位 122 が設けられて構成されている。

10

#### 【 0 0 6 2 】

これに対して、図 15 ( b ) に示す比較例のように、小面積化のために隣接する各冗長用ヒューズ 131 の切断部位 132 を交互に設ける構成が案出されている。変形例 3 では、全ての冗長用ヒューズ 121 を高電圧 ( Vcc ) の印加される第 2 の配線 36a の一端側から離れた他端側で切断するように構成することにより、前記比較例と比べても Cu<sup>n+</sup> のグローバック開始時間を大幅に遅延させることが可能となり、装置の保証寿命の確保が実現する。

#### 【 0 0 6 3 】

変形例 3 の半導体装置、特にその構成要素である冗長用ヒューズ 121 によれば、当該ヒューズ 121 のコロージョン耐性を高め、切斷によるコロージョンの発生を抑制して、半導体装置における将来の更なる大規模集積化に十分対応することが可能となる。

20

#### 【 0 0 6 4 】

##### [ 第 2 の実施形態 ]

次いで、第 2 の実施形態について説明する。ここでは、本実施形態と同様に、Cu 多層配線及び冗長用ヒューズを有する配線構造を備えた半導体装置を例示するが、冗長用ヒューズの材質が異なる点で相違する。なお、第 1 の実施形態で説明した構成部材等については同符号を記して説明を省略する。

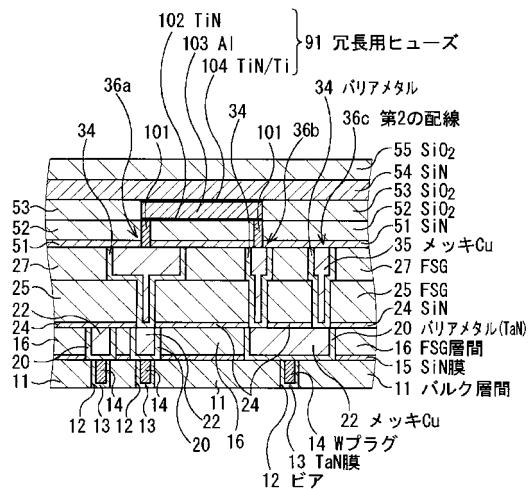

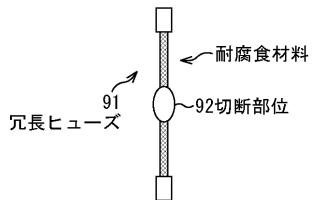

#### 【 0 0 6 5 】

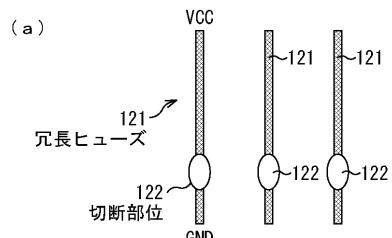

図 16 は、第 2 の実施形態における冗長用ヒューズの構成を示す概略平面図である。本実施形態における冗長用ヒューズ 91 は、耐腐食材料、例えば Al を含有する金属又は不純物が添加された多結晶シリコンから構成されている。この場合、切断部位に特に制限はないが、冗長用ヒューズ 91 の他端側、ここでは接地電位 ( GND ) となる第 2 の配線 36b 側の近傍に切断部位 92 を設けることがより好ましい。

30

#### 【 0 0 6 6 】

この場合、冗長用ヒューズ 91 は、図 17 に示すように、第 2 の配線 36a, 36b 上で、SiN 膜 51 及び SiO<sub>2</sub> 膜 52 に形成された W プラグ 101 を介し、W プラグ 101 上で膜厚 100 nm 程度の TiN 膜 102、膜厚 1000 nm 程度の Al 合金膜 103、及び TiN / Ti の 2 層膜 104 からなり、これらが SiO<sub>2</sub> 膜 53 に形成されて構成されている。そして、冗長用ヒューズ 91 を覆うように、SiN 膜 54 及び SiO<sub>2</sub> 膜 55 からなるカバー膜が形成されている。

40

#### 【 0 0 6 7 】

このように、冗長用ヒューズ 91 を耐腐食材料から構成することにより、切 Cu<sup>n+</sup> のグローバック開始時間を大幅に遅延させることができ、装置の保証寿命の確保が実現する。

#### 【 0 0 6 8 】

なお、本発明は上述した諸実施形態及び諸変形例に限定されるものではない。例えば、上述した腐食遅延構造は、高電圧印加側にあれば、更に低電圧印加側に形成しても、上述の効果を奏すことができる。

50

**【0069】**

また、第1の実施形態と第2の実施形態とを融合させた実施形態、即ち、冗長用ヒューズをA1や多結晶シリコン等の耐腐食性材料で形成し、更にこの冗長用ヒューズに蛇行状構造や幅広・厚膜構造、分岐構造等の腐食遅延構造を設けることも可能である。このような構成を採ることにより、更なるコロージョン発生を抑止・遅延し、保証寿命の確保が実現する。

**【0070】**

以下、本発明の諸態様を付記としてまとめて記載する。

**【0071】**

(付記1)配線及びヒューズを含む配線構造を備えてなる半導体装置であって、前記ヒューズは、形状的な腐食遅延構造を有することを特徴とする半導体装置。

10

**【0072】**

(付記2)前記腐食遅延構造は、前記ヒューズの所定部位に形成された蛇行状構造であることを特徴とする付記1に記載の半導体装置。

**【0073】**

(付記3)前記蛇行状構造は多層に形成されていることを特徴とする付記2に記載の半導体装置。

**【0074】**

(付記4)前記腐食遅延構造は、前記ヒューズの所定部位に形成された分岐構造であることを特徴とする付記1~3のいずれか1項に記載の半導体装置。

20

**【0075】**

(付記5)前記分岐構造は、多層に形成されていることを特徴とする付記4に記載の半導体装置。

**【0076】**

(付記6)前記腐食遅延構造は、前記ヒューズの所定部位に形成された幅広構造及び/又は厚膜構造であることを特徴とする付記1~5のいずれか1項に記載の半導体装置。

**【0077】**

(付記7)前記配線が少なくとも銅を含有する材料からなるものであることを特徴とする付記1~6のいずれか1項に記載の半導体装置。

**【0078】**

(付記8)前記腐食遅延構造は、前記ヒューズの切断部位と高電圧印加側との間に設けられていることを特徴とする付記1~7のいずれか1項に記載の半導体装置。

30

**【0079】**

(付記9)少なくとも銅を含有する配線と、ヒューズとを有する配線構造を備えてなる半導体装置であって、

前記ヒューズは、耐腐食材料から形成されていることを特徴とする半導体装置。

**【0080】**

(付記10)前記耐腐食材料がアルミニウムを含有する金属又は多結晶シリコンであることを特徴とする付記9に記載の半導体装置。

**【0081】**

(付記11)配線を所定形状に形成する工程と、

切断部位と高電圧印加側との間の所定部位が蛇行状構造となるヒューズを形成する工程とを含むことを特徴とする半導体装置の製造方法。

40

**【0082】**

(付記12)前記蛇行状構造を多層に形成することを特徴とする付記11に記載の半導体装置の製造方法。

**【0083】**

(付記13)配線を所定形状に形成する工程と、

切断部位と高電圧印加側との間の所定部位が幅広構造及び/又は厚膜構造となるヒューズを形成する工程と

50

を含むことを特徴とする半導体装置の製造方法。

【0084】

(付記14) 前記幅広構造及び／又は厚膜構造を分岐構造として形成することを特徴とする付記13に記載の半導体装置の製造方法。

【0085】

(付記15) 前記配線を少なくとも銅を含有する材料から形成することを特徴とする付記11～14のいずれか1項に記載の半導体装置の製造方法。

【0086】

(付記16) 少なくとも銅を含有する配線を所定形状に形成する工程と、

耐腐食材料からなるヒューズを形成する工程と

を含むことを特徴とする半導体装置の製造方法。 10

【0087】

(付記17) 前記耐腐食材料は、アルミニウムを含有する金属又は多結晶シリコンであることを特徴とする付記16に記載の半導体装置の製造方法。

【0088】

(付記18) 配線及びヒューズを含む配線構造が構成されており、

前記ヒューズは、その一端が高電圧印加部位とされ、当該高電圧印加部位の近傍に蛇行状構造が形成されており、

前記ヒューズを、その他端と前記蛇行状構造との間で切断することを特徴とするヒューズの切断方法。 20

【0089】

(付記19) 前記蛇行状構造が多層に形成されていることを特徴とする付記18に記載のヒューズの切断方法。

【0090】

(付記20) 配線及びヒューズを含む配線構造が構成されており、

前記ヒューズは、その一端が高電圧印加部位とされ、当該高電圧印加部位の近傍に幅広構造及び／又は厚膜構造が形成されており、

前記ヒューズを、その他端と前記蛇行状構造との間で切断することを特徴とするヒューズの切断方法。 30

【0091】

(付記21) 前記幅広構造及び／又は厚膜構造が分岐構造として形成されていることを特徴とする付記20に記載のヒューズの切断方法。

【0092】

(付記22) 前記配線が少なくとも銅を含有する材料からなるものであることを特徴とする付記18～21のいずれか1項に記載のヒューズの切断方法。

【0093】

(付記23) 少なくとも銅を含有する配線と、ヒューズとを有する配線構造が構成されており、

前記ヒューズは、耐腐食材料から形成され、その一端が高電圧印加部位とされており、

前記ヒューズを、その他端の近傍で切断することを特徴とするヒューズの切断方法。 40

【0094】

(付記24) 前記耐腐食材料は、アルミニウムを含有する金属又は多結晶シリコンであることを特徴とする付記23に記載のヒューズの切断方法。

【0095】

【発明の効果】

本発明によれば、配線（特にCuを含有する配線）と共に配線構造を構成するヒューズについて、当該ヒューズのコロージョン耐性を高め、切断によるコロージョンの発生を抑制することができるため、半導体装置におけるヒューズ個々の信頼性向上により、ヒューズ搭載本数の増加が可能となり、将来の更なる大規模集積化に十分対応することができる。

【図面の簡単な説明】

【図 1】冗長用ヒューズの切断（初期状態）によりコロージョンが発生するメカニズムを説明するための模式図である。

【図 2】冗長用ヒューズの切断（末期状態）によりコロージョンが発生するメカニズムを説明するための模式図である。

【図 3】第 1 の実施形態に係る半導体装置の製造方法を工程順に示す概略断面図である。

【図 4】図 3 に引き続き、第 1 の実施形態に係る半導体装置の製造方法を工程順に示す概略断面図である。

【図 5】図 4 に引き続き、第 1 の実施形態に係る半導体装置の製造方法を工程順に示す概略断面図である。

【図 6】図 5 に引き続き、第 1 の実施形態に係る半導体装置の製造方法を工程順に示す概略断面図である。 10

【図 7】図 6 に引き続き、第 1 の実施形態に係る半導体装置の製造方法を工程順に示す概略断面図である。

【図 8】図 7 に引き続き、第 1 の実施形態に係る半導体装置の製造方法を工程順に示す概略断面図である。

【図 9】図 8 に引き続き、第 1 の実施形態に係る半導体装置の製造方法を工程順に示す概略断面図である。

【図 10】第 1 の実施形態に係る半導体装置の冗長用ヒューズの構成を示す模式図である。

。

【図 11】耐湿性加速試験の各サンプルを示す概略平面図である。 20

【図 12】サンプル 1 とサンプル 4 について実際に耐湿性加速試験を行った様子を示す顕微鏡写真である。

【図 13】第 1 の実施形態の変形例 1 における冗長用ヒューズの構成を示す模式図である。

。

【図 14】第 1 の実施形態の変形例 2 における冗長用ヒューズの構成を示す模式図である。

。

【図 15】第 1 の実施形態の変形例 3 における冗長用ヒューズの構成を示す模式図である。

。

【図 16】第 2 の実施形態における冗長用ヒューズの構成を示す概略平面図である。

【図 17】第 2 の実施形態における冗長用ヒューズを備えた半導体装置の主要構成を示す概略断面図である。 30

#### 【符号の説明】

1 シリコン半導体基板

2 ゲート絶縁膜

3 ゲート電極

4 ソース／ドレイン

10 素子分離構造

11, 16, 25, 27 層間絶縁膜

14 W プラグ

15, 24, 26, 41, 43, 51, 54 SiN 膜

19 第 1 の配線溝

20, 34 バリアメタル膜

21 シード Cu 膜

22, 35 Cu 膜

23 第 1 の配線

30 ピアホール

31 保護材料

33 第 2 の配線溝

36a, 36b, 36c 第 2 の配線

42, 52, 53, 55 SiO<sub>2</sub> 膜

40

50

7 1 , 8 1 , 9 1 , 1 0 1 , 1 1 1 , 1 2 1 , 1 3 1 冗長用ヒューズ

6 1 蛇行状構造

6 2 , 7 3 , 8 3 , 9 2 , 1 1 2 , 1 2 2 , 1 3 2 切断部位

7 2 幅広構造

8 2 分岐構造

1 0 1 W ブラグ

1 0 2 TiN 膜

1 0 3 Al 合金膜

1 0 4 TiN / Ti の 2 層膜

1 1 2 ヒューズ溝

10

【図1】

【図2】

【 図 3 】

【 図 4 】

〔 図 5 〕

【 四 6 】

【 図 7 】

(b) 第2の配線2次エッティング

〔 図 9 〕

【 四 8 】

( b ) 第2の配線の研磨

【 义 1 0 】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

---

フロントページの続き

(72)発明者 大塚 敏志

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 中田 雅之

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 早川 朋一

(56)参考文献 特開平07-078872(JP,A)

特開平11-154706(JP,A)

特開平04-014246(JP,A)

特開2000-049234(JP,A)

特開2001-298093(JP,A)

特開平11-224900(JP,A)

特開2000-057933(JP,A)

特開平11-284074(JP,A)

国際公開第01/17026(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/82-21/822

H01L 27/04

H01L 21/3205-21/3215

H01L 21/768

H01L 23/52

H01L 23/522-23/532