(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4397210号

(P4397210)

(45) 発行日 平成22年1月13日(2010.1.13)

(24) 登録日 平成21年10月30日(2009.10.30)

(51) Int.Cl.

F 1

H01L 21/822 (2006.01)

H01L 27/04 (2006.01)

H01L 21/82 (2006.01)H01L 27/04

H01L 21/82

H01L 21/82A

E

P

D

請求項の数 7 (全 13 頁)

(21) 出願番号

特願2003-358599 (P2003-358599)

(22) 出願日

平成15年10月20日 (2003.10.20)

(65) 公開番号

特開2005-123486 (P2005-123486A)

(43) 公開日

平成17年5月12日 (2005.5.12)

審査請求日

平成18年8月10日 (2006.8.10)

(73) 特許権者 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(74) 代理人 100085501

弁理士 佐野 静夫

(74) 代理人 100134555

弁理士 林田 英樹

(72) 発明者 小宮 邦裕

京都市右京区西院溝崎町21番地 ローム

株式会社内

審査官 大嶋 洋一

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数 N ( N ≥ 2 ) 個の半導体パワー素子を備える半導体装置において、

前記各半導体パワー素子を複数 M ( M ≥ 2 ) 個の分割素子から構成し、 N × M 個の分割素子を異なる半導体パワー素子に属する分割素子が順次繰り返して並ぶように配置し、前記 N × M 個の分割素子からの出力配線を各出力配線同士が交差しないように N × M 個の出力パッドに接続している半導体集積回路本体と、

前記半導体集積回路本体の上に、前記 N × M 個の出力パッドに電気的に接続して各出力を出力する出力バンプが配置されており、前記 N 個の半導体パワー素子のうちの同じパワー素子に属する前記出力バンプを、前記半導体集積回路本体との間に絶縁層を介して設けられた出力結合配線で接続して、外部へ接続するための出力外部電極に接続する、再配線層と、を有することを特徴とする、半導体装置。

## 【請求項 2】

前記半導体集積回路本体には、前記 N × M 個の分割素子を少なくとも 1 つの電源パッドまたはグランドパッドに接続する電源配線またはグランド配線を有しており、

前記再配線層には、前記電源パッドまたはグランドパッドに電気的に接觸するように電源バンプまたはグランドバンプが配置されており、前記電源バンプまたはグランドバンプに電源外部電極またはグランド外部電極が接続されていることを特徴とする、請求項 1 記載の半導体装置。

## 【請求項 3】

10

20

前記電源配線またはグランド配線は前記出力配線のいずれとも同一平面上で交差しないように配置されていることを特徴とする、請求項 2 記載の半導体装置。

**【請求項 4】**

前記  $N \times M$  個の出力パッドが、各半導体パワー素子に属する分割素子群毎に、各分割素子に対して異なる方向に配置されていることを特徴とする、請求項 2 記載の半導体装置。

**【請求項 5】**

前記  $N \times M$  個の電源パッドまたはグランドパッドが、各半導体パワー素子に属する分割素子群毎に、各分割素子に対して前記出力パッドとはさらに異なる方向に配置されていることを特徴とする、請求項 4 記載の半導体装置。

**【請求項 6】**

前記出力結合配線は、前記出力バンプと前記絶縁層が形成された後に、前記出力バンプと同じ材料で形成されていることを特徴とする、請求項 1 乃至 5 記載の半導体装置。

**【請求項 7】**

前記出力外部電極は、ポール電極であることを特徴とする、請求項 1 乃至 6 記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、パワートランジスタなどの大容量パワー素子を複数個備えている半導体装置に関する。 20

**【背景技術】**

**【0002】**

半導体装置にパワートランジスタなどの大容量パワー素子を複数個設けるものがあり、パワー素子同士を隣接して配置することが行われている（特許文献 1 参照）。

**【0003】**

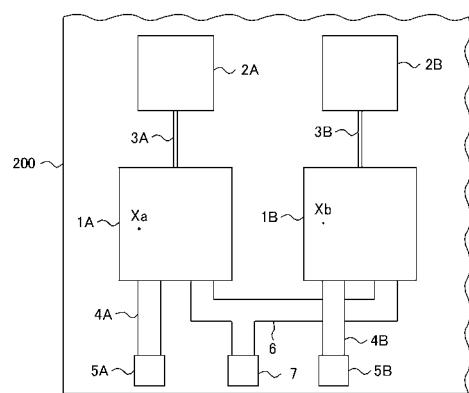

この場合に、これら複数個の大容量パワー素子間の特性の相対的なばらつきを低減することが必要となることがある。その相対的なばらつきを低減する方法として、図 8 に示す方法がある。

**【0004】**

図 8 は、2 個のパワートランジスタ 1 A, 1 B を設けた半導体集積回路 200 の構成を示す図である。パワートランジスタ 1 A, 1 B は、信号処理回路やプリドライブ回路等を含む制御回路 2 A, 2 B からそれぞれ信号線 3 A, 3 B を介して供給される制御信号に応じて、その動作状態が制御される。パワートランジスタ 1 A の出力端は、出力配線 4 A を介して出力パッド 5 A に接続され、パワートランジスタ 1 B の出力端は、出力配線 4 B を介して出力パッド 5 B に接続される。また、パワートランジスタ 1 A, 1 B の電源端は、電源配線 6 を介して共通に電源パッド 7 に接続される。なお、電源に代えて、グランドの場合もある。この場合、電源端はグランド端に、電源配線 6 はグランド配線に、電源パッド 7 はグランドパッドになる。以下、同様である。

**【特許文献 1】特開平 7 - 135299 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

この従来のものでは、パワートランジスタ 1 A、パワートランジスタ 1 B 等は、できるだけ近接するように、隣接して配置される。しかし、例えば、パワートランジスタ 1 A, 1 B を隣接して配置しても、パワートランジスタ 1 A, 1 B 自体の面積が大きいから、両パワートランジスタ 1 A, 1 B の対応する個所（図 8 中、X a と X b で表示している）間の距離が遠くなってしまう。パワートランジスタ 1 A, 1 B が作り込まれている半導体基板中には、その製造上で発生する不純物に関する濃度勾配がある。この濃度勾配と距離とに起因するパワートランジスタ 1 A, 1 B の特性のばらつきは、避けられない。また、同様に、動作中の半導体基板の温度勾配による特性のばらつきも避けられない。

10

20

30

40

50

## 【0006】

そこで、本発明は、パワートランジスタなどの大容量パワー素子を複数個設ける半導体装置において、これら複数個の大容量パワー素子間の特性の相対的なばらつきを低減することができる半導体装置を提供することを目的とする。

## 【0007】

また、パワートランジスタなどの大容量パワー素子を複数個設ける半導体装置において、これら複数個の大容量パワー素子間の特性の相対的なばらつきを低減するとともに、出力配線間の交差を無くしてレイアウト面積の増大を抑制することができる半導体装置を提供することを目的とする。

## 【課題を解決するための手段】

10

## 【0009】

請求項1の半導体装置は、複数N(N>2)個の異なる動作を行う半導体パワー素子を備える半導体装置において、前記各半導体パワー素子を複数M(M>2)個の分割素子から構成し、N×M個の分割素子を異なる半導体パワー素子に属する分割素子が順次繰り返して並ぶように配置し、前記N×M個の分割素子からの出力配線を各出力配線同士が交差しないようにN×M個の出力パッドに接続している半導体集積回路本体と、

前記半導体集積回路本体の上に、前記N×M個の出力パッドに電気的に接続して各出力を出力する出力バンプが配置されており、前記N個の半導体パワー素子のうちの同じパワー素子に属する前記出力バンプを、前記半導体集積回路本体との間に絶縁層を介して設けられた出力結合配線で接続して、外部へ接続するための出力外部電極に接続する、再配線層と、を有することを特徴とする。

20

## 【0010】

請求項2の半導体装置は、請求項1記載の半導体装置において、前記半導体集積回路本体には、前記N×M個の分割素子を少なくとも1つの電源パッドまたはグランドパッドに接続する電源配線またはグランド配線を有しており、

前記再配線層には、前記電源パッドまたはグランドパッドに電気的に接触するように電源バンプまたはグランドバンプが配置されており、前記電源バンプまたはグランドバンプに電源外部電極またはグランド外部電極が接続されていることを特徴とする。

## 【0011】

請求項3の半導体装置は、請求項2記載の半導体装置において、前記電源配線またはグランド配線は前記出力配線のいずれとも同一平面上で交差しないように配置されていることを特徴とする。

30

## 【0012】

請求項4の半導体装置は、請求項2記載の半導体装置において、前記N×M個の出力パッドが、各半導体パワー素子に属する分割素子群毎に、各分割素子に対して異なる方向に配置されていることを特徴とする。

## 【0013】

請求項5の半導体装置は、請求項4記載の半導体装置において、前記N×M個の電源パッドまたはグランドパッドが、各半導体パワー素子に属する分割素子群毎に、各分割素子に対して前記出力パッドとはさらに異なる方向に配置されていることを特徴とする。

40

## 【0014】

請求項6の半導体装置は、請求項1乃至5記載の半導体装置において、前記出力結合配線は、前記出力バンプと前記絶縁層が形成された後に、前記出力バンプと同じ材料で形成されていることを特徴とする。

## 【0015】

請求項7の半導体装置は、請求項1乃至6記載の半導体装置において、前記出力外部電極は、ボール電極であることを特徴とする。

## 【発明の効果】

## 【0016】

本発明によれば、パワートランジスタなどの大容量パワー素子を複数個設ける半導体装

50

置において、これら複数個の大容量パワー素子のそれぞれを複数の分割素子から構成し、それら分割素子を異なるパワー素子に属するものが順次隣接するように配置しているから、パワー素子間の特性の相対的なばらつきを低減することができる。

【0017】

また、パワートランジスタなどの大容量パワー素子を複数個設ける半導体装置において、これら複数個の大容量パワー素子のそれぞれを複数の分割素子から構成し、それら分割素子を異なるパワー素子に属するものが順次隣接するように配置するとともに、出力配線間の交差を無くしているから、パワー素子間の特性の相対的なばらつきを低減することができるとともに、レイアウト面積の増大を抑制することができる。

【0018】

また、複数の半導体パワー素子を設けている半導体集積回路本体に、分割素子をパワー素子毎に出力結合配線で接続している再配線層を形成するから、本発明の半導体装置を通常の半導体集積回路として、使用することができる。

【発明を実施するための最良の形態】

【0019】

以下、本発明の半導体装置の実施の形態について、図を参照して説明する。

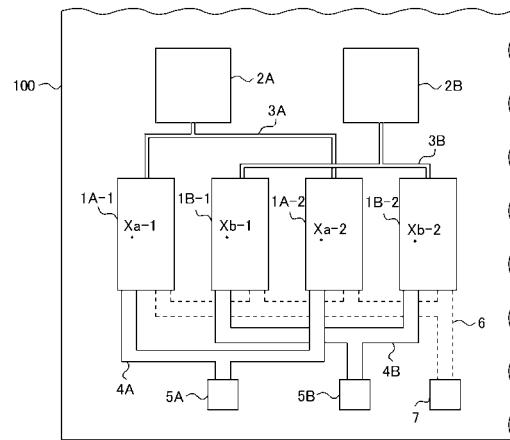

【0020】

図1は、本発明の第1実施例に係る半導体装置の構成を示す図であり、相対的なばらつきを低減するために、対象となる各パワー素子を複数の分割素子で構成し、それら分割素子を異なるパワー素子に属するものが順次隣接するように配置している。各パワー素子は、それぞれ出力を有し、異なる動作を行う。勿論、同時に動作するものでも良い。これらの点は、他の実施例でも同様である。

【0021】

図1において、分割素子による2個のパワートランジスタ1A, 1Bを設けた半導体集積回路（以下、ICチップ）100の構成を示している。パワートランジスタ1A, 1Bのコンポーネントとなる複数の分割素子1A-1, 1B-1, 1A-2, 1B-2を順次隣接するように配置している。

【0022】

そして、2つの分割素子1A-1, 1A-2を信号線3A、出力配線4Aで相互に接続してパワートランジスタ1Aとし、他の2つの分割素子1B-1, 1B-2を信号線3B、出力配線4Bで相互に接続して他のパワートランジスタ1Bとする。電源配線6は破線で示すように、出力配線4A、4Bとは異なる配線層により形成されており、全ての分割素子1A-1～1B-2に共通に接続している。出力配線4A, 4Bをそれぞれ出力パッド5A, 5Bに接続し、電源配線6を電源パッド7に接続する。なお、その他は、図8と同様である。なお、他の実施例でも、破線で示している電源配線は、出力配線とは異なる配線層で形成されていることを示している。

【0023】

このICチップ100によれば、パワートランジスタ1Aに属する分割素子1A-1あるいは分割素子1A-2と、パワートランジスタ1Bに属する分割素子1B-1あるいは分割素子1B-2とが接近して配置され、その対応する個所（図1中、Xa-1とXb-1及びXa-2とXb-2で表示している）間の距離も従来の半分程に近くなる。また、対応する個所の相対性は、「Xa-1とXb-1」や「Xa-2とXb-2」で比較されることになる。これにより、パワートランジスタ1A, 1B間の特性のばらつきは、低減される。

【0024】

ただ、第1実施例では、特性のばらつきは改善されるものの、次のような点で充分とは言えない。即ち、この第1実施例では、分割素子1A-1～1B-2からの出力配線4A, 4Bを出力パッド5A, 5Bに配線抵抗のばらつきを少なくして接続するために、同一の配線層を用いて同じ方向のパッドに接続しようとすれば、出力配線4A, 4B同士を交差させることになる。また、電源配線6も、同一の配線層を用いる場合には、出力配線4A, 4Bと交差する。これらパワー素子からの出力配線4A, 4Bや電源配線6は、パワー

10

20

30

40

50

素子のオン抵抗を少なくするためにその配線幅を太くする必要がある。さらに、配線同士の交差に伴い配線の引き回し距離が長くなるから、オン抵抗を小さく維持するためにその配線幅も太くする必要がある。また、分割素子 1 A - 1 ~ 1 B - 2 と出力パッド 5 A , 5 B や電源パッド 7 の間の領域に、出力配線 4 A , 4 B や電源配線 6 を図 1 のように配置すると、その領域の配線に要する配線面積が大きいので、その分、レイアウト効率が低下する。

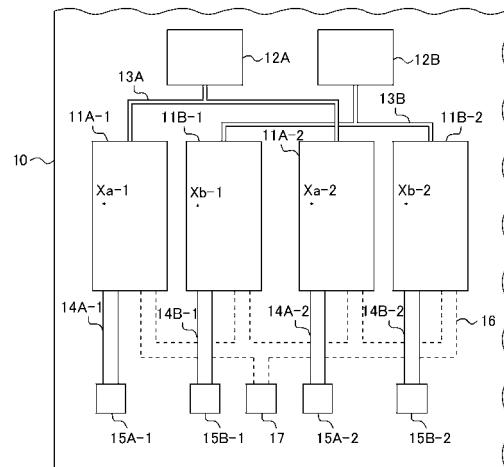

【 0 0 2 5 】

図 2 - 1 、図 2 - 2 は、本発明の第 2 実施例に係る半導体装置の構成を示す図である。この第 2 実施例では、パワー素子間の特性の相対的なばらつきを低減するとともに、レイアウト面積の増大を抑制する。図 3 は、本発明の第 2 実施例に係る半導体装置の構成を説明するための模式的な断面図である。 10

【 0 0 2 6 】

図 2 - 1 は本発明の半導体集積回路本体（以下、IC チップ本体）の構成を示す図であり、図 2 - 2 は、IC チップ本体上に形成される再配線層の構成を示す図である。以下の各実施例においては、パワー素子として、パワートランジスタを例にして説明する。パワートランジスタ以外にも、特性の相対的なばらつきを低減したい他のパワー素子にも同様に、適用することができる。

【 0 0 2 7 】

図 2 - 1 において、2 つのパワートランジスタ 11 A , 11 B ( 即ち、N = 2 ) を、それぞれ 2 つの分割素子 ( 即ち、M = 2 ) で構成する例を示している。パワートランジスタ 11 A , 11 B のコンポーネントとなる複数の分割素子 11 A - 1 , 11 B - 1 , 11 A - 2 , 11 B - 2 を順次隣接するように配置する。2 つの分割素子 11 A - 1 , 11 A - 2 は、制御回路 12 A から信号線 13 A を介して供給される制御信号に応じて、その動作状態が制御される。即ち、分割素子 11 A - 1 , 11 A - 2 は、パワートランジスタ 11 A として同時に駆動される。また、2 つの分割素子 11 B - 1 , 11 B - 2 は、制御回路 12 B から信号線 13 B を介して供給される制御信号に応じて、その動作状態が制御される。即ち、分割素子 11 B - 1 , 11 B - 2 は、パワートランジスタ 11 B として同時に駆動される。 20

【 0 0 2 8 】

各分割素子 11 A - 1 ~ 11 B - 2 からの出力配線 14 A - 1 , 14 B - 1 , 14 A - 2 , 14 B - 2 を、それぞれ出力パッド 15 A - 1 , 15 B - 1 , 15 A - 2 , 15 B - 2 に接続する。 30

【 0 0 2 9 】

また、各分割素子 11 A - 1 ~ 11 B - 2 からの電源配線 16 を、出力配線 14 A - 1 ~ 14 B - 2 とは異なる配線層で共通に接続し、電源パッド 17 に接続する。なお、「電源」は、「グランド」としてもよい。この場合、電源パッド 17 に供給される電圧がグランド電圧である場合には、電源配線 16 はグランド配線 16 と読み替え、電源パッド 17 はグランドパッド 17 と読み替えることになる。この点は、他の実施例でも同様である。

【 0 0 3 0 】

この IC チップ本体 10 では、パワートランジスタ 11 A に属する分割素子 11 A - 1 及び分割素子 11 A - 2 と、パワートランジスタ 11 B に属する分割素子 11 B - 1 及び分割素子 11 B - 2 とが接近して配置される。その対応する個所（図 2 - 1 中、X a - 1 と X b - 1 及び X a - 2 と X b - 2 で表示している）間の距離も近くなる。即ち、対応する個所の相対性は、「X a - 1 と X b - 1 」や「X a - 2 と X b - 2 」で比較されることになる。これにより、パワートランジスタ 11 A , 11 B 間の特性のばらつきは、かなり低減される。 40

【 0 0 3 1 】

また、この IC チップ本体 10 では、分割素子 11 A - 1 ~ 11 B - 2 からの出力配線 14 A - 1 ~ 14 B - 2 を出力パッド 15 A - 1 ~ 15 B - 2 にストレートに接続する。即ち、出力配線 14 A - 1 ~ 14 B - 2 同士が交差しない。したがって、配線抵抗を含めたパワー 50

トランジスタ 11A, 11B のオン抵抗を小さくすることができる。

【0032】

なお、出力配線 14A-1 ~ 14B-2 が電源配線 6 と交差するが、ICチップ本体 10 では、出力配線のための導電層と電源配線のための導電層とは異なる配線層で形成されているから、特に問題とはならない。

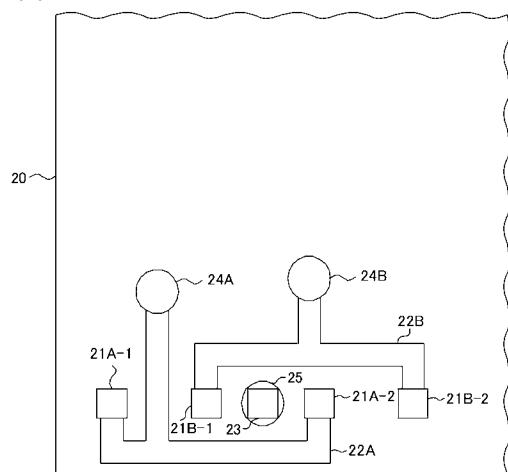

【0033】

図 2-2 の ICチップ本体上に形成される再配線層 20 において、出力バンプ（または、出力ポスト、以下同じ）21A-1, 21B-1, 21A-2, 21B-2 及び電源バンプ（または、電源ポスト、以下同じ）23 が、ICチップ本体 10 上の出力パッド 15A-1, 15B-1, 15A-2, 15B-2 及び電源パッド 17 に電気的に接触するように設けられる。そして、ICチップ本体 10 上の他の部分にポリイミド樹脂等の絶縁層が設けられる。この絶縁層は、ほぼ出力バンプ 21A-1 ~ 21B-2 や電源バンプ 23 の高さと同程度の厚みでよい。

10

【0034】

パワートランジスタ 11A に対応する出力バンプ 21A-1 と出力バンプ 21A-2 を出力結合配線 22A で接続し、その出力結合配線 22A を外部へ接続したい位置まで配設する。そして、出力外部電極 24A を出力結合配線 22A に接続する。また、パワートランジスタ 11B に対応するバンプ 21B-1 とバンプ 21B-2 を出力結合配線 22B で接続し、その出力結合配線 22B を外部へ接続したい位置まで配設する。そして、出力外部電極 24B を出力結合配線 22B に接続する。また、電源バンプ 23 に電源バンプ電極 25 を接続する。この再配線層 20 において、出力結合配線 22A, 22B 同士の交差はないし、他の配線もない。したがって、出力結合配線を 1 つの層で充分に幅広く形成し、配線抵抗を小さくすることができる。

20

【0035】

なお、出力外部電極 24A, 24B を、バンプ 21A-1 やバンプ 21A-2 あるいはバンプ 21B-1 やバンプ 21B-2 に直接設けるようにしてもよい。

【0036】

出力結合配線 22A, 22B は、出力バンプ 21A ~ 21B と絶縁層が形成された後に形成される。出力結合配線 22A, 22B は、それらバンプと同じ材料で形成されることが望ましいし、また、同一の太さ、同一の長さに形成されることが望ましい。出力外部電極 24A, 24B や電源バンプ電極 25 は、ボール電極、バンプ電極などで構成される。

30

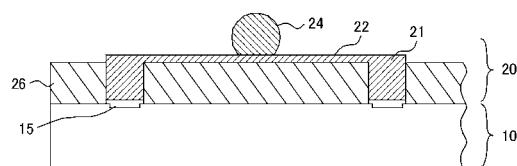

【0037】

図 3 は、図 2-1, 図 2-2 の半導体装置の構成を説明するための模式的な断面図であり、A, B の記号は省略している。

【0038】

図 3 において、ICチップ本体 10 の内部に図 2-1 に示した各構成要素が作り込まれている。その ICチップ本体 10 表面に出力パッド 15 が形成され、その出力パッド 15 にバンプ（またはポスト）21 を電気的に接続するように形成する。そして、ICチップ本体 10 上の他の部分には絶縁層 26 を形成する。次に、所定のバンプ 21 同士が出力結合配線 22 で接続され、出力外部電極 24 が出力結合配線 22 に接続されている。

40

【0039】

この第 2 実施例によれば、複数個のパワー素子 11A, 11B のそれぞれを複数の分割素子 11A-1 ~ 11B-2 から構成し、それら分割素子を異なるパワー素子に属するものが順次隣接するように配置しているから、パワー素子間の特性の相対的なばらつきを低減することができる。また、出力配線 14A-1 ~ 14B-2 間の同一平面上での交差を無くしているから、レイアウト面積の増大を抑制することができる。また、再配線層 20 において、出力結合配線 22A, 22B 同士の交差はないように、出力結合配線を 1 つの層で実現している。さらに、複数の半導体パワー素子 11A, 11B を設けている ICチップ本体 10 に、分割素子をパワー素子毎に出力結合配線 22A, 22B で接続している再配線層 20 を形成するから、本発明の半導体装置を通常の半導体集積回路として、使用する

50

ことができる。

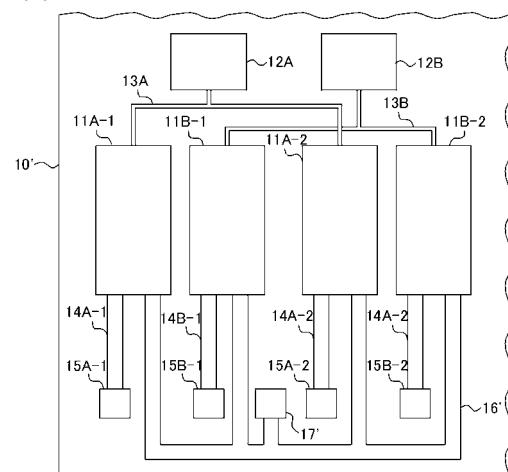

【0040】

図4-1は、本発明の第3実施例に係る半導体装置のICチップ本体10の構成を示す図である。

【0041】

図4-1において、ICチップ本体10には、分割素子11A-1～11B-2を電源パッド17に接続する電源配線16が、同一平面上で出力配線14A-1～14B-2のいずれとも交差しないように配置されている。したがって、出力配線14A-1～14B-2と電源配線16とを、同一配線層で形成できるようになっている。そのほかの点は、図2-1のICチップ本体10と同様である。

10

【0042】

このICチップ本体10上には、図2-2で示した再配線層20が形成される。

【0043】

この第3実施例によれば、第2実施例に比べて電源配線16の配線長は長くなるが、出力配線14A-1～14B-2及び電源配線16を同一の配線層で形成できる他、第2実施例と同様の効果を得ることができる。

【0044】

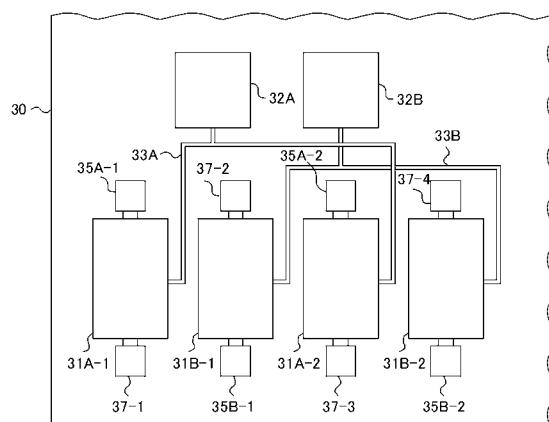

図5-1、図5-2は、本発明の第4実施例に係る半導体装置の構成を示す図である。図5-1はICチップ本体30の構成を示す図であり、図5-2は、ICチップ本体上に形成される再配線層40の構成を示す図である。

20

【0045】

図5-1において、ICチップ本体30には、2つのパワートランジスタ31A、31B（即ち、 $N = 2$ ）を、それぞれ2つの分割素子（即ち $M = 2$ ）で構成する例を示している。パワートランジスタ31A、31Bのコンポーネントとなる複数の分割素子31A-1、31B-1、31A-2、31B-2を順次隣接するように配置する。2つの分割素子31A-1、31A-2は、制御回路32Aから信号線33Aを介して供給される制御信号に応じて、その動作状態が制御される。

【0046】

パワートランジスタ31Aを構成する分割素子31A-1、31A-2からの出力パッド35A-1、35A-2は図中に示すようにその分割素子の上側に接近して設けられており、電源パッド37-1、37-3は図中に示すようにその分割素子の下側に接近して設けられている。また、パワートランジスタ31Bを構成する分割素子31B-1、31B-2からの出力パッド35B-1、35B-2は図中に示すようにその分割素子の下側に接近して設けられており、電源パッド37-2、37-4は図中に示すようにその分割素子の上側に接近して設けられている。2つの分割素子31A-1、31A-2及び2つの分割素子31B-1、31B-2は、制御回路32A、32Bから信号線33A、33Bを介して供給される制御信号に応じて、その動作状態が制御される。即ち、分割素子31A-1、31A-2及び分割素子31B-1、31B-2は、パワートランジスタ31A、31Bとして同時に駆動される。

30

【0047】

このように、 $4(N \times M)$ 個の分割素子31A-1～31B-2の各々に対して、出力配線（図5-1では、記号を省略している）により接続される出力パッド31A-1～31B-2及び電源配線（図5-1では、記号を省略している）により接続される電源パッド37-1～37-4が個々に設けられている。

40

【0048】

そして、 $4(N \times M)$ 個の出力パッド35A-1～35B-2が、半導体パワー素子に属する分割素子群毎に、即ち半導体パワー素子31Aに属する分割素子群31A-1、31A-2に対して上方向に配置され、半導体パワー素子31Bに属する分割素子群31B-1、31B-2に対して異なる方向（下方向）に配置されている。また、 $4(N \times M)$ 個の電源パッド37-1～37-4が、半導体パワー素子に属する分割素子群毎に、即ち半導体

50

パワー素子 31A に属する分割素子群 31A-1、31A-2 に対して下方向に配置され、半導体パワー素子 31B に属する分割素子群 31B-1、31B-2 に対して異なる方向(上方向)に配置されている。

【0049】

このように、出力パッド 35A-1～35B-2 及び電源パッド 37-1～37-4 を配置することにより、出力配線及び電源配線が互いに交差しないし、出力配線及び電源配線の長さがきわめて短くできる。

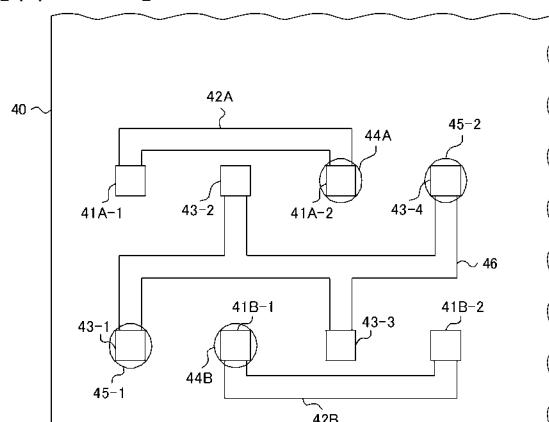

【0050】

図 5-2 の、IC チップ本体上に形成される再配線層 40 において、出力バンプ 41A-1、41B-1、41A-2、41B-2、及び電源バンプ 43-1～43-4 が、IC チップ本体 30 上の出力パッド 35A-1、35B-1、35A-2、35B-2 及び電源パッド 37-1～37-4 に電気的に接触するように設けられる。そして、IC チップ本体 30 上の他の部分に絶縁層が設けられる。

10

【0051】

パワートランジスタ 31A に対応する出力バンプ 41A-1 と出力バンプ 41A-2 とを出力結合配線 42A で接続し、その出力結合配線 42A を外部へ接続したい位置まで配設する。そして、出力外部電極 44A を出力結合配線 42A にこの例では出力バンプ 41A-2 のポイントで接続する。また、パワートランジスタ 31B に対応するバンプ 41B-1 とバンプ 41B-2 とを出力結合配線 42B で接続し、その出力結合配線 42B を外部へ接続したい位置まで配設する。そして、出力外部電極 44B を出力結合配線 42B にこの例では出力バンプ 41B-1 のポイントで接続する。また、電源バンプ 43-1～43-4 を電源結合配線 46 で接続し、その電源結合配線 46 を外部へ接続したい位置まで配設する。

20

【0052】

そして、電源電極 45-1、45-2 を電源結合配線 46 にこの例では電源バンプ 43-1、43-4 の 2 つのポイントで接続する。この再配線層 40 において、出力結合配線 42A、42B 同士の交差はない。また、電源結合配線 46 との交差もない。したがって、出力結合配線 42A、42B、電源結合配線 46 を 1 つの層で実現できる。この半導体装置のそのほかの点は、第 2～第 3 の実施例におけると同様である。

30

【0053】

この第 4 実施例によれば、出力配線及び電源配線が全く交差することがないし、出力配線及び電源配線の長さがきわめて短くできる他、第 2 実施例と同様の効果を得ることができる。

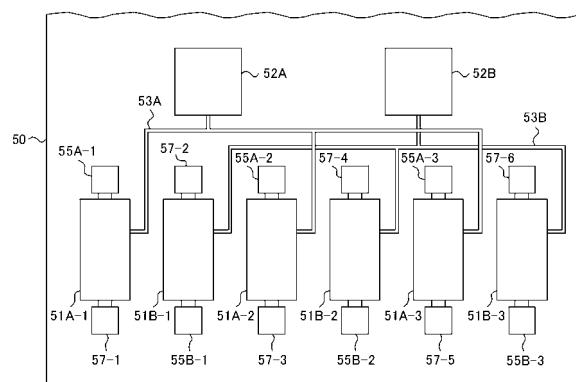

【0054】

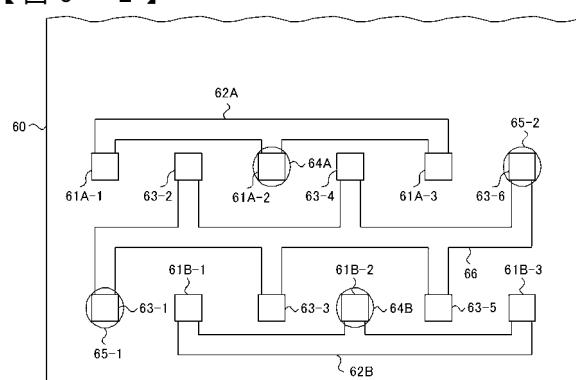

図 6-1、図 6-2 は、本発明の第 5 実施例に係る半導体装置の構成を示す図である。図 6-1 は IC チップ本体 50 の構成を示す図であり、図 6-2 は、IC チップ本体上に形成される再配線層 60 の構成を示す図である。

【0055】

図 6-1 において、IC チップ本体 50 には、2 つのパワートランジスタ 51A、51B(即ち、N=2)を、それぞれ 3 つの分割素子(即ち、M=3)で構成する例を示している。図 6-2 の IC チップ本体上に形成される再配線層 60 において、IC チップ本体 50 でのパワートランジスタの 3 分割構成に対応した構成となっている。この図 6-1 の IC チップ本体 50 及び図 6-2 の再配線層 60 において、各パワートランジスタが 3 分割構成となっている他は、図 5-1、図 5-2 で説明した第 4 実施例と同様である。ただ、各構成要素の記号が、図 6-1 では 50 番台に、図 6-2 では 60 番台になっている。

40

【0056】

即ち、51A-1～51B-3 は、パワートランジスタ 51A、51B の各分割素子、52A、52B は制御回路、53A、53B は信号線、55A-1～55B-3 は出力パッド、57-1～57-6 は電源パッドである。また、61A-1～61B-3 は出力バンプ、62A、62B は出力結合配線、63-1～63-6 は電源バンプ、64A、64B は出力外

50

部電極、65-1, 65-2は電源外部電極、66は電源結合配線、である。

【0057】

この第5実施例においては、1つのパワー素子当たりの分割素子数Mを増やすことができ、その場合でも第4実施例と同様の効果を得ることができる。

【0058】

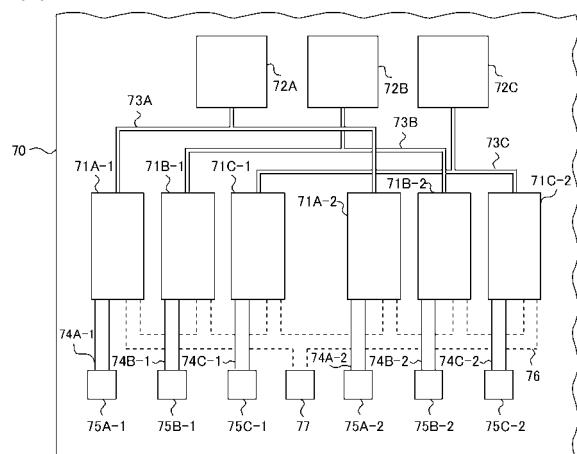

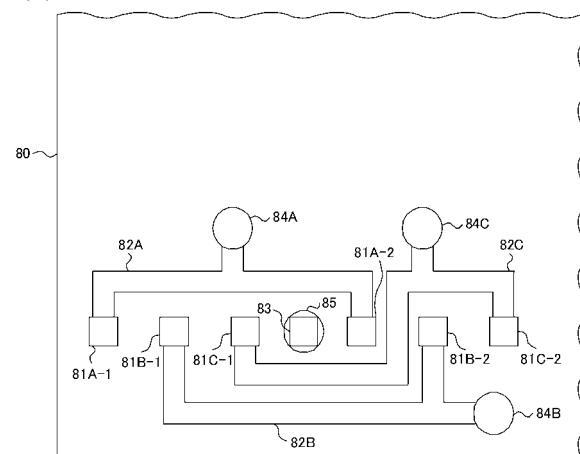

図7-1、図7-2は、本発明の第6実施例に係る半導体装置の構成を示す図である。図7-1はICチップ本体70の構成を示す図であり、図7-2は、ICチップ本体上に形成される再配線層80の構成を示す図である。

【0059】

図7-1において、ICチップ本体70には、3つのパワートランジスタ71A, 71B, 71C(即ち、N=3)を、それぞれ2つの分割素子(即ちM=2)で構成する例を示している。図7-2のICチップ本体上に形成される再配線層80において、ICチップ本体70での3つのパワートランジスタの2分割構成に対応した構成となっている。この図7-1のICチップ本体70及び図7-2の再配線層80において、3つのパワートランジスタが2分割構成となっている他は、図2-1、図2-2で説明した第2実施例と同様である。ただ、各構成要素の記号が、図7-1では70番台に、図7-2では80番台になっている。

【0060】

即ち、71A-1～71C-2は、パワートランジスタ71A, 71B, 71Cの各分割素子、72A, 72B, 72Cは制御回路、73A, 73B, 73Cは信号線、74A-1～74C-2は出力配線、75A-1～75C-2は出力パッド、76は電源配線、77は電源パッドである。また、81A-1～81C-2は出力バンプ、82A, 82B, 82Cは出力結合配線、83は電源バンプ、84A, 84B, 84Cは出力外部電極、85は電源外部電極、である。

【0061】

この第6実施例においては、パワー素子数Nを増やした場合でも、出力配線を同一平面上で交差することなく各ブロックを接続することができる、第2実施例や他の実施例と同様の効果を得ることができる。

【0062】

以上の説明では、M=2またはN=2までの場合についてのみ説明したが、M=3、N=3でも同様であり、より容易に配線抵抗を小さくし、配線スペースを削減することができる。

【図面の簡単な説明】

【0063】

【図1】本発明の第1実施例のICチップの構成を示す図

【図2-1】本発明の第2実施例のICチップ本体の構成を示す図

【図2-2】第2実施例のICチップ本体上に形成される再配線層の構成図

【図3】第2実施例の半導体装置の構成を説明するための模式的な断面図

【図4-1】本発明の第3実施例のICチップ本体の構成を示す図

【図5-1】本発明の第4実施例のICチップ本体の構成を示す図

40

【図5-2】第4実施例のICチップ本体上に形成される再配線層の構成図

【図6-1】本発明の第5実施例のICチップ本体の構成を示す図

【図6-2】第5実施例のICチップ本体上に形成される再配線層の構成図

【図7-1】本発明の第6実施例のICチップ本体の構成を示す図

【図7-2】第6実施例のICチップ本体上に形成される再配線層の構成図

【図8】従来の半導体集積回路の構成図

【符号の説明】

【0064】

100 ICチップ

1A-1～1B-2 分割素子

50

2 A、2 B 制御回路

3 A、3 B 信号線

4 A、4 B 出力配線

5 A、5 B 出力パッド

6 電源配線

7 電源パッド

10, 10, 30, 50, 70 I Cチップ本体

20, 40, 60, 80 再配線層

11A-1 ~ 11B-2 分割素子

12A, 12B 制御回路

13A, 13B 信号線

14A-1 ~ 14B-2 出力配線

15A-1 ~ 15B-2 出力パッド

16 電源配線

17 電源パッド

21A-1 ~ 21B-2 出力バンプ

22A, 22B 出力結合配線

23 電源バンプ

24A, 24B 出力外部電極

25 電源バンプ電極

26 絶縁層

10

20

【図1】

【図2-1】

【図 2 - 2】

【図 4 - 1】

【図 3】

【図 5 - 1】

【図 6 - 1】

【図 5 - 2】

【図 6 - 2】

【図 7 - 1】

【図 7 - 2】

【図 8】

---

フロントページの続き

(56)参考文献 特開平11-168178(JP,A)

特開平02-126672(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 21/82

H01L 27/04