(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-114747

(P2006-114747A)

(43) 公開日 平成18年4月27日(2006.4.27)

| (51) Int.C1.       | F 1       | テーマコード (参考) |            |

|--------------------|-----------|-------------|------------|

| <b>HO1L 21/316</b> | (2006.01) | HO1L 21/316 | P 4M104    |

| <b>HO1L 21/28</b>  | (2006.01) | HO1L 21/28  | A 5F058    |

| <b>HO1L 29/78</b>  | (2006.01) | HO1L 21/28  | 301R 5F140 |

| <b>HO1L 29/417</b> | (2006.01) | HO1L 21/28  | 301S       |

| <b>HO1L 29/423</b> | (2006.01) | HO1L 29/78  | 301F       |

審査請求 未請求 請求項の数 8 O L (全 13 頁) 最終頁に続く

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2004-301462 (P2004-301462) | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号   |

| (22) 出願日  | 平成16年10月15日 (2004.10.15)     | (74) 代理人 | 100088487<br>弁理士 松山 允之                          |

|           |                              | (72) 発明者 | 佐々木 隆興<br>茨城県つくば市小野川16番地1 株式会<br>社半導体先端テクノロジーズ内 |

|           |                              |          |                                                 |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhig h-k膜21とゲート電極24を形成する半導体装置の製造方法において、hig h-k膜形成後にフッ素雰囲気でアーチル処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

【選択図】 図7

**【特許請求の範囲】****【請求項 1】**

シリコン基板上に高誘電率膜とゲート電極を形成する半導体装置の製造方法において、高誘電率膜形成後にフッ素雰囲気でアニール処理を施し、その後のプロセス温度を600以下で行うことを特徴とする半導体装置の製造方法。

**【請求項 2】**

請求項1に記載の半導体装置の製造方法において、アニール処理は、フッ素を含有するガスを成分とすることを特徴とする半導体装置の製造方法。

**【請求項 3】**

請求項1に記載の半導体装置の製造方法において、高誘電率膜と半導体基板の界面付近のフッ素の濃度が $10^{20} / \text{cm}^3$ 以上であることを特徴とする半導体装置の製造方法。 10

**【請求項 4】**

シリコン基板上に高誘電率膜とゲート電極を形成する半導体装置の製造方法において、高誘電率膜に積層する該高誘電率膜とは異種の薄膜を形成後にフッ素雰囲気でアニール処理を施すことを特徴とする半導体装置の製造方法。

**【請求項 5】**

シリコン基板上に高誘電率膜とゲート電極を形成する半導体装置の製造方法において、高誘電率膜に積層する該高誘電率膜とは異種のフッ素ドープの薄膜を形成することを特徴とする半導体装置の製造方法。

**【請求項 6】**

請求項1、4又は5に記載の半導体装置の製造方法において、高誘電率膜形成後、酸素プラズマ処理を行い、その後にフッ素雰囲気でのアニール処理あるいは前記薄膜形成することを特徴とする半導体装置の製造方法。 20

**【請求項 7】**

請求項4又は5に記載の半導体装置の製造方法において、前記薄膜はシリコン酸化膜、シリコン窒化膜あるいはシリコン酸窒化膜であることを特徴とする半導体装置の製造方法。 30

**【請求項 8】**

請求項4又は5に記載の半導体装置の製造方法において、前記フッ素雰囲気でのアニール処理後あるいは前記フッ素ドープの薄膜形成後のプロセス温度が600以下であることを特徴とする半導体装置の製造方法。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置の製造方法に関するもので、詳しくは、絶縁ゲート電界効果トランジスタ(MISFET)用のゲート絶縁膜に高誘電率膜(High-k膜)が適用される半導体装置の製造方法に関する。

**【背景技術】****【0002】**

シリコン基板上に絶縁膜とゲート電極を形成した半導体装置において、絶縁膜にフッ素を添加することにより、シリコン基板との界面に存在するダンギングボンドを終端させることは、特許文献1に示されているが、電極形成前に低温でフッ素アニール処理を行う点が示されていない。

**【特許文献1】特開2001-257344号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

メタルゲートは、通常、high-k膜に有利な材料であるが、high-k膜の成膜温度は、低い場合が多く、シリコン基板界面状態を良好にする熱工程を経ていないのが普通である。また、先にシリコン基板中にソースドレインを形成する工程(ダマシングート) 50

などゲート後付けプロセス)では、サリサイドの形成(例えばNiSiでは500未満)を行った後に、本来の絶縁膜を形成する場合が多く、これも高温化を適用できない一つの要因となっている。

#### 【0004】

このように、低温化に伴い、シリコン基板の界面の状態が熱工程で回復せず、界面準位が多いことが避けて通れない。これを低減する方法として、水素アニール工程を行うことが挙げられるが、水素や重水素ではその回復の度合いが温度で制限されてしまい、例えば配線形成後に行うシンターリング工程では約500未満で、大きな効果が期待できない。

#### 【0005】

また、水素は界面付近に存在する場合、NBTI(Negative Bias Temperature Instability)をより悪化させると言わされており、信頼性に対する影響が大きい。また、イオン注入でフッ素を導入する方法については、例えばゲート後付け工程(ダマシングートプロセスなど)を経る場合、十分に界面にフッ素を導入することが困難である。

#### 【0006】

以上のように、シリコン基板の界面の改質に必要な高温化の導入不可能、シンターの限界があることから、デバイスへ与える影響は計り知れないものがある。界面準位の増加に伴い、例えば移動度の劣化、BTストレス耐性の低減など、深刻な問題が存在する。

#### 【0007】

本発明は、上述の事情に鑑みてなされたもので、MISFETにおいてhigh-k膜を含むゲート絶縁膜(高誘電体ゲート絶縁膜)にフッ素を低温下で導入し、高性能なMISFETを可能にする半導体装置の製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

上記課題を解決するために、半導体装置の製造方法にかかる第1の発明は、シリコン基板上にhigh-k膜とゲート電極を形成する半導体装置の製造方法において、high-k膜形成後にフッ素雰囲気でアニール処理を施し、その後のプロセス温度を600以下、500程度で行うという構成を有している。

#### 【0009】

そして、半導体装置の製造方法にかかる第2の発明は、シリコン基板上にhigh-k膜とゲート電極を形成する半導体装置の製造方法において、high-k膜形成後にhigh-k膜に積層した極薄絶縁膜を形成し、上記high-k膜と極薄絶縁膜の界面領域にフッ素を含有させるという構成を有している。

#### 【発明の効果】

#### 【0010】

本発明は、シリコン基板と高誘電体ゲート絶縁膜の界面および高誘電体ゲート絶縁膜の膜質を改質して、MISFETの特性の向上を図ることができる。

#### 【発明を実施するための最良の形態】

#### 【0011】

以下に、図面を参照して本発明の実施の形態の幾つかを詳細に説明する。

#### (実施の形態1)

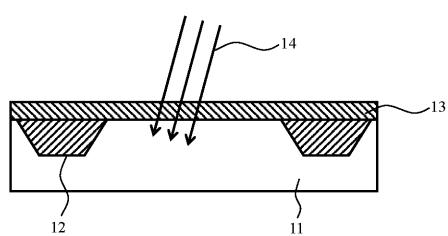

はじめに、本発明の実施の形態1を図1～図8を参照して説明する。まず、図1に示す通り、シリコン基板11にSTI(shallow trench isolation)12を形成し、更に、犠牲酸化膜13を形成する。犠牲酸化膜13を介してウエル(Well)インプラ注入14を行う。次に、犠牲酸化膜13をエッティング除去し、その後、酸化膜形成前の洗浄処理を行う。

#### 【0012】

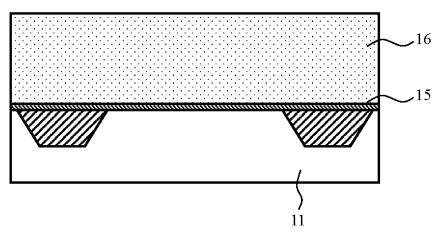

次に、図2に示す通り、シリコン基板11表面に任意の厚さのダミーゲート絶縁膜15を形成後、アモルファス或いはポリ状のシリコン膜、或いはシリコングルマニウム膜のダミーゲート電極16を堆積させる。

10

20

30

40

50

## 【0013】

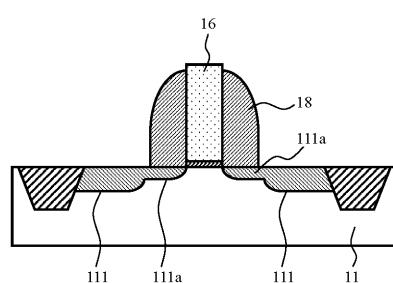

次に、図3に示す通り、ダミーゲート電極16を加工後、エクステンション層111a及びハロー用の不純物をイオン注入し、更に、サイドウォール18を形成し、ソースドレイン用の不純物をイオン注入して、活性化アニールを施す。活性化アニールは、例えば約1050で数秒間のスパイクアニール(spikeアニール)とする。このようにして、浅接合のソースドレイン拡散層111を形成する。ここで、エクステンション層111aとソースドレイン拡散層111は同導電型の拡散層であり、ハローは逆導電型の拡散層となる。

## 【0014】

上記ソースドレイン拡散層111等を浅接合に形成する活性化アニールは、その他に、10

フラッシュランプアニール、レーザーアニール等のような低サーマルバジェットによる熱処理がある。ここで、フラッシュランプアニールにおいては、可視域から近赤外線域までの広い範囲に発光波長を有している白色光のキセノン(Xe)フラッシュランプを用いるとよい。このXeフラッシュランプは、数100μ秒～数10m秒という極めて短時間の発光が可能な光源であり、その処理温度450～600、処理時間10m秒程度で上記活性化アニールをすることができる。

## 【0015】

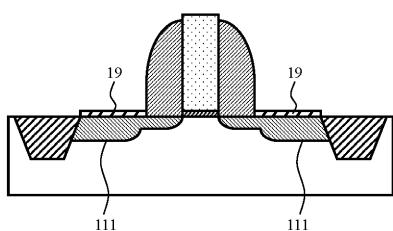

その後、図4に示す通り、例えばCo、Niなどの金属膜をスパッタ法で成膜し、公知のサリサイド技術によりソースドレイン拡散層111表面にシリサイド層19を低温で形成する。

## 【0016】

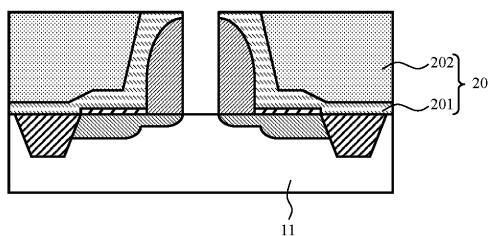

次に、図5に示す通り、窒化膜201と酸化膜202の層間膜20を形成する。下地の窒化膜201をストップにCMP(Chemical Mechanical Polishing)を施し、アモルファス或いはポリ状のシリコン膜、或いはシリコンゲルマニウム膜のダミーゲート電極16を露出させ、ダミーゲート電極16をエッチングで除去し、シリコン基板11を露出させる。

## 【0017】

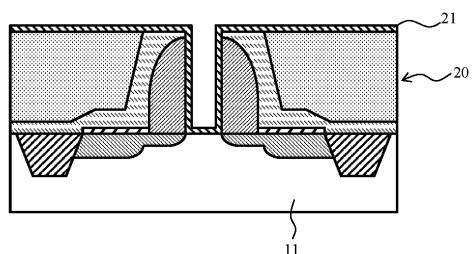

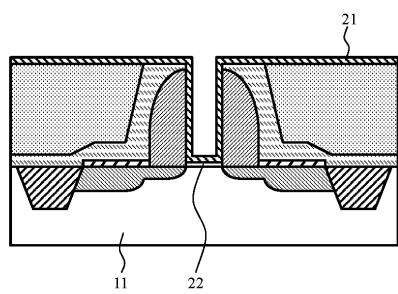

その後、図6に示す通り、例えばHfO<sub>2</sub>などのHigh-k材料をALD(Atomic Layer Deposition)或いはMOCVD法(Metal Organic Chemical Vapor Deposition)で堆積し、上記露出したシリコン基板11表面および層間膜20表面を被覆するhigh-k膜21を形成する。このようにして、高誘電体ゲート絶縁膜を構成する絶縁膜として、シリコン基板11上直にhigh-k膜21が形成される。

## 【0018】

ここで、high-k膜21としては、上述したところのHfO<sub>2</sub>の他にZrO<sub>2</sub>といった金属酸化物や、HfSiO<sub>x</sub>、ZrSiO<sub>x</sub>といった金属シリケート、HfAlO<sub>x</sub>、ZrAlO<sub>x</sub>といった金属アルミネート、La<sub>2</sub>O<sub>3</sub>、Y<sub>2</sub>O<sub>3</sub>等のランタノイド系元素の酸化物を主体とした高誘電率膜材料で構成すると好適である。そして、上記高誘電率膜材料から成るhigh-k膜のうち2種類以上の絶縁膜を選択し積層した積層構造の絶縁膜を用いてもよい。

## 【0019】

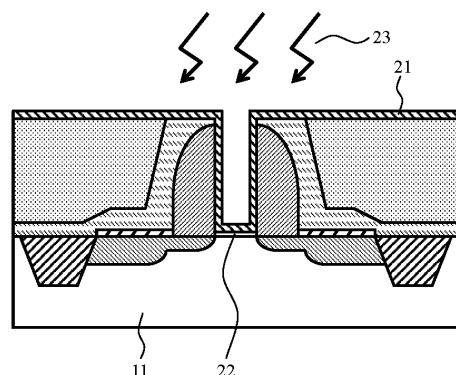

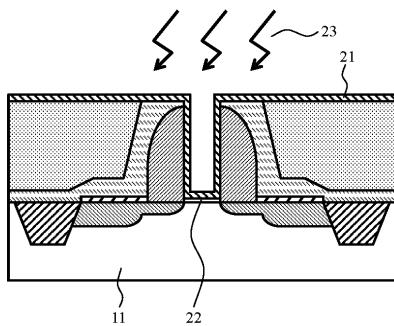

この後、図7に示す通り、酸素雰囲気でプラズマ処理を施し、high-k膜21中の酸素欠損を補う。この処理により同時にシリコン基板11とhigh-k膜21の界面にSiO<sub>2</sub>界面形成膜22が形成される。このSiO<sub>2</sub>界面形成膜22は、400程度でサブナノメータ程度の膜厚に形成される。

## 【0020】

以上のようにして、高誘電体ゲート絶縁膜を構成するhigh-k膜21とSiO<sub>2</sub>界面形成膜22を形成後、フッ素を界面に導入する目的で、F<sub>2</sub>の雰囲気(窒素との混合比で1vol.%から10vol.%程度の濃度に希釈した雰囲気)中で、100から400まで昇温し、1分から10分程度保持したプロセスを経てF<sub>2</sub>アニール23を施す。このプロセスを取ることにより、フッ素添加時に特別なアニール処理を行わない。この

10

20

20

30

40

50

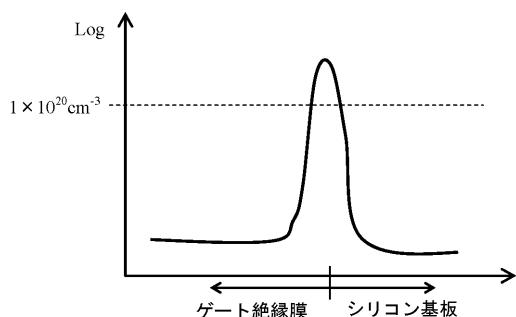

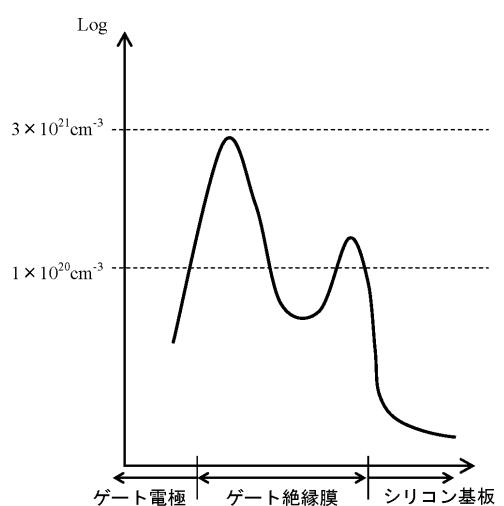

処理によって  $h$  i g h - k 膜 2 1、  $S$  i  $O$ <sub>2</sub> 界面形成膜 2 2 中、そして特にシリコン基板 1 1 との界面付近に多くのフッ素が局在する状態を実現できる(図 1 1 参照)。この界面には、 $10^{20} / cm^3$  以上の量のフッ素が存在する。

### 【 0 0 2 1 】

フッ素を導入するガス雰囲気として  $F_2$  を挙げたが、これはフッ素を含有する例えばフロロカーボン系ガス( $C F_4$ 、 $C_2 F_6$ 、 $C_3 F_8$ 、 $C_4 F_8$ 、 $C_4 F_4$ 、 $C_4 F_6$ 、 $C_5 F_8$ )やトリフルオロメタン( $C H F_3$ )、ジフルオロメタン( $C H_2 F_2$ )、六フッ化硫黄( $S F_6$ )、三フッ化窒素( $N F_3$ )、三フッ化塩素( $C_1 F_3$ )でも同様の効果が確認されている。但し、400 以下の低温で実現するためには、 $F_2$  が望ましい。

### 【 0 0 2 2 】

あるいは、上記  $N F_3$  ガス、 $F_2$  ガスをプラズマ励起し、このプラズマ励起で生成するフッ素の活性種の中でイオン種を除き、フッ素の中性ラジカルを上記  $h$  i g h - k 膜 2 1 表面に照射する、いわゆるフッ素のリモートプラズマ処理を施してもよい。この場合も、400 以下の低温下にて、 $h$  i g h - k 膜 2 1、 $S$  i  $O$ <sub>2</sub> 界面形成膜 2 2 中、及びシリコン基板 1 1 との界面付近に多くのフッ素を導入させることができる。

### 【 0 0 2 3 】

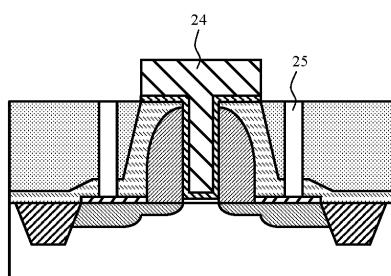

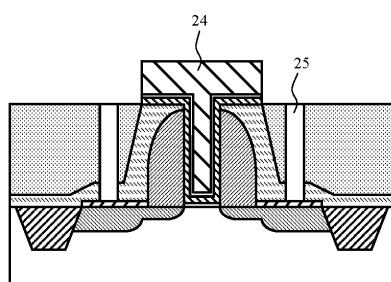

この後、図 8 に示す通り、例えば  $T$  i  $N$  または  $W$  などのメタル膜を CVD 法等で成膜し、公知のドライエッチング技術で加工してゲート電極 2 4 を形成し、ソースドレインのコンタクト 2 5 を形成し、配線材料工程を経て、例えば  $W$ 、 $A$  1 を用いて任意の回路を構成する。メタルゲート電極の形成など、 $h$  i g h - k 膜 2 1 形成後のプロセスは、600 以下の低温で行われる。このように 600 以下の低温のプロセスにすることにより、高誘電体ゲート絶縁膜に含有されるフッ素の活性化は抑制されて安定化し、高品質の高誘電体ゲート絶縁膜および界面が得られるようになる。また、このように低温プロセスにすることで、 $h$  i g h - k 膜 2 1 の膜質劣化、シリサイド層 1 9 の凝集等の問題は皆無になる。

### 【 0 0 2 4 】

上記ゲート電極 2 4 としては、 $T$  i  $N$  の他に、 $Z$  r  $N$  x、 $H$  f  $N$  x、 $V$  N x、 $N$  b  $N$  x、 $T$  a  $N$  x、 $M$  o  $N$  x、 $W$  N x、あるいは  $T$  i  $S$  i x  $N$  y、 $Z$  r  $S$  i x  $N$  y、 $H$  f  $S$  i x  $N$  y、 $V$  S i x  $N$  y、 $N$  b  $S$  i x  $N$  y、 $T$  a  $S$  i x  $N$  y、 $M$  o  $S$  i x  $N$  y、 $W$  S i x  $N$  y 等の導電体膜材料またはそれらの積層した材料を用いることができる。あるいは、 $T$  i、 $Z$  r、 $H$  f、 $V$ 、 $N$  b、 $T$  a、 $M$  o、 $W$  などの金属、 $T$  i  $S$  i x、 $Z$  r  $S$  i x、 $H$  f  $S$  i x、 $V$  S i x、 $N$  b  $S$  i x、 $T$  a  $S$  i x、 $M$  o  $S$  i x、 $W$  S i x、 $N$  i  $S$  i x、 $C$  o  $S$  i x などの金属珪化物、 $T$  i  $C$  x、 $Z$  r  $C$  x、 $H$  f  $C$  x、 $V$  C x、 $N$  b  $C$  x、 $T$  a  $C$  x、 $M$  o  $C$  x、 $W$  C x などの金属炭化物から成る導電体膜材料またはそれらの積層した材料を用いることができる。また、上記  $W$  の代わりに  $A$  1 や  $A$  1 合金、 $C$  u や  $C$  u 合金等を用いることができる。

### 【 0 0 2 5 】

次に、上記実施の形態 1 の一実施例における効果について説明する。

フッ素処理をした MISFET について、ゲート領域は、 $W / T$  i  $N / H$  f  $O_2$  (膜厚 2.5 nm) /  $S$  i  $O_2$  (膜厚 0.5 nm) の構造に形成され、その形成工程の順序は、図 1 ~ 図 8 の通りである。ここで、上記フッ素ガスの処理により、高誘電体ゲート絶縁膜中のフッ素分布は図 1 1 に示すようになる。そして、ダミーゲート時のソースドレイン拡散層の活性化アニールは、1000、3 秒程度であり、最終的なシンターは 400 である。また、フッ素処理をしない MISFET は、フッ素アニール工程のみを行わず、その他の工程は同じである。

### 【 0 0 2 6 】

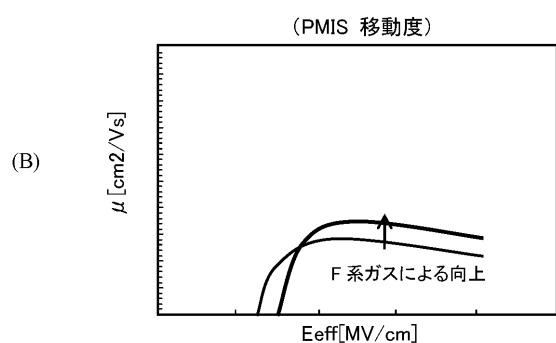

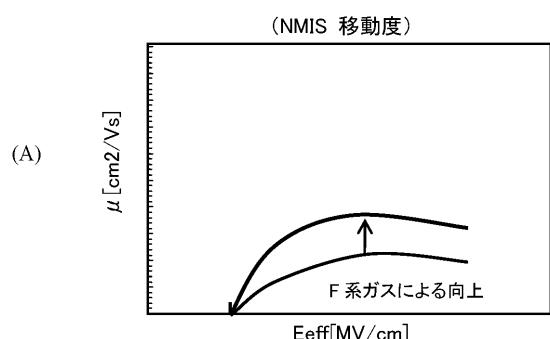

図 9 は、上記フッ素処理をした場合と、処理をしない場合の MISFET の移動度を示している。横軸が電界の強さ( $E_{eff} (MV / cm)$ )を示し、縦軸が移動度( $\mu (cm^2 / Vs)$ )を示している。図 9 (A) は、N 型 MISFET の移動度を示し、図 9 (B) は、P 型 MISFET の移動度を示している。N 型も P 型もともにフッ素処理により移

10

20

30

40

50

動度が向上している。N型MISFETは、P型MISFETより電界(横軸)全般に亘って移動度が向上しており、フッ素処理による効果がより多く得られていることを示している。

【0027】

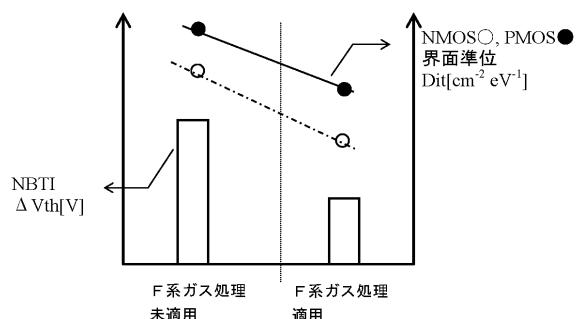

図10は、横軸の右部がフッ素系ガス処理を行った場合を示し、左部がフッ素系ガス処理を行わない場合を示している。右側の縦軸が界面準位( $D_{it}$  (cm<sup>-2</sup> eV<sup>-1</sup>))を示し、左側の縦軸がNBTI (Negative Bias Temperature Instability) (Vth (V))を示している。白丸がN型MISFETを示し、黒丸がP型MISFETを示している。折れ線グラフは、右側の縦軸を利用し、N型とP型のMISFETの界面準位の相違を示している。棒グラフは、左側の縦軸を利用し、フッ素系ガス処理による、しきい値の変動を示している。

【0028】

図10に示す通り、N型もP型も、フッ素系ガス処理により、界面準位が低下しており、大きく改善していることが読み取れる。特に、N型の界面準位がP型より小さいことが分かる。また、フッ素系ガス処理により、しきい値の変動が小さくなっていることを示している。この結果、BTストレスを印加した場合、デバイスの信頼性の差も明らかであり、デバイス特性と信頼性の両方を同時に満足できることが確認される。

【0029】

図11は、シリコン基板11とゲート絶縁膜21、22との界面付近のフッ素の導入量を示しており、界面付近のフッ素の導入量は、 $1 \times 10^{20} / \text{cm}^3$ 以上を示している。これにより、フッ素の導入量が界面付近で $1 \times 10^{20} / \text{cm}^3$ 以上であると、より効果が得られることが知られる。

【0030】

(実施の形態2)

次に、本発明の実施の形態2を図1～図6、図12～図15を参照して説明する。この実施の形態の特徴は、実施の形態1において説明したhigh-k膜上に更に極薄絶縁膜を形成してから、上述したところのフッ素導入を行うところにある。あるいは、high-k膜上にフッ素を含有する極薄絶縁膜を積層して形成するところにある。このようにすることで、high-k膜と極薄絶縁膜との界面領域に更に多量のフッ素が容易に導入できるようになる。

【0031】

実施の形態2の場合においても、実施の形態1の場合と全く同様に、図1～図6までの工程を経て、図6に示すダマシングートを構成するhigh-k膜21を成膜する。

【0032】

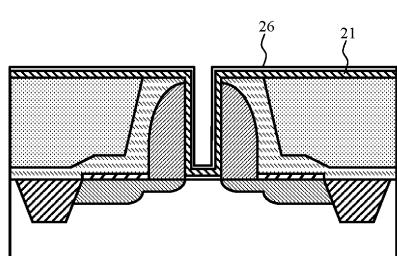

この後、図12に示す通り、酸素雰囲気でプラズマ処理を施し、high-k膜21中の酸素欠損を補う。同時に、この処理によりシリコン基板11とhigh-k膜21の界面にSiO<sub>2</sub>界面形成膜22が形成される。このSiO<sub>2</sub>界面形成膜22は、400程度で例えば0.5nm程度の膜厚に形成される。

【0033】

この後、図13に示す通り、例えばALD法により0.5nm～1.5nm程度の膜厚の極薄絶縁膜26を形成する。上記ALD法において、例えばジクロールシランガス(SiH<sub>2</sub>Cl<sub>2</sub>)、水(H<sub>2</sub>O)等を成膜原料のプリカーサとして使用しシリコン酸化膜を成膜温度200～300程度で堆積させる。この場合、high-k膜21を成膜するALD成膜装置と極薄絶縁膜26を成膜する成膜装置はマルチチャンバー構造になっており、high-k膜21と極薄絶縁膜26とを上記装置内で連続的に成膜するようすれば好適である。ここで、極薄絶縁膜26としてシリコン窒化膜、シリコン酸窒化膜等を形成してもよい。シリコン窒化膜の成膜では、成膜原料のプリカーサとしてジクロールシランガス(SiH<sub>2</sub>Cl<sub>2</sub>)とアンモニア(NH<sub>3</sub>)を用いればよく、シリコン酸窒化膜の成膜におけるプリカーサとしてはジクロールシランガス(SiH<sub>2</sub>Cl<sub>2</sub>)、水(H<sub>2</sub>O)およびアンモニア(NH<sub>3</sub>)を使用する。

10

20

30

40

50

## 【0034】

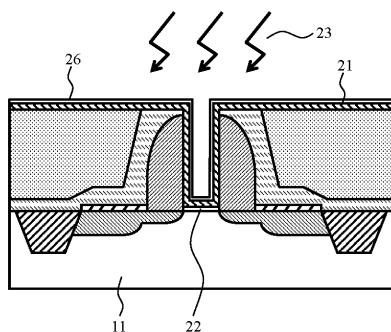

以上のようにして、高誘電体ゲート絶縁膜を構成するhigh-k膜21、 $\text{SiO}_2$ 界面形成膜22および極薄絶縁膜26を形成後、実施の形態1の場合と同様に、図14に示す通り、 $\text{F}_2$ ガスの雰囲気（窒素との混合比で1vol.%から10vol.%程度の濃度に希釈した雰囲気）中で、100から400まで昇温し、1分から10分程度保持したプロセスを経て $\text{F}_2$ アニール23を施す。このプロセスを取ることにより、フッ素添加時に特別なアニール処理を行わない。この処理によって極薄絶縁膜26とhigh-k膜21の界面、high-k膜21中、 $\text{SiO}_2$ 界面形成膜22中、及びシリコン基板11との界面付近に多くのフッ素が局在する状態を実現できる（図17参照）。これらの界面領域には、それぞれ $3 \times 10^{21} / \text{cm}^3$ 程度、 $1 \times 10^{20} / \text{cm}^3$ 以上のフッ素量が含有されるようになる。しかも、図11と比較しても明らかのように、極薄絶縁膜26、high-k膜21および $\text{SiO}_2$ 界面形成膜22から成る高誘電体ゲート絶縁膜に、実施の形態1の場合よりも1桁以上多量のフッ素を導入することが可能になる。

## 【0035】

この場合も、実施の形態1の場合と同様に、フッ素を導入するガス雰囲気として $\text{F}_2$ ガスの代わりにフッ素を含有する、例えばフロロカーボン系ガス（ $\text{CF}_4$ 、 $\text{C}_2\text{F}_6$ 、 $\text{C}_3\text{F}_8$ 、 $\text{C}_4\text{F}_8$ 、 $\text{C}_4\text{F}_4$ 、 $\text{C}_4\text{F}_6$ 、 $\text{C}_5\text{F}_8$ ）やトリフルオロメタン（ $\text{CHF}_3$ ）、ジフルオロメタン（ $\text{CH}_2\text{F}_2$ ）、六フッ化硫黄（ $\text{SF}_6$ ）、三フッ化窒素（ $\text{NF}_3$ ）、三フッ化塩素（ $\text{ClF}_3$ ）でも同様の効果が生じる。あるいは、上記 $\text{NF}_3$ ガス、 $\text{F}_2$ ガスをプラズマ励起し、フッ素の活性種の中でイオン種を除き、フッ素の中性ラジカルを上記high-k膜21表面に照射する、いわゆるフッ素のリモートプラズマ処理を施してもよい。この場合も、400以下の低温下にて、high-k膜21、 $\text{SiO}_2$ 界面形成膜22中、及びシリコン基板11との界面付近に多くのフッ素を導入させることができる。

## 【0036】

また、極薄絶縁膜26の上記成膜においてフッ素をドープしてもよい。例えば上記ALD法の成膜時に上記プリカーサと共にドーピングガスとして希釈した $\text{F}_2$ ガス（窒素との混合比で0.1vol.%～5vol.%程度）、 $\text{NF}_3$ ガスあるいは $\text{SF}_6$ ガスを成膜室（チャンバー）に導入し、フッ素ドープの極薄絶縁膜26を成膜する。この方法においても、図17に示したのと同様の濃度分布を有し多量のフッ素を含有する高誘電体ゲート絶縁膜を形成することが可能になる。

## 【0037】

この後、図15に示す通り、実施の形態1と同様にして、例えばTiNまたはWなどのメタル膜から成るゲート電極24を形成し、更にソースドレインのコンタクト25を形成し、配線材料工程を経て、例えばW、Alを用いて任意の回路を構成する。メタルゲート電極の形成など、high-k膜21形成後のプロセスは、600以下の低温で行うと好適である。この600以下の低温のプロセスにすることにより、高誘電体ゲート絶縁膜に含有する多量のフッ素は不活性で安定化したままであり、高品質の高誘電体ゲート絶縁膜および界面が得られる。ここで、600温度を超えるプロセスを用いると、上記含有するフッ素は活性化し逆にシリコン基板との界面に損傷を与え易くなる。

## 【0038】

以下、上記実施の形態2の一実施例における効果について説明する。

上述した $\text{F}_2$ アニールによるフッ素処理をしたMISFETについて、ゲート領域は、W/TiN/SiN（膜厚0.5nm）/HfSiOx（膜厚2.0nm）/SiO<sub>2</sub>（膜厚0.5nm）の構造に形成され、その形成工程の順序は、図1～図6、図12～図15の通りである。ここで、上記 $\text{F}_2$ アニールにより、高誘電体ゲート絶縁膜中のフッ素分布は図17に示すようになる。そして、ダミーゲート時の活性化アニールは、1000、3秒程度であり、最終的なシンターは400である。また、フッ素処理をしないMISFETは、 $\text{F}_2$ アニール工程のみを行わず、その他の工程は同じである。

## 【0039】

10

20

30

40

50

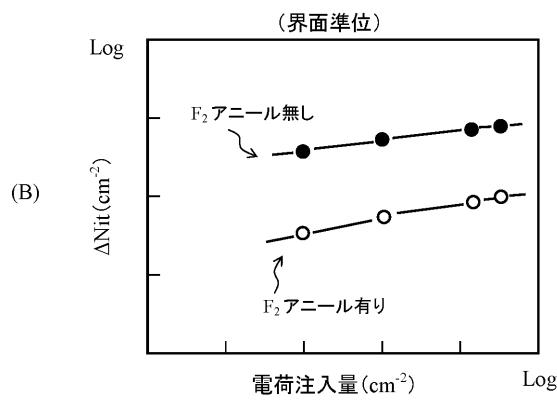

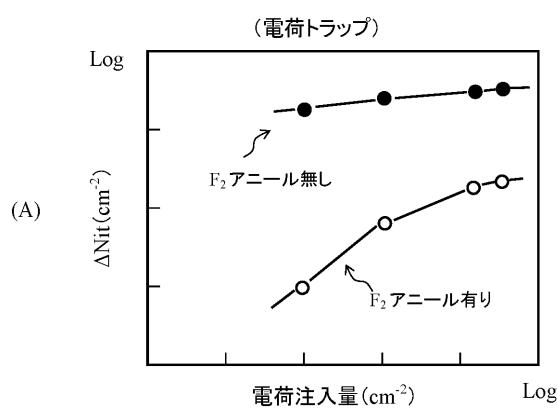

図16は、上記フッ素処理をした場合と、処理をしない場合のnチャネルMISFETの高誘電体ゲート絶縁膜中の電荷トラップ量と、上記高誘電体ゲート絶縁膜/シリコン基板界面の界面準位とを評価した結果を示している。この評価は、上記MISFETを公知のチャージポンピング法で測定して行った。ここで、図16(A)は、電荷トラップ量の評価結果を示し、図16(B)は、界面準位の評価結果を示している。図16(A、B)の横軸に高誘電体ゲート絶縁膜中の電荷注入量をとり、図16(A)の縦軸には高誘電体ゲート絶縁膜中の電荷注入により電荷トラップに捕獲された電荷キャリア数(トラップ電荷の増加量に対応している)を単位面積当たりで示す。そして、図16(B)の縦軸は高誘電体ゲート絶縁膜中の電荷注入ストレス(BTストレスに相当する)による界面準位密度の増加量を示している。

10

## 【0040】

図16(A)に示す通り、黒丸のフッ素処理をしないMISFETの場合は、白丸のフッ素処理をしたMISFETの場合よりも、電荷トラップは少なくとも1桁以上多く存在する。これは、上記実施の形態2で説明したようにMISFETの高誘電体ゲート絶縁膜中にフッ素を含有させることにより、膜中、特にhigh-k膜中の電荷トラップ量が1桁以上低減することを示している。

## 【0041】

図16(B)に示す通り、黒丸のフッ素処理をしないMISFETの場合は、白丸のフッ素処理をしたMISFETの場合よりも、上記ストレスによる界面準位の生成量は少なくとも1桁以上多くなる。これは、上記実施の形態2で説明したようにMISFETの高誘電体ゲート絶縁膜中にフッ素を含有させることにより、高誘電体ゲート絶縁膜/シリコン基板界面の結合状態が安定化することを示している。また、上記フッ素処理により、図10で説明したように界面準位は低下することは、実施の形態1の場合と全く同じである。上記図16で説明したフッ素処理の効果は、pチャネルMISFETの場合にも同様に生じるものである。

20

## 【0042】

図17は、実施の形態2特有の3層構造になる高誘電体ゲート絶縁膜へのフッ素の導入量を示している。図11と比較して判るように、この場合は、シリコン基板11とSiO<sub>2</sub>界面形成膜22、high-k膜21との界面付近、high-k膜21と極薄絶縁膜26との界面領域に多量のフッ素が蓄積(バイルアップ)する形態で含有される。そして、シリコン界面付近のフッ素の導入量は、 $1 \times 10^{20} / \text{cm}^3$ 以上を示し、high-k膜21と極薄絶縁膜26と界面付近のフッ素の導入量は、更に1桁以上の多い $3 \times 10^{21} / \text{cm}^3$ 程度になる。

30

## 【0043】

このようにhigh-k膜21を挟む上記2箇所の界面領域にフッ素が含有するようになるために、通常ではフッ素固溶度の小さいhigh-k膜21中であっても多量のフッ素を含有させることができ可能になり、シリコン基板表面の界面準位の低減、膜中の電荷トラップの低減が容易に達成できるようになる。そして、高品質および信頼性の高い高誘電体ゲート絶縁膜の形成が可能になる。

40

## 【0044】

また、この実施の形態2の場合には、上記メカニズムによりhigh-k膜21に充分なフッ素量を含有させることが可能になり、フッ素導入のプロセス余裕度が非常に高くなつて導入フッ素量の調整/制御が容易になる。

## 【0045】

本発明は、上記実施の形態に限定されるものでなく、発明の趣旨を逸脱しない範囲でいろいろの変形を探ることができる。例えば、上述したようなダマシン構造のゲート電極のMISFETの代わりに、通常の構造であるフラット構造のゲート電極を有するMISFETの形成の場合にも本発明は同様に適用できるものである。この場合、高誘電体ゲート絶縁膜を形成後に、MISFETのソースドレイン等の拡散層を形成する。そこで、high-k膜の耐熱性を高めるために窒素を膜中に含有させるとよい。あ

50

- 2 0 1 · · 層間膜(窒化膜)

2 0 2 · · 層間膜(酸化膜)

2 1 · · · h i g h - k 膜

2 2 · · · SiO<sub>2</sub> 界面形成膜

2 3 · · · F<sub>2</sub> アニール

2 4 · · · メタルゲート電極

2 5 · · · コンタクト電極

2 6 · · · 極薄絶縁膜

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

**H 01 L 29/49 (2006.01)** H 01 L 29/78 3 0 1 G

H 01 L 29/50 M

H 01 L 29/58 G

F ターム(参考) 4M104 AA01 BB02 BB04 BB13 BB14 BB16 BB17 BB18 BB20 BB21

BB24 BB25 BB26 BB27 BB28 BB29 BB30 BB31 BB32 BB33

BB34 BB36 CC01 CC05 DD03 DD04 DD22 DD26 DD37 DD65

DD84 EE03 EE16 GG09 GG10 GG14

5F058 BA20 BC03 BD04 BD05 BD10 BD15 BH02 BH03 BH16 BJ01

5F140 BA01 BD01 BD02 BD05 BD07 BD09 BD11 BD12 BD13 BD15

BD17 BE03 BE09 BE10 BE17 BF01 BF05 BF06 BF07 BF08

BF10 BF11 BF17 BG03 BG04 BG08 BG28 BG38 BJ08 BJ11

BJ15 BJ17 BJ27 BK02 BK05 BK13 BK21 BK25 BK29 BK34

CB04 CC01 CC03 CC08 CE07 CE10 CE18