(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-49759

(P2006-49759A)

(43) 公開日 平成18年2月16日(2006.2.16)

(51) Int.CI.

HO1L 21/768 (2006.01)

F 1

HO1L 21/90

HO1L 21/90

テーマコード(参考)

5FO33

C

審査請求 未請求 請求項の数 9 O L (全 14 頁)

(21) 出願番号

特願2004-232098 (P2004-232098)

(22) 出願日

平成16年8月9日(2004.8.9)

(71) 出願人

503121103 株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人

100089118

弁理士 酒井 宏明

(72) 発明者

清水 秀

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5F033 HH04 HH09 HH28 HH33 JJ19

JJ33 KK01 KK09 KK33 MM07

MM08 MM13 MM15 NN06 NN07

NN08 NN40 QQ08 QQ09 QQ10

QQ11 QQ28 QQ31 QQ35 QQ37

QQ39 QQ48 RR04 RR06 RR20

SS15 TT08 VV06 XX03

(54) 【発明の名称】半導体装置及び半導体装置の製造方法

(57) 【要約】 (修正有)

【課題】多層配線の狭ピッチ化に対応可能な半導体装置

およびその製造方法を得る。

【解決手段】半導体基板上に複数の第1配線層を形成する工程と、第1配線層を覆うように第1層間絶縁膜層9を形成する工程と、第1層間絶縁膜層に、表面からその厚み方向に貫いて第1配線層に接続する複数の第1プラグ14を形成する工程と、第1層間絶縁層上であって、第1プラグのうち一部の第1プラグの直上部に第2配線層40を形成する工程と、第1層間絶縁膜層上に第2配線層を覆うように第2層間絶縁膜層19を形成する工程と、第2層間絶縁膜層に、表面からその厚み方向に貫いて第2配線層に接続する第2プラグ24'、と、表面からその厚み方向に貫いて第1プラグに直接接続する第3プラグ24と、を同時に形成する工程と、第2層間絶縁膜層上であって、第2プラグおよび第3プラグの直上部に第3配線層50を形成する工程と、を含む。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体基板上に多層にわたって形成された配線層を有する半導体装置であって、その厚み方向に隣り合わない配線層同士、または前記半導体基板と該半導体基板にその厚み方向に隣り合わない配線層とが、プラグにより直接、電気的に接続されていることを特徴とする半導体装置。

**【請求項 2】**

前記隣り合わない配線層の間に形成された配線層上に、該配線層を覆う層間絶縁膜層よりもエッティング選択比が高い層を有し、前記配線層と該配線層の上層の配線層とが前記層間絶縁膜層および前記層間絶縁膜層よりもエッティング選択比が高い層をその厚み方向に貫くプラグを介して電気的に接続されていること

を特徴とする請求項 1 に記載の半導体装置。

**【請求項 3】**

前記層間絶縁膜層よりもエッティング選択比が高い層が、前記配線層よりもエッティング選択比が高いこと

を特徴とする請求項 2 に記載の半導体装置。

**【請求項 4】**

半導体基板上に複数の第 1 配線層を形成する第 1 配線層形成工程と、

前記第 1 配線層を覆うように第 1 層間絶縁膜層を形成する第 1 層間絶縁層形成工程と、

前記第 1 層間絶縁膜層に、表面からその厚み方向に貫いて前記第 1 配線層に接続する複数の第 1 プラグを形成する第 1 プラグ形成工程と、

前記第 1 層間絶縁層上であって、前記第 1 プラグのうち一部の第 1 プラグの直上部に第 2 配線層を形成する第 2 配線層形成工程と、

前記第 1 層間絶縁膜層上に前記第 2 配線層を覆うように第 2 層間絶縁膜層を形成する第 2 層間絶縁膜層形成工程と、

前記第 2 層間絶縁膜層に、表面からその厚み方向に貫いて前記第 2 配線層に接続する第 2 プラグと、表面からその厚み方向に貫いて前記第 1 プラグに直接接続する第 3 プラグと、を同時に形成する第 2 および第 3 プラグ形成工程と、

前記第 2 層間絶縁膜層上であって、前記第 2 プラグおよび第 3 プラグの直上部に第 3 配線層を形成する第 3 配線層形成工程と、

を含むことを特徴とする半導体装置の製造方法。

**【請求項 5】**

前記第 2 配線層形成工程が、

前記第 2 配線層上に前記第 2 層間絶縁膜層よりもエッティング選択比の高い層を形成する工程をさらに含み、

前記第 2 および第 3 プラグ形成工程において、

前記第 2 層間絶縁膜層および前記エッティング選択比の高い層をエッティングすることにより前記第 3 のプラグを前記第 2 のプラグと同時に形成すること

を特徴とする請求項 4 に記載の半導体装置の製造方法。

**【請求項 6】**

前記第 2 配線層形成工程が、

前記第 1 層間絶縁層上に第 2 配線層膜を成膜する工程と、

前記第 2 配線層膜上に、前記第 2 層間絶縁膜層と前記第 2 配線層膜とよりもエッティング選択比の高い膜を成膜する工程と、

前記エッティング選択比の高い膜をエッティングによりパターニングして前記第 2 層間絶縁膜層および前記第 2 配線層膜よりもエッティング選択比の高い層を形成する工程と、

前記エッティング選択比の高い層をエッティングマスクとして前記第 2 配線層膜をエッティングすることにより前記第 2 配線層を形成する工程と、

を含み、

前記第 2 および第 3 プラグ形成工程において、

10

20

30

40

50

前記第2層間絶縁膜層および前記エッチング選択比の高い層をエッチングすることにより前記第3のプラグを前記第2のプラグと同時に形成することを特徴とする請求項4に記載の半導体装置の製造方法。

**【請求項7】**

半導体基板上に不純物拡散層を含む半導体素子を形成する半導体素子工程と、前記半導体素子を覆うように第1層間絶縁膜層を形成する第1層間絶縁膜層形成工程と、

前記第1層間絶縁膜層に、表面からその厚み方向に貫いて前記不純物拡散層に接続する複数の第1プラグを形成する第1プラグ形成工程と、

前記第1層間絶縁層上であって、前記第1プラグのうち一部の第1プラグの直上部に第1配線層を形成する第1配線層形成工程と、

前記第1層間絶縁膜層上に前記第1配線層を覆うように第2層間絶縁膜層を形成する第2層間絶縁膜層形成工程と、

前記第2層間絶縁膜層に、表面からその厚み方向に貫いて前記第1配線層に接続する第2プラグと、表面からその厚み方向に貫いて前記第1プラグに直接接続する第3プラグと、を同時に形成する第2および第3プラグ形成工程と、

前記第2層間絶縁膜層上であって、前記第2プラグおよび第3プラグの直上部に第2配線層を形成する第2配線層形成工程と、

を含むことを特徴とする半導体装置の製造方法。

**【請求項8】**

前記第1配線層形成工程が、

前記第1配線層上に前記第2層間絶縁膜層よりもエッチング選択比の高い層を形成する工程をさらに含み、

第2および第3プラグ形成工程において、

前記第2層間絶縁膜層および前記エッチング選択比の高い層をエッチングすることにより前記第3のプラグを前記第2のプラグと同時に形成することを特徴とする請求項7に記載の半導体装置の製造方法。

**【請求項9】**

前記第1配線層形成工程が、

前記第1層間絶縁層上に第1配線層膜を成膜する工程と、

前記第1配線層膜上に、前記第2層間絶縁膜層と前記第1配線層膜とよりもエッチング選択比の高い膜を成膜する工程と、

前記エッチング選択比の高い膜をエッチングによりパターニングして前記第2層間絶縁膜層および前記第1配線層膜よりもエッチング選択比の高い層を形成する工程と、

前記エッチング選択比の高い層をエッチングマスクとして前記第2配線層膜をエッチングすることにより前記第2配線層を形成する工程と、

を含み、

前記第2および第3プラグ形成工程において、

前記第2層間絶縁膜層および前記エッチング選択比の高い層をエッチングすることにより前記第3のプラグを前記第2のプラグと同時に形成することを特徴とする請求項7に記載の半導体装置の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、多層配線を有して成る半導体装置及び半導体装置の製造方法に関するものであり、特に多層配線の狭ピッチ化に対応可能な半導体装置および半導体装置の製造方法に関するものである。

**【背景技術】**

**【0002】**

10

20

30

40

50

近年、半導体集積回路の小型化、高性能化に伴って半導体装置の高集積化が進んでいる。そして、半導体装置の高集積化を進めるために多層配線が広く用いられている。このような多層配線を用いた半導体装置として多くの技術が研究されているが、たとえば、基板と、少なくとも1層のメタル配線と、セラミック薄膜容量を有する半導体装置であって前記セラミック薄膜容量は、下部電極、セラミック薄膜、上部電極がこの順に積層されてなり、前記下部電極、セラミック薄膜、上部電極がメタル配線よりも上部に形成されてなる、容易に多層メタル配線を形成可能な半導体装置が提案されている（たとえば特許文献1参照）。

#### 【0003】

【特許文献1】特開平11-317500号公報

10

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0004】

ところで、このような半導体装置の高集積化が進むにつれて、メタル配線の狭ピッチ化が必須となる。従来の半導体装置においては、たとえば3層のメタル配線を有して成る半導体装置の場合、すなわち半導体基板と、該半導体基板側の第1層目のメタル配線と、その直上の第2層目のメタル配線、さらにその直上の第3層目のメタル配線と、を備えて構成される場合、まず、半導体基板または第1層メタル配線と、第2層メタル配線とをプラグでつなぎ、さらに第2層メタル配線と第3層メタル配線とをプラグでつながなくてはならない。

20

#### 【0005】

このため、メタル配線の狭ピッチ化が進むと、メタル配線全体のレイアウトが第2層メタル配線の最小デザインルールで律速されてしまうことがある。第2層メタル配線のデザインルールをより微細のパターンに対応できるようにするためにには、高価な製造装置やプロセスを使用する必要があり、製造コストが高くなるという問題がある。またこれらを使用することができない場合には、レイアウト面積が拡大し、半導体チップのチップサイズが大きくなってしまうという問題がある。

#### 【0006】

しかしながら、上述したような特許文献1にかかる従来の技術ではメタル配線の狭ピッチ化については検討されていない。

30

#### 【0007】

本発明は、上記に鑑みてなされたものであって、多層配線の狭ピッチ化に対応可能な半導体装置およびその製造方法を得ることを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

上述した課題を解決し、目的を達成するために、本発明にかかる半導体装置は、半導体基板上に多層にわたって形成された配線層を有する半導体装置であって、その厚み方向に隣り合わない配線層同士、または半導体基板と該半導体基板にその厚み方向に隣り合わない配線層とが、プラグにより直接、電気的に接続されていることを特徴とする。

40

#### 【0009】

この発明によれば、その厚み方向に隣り合わない配線層同士、または半導体基板と該半導体基板にその厚み方向に隣り合わない配線層とが、他の配線層を介さずに直接電気的に接続されている。これにより、配線層のレイアウトに因らずその厚み方向に隣り合わない配線層同士、または半導体基板と該半導体基板にその厚み方向に隣り合わない配線層とが接続される。

#### 【発明の効果】

#### 【0010】

この発明によれば、多層配線の狭ピッチ化が進んだ場合においても、配線層のデザインルールによらず確実にその厚み方向に隣り合わない配線層同士、または半導体基板と該半導体基板にその厚み方向に隣り合わない配線層とを電気的に接続することが可能である。

50

すなわち、この半導体装置によれば、配線層全体のレイアウトが特定の配線層のデザインルールにより律速されることが無く、多層配線の狭ピッチ化が進んだ場合においても、配線層全体のレイアウトをより微細なパターンに対応させることができ、配線レイアウトの縮小が可能である。したがって、この発明によれば、多層配線の狭ピッチ化に対応可能な半導体装置を提供することができるという効果を奏する。

#### 【発明を実施するための最良の形態】

##### 【0011】

以下に、本発明にかかる半導体装置およびその製造方法の実施の形態を図面に基づいて詳細に説明する。なお、本発明は以下の記述に限定されるものではなく、本発明の要旨を逸脱しない範囲において適宜変更可能である。

10

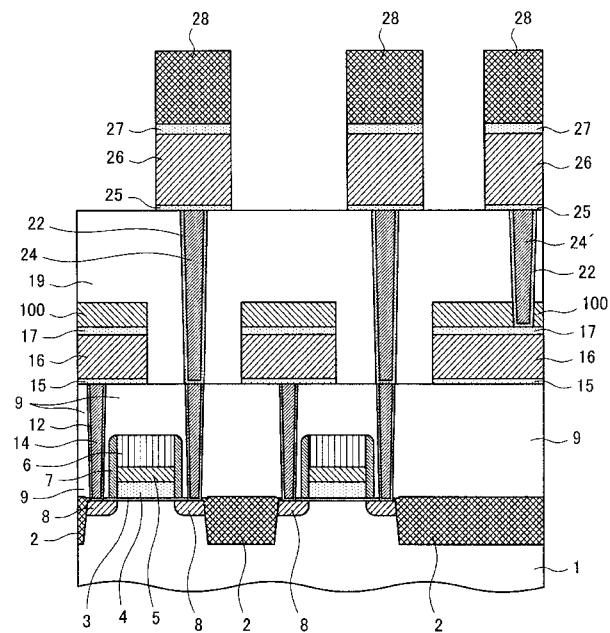

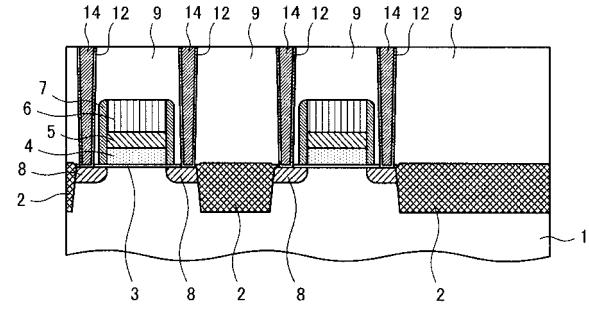

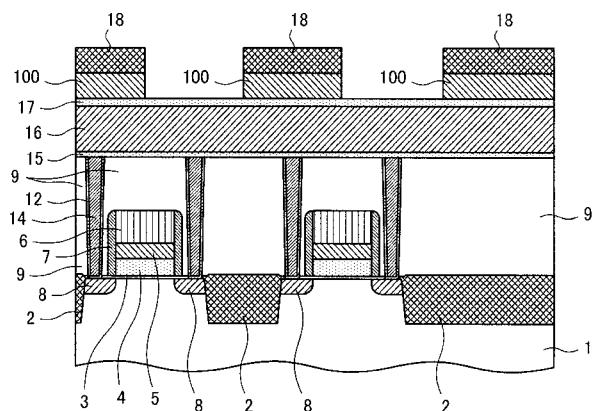

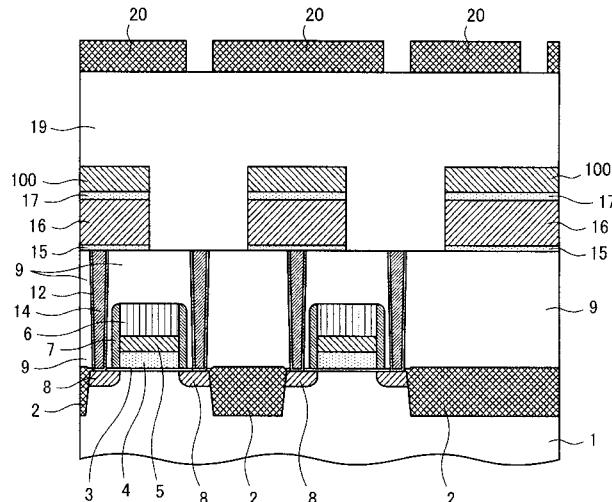

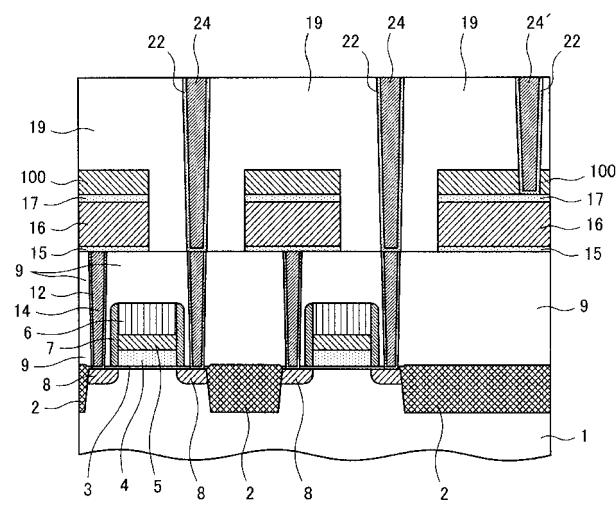

##### 【0012】

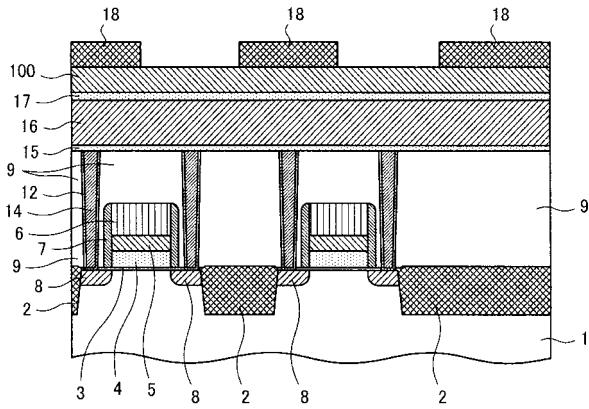

#### 実施の形態 .

図1は、本発明の実施の形態にかかる半導体装置の構成を示す断面図である。まず、半導体装置の構成について説明する。半導体基板であるシリコン基板1上には、ゲート構造30が形成されている。また、このゲート構造30上には層間絶縁膜9を挟んで第1メタル配線40が設けられている。この第1メタル配線40は、窒化チタン(TiN)等から成るバリアメタル膜15、17と、アルミ銅(AlCu)などから成る導電膜16と、が積層されて構成されている。

##### 【0013】

また、第1メタル配線40上、すなわちバリアメタル膜17上には、該第1メタル配線40の周囲に形成されている層間絶縁膜19よりも高いエッティング選択比を有する酸化膜100が積層されている。この酸化膜100は、シリコン(Si)と酸素(O)との含有比がシリコン(Si)が1に対して酸素(O)が2未満とされている。そして、この第1メタル配線40とゲート構造30のソース/ドレインとして機能する不純物拡散領域8とがコンタクトプラグ14およびバリアメタル膜12を介して電気的に接続されている。

20

##### 【0014】

第1メタル配線40の上面および周囲は層間絶縁膜19により覆われており、該層間絶縁膜19上に第2メタル配線50が形成されている。この第2メタル配線50は、窒化チタン(TiN)等から成るバリアメタル膜25、27と、アルミ銅(AlCu)などから成る導電膜26と、が積層されて構成されている。そして、この第2メタル配線50と第1メタル配線40とがヴィアプラグ24およびバリアメタル膜22を介して電気的に接続されている。また、この第2メタル配線50と不純物拡散領域8とがヴィアプラグ24、バリアメタル膜22、コンタクトプラグ14およびバリアメタル膜12を介して電気的に接続されている。すなわち、この第2メタル配線50と不純物拡散領域8とは、第1メタル配線40を介さずに電気的に接続されている。

30

##### 【0015】

上述したように、本実施の形態にかかる半導体装置においては、不純物拡散領域8と第2メタル配線50との接続において、ヴィアプラグ24とコンタクトプラグ14とが、第1メタル配線40を介すことなく直接つながれている。すなわち、この半導体装置においては、ヴィアプラグ24とコンタクトプラグ14とが、第1メタル配線40を介すことなく直接電気的に接続されている。

40

##### 【0016】

このように、ヴィアプラグ24とコンタクトプラグ14とが、第1メタル配線40を介すことなく直接つながることにより、第1メタル配線40のデザインルールに起因して第2メタル配線50と不純物拡散領域8とが接続できないという状況が発生せず、第1メタル配線40のデザインルールによらず確実に第2メタル配線50と不純物拡散領域8とを接続することが可能である。

##### 【0017】

すなわち、この半導体装置によれば、多層配線の狭ピッチ化が進んだ場合においても、第1メタル配線40のデザインルールによらず確実に第2メタル配線50と不純物拡散領

50

域 8 とを確実に接続することが可能である。したがって、この半導体装置によれば、メタル配線全体のレイアウトが第 1 層メタル配線の最小デザインルールにより律速されること無く、多層配線の狭ピッチ化が進んだ場合においても、メタル配線全体のレイアウトをより微細なパターンに対応させることができ、配線レイアウトの縮小が可能である。

#### 【 0 0 1 8 】

したがって、本実施の形態にかかる半導体装置によれば、多層配線の狭ピッチ化に対応可能な半導体装置を提供することができる。

#### 【 0 0 1 9 】

また、この半導体装置によれば、第 2 メタル配線 50 と不純物拡散領域 8 とを接続するために、高価な製造装置やプロセスを使用する必要が無く、複雑なレイアウト設計も必要ない。このため、製造コストの増加を伴うことなく安価に製造することができる。そして、多層配線の狭ピッチ化が進んだ場合においても、メタル配線全体のレイアウトをより微細なパターンに対応させることができるので、レイアウト面積を拡大させることなく、小型化された半導体装置を製造することができる。

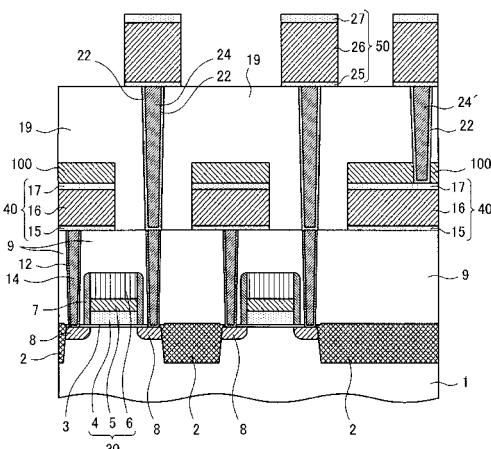

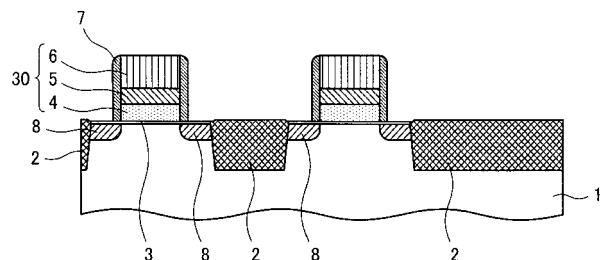

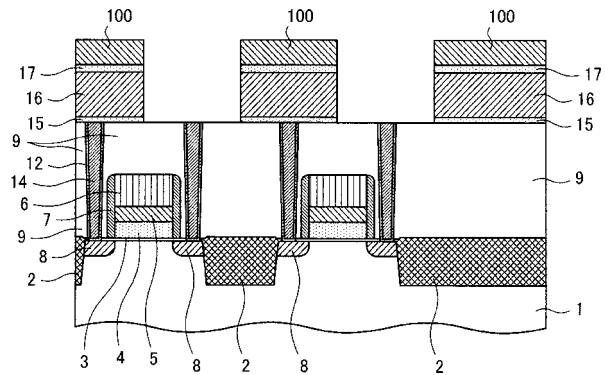

#### 【 0 0 2 0 】

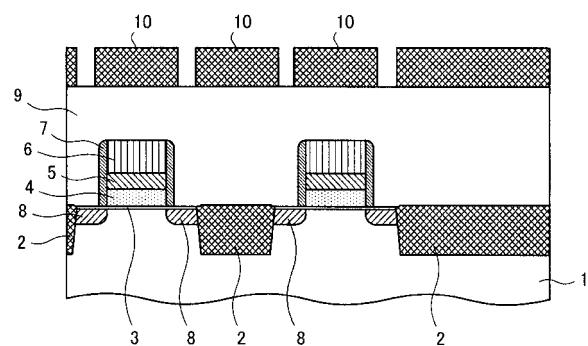

つぎに、以上のように構成された本実施の形態にかかる半導体装置の製造方法について図面を用いて説明する。まず、図 2 に示すように公知の技術によりシリコン基板 1 に素子分離酸化膜 2、およびゲート構造 30 を形成する。すなわち、ゲート酸化膜 3 を介してシリコン基板 1 上にポリシリコンから成るゲート電極 4、タングステンシリサイド (W Si) から成るゲート電極 5、シリコン窒化膜 (SiN) から成るハードマスク 6 を形成し、またシリコン基板 1 中に不純物拡散領域 8 を形成する。また、ゲート電極 4、5 およびハードマスク 6 の側壁に窒化シリコン (SiN) から成るサイドウォール 7 を形成する。

#### 【 0 0 2 1 】

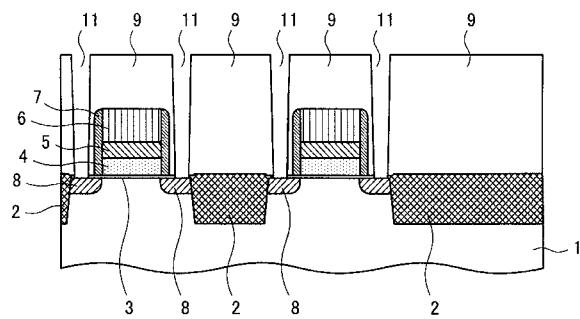

つぎに、図 3 に示すようにプラズマ CVD (Chemical Vapor Deposition) 法などにより、ゲート構造 30 を覆うようにシリコン基板 1 上にシリコン酸化膜などから成る層間絶縁膜 9 を形成し、さらに該層間絶縁膜 9 上に写真製版によりフォトレジスト 10 を形成する。ここで、該フォトレジスト 10 は、次工程におけるコンタクトホールの形成領域に対応する部分に開口部を有するパターンにて形成する。

#### 【 0 0 2 2 】

つぎに、フォトレジスト 10 をエッチングマスクとして層間絶縁膜 9 をドライエッチングして、コンタクトホールの形成領域の層間絶縁膜 9 を除去する。そして、ドライエッチング後、フォトレジスト 10 を除去する。これにより、図 4 に示すようにコンタクトホール 11 が形成される。

#### 【 0 0 2 3 】

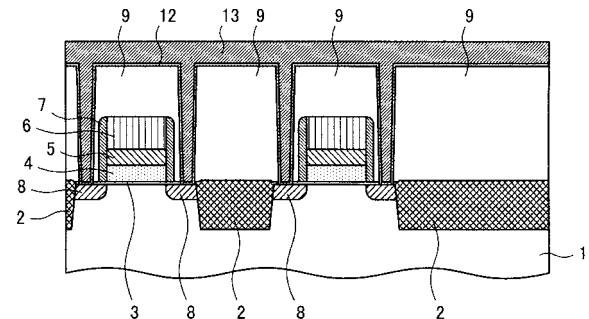

つぎに、図 5 に示すように層間絶縁膜 9 の上面およびコンタクトホール 11 の内壁、すなわち内側面および底面に窒化チタン (TiN) などを成膜してバリアメタル膜 12 を形成する。そして、図 6 に示すようにバリアメタル膜 12 の上面およびコンタクトホール 11 の内壁に、タングステン (W) などの導電膜 13 を成膜する。この導電膜 13 は、コンタクトホール 11 が確実に埋まるようにコンタクトホール 11 の上径の半分以上の膜厚で成膜する。

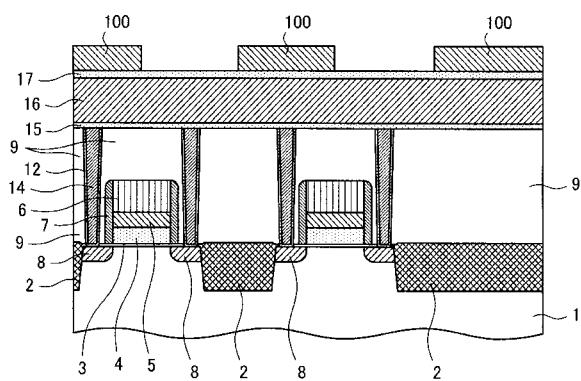

#### 【 0 0 2 4 】

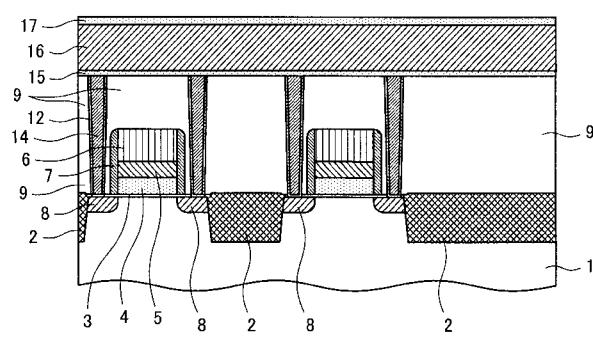

つぎに、図 7 に示すように、CMP (Chemical Mechanical Polishing) またはエッチバックによりコンタクトホール 11 内の導電膜 13 を残した状態で層間絶縁膜 9 の上面に成膜された導電膜 13 およびバリアメタル膜 12 を除去してコンタクトプラグ 14 を形成する。ついで、図 8 に示すように層間絶縁膜 9、バリアメタル膜 12 およびコンタクトプラグ 14 の上面に窒化チタン (TiN) などを成膜してバリアメタル膜 15 を形成し、該バリアメタル膜 15 上にアルミ銅 (AlCu) などの導電膜 16 を形成し、さらにその上に窒化チタン (TiN) などを成膜してバリアメタル膜 17 を形成する。

#### 【 0 0 2 5 】

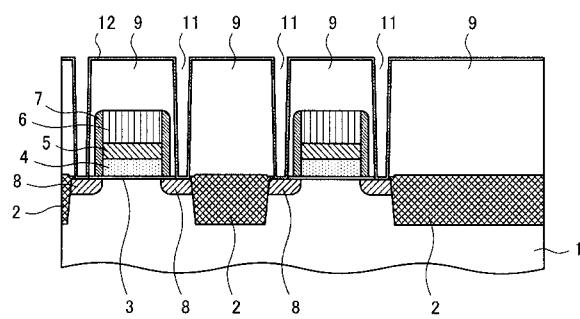

そして、図 9 に示すようにバリアメタル膜 17 上に酸化膜 100 を形成する。ここで、

10

20

30

40

40

50

酸化膜 100 は、シリコン (Si) と酸素 (O) との含有比がシリコン (Si) が 1 に対して酸素 (O) が 2 未満であり、後述する層間絶縁膜 19 よりもシリコン (Si) の含有率が高くドライエッティングにおいて該層間絶縁膜 19 よりも高い選択比を有する膜である。また、この酸化膜 100 は、バリアメタル膜 17、導電膜 16 およびバリアメタル膜 15 よりも高い選択比を有する膜である。このような酸化膜 100 としては、たとえばシリコンと酸素 ( $O_2$ ) との混合ガスからプラズマ CVD 法で作られる酸化膜などを形成することができます。

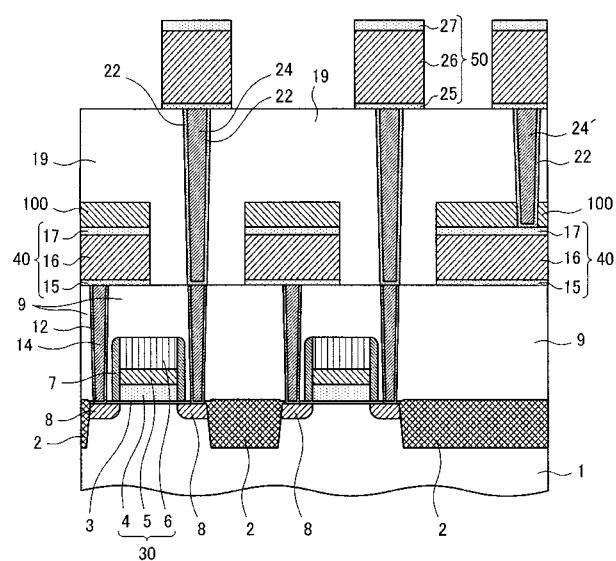

#### 【0026】

つぎに、図 10 に示すように写真製版により酸化膜 100 上にフォトレジスト 18 を形成する。ここで、該フォトレジスト 18 は、第 1 メタル配線 40 の形成領域に対応する部分を覆い、それ以外の部分に開口部を有するパターンにて形成する。10

#### 【0027】

つぎに、図 11 に示すようにフォトレジスト 18 をエッティングマスクとして酸化膜 100 をドライエッティングして、第 1 メタル配線 40 の形成領域以外の酸化膜 100 を除去する。そして、ドライエッティング後、フォトレジスト 18 を除去する。これにより、図 12 に示すように第 1 メタル配線 40 の形成領域にのみ酸化膜 100 が残されたパターンがなされる。20

#### 【0028】

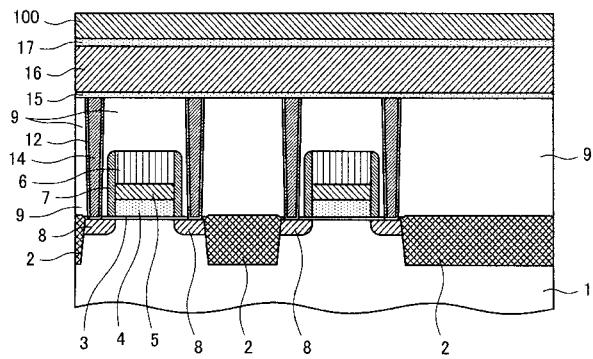

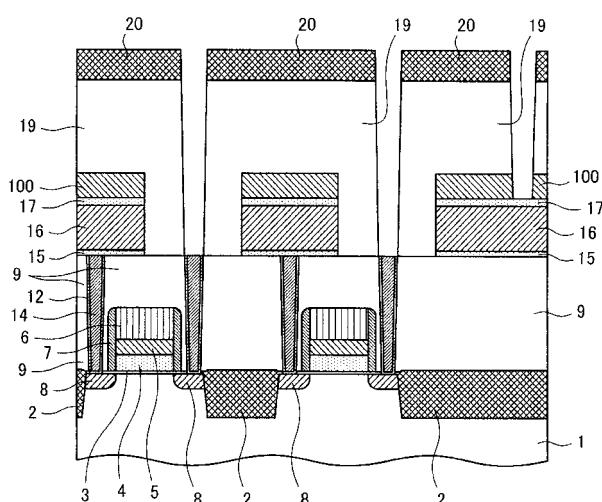

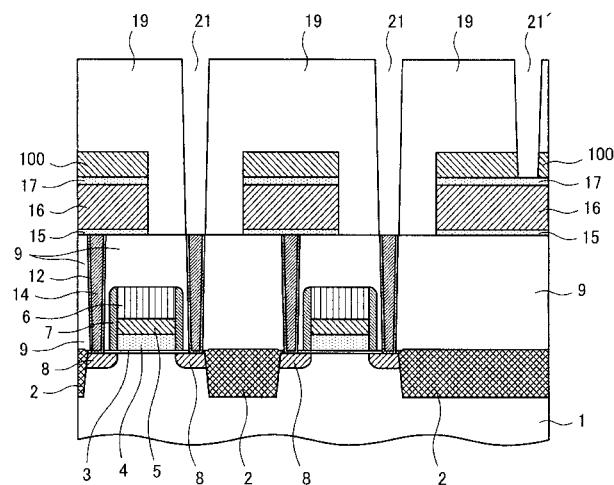

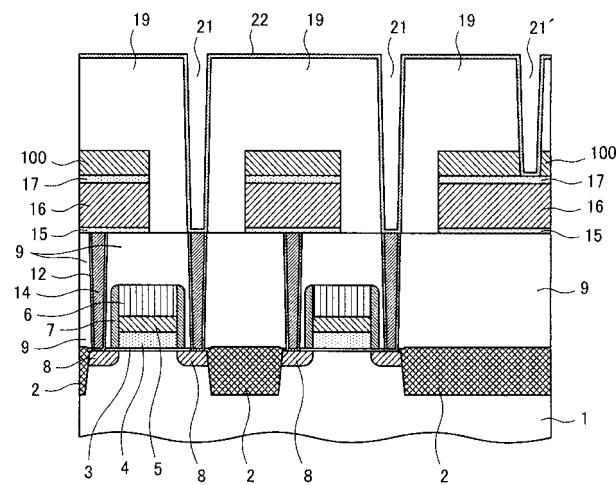

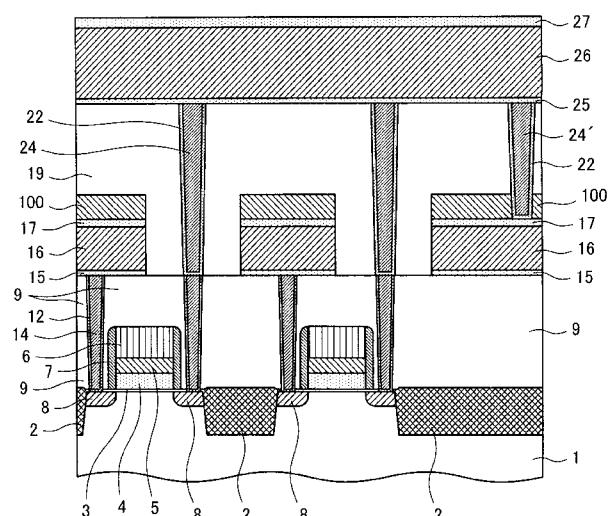

つぎに、図 13 に示すようにパターンングされた酸化膜 100 をエッティングマスクとしてバリアメタル膜 17、導電膜 16 およびバリアメタル膜 15 をドライエッティングする。これにより、図 13 に示すように第 1 メタル配線 40 が形成される。その後、図 14 に示すように、第 1 メタル配線 40 を覆うように酸化膜などから成る層間絶縁膜 19 を形成し、さらに該層間絶縁膜 19 上に写真製版によりフォトレジスト 20 を形成する。ここで、該フォトレジスト 20 は、コンタクトプラグ 14 に到達するヴィアホール 21 および第 1 メタル配線 40 に到達するヴィアホール 21 の形成領域に対応する部分に開口部を有するパターンにて形成する。20

#### 【0029】

つぎに、図 15 に示すようにフォトレジスト 20 をエッティングマスクとして層間絶縁膜 19 をドライエッティングして、ヴィアホール 21 およびヴィアホール 21 の形成領域の層間絶縁膜 19 を除去しヴィアホールを形成する。ここで、従来の製造方法では、コンタクトプラグ 14 上と第 1 メタル配線 40 上とでは、形成されるヴィアホールの深さが異なるため、コンタクトプラグ 14 上と第 1 メタル配線 40 上とに、同時にヴィアホールを形成することは困難である。30

#### 【0030】

そこで、本発明においては、第 1 メタル配線 40 上に酸化膜 100 を形成している。ここで酸化膜 100 は、層間絶縁膜 19 よりもシリコン (Si) の含有率を高くして、ヴィアホールを形成する際のドライエッティング工程における選択比を層間絶縁膜 19 よりも高くしている。これにより、フォトレジスト 20 をエッティングマスクとして層間絶縁膜 19 をドライエッティングしてヴィアホールを形成する際に、第 1 メタル配線 40 上ではエッティングレートが下がることになる。その結果、層間絶縁膜 19 をエッティングしてヴィアホールを形成する際に、形成するヴィアホールの深さの差を吸収して、コンタクトプラグ 14 上と第 1 メタル配線 40 上とにおいて同時に深さの異なるヴィアホールを形成することができる。40

#### 【0031】

そして、ドライエッティング後、フォトレジスト 20 を除去する。これにより、図 16 に示すようにコンタクトプラグ 14 に到達するヴィアホール 21 および第 1 メタル配線 40 に到達するヴィアホール 21 を同時に形成することができる。

#### 【0032】

つぎに、図 17 に示すように層間絶縁膜 19 の上面、ヴィアホール 21 およびヴィアホール 21 の内壁、すなわち内側面および底面に窒化チタン (TiN) などを成膜してバ50

リニアメタル膜 22 を形成する。そして、図 18 に示すようにバリアメタル膜 22 の上面、ヴィアホール 21 およびヴィアホール 21 の内壁に、タンゲステン (W) などの導電膜 23 を成膜する。この導電膜 23 は、ヴィアホール 21 およびヴィアホール 21 が確実に埋まるように、ヴィアホール 21 およびヴィアホール 21 の上径の半分以上の膜厚で成膜する。

### 【 0 0 3 3 】

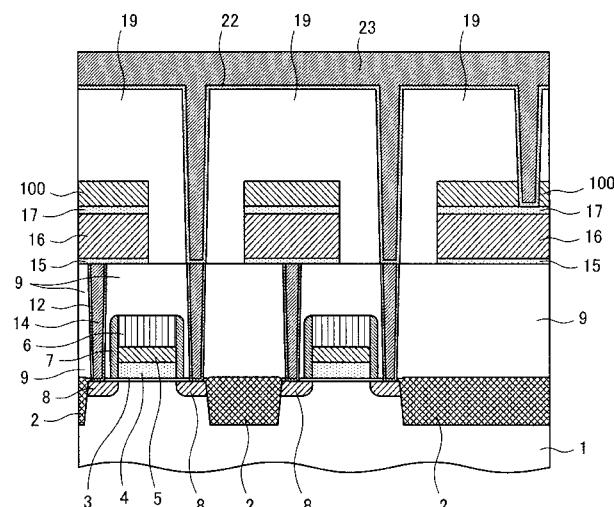

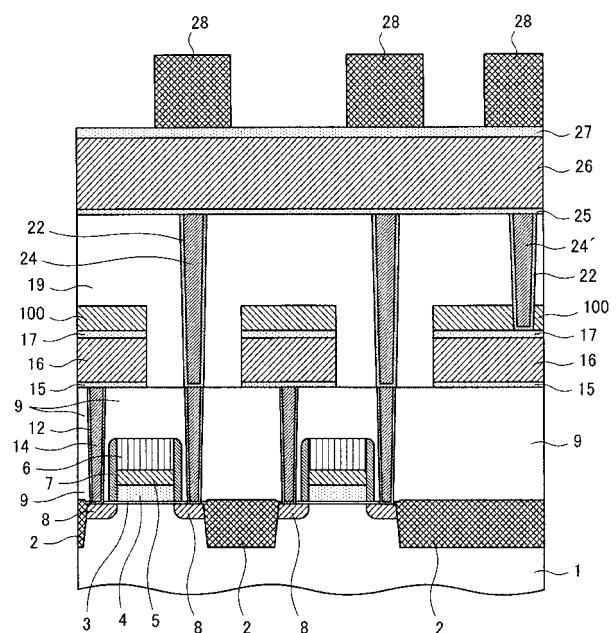

つぎに、図 19 に示すように、CMP またはエッチバックによりヴィアホール 21 内およびヴィアホール 21 内の導電膜 23 を残した状態で層間絶縁膜 19 の上面に成膜された導電膜 23 およびバリアメタル膜 22 を除去する。これにより、バリアメタル膜 22 を介してコンタクトプラグ 14 に接続するヴィアプラグ 24、およびバリアメタル膜 22 を介して第 1 メタル配線 40 に接続するヴィアプラグ 24 を形成することができる。10

### 【 0 0 3 4 】

つぎに、図 20 に示すように層間絶縁膜 19、バリアメタル 22、ヴィアプラグ 24 およびヴィアプラグ 24 の上面に窒化チタン (TiN) などを成膜してバリアメタル膜 25 を形成し、該バリアメタル膜 25 上にアルミ銅 (AlCu) などの導電膜 26 を形成し、さらにその上に窒化チタン (TiN) などを成膜してバリアメタル膜 27 を形成する。

### 【 0 0 3 5 】

ついで、図 21 に示すようにバリアメタル膜 27 上に写真製版によりフォトレジスト 28 を形成する。ここで、該フォトレジスト 28 は、第 2 メタル配線 50 の形成領域に対応する部分を覆い、それ以外の部分に開口部を有するパターンにて形成する。20

### 【 0 0 3 6 】

つぎに、図 22 に示すようにフォトレジスト 28 をエッティングマスクとしてドライエッティングして、第 2 メタル配線 50 の形成領域以外のバリアメタル膜 27、導電膜 26 およびバリアメタル膜 25 を除去する。そして、ドライエッティング後、フォトレジスト 28 を除去する。これにより、図 1 に示すような半導体装置を作製することができる。

### 【 0 0 3 7 】

上述したように、本実施の形態にかかる半導体装置の製造方法においては、ゲート構造 30 の不純物拡散領域 8 と第 2 メタル配線 50 とを接続する場合に、第 1 メタル配線 40 と第 2 メタル配線 50 とをつなぐヴィアプラグ 24 と同時に形成したヴィアプラグ 24 と、不純物拡散領域 8 に接続するコンタクトプラグ 14 と、を第 1 メタル配線 40 を介すことなく直接つなぐことが可能である。すなわち、ヴィアプラグ 24 とコンタクトプラグ 14 とを、第 1 メタル配線 40 を介すことなく直接電気的に接続することが可能である。これにより、第 2 メタル配線 50 と不純物拡散領域 8 とを容易に且つ確実に接続することができる。すなわち、第 1 メタル配線 40 のデザインルールに起因して第 2 メタル配線 50 と不純物拡散領域 8 とが接続できないという状況の発生を防止することができ、第 1 メタル配線 40 のデザインルールによらず確実に第 2 メタル配線 50 と不純物拡散領域 8 とを接続することが可能である。30

### 【 0 0 3 8 】

すなわち、この半導体装置の製造方法によれば、多層配線の狭ピッチ化が進んだ場合においても、第 1 メタル配線 40 のデザインルールによらず確実に第 2 メタル配線 50 と不純物拡散領域 8 とを容易に且つ確実に接続することが可能である。したがって、この半導体装置の製造方法によれば、メタル配線全体のレイアウトが第 1 層メタル配線の最小デザインルールにより律速されることが無く、多層配線の狭ピッチ化が進んだ場合においても、メタル配線全体のレイアウトをより微細なパターンに対応させることができ、配線レイアウトの縮小が可能である。40

### 【 0 0 3 9 】

したがって、本実施の形態にかかる半導体装置の製造方法によれば、多層配線の狭ピッチ化に対応可能な半導体装置を提供することができる。

### 【 0 0 4 0 】

また、この半導体装置の製造方法によれば、高価な製造装置やプロセスを使用する必要50

が無く、複雑なレイアウト設計も必要ないため、製造コストの増加を伴うことなく安価に半導体装置を製造することができる。そして、多層配線の狭ピッチ化が進んだ場合においても、メタル配線全体のレイアウトをより微細なパターンに対応させることができるので、レイアウト面積を拡大させることなく、小型化された半導体装置を製造することができる。

#### 【0041】

なお、上記においては、多層配線として第1メタル配線40と第2メタル配線50とを有し、第2メタル配線50と不純物拡散領域8とを電気的に接続する場合を例に説明したが、本発明はこれに限定されるものではなく、さらに多くの多層配線を有する場合に、メタル配線と不純物拡散領域8、またはメタル配線同士を電気的に接続する場合についても広く適用可能である。10

#### 【産業上の利用可能性】

#### 【0042】

以上のように、本発明にかかる半導体装置は、多層配線を有する半導体装置に有用であり、特に、多層配線が狭ピッチ化された半導体装置に適している。

#### 【図面の簡単な説明】

#### 【0043】

【図1】本発明の実施の形態にかかる半導体装置の構成を示す断面図である。

【図2】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

20

【図3】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図4】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図5】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図6】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図7】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図8】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図9】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図10】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図11】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図12】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

30

【図13】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図14】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図15】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図16】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図17】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図18】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図19】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図20】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図21】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

【図22】本発明の実施の形態にかかる半導体装置の製造方法を説明する断面図である。

#### 【符号の説明】

40

#### 【0044】

- 1 シリコン基板

- 2 素子分離酸化膜

- 3 ゲート酸化膜

- 4 ポリシリコンから成るゲート電極

- 5 タングステンシリサイド(WSi)から成るゲート電極

- 6 ハードマスク

- 7 サイドウォール

- 8 不純物拡散領域

- 9 層間絶縁膜

50

- 1 0 フォトレジスト

1 1 コンタクトホール

1 2 バリアメタル膜

1 3 導電膜

1 4 コンタクトプラグ

1 5 バリアメタル膜

1 6 導電膜

1 7 バリアメタル膜

1 8 フォトレジスト

1 9 層間絶縁膜

2 0 フォトレジスト

2 1 ヴィアホール

2 1 ヴィアホール

2 2 バリアメタル膜

2 3 導電膜

2 4 ヴィアプラグ

2 4 ヴィアプラグ

2 5 バリアメタル膜

2 6 導電膜

2 7 バリアメタル膜

2 8 フォトレジスト

3 0 ゲート構造

1 0 0 酸化膜

10

20

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図11】

【図13】

【図12】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】