(19) 日本国特許庁(JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-226225

(P2007-226225A)

(43) 公開日 平成19年9月6日(2007.9.6)

(51) Int.C1.

**G09F** 9/30 (2006.01)

**G02F** 1/1368 (2006.01)

F 1

GO9F 9/30 338

GO2F 1/1368

### テーマコード（参考）

2H092

5C094

審査請求 未請求 請求項の数 43 O.L. (全 20 頁)

(21) 出願番号 特願2007-36657 (P2007-36657)

(22) 出願日 平成19年2月16日 (2007. 2. 16)

(31) 優先権主張番号 10-2006-0016063

(32) 優先日 平成18年2月20日 (2006. 2. 20)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市八達区梅灘洞416

番地

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 鄭 営 培

大韓民国 京畿道 華城市 台安邑 餅店

里 858番地 シンチャンビバファアミリ

一2次 201棟 702号

Fターム(参考) 2H092 GA50 HA04 HA05 JA24 JB64

JB66 JB67 JB68 JB69 KA05

KA12 MA12 NA26 NA29 PA06

(54) 【発明の名称】アレイ基板

(57) 【要約】

【課題】非表示領域に位置するキャパシタが占める面積を最小化しながら高容量のキャパシタを具現することができ、別の追加工程なしに高容量を有するキャパシタを具現することができる構造を有するアレイ基板を提供する。

【解決手段】アレイ基板は、多数の画素部を含む表示領域及び該表示領域の外郭に位置する周辺領域を有する基板と、基板の表示領域に形成されゲート電極、ソース電極、及びドレイン電極を含む薄膜トランジスタと、基板の周辺領域に形成され下部に位置する第1サブキャパシタ及び上部に位置する第2サブキャパシタが電気的に並列接続される構造を有するキャパシタと、を備える。

【選択図】図 3

**【特許請求の範囲】****【請求項 1】**

多数の画素部を含む表示領域及び該表示領域の外郭に位置する周辺領域を有する基板と、

前記基板の表示領域に形成され、ゲート電極、ソース電極、及びドレイン電極を含む薄膜トランジスタと、

前記基板の周辺領域に形成されるキャパシタと、を備え、

前記キャパシタは、下部電極層、該下部電極層上に形成される中間電極層、及び前記下部電極層と該中間電極層との間に介在する第1誘電層を有する第1サブキャパシタ、及び該第1サブキャパシタの上部に配置され、前記中間電極層、前記中間電極層上に形成される上部電極層、及び前記中間電極層と該上部電極層との間に介在する第2誘電層を有する第2サブキャパシタを含むことを特徴とするアレイ基板。

10

**【請求項 2】**

前記第1サブキャパシタの下部電極層は、前記薄膜トランジスタのゲート電極を形成する層と同じ層から形成されることを特徴とする請求項1記載のアレイ基板。

**【請求項 3】**

前記中間電極層は、前記薄膜トランジスタのソース電極及びドレイン電極を形成する層と同じ層から形成されることを特徴とする請求項2記載のアレイ基板。

**【請求項 4】**

前記薄膜トランジスタのゲート電極上に形成されるゲート絶縁層を更に含み、前記第1サブキャパシタの第1誘電層は、該ゲート絶縁層を形成する層と同じ層から形成されることを特徴とする請求項3記載のアレイ基板。

20

**【請求項 5】**

前記薄膜トランジスタのドレイン電極と電気的に連結される透明電極を更に含み、前記第2サブキャパシタの上部電極層は、該透明電極を形成する層と同じ層から形成されることを特徴とする請求項3記載のアレイ基板。

**【請求項 6】**

前記薄膜トランジスタのソース電極及びドレイン電極上に形成されるパシベーション層を更に含み、前記第2サブキャパシタの第2誘電層は、該パシベーション層を形成する層と同じ層から形成されることを特徴とする請求項5記載のアレイ基板。

30

**【請求項 7】**

前記薄膜トランジスタ上に形成される反射電極を更に含み、前記第2サブキャパシタの上部電極層は、該反射電極を形成する層と同じ層から形成されることを特徴とする請求項3記載のアレイ基板。

**【請求項 8】**

前記第1サブキャパシタの下部電極層と前記第2サブキャパシタの上部電極層とは電気的に連結され、前記第1サブキャパシタ及び前記第2サブキャパシタが電気的に並列接続されることを特徴とする請求項1記載のアレイ基板。

**【請求項 9】**

多数の画素部を含む表示領域及び該表示領域の外郭に位置する周辺領域を有する基板と

40

前記基板の表示領域に形成され、ゲート電極、ソース電極、及びドレイン電極を含む薄膜トランジスタと、

前記基板の周辺領域に形成され、第1サブキャパシタ及び該第1サブキャパシタの上部に配置される第2サブキャパシタを含むキャパシタと、

前記キャパシタに電圧を印加するために、前記基板の周辺領域に形成されるパッド部と、を備えることを特徴とするアレイ基板。

**【請求項 10】**

前記第1サブキャパシタは、下部電極層、該下部電極層上に形成される中間電極層、及び前記下部電極層と該中間電極層との間に介在する第1誘電層を含むことを特徴とする請

50

求項 9 記載のアレイ基板。

【請求項 1 1】

前記第 2 サブキャパシタは、前記中間電極層、前記中間電極層上に形成される上部電極層、及び前記中間電極層と該上部電極層との間に介在する第 2 誘電層を含むことを特徴とする請求項 1 0 記載のアレイ基板。

【請求項 1 2】

前記パッド部は、前記第 1 サブキャパシタの下部電極層と前記第 2 サブキャパシタの上部電極層に電気的に連結される第 1 パッド及び前記中間電極層に電気的に連結される第 2 パッドを含むことを特徴とする請求項 1 1 記載のアレイ基板。

【請求項 1 3】

前記第 1 サブキャパシタの下部電極層と前記第 2 サブキャパシタの上部電極層とは、前記第 1 パッドで電気的に連結され、前記第 1 サブキャパシタ及び前記第 2 サブキャパシタが電気的に並列接続されることを特徴とする請求項 1 2 記載のアレイ基板。

【請求項 1 4】

前記第 1 サブキャパシタの下部電極層から延長された第 1 電圧印加配線を更に含み、前記下部電極層と前記第 1 パッドとは該第 1 電圧印加配線を通じて電気的に連結されることを特徴とする請求項 1 3 記載のアレイ基板。

【請求項 1 5】

前記第 1 パッドは、前記第 1 電圧印加配線から延長された第 1 パッド電極を含むことを特徴とする請求項 1 4 記載のアレイ基板。

【請求項 1 6】

前記第 1 サブキャパシタの下部電極層、前記第 1 電圧印加配線、及び前記第 1 パッド電極は、前記薄膜トランジスタのゲート電極を形成する層と同じ層から形成されることを特徴とする請求項 1 5 記載のアレイ基板。

【請求項 1 7】

前記第 2 サブキャパシタの上部電極層から延長された第 3 電圧印加配線を更に含むことを特徴とする請求項 1 5 記載のアレイ基板。

【請求項 1 8】

前記第 1 パッドは、前記第 3 電圧印加配線から延長された第 1 カバー電極を更に含むことを特徴とする請求項 1 7 記載のアレイ基板。

【請求項 1 9】

前記薄膜トランジスタのドレイン電極と電気的に連結される透明電極を更に含み、前記第 2 サブキャパシタの上部電極層、前記第 3 電圧印加配線、及び前記第 1 カバー電極は、該透明電極を形成する層と同じ層から形成されることを特徴とする請求項 1 8 記載のアレイ基板。

【請求項 2 0】

前記第 1 パッドは、前記第 1 パッド電極と前記第 1 カバー電極との間に介在する第 1 中間層を更に含むことを特徴とする請求項 1 8 記載のアレイ基板。

【請求項 2 1】

前記第 1 中間層は、前記第 1 サブキャパシタの第 1 誘電層を形成する層と同じ層から形成されることを特徴とする請求項 2 0 記載のアレイ基板。

【請求項 2 2】

前記ゲート電極上に形成されるゲート絶縁層を更に含み、前記第 1 サブキャパシタの第 1 誘電層及び前記第 1 中間層は、該ゲート絶縁層を形成する層と同じ層から形成されることを特徴とする請求項 2 1 記載のアレイ基板。

【請求項 2 3】

前記第 1 パッドは、前記第 1 中間層を貫通する第 1 コンタクトホールを更に含み、前記第 1 パッド電極と前記第 1 カバー電極とは、該第 1 コンタクトホールで互いに接触することを特徴とする請求項 2 0 記載のアレイ基板。

【請求項 2 4】

10

20

30

40

50

前記薄膜トランジスタ上に形成される反射電極を更に含み、前記第2サブキャパシタの上部電極層及び前記第3電圧印加配線は、該反射電極を形成する層と同じ層から形成されることを特徴とする請求項17記載のアレイ基板。

**【請求項25】**

前記中間電極層から延長された第2電圧印加配線を更に含み、前記中間電極層と前記第2パッドとは、該第2電圧印加配線を通じて電気的に連結されることを特徴とする請求項13記載のアレイ基板。

**【請求項26】**

前記第2パッドは、前記第2電圧印加配線から延長された第2パッド電極を含むことを特徴とする請求項25記載のアレイ基板。

10

**【請求項27】**

前記中間電極層、前記第2電圧印加配線、及び前記第2パッド電極は、前記薄膜トランジスタのソース電極及びドレイン電極を形成する層と同じ層から形成されることを特徴とする請求項26記載のアレイ基板。

**【請求項28】**

前記第2パッドは、前記第2パッド電極上に形成される第2カバー電極を更に含むことを特徴とする請求項27記載のアレイ基板。

**【請求項29】**

前記薄膜トランジスタのドレイン電極と電気的に連結される透明電極を更に含み、前記第2カバー電極は該透明電極を形成する層と同じ層から形成されることを特徴とする請求項28記載のアレイ基板。

20

**【請求項30】**

多数の画素部を含む表示領域及び該表示領域の外郭に位置する周辺領域を有する基板と、

前記基板の表示領域に形成され、ゲート電極、ソース電極、及びドレイン電極を含む薄膜トランジスタと、

前記基板の周辺領域に形成されるキャパシタと、を備え、

前記キャパシタは、下部電極層、該下部電極層上に形成される中間電極層、及び前記下部電極層と該中間電極層との間に介在する第1誘電層を有する第1サブキャパシタ、該第1サブキャパシタの上部に配置され、前記中間電極層、前記中間電極層上に形成される上部電極層、及び前記中間電極層と該上部電極層との間に介在する第2誘電層を有する第2サブキャパシタ、及び前記第1サブキャパシタの第1誘電層及び前記第2サブキャパシタの第2誘電層を貫通するコンタクト部を含み、

30

前記第1サブキャパシタの下部電極層と前記第2サブキャパシタの上部電極層とは前記コンタクト部で互いに接触し、前記第1サブキャパシタ及び前記第2サブキャパシタは電気的に並列接続されることを特徴とするアレイ基板。

**【請求項31】**

前記第1サブキャパシタの下部電極層は、前記薄膜トランジスタのゲート電極を形成する層と同じ層から形成されることを特徴とする請求項30記載のアレイ基板。

40

**【請求項32】**

前記中間電極層は、前記薄膜トランジスタのソース電極及びドレイン電極を形成する層と同じ層から形成されることを特徴とする請求項31記載のアレイ基板。

**【請求項33】**

前記薄膜トランジスタのドレイン電極と電気的に連結される透明電極を更に含み、前記第2サブキャパシタの上部電極層は該透明電極を形成する層と同じ層から形成されることを特徴とする請求項32記載のアレイ基板。

**【請求項34】**

前記薄膜トランジスタ上に形成される反射電極を更に含み、前記第2サブキャパシタの上部電極層は、該反射電極を形成する層と同じ層から形成されることを特徴とする請求項32記載のアレイ基板。

50

**【請求項 3 5】**

前記第1サブキャパシタの下部電極層と電気的に連結される第1パッド及び前記中間電極層と電気的に連結される第2パッドを更に含むことを特徴とする請求項30記載のアレイ基板。

**【請求項 3 6】**

前記下部電極層から延長された第1電圧印加配線を更に含み、前記下部電極層と前記第1パッドとは、該第1電圧印加配線を通じて電気的に連結されることを特徴とする請求項31記載のアレイ基板。

**【請求項 3 7】**

前記第1パッドは、前記第1電圧印加配線から延長された第1パッド電極を含むことを特徴とする請求項36記載のアレイ基板。 10

**【請求項 3 8】**

前記下部電極層、前記第1電圧印加配線、及び前記第1パッド電極は、前記薄膜トランジスタのゲート電極を形成する層と同じ層から形成されることを特徴とする請求項37記載のアレイ基板。

**【請求項 3 9】**

前記第1パッドは、前記第1パッド電極上に形成される第1カバー電極を更に含むことを特徴とする請求項38記載のアレイ基板。

**【請求項 4 0】**

前記アレイ基板は、前記中間電極層から延長された第2電圧印加配線を更に含み、前記中間電極層と前記第2パッドとは、該第2電圧印加配線を通じて電気的に連結されることを特徴とする請求項35記載のアレイ基板。 20

**【請求項 4 1】**

前記第2パッドは、前記第2電圧印加配線から延長された第2パッド電極を含むことを特徴とする請求項40記載のアレイ基板。

**【請求項 4 2】**

前記中間電極層、前記第2電圧印加配線、及び前記第2パッド電極は、前記薄膜トランジスタのソース電極及びドレイン電極を形成する層と同じ層から形成されることを特徴とする請求項41記載のアレイ基板。

**【請求項 4 3】**

前記第2パッドは、前記第2パッド電極上に形成される第2カバー電極を更に含むことを特徴とする請求項41記載のアレイ基板。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、アレイ基板に係り、より詳細には、高容量のキャパシタを具現することができる構造を有する液晶表示パネル用アレイ基板に関する。

**【背景技術】****【0002】**

代表的な平板表示装置である液晶表示装置（LCD）は、液晶の電気的及び光学的特性を利用して画像を表示する。液晶表示装置は他の表示装置に対して厚みが薄く、重量が軽く、低い消費電力及び低い駆動電圧で作動する長所を有しているため、産業全般にかけて多く使用されている。 40

**【0003】**

一般的に、液晶表示装置は、アレイ基板、アレイ基板に対向するカラーフィルタ基板、及び両基板の間に介在する液晶を含む液晶表示パネルを具備する。又、アレイ基板には、多数の薄膜トランジスタ、多数のゲート配線、及びドレイン配線が形成される。

**【0004】**

薄膜トランジスタを駆動するための駆動回路は、別のPCB（Printed Circuit Board）に実装され、TCP（Tape Carrier Package） 50

e)によってアレイ基板に連結でき、アレイ基板の外郭領域に直接形成されるようになることもできる。

【0005】

特に、駆動回路がアレイ基板上に形成される構造を有する液晶表示パネルのアレイ基板上には、例えば、電圧を安定させるか、電荷をポンピングする用途として使用されるキャパシタを形成することができる。

【0006】

キャパシタの容量を増加させるためには、キャパシタが占める面積を大きくする必要がある。しかし、液晶表示パネルの非表示領域(又は、周辺領域)の面積が小さい場合には、キャパシタの容量を増加させるために、キャパシタの面積を大きくすることに限界があるという問題点がある。10

【0007】

従って、キャパシタが占める面積を更に増加させることなく、高容量を具現することができる構造を有するキャパシタが必要である。

【発明の開示】

【発明が解決しようとする課題】

【0008】

そこで、本発明は、上記従来の問題点に鑑みてなされたものであって、本発明の目的は、キャパシタが占める面積を最小化しながら、高容量のキャパシタを具現することができる構造を有するアレイ基板を提供することにある。20

【0009】

また、本発明の他の目的は、別の追加工程なしに、高容量を具現することができる構造を有するアレイ基板を提供することにある。

【課題を解決するための手段】

【0010】

上記目的を達成するためになされた本発明の一特徴によるアレイ基板は、多数の画素部を含む表示領域及び該表示領域の外郭に位置する周辺領域を有する基板と、前記基板の表示領域に形成されゲート電極、ソース電極、及びドレイン電極を含む薄膜トランジスタと、前記基板の周辺領域に形成される第1サブキャパシタ及び第2サブキャパシタを含むキャパシタと、を備える。30

【0011】

前記第1サブキャパシタは、下部電極層、該下部電極層上に形成される中間電極層、及び前記下部電極層と該中間電極層との間に介在する第1誘電層を有する。

【0012】

前記第2サブキャパシタは、前記第1サブキャパシタの上部に配置され、前記中間電極層、前記中間電極層上に形成される上部電極層、及び前記中間電極層と該上部電極層との間に介在する第2誘電層を有する。

【0013】

前記第1サブキャパシタの下部電極層は、前記薄膜トランジスタのゲート電極を形成する層と同じ層から形成できる。前記中間電極層は、前記薄膜トランジスタのソース電極及びドレイン電極を形成する層と同じ層から形成できる。40

【0014】

前記アレイ基板は前記薄膜トランジスタのゲート電極上に形成されるゲート絶縁層を更に含み、前記第1サブキャパシタの第1誘電層は該ゲート絶縁層を形成する層と同じ層から形成できる。

【0015】

前記アレイ基板は前記薄膜トランジスタのドレイン電極と電気的に連結される透明電極を更に含み、前記第2サブキャパシタの上部電極層は該透明電極を形成する層と同じ層から形成できる。

【0016】

10

20

30

40

50

前記アレイ基板は前記薄膜トランジスタのソース電極及びドレイン電極上に形成されるパシベーション層を更に含み、前記第2サブキャパシタの第2誘電層は前記パシベーション層を形成する層と同じ層から形成できる。

## 【0017】

前記アレイ基板が前記薄膜トランジスタ上に形成される反射電極を更に含む場合、前記第2サブキャパシタの上部電極層は該反射電極を形成する層と同じ層から形成できる。

## 【0018】

前記第1サブキャパシタの下部電極層と前記第2サブキャパシタの上部電極層とは電気的に連結され、前記第1サブキャパシタ及び前記第2サブキャパシタが電気的に並列接続される。

## 【0019】

上記目的を達成するためになされた本発明の他の特徴によるアレイ基板は、多数の画素部を含む表示領域及び該表示領域の外郭に位置する周辺領域を有する基板と、前記基板の表示領域に形成されゲート電極、ソース電極、及びドレイン電極を含む薄膜トランジスタと、前記基板の周辺領域に形成され第1サブキャパシタ及び第2サブキャパシタを含むキャパシタと、前記キャパシタに電圧を印加するために前記基板の周辺領域に形成されるパッド部と、を備える。

## 【0020】

前記第1サブキャパシタは、下部電極層、該下部電極層上に形成される中間電極層、及び前記下部電極層と該中間電極層との間に介在する第1誘電層を含む。

## 【0021】

前記第2サブキャパシタは、前記第1サブキャパシタの上部に配置され、前記中間電極層、前記中間電極層上に形成される上部電極層、及び前記中間電極層と該上部電極層との間に介在する第2誘電層を含む。

## 【0022】

前記パッド部は、前記第1サブキャパシタの下部電極層と前記第2サブキャパシタの上部電極層に電気的に連結される第1パッド及び前記中間電極層に電気的に連結される第2パッドを含む。

## 【0023】

前記第1サブキャパシタの下部電極層と前記第2サブキャパシタの上部電極層とは、前記第1パッドで電気的に連結され、前記第1サブキャパシタ及び前記第2サブキャパシタが電気的に並列接続される。

## 【0024】

前記第1サブキャパシタの下部電極層から延長された第1電圧印加配線を更に含み、前記下部電極層と前記第1パッドとは該第1電圧印加配線を通じて電気的に連結できる。前記第1パッドは前記第1電圧印加配線から延長された第1パッド電極を含む。

## 【0025】

前記第1サブキャパシタの下部電極層、前記第1電圧印加配線、及び前記第1パッド電極は、前記薄膜トランジスタのゲート電極を形成する層と同じ層から形成できる。

## 【0026】

前記アレイ基板は前記第2サブキャパシタの上部電極層から延長された第3電圧印加配線を更に含むことができ、前記第1パッドは前記第3電圧印加配線から延長された第1カバー電極を更に含むこともできる。

## 【0027】

前記アレイ基板が前記薄膜トランジスタのドレイン電極と電気的に連結される透明電極を更に含む場合、前記第2サブキャパシタの上部電極層、前記第3電圧印加配線、及び前記第1カバー電極は、該透明電極を形成する層と同じ層から形成できる。

## 【0028】

前記第1パッドは前記第1パッド電極と前記第1カバー電極との間に介在する第1中間層を更に含み、前記第1中間層は前記第1サブキャパシタの第1誘電層を形成する層と同

10

20

30

40

50

じ層から形成できる。前記アレイ基板が前記ゲート電極上に形成されるゲート絶縁層を更に含む場合、前記第1サブキャパシタの第1誘電層及び前記第1中間層は該ゲート絶縁層を形成する層と同じ層から形成できる。

#### 【0029】

前記第1パッドは前記第1中間層を貫通する第1コンタクトホールを更に含み、前記第1パッド電極と前記第1カバー電極とは該第1コンタクトホールで互いに接触することができる。

#### 【0030】

前記アレイ基板が前記薄膜トランジスタ上に形成される反射電極を更に含む場合には、前記第2サブキャパシタの上部電極層及び前記第3電圧印加配線は該反射電極を形成する層と同じ層から形成できる。10

#### 【0031】

前記アレイ基板は前記中間電極層から延長された第2電圧印加配線を更に含み、前記中間電極層と前記第2パッドとは該第2電圧印加配線を通じて電気的に連結できる。前記第2パッドは前記第2電圧印加配線から延長された第2パッド電極を含むことができる。

#### 【0032】

前記中間電極層、前記第2電圧印加配線、及び前記第2パッド電極は、前記薄膜トランジスタのソース電極及びドレイン電極を形成する層と同じ層から形成できる。

#### 【0033】

前記第2パッドは前記第2パッド電極上に形成される第2カバー電極を更に含むことができる。前記アレイ基板が前記薄膜トランジスタのドレイン電極と電気的に連結される透明電極を更に含む場合、前記第2カバー電極は該透明電極を形成する層と同じ層から形成できる。20

#### 【0034】

上記目的を達成するためになされた本発明の更に他の特徴によるアレイ基板は、多数の画素部を含む表示領域及び該表示領域の外郭に位置する周辺領域を有する基板と、前記基板の表示領域に形成されゲート電極、ソース電極、及びドレイン電極を含む薄膜トランジスタと、前記基板の周辺領域に形成され第1サブキャパシタ、第2サブキャパシタ、及びコンタクト部を含むキャパシタと、を備える。

#### 【0035】

前記第1サブキャパシタは、下部電極層、該下部電極層上に形成される中間電極層、及び前記下部電極層と該中間電極層との間に介在する第1誘電層を有する。30

#### 【0036】

前記第2サブキャパシタは、前記第1サブキャパシタの上部に配置され、前記中間電極層、前記中間電極層上に形成される上部電極層、及び前記中間電極層と該上部電極層との間に介在する第2誘電層を有する。

#### 【0037】

前記コンタクト部は、前記第1サブキャパシタの第1誘電層及び前記第2サブキャパシタの第2誘電層を貫通する。ここで、前記第1サブキャパシタの下部電極層と前記第2サブキャパシタの上部電極層とは前記コンタクト部で互いに接触し、前記第1サブキャパシタ及び前記第2サブキャパシタは電気的に並列接続される。40

#### 【発明の効果】

#### 【0038】

このように、本発明によるアレイ基板は、下部に位置する第1サブキャパシタ及び上部に位置する第2サブキャパシタが電気的に並列接続される構造を有するキャパシタを含むので、面積を増加させることなく、キャパシタの容量を増加させることができる。

#### 【0039】

又、薄膜トランジスタのゲート電極、ソース電極、及びドレイン電極が形成される工程や透明電極又は反射電極が塗布される工程が進行される際、第1及び第2サブキャパシタのそれぞれの電極が形成できるので、別の追加工程なしに、高容量を有するキャパシタを50

具現することができる。

**【発明を実施するための最良の形態】**

**【0040】**

以下、本発明のアレイ基板を実施するための最良の形態の具体例を、液晶表示パネルに適用した実施例により添付図面を参照して詳細に説明する。

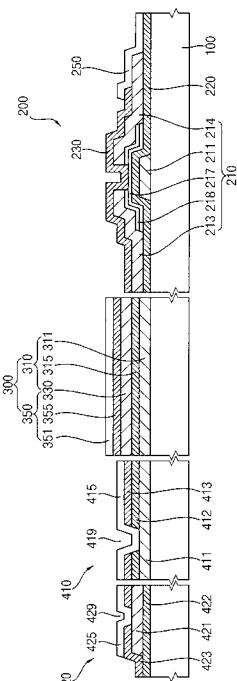

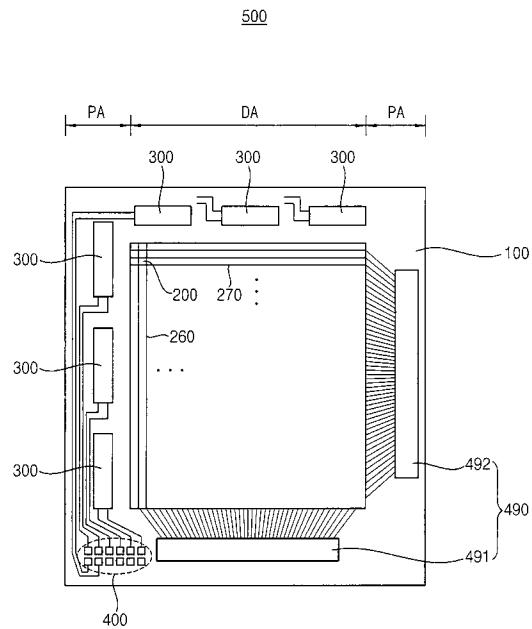

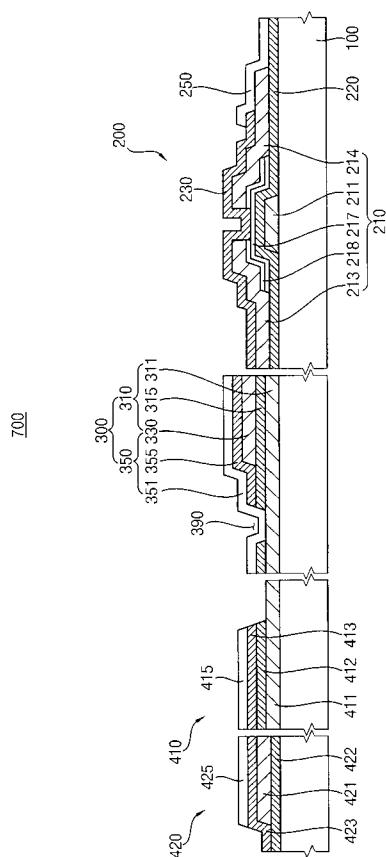

**【0041】**

図1は、本発明の第1実施例によるアレイ基板を概略的に示す平面図であり、図2は、図1に示したキャパシタ及び画素部を拡大して示す平面図であり、図3は、図2に示したI-I'に沿って切断した断面図である。

**【0042】**

図1乃至図3を参照すると、本発明の一実施例によるアレイ基板500は、表示領域DA及び周辺領域PAを有する基板100、基板100の表示領域DAに形成される薄膜トランジスタ210及び基板100の周辺領域PAに形成されるキャパシタ300を含む。

**【0043】**

基板100の表示領域DAは、多数のゲートライン270及び多数のデータライン260によって定義される多数の画素部200を含む。画素部200には、薄膜トランジスタ210が画素部200毎に形成される。

**【0044】**

薄膜トランジスタ210は、ゲートライン270に電気的に連結されるゲート電極211、データライン260に電気的に連結されるソース電極213、及びドレイン電極214を含む。薄膜トランジスタ210は、ソース電極213及びドレイン電極214とゲート電極211との間に形成されるアモルファスシリコン層217、及びn<sup>+</sup>アモルファスシリコン層218を更に含むこともできる。

**【0045】**

薄膜トランジスタ210のゲート電極211上にはゲート絶縁層220が形成される。ゲート絶縁層220は、例えば、窒化シリコン(SiNx)又は酸化シリコン(SiOx)からなる。又、薄膜トランジスタ210のソース電極213及びドレイン電極214上にはパシベーション層230を形成することもできる。パシベーション層230は、例えば、窒化シリコン(SiNx)、酸化シリコン(SiOx)、又は有機絶縁物質からなる。

**【0046】**

表示領域DAの画素部200には、薄膜トランジスタ210のドレイン電極214と電気的に連結される透明電極250が塗布される。透明電極250は、例えば、ITO、IZO、又はZOのような透明な導電性物質からなる。

**【0047】**

基板100の周辺領域PAには、薄膜トランジスタ210を駆動する駆動回路部490を形成することができる。本実施例では、駆動回路部490がゲートライン270と電気的に連結されるゲート駆動部492及びデータライン260と電気的に連結されるデータ駆動部491に分けられている。しかし、他の実施例として、ゲート駆動部とデータ駆動部を1つの駆動回路部に形成することもできる。

**【0048】**

基板100の周辺領域PAには、少なくとも1つ以上のキャパシタ300が形成される。キャパシタ300は、例えば、駆動回路部490又は薄膜トランジスタ210に印加される電圧を安定化する回路に使用でき、表示パネルに使用される電圧を昇圧するか、反転させるチャージポンプ回路のフライングキャパシタ(flying capacitor)として使用できる。

**【0049】**

キャパシタ300は、下部に位置する第1サブキャパシタ310及び第2サブキャパシタ310の上部に位置する第2サブキャパシタ350を含む。

**【0050】**

10

20

30

40

50

第1サブキャパシタ310は、下部電極層311、下部電極層311上に形成される中間電極層330、及び下部電極層311と中間電極層330との間に介在する第1誘電層315を含む。

【0051】

又、第2サブキャパシタ350は、中間電極層330、中間電極層330上に形成される上部電極層351及び中間電極層330と上部電極層351との間に介在する第2誘電層355を含む。

【0052】

下部電極層311、中間電極層330、及び上部電極層351は、例えば、銅又はアルミニウムのような金属で形成でき、ITO又はIZOのような導電性酸化物で形成されるようにすることもできる。

【0053】

一方、追加工程を減らすために、薄膜トランジスタ210のゲート電極211、薄膜トランジスタ210のソース電極213及びドレイン電極214、又は透明電極250を形成する工程が進行される時に、下部電極層311、中間電極層330、及び上部電極層351を形成する工程を同時に進行することができる。

【0054】

例えば、第1サブキャパシタ310の下部電極層311は、薄膜トランジスタ210のゲート電極211を形成する層と同じ層から形成でき、中間電極層330は、薄膜トランジスタ200のソース電極213及びドレイン電極214を形成する層と同じ層から形成できる。

【0055】

又、第2サブキャパシタ350の上部電極層351は、透明電極250を形成する層と同じ層から形成できる。仮に、アレイ基板500が反射電極(図示せず)を更に含むと、第2サブキャパシタ350の上部電極層351は反射電極(図示せず)を形成する層と同じ層から形成されるようにすることもできる。

【0056】

同様に、別の追加工程なしに、第1誘電層315及び第2誘電層355を形成するため、第1サブキャパシタ310の第1誘電層315はゲート絶縁層220を形成する層と同じ層から形成でき、第2サブキャパシタ350の第2誘電層355はパシベーション層230を形成する層と同じ層から形成されるようにすることもできる。

【0057】

アレイ基板500は、キャパシタ300に電圧を印加するために、基板100の周辺領域PAに形成されるパッド部400を更に含むことができる。

【0058】

本実施例において、パッド部400は、第1サブキャパシタ310の下部電極層311と第2サブキャパシタ350の上部電極層351に電気的に連結される第1パッド410及び中間電極層330に電気的に連結される第2パッド420を含む。

【0059】

第1パッド410は、第1サブキャパシタ310の下部電極層311から延長された第1電圧印加配線460を通じて下部電極層311と電気的に連結できる。しかし、第1パッド410が下部電極層311と電気的に連結される方法はこれに限定されない。即ち、連結配線が必ず第1サブキャパシタ310の下部電極層311から延長される必要はなく、第1パッド410と下部電極層311を電気的に連結する別の配線を形成することもできる。

【0060】

第1パッド410と第1サブキャパシタ310の下部電極層311が下部電極層311から延長された第1電圧印加配線460を通じて電気的に連結される場合には、第1パッド410は、第1電圧印加配線460から延長される第1パッド電極411を含むこともできる。これによって、第1サブキャパシタ310の下部電極層311、第1電圧印加配

10

20

30

40

50

線 4 6 0、及び第 1 パッド電極 4 1 1 を一体に形成することができる。

【 0 0 6 1 】

下部電極層 3 1 1、第 1 電圧印加配線 4 6 0、及び第 1 パッド電極 4 1 1 は、例えば、薄膜トランジスタ 2 1 0 のゲート電極 2 1 1 を形成する層と同じ層から形成できる。

【 0 0 6 2 】

第 1 パッド 4 1 0 は、第 2 サブキャパシタ 3 5 0 の上部電極層 3 5 1 から延長された第 3 電圧印加配線 4 8 0 を通じて上部電極層 3 5 1 と電気的に連結されるようにすることもできる。

【 0 0 6 3 】

第 2 サブキャパシタ 3 5 0 の上部電極層 3 5 1、上部電極層 3 5 1 から延長された第 3 電圧印加配線 4 8 0 は、透明電極 2 5 0 を形成する層と同じ層から形成できる。 10

【 0 0 6 4 】

第 1 パッド 4 1 0 は、第 1 パッド電極 4 1 1 上に形成される第 1 カバー電極 4 1 5 を更に含むことができる。第 1 カバー電極 4 1 5 は、第 1 パッド電極 4 1 1 が腐食することを防止するか、第 1 パッド 4 1 0 の抵抗値を低くする役割を果たす。

【 0 0 6 5 】

第 1 カバー電極 4 1 5 は、例えば、ITO、IZO のように耐蝕性と導電性を同時に有する物質からなることが好ましい。

【 0 0 6 6 】

第 2 サブキャパシタ 3 5 0 の上部電極層 3 5 1、上部電極層 3 5 1 から延長された第 3 電圧印加配線 4 8 0 が透明電極 2 5 0 を形成する層と同じ層から形成される場合には、第 1 カバー電極 4 1 5 が第 3 電圧印加配線 4 8 0 から延長されて形成できる。即ち、上部電極層 3 5 1、第 3 電圧印加配線 4 8 0、及び第 1 カバー電極 4 1 5 を一体に形成することができる。 20

【 0 0 6 7 】

第 1 パッド 4 1 0 は、第 1 パッド電極 4 1 1 と第 1 カバー電極 4 1 5 との間に形成される第 1 中間層 4 1 2 を更に含むことができる。第 1 中間層 4 1 2 は、第 1 サブキャパシタ 3 1 0 の第 1 誘電層 3 1 5 を形成する層と同じ層から形成できる。第 1 サブキャパシタ 3 1 0 の第 1 誘電層 3 1 5 及び第 1 中間層 4 1 2 は、ゲート絶縁層 2 2 0 を形成する層と同じ層から形成できる。又、第 1 中間層 4 1 2 と第 1 カバー電極 4 1 5 との間には第 3 中間層 4 1 3 を更に形成することもできる。 30

【 0 0 6 8 】

本実施例では、第 1 サブキャパシタ 3 1 0 の下部電極層 3 1 1 に電気的に連結された第 1 パッド 4 1 0 の第 1 パッド電極 4 1 1 と第 2 サブキャパシタ 3 5 0 の上部電極層 3 5 1 に電気的に連結された第 1 パッド 4 1 0 の第 1 カバー電極 4 1 5 が第 1 中間層 4 1 2 を貫通する第 1 コンタクトホール 4 1 9 で互いに接触して、下部電極層 3 1 1 と上部電極層 3 5 1 が互いに電気的に連結される。

【 0 0 6 9 】

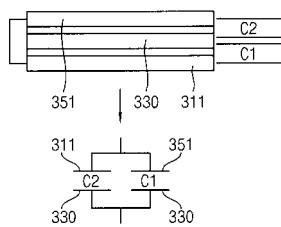

図 4 は、図 2 に示した第 1 及び第 2 サブキャパシタが電気的に並列接続された場合の、キャパシタの電気容量の増加を説明するための概念図である。 40

【 0 0 7 0 】

図 4 に示すように、下部電極層 3 1 1 と上部電極層 3 5 1 が互いに電気的に連結されると、第 1 サブキャパシタ 3 1 0 と第 2 サブキャパシタ 3 5 0 が電気的に並列接続される。

【 0 0 7 1 】

2 つのサブキャパシタが並列に接続される場合、全体キャパシタの容量はそれぞれのサブキャパシタの容量の和と同じである。即ち、キャパシタ 3 0 0 の容量は、第 1 サブキャパシタ 3 1 0 の容量 C 1 と第 2 サブキャパシタ 3 5 0 の容量 C 2 の和と同じである。従って、本発明によると、第 1 サブキャパシタ 3 1 0 上に第 2 サブキャパシタ 3 5 0 が位置して、第 1 及び第 2 サブキャパシタ 3 1 0、3 5 0 が電気的に並列接続される構造を通じて、面積を増加させることなく、キャパシタ 3 0 0 の容量を増加させることができる。 50

## 【0072】

図2及び図3に示すように、第2パッド420は、中間電極層330から延長された第2電圧印加配線470を通じて中間電極層330と電気的に連結できる。しかし、第2パッド420が中間電極層330と電気的に連結される方法はこれに限定されない。即ち、連結配線が必ず中間電極層330から延長される必要はなく、第2パッド420と中間電極層330を電気的に連結する別の配線を形成することもできる。

## 【0073】

第2パッド420と中間電極層330が中間電極層330から延長された第2電圧印加配線470を通じて電気的に連結される場合には、第2パッド420は、第2電圧印加配線470から延長された第2パッド電極421を含むこともできる。これによって、中間電極層330、第2電圧印加配線470、及び第2パッド電極421を一体に形成することができる。

## 【0074】

中間電極層330、第2電圧印加配線470、及び第2パッド電極421は、例えば、薄膜トランジスタ210のソース電極213及びドレイン電極214を形成する層と同じ層から形成できる。

## 【0075】

第2パッド420は、第2パッド電極421上に形成される第2カバー電極425を更に含むことができる。第2カバー電極425は、第2パッド電極421が腐食することを防止するか、第2パッド420の抵抗値を低くする役割を果たす。

## 【0076】

第2カバー電極425は、第1カバー電極415と同様に、例えば、ITO、IZOのように耐蝕性と導電性を同時に有する物質からなることが好ましい。

## 【0077】

第2パッド420は、第2パッド電極421と第2カバー電極425との間に形成される第2中間層423を更に含むことができる。第2中間層423は、第2サブキャパシタ350の第2誘電層355を形成する層と同じ層から形成できる。第2サブキャパシタ350の第2誘電層355及び第2中間層423は、パシベーション層230を形成する層と同じ層から形成できる。

## 【0078】

第2中間層423と基板100との間には、第4中間層422を更に形成することもできる。又、第2カバー電極425は、第2パッド420内に形成された第2コンタクトホール429で第2パッド電極421と接触することもできる。

## 【0079】

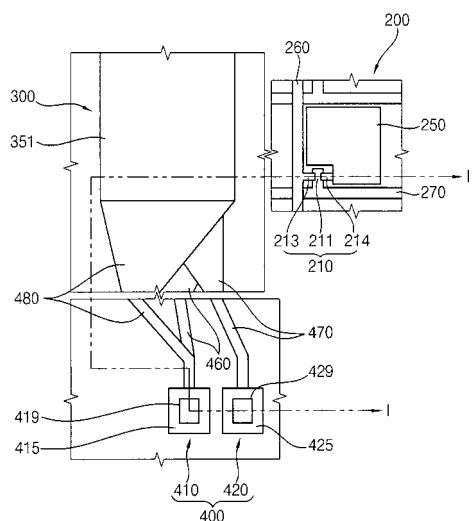

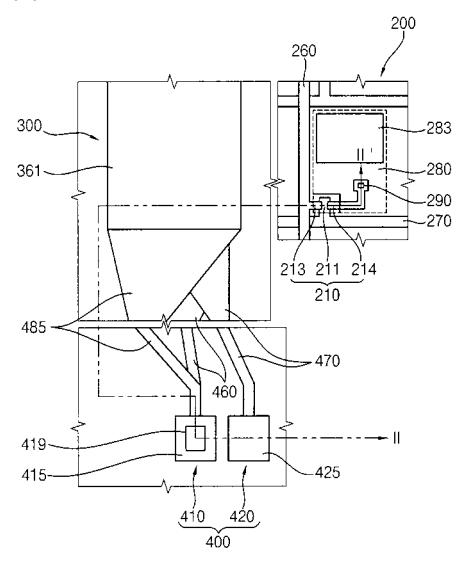

図5は、本発明の第2実施例によるアレイ基板のキャパシタ及び画素部を拡大して示す平面図であり、図6は、図5に示したII-II'に沿って切断した断面図である。

## 【0080】

図5及び図6を参照すると、本発明の第2実施例によるアレイ基板600は、表示領域と周辺領域とを有する基板100、基板100の表示領域に形成される薄膜トランジスタ210及び基板100の周辺領域に形成されるキャパシタ300を含む。

## 【0081】

図5及び図6に示したキャパシタ300がアレイ基板600上に配置される位置は、図1のアレイ基板500に示したキャパシタ300が配置される位置と実質的に同じなので、キャパシタ300が形成される位置と関連する重複説明は省略する。又、図1乃至図3に示したアレイ基板500の構成要素と類似であるか、実質的に同じ構成要素には同じ参考符号を付与し、重複する詳細な説明は省略する。

## 【0082】

図2に示した画素部200が透過型方式の液晶表示パネルに適用されるのに対し、図5に示した画素部200は反射・透過型方式の液晶表示パネルに適用される。

## 【0083】

10

20

30

40

50

画素部 200 は、下部から提供される光を透過させる透過窓 283 及び上部から提供される光を反射する反射領域 280 を含む。図 6 に示した画素部 200 は、反射領域 280 の断面の一部を示す。

#### 【0084】

画素部 200 の反射領域 280 には、薄膜トランジスタ 210 が形成される。薄膜トランジスタ 210 は、ゲート電極 211、ソース電極 213、及びドレイン電極 214 を含む。薄膜トランジスタ 210 は、ソース電極 213 及びドレイン電極 214 とゲート電極 211との間に形成されるアモルファスシリコン層 217 及び  $n^+$  アモルファスシリコン層 218 を更に含むこともできる。

#### 【0085】

薄膜トランジスタ 210 のゲート電極 211 上にはゲート絶縁層 220 が形成され、薄膜トランジスタ 210 のソース電極 213 及びドレイン電極 214 上にはパシベーション層 230 を形成することもできる。

#### 【0086】

薄膜トランジスタ 210 の上部には、有機絶縁層 235 が形成される。有機絶縁層 235 の上部面は、反射効率を向上させるために、ウェーブ形状にパターニングされるようになることができる。

#### 【0087】

有機絶縁層 235 の上面には、透明で導電性である物質からなる透明電極 250 が塗布される。透明電極 250 上には、上部から提供される光を反射する反射電極 255 が塗布される。反射電極 255 は、例えば、モリブデン (Mo) - アルミニウム (Al) 合金、モリブデン (Mo) - タングステン (W) 合金、又はアルミニウム (Al) - ネオジウム (Nd) 合金等からなる。一方、他の実施例としては、有機絶縁層 235 の上面に透明電極 250 を塗布せず、反射電極 255 を直接塗布することもできる。

#### 【0088】

透明電極 250 及び反射電極 255 は、有機絶縁層 235 を貫通する第 3 コンタクトホール 290 で薄膜トランジスタ 210 のドレイン電極 214 と接触して電気的に連結される。

#### 【0089】

キャパシタ 300 は、下部に位置する第 1 サブキャパシタ 310 及び第 1 サブキャパシタ 310 の上部に位置する第 2 サブキャパシタ 360 を含む。

#### 【0090】

第 1 サブキャパシタ 310 は、下部電極層 311、下部電極層 311 上に形成される中間電極層 330、及び下部電極層 311 と中間電極層 330 との間に介在する第 1 誘電層 315 を含む。

#### 【0091】

又、第 2 サブキャパシタ 360 は、中間電極層 330、中間電極層 330 上に形成される上部電極層 361 及び中間電極層 330 と上部電極層 361 との間に介在する第 2 誘電層 365 を含む。

#### 【0092】

一方、追加工程を減らすために、薄膜トランジスタ 200 のゲート電極 211、薄膜トランジスタ 200 のソース電極 213 及びドレイン電極 214、透明電極 250 又は反射電極 255 を形成する工程が進行される時に、下部電極層 311、中間電極層 330、及び上部電極層 361 を形成する工程を同時に進行することができる。

#### 【0093】

例えば、第 1 サブキャパシタ 310 の下部電極層 311 は、薄膜トランジスタ 210 のゲート電極 211 を形成する層と同じ層から形成でき、中間電極層 330 は、薄膜トランジスタ 210 のソース電極 213 及びドレイン電極 214 を形成する層と同じ層から形成できる。

#### 【0094】

10

20

30

40

50

本実施例では、第2サブキャパシタ360の上部電極層361が反射電極255を形成する層と同じ層から形成される。

【0095】

アレイ基板600は、第1サブキャパシタ310の下部電極層311と第2サブキャパシタ360の上部電極層361に電気的に連結される第1パッド410及び中間電極層30に電気的に連結される第2パッド420を含む。

【0096】

第1パッド410は、第1サブキャパシタ310の下部電極層311から延長された第1電圧印加配線460を通じて下部電極層311と電気的に連結できる。又、第1パッド410は、第1電圧印加配線460から延長された第1パッド電極411を含むこともできる。その際、下部電極層311、第1電圧印加配線460、及び第1パッド電極411を、例えば、薄膜トランジスタ210のゲート電極211を形成する層と同じ層から形成されるようにすることができる。

【0097】

第1パッド410は、第1パッド電極411上に形成される第1カバー電極415を更に含むことができる。第1カバー電極415は、例えば、ITO、IZOのように耐蝕性と導電性を同時に有する物質からなることが好ましい。

【0098】

第1パッド410の第1カバー電極415は、第2サブキャパシタ360の上部電極層361から延長された第4電圧印加配線485を通じて上部電極層361と電気的に連結されるようにすることもできる。

【0099】

例えば、第2サブキャパシタ360の上部電極層361が反射電極255を形成する層と同じ層から形成される場合には、第4電圧印加配線485も反射電極255を形成する層と同じ層から形成される。

【0100】

本実施例では、第1サブキャパシタ310の下部電極層311と第2サブキャパシタ360の上部電極層361が第1パッド410に形成された第1コンタクトホール419で互いに接触して電気的に連結される。

【0101】

これによって、第1サブキャパシタ310と第2サブキャパシタ360が電気的に並列接続されるので、図4で説明したように、面積を増加させることなく、キャパシタ300の容量を増加させることができる。

【0102】

上述した事項を除くと、第1パッド410の構造は、図4に示した第1パッド410の構造と類似なので、重複説明は省略する。

【0103】

第2パッド420は、第2コンタクトホール429が形成されないことを除くと、図3に示した第2パッド420と実質的に同じなので、重複する詳細な説明は省略する。但し、第2パッド420は、必要に応じて図3に示すように、第2コンタクトホール429を含むこともできる。

【0104】

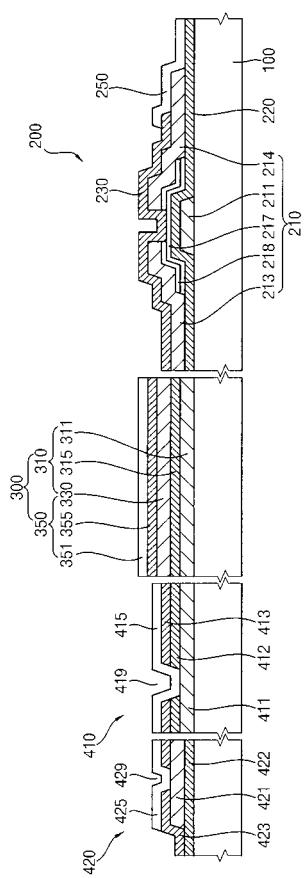

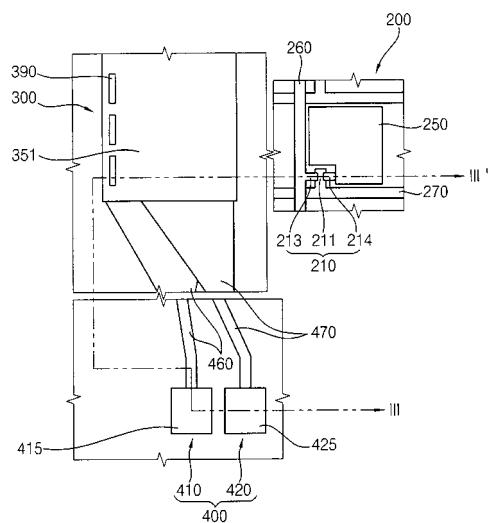

図7は、本発明の第3実施例によるアレイ基板のキャパシタ及び画素部を拡大して示す平面図であり、図8は、図7に示したI—I—I'—I'I'に沿って切断した断面図である。

【0105】

図7及び図8を参照すると、本発明の第3実施例によるアレイ基板700は、表示領域と周辺領域を有する基板100、基板100の表示領域に形成される薄膜トランジスタ210及び基板100の周辺領域に形成されるキャパシタ300を含む。

【0106】

図7及び図8に示したキャパシタ300がアレイ基板700上に配置される位置は、図

10

20

30

40

50

1のアレイ基板500に示したキャパシタ300が配置される位置と実質的に同じなので、キャパシタが形成される位置と関連する重複説明は省略する。又、図1乃至図3に示したアレイ基板500の構成要素と類似であるか、実質的に同じ構成要素には同じ参照番号を付与し、反復される詳細な説明は省略する。

#### 【0107】

キャパシタ300は、下部に位置する第1サブキャパシタ310、第1サブキャパシタ310の上部に位置する第2サブキャパシタ350を含む。

#### 【0108】

第1サブキャパシタ310は、下部電極層311、下部電極層311上に形成される中間電極層330、及び下部電極層311と中間電極層330との間に介在する第1誘電層315を含む。

10

#### 【0109】

又、第2サブキャパシタ350は、中間電極層330、中間電極層330上に形成される上部電極層351、及び中間電極層330と上部電極層351との間に介在する第2誘電層355を含む。

#### 【0110】

キャパシタ300は、第1サブキャパシタ310の第1誘電層315及び第2サブキャパシタ350の第2誘電層355を貫通する少なくとも1つ以上のコンタクト部390を更に含む。

#### 【0111】

本実施例では、コンタクト部390は、キャパシタ300の外郭に形成されているが、本発明はこれに限定されるものではない。即ち、コンタクト部390は、キャパシタの内部に形成されるようにすることもできる。

#### 【0112】

第1サブキャパシタ310の下部電極層311と第2サブキャパシタ350の上部電極層351は、コンタクト部390で互いに接触する。これによって、第1サブキャパシタ310と第2サブキャパシタ350は電気的に並列接続される。第1サブキャパシタ310と第2サブキャパシタ350が電気的に並列接続されるので、図4で説明したように、面積を増加させることなく、キャパシタ300の容量を増加させることができる。

#### 【0113】

一方、追加工程を減らすために、薄膜トランジスタ210のゲート電極211、薄膜トランジスタ210のソース電極213及びドレイン電極214、又は透明電極250を形成する工程が進行される時に、下部電極層311、中間電極層330、及び上部電極層351を形成する工程を同時に進行することができる。

30

#### 【0114】

例えば、第1サブキャパシタ310の下部電極層311は、薄膜トランジスタ210のゲート電極211を形成する層と同じ層から形成でき、中間電極層330は、薄膜トランジスタ210のソース電極213及びドレイン電極214を形成する層と同じ層から形成できる。

#### 【0115】

又、第2サブキャパシタ350の上部電極層351は、透明電極250を形成する層と同じ層から形成できる。仮に、アレイ基板700が反射電極(図示せず)を更に含むと、第2サブキャパシタ350の上部電極層351は、反射電極(図示せず)を形成する層と同じ層から形成されるようにすることもできる。

40

#### 【0116】

アレイ基板700は、第1サブキャパシタ310の下部電極層311と電気的に連結される第1パッド410及び中間電極層330に電気的に連結される第2パッド420を含む。

#### 【0117】

第1パッド410は、第1サブキャパシタ310の下部電極層311から延長された第

50

1電圧印加配線460を通じて下部電極層311と電気的に連結できる。又、第1パッド410は、第1電圧印加配線460から延長された第1パッド電極411を含むことができる。その際、下部電極層311、第1電圧印加配線460、及び第1パッド電極411は、例えば、薄膜トランジスタ210のゲート電極211を形成する層と同じ層から形成されるようにすることができる。

#### 【0118】

第2パッド410は、第2サブキャパシタ350の上部電極層351から延長された第2電圧印加配線470を通じて上部電極層351と電気的に連結できる。又、第2パッド410は、第2電圧印加配線470から延長された第2パッド電極421を含むことができる。その際、上部電極層351、第2電圧印加配線470、及び第2パッド電極421は、例えば、薄膜トランジスタ210のソース及びドレイン電極213、214を形成する層と同じ層から形成されるようにすることができる。10

#### 【0119】

第1パッド410は、第1パッド電極411上に形成される第1カバー電極415を更に含むことができ、第2パッド420は、第2パッド電極421上に形成される第2カバー電極425を更に含むことができる。

#### 【0120】

第1及び第2カバー電極415、425は、第1及び第2パッド電極411、421が腐食されることを防止するか、第1及び第2パッド410、420の抵抗値を低くする役割を果たす。20

#### 【0121】

第1及び第2カバー電極415、425は、例えば、ITO、IZOのように耐蝕性と導電性を同時に有する物質からなることが好ましい。

#### 【0122】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離ることなく、本発明を修正または変更できる。

#### 【図面の簡単な説明】

#### 【0123】

【図1】本発明の第1実施例によるアレイ基板を概略的に示す平面図である。

【図2】図1に示したキャパシタ及び画素部を拡大して示す平面図である。30

【図3】図2に示したI-I'に沿って切断した断面図である。

【図4】図2に示した第1及び第2サブキャパシタが電気的に並列接続された場合の、キャパシタの電気容量の増加を説明するための概念図である。

【図5】本発明の第2実施例によるアレイ基板のキャパシタ及び画素部を拡大して示す平面図である。

【図6】図5に示したI'I'-II'に沿って切断した断面図である。

【図7】本発明の第3実施例によるアレイ基板のキャパシタ及び画素部を拡大して示す平面図である。

【図8】図7に示したIII'-II'I'に沿って切断した断面図である。40

#### 【符号の説明】

#### 【0124】

100 基板

200 画素部

210 薄膜トランジスタ

211 ゲート電極

213 ソース電極

214 ドレイン電極

217 アモルファスシリコン層

218 n<sup>+</sup>アモルファスシリコン層

|                   |             |    |

|-------------------|-------------|----|

| 2 2 0             | ゲート絶縁層      |    |

| 2 3 0             | パシベーション層    |    |

| 2 3 5             | 有機絶縁層       |    |

| 2 5 0             | 透明電極        |    |

| 2 5 5             | 反射電極        |    |

| 2 6 0             | データライン      |    |

| 2 7 0             | ゲートライン      |    |

| 2 8 0             | 反射領域        |    |

| 2 8 3             | 透過窓         |    |

| 2 9 0             | 第3コントラクトホール | 10 |

| 3 0 0             | キャパシタ       |    |

| 3 1 0             | 第1サブキャパシタ   |    |

| 3 1 1             | 下部電極層       |    |

| 3 1 5             | 第1誘電層       |    |

| 3 3 0             | 中間電極層       |    |

| 3 5 0、3 6 0       | 第2サブキャパシタ   |    |

| 3 5 1、3 6 1       | 上部電極層       |    |

| 3 5 5、3 6 5       | 第2誘電層       |    |

| 3 9 0             | コントラクト部     |    |

| 4 0 0             | パッド部        | 20 |

| 4 1 0             | 第1パッド       |    |

| 4 1 1             | 第1パッド電極     |    |

| 4 1 2             | 第1中間層       |    |

| 4 1 3             | 第3中間層       |    |

| 4 1 5             | 第1カバー電極     |    |

| 4 1 9             | 第1コントラクトホール |    |

| 4 2 0             | 第2パッド       |    |

| 4 2 1             | 第2パッド電極     |    |

| 4 2 2             | 第4中間層       |    |

| 4 2 3             | 第2中間層       | 30 |

| 4 2 5             | 第2カバー電極     |    |

| 4 2 9             | 第2コントラクトホール |    |

| 4 6 0             | 第1電圧印加配線    |    |

| 4 7 0             | 第2電圧印加配線    |    |

| 4 8 0             | 第3電圧印加配線    |    |

| 4 8 5             | 第4電圧印加配線    |    |

| 4 9 0             | 駆動回路部       |    |

| 4 9 1             | データ駆動部      |    |

| 4 9 2             | ゲート駆動部      |    |

| 5 0 0、6 0 0、7 0 0 | アレイ基板       | 40 |

| D A               | 表示領域        |    |

| P A               | 周辺領域        |    |

【 図 1 】

【 図 2 】

【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

F ターム(参考) 5C094 AA15 AA43 BA03 BA43 CA19 DA13 DA15 EA10 FB16 FB19

GA10