(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5961618号

(P5961618)

(45) 発行日 平成28年8月2日(2016.8.2)

(24) 登録日 平成28年7月1日(2016.7.1)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| H01L 21/822  | (2006.01) |

| H01L 27/04   | (2006.01) |

| H01L 21/8234 | (2006.01) |

| H01L 27/06   | (2006.01) |

|      |       |      |

|------|-------|------|

| H01L | 27/04 | C    |

| H01L | 27/06 | 102A |

請求項の数 20 (全 12 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-536720 (P2013-536720)  |

| (86) (22) 出願日 | 平成23年10月25日 (2011.10.25)      |

| (65) 公表番号     | 特表2013-545302 (P2013-545302A) |

| (43) 公表日      | 平成25年12月19日 (2013.12.19)      |

| (86) 國際出願番号   | PCT/US2011/057672             |

| (87) 國際公開番号   | W02012/061126                 |

| (87) 國際公開日    | 平成24年5月10日 (2012.5.10)        |

| 審査請求日         | 平成26年10月24日 (2014.10.24)      |

| (31) 優先権主張番号  | 61/406,375                    |

| (32) 優先日      | 平成22年10月25日 (2010.10.25)      |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 13/267,674                    |

| (32) 優先日      | 平成23年10月6日 (2011.10.6)        |

| (33) 優先権主張国   | 米国(US)                        |

|               |                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者     | 390020248<br>日本テキサス・インスツルメンツ株式会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (73) 特許権者     | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 上記1名の代理人 | 100098497<br>弁理士 片寄 恒三                                                                                                |

最終頁に続く

(54) 【発明の名称】ゼロ温度係数キャパシタを備えた集積回路

## (57) 【特許請求の範囲】

## 【請求項1】

電気的導電性材料を含むキャパシタ下部プレートと、

前記キャパシタ下部プレートの上に形成される二酸化シリコンのキャパシタ誘電体層であって、前記キャパシタ誘電体層内のリン、シリコン及び酸素以外の原子の全濃度が $1 \times 10^{-1} \sim 10^{-8}$  原子/ $\text{cm}^3$ より小さくなるように、前記キャパシタ誘電体層が、 $1.7 \times 10^{-2} \sim 2.3 \times 10^{-2}$  原子/ $\text{cm}^3$ のリン濃度を有する、前記キャパシタ誘電体層と、

前記キャパシタ誘電体層の上に形成されるキャパシタ上部プレートであって、電気的導電性材料を含む、前記キャパシタ上部プレートと、

を含む、キャパシタ。

10

## 【請求項2】

請求項1に記載のキャパシタであって、

前記キャパシタ誘電体層が $4.5 \sim 5.5$  ナノメートル厚みである、キャパシタ。

## 【請求項3】

請求項1に記載のキャパシタであって、

前記キャパシタ下部プレートが多結晶シリコンを含む、キャパシタ。

## 【請求項4】

請求項3に記載のキャパシタであって、

前記キャパシタ上部プレートが、Ti、TiN、TiSiN、Ta、TaN、TaSiN、WN、WSiN及びそれらの任意の組み合わせから成るグループから選択される

20

材料を含む、キャパシタ。

**【請求項 5】**

請求項 1 に記載のキャパシタであって、

前記キャパシタ下部プレートが、アルミニウム、銅及び金から成るグループから選択される金属を含む、キャパシタ。

**【請求項 6】**

基板と、

前記基板の上に形成されるキャパシタと、

を含む、集積回路であって、

前記キャパシタが、

前記基板の上に形成されるキャパシタ下部プレートであって、電気的導電性材料を含む、前記キャパシタ下部プレートと、

前記キャパシタ下部プレートの上に形成される二酸化シリコンのキャパシタ誘電体層であって、前記キャパシタ誘電体層内のリン、シリコン及び酸素以外の原子の全濃度が  $1 \times 10^{18}$  原子 /  $\text{cm}^3$  より小さくなるように、前記キャパシタ誘電体層が  $1.7 \times 10^{20}$  原子 /  $\text{cm}^3$  ~  $2.3 \times 10^{20}$  原子 /  $\text{cm}^3$  のリン濃度を有する、前記キャパシタ誘電体層と、

前記キャパシタ誘電体層の上に形成されるキャパシタ上部プレートであって、電気的導電性材料を含む、前記キャパシタ上部プレートと、

を含む、回路。

**【請求項 7】**

請求項 6 に記載の回路であって、

前記基板の上に形成される金属酸化物半導体 (MOS) ドラミジスタを更に含み、

前記トランジスタが、前記キャパシタ下部プレートと同じ材料で形成されるトランジスタゲート電極を含む、回路。

**【請求項 8】**

請求項 6 に記載の回路であって、

前記キャパシタ誘電体層が 45 ~ 55 ナノメートル厚みである、回路。

**【請求項 9】**

請求項 6 に記載の回路であって、

前記基板の上面において形成されるフィールド酸化物の要素を更に含み、

前記キャパシタ下部プレートが前記フィールド酸化物要素上に形成され、前記キャパシタ下部プレートが多結晶シリコンを含む、回路。

**【請求項 10】**

請求項 9 に記載の回路であって、

前記キャパシタ上部プレートが、Ti、TiN、TiSiN、Ta、TaN、TaSiN、WN、WSiN 及びそれらの任意の組み合わせから成るグループから選択される材料を含む、回路。

**【請求項 11】**

請求項 6 に記載の回路であって、

前記集積回路が、前記基板の上に形成される相互接続誘電体層を更に含み、

金属相互接続ラインが前記相互接続誘電体層上に形成され、

前記キャパシタ下部プレートが、前記金属相互接続ラインと同時に前記相互接続誘電体層上に形成され、更に

前記キャパシタ下部プレートが、アルミニウム、銅及び金から成るグループから選択される金属を含む、回路。

**【請求項 12】**

集積回路を形成するプロセスであって、

基板を提供することと、

前記基板の上にキャパシタを形成することと、

10

20

30

40

50

を含み、

前記キャパシタを形成することが、

前記基板の上にキャパシタ下部プレートを形成する工程であって、前記キャパシタ下部プレートが電気的導電性材料を含む、前記キャパシタ下部プレートを形成する工程と、

前記キャパシタ下部プレートの上に二酸化シリコンのキャパシタ誘電体層を形成する工程であって、前記キャパシタ誘電体層内のシリコン及び酸素以外の原子の全濃度が $1 \times 10^{-8}$  原子 /  $\text{cm}^3$  より小さくなるようにする、前記キャパシタ誘電体層を形成する工程と、

前記キャパシタ誘電体層において $1.7 \times 10^{-2}$  原子 /  $\text{cm}^3$  ~  $2.3 \times 10^{-2}$  原子 /  $\text{cm}^3$  のリン濃度を提供するように、前記キャパシタ誘電体層内にリンを置く工程と、

前記キャパシタ誘電体層の上にキャパシタ上部プレートを形成する工程であって、前記キャパシタ上部プレートが電気的導電性材料を含む、前記キャパシタ上部プレートを形成する工程と、

を含むプロセスによる、プロセス。

#### 【請求項 1 3】

請求項 1 2 に記載のプロセスであって、

キャパシタ下部プレートを形成する前記工程が、トランジスタのゲート電極を同時に形成する、プロセス。

#### 【請求項 1 4】

請求項 1 3 に記載のプロセスであって、

リンを置く前記工程において、前記キャパシタ誘電体層におけるリンの全ドーズ量が、 $8.5 \times 10^{-4}$  原子 /  $\text{cm}^2$  ~  $1.15 \times 10^{-4}$  原子 /  $\text{cm}^2$  であるように、且つ、注入されたリンの分布のピークが前記キャパシタ誘電体層のほぼ中央に置かれるように、イオン注入プロセスによって実行される、プロセス。

#### 【請求項 1 5】

請求項 1 2 に記載のプロセスであって、

リンを置く前記工程が、300 より高い温度でリン含有ガスに前記集積回路をさらすことにより行われる、プロセス。

#### 【請求項 1 6】

請求項 1 2 に記載のプロセスであって、

リンを置く前記工程が、リン含有プラズマに前記集積回路をさらすことにより行われる、プロセス。

#### 【請求項 1 7】

請求項 1 4 に記載のプロセスであって、

前記集積回路を形成する前記プロセスが、前記基板の上面においてフィールド酸化物の要素を形成する工程を更に含み、

前記キャパシタ下部プレートを形成する前記工程が、前記キャパシタ下部プレートが前記フィールド酸化物要素上の多結晶シリコンで形成されるように実行される、プロセス。

#### 【請求項 1 8】

請求項 1 7 に記載のプロセスであって、

前記キャパシタ上部プレートが、Ti、TiN、TiSiN、Ta、TaSiN、WN、WSiN 及びそれらの任意の組み合わせから成るグループから選択される材料を含む、プロセス。

#### 【請求項 1 9】

請求項 1 2 に記載のプロセスであって、

前記基板の上に相互接続誘電体層を形成することと、

前記相互接続誘電体層上に金属相互接続ラインを形成することと、

を更に含み、

前記キャパシタ下部プレートが、前記金属相互接続ラインと同時に前記相互接続誘電体

10

20

30

40

50

層上に形成され、

前記キャパシタ下部プレートが、アルミニウム、銅及び金から成るグループから選択される金属を含む、プロセス。

**【請求項 20】**

請求項 12 に記載のプロセスであって、

前記基板上にゲート誘電体層を形成することと、

前記ゲート誘電体層上にMOS ゲートを形成することと、

前記基板に前記MOS ゲートに隣接してソース及びドレイン領域を形成することと、

を更に含む、プロセス。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は電子キャパシタの分野に関連する。

**【背景技術】**

**【0002】**

電子キャパシタは、或る範囲の温度にわたって動作し得る。或る動作温度範囲にわたって実質的に一定の静電容量を呈するキャパシタを形成することが望ましい場合がある。

**【発明の概要】**

**【0003】**

二酸化シリコンキャパシタ誘電体層を形成し、その後続いて、 $1.7 \times 10^{20}$  原子/ $\text{cm}^3$  ~  $2.3 \times 10^{20}$  原子/ $\text{cm}^3$  のリン濃度を得るようにその誘電体層にリンを置くことにより、ゼロ温度係数 (ZTC) キャパシタが形成され得る。リンは、イオン注入され得るか、拡散源から供給され得るか、又は他の手段により供給され得る。ZTC キャパシタの温度係数は、-1 ppm / ~ 1 ppm / の間であり得る。ZTC キャパシタは集積回路の一部として形成され得る。

20

**【図面の簡単な説明】**

**【0004】**

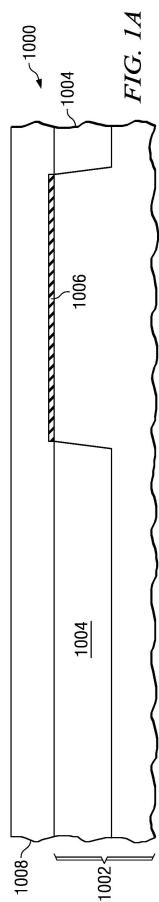

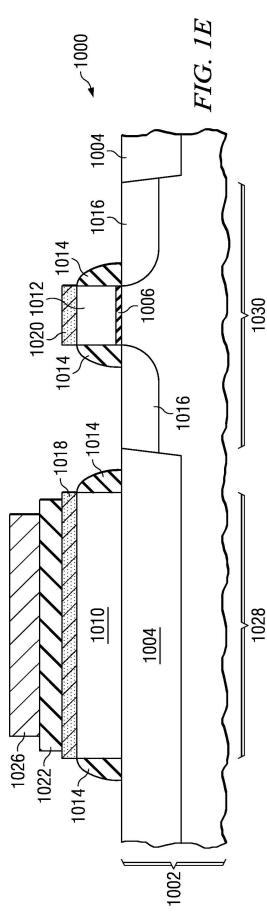

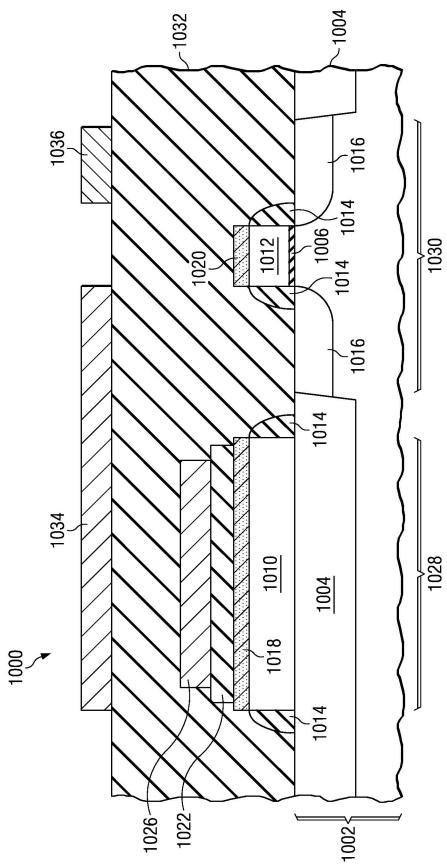

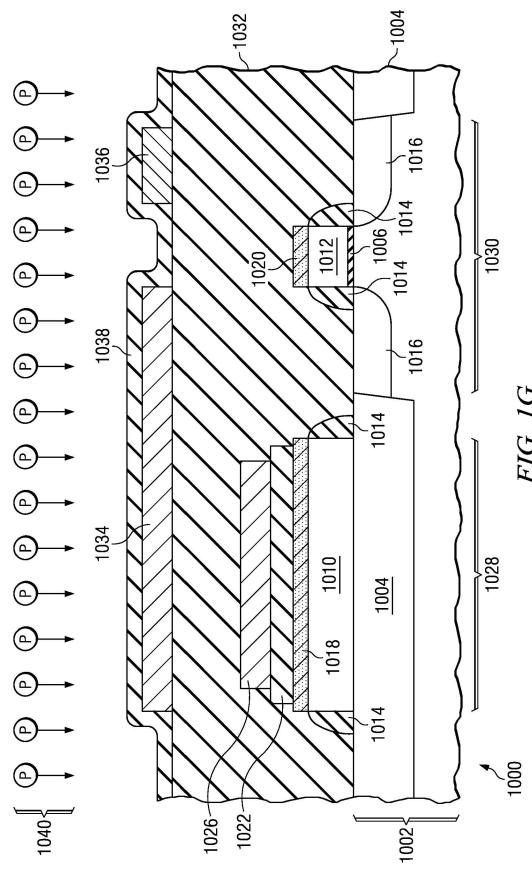

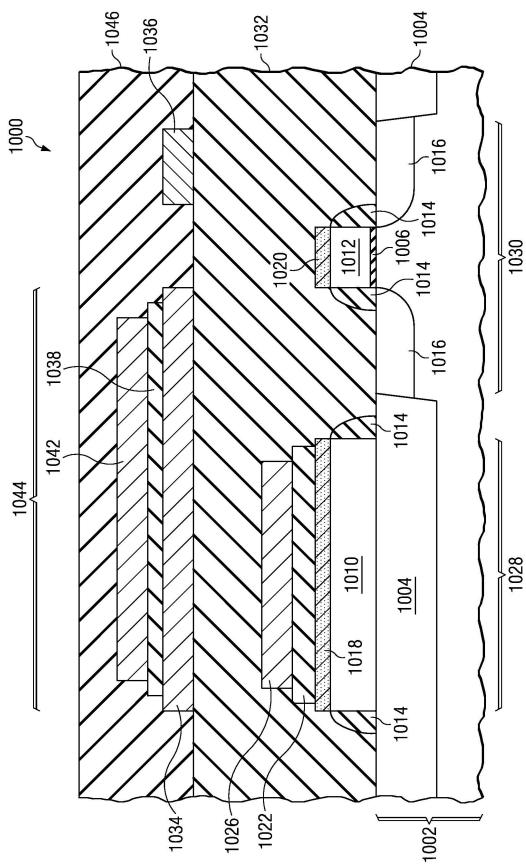

**【図 1 A】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

30

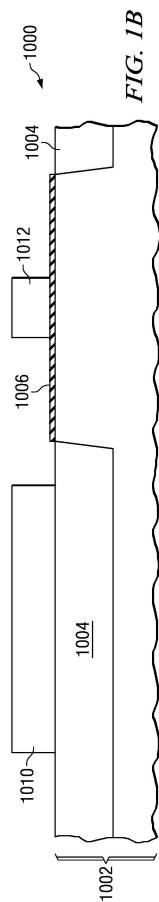

**【図 1 B】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

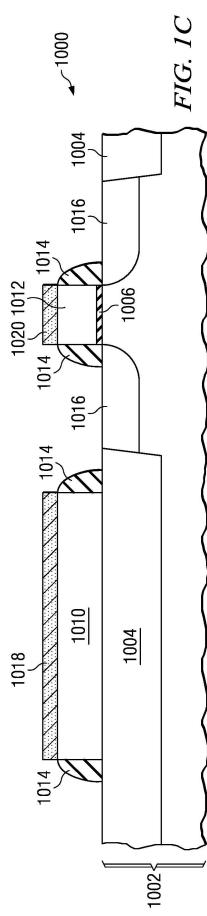

**【図 1 C】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

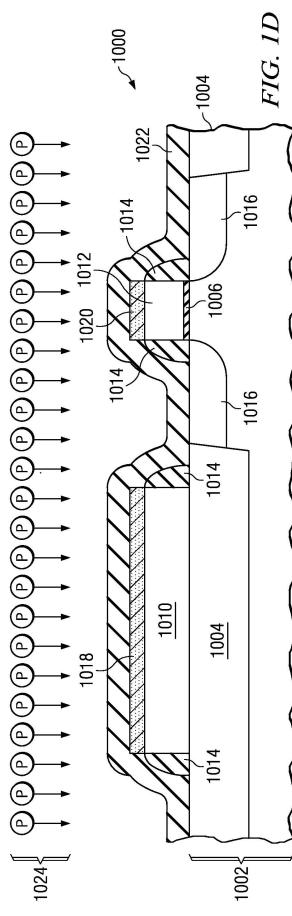

**【図 1 D】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

**【図 1 E】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

**【図 1 F】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

**【図 1 G】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

40

**【図 1 H】** 製造の連続的な段階で示す、実施例に従って形成された ZTC キャパシタを有する集積回路の断面図である。

**【0005】**

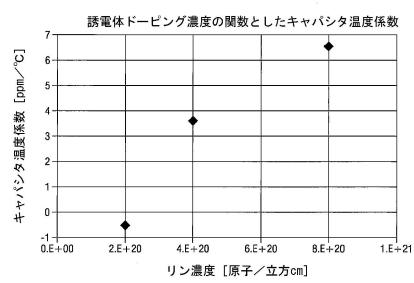

**【図 2】** キャパシタの誘電体層におけるリン濃度の関数とした、キャパシタの測定された温度係数のグラフである。

**【発明を実施するための形態】**

**【0006】**

ゼロ温度係数 (ZTC) キャパシタが、下部導電プレート、キャパシタ誘電体層、及び上部導電プレートを含み得る。ZTC キャパシタの静電容量は、或る温度範囲にわたって

50

変化し得る。ZTCキャパシタの温度係数 $K_T$ は、温度範囲内の一つより多い温度のZTCキャパシタの測定された静電容量値を数式1の表現に合わせることにより推定され得る。

(式1)

$$C(T) = C(T_{REF}) \times [1 + (K_T \times (T - T_{REF}))]$$

ここで、 $C(T)$ は温度 $T$ での静電容量値であり、 $T_{REF}$ は、例えば27である、参考温度である。

【0007】

1.7 × 10<sup>-20</sup>原子/cm<sup>3</sup> ~ 2.3 × 10<sup>-20</sup>原子/cm<sup>3</sup>のリン原子密度を得るようにキャパシタ誘電体層にリンが置かれ得る。本発明に関連して実行される作業では、ZTCキャパシタの温度係数 $K_T$ が、-1 ppm / ~ 1 ppm / あり得ることが示されている。

【0008】

ZTCキャパシタは集積回路の一部として形成され得る。一実施例において、底部プレートは、集積回路において金属酸化物半導体(MOS)トランジスタのゲートを形成するために用いられるゲート材料を含み得る。別の実施例において、底部プレートは、集積回路において相互接続を形成するために用いられる金属を含み得る。

【0009】

この説明のため、下付き文字なしの材料の元素式を表す用語は、それらの要素の特定の化学量は示唆しない。例えば、TiSiNという用語は、チタン(Ti)、シリコン(Si)、及び窒素(N)を含む材料を表し、1:1:1のTi:Si:N原子比を必ずしも有する必要はない。下付き文字のついた材料の元素式を表す用語は、下付き文字によって付与される化学量を示唆する。例えば、SiO<sub>2</sub>という用語は、1:2に実質的に等しいSi:O原子比を有するシリコン及び酸素(O)を含む材料を表す。

【0010】

ZTCキャパシタを含む集積回路の幾つかの場合において、実質的に集積回路全体がそのZTCキャパシタ専用である。アナログ集積回路など、ZTCキャパシタを含む集積回路の他の例では、集積回路は、金属酸化物半導体(MOS)トランジスタなど別の能動構成要素を含み得る。

【0011】

図1A～図1Hは、製造の連続的な段階で示す、実施例に従って形成されたZTCキャパシタを有する集積回路の断面図である。

【0012】

図1Aを参照すると、集積回路1000は基板1002の中及び上に形成され、基板1002は、単結晶シリコンウエハであり得るが、これは、シリコンオンインシュレータ(SOI)ウエハ、異なる結晶配向の領域を有するハイブリッド配向技術(HOT)ウエハ、ガリウム砒素など別の材料の半導体ウエハ、又はIC1000の製造に適切な他の材料、であってもよい。本実施例の1つの実現例において、基板1002は、セラミック、結晶性アルミニウム酸化物、ガラス、プラスチック、又は他の非導電性材料など、電気的絶縁性層を含み得る。

【0013】

フィールド酸化物1004の1つ又は複数の要素が、例えば、250～600ナノメートル厚みの二酸化シリコンで、基板1002の上面において形成され得る。フィールド酸化物要素1004は、シャロートレンチアイソレーション(STI)又はシリコンの局所酸化(LOCOS)プロセスにより形成され得る。STIプロセスにおいて、二酸化シリコンは、高密度プラズマ(HDP)又は高アスペクト比プロセス(HARP)により堆積され得る。本実施例の1つの実現例において、MOSトランジスタのためのゲート誘電体層1006が、基板1002の上面において形成され得る。

【0014】

第1の電気的導電層1008が、基板1002上に形成され、存在する場合フィールド

10

20

30

40

50

酸化物要素 1004 に接し得、及び存在する場合ゲート誘電体層 1006 に接し得る。集積回路 1000 内に MOS トランジスタを含む本実施例の実現例において、第 1 の電気的導電層 1008 は、MOS トランジスタのゲートを形成するための多結晶シリコンなどの材料を含み得る。

#### 【0015】

図 1B を参照すると、図 1A の第 1 の電気的導電層 1008 がパターニング及びエッチングされて、第 1 のキャパシタ下部プレート 1010 を形成する。集積回路 1000 内に MOS トランジスタを含む本実施例の実現例において、MOS ゲート 1012 が、第 1 のキャパシタ下部プレート 1010 と同時に、図 1A の第 1 の電気的導電層 1008 から形成され得る。

10

#### 【0016】

図 1C を参照すると、側壁スペーサ 1014 が、例えば、シリコンナイトライドで、又はシリコンナイトライド及び二酸化シリコンの層で、第 1 のキャパシタ下部プレート 1010 の横方向表面に、及び形成される場合 MOS ゲート 1012 の横方向表面に、形成され得る。集積回路 1000 内に MOS トランジスタを含む本実施例の実現例において、ソース及びドレイン領域 1016 が、MOS ゲート 1012 近傍の基板 1002 において形成され得る。第 1 のキャパシタ下部プレート 1010 が多結晶シリコンを含む本実施例の実現例において、任意選択の金属シリサイド層 1018 が、第 1 のキャパシタ下部プレート 1010 の上面において形成され得る。集積回路 1000 内に MOS トランジスタを含む本実施例の実現例において、金属シリサイド層 1020 が、MOS ゲート 1012 の上面において形成され得る。存在する場合、金属シリサイド層 1018 及び 1020 は、集積回路 1000 の上面に、ニッケル、コバルト、又はチタンなどの金属の層を堆積し、金属の一部を、露出された多結晶シリコンと反応させるよう集積回路 1000 を過熱し、更に、例えば、酸及び過酸化水素の混合物を含むウェットエッチャントに集積回路 1000 を曝すことにより、集積回路 1000 表面から反応していない金属を選択的に取り除くことにより、形成され得る。

20

#### 【0017】

図 1D を参照すると、集積回路 1000 上に第 1 のキャパシタ誘電体層 1022 が形成される。第 1 のキャパシタ誘電体層 1022 は、二酸化シリコンから成り、場合によっては炭素又はフッ素などの他の要素を含む。第 1 のキャパシタ誘電体層 1022 におけるシリコン及び酸素以外の原子の全濃度が、 $1 \times 10^{-8}$  原子 / cm<sup>3</sup> より小さい。第 1 のキャパシタ誘電体層 1022 は、10 ~ 200 ナノメートル厚みであり得る。本実施例の 1 つの実現例において、第 1 のキャパシタ誘電体層 1022 は、45 ~ 55 ナノメートル厚みであり得る。第 1 のキャパシタ誘電体層 1022 は、化学気相成長 (CVD)、プラズマ化学気相成長 (PECVD)、低圧化学気相成長 (LPCVD)、常圧化学気相成長 (APCVD)、高密度プラズマ (HDP)、高アスペクト比プロセス (HARP) としても知られている、オゾンベースの熱的化学気相成長 (CVD) プロセス、又は他の適切な二酸化シリコン層形成プロセス堆積により、形成され得る。第 1 のキャパシタ誘電体層 1022 は、テトラエトキシシラン又は TEOS としても知られている、オルトけい酸テトラエチルの分解、又はメチルシルセスキオキサン (MSQ) の堆積により形成され得る。

30

#### 【0018】

第 1 のキャパシタ誘電体層 1022 にリン原子を配置する第 1 のリン配置プロセス 1024 が実行される。第 1 のリン配置プロセス 1024 は、第 1 のキャパシタ誘電体層 1022 において  $1.7 \times 10^{-6} \sim 2.3 \times 10^{-6}$  原子 / cm<sup>3</sup> のリン原子の平均濃度を提供するように調整される。第 1 のリン配置プロセス 1024 は、例えば、第 1 のキャパシタ誘電体層 1022 が 50 ナノメートル厚みである本実施例の実現例において、 $8.5 \times 10^{-4}$  原子 / cm<sup>2</sup> ~  $1.15 \times 10^{-4}$  原子 / cm<sup>2</sup> のドーズ量を提供するように実行される。本実施例の 1 つの実現例において、第 1 のリン配置プロセス 1024 は、イオン注入プロセスであり得、第 1 のリン配置プロセス 1024 の注入エネルギーは、注入されたリン原子の分布のピークが第 1 のキャパシタ誘電体層 1022 のほぼ中央に置かれ

40

50

るよう調節され得る。例えば、第1のキャパシタ誘電体層1022が50ナノメートル厚みである本実施例の実現例において、第1のリン配置プロセス1024の注入エネルギーは、10～20キロメートル電子ボルト(k e V)に設定され得る。本実施例の代替実現例において、第1のリン配置プロセス1024は、300を上回る温度のガスを含むリンに集積回路1000を曝すことを含み得る。別の実現例において、第1のリン配置プロセス1024は、プラズマを含むリンに集積回路1000を曝すことを含み得る。更なる実現例において、リンは、他の手段により第1のキャパシタ誘電体層1022に配置されてもよい。

#### 【0019】

図1Eを参照すると、第1のキャパシタ誘電体層1022は、任意選択でパターニング及びエッチングされ得、図1Eに示すような、第1のキャパシタ下部プレート1010の境界に近接する境界を形成し得る。第1のキャパシタ誘電体層1022上に第1のキャパシタ上部プレート1026が形成される。第1のキャパシタ上部プレート1026は、金属又はドープされた半導体材料など、電気的導電性材料で形成される。本実施例の1つの実現例において、第1のキャパシタ上部プレート1026は、50～400ナノメートル厚みの、Ti、TiN、TiSiN、Ta、TaN、TaSiN、W、WN、WSiN、又はそれらの任意の組み合わせ、を含み得る。別の実現例において、第1のキャパシタ上部プレート1026は、50～500ナノメートル厚みの、アルミニウム、銅、金、又は集積回路1000における相互接続のために用いられる他の金属を含み得る。

#### 【0020】

第1のキャパシタ下部プレート1010、 $1.7 \times 10^{20}$ 原子/cm<sup>3</sup>～ $2.3 \times 10^{20}$ 原子/cm<sup>3</sup>のリン濃度を有する第1のキャパシタ誘電体層1022、及び第1のキャパシタ上部プレート1026は、第1のZTCキャパシタ1028を形成する。存在する場合、ゲート誘電体層1006、MOSゲート1012、及びソース及びドレイン領域1016は、基板1002の中及び上に形成されるMOSトランジスタ1030の一部である。

#### 【0021】

第2のZTCキャパシタが、図1F～図1Hを参照して説明するように、基板1002の上の相互接続領域において集積回路1000内に形成され得る。図1Fを参照すると、集積回路1000上に第1の相互接続誘電体層1032が形成される。第1の相互接続誘電体層1032は、二酸化シリコン、シリコンナイトライド、オルガノシリケートガラス(OSG)、炭素ドープされたシリコン酸化物(SiCO又はCDO)、フルオロシリケートガラス(FSG)、又は他の誘電性材料、の1つ又は複数の層を含み得る。第1の相互接続誘電体層1032は、アルミニウム、銅、及び/又は金の金属配線、及びアルミニウム、銅、金、及び/又はタンゲステンのビアなど、金属相互接続要素の1つ又は複数の層を含み得る。第1の相互接続誘電体層1032における金属相互接続要素は、図1Fには示していない。

#### 【0022】

第1の相互接続誘電体層1032上に第2のキャパシタ下部プレート1034が形成される。第2のキャパシタ下部プレート1034は、金属又はドープされた半導体材料など、電気的導電性材料で形成される。任意選択の金属相互接続ライン1036が、第1の相互接続誘電体層1032上に形成され得る。本実施例の1つの実現例において、第2のキャパシタ下部プレート1034は、金属相互接続ライン1036と同時に形成され得る。形成される場合、第2のキャパシタ下部プレート1034及び金属相互接続ライン1036は、アルミニウム、銅、及び/又は金を含み得る。

#### 【0023】

図1Gを参照すると、図1Dを参照して説明したように集積回路1000上に第2のキャパシタ誘電体層1038が形成される。第2のキャパシタ誘電体層1038の材料特性及びあり得る形成プロセスは、図1Dを参照して説明したとおりである。本実施例の1つの実現例において、第2のキャパシタ誘電体層1038の厚みは、第1のキャパシタ誘電

10

20

30

40

50

体層 1022 の厚みとは異なっていてよい。代替の実現例において、第2のキャパシタ誘電体層 1038 の厚みは、第1のキャパシタ誘電体層 1022 の厚みに実質的に等しく得る。本実施例の1つの実現例において、第2のキャパシタ誘電体層 1038 の形成プロセスは、第1のキャパシタ誘電体層 1022 のものとは異なるプロセスパラメータを用いてよい。

#### 【0024】

リン原子を第2のキャパシタ誘電体層 1038 内に置く第2のリン配置プロセス 1040 が実行される。第2のリン配置プロセス 1040 は、図 1D を参照して説明したようなリン濃度を提供するように調節される。本実施例の1つの実現例において、第2のリン配置プロセス 1040 は、図 1D を参照して説明したようなイオン注入プロセスであり得る。代替の実現例において、第2のリン配置プロセス 1040 は、図 1D を参照して説明したようなガスを含むリンからの拡散プロセスであり得る。別の実現例において、第2のリン配置プロセス 1040 は、図 1D を参照して説明したように、プラズマを含むリンへの露出を含み得る。更なる実現例において、リンは、他の手段により第2のキャパシタ誘電体層 1038 に配置されてもよい。

#### 【0025】

図 1H を参照すると、第2のキャパシタ誘電体層 1038 は、任意選択でパターニング及びエッチングされ得、図 1H に示すように、第2のキャパシタ下部プレート 1034 の境界に近接する境界を形成し得る。第2のキャパシタ誘電体層 1038 上に第2のキャパシタ上部プレート 1042 が形成される。第2のキャパシタ上部プレート 1042 は、金属又はドープされた半導体材料など、電気的導電性材料で形成される。本実施例の1つの実現例において、第2のキャパシタ上部プレート 1042 は、50 ~ 400 ナノメートル厚みの、Ti、TiN、TiSiN、Ta、TaN、TaSiN、W、WN、WSiN、又はそれらの任意の組み合わせ、を含み得る。別の実現例において、第2のキャパシタ上部プレート 1042 は、100 ~ 2000 ナノメートル厚みの、アルミニウム、銅、金、又は集積回路 1000 において相互接続に用いられる他の金属、を含み得る。

#### 【0026】

第2のキャパシタ下部プレート 1034、 $1.7 \times 10^{20}$  原子 /  $\text{cm}^3$  ~  $2.3 \times 10^{20}$  原子 /  $\text{cm}^3$  のリン濃度を有する第2のキャパシタ誘電体層 1038、及び第2のキャパシタ上部プレート 1042 は、第2のZTC キャパシタ 1044 を形成する。

#### 【0027】

任意選択の第2の相互接続誘電体層 1046 が、第2のZTC キャパシタ 1044 の上に形成され得る。第2の相互接続誘電体層 1046 は、形成される場合、第1の相互接続誘電体層 1032 に関連して参照したような材料を含み得る。第2の相互接続誘電体層 1046 は、アルミニウム、銅、及び / 又は金の金属配線、及びアルミニウム、銅、金、及び / 又はタンゲステンのピアなど、金属相互接続要素の1つ又は複数の層を含み得る。金属相互接続要素は、図 1H には示していない。

#### 【0028】

本実施例の1つの実現例において、集積回路 1000 は、第1のZTC キャパシタ 1028 のみを含み、第2のZTC キャパシタ 1044 は含まなくてよい。本実施例の別の実現において、集積回路 1000 は、第1のZTC キャパシタ 1028 及び第2のZTC キャパシタ 1044 の両方を含み得る。代替の実施例において、集積回路が、相互接続誘電体層の上に形成される ZTC キャパシタの場合のみ、図 1H を参照して説明したような第2のZTC キャパシタ 1044 を含み得る。

#### 【0029】

図 2 は、キャパシタの誘電体層におけるリン濃度の関数とした、キャパシタの測定された温度係数のグラフである。図 2 におけるデータは、約 50 ナノメートル厚みで、16 keV のイオン注入エネルギーのリンでイオン注入されたキャパシタ誘電体層を用いて、本発明に関連して実行された作業から得たものである。キャパシタの製造に精通するものであれば、図 2 に示すデータを参照すれば、 $1.7 \times 10^{20}$  原子 /  $\text{cm}^3$  ~  $2.3 \times 10^{20}$

10

20

30

40

50

$^{20}$  原子 /  $\text{cm}^3$  のリン密度を供給することが、-1 ppm / ~1 ppm / の温度係数を提供し得ることが分かるであろう。

【0030】

本発明に関連する技術に習熟した者であれば、説明した例示の実施例に変形が成され得ること、及び本発明の特許請求の範囲内で他の実施例を実装し得ることが分かるであろう。

【図 1 A】

【図 1 B】

【図 1 C】

FIG. 1C

【図 1 D】

FIG. 1D

【図 1 E】

FIG. 1E

【図 1 F】

FIG. 1F

【図 1 G】

FIG. 1G

【図 1 H】

FIG. 1H

【図 2】

FIG. 2

---

フロントページの続き

(72)発明者 ウエイドン ティエン

アメリカ合衆国 75252 テキサス州 ダラス, ベンチマーク ドライブ 17843

(72)発明者 イムラン カーン

アメリカ合衆国 75082 テキサス州 リチャードソン, モロニー ドライブ 3725

審査官 宇多川 勉

(56)参考文献 米国特許出願公開第2004/0209423(US, A1)

特開2009-182271(JP, A)

特開2009-290179(JP, A)

特開昭63-301554(JP, A)

特開2010-109341(JP, A)

米国特許第04938847(US, A)

特開2011-077294(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 21/8234

H01L 27/04

H01L 27/06