(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4481458号

(P4481458)

(45) 発行日 平成22年6月16日(2010.6.16)

(24) 登録日 平成22年3月26日(2010.3.26)

(51) Int.Cl.

F 1

**G06F 13/38 (2006.01)**

**HO4N 5/907 (2006.01)**

**HO4N 5/765 (2006.01)**

**HO4N 7/14 (2006.01)**

GO 6 F 13/38 3 1 O F

HO 4 N 5/907 B

HO 4 N 5/91 L

HO 4 N 7/14

請求項の数 3 (全 16 頁)

(21) 出願番号

特願2000-256130 (P2000-256130)

(22) 出願日

平成12年8月25日 (2000.8.25)

(65) 公開番号

特開2002-73538 (P2002-73538A)

(43) 公開日

平成14年3月12日 (2002.3.12)

審査請求日

平成19年8月27日 (2007.8.27)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置のデータ処理回路

## (57) 【特許請求の範囲】

## 【請求項 1】

撮像装置内の撮像手段より連続して出力される各フレームの画像データを順次取り込んで表示する E V F モードと、前記撮像手段より出力された 1 フレーム分の画像データを取り込んで記憶手段に記憶する撮影モードと、該記憶手段に記憶された画像データを読み出して再生する再生モードと、を含む複数の動作モードから何れか 1 つの動作モードを選択する選択手段と、

前記撮像装置内のバスとの間で転送される画像データを一時的に記憶するための画像メモリと

を有し、前記バス上に接続される、前記撮像装置のデータ処理回路であって、

前記画像メモリに格納されている画像データのデータ量を検出する検出手段と、

前記データ量に対して前記動作モード毎に予め定められた、前記転送におけるデータ転送長のうち、前記選択手段が選択した動作モードに対応するデータ転送長を特定し、前記画像メモリに格納されている画像データのデータ転送長を該特定したデータ転送長とする調整手段と

を備えることを特徴とする前記撮像装置のデータ処理回路。

## 【請求項 2】

前記調整手段は、前記動作モード毎の、前記データ量と前記転送におけるデータ転送長との対応関係を示すテーブルのうち、前記選択手段が選択した動作モードに対応するテーブルを用いて、前記選択手段が選択した動作モードに対応するデータ転送長を特定するこ

とを特徴とする請求項 1 に記載の前記撮像装置のデータ処理回路。

【請求項 3】

前記対応関係は、プログラムにより可変であることを特徴とする請求項 1 又は 2 に記載の前記撮像装置のデータ処理回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、撮像装置のデータ処理回路に関するものである。

【0002】

【従来の技術】

近年、C C D 等の固体撮像装置の小型化、省電力化および L S I の高集積化、高機能化、低消費電力化などの技術の進展に伴い、デジタルスチルカメラに代表される高機能・高性能な画像処理装置が一般に利用されるようになった。さらには、携帯電話機能を内蔵した携帯型テレビ電話端末やカメラを内蔵したノート型 P C 等も開発されている。このような画像装置においては、処理すべきデータは主に画像データであり、特に表示部のように、画像データを格納したメモリからの平均データ転送量は多くないが、データ転送のピーク時にメモリからのデータの取りこぼしの許されないリアルタイムのデータ転送を必要とするデータ処理部と、画像圧縮・伸長部のように平均データ転送量が多いが必ずしもリアルタイムのデータ転送は必要ではなく、平均として必要なデータ転送が行われればよいようなデータ処理部が混在しており、かつこれらのデータ処理部が同時動作している。

10

【0003】

また、画像データのリアルタイム転送においては、ピーク時（アクティブ時）のデータ転送量とピーク時以外（ブランкиング時）のデータ転送量の差が極めて大きいため、データ転送レートを平均化するために F I F O を設ける場合がある。この場合、データ転送路全体のデータ転送レート（バンド幅）を平均転送レートに合わせるために巨大な F I F O の容量を必要とする。

【0004】

通常、データ転送路のバンド幅はデータ幅と動作周波数の積に比例しているため、バンド幅を保ちつつ F I F O の容量を小さくするためにはバンド幅を大きく取る必要があり、従来技術では装置全体を高い動作周波数で動作させるか、データ幅を拡大する必要があった。

30

【0005】

あるいは従来技術においては、限られたデータ転送路のバンド幅を各モジュールに割り当てるための調停方式を工夫して、リアルタイムのデータ転送にリアルタイムではないデータ転送よりも高いプライオリティを与えるような制御を行うことによりリアルタイムのデータ転送を保証していた。

【0006】

【発明が解決しようとする課題】

しかしながら、従来技術の巨大な F I F O を備える方式では回路規模が増大するため、装置の消費電力、コストが増大するという問題があった。

40

【0007】

また、リアルタイム性を保証するために装置全体を高い動作周波数で動作させる場合には、装置全体の消費電力が増大するため、特に電池駆動のような携帯型の画像処理装置には適さないという問題点があった。

【0008】

さらに、リアルタイムのデータ転送にリアルタイムではないデータ転送よりも高いプライオリティを与えるような制御を行うための調停方式は複雑であり、調停装置の設計および動作検証が困難であると同時に調停装置の規模が大きくなるという問題点があった。

【0009】

本発明は以上の問題点に鑑みてなされたものであり、記憶メモリに格納されているデータ

50

量に応じて、データ転送で転送するデータの転送長を調整することを目的とする。

### 【0010】

#### 【課題を解決するための手段】

本発明の目的を達成するために、例えば本発明の撮像装置のデータ処理回路は以下の構成を備える。すなわち、

撮像装置内の撮像手段より連続して出力される各フレームの画像データを順次取り込んで表示するEVFモードと、前記撮像手段より出力された1フレーム分の画像データを取り込んで記憶手段に記憶する撮影モードと、該記憶手段に記憶された画像データを読み出して再生する再生モードと、を含む複数の動作モードから何れか1つの動作モードを選択する選択手段と、

10

前記撮像装置内のバスとの間で転送される画像データを一時的に記憶するための画像メモリと

を有し、前記バス上に接続される、前記撮像装置のデータ処理回路であって、前記画像メモリに格納されている画像データのデータ量を検出する検出手段と、

前記データ量に対して前記動作モード毎に予め定められた、前記転送におけるデータ転送長のうち、前記選択手段が選択した動作モードに対応するデータ転送長を特定し、前記画像メモリに格納されている画像データのデータ転送長を該特定したデータ転送長とする調整手段と

を備えることを特徴とする。

### 【0012】

20

#### 【発明の実施の形態】

以下添付図面を用いて、本発明を好適な実施形態に従って詳細に説明する。

### 【0013】

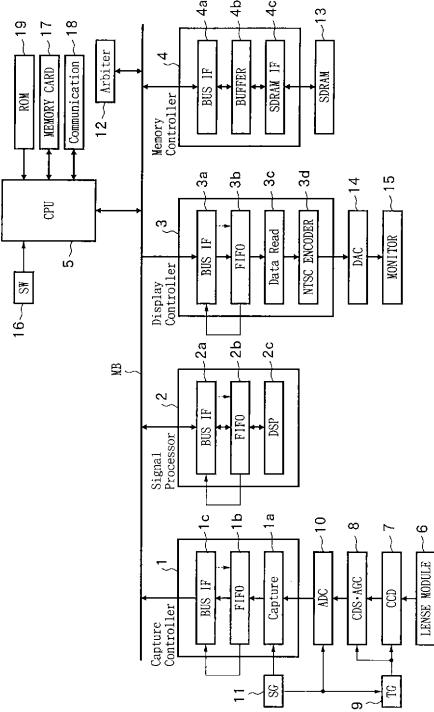

図1は本実施形態としての携帯型テレビ電話端末の内部構成を示すブロック図である。ブロック間を結合する線の表記は、データ系の接続を太い実線で図示し、制御系の接続を細い実線で図示した。ただし、すべての接続が図示されているわけではなく、説明に必要な代表的な接続のみを図示した。

### 【0014】

主要なブロックとして、画像取り込みに関わる画像取り込みコントローラ(Capture Controller)1、画像処理に関わる信号処理プロセッサ(Signal Processor)2、画像表示に関わる表示コントローラ(Display Controller)3、画像メモリ制御のメモリコントローラ(Memory Controller)4、全体制御に関わるCPU5からなる。

30

### 【0015】

次に、本実施形態における携帯型テレビ電話端末の動作を説明するために、各ブロックの動作を説明する。

### 【0016】

まずレンズモジュール6に入力された画像がCCD7に結像する。レンズモジュール6はレンズ、オートアイリスのための駆動系、オートフォーカスのための駆動系等からなる。駆動系の制御はCPU5からの不図示の制御信号によって行われる。CCD7に結像した画像データは前処理モジュール(CDS・AGC)8に入力される。本実施形態においては、CCD7の取り込む有効画素数は $640 \times 480$ 画素(VGA相当)である。前処理モジュール8はCDS(相関二重サンプリング)およびAGC(自動利得制御)からなる。また、CCD7および前処理モジュール8に対するクロックおよびタイミング信号はタイミング生成回路9(TG)より供給される。前処理を行った画像データはADC変換器(ADC)10により10ビットのデジタルデータに変換されて、タイミング生成回路11(SG)により生成されるピクセルクロックに同期して画像取り込みコントローラ1に入力される。

40

### 【0017】

画像取り込みコントローラ1に入力された画像データは、まず取り込み回路1aによって

50

取り込まれ、直ちに有効画素データのみが FIFO1b に書き込まれる。

**【0018】**

バスインターフェース回路 (BUS IF) 1c は FIFO1b が Empty でない状態を検知すると、メインバス MB 上に書き込みのバストランザクションを発生し、メモリコントローラ 4 に FIFO1b から読み出したデータを転送する。バストランザクションはデータ転送を行うための転送先開始アドレスおよびデータ長送出 (アドレス・フェーズ) と転送すべきデータ送出 (データ・フェーズ) の 2 つのフェーズからなる。

**【0019】**

なお、バスインターフェース回路 1c は通常画像取り込みクロック (Latch Clock) とは非同期のバスクロックで動作している。したがって、FIFO1b の読み出しきロックは、書き込みクロックとは非同期であり、FIFO1b はこの非同期データ転送を緩衝するための目的にも用いられる。10

**【0020】**

メインバス MB には、他にもバストランザクションを発生するバスマスターが複数接続されている (信号処理プロセッサ 2、表示コントローラ 3、CPU 5) ので、同時に複数のバストランザクションが発生する可能性がある。バスアービタ 12 は、一度に 1 つだけのバスマスターがバストランザクションを発生できるようにバスを調停する。

**【0021】**

メモリコントローラ 4 は、バスインターフェース回路 (BUS IF) 4a においてバストランザクションを受信し、データおよびデータを格納すべきメモリアドレスを一時バッファ (BUFFER) 4b に書き込む。SDRAM インターフェース回路 (SDRAM IF) 4c は SDRAM 13 への制御信号を出力するとともに、バッファ 4b に格納されたアドレス、データを SDRAM 13 に対して出力する。ここで、メモリアドレスはバストランザクションのアドレス・フェーズにおいて得られたアドレスから生成されるのである。SDRAM インターフェース 4c は前記アドレスから始まる連続アドレスに対して、同じくアドレス・フェーズにおいて得られたデータ長分のメモリアクセスを連続的に、すなわちバースト転送を用いて行う。20

**【0022】**

画像メモリとしては SDRAM 13 が接続されている。バスインターフェース回路 4a、バッファ 4b、SDRAM インターフェース回路 4c、及び SDRAM 13 はすべてバスクロックに同期して動作する。30

**【0023】**

次に、信号処理プロセッサ 2 は読み出しのためのバストランザクションを発生し、バスクロックで動作するバスインターフェース回路 2a によって画像メモリ (SDRAM 13) から画像データを読み出す。読み出されたデータはバスクロックに同期して双方向 FIFO2b に書き込まれる。DSP 2c はバスクロックとは異なるクロック (DSP クロック) で動作しており、DSP クロックに同期して双方向 FIFO2b のデータにアクセスして、カラーマトリクス処理により YC 分離を行い、続いて色補正、エッジ強調、ホワイトバランス調整、ガンマ補正などの処理を行う。このようにして得られた画像データは、表示に用いられるほか画像圧縮にも用いられる。例として表示用に用いる場合は、表示コントローラ 3 が読み出せるように、バスインターフェース回路 2a を起動して書き込みのバストランザクションを発生し、SDRAM 13 にデータ (DSP 2c により処理された画像データ) を転送する。40

**【0024】**

信号処理プロセッサ 2 においても、バストランザクションはデータ転送を行うための転送先開始アドレスおよびデータ長送出 (アドレス・フェーズ) と転送すべきデータ送出 (データ・フェーズ) の 2 つのフェーズからなる。但し、アドレス・フェーズにおいては、読み出しか書き込みかを示す信号も合わせて送出される。

**【0025】**

次に、本実施形態における携帯型テレビ電話端末におけるそれぞれの動作モードについて50

説明する。動作モードとしては、EVFモード、撮影モード、再生モード、テレビ電話モードがある。

【0026】

EVFモードにおいては、上述した動作を毎フレーム毎に繰り返すことによって、連続したフレームを画像メモリに取り込む。信号処理プロセッサ2が取り込み、格納する画像メモリ上の領域としては、同一領域を上書きする動作でよい。そして表示コントローラ3は、信号処理プロセッサ2が上書きした前記領域より画像データを読み出すことにより、表示データを得る。

【0027】

表示コントローラ3は読み出しのためのバストランザクションを発生し、バスロックで動作するバスインターフェース回路3aによって画像メモリから表示データを読み出す。

10 次に、このデータをバスロックに同期して FIFO3bの書き込みポートに入力する。NTSCのモニターや液晶ディスプレイに代表されるように、一般に表示装置は画面を絶え間なくリフレッシュする必要があるため、有効画面期間中はあるピクセルクロックで動作し続けなければならない。そのためバスインターフェース回路3aは、FIFO3bがフル状態になるまで上述のデータを読み出し続ける。

【0028】

次に、読み出し回路3cは表示ピクセルクロックに同期して FIFO3bよりデータを読み出し、NTSCエンコーダ3dに送出する。FIFO3bより読み出されたデータはNTSCエンコーダ3dによってNTSCフォーマットに変換され、DAコンバータ(DAC)14によってアナログ信号に変換され、その後にNTSCモニタ15によって表示される。

20

【0029】

上記の動作をフレームごとに連続することにより、EVFモードの動作となる。

【0030】

次に、撮影モードの動作を説明する。撮影モードでは1フレーム分の画像を取り込んだ後、該データをJPEG圧縮して外部記憶装置等に記録する。なおこの外部記憶装置は、ハードディスク等の装置、フロッピーディスクやCD-ROMなどの記憶媒体、もしくはこの記憶媒体を読み込む装置をも含む。

【0031】

まず、スイッチ群16のうちの1つはシャッターボタンであり、該ボタンの押下がCPU5によって検出されると、CPU5は不図示の制御信号により画像取り込みコントローラ1に対し、次の1フレームを取り込み終わったら以降のフレームは取り込まないように指示する。同様に、信号処理プロセッサ2に対し、次の1フレームは画像圧縮処理を行うことを通知する。

30

【0032】

画像取り込みコントローラ1はEVFモードの場合とは異なり、1フレーム取り込んで画像メモリにデータ転送を行い終わると一時停止する。信号処理プロセッサ2は取り込まれたデータを読み出して、表示データを生成した場合とまったく同様にY/C分離、色補正、エッジ強調、ホワイトバランス調整、ガンマ補正等の画像処理を行った後、直ちに該データに対して、DCT演算処理、量子化処理、可変長符号化処理などを施して得た符号データを、画像メモリ内の表示用データ領域とは別の領域に書き込む。

40

【0033】

CPU5は前記符号データを読み出し、必要なマーカー等を付加してJPEGデータとした後に、メモリカード(Memory Card)17に格納する。1フレーム分のデータの格納が終了すると、CPU5は画像取り込みコントローラ1に対して、取り込み再開を通知する。

【0034】

なお、メモリカード17に格納されたデータはホストインターフェースとなるコミュニケーション回路(Communication)18によりパーソナルコンピュータ等から

50

アクセスすることが可能である。本実施形態においてはコミュニケーション回路18はシリアルインターフェース、USB、IrDAおよび携帯電話モジュールなどからなる。

#### 【0035】

次に再生モードの動作を説明する。再生モードでは、画像取り込みコントローラ1は停止している。CPU5はメモリカード17に格納された、符号化された圧縮データを読み出してSDRAM13に書き込む。信号処理プロセッサ2は、符号データをSDRAM13より読み出して、復号化、逆量子化、逆DCT変換等の画像伸長処理を行って、表示可能な画像データとしたのちに再びSDRAM13に書き戻す。表示コントローラ3は前記表示可能データをSDRAM13より読み出して表示動作を行う。

#### 【0036】

次に、テレビ電話モードの動作を説明する。撮影モードでは、1フレーム取り込んだ後に画像取り込みコントローラ1は一時停止したが、テレビ電話モードでは、取り込みを中断せずに次々に連続するフレームを取り込む。取り込まれた画像は撮影モードと同様の処理によって信号処理プロセッサ2によって画像処理および画像圧縮・符号化を施され、SDRAM13に書き込まれる。書き込まれた符号データは、CPU5により読み出され所定のマーカー挿入等を行ったのちにコミュニケーション回路18の携帯電話モジュールによって電話回線を通じて通話相手に対して転送される。

#### 【0037】

一方、電話回線を通じて通話相手より受信した符号データは、コミュニケーション回路18からCPU5を経由してSDRAM13に書き込まれる。信号処理プロセッサ2は、符号データをSDRAM13より読み出して、復号化、逆量子化、逆DCT変換等の画像伸長処理を行って表示可能な画像データとしたのちに再びSDRAM13に書き戻す。表示コントローラ3は前記表示可能データをSDRAM13より読み出して表示動作を行う。以上のようにして、自画像を通話相手に電送すると同時に相手画像を自端末に表示する。

#### 【0038】

動作モードの変更は、ユーザによるスイッチ群16の操作によって行われる。スイッチの構成は様々な例が考えられるが、本実施形態ではダイアルと押しボタンにより構成する。ダイアルの回転により動作モードの候補が順次更新され、押しボタンの押下により候補が選択される。選択のイベントによりCPU5に割り込みが発生する。ROM19に格納された割り込み処理ルーチンは動作モード変更ルーチンをコールする。

#### 【0039】

動作モード変更ルーチンでは新たに選択された動作モードを読み取り、読み取られた動作モードに対応して各モジュールの設定を行う。

#### 【0040】

次にバスインターフェース回路1c, 2a, 3aの動作を説明する。バスインターフェース回路2aはリードとライト動作を行うので、これを例として説明する。バスインターフェース回路1cはライト動作のみ、3aはリード動作のみを行う。

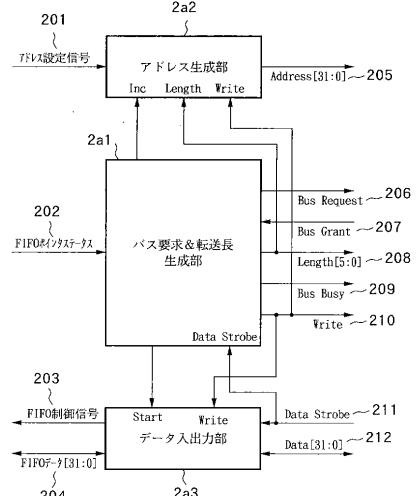

#### 【0041】

図2はバスインターフェース回路2aの内部構成を示す図である。バス要求および転送長生成部2a1には FIFO2bが出力するFIFOポインターステータス信号202が入力され、FIFO2bのステータスに応じてバス転送要求信号(Bus Request)206、6ビットの転送長信号(Length[5:0])208、ライトインジケータ信号(Write)210、及びバス使用信号(Bus Busy)209を出力する。

#### 【0042】

バス要求信号206はデータ転送要求を示し、ライト時はFIFO2bが空でない限り出力され、リード時はFIFO2bがフルでない限り出力される。バス要求信号206とバス使用信号209はバスアービタ12に接続されており、バスアービタ12は要求を出しているバスマスターを検出し、ラウンドロビン等の単純な調停方式によってバス使用権を与えるマスターに対してバス許可信号(Bus Grant)207を出力する。なお、バス許

10

20

30

40

50

可信号は、いずれのマスタもバス使用信号をアサートしていないときに出力される。バス許可信号を与えられたマスタは直ちにバス使用信号をアサートすることにより、バスアービタ12に対してバス使用許可権を獲得したことを通知する。

#### 【0043】

転送長信号208は転送データ長を2進表現したものであり、例えば転送長が8の場合、転送長信号208は”001000”となる。また、ライトインジケータ信号210にはライト時に”1”、リード時には”0”が出力される。この転送長信号208により、転送データ長を調整することができる。

#### 【0044】

アドレス生成部2a2は、CPU5から入力されるアドレス設定信号201に応じて開始アドレスが設定され、メインバスMBへの32ビットアドレス出力(Address[31:0])205を生成する。また、1トランザクション毎にバス要求および転送長生成部2a1からのアドレスインクリメント信号(Inc)および転送長信号208が入力され、次の転送のためのアドレスを生成する。10

#### 【0045】

データ入出力部2a3はバス要求および転送長生成部2a1からの転送開始信号(Start)と、ライトインジケータ信号210を受けて、 FIFO2bとメインバスMB間のデータ転送(FIFO2bとデータ入出力部2a3間では、 FIFOデータ[31:0]、データ入出力部2a3とメインバスMB間では、Data[31:0])を実行する。データライト時(ライトインジケータ信号210が”1”)は、メインバスMBからのデータストローブ信号(Data Strobe)211に応じてFIFO制御信号203を駆動してFIFO2bから32ビットのFIFOデータ204を取り出し、メインバスMB上に32ビットデータ(Data[31:0])212を出力する。20

#### 【0046】

一方、データリード時(ライトインジケータ信号210が”0”)は、データストローブ信号211に応じてメインバスMB上のデータ212を取り込み、FIFO制御信号203を駆動してFIFO2bへデータ204を書き込む。

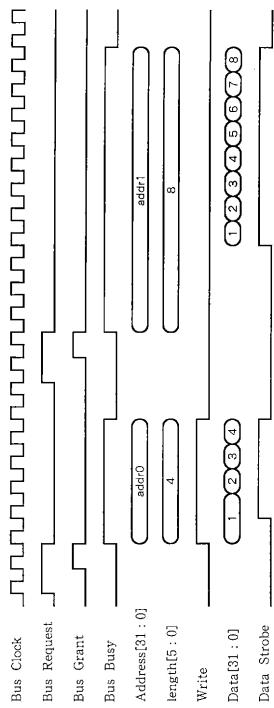

#### 【0047】

図3は、バスインターフェース回路2aのメインバスMB上の信号のタイミングを示したタイミング図である。すべての信号はバスクロック(Bus Clock)の立ち上がりエッジに同期して動作する。まずバス要求信号206をアサートすると、次のサイクルでバスアービタ12からのバス許可信号207がアサートされる。バスインターフェース回路2aは直ちにバス使用信号209をアサートすると同時に、転送開始アドレス(address)をアドレス信号205上に出力し、転送長信号208として4、すなわち”000100”を出力する。30

#### 【0048】

また、最初の転送はライト転送なのでライトインジケータ信号210に”1”を出力するとともにデータ0を出力する。次のサイクルからバスストレーブであるメモリコントローラ4からのデータストローブ211が4クロック間連続的に入力されるので、これに応じて出力データを1, 2, 3のように変化させる。データストローブ信号211が4クロックサイクル間アサートされると当バストランザクションでのデータ転送は終了し、バス使用信号209がネゲートされる。40

#### 【0049】

次にリード要求が発生すると、バスインターフェース回路2aは再びバス要求信号206をアサートする。アービタ12からのバス許可信号207を受信すると、データ212、アドレス信号205および転送長信号208を出力する。転送長は8であるので、”001000”がドライブされる。また今回はリード要求であるので、ライトインジケータ信号210には”0”が出力される。そしてメモリコントローラ4からのデータ受信待ちになる。メモリコントローラ4はメモリ(SDRAM13)からのデータをリードした後に、メインバスMBにデータを出力するとともにデータストローブ信号211をアサートす50

る。バスインターフェース回路 2 a はデータストローブ信号 2 1 1 のアサートを 8 クロックサイクル分検知するとともに、8 個のデータを読み込むことになる。

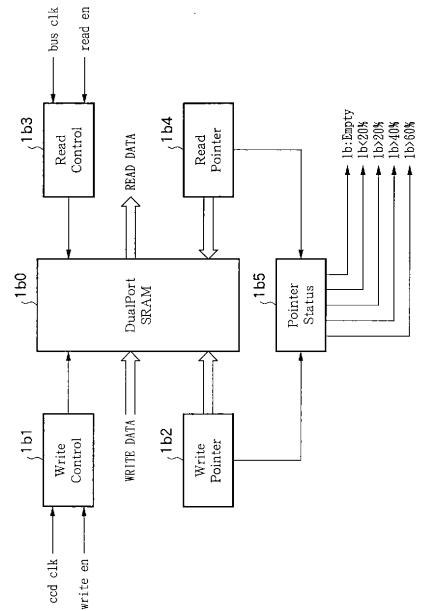

#### 【0050】

次に、各々のポインタステータス信号 2 0 2 の意味するところを、FIFO1 b の内部構成例であるブロック図(図4)、FIFO2 b の内部構成例であるブロック図(図5)、FIFO3 b の内部構成例であるブロック図(図6)を用いて説明する。

#### 【0051】

FIFO1 b は図4に示すように、同期型デュアルポートSRAM(Dual Port SRAM)1 b 0、書き込み制御回路(Write Control)1 b 1、書き込みアドレス生成(ポインタ生成)回路(Write Pointer)1 b 2、読み出し制御回路(Read Control)1 b 3、読み出しアドレス生成(ポインタ生成)回路(Read Pointer)1 b 4およびポインタステータス生成回路(Pointer Status)1 b 5よりなる。同期型デュアルポートSRAM1 b 0 は、例えば128(WORD)×8(BIT)のデュアルポートSRAMであり、取り込み回路1 a よりの書き込み有効信号write\_enが入力されるとCCD7のピクセルクロックccd\_ckに同期してCCD7からの画像データであるWRITE DATAが書き込みアドレス生成(ポインタ生成)回路1 b 2 の生成するアドレスに書き込まれる。1データの書き込み後、書き込みアドレス生成(ポインタ生成)回路1 b 2 が生成した書き込みポインタはインクリメントされる。

#### 【0052】

読み出し動作は、バスインターフェース回路1 c からの読み出し有効信号read\_enが入力されると、バスクロックbus\_ckに同期して読み出しアドレス生成(ポインタ生成)回路1 b 4 の生成するポインタの示すアドレスからREAD DATAを出力するのでこれを読み出す。読み出し後読み出しポインタはインクリメントされる。

#### 【0053】

ポインタステータス回路1 b 5 は、上述の書き込みポインタと読み出しポインタの差の絶対値を演算することにより、FIFO1 b のステータスを出力する。例えば、差の絶対値が0の場合はFIFO1 b が空であることを示すので1 b : Empty信号を出力し、差の絶対値がFIFO容量128の80%以上の場合はFIFO1 b の有効データがFIFO容量の20%以下であることを示すので1 b < 20%信号を出力する。同様に、FIFO1 b の有効データが20%から40%の間の場合は1 b > 20%信号を出力し、40%から60%の間の場合は1 b > 40%信号を出力し、60%以上の場合は1 b > 60%信号を出力する。

#### 【0054】

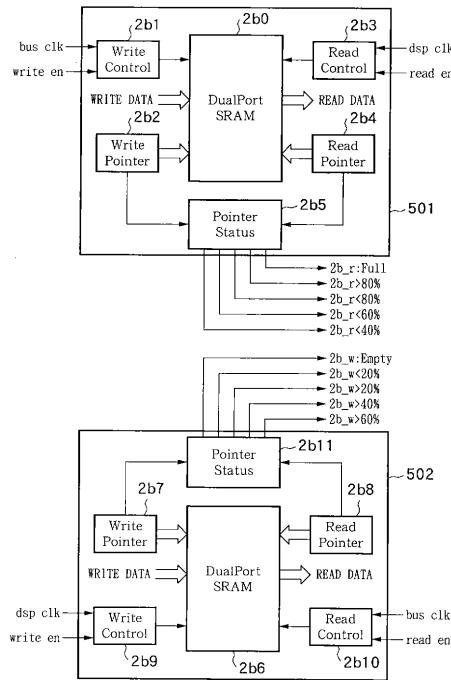

FIFO2 b は図5に示すように、バスインターフェース回路2 a からDSP2 c 方向のFIFO501と逆向きのFIFO502の組み合わせとして実現される。

#### 【0055】

バスインターフェース回路2 a からDSP2 c 方向のFIFO501は、同期型デュアルポートSRAM2 b 0、書き込み制御回路2 b 1、書き込みアドレス生成(ポインタ生成)回路2 b 2、読み出し制御回路2 b 3、読み出しアドレス生成(ポインタ生成)回路2 b 4 およびポインタステータス生成回路2 b 5 よりなる。

#### 【0056】

一方DSP2 c からバスインターフェース回路2 a 向きのFIFO502は、同期型デュアルポートSRAM2 b 6、書き込みアドレス生成(ポインタ生成)回路2 b 7、読み出しアドレス生成(ポインタ生成)回路2 b 8、書き込み制御回路2 b 9、読み出し制御回路2 b 10 およびポインタステータス生成回路2 b 11 よりなる。

#### 【0057】

同期型デュアルポートSRAM2 b 0 は例えば、128(WORD)×8(BIT)のデュアルポートSRAMであり、バスインターフェース回路2 a よりの書き込み有効信号write\_enが入力されると、バスクロックbus\_ckに同期してバス転送データ

10

20

30

40

50

であるW R I T E D A T Aが書き込みアドレス生成(ポインタ生成)回路2 b 2の生成するアドレスに書き込まれる。

#### 【0058】

データ書き込み後、書き込みポインタはインクリメントされる。読み出し動作は、D S P 2 cからの読み出し有効信号r e a d e nが入力されるとD S Pクロックd s p c l kに同期して読み出しアドレス生成(ポインタ生成)回路2 b 4の生成するポインタの示すアドレスからR E A D D A T Aを出力するのでこれを読み出す。読み出し後読み出しポインタはインクリメントされる。ポインタステータス回路2 b 5は書き込みポインタと読み出しポインタの差の絶対値を演算することにより、F I F O 2 bのステータスを出力する。例えば、差の絶対値が1 2 8の場合はF I F O 2 bが空であることを示すので、2 b \_ r : F u l l信号を出力し、差の絶対値がF I F O容量1 2 8の2 0 %以下の場合はF I F O 2 bの有効データがF I F O容量の8 0 %以上であることを示すので2 b \_ r > 8 0 %信号を出力する。同様に、F I F O 2 bの有効データが8 0 %から6 0 %の間の場合は2 b \_ r < 6 0 %信号を出力し、6 0 %から4 0 %の間の場合は2 b \_ r < 4 0 %信号を出力し、4 0 %以下の場合は2 b \_ r < 4 0 %信号を出力する。10

#### 【0059】

同期型デュアルポートS R A M 2 b 6は、例えば1 2 8 ( W O R D ) × 8 ( B I T )のデュアルポートS R A Mであり、D S P 2 cからの書き込み有効信号w r i t e e nが入力されるとD S PクロックD S P c l kに同期してバス転送データであるW R I T E D A T Aが書き込みアドレス生成(ポインタ生成)回路2 b 7の生成するアドレスに書き込まれる。データ書き込み後、書き込みポインタはインクリメントされる。読み出し動作は、バスインターフェース回路2 aからの読み出し有効信号r e a d e nが入力されるとバスクロックb u s c l kに同期して読み出しアドレス生成(ポインタ生成)回路2 b 8の生成するポインタの示すアドレスからR E A D D A T Aを出力するのでこれを読み出す。読み出し後読み出しポインタはインクリメントされる。ポインタステータス回路2 b 1 1は書き込みポインタと読み出しポインタの差の絶対値を演算することにより、F I F O 2 bのステータスを出力する。例えば、差の絶対値が0の場合はF I F O 2 bが空であることを示すので2 b \_ w : E m p t y信号を出力し、差の絶対値がF I F O容量1 2 8の8 0 %以上の場合はF I F O 2 bの有効データがF I F O容量の2 0 %以下であることを示すので2 b \_ w < 2 0 %信号を出力する。同様に、F I F O 2 bの有効データが2 0 %から4 0 %の間の場合は2 b \_ w > 2 0 %信号を出力し、4 0 %から6 0 %の間の場合は2 b \_ w > 4 0 %信号を出力し、6 0 %以上の場合は2 b \_ w > 6 0 %信号を出力する。20

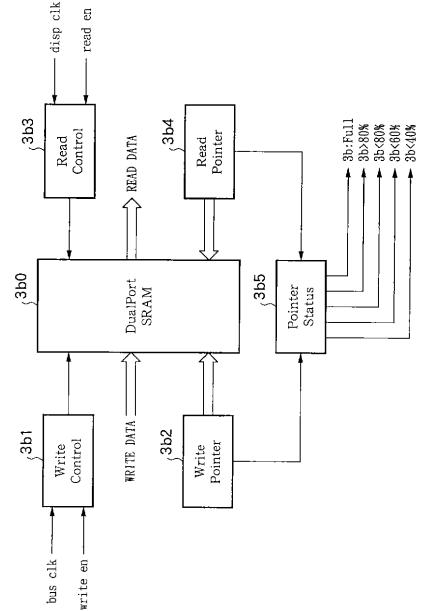

#### 【0060】

F I F O 3 bは図6に示すように、同期型デュアルポートS R A M 3 b 0、書き込み制御回路3 b 1、書き込みアドレス生成(ポインタ生成)回路3 b 2、読み出し制御回路3 b 3、読み出しアドレス生成(ポインタ生成)回路3 b 4およびポインタステータス生成回路3 b 5よりなる。同期型デュアルポートS R A M 3 b 0は例えば1 2 8 ( W O R D ) × 8 ( B I T )のデュアルポートS R A Mであり、バスインターフェース回路3 aよりの書き込み有効信号w r i t e e nが入力されるとバスクロックb u s c l kに同期してバス転送データであるW R I T E D A T Aが書き込みアドレス生成(ポインタ生成)回路3 b 2の生成するアドレスに書き込まれる。データ書き込み後、書き込みポインタはインクリメントされる。読み出し動作は、読み出し回路3 cからの読み出し有効信号r e a d e nが入力されると表示クロックd i s p c l kに同期して読み出しアドレス生成(ポインタ生成)回路3 b 4の生成するポインタの示すアドレスからR E A D D A T Aを出力するのでこれを読み出す。読み出し後読み出しポインタはインクリメントされる。ポインタステータス回路3 b 5は書き込みポインタと読み出しポインタの差の絶対値を演算することにより、F I F O 3 bのステータスを出力する。例えば、差の絶対値が1 2 8の場合はF I F O 3 bが空であることを示すので3 b : F u l l信号を出力し、差の絶対値がF I F O容量1 2 8の2 0 %以下の場合はF I F O 3 bの有効データがF I F O容量40

の 80 %以上であることを示すので 3 b > 80 % 信号を出力する。同様に、FIFO3 b の有効データが 80 %から 60 %の間の場合は 3 b < 60 % 信号を出力し、60 %から 40 %の間の場合は 3 b < 60 % 信号を出力し、40 %以下の場合は 3 b < 40 % 信号を出力する。

#### 【0061】

FIFOステータス 1 b 及び 2 b\_w は夫々の FIFO 内の有効データが少ないほどバスの転送能力に余裕があることを示している。一方 FIFOステータス 2 b\_r 及び 3 b は空き容量がある限りデータを先読みするため、夫々の FIFO が FULL に近いほどバスの転送能力に余裕があることを示す。

#### 【0062】

次に、夫々の FIFO のポインタステータス信号に応じて夫々のバスインターフェース回路が出力する転送長信号がどのように生成されるかを、バスインターフェース回路 2 a を例にとって説明する。

#### 【0063】

まずライト転送については、2 b\_w ステータスが Emp\_ty である間はデータ転送は始まらない。2 b\_w ステータスが示す FIFO 2 b のステータスが Emp\_ty でなくなると、2 b\_w < 20 % ステータスがアサートされる。バス要求および転送長生成部 2 a 1 はバス要求信号 206 をアサートし、バス許可信号 207 を受け取ったならば転送長信号 208 として "000001" すなわち転送長 = 1 を出力する。2 b\_w > 20 % ステータスがアサートされた場合は転送長 = 2、2 b\_w > 40 % ステータスがアサートされた場合は転送長 = 4、2 b\_w > 60 % ステータスがアサートされた場合は転送長 = 8 を出力する。すなわち、書き込みのための FIFO 2 b の空き容量が減少するに伴って、転送長が大きくなるように調整する。このようにすることで、FIFO 2 b に多くのデータが蓄積したときほど早くデータを出力することができる。

#### 【0064】

一方、リード転送では、2 b\_r ステータスが FULL である間はデータ転送は始まらない。FULL でなくなると 2 b\_r > 80 % ステータスがアサートされる。バス要求および転送長生成部 2 a 1 はバス要求信号 206 をアサートし、バス許可信号 207 を受け取ったならば転送長信号 208 として "000001" すなわち転送長 = 1 を出力する。2 b\_r < 80 % ステータスがアサートされた場合は転送長 = 2、2 b\_r < 60 % ステータスがアサートされた場合は転送長 = 4、2 b\_r < 40 % ステータスがアサートされた場合は転送長 = 8 を出力する。すなわち、読み出しのための FIFO 2 b の空き容量が減少するに伴って、転送長が大きくなるように調整する。このようにすることで、FIFO 2 b の空き容量の減少を抑えることができる。

#### 【0065】

以上で述べた FIFO 2 b ステータスと転送長の対応をまとめて図 7 に示す。

#### 【0066】

バスインターフェース回路 1 c、3 a に関しても全く同様に FIFO ポインタステータス信号と転送長信号 208 の対応付けが可能である。よって、FIFO ステータス信号 1 b と転送長との対応を図 8 に、FIFO ステータス信号 3 b と転送長との対応を図 9 に示す。

#### 【0067】

なお、図 7, 8, 9 に示した FIFO ポインタステータス信号 202 と転送長信号 208 の対応付けのテーブルは ROM 19 に格納され、この ROM 19 に格納されたテーブルを参照して、上述の転送長の調整を行う。なお、このテーブルを搭載し、転送長信号 208 を生成するユニットを 1 チップ化した場合、このチップを画像取り込みコントローラ 1、信号処理プロセッサ 2、表示コントローラ 3、メモリコントローラ 4 に共通に搭載しても良い。

#### 【0068】

更に、ポインタステータス信号と転送長の対応をプログラムにより CPU 5 が設定する

10

20

30

40

50

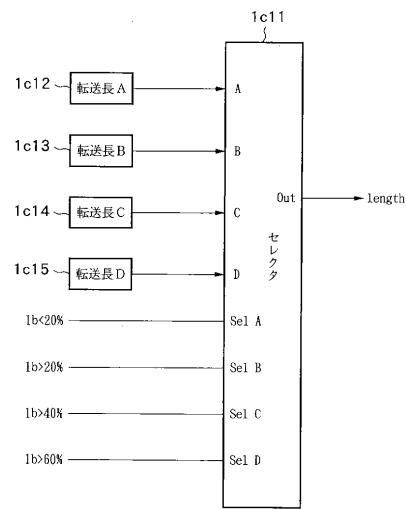

構成にすることも可能である。この場合にポインターステータス信号と転送長の対応付けを行うハードウェアの構成をバスインターフェース回路 1c を例にとって図 10 を用いて説明する。

#### 【0069】

セレクタ 1c11 はセレクト信号 SelA, SelB, SelC, SelD の状態に基づいて各々 6 ビットの入力 A, B, C, D のいずれかを選択して 6 ビットの Out 出力ポートに出力する。セレクト信号と選択される出力との対応を図 11 に示す。4 つの入力は 4 つの 6 ビットレジスタ 1c12, 1c13, 1c14, 1c15 にそれぞれ接続されている。これらの 6 ビットレジスタにはそれぞれのポインターステータスに対応する転送長が格納されており、その値は CPU5 からの不図示の制御信号により変更が可能となっている。

10 例えれば、図 8 に示すような対応関係を実現するためには 1c12 (転送長 A) に "000001" を格納し、1c13 (転送長 B) に "000010" を格納し、1c14 (転送長 C) に "000100" を格納し、1c15 (転送長 D) に "001000" を格納しておけばよい。なお、セレクタ 1c11 の出力はバス要求および転送長生成部 1c1 の length 出力に接続される。

#### 【0070】

一般に動作モードによって、各バスマスターの要求するデータ転送レートやリアルタイムデータ転送の必要性が様々に異なる。上記のような構成を用いることにより、様々な動作モードにおける各バスマスターのデータ転送レートを柔軟に設定することができる。

#### 【0071】

例えば EVF モードでは、常に表示が乱れてはならないので表示コントローラ 3 はリアルタイムデータ転送を要求する。また、画像取り込みコントローラ 1 についても、少なくとも 1 フレーム分のデータを連続して取り込む必要がある。したがって表示コントローラと取り込みコントローラの転送長は図 8 および図 9 に示すような設定にする。一方、画像処理コントローラ 2 は表示のこま落しを許す場合には必ずしもリアルタイムデータ転送を必要としない。したがって、例えば全ての転送長を FIFO ステータスに関わらず 2 に設定する。

#### 【0072】

撮影モードにおいては、画像取り込みコントローラは少なくとも 1 フレーム分のデータを連続して取り込む必要があるので、転送長は図 8 に示すような設定にする。一方、画像処理コントローラ 2 は取り込みが途中であっても画像処理を開始できるので、画像取り込みコントローラ 1 のデータ転送を妨げないように全ての転送長を FIFO ステータスに関わらず 4 に設定する。この際、表示コントローラ 3 のデータ転送は行われないので、EVF モードにおける転送長よりも大きな値が設定可能である。

30

#### 【0073】

表示モードにおいては、表示コントローラ 3 は常に表示が乱さないようにリアルタイムデータ転送を要求するため、転送長は図 9 に示すような設定にする。一方、画像処理コントローラ 2 は表示コントローラ 3 のデータ転送を妨げないように全ての転送長を FIFO ステータスに関わらず 4 に設定する。この場合も、画像取り込みコントローラ 1 のデータ転送は行われないので、EVF モードにおける転送長よりも大きな値が設定可能である。テレビ電話モードの設定は EVF モードと同様である、すなわち表示コントローラ 3 は常に表示が乱れてはならないのでリアルタイムデータ転送を要求する。また、画像取り込みコントローラ 1 についても、少なくとも 1 フレーム分のデータを連続して取り込む必要がある。したがって取り込みコントローラ 1 と表示コントローラ 3 の転送長は夫々図 8、図 9 に示すような設定にする。

40

#### 【0074】

一方、画像処理コントローラ 2 は電話回線のデータ転送能力以上のデータレートでのデータ処理を必要としない。したがって、例えば全ての転送長を FIFO ステータスに関わらず 2 に設定する。

#### 【0075】

10

20

30

40

50

上記の構成によれば、様々な動作モードにおける画像処理に必要なデータ転送をリアルタイム性を損なうことなく行うことができる。また、リアルタイム性を保つために不必要に動作周波数を高めたりデータ幅を拡大する必要がないため、消費電力を低減化することができる。

### 【0076】

#### 【発明の効果】

以上に述べたように本発明によれば、記憶メモリに格納されているデータ量に応じて、データ転送で転送するデータの転送長を調整することができる。

#### 【図面の簡単な説明】

【図1】本発明の実施形態における携帯型テレビ電話の内部構成を示すブロック図である 10

。

【図2】バスインターフェース回路2aの内部構成を示す図である。

【図3】バスインターフェース回路2aのメインバスMB上の信号のタイミングを示したタイミング図である。

【図4】 FIFO1bの内部構成例を示すブロック図である。

【図5】 FIFO2bの内部構成例を示すブロック図である。

【図6】 FIFO3bの内部構成例を示すブロック図である。

【図7】 FIFO2bステータスと転送長の対応をまとめた図である。

【図8】 FIFOステータス信号1bと転送長との対応を示す図である。

【図9】 FIFOステータス信号3bと転送長との対応を示す図である。

【図10】ポインターステータス信号と転送長との対応をプログラムにより設定する場合、ポインターステータス信号と転送長の対応付けを行うハードウェアの構成を示す図である。 20

【図11】セレクト信号と選択される出力との対応を示す図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

| FIFOステータス   | 転送長           |

|-------------|---------------|

| 2b_w:Empty  | 転送なし          |

| 2b_w < 20 % | 転送長 = 1 (ライト) |

| 2b_w > 20 % | 転送長 = 2 (ライト) |

| 2b_w > 40 % | 転送長 = 4 (ライト) |

| 2b_w > 60 % | 転送長 = 8 (ライト) |

| 2b_r:Full   | 転送なし          |

| 2b_r > 80 % | 転送長 = 1 (リード) |

| 2b_r < 80 % | 転送長 = 2 (リード) |

| 2b_r < 60 % | 転送長 = 4 (リード) |

| 2b_r < 40 % | 転送長 = 8 (リード) |

| FIFOステータス | 転送長     |

|-----------|---------|

| 1b:Empty  | 転送なし    |

| 1b < 20 % | 転送長 = 1 |

| 1b > 20 % | 転送長 = 2 |

| 1b > 40 % | 転送長 = 4 |

| 1b > 60 % | 転送長 = 8 |

【図9】

【図10】

| FIFOステータス | 転送長     |

|-----------|---------|

| 3b:Full   | 転送なし    |

| 3b > 80 % | 転送長 = 1 |

| 3b < 80 % | 転送長 = 2 |

| 3b < 60 % | 転送長 = 4 |

| 3b < 40 % | 転送長 = 8 |

【図 1 1】

| SelA | SelB | SelC | SelD | Out |

|------|------|------|------|-----|

| x    | x    | x    | 1    | D   |

| x    | x    | 1    | 0    | C   |

| x    | 1    | 0    | 0    | B   |

| 1    | 0    | 0    | 0    | A   |

| 0    | 0    | 0    | 0    | 0   |

---

フロントページの続き

(72)発明者 白神 慎二

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 梅景 篤

(56)参考文献 特開平7-178972(JP,A)

特開平3-100751(JP,A)

特開2000-125163(JP,A)

特開2000-156849(JP,A)

特開平6-110653(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 13/38

G06F 13/20-13/378

H04N 5/765

H04N 5/907

H04N 7/14