(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

15 December 2011 (15.12.2011)

(10) International Publication Number

WO 2011/156277 A3

(51) International Patent Classification:

G06F 1/26 (2006.01)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

PCT/US2011/039292

(22) International Filing Date:

6 June 2011 (06.06.2011)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/352,378 7 June 2010 (07.06.2010) US

61/352,369 7 June 2010 (07.06.2010) US

61/352,349 7 June 2010 (07.06.2010) US

61/352,359 7 June 2010 (07.06.2010) US

13/153,224 3 June 2011 (03.06.2011) US

(72) Inventors; and

(71) Applicants : SULLIVAN, Jason, A. [US/US]; 299 South Main Street, Suite 1300, Salt Lake City, Utah 84111 (US). ABDOUCH, Charles [US/US]; 299 South Main Street, Suite 1300, Salt Lake City, Utah 84111 (US).

(74) Agent: TINGEY, David, B.; Kirton & McConkie, 60 East South Temple, Suite 1800, Salt Lake City, Utah 84111 (US).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

[Continued on next page]

(54) Title: MINITURIZATION TECHNIQUES, SYSTEMS, AND APPARATUS RELATING TO POWER SUPPLIES, MEMORY, INTERCONNECTIONS, AND LEDS

(57) Abstract: Miniaturization techniques, systems, and apparatus relating to power supplies, memory, interconnections, and LEDS are described herein. Specifically, some aspects of the invention relate to techniques for miniaturization of power supplies. Other aspects relate to systems and methods for optimizing memory performance in a computer device or system. Still further, some aspects relate to systems and methods for miniaturizing and optimizing memory layout on a circuit board. Other aspects relate to systems and methods for attaching an integrated circuit, which comprises an array of pins, to a circuit board through the use of an adaptor that comprises a BGA, and which is configured to electrically and physically attach to the circuit board. Furthermore, some aspects relate to systems and methods for achieving activation of at least one multi-color LED, such as a bi-color or tri-color LED, using multiple electrical ground outputs or signals intended to activate only a single unicolor LED.

FIG. 1

WO 2011/156277 A3

---

(88) Date of publication of the international search report:

26 April 2012

**MINITURIZATION TECHNIQUES,

SYSTEMS, AND APPARATUS RELATING

TO POWER SUPPLIES, MEMORY,

INTERCONNECTIONS, AND LEDS**

5

**CROSS-REFERENCE TO RELATED APPLICATIONS**

This application claims the benefit of United States Patent Application No. 13/153,224, filed June 3, 2011, entitled “MINITURIZATION TECHNIQUES, SYSTEMS, AND APPARATUS RELATING TO POWER SUPPLIES, MEMORY, 10 INTERCONNECTIONS, AND LEDS” and to the following provisional applications: United States Provisional Application No. 61/352,359, filed June 7, 2010, entitled “MINITURIZED POWER SUPPLY;” United States Provisional Application No. 61/352,349, filed June 7, 2010, entitled “SYSTEMS AND METHODS FOR OPTIMIZING MEMORY PERFORMANCE;” United States Provisional Application 15 No. 61/352,369, filed June 7, 2010, entitled “SYSTEMS AND METHODS FOR PROVIDING A PIN GRID ARRAY TO BALL GRID ARRAY ADAPTOR;” and United States Provisional Application No. 61/352,378, filed June 7, 2010, entitled “SYSTEMS AND METHODS FOR ACTIVATING MULTI-COLOR LIGHT 20 EMITTING DIODES; the entire disclosures of all of the applications are hereby incorporated by reference.

**BACKGROUND OF THE INVENTION**

**1. Field of the Invention**

The present invention relates to electronic systems and components. In particular, the present invention relates to miniaturization techniques, systems, and 25 apparatus relating to power supplies, memory, interconnections, and LEDs.

**2. Background and Related Art**

Electronic systems, such as computers, are becoming increasingly ubiquitous. For instance, electronic systems, including computers, are constantly being utilized in an ever growing number of divergent fields of technologies and to perform an ever 30 increasing variety of functions. As the use and function of electronic systems increases, there is often a need to improve some of the systems' components. In particular, as computers and other electronic systems become more complicated, advanced, and compact, there is a need to miniaturize and otherwise improve several of the system components. In this regard, power supplies, memory, integrated circuit

connectors, and light emitting diode (“LED”) circuitry are some examples of computer components that can be miniaturized or otherwise improved.

With respect to power supplies, electronic systems often include a power supply which converts raw input power (*e.g.*, alternating current supplied from 5 commercial mains) into necessary internal supply voltages (*e.g.*, direct current voltages such as 5 volts, 3.3. volts, etc.) within the systems. Many electronic systems also include components (*e.g.*, integrated circuits) that require multiple voltages and require special sequencing of the voltages during ramp up and ramp down.

While power supplies are usually a necessary part of an electronic system, 10 they can provide many undesirable aspects. For example, noise generated by a power supply can be conducted or radiated to susceptible components of the electronic systems—causing improper operation of the susceptible components. Accordingly, a difficult aspect of power supply design is to ensure that undesired noise is not emitted from the power supply. On the other hand, modern power supplies often include 15 complex monitoring circuitry that can be susceptible to noise. Noise ingress into the monitoring circuitry can result in improper operation, such as erroneous shut down, poor regulation, and other undesirable effects. Power supplies also tend to be bulky, and can use up valuable, limited space on printed circuit boards.

Due to the difficulty in meeting the myriad design requirements, many system 20 designers are reluctant to change established power supply design approaches. For example, some component suppliers provide a reference power supply design that purports to meet the requirements of their components. Even though the reference power supply design may not be optimized for cost or circuit board area, designers often simply adopt the component supplier’s reference design. While the supplier’s 25 reference design may provide a suboptimal solution from a cost, area, or performance perspective, using such a design can help to reduce risk to the overall project.

As electronic systems become increasingly smaller, however, the cost and space consumed by power supplies has become a greater percentage of the overall 30 electronic system. This is particularly pronounced in very small computer systems, which target a variety of different markets. For example, for a computer system which is designed to fit in a volume on the order of about 65 cubic centimeters (about 25 cubic inches), a power supply design which requires in excess of 10 square centimeters (about 4 square inches) of board area may not be practical. Accordingly,

it has been recognized by the present inventors that miniaturization of power supply systems would be beneficial.

Regarding memory, most (if not all) of today's computer systems include memory, which is typically held on a memory module. A memory module typically 5 includes a circuit board, such as a printed circuit board ("PCB"), with a number of integrated circuits ("ICs"), or chips, coupled to one or more surfaces of the circuit board. The chips are memory devices to provide memory resources to a computing platform such, as a personal computer ("PC"). One type of memory module uses dynamic random access memory ("DRAM") chips in a dual data rate ("DDR") 10 manner. These modules arrange the DRAM chips as a single in-line memory module ("SIMM") or as a dual in-line memory module ("DIMM" or "DIMMS").

The circuit board (or PCB) can have a connector along one edge that is compatible with a socket connector on a motherboard for integration of the memory module into the computing platform. One type of technology (known as a DDR2 15 DIMM) has an electrical connector with 240 pins.

DIMMS include multiple DRAM chips coupled to the PCB. For example, some implementations include eight DRAM chips coupled to the PCB. These DRAM chips include a set of terminating resistors that prevent data corruption and line loss in the transmission lines. The combination of the DIMMS and the terminating resistors 20 has a large footprint on the PCB, which limits the miniaturization of the system.

Cross talk and line loss further limit memory layout configurations by requiring memory modules to be located away from the memory controller (which is occasionally integrated into the processor) in order to allow lines between the memory controller and the memory modules to fan out or otherwise have sufficient space 25 between adjacent lines. Generally, the physical size of the DRAMs (typically greater than 12.5 mm), combined with the DIMM sockets, decoupling capacitors, and termination resistors, require that the memory modules and the memory controller are located more than 6.4 centimeters (2.5 inches) away from each other.

Turning now to integrated circuit connectors, central processing units ("CPU") 30 can be electrically and physically connected to a circuit board in a variety of manners. Indeed, in some cases, a CPU is soldered directly to a circuit board. In other cases, however, a CPU is attached to a circuit board through the use of a CPU socket.

Where a CPU is attached to the circuit board through the use of a CPU socket, the CPU socket can function in a variety of manners. Indeed, in some instances, the CPU socket comprises a plastic housing that has a latch and a metal contact for each of the pins on the CPU. In such instances, when a CPU with a pin grid array (“PGA”) 5 is inserted in the CPU socket and the latch is closed, the metal contacts are forced into contact with the pins of the CPU’s PGA. In other instances in which the CPU comprises a land grid array (“LGA”) and the CPU socket comprises a corresponding PGA, the CPU is placed in the CPU socket and the latch is closed over the CPU to secure it in place and to force the LGA into contact with corresponding PGA within 10 the CPU socket.

While conventional methods for attaching CPUs to circuit boards have been found to be useful, such methods are not necessarily without their shortcomings. For instance, where a CPU is directly attached to a circuit board, the CPU (which is often the most expensive component of the circuit board) can be very difficult to remove 15 from the circuit board. Accordingly, when such a CPU fails or when a user desires to upgrade such a CPU, it can be more convenient to replace the entire circuit board than to remove the CPU and replace it with another.

In another example, where a CPU attaches to a first side of a circuit board through the use of a PGA that extends from the CPU or a CPU socket and penetrates 20 the circuit board, the CPU can prevent components from being placed on opposite side of the board—directly behind the CPU. In other words, a CPU that attaches to a circuit board through the use of a PGA that penetrates the board, can require more real estate than would be required if the CPU were strictly attached to one side of the board.

25 In still another example, in some cases in which a CPU attaches to a circuit board through the use of a conventional CPU socket, the CPU socket, with its lever, tends to have a larger footprint than does the CPU. Accordingly, in this example, the CPU socket can take up excessive real estate on a circuit board, which can be detrimental in applications in which space is a limiting factor.

30 In yet another example, in some cases in which a CPU is attached to a circuit board through the use of a CPU socket, the metal contacts in the CPU socket can be damaged during their production process, during insertion of the CPU’s PGA, or as the circuit board is exposed to shock and vibration during use. As a result of this

damage, the CPU socket can lose its electrical connection with one or more of the CPU's pins and, thereby, causes the CPU to fail or to function improperly.

Turning now to LEDs, LEDs are an increasingly ubiquitous semiconductor light source capable of emitting high intensity light across the visible wavelength (or color) spectrum, as well as ultraviolet and infrared wavelengths. LEDs can present many advantages over traditional light sources, including lower energy consumption, longer lifetime, improved robustness, smaller size, faster switching, and greater durability and reliability. As a result, LEDs are frequently used as indicator lamps in electronic devices and are increasingly used in numerous diverse applications, including replacing traditional light sources in aviation lighting, automotive lighting, traffic signal illumination, text and/or video display illumination, sensor illumination, sign or other visual and/or informational display device illumination, ambient or direct lighting, and operable printhead lighting.

In electronics, a diode is one of the simplest sorts of semiconductor devices, comprising a two-terminal electronic component that conducts electric current in only one direction (called the diode's "forward" direction). Generally speaking, a semiconductor is a material with a varying ability to conduct electrical current. Most LEDs consist of a chip of semiconducting material "doped" with impurities to create a p-n junction with electrodes or leads on each end. A p-n junction generally consists of a single semiconductor having a region on one side that contains negative charge carriers (electrons), resulting in an n-type region, while a region on the other side contains positive charge carriers (holes), resulting in a p-type region. The term "junction" refers to the boundary interface where the two regions of the semiconductor meet. In operation, current flows in a direction from the p-type side (the anode) to the n-type side (the cathode). The wavelength of light emitted, and therefore its color, depends on the band gap energy of the material forming the p-n junction.

The basic LED circuit is an electric power circuit used to power a LED. It consists of a voltage source powering two components connected in series: a current limiting resistor and an LED. The LED circuit is powered and produces light when a positive voltage and a negative voltage source are connected to the appropriate LED electrodes or leads, respectively.

Ethernet is a widely-installed local area network (“LAN”) technology defining a number of wiring and signaling standards for the physical layer of the open systems interconnect (“OSI”) networking model as well as a common addressing format and media access control at the data link layer. Using an Ethernet interface, many 5 computer devices can communicate with one another over a LAN. Ethernet is standardized as IEEE 802.3.

As mentioned above, LEDs are commonly used as indicator lamps in electronic devices. For example, Ethernet ports are commonly equipped with two indicator LEDs. One LED often indicates activity (“ACT signal”) on the Ethernet 10 port while the other LED indicates the speed (Speed signal) of the Ethernet link (*e.g.*, 10Mb, 100 Mb, or 1000 Mb and so forth). Generally, the indicator LED denoting activity will blink when the port is active (*i.e.*, transmitting or receiving). The LED indicating speed, on the other hand, will often be either lit or turned off depending on the speed of the Ethernet link (*e.g.*, off for 10 Mb or lit for 100 Mb and so forth).

15 Generally, an Ethernet port is connected to and driven by an Ethernet chip located on a PCB. The chip can also operate the Ethernet’s indicator LEDs. Some Ethernet chips, such as some of the chips manufactured by Broadcom Corp., have internal circuitry incorporated into the chip during the manufacturing process which automatically generates a speed signal based on the speed of the Ethernet link and 20 activates the appropriate Ethernet port indicator LED accordingly. Often bi-color LEDs are used in connection with such chips. Bi-color LEDs are actually two different LEDs housed in one case or lens. They consist of two semiconductor dies connected to the same two leads anti-parallel to each other. Current flow in one direction produces one color, and current flow in the opposite direction produces the 25 other color. The combination of chips having such internal circuitry and bi-color LEDs permit the automated visual indication of a range of three discrete speeds. For example, at 10Mb the bi-color LED is off, at 100 Mb the bi-color LED is one color, such as green, and at 1000 Mb the bi-color LED is the alternate color, such as amber.

Thus, while techniques currently exist relating to the use of power supplies, 30 memory, IC connectors, and LED circuitry, challenges still exist. Accordingly, it would be an improvement in the art to augment or even replace current techniques with other techniques.

SUMMARY OF THE INVENTION

The present invention relates to electronic systems and components. In particular, the present invention relates to miniaturization techniques, systems, and apparatus relating to power supplies, memory, interconnections, and LEDs.

5 Some aspects of the invention relate to power supplies. In particular, in some implementations, the invention relates to a miniaturized power supply that includes a PCB (or other circuit board). In such implementations, a first active component is disposed on a first side of the PCB. A second active component is disposed on a second side of the PCB and electrically connected to the first active component. The

10 first side and the second side are different from each other.

In some implementations, a method of making a miniaturized power supply is provided. The method includes obtaining a design schematic for the power supply, wherein the design schematic comprises a plurality of electronic components. Some of the electronic components can be active components. Additional operations in the

15 method are selecting positions on a first side of a PCB for first ones of the active components and selecting positions on a second side of the PCB for second ones of the active components. The first side and the second side are different from each other. The positions of the second ones of the plurality of active components are selected with respect to the positions of the first ones of the plurality of active

20 components. The method can also include defining interconnections between the plurality of electronic components, wherein the interconnections comprise traces and vias to form a PCB layout.

Some aspects of the invention relate to memory. In particular, some aspects of the present invention relate to systems and methods for optimizing memory

25 performance in a computer device or system. Still further, some aspects of the present invention relate to systems and methods for miniaturizing and optimizing memory layout on a circuit board.

Implementations of the present systems and methods can enable enhanced performance and miniaturized layout of memory and memory controllers.

30 Accordingly, in some aspects, a circuit board is provided having a top and a bottom side. A memory controller is coupled to the circuit board along with a plurality of memory devices. To improve functionality and decrease footprint, the memory devices are soldered (or otherwise electrically connected) directly to the circuit board

on both the top and bottom sides of the board. In this manner, each of the memory devices can be located within about 6.4 centimeters (about 2.5 inches) of the memory controller. Soldering can also provide a more robust connection than a DIMM socket, which can create a point of failure in the system. Thus, the removal of the DIMM can 5 free up PCB real estate and increase system performance.

In some implementations, the representative system further includes a system clock that is electronically coupled to each of the plurality of memory devices via a clock line. Each of the plurality of electronic coupling clock lines is approximately of equal lengths to provide simultaneous clock signals to the memory devices. 10 Additionally, in some implementations, each of the plurality of memory devices is electronically coupled to the memory controller via a separate data line. This direct connection eliminates the need for terminating resistors on the data lines, further reducing the footprint of the memory system. Furthermore, in some implementations, a representative system includes an address line that is in electronic communication 15 with the memory controller and each of the plurality of memory devices.

In some implementations, a representative method provides soldering a plurality of memory devices directly to a PCB. In some instances, this includes locating each of the plurality of memory devices within about 6.4 centimeters (about 2.5 inches) from the memory controller. This includes disposing at least one of the 20 memory devices on a top surface of the PCB, while disposing at least one of the memory devices on a bottom surface. In some implementations, one half of the memory devices are disposed on the top surface of the PCB and the other half on the bottom surface of the PCB. In some implementations, a representative method further provides electronically coupling each of the memory devices to the memory controller 25 via a separate data line. In some implementations, a representative method further provides electronically coupling each of the memory devices to a system clock via a plurality of equidistant clock lines.

In some implementations, the present systems and methods enable both higher memory performance levels while miniaturizing PCB layout and substantially 30 reducing the cost of the system. These results are enabled in part by the replacement of DIMM connector sockets with the soldering of memory devices directly to the PCB, on opposing sides of the PCB. The absence of the DIMM connector sockets can free up PCB real estate and avoid the need for DIMM terminating resistors, which

in turn can free up additional real estate. Furthermore, in some instances, it is functionally advantageous and less expensive to include the maximum system memory fixedly on the PCB rather than providing memory scalability using DIMM sockets. Soldered memory devices can have enhanced impact and shock resistance

5 over DIMM sockets, thus reducing the likelihood of device failure while providing a lock-tight system that can be incorporated into a more rugged environment. Furthermore, the removal of scalability and the reduction of line loss can allow system designers to optimize memory device performance, pushing memory devices to perform at their highest levels, and increasing system performance without

10 increasing costs.

Turning now to IC connectors, some aspects of the current invention relate to IC interconnections. In particular, some aspect of the present invention relates to systems and methods for attaching an IC device to a circuit board. In particular, some aspects of the present invention relate to systems and methods for attaching an IC,

15 which comprises an array of pins, to a circuit board through the use of an adaptor, which comprises a ball grid array, and which is configured to electrically and physically attach to the circuit board.

Generally, the adaptor, or interposer, includes a rigid, insulative casing having an array of machined pin sockets disposed therein. While the casing can have any

20 suitable characteristic, in some cases, the casing has a substantially planar first surface and a substantially planar second surface, which is disposed opposite to the first surface. In some cases, one or more of the pin sockets in the array of machined pin sockets have a pin receptacle that opens at the casing's first surface and a solder ball that is disposed at the casing's second surface. Additionally, in some cases, each of

25 the plurality of sockets includes two or more internal, resilient finger contacts. Thus, the adaptor is configured to electrically connect an integrated circuit having a PGA to a circuit board via a ball grid array.

While the methods and processes of the present invention have proven to be particularly useful in the area of physically and electrically connecting CPUs to PCBs,

30 those skilled in the art can appreciate that the methods and processes can be used in a variety of different applications and in a variety of different areas of manufacture to attach any other suitable integrated circuit comprising a PGA to a circuit board. Indeed, according to some non-limiting examples, the described systems and methods

electrically and physically connect a semi-conductor package, a memory chip, a processor chip, a northbridge, a southbridge, and/or any other suitable IC to a corresponding circuit board.

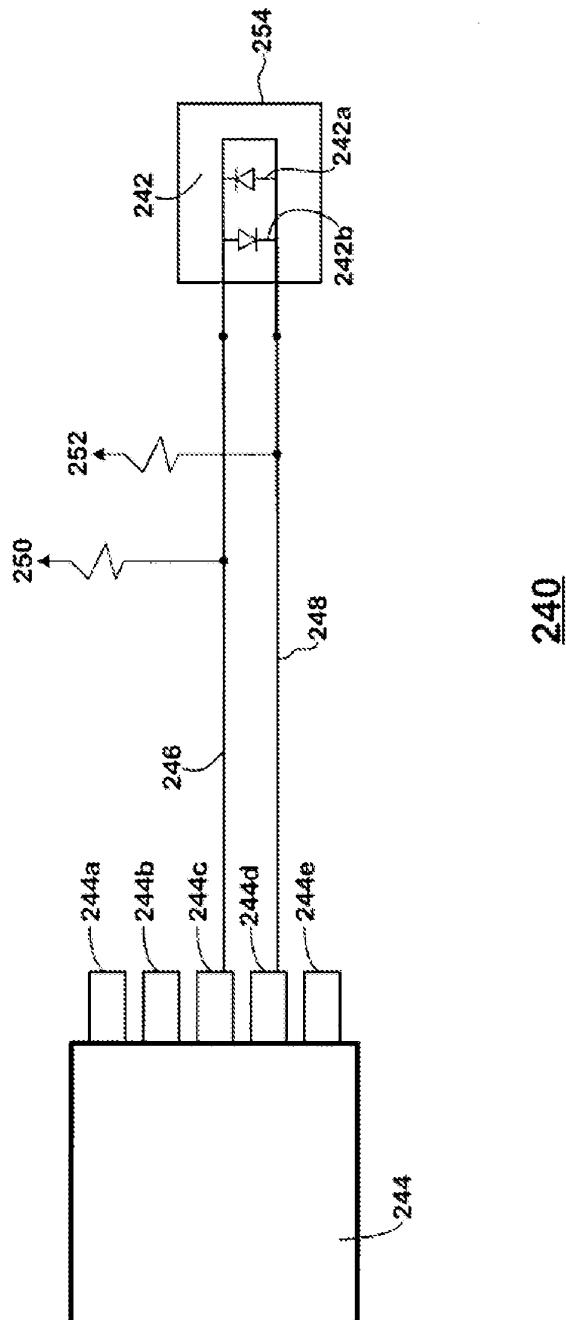

Finally, some aspects of the invention relate to LED circuitry. Specifically, 5 some aspects relate to systems and methods for achieving activation of at least one multi-color LED, such as a bi-color or tri-color LED, using multiple electrical ground outputs or signals intended to activate only a single unicolor LED.

Implementation of such aspects of the present invention takes place in association with at least one multi-color LED, such as a bi-color or tri-color LED, 10 being electrically connected such that the LED is capable of emitting each discrete color dictated by the LED's component materials and construction as a visual representation or indication of user desired information or a user defined status. In at least one implementation, a bi-color LED electrical indicator system includes a bi-color LED. In such implementations, the LED is capable of emitting two colors: a 15 first color in accordance with current flow in one direction and a second color in accordance with current flow in the opposite direction. As with all diodes, the bi-color LED includes two leads or electrical terminals. However, one lead behaves as the cathode while the other lead behaves as the anode relative to the appropriate diode when the current flows in one direction. When the current is reversed though, the 20 former cathode lead behaves as the anode and the former anode lead behaves as the cathode relative to the other diode.

In addition to the bi-color LED, some implementations of the foregoing system include a first electrical line providing an electrical ground output. In such implementations, the output is ordinarily intended to be connected to and to activate 25 only a single independent unicolor LED. However, the first electrical line is connected to one lead of the bi-color LED and to a pull-up resistor. The pull-up resistor provides current flow in the appropriate direction for activating one of the bi-color LED's two possible colors.

Some implementations of the invention that relate to LED circuitry also 30 include a second electrical line providing an electrical ground output similar to the first output discussed above. In like manner, the second electrical line is connected to the other lead of the bi-color LED and to another pull-up resistor. The pull-up resistor provides current flow in the appropriate direction for activating the other of the bi-

color LED's two possible colors. In this manner, the bi-color LED's two discrete colors can both be activated at separate times according to the appropriate electrical output or signal.

While the methods, processes, systems, and apparatus of the present invention 5 have proven to be particularly useful in the area of personal computing enterprises, those skilled in the art will appreciate that the methods, processes, system, and apparatus of the present invention can be used in a variety of different applications and in a variety of different areas of manufacture to yield customizable enterprises, including enterprises for any industry utilizing electronic systems. Examples of such 10 industries include, but are not limited to, automotive industries, avionic industries, hydraulic control industries, auto/video control industries, telecommunications industries, medical industries, special application industries, and electronic consumer device industries. Accordingly, the methods, processes, systems, and apparatus of the present invention can provide improvements (such as massive computing power) to 15 markets, including markets that have traditionally been untapped by current computer and electronic techniques.

These and other features and advantages of the present invention will be set forth or will become more fully apparent in the description that follows and in the appended claims. The features and advantages may be realized and obtained by 20 means of the instruments and combinations particularly pointed out in the appended claims. Furthermore, the features and advantages of the invention may be learned by the practice of the invention or will be obvious from the description, as set forth hereinafter.

#### BRIEF DESCRIPTION OF THE DRAWINGS

25 In order that the manner in which the above recited and other features and advantages of the present invention are obtained, a more particular description of the invention will be rendered by reference to specific embodiments thereof, which are illustrated in the appended drawings. Understanding that the drawings depict only typical embodiments of the present invention and are not, therefore, to be considered 30 as limiting the scope of the invention, the present invention will be described and explained with additional specificity and detail through the use of the accompanying drawings in which:

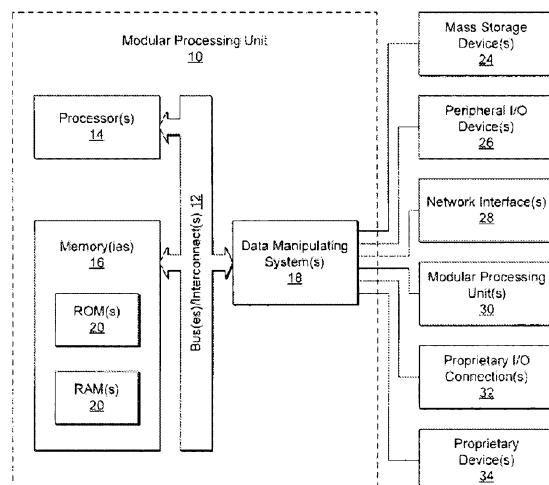

Figure 1 illustrates a representative system that provides a suitable operating environment for use of the present invention;

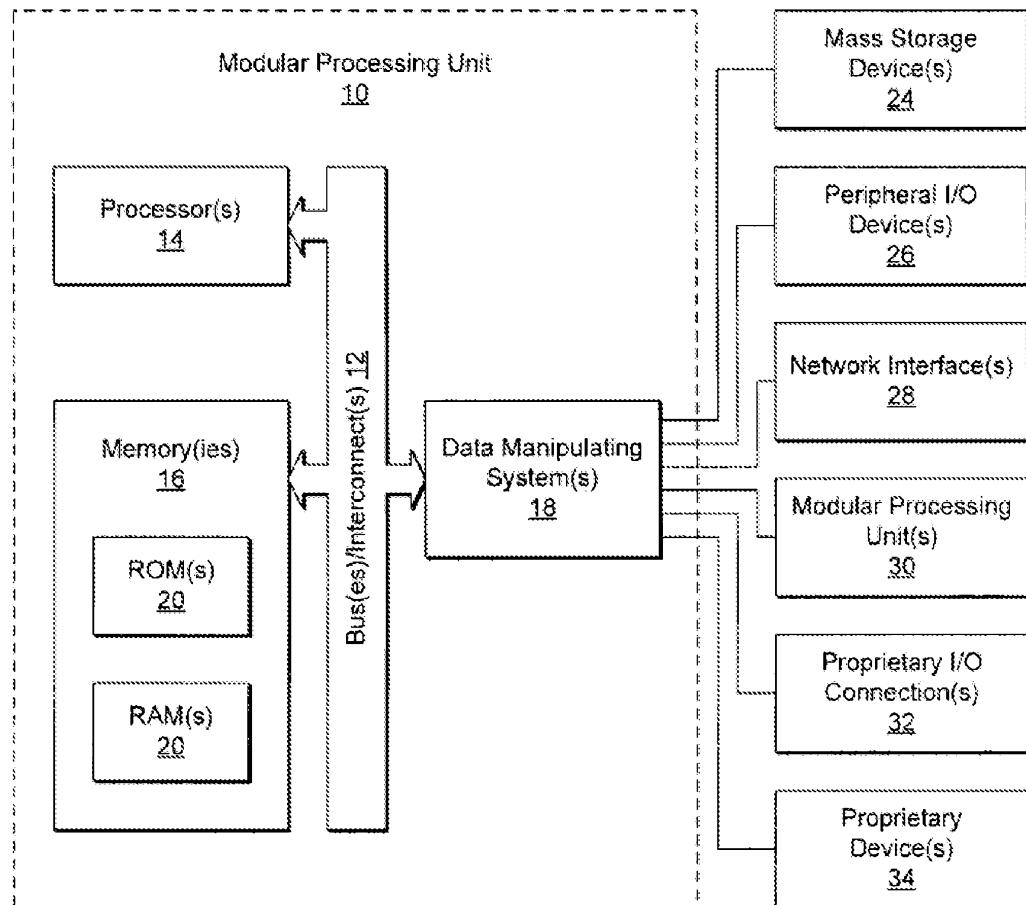

Figure 2 illustrates a representative networked system configuration that may be used in association with embodiments of the present invention;

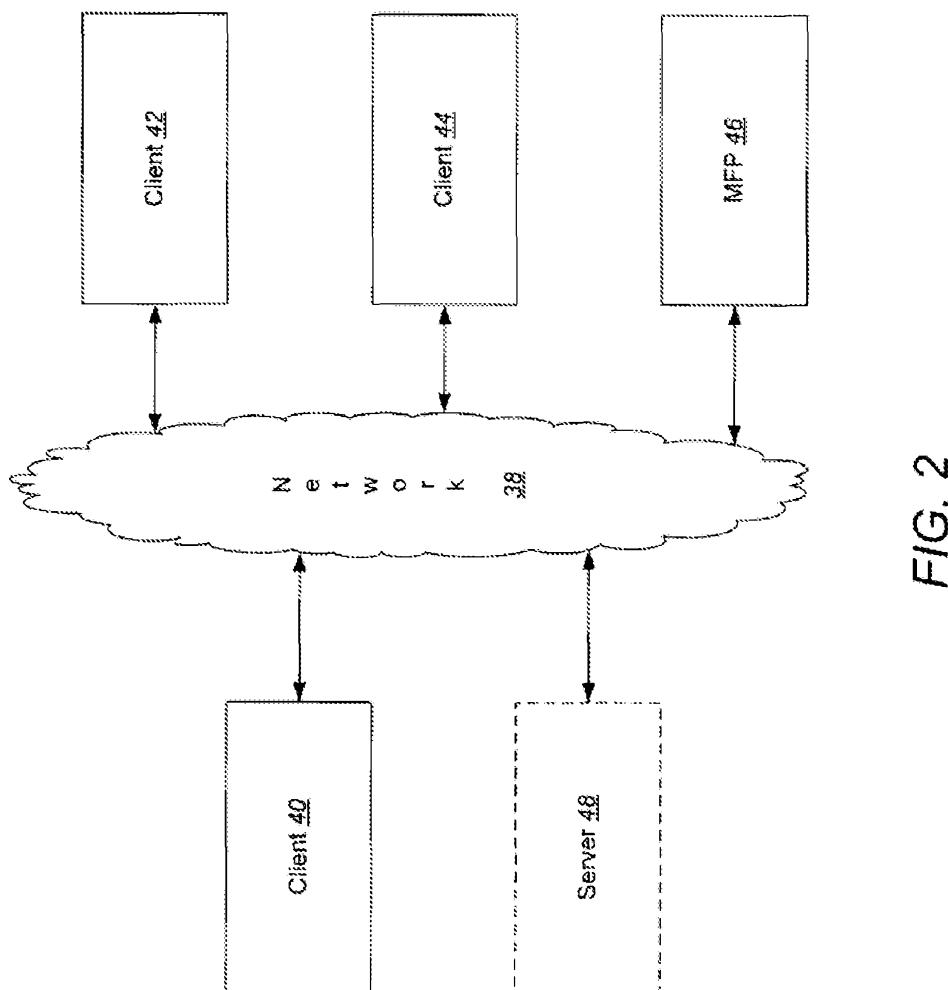

5 Figure 3 illustrates a side view of a representative embodiment of power supply with components mounted on one side of a PCB;

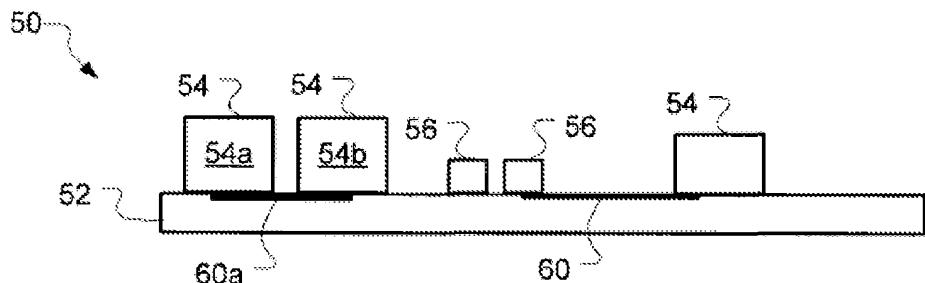

Figure 4 illustrates a side view of a representative embodiment of the miniaturized power supply with active components mounted on both sides of a PCB;

10 Figure 5 illustrates a side view of a shielded trace, which can be used in the miniaturized power supply according to a representative embodiment of the present invention;

Figure 6 illustrates a top view of a PCB design for the miniaturized power supply according to a representative embodiment of the present invention;

15 Figure 7 illustrates a flow chart of a method for making the miniaturized power supply according to a representative embodiment of the present invention;

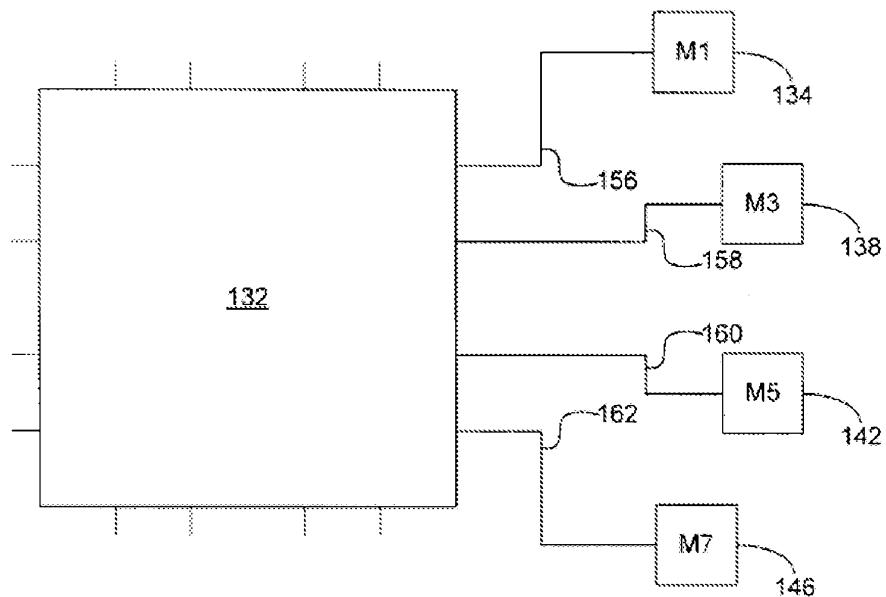

Figure 8 illustrates a perspective view of a memory system layout according to a representative embodiment of the present invention;

Figure 9 illustrates a top view of the memory system and system data lines according to a representative embodiment of the present invention;

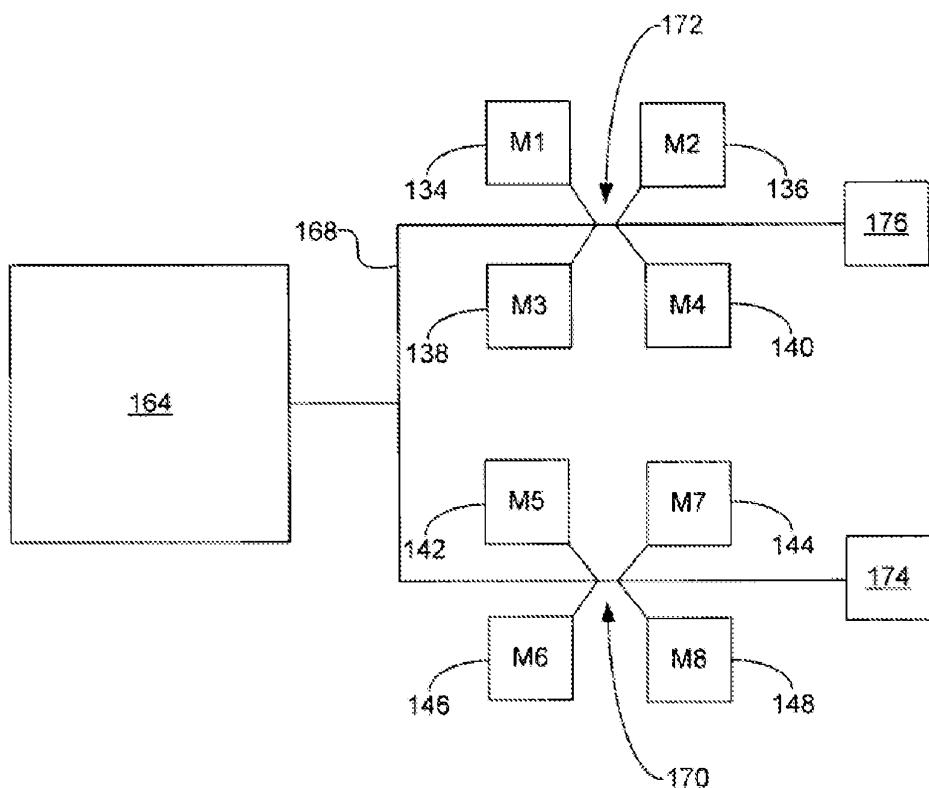

20 Figure 10 illustrates a block diagram view of system clock lines according to a representative embodiment of the present invention;

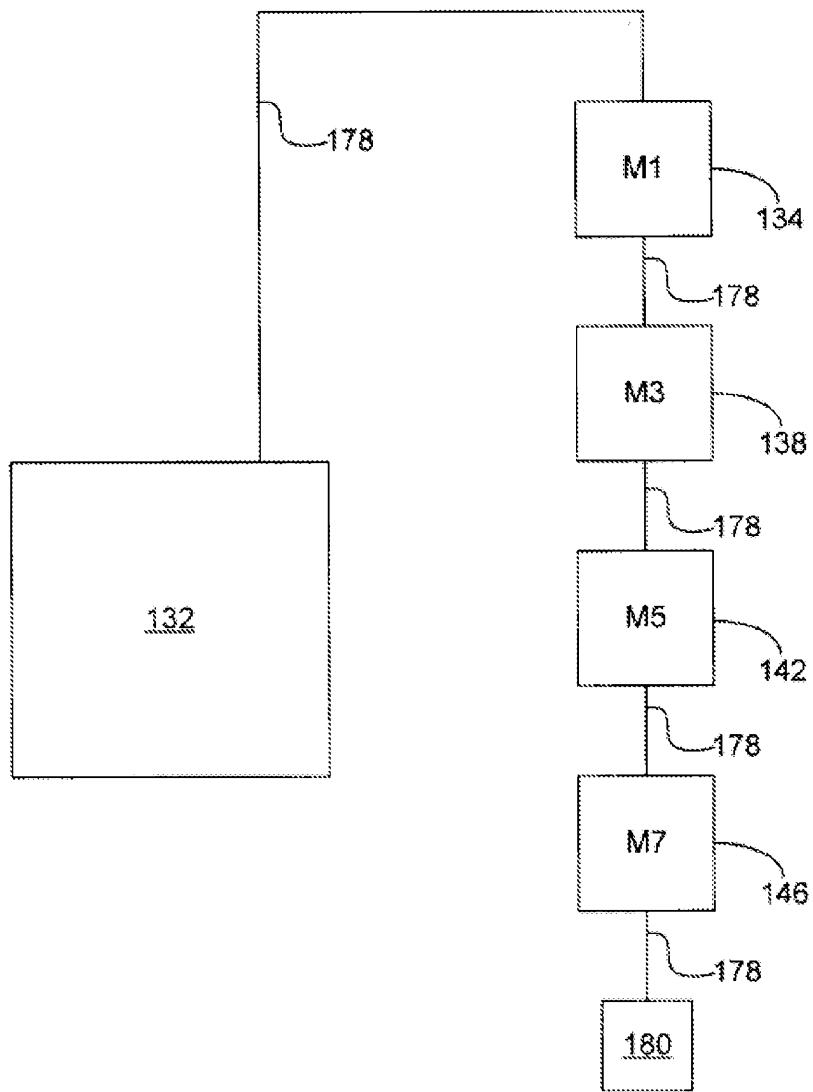

Figure 11 illustrates a top view of a memory system layout and a system address line according to a representative embodiment of the present invention;

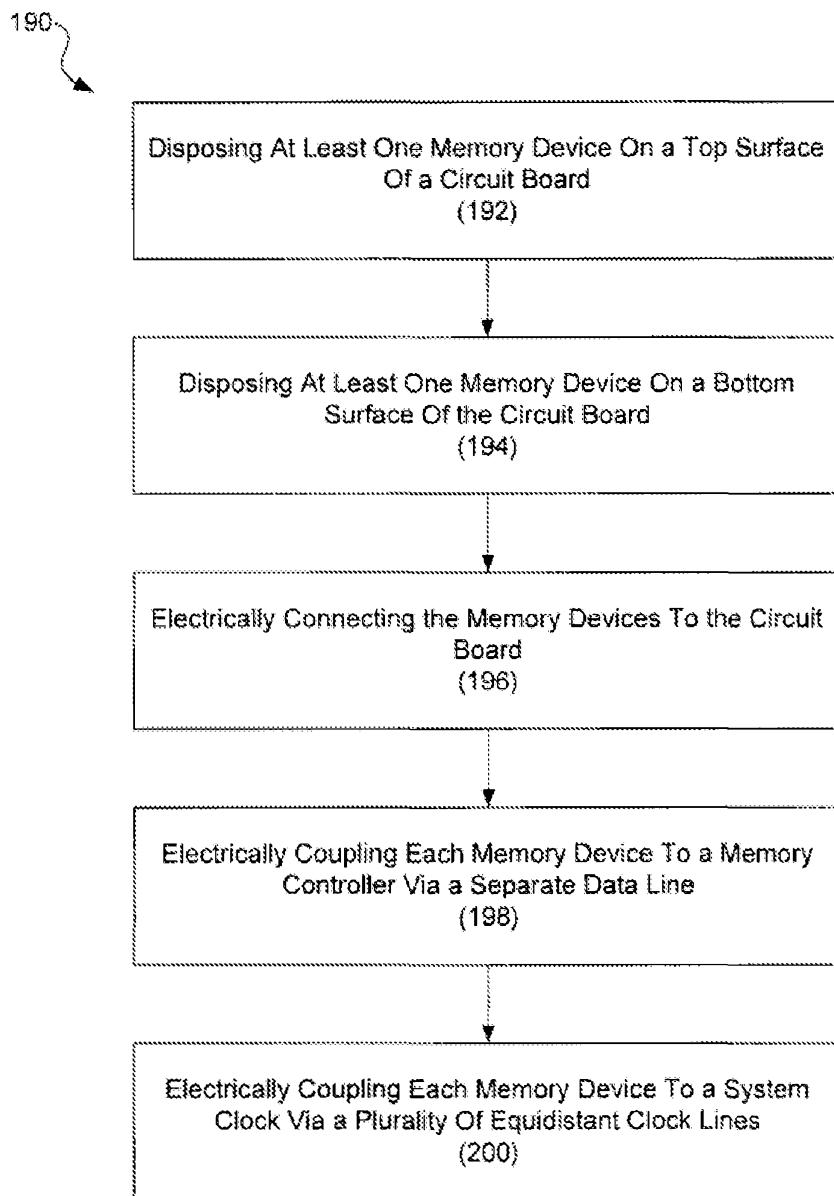

25 Figure 12 illustrates a block diagram of a method for optimizing memory performance according to a representative embodiment of the present invention;

Figure 13 illustrates a top-schematic view of a pin grid array to ball grid array adaptor according to a representative embodiment of the invention;

Figure 14 illustrates a side-schematic view of the pin grid array to ball grid array adaptor according to a representative embodiment of the invention;

30 Figure 15 illustrates a cross-sectional view of a machined pin socket disposed in a casing according to a representative embodiment of the invention;

Figure 16 illustrates top view of the pin grid array to ball grid array adaptor according to a representative embodiment of the invention, wherein the adaptor is disposed on a PCB;

Figure 17 illustrates a representative bi-color LED electrical circuit according

5 to a representative embodiment of the invention; and

Figure 18 illustrates a schematic view of a representative embodiment of PCB layout for some embodiments of an LED circuit.

### **DETAILED DESCRIPTION OF THE INVENTION**

The present invention relates to electronic systems and components. In

10 particular, the present invention relates to miniaturization techniques, systems, and apparatus relating to power supplies, memory, interconnections, and LEDs.

In the disclosure and in the claims, the term array may refer to any suitable arrangement that comprises a plurality of adjacent rows and a plurality of adjacent columns.

15 The following disclosure of the present invention is grouped into five subheadings, namely “Representative Operating Environment,” “Power Supplies,” “Memory,” “IC Connectors,” and “Logic Chip/LED Connection.” The utilization of the subheadings is for convenience of the reader only and is not to be construed as limiting in any sense.

20 *Representative Operating Environment*

Figure 1 and the corresponding discussion are intended to provide a general description of a suitable operating environment in accordance with embodiments of the present invention. As will be further discussed below, embodiments of the present invention embrace the use of one or more dynamically modular processing units in a

25 variety of customizable enterprise configurations, including in a networked or combination configuration, as will be discussed below.

Embodiments of the present invention embrace one or more computer readable media, wherein each medium may be configured to include or includes thereon data or computer executable instructions for manipulating data. The

30 computer executable instructions include data structures, objects, programs, routines, or other program modules that may be accessed by one or more processors, such as one associated with a general-purpose modular processing unit capable of performing

various different functions or one associated with a special-purpose modular processing unit capable of performing a limited number of functions.

Computer executable instructions cause the one or more processors of the enterprise to perform a particular function or group of functions and are examples of 5 program code means for implementing steps for methods of processing. Furthermore, a particular sequence of the executable instructions provides an example of corresponding acts that may be used to implement such steps.

Examples of computer readable media include random-access memory (“RAM”), read-only memory (“ROM”), programmable read-only memory 10 (“PROM”), erasable programmable read-only memory (“EPROM”), electrically erasable programmable read-only memory (“EEPROM”), compact disk read-only memory (“CD-ROM”), any solid state storage device (e.g., flash memory, smart media, etc.), or any other device or component that is capable of providing data or executable instructions that may be accessed by a processing unit.

15 With reference to Figure 1, a representative enterprise includes modular processing unit 10, which may be used as a general-purpose or special-purpose processing unit. For example, modular processing unit 10 may be employed alone or with one or more similar modular processing units as a personal computer, a notebook computer, a personal digital assistant (“PDA”) or other hand-held device, a 20 workstation, a minicomputer, a mainframe, a supercomputer, a multi-processor system, a network computer, a processor-based consumer device, a cellular phone, a smart appliance or device, a control system, or the like. Using multiple processing units in the same enterprise provides increased processing capabilities. For example, each processing unit of an enterprise can be dedicated to a particular task or can 25 jointly participate in distributed processing.

In Figure 1, the modular processing unit 10 includes one or more buses and/or interconnects 12, which may be configured to connect various components thereof and enables data to be exchanged between two or more components. The bus(es)/interconnect(s) 12 may include one of a variety of bus structures, including a 30 memory bus, a peripheral bus, or a local bus that uses any of a variety of bus architectures. Typical components connected by the bus(es)/interconnect(s) 12 include one or more processors 14 and one or more memories 16. Other components may be selectively connected to the bus(es)/interconnect(s) 12 through the use of

logic, one or more systems, one or more subsystems and/or one or more I/O interfaces, hereafter referred to as “data manipulating system(s) 18.” Moreover, other components may be externally connected to the bus(es)/interconnect(s) 12 through the use of logic, one or more systems, one or more subsystems and/or one or more I/O interfaces, and/or may function as logic, one or more systems, one or more subsystems, and/or one or more I/O interfaces, such as one or more modular processing unit(s) 30 and/or proprietary device(s) 34. Examples of I/O interfaces include one or more mass storage device interfaces, one or more input interfaces, one or more output interfaces, and the like. Accordingly, embodiments of the present invention embrace the ability to use one or more I/O interfaces and/or the ability to change the usability of a product based on the logic or other data manipulating system employed.

The logic may be tied to an interface, part of a system, subsystem and/or be used to perform a specific task. Accordingly, the logic or other data manipulating system may allow, for example, for IEEE1394 (firewire), wherein the logic or other data manipulating system is an I/O interface. Alternatively or additionally, logic or another data manipulating system may be used that allows a modular processing unit to be tied into another external system or subsystem. For example, an external system or subsystem that may or may not include a special I/O connection. Alternatively or additionally, logic or another data manipulating system may be used wherein no external I/O is associated with the logic. Embodiments of the present invention also embrace the use of specialty logic, such as for ECUs for vehicles, hydraulic control systems, etc. and/or logic that informs a processor how to control a specific piece of hardware. Moreover, those skilled in the art will appreciate that embodiments of the present invention embrace a plethora of different systems and/or configurations that utilize logic, systems, subsystems and/or I/O interfaces.

As provided above, embodiments of the present invention embrace the ability to use one or more I/O interfaces and/or the ability to change the usability of a product based on the logic or other data manipulating system employed. For example, where a modular processing unit is part of a personal computing system that includes one or more I/O interfaces and logic designed for use as a desktop computer, the logic or other data manipulating system can be changed to include flash memory or logic to perform audio encoding for a music station that wants to take analog audio via two

standard RCAs and broadcast them to an IP address. Accordingly, the modular processing unit may be part of a system that is used as an appliance rather than a computer system due to a modification made to the data manipulating system(s) (e.g., logic, system, subsystem, I/O interface(s), etc.) on the back plane of the modular processing unit. Thus, a modification of the data manipulating system(s) on the back plane can change the application of the modular processing unit. Accordingly, embodiments of the present invention embrace very adaptable modular processing units.

As provided above, processing unit 10 includes one or more processors 14, such as a central processor (or CPU) and optionally one or more other processors designed to perform a particular function or task. It is typically the processor 14 that executes the instructions provided on computer readable media, such as on the memory(ies) 16, a magnetic hard disk, a removable magnetic disk, a magnetic cassette, an optical disk, or from a communication connection, which may also be viewed as a computer readable medium.

The memory(ies) 16 includes one or more computer readable media that may be configured to include or includes thereon data or instructions for manipulating data, and may be accessed by the processor(s) 14 through the bus(es)/interconnect(s) 12. The memory(ies) 16 may include, for example, ROM(s) 20, used to permanently store information, and/or RAM(s) 22, used to temporarily store information. The ROM(s) 20 may include a basic input/output system (“BIOS”) having one or more routines that are used to establish communication, such as during start-up of the modular processing unit 10. During operation, the RAM(s) 22 may include one or more program modules, such as one or more operating systems, application programs, and/or program data.

As illustrated, at least some embodiments of the present invention embrace a non-peripheral encasement, which provides a more robust processing unit that enables use of the unit in a variety of different applications. In Figure 1, one or more mass storage device interfaces (illustrated as data manipulating system(s) 18) may be used to connect one or more mass storage devices 24 to the bus(es)/interconnect(s) 12. The mass storage devices 24 are peripheral to the modular processing unit 10 and allow the modular processing unit 10 to retain large amounts of data. Examples of mass

storage devices include hard disk drives, magnetic disk drives, tape drives and optical disk drives.

A mass storage device 24 may read from and/or write to a magnetic hard disk, a removable magnetic disk, a magnetic cassette, an optical disk, or another computer readable medium. The mass storage devices 24 and their corresponding computer readable media provide nonvolatile storage of data and/or executable instructions that may include one or more program modules, such as an operating system, one or more application programs, other program modules, or program data. Such executable instructions are examples of program code means for implementing steps for methods disclosed herein.

The data manipulating system(s) 18 may be employed to enable data and/or instructions to be exchanged with the modular processing unit 10 through one or more corresponding peripheral I/O devices 26. Examples of the peripheral I/O devices 26 include input devices such as a keyboard and/or alternate input devices, such as a mouse, trackball, light pen, stylus, or other pointing device, a microphone, a joystick, a game pad, a satellite dish, a scanner, a camcorder, a digital camera, a sensor, and the like, and/or output devices such as a monitor or display screen, a speaker, a printer, a control system, and the like. Similarly, examples of the data manipulating system(s) 18 coupled with specialized logic that may be used to connect the peripheral I/O devices 26 to the bus(es)/interconnect(s) 12 include a serial port, a parallel port, a game port, a universal serial bus (“USB”), a firewire (IEEE 1394), a wireless receiver, a video adapter, an audio adapter, a parallel port, a wireless transmitter, any parallel or serialized I/O peripherals or another interface.

The data manipulating system(s) 18 enable an exchange of information across one or more network interfaces 28. Examples of the network interfaces 28 include a connection that enables information to be exchanged between processing units, a network adapter for connection to a local area network (“LAN”) or a modem, a wireless link, or another adapter for connection to a wide area network (“WAN”), such as the Internet. The network interface 28 may be incorporated with or peripheral to modular processing unit 10, and may be associated with a LAN, a wireless network, a WAN and/or any connection between processing units.

The data manipulating system(s) 18 enable the modular processing unit 10 to exchange information with one or more other local or remote modular processing

units 30 or computer devices. A connection between modular processing unit 10 and modular processing unit 30 may include hardwired and/or wireless links. Accordingly, embodiments of the present invention embrace direct bus-to-bus connections. This enables the creation of a large bus system. It also eliminates 5 hacking as currently known due to direct bus-to-bus connections of an enterprise. Furthermore, the data manipulating system(s) 18 enable the modular processing unit 10 to exchange information with one or more proprietary I/O connections 32 and/or one or more proprietary devices 34.

Program modules or portions thereof that are accessible to the processing unit 10 may be stored in a remote memory storage device. Furthermore, in a networked system or combined configuration, the modular processing unit 10 may participate in a distributed computing environment where functions or tasks are performed by a plurality of processing units. Alternatively, each processing unit of a combined configuration/enterprise may be dedicated to a particular task. Thus, for example, one 15 processing unit of an enterprise may be dedicated to video data, thereby replacing a traditional video card, and provides increased processing capabilities for performing such tasks over traditional techniques.

While those skilled in the art will appreciate that the invention may be practiced in networked computing environments with many types of computer system 20 configurations, Figure 2 represents an embodiment of the present invention in a networked environment that includes clients connected to a server via a network. While Figure 2 illustrates an embodiment that includes two clients connected to the network, alternative embodiments include one client connected to a network or many clients connected to a network. Moreover, embodiments in accordance with the 25 present invention also include a multitude of clients throughout the world connected to a network, where the network is a wide area network, such as the Internet.

#### Power Supplies

Some aspects of the present invention relate to power supplies. As introduced above, many conventional power supply designs are often not very space efficient. A 30 power supply can include a plurality of electronic components, which can include active components and passive components. Active components include parts, such as switches (e.g., bipolar transistors, field effect transistors, etc,), regulators, comparators, and the like. Passive components include parts, such as resistors,

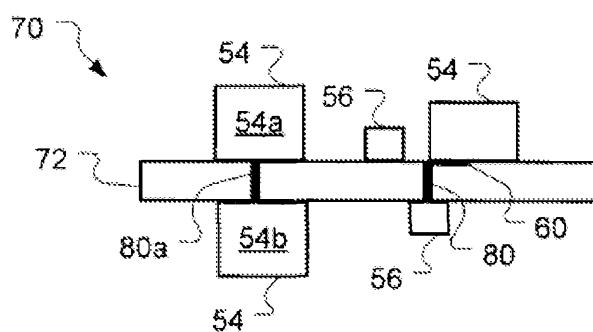

inductors, capacitors, and the like. Electronic components are typically mounted on a PCB, and interconnected through traces on the PCB. Typically, the electronic components are mounted on only one side of the PCB. This is viewed as desirable in the electronics industry for cost considerations. In some instances, passive 5 components (e.g., small capacitors or small resistors) are occasionally placed on the opposite side of the board. For example, Figure 3 illustrates a power supply, shown generally at 50, where a PCB 52 has a plurality of components 54 and 56 mounted on one side 58 of the PCB (or other circuit board). The components can include active components 54 and passive components 56. Interconnections between the 10 components are provided by traces 60 (e.g., conductive material attached to or deposited on a non-conductive substrate). The PCB can be, for example, a multilayer PCB providing multiple layers of traces (not shown).

A miniaturized power supply, in accordance with some embodiments of the invention, is shown in Figure 4. In contrast to a conventional power supply, the 15 miniaturized power supply 70 can include active components 54 placed on both sides of a PCB 72. Accordingly, some active components can be placed directly opposite each other in some embodiments. In other embodiments, active components can be opposite each other and partly overlapping. Passive components 56 can also be placed on one or both sides of the PCB. Traces 60 and vias 80 can interconnect the 20 components.

Several benefits can be obtained by mounting components on both sides of the PCB 72. For example, interconnection distances between components can be reduced. For example, considering a first component 54a and a second component 54b, these components cannot be placed substantially closer than shown in Figure 3 25 when on the same side of the PCB. For example, some spacing is typically required between components to allow for component size tolerances and access for a pick and place machine. Thus, trace 60a interconnecting a terminal of the first component to a terminal of the second component must generally have a length equal or greater than the horizontal dimension of the components. For example, to interconnect two 30 components having horizontal lengths of about 0.64 centimeters (about 0.25 inches), the trace must be at least about 0.64 centimeters (about 0.25 inches) in length.

In contrast, when the components 54a, 54b are placed opposite each other on opposite sides of the PCB 72, the trace length can be significantly shorter. For

example, the components can be placed so that the terminals are directly opposite each other, making the trace length essentially the length of the via 80a interconnecting the components to each other (there can be additional length due to, for example, a pad). For a PCB 72 having a thickness of about 0.13 centimeters 5 (about 0.05 inches), the trace length is thus about 0.13 centimeters (about 0.05 inches) in length – a reduction of a factor of about five.

The reduction in trace length provided in some embodiments of the invention can provide multiple benefits. For example, while an ideal electrical interconnection has zero resistance, zero capacitance, and zero inductance, actual traces will exhibit 10 some parasitic resistance, capacitance, and inductance (RLC). While the parasitic RLC of a trace is a function of various parameters (*e.g.*, board thickness, conductive material thickness, dielectric constant of insulating substrate, proximity of other traces, etc.), there is a significant dependence of parasitic RLC on the length of a trace. Generally, the parasitic RLC increases linearly with the length of the trace. 15 Accordingly, by reducing trace length, the parasitic RLC can be reduced, which in turn allows the electrical connections to behave more like ideal (*e.g.*, zero RLC) interconnections. In some cases, the reduced parasitic RLC can require adjustment of the component values. For example, a circuit design may require a certain amount of inductance. In a one-sided design, this required inductance may be provided in part 20 by a component and in part by parasitic inductance of the PCB 52. In the two-sided designed, with the reduced parasitic inductance provided by the PCB 72, the component inductance may therefore be reduced. As another example, in a one-sided design, a component value may be required to compensate for parasitic RLC, and thus the component value may be reduced or the component entirely eliminated in the two- 25 sided design due to the reduced parasitic RLC.

Another benefit of reduced trace length is reduced noise emission and reduced noise susceptibility. An electrical interconnection can emit noise, both through radiated and non-radiated electromagnetic coupling. In general, the amount of noise coupling is increased for longer electrical interconnections. For example, longer 30 traces can have higher mutual capacitance or inductance between each other, providing for higher coupling through electromagnetic fields. Longer traces can also act more effectively as an antenna, emitting or collecting energy from adjacent traces

through propagating electromagnetic waves. Accordingly, by reducing trace length, noise coupling can also be reduced.

In some instances, the trace lengths in the two-sided design can be sufficiently short that shielding that would otherwise be needed can be eliminated. In other cases, 5 the area lost due to shielding can be significantly reduced. For example, Figure 5 illustrates a shielded connection between two components 54 mounted on opposite sides of a PCB 72. The shielded connection comprises a signal conductor 82 electrically connecting the two components and surrounded by a plurality of shield structures 84. The shield structures can include, for example, vias and/or traces which 10 connect to a ground plane. It can be seen that the shield structures are entirely contained within the footprint of the components, and thus do not require any additional PCB area beyond that already covered by the components. Shielded connections can be used for electrical connections which are particularly sensitive to picking up noise and for electrical connections which are particularly prone to 15 emitting noise. While the shielded connection shown in Figure 5 is in the vertical direction (using vias for the signal conductor and shield structures), shielded connections can also be provided in the horizontal direction (using traces for the signal conductor and shield structures), or using combinations of both.

An additional benefit of the shortened trace lengths is the reduced amount of 20 board area consumed by the traces. This area can be used in various beneficial ways. For example, trace widths can be increased. In general, wider trace widths can provide for lower resistance and inductance, in turn providing for higher current handling capability.

The power supply can also make effective use of interconnection planes. For 25 example, an interconnection plane can consist of an essentially continuous plane (*e.g.*, continuous over a defined two-dimensional area extent except for clearance holes) of conductive material disposed on an exterior or interior layer of the PCB 72. For example, a ground plane can be used for connecting ground terminals of two or more components together. As another example, a power plane can be used for connecting 30 power terminals of two or more components together. An interconnection plane can be beneficial because it provides a low resistance and low inductance interconnection between the components tied to the plane. When necessary, holes can

provided in the plan to provide clearance for vias (*e.g.*, for signal interconnections) to pass through the plane without electrically connecting to the plane.

In some instances, it can be beneficial to provide one or more split planes which are interconnected to each other at a single point. For example, Figure 6 5 illustrates a PCB design 90 for an electronic system in which the PCB 92 includes a power supply portion 94 and an operational circuit portion 96. Multiple split plane sections 98, 100, and 102 are provided. The split planes can be, for example, a conductive layer disposed on an exterior or interior layer of the PCB which has cut away or etched portions to define the split planes. The operational circuitry 10 comprises a split plane section 102 which is contiguous underneath the operational circuitry (except for via clearance holes 104). The power supply portion comprises two split plane sections 98 and 100. The plane portions are each connected to each other via single point of connection 106. Use of multiple split planes can be beneficial at keeping noise generated within the power supply confined within the 15 power supply, and for keeping noise sensitive portions of the power supply (*e.g.*, disposed over and under plane 98) isolated from noise generating portions of the power supply (*e.g.*, portions disposed over and under plane 100).

Additional miniaturization of a power supply can be obtained by optimizing the amount and type of capacitors. Capacitors can serve several purposes in a power 20 supply. Capacitors can provide charge storage between cycles of the power supply (*e.g.*, cycles of the alternating current input in a linear supply, or during switching cycles in a switching power supply). Capacitors can also provide energy storage to meet surge current demands (*e.g.*, which occur too fast for a regulator to respond to). Capacitors can also provide for noise filtering (*e.g.*, shunting noise signals to ground). 25 Typically, power supplies are designed with a large amount of capacitance in excess of that required for charge storage under normal operating conditions. This excess capacitance is provided in part, due to the non-ideal response of large capacitors (*e.g.*, equivalent series resistance) which limits the effectiveness of the capacitors.

In contrast, it has been determined by the present inventors that the total 30 capacitance provided can be reduced by using a mixture of capacitor types. For example, a total capacitance requirement can be determined based on the requirements of the operational circuitry supplied by the power supply and the characteristics of the power supply. The total capacitance requirement can then be

partitioned into different types of capacitors. Some small, low equivalent series resistance (ESR) capacitors can be provided. The low ESR capacitors can respond quickly to rapid changes in load, but provide a limited ability to store charge. Use of all low ESR capacitors to provide the total capacitance requirement would be 5 impractical, however, due to the size and cost of the low ESR capacitors. Thus, additional capacitors can be provided which have a higher ESR. The higher ESR capacitors, while responding slower, can respond when the load variation exceeds the capability of the low ESR capacitors. Thus, the total capacitance requirement can be met in part by low ESR capacitors and in part by high ESR capacitors. If desired, the 10 total capacitance requirement can be partitioned into two or more types of capacitors. As a particular example, a total capacitance requirement of 1 Farad can be partitioned into 100 milliFarad of low ESR capacitors, 400 milliFarad of medium ESR capacitors, and 0.5 Farad of high ESR capacitors.

By partitioning the total capacitance requirement in such a manner, the total 15 capacitance can be reduced relative to a conventional design, in turn providing for reduced board area usage. Moreover, it has been observed that the total amount of capacitance required can generally be reduced as compared to a conventional design which uses all medium or high ESR capacitors.

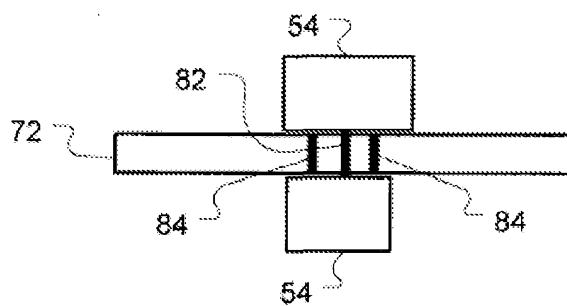

Making a miniaturized power supply can proceed in any suitable manner, 20 including according to the flow chart illustrated in Figure 7. The method 110 can begin at box 112 with obtaining a design schematic for the power supply. For example, the design schematic can be developed by engineers. The design schematic can be, for example, based on a reference design provided by a component manufacturer or can be a customized design.

25 The design schematic can include a parts list defining the components composing the power supply, and a net list defining interconnections between the components. The design schematic can be in an electronic form. The design schematic can be in a form which is usable by computer automatic design (“CAD”) systems, such as an industry standard file format.

30 Boxes 114 and 116 show the method 110 can continue by selecting positions on the first and second sides of the PCB for first and second ones of a plurality of electrical components. The layout of the PCB can be determined using a CAD layout tool. Using the CAD layout tool, positions for the components on a PCB can be

defined. For example, first ones of the electronic components can be positioned on a first side of the PCB and second ones of the electronic components can be positioned on a second side of the PCB. The positions of the second ones of the electronic components can be related to the positions of the first ones of the electronic components as will now be described.

Various aspects can be taken into consideration when positioning the electronic components. Components can be positioned relative to each other to minimize trace lengths. Relative importance of trace lengths can be considered as well, with compromises made to keep critical traces (*e.g.*, traces corresponding to 10 interconnections which are susceptible to noise or highly likely to emit noise) shorter at the expense of making non-critical traces longer. For example, sensing lines tend to be particularly sensitive to noise, and thus can be kept away from other traces or shielded. As a particular example, sense lines can be used by sensing circuitry in the power supply to detect over current and over/under voltage conditions. Noise pickup 15 by the sense lines can result in spurious detections, resulting in undesired shut down of the power supply.

Components can be positioned relative to each other on opposite sides of the board to allow vias to serve multiple purposes. For example, conventional one-sided PCBs often include vias to provide connections between traces on the top side and the 20 bottom side (and, when present, traces on internal layers) of the PCB. In the miniaturized power supply, components can also be positioned on the opposite side of the PCB to allow vias to serve multiple purposes. For example, a via used to connect a trace on the top side to the bottom side can also be used to connect to a part on the bottom side.

25 When positioning parts on the second side relative to the first side, consideration of the position of parts need not exclusively focused on interconnection length. For example, noise susceptible components can be kept away from noise generating components.

When laying out the miniaturized power supply, the selecting of locations can 30 be viewed as a three dimensional positioning task. In other words, the locations of components can be defined in X, Y, and Z dimensions, wherein X and Y correspond to lateral dimensions on the PCB (within the plane defined by the PCB, *e.g.*, “left/right”) and the Z dimension corresponds to a vertical dimension on the PCB

(normal to the plane defined by the PCB, *e.g.*, “up” and “down”). Positions can be defined relative to a reference point on the PCB. This is in contrast to a conventional single sided PCB design which merely positions in X and Y dimensions.

Once the components are positioned, box 118 shows that the interconnections 5 can be defined. For example, the interconnections can include pads (for electrical connections to terminals of the components), traces, and vias. The positions of pads, traces, and vias can be defined relative to the reference point. Routing of interconnections can be performed, for example, using an automated routing tool. A PCB layout, defining the positions of the pads, traces, and vias, can be provided in an 10 electronic form from the CAD system. For example, the PCB layout can be defined in an industry standard format useable for fabrication of PCBs. PCBs can be fabricated according to the PCB layout. As shown at box 120, a power supply can be constructed from the fabricated PCB by mounting and electrically connecting components to the PCB.

15 Miniaturized power supplies in accordance with some embodiments of the present invention provide benefits in reduced area consumption. For example, in some embodiments, PCB area has been reduced from approximately 10.2 square centimeters (approximately 4 square inches) for a conventional single-sided design to approximately 2.5 square centimeters (approximately 1 square inch) or less for a two- 20 sided design.

Surprisingly, additional benefits in improved performance have also been observed in some embodiments. For example, due to the reduced trace lengths and reduced interaction between traces, improved noise performance has been observed. In particular, stability of regulation and output noise of the miniaturized power supply 25 has been observed to be significantly improved as compared to a conventional one-sided PCB design. In general, the improved efficiencies in space and performance can be enough to offset the additional manufacturing (and repair) costs associated with placing active parts on both sides of the PCB.

As will now be appreciated, miniaturized power supplies in accordance with 30 the present disclosure can help to provide more area efficient, higher performance power supplies. Such power supplies can be particularly useful in area constrained applications, such as compact computing systems, embedded computers, laptop computers, and similar applications.

Thus, as discussed herein, at least some aspects of the present invention embrace techniques for miniaturization of power supplies. In particular, at least some aspects of the invention relate miniaturized power supplies which make effective utilization of PCB area.

5

*Memory*

Some aspects of the present invention relate to systems and methods for optimizing memory performance in a computer device or system. Still further, the some aspects of the present invention relate to systems and methods for miniaturizing and optimizing memory layout on a circuit board.

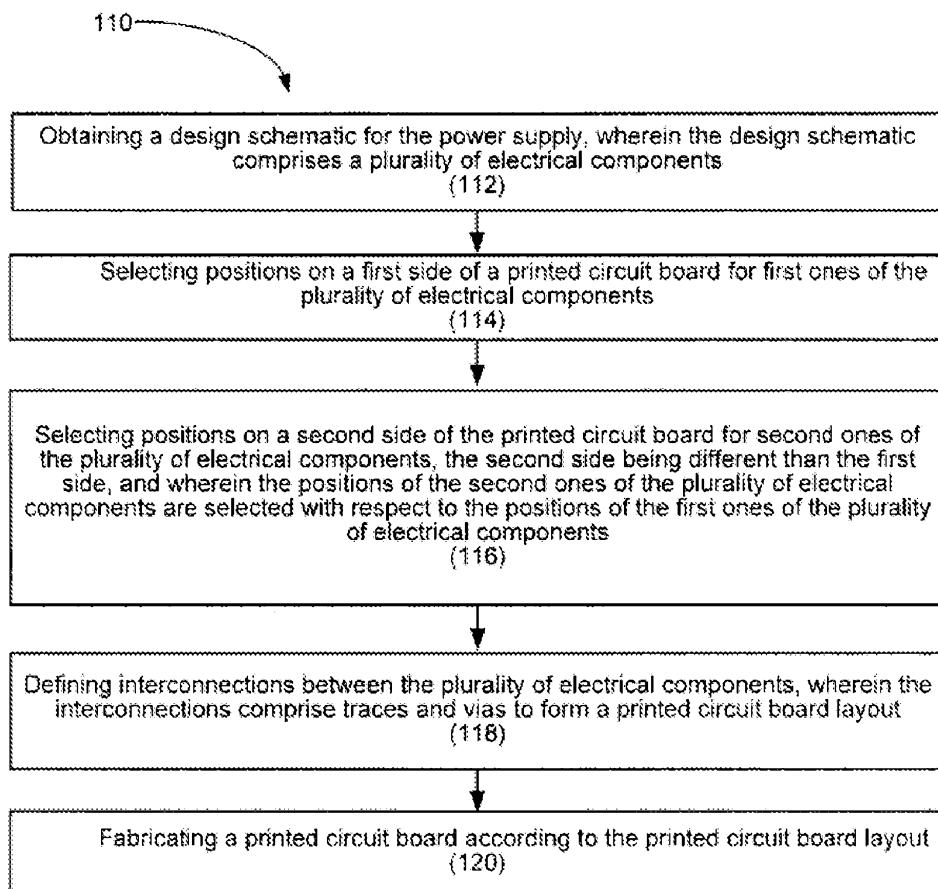

10 Referring now to Figure 8, which depicts a PCB layout of a memory system 130 having a memory controller 132 and a set of eight memory devices 134, 136, 138, 140, 142, 144, 146, and 148 (also labeled M1-M8). Each of the eight memory devices is soldered or otherwise electrically coupled directly to the PCB 150. Four memory devices M1, M3, M5, and M7 are soldered to the top surface of the PCB 150a and 15 four others M2, M4, M6, and M8 are soldered to the bottom surface 150b (not directly shown) (these devices are illustrated a dotted lines to represent their being on the bottom surface 150b of the PCB 150). This direct connection is a deviation from certain prior memory connections having a DIMM with one or more connecting slots. In those devices, memory was soldered to memory cards, which were inserted into the 20 DIMM. Accordingly, the representative embodiment removes this indirect connection, which eliminates the need for a DIMM and corresponding circuitry.

25 By removing the DIMM, the memory devices can be located much closer to the memory controller 132. Accordingly, in at least some embodiments a portion of each memory devices is located within a distance 152 of approximately 6.4 centimeters (approximately 2.5 inches) or less from the memory controller 152. This distance 152, enables a more compact, optimized PCB layout that enables a memory system to be placed into more compact devices, such as handheld and miniaturized computer systems. Furthermore, in some embodiments, the entire memory device is located within the distance 154 of approximately 6.4 centimeters (approximately 2.5 30 inches) or less from the memory controller 132.

As stated, the memory devices M1-M8 are soldered directly to the PCB. Soldered memory device have enhanced impact and shock resistance over DIMM sockets, thus reducing the likelihood of device failure while providing a lock-tight

system that can be incorporated into a more rugged environment. When memory is soldered to a memory card that is inserted into a DIMM slot, the connection between the memory card and the slot is weak and reduced the versatility of the entire computer system. Accordingly, the present system with its soldered memory devices 5 enables the entire PCB to be incorporated into a computer device or system designed to resist high impacts and more rugged environments than the traditional desktop computer system, such as automobile computer systems.

In addition to adding physical strength and an optimized layout, the soldered memory devices remove the uncertainty of a scalable memory system. Fixing the 10 memory devices M1-M8 to the PCB 150 enables system designers to optimize memory device performance, pushing memory devices to perform at higher levels, thus increasing system performance without increasing costs.

Furthermore, in light of the recent trend of lowering memory device cost, in at least some embodiments, it is economically feasible to include the maximum usable 15 memory on the PDB, rather than providing memory scalability using DIMM connector sockets. In at least some embodiments, it is now feasible to initially install the maximum foreseeable system memory directly usable by the host computer system onto the device. This eliminates the need for the scalable DIMM, the cost of such parts, the size of such parts, as well as the corresponding design uncertainty.

20 With continuing reference to Figure 8, in the representative embodiment the system 130 includes a plurality of memory devices soldered directly to the PCB 150 in proximity to the memory controller 132. In some embodiments, the memory devices are disposed on both the top 150a and bottom 150b surface of the PCB 150 to maximize PCB space. Accordingly, in some embodiments, memory devices on the 25 top surface 150a of the PCB are directly above the memory devices that are on the bottom surface 150b. In other embodiments, the memory devices on the top surface are staggered from the memory devices that are on the bottom surface. As shown, the memory devices are disposed in a straight line. However, in other embodiments, the memory devices are clustered in a group, disposed around the memory controller 132, 30 arranged in multiple lines, or otherwise situated near the memory controller 132.

In some embodiments, the individual memory devices M1-M8 are DRAM memory which may, in combination, form the main memory (the “RAM”) of a personal computer. DRAM is a type of random access memory that stores each bit of

data in a separate capacitor within an integrated circuit. Since real capacitors leak charge, the information eventually fades unless the capacitor charge is refreshed periodically. Because of this refresh requirement, it is a dynamic memory as opposed to SRAM and other static memory. DRAM memory devices can be manufactured to 5 be very small, which enable an optimized PCB layout, and small PCB footprints. In other embodiments, the memory devices include SRAM, TRAM, ZRAM, and/or TTRAM memory. Still in other embodiments, the system includes non-volatile memory devices, such as EEPROM memory, or flash memory.

Based on the needs of the memory system, the individual memory devices 10 M1-M8 have varying storage capacities. In some embodiments, the individual memory devices have a 128 MB, a 256 MB, a 512 MB, a 1GB, etc. storage capacity. Additionally, while Figure 8 illustrates eight memory devices, more or less memory devices can be included in the system. For example, two, three, four, six, ten, or more memory devices can be included in the system.

15 The memory system 130 of Figure 8 includes lines that form electrical connections between the memory controller 132 and/or other devices of the computer system. For clarity, these lines are not illustrated in Figure 8. Figures 9-11 illustrate representative embodiments of the system data lines, clock lines, and address lines, which may be incorporated into the system 130 shown in Figure 8. Referring now to 20 Figure 9, the memory system 130 is depicted having a set of data lines 156, 158, 160, and 162. As will be understood by those of skill in the art, each illustrated data line can represent multiple data lines, such as 16, 32, 64, etc. Providing each memory device with a separate, direct data line eliminates the need for a terminating resistor on the end of the data line, as is required in series connections. Furthermore, the 25 direct connection also eliminates the need for a trace resistor along the data line. Thus, these direct connections require only minimal PCB real estate. Subsequently, this configuration allows the memory devices M1-M8 to be positioned close to the memory controller 132 since they occupy limited space therebetween.

30 Direct, individual data lines provide advancement over DIMM data lines, which connect the DIMM slots in series and require terminating resistors on the end of each line. In this configuration, DIMMs require more space on the PCB as well as more parts. Accordingly, embodiments of the present system eliminate these space requirements and thus decrease both the cost and size of the resulting system.

Referring now to Figure 10, a set of clock lines (represented collectively at 168) is depicted, which prove electrical communication between the system clock 164 and the individual memory devices M1-M8. Figure 10 is a block diagram that illustrates graphically representative clock line paths and lengths. However, it will be 5 understood that Figure 10 does not accurately represent a complete layout of the PCB since in accordance with at least some embodiments of the present invention, at least some memory devices may be disposed on the opposite side of the PCB, as is illustrated in Figure 8.

Clock signals synchronize the memory devices and allow the entire system to 10 operate properly and rapidly. Accordingly, clock signals from the system clock should arrive simultaneously at each memory device. Thus, in some embodiments, the length of the lines between the system clock 164 and the individual memory devices (e.g., M1-M8) are equidistant (or substantially equidistant). A starburst configuration 170 and 172 enables the line from the system clock to be divided into 15 multiple lines each having an equal distance. The lines proceeding from the starburst configurations 170 and 172 connect to the memory devices and provide a clock signal thereto. By disposing the center of the starburst at a point equidistant from each memory device, the starburst properly and accurately transmits a synchronized clock signal to the memory devices M1-M8. In some embodiments, the starburst 20 configurations 170 and 172 each include a terminator resistor 174 and 176 in parallel with the memory devices to ensure proper function.

Referring now to Figure 11, which illustrates an address line 178 in electrical communication with each of the memory devices M1, M3, M5, and M7 (also M2, M4, M6, and M8, which are not shown) and the memory controller 132. The address 25 line connects the memory devices in series and provides electrical signals between the memory controller 132 and the memory devices during reading and writing memory operations. In some embodiments, a terminator resistor 180 is connected at the end of the addressing line to improve system functionality.

The routing of memory system lines, in particular the data, clock, and address 30 lines enable a compact and optimized memory system layout that, in some embodiments, enables each memory device to be disposed within two and a half inches or less of the memory controller 132. Furthermore, the configuration and orientation of system lines reduces the requirement for additional components, while

providing highly optimized memory performance.

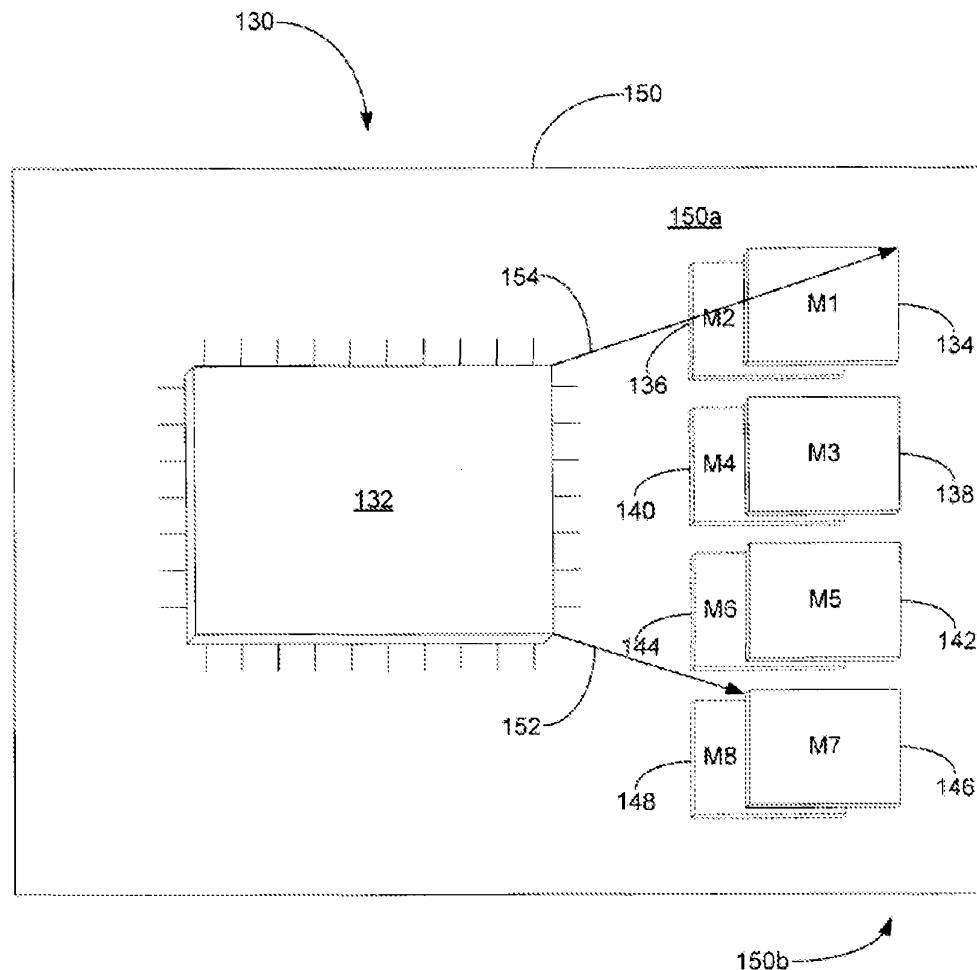

Referring now to Figure 12, a block diagram of a method 190 for optimizing a memory system is illustrated, according to one representative embodiment. The representative method provides (at box 102) disposing at least one memory device on a top surface of a circuit board. Additionally, box 194 shows the method can progress as at least one memory device is disposed on the bottom surface of the circuit board. At box 196, Figure 12 shows the memory devices are then soldered directly to the circuit board. In some embodiments, memory devices are placed 6.4 centimeters (2.5 inches) or less from the memory controller. In some embodiments, soldering includes disposing at least one of the memory devices on a top surface of the PCB, while disposing at least one of the memory devices on a bottom surface. The method 190 (as shown at box 198) further provides electronically coupling each of the memory devices to the memory controller via a separate data line. Lastly, box 200 shows the method 190 provides electronically coupling each of the memory devices to a system clock via a plurality of equidistant clock lines.

Thus, embodiments of the present invention relate to computer circuit board layouts. In particular, at least some aspects of the present invention relate to systems and methods for optimizing memory performance in a computer device or system. Still further, at least some aspects of the present invention relate to systems and methods for miniaturizing and optimizing memory layout on a circuit board.

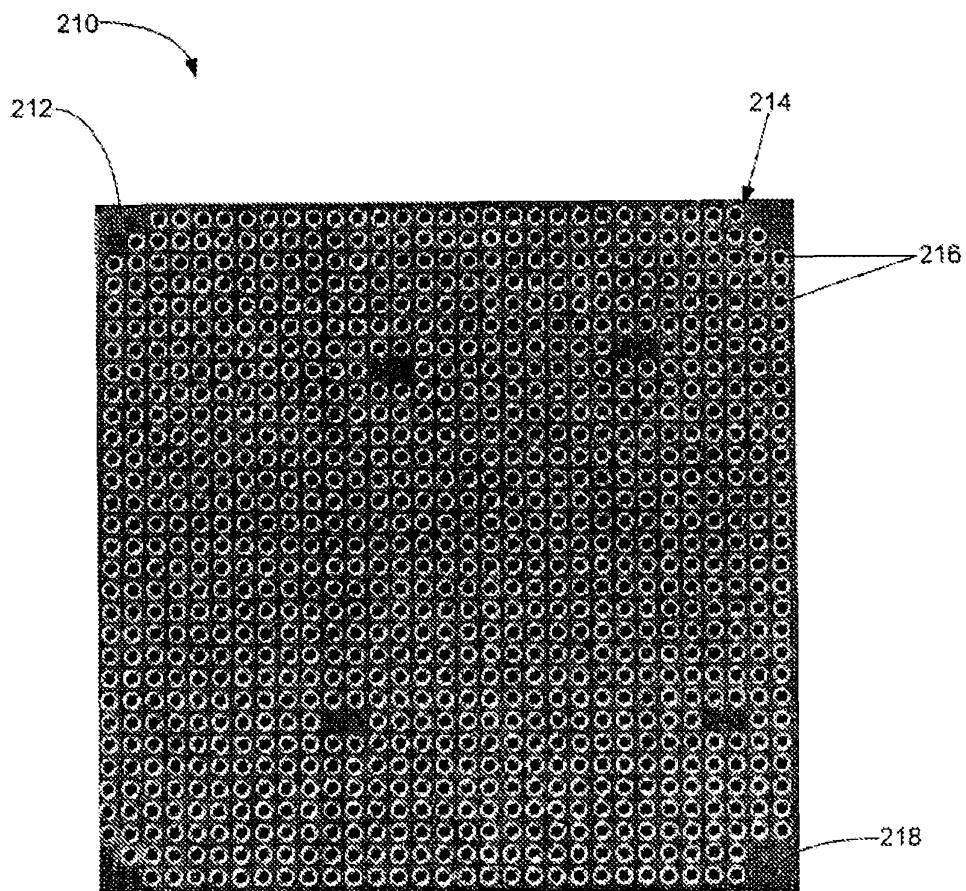

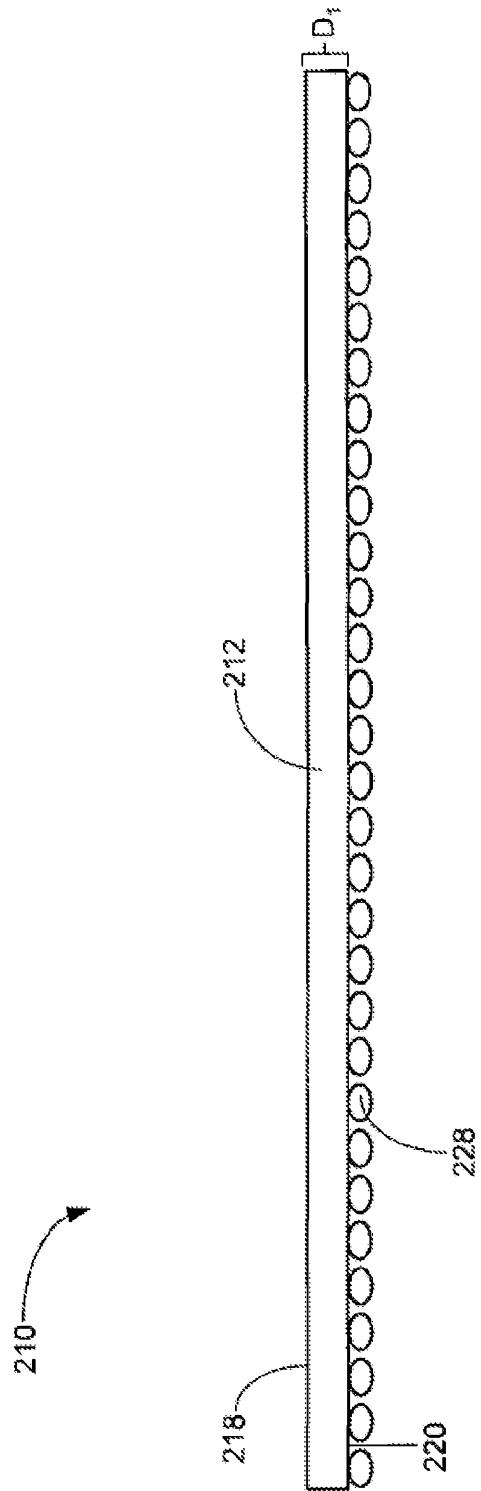

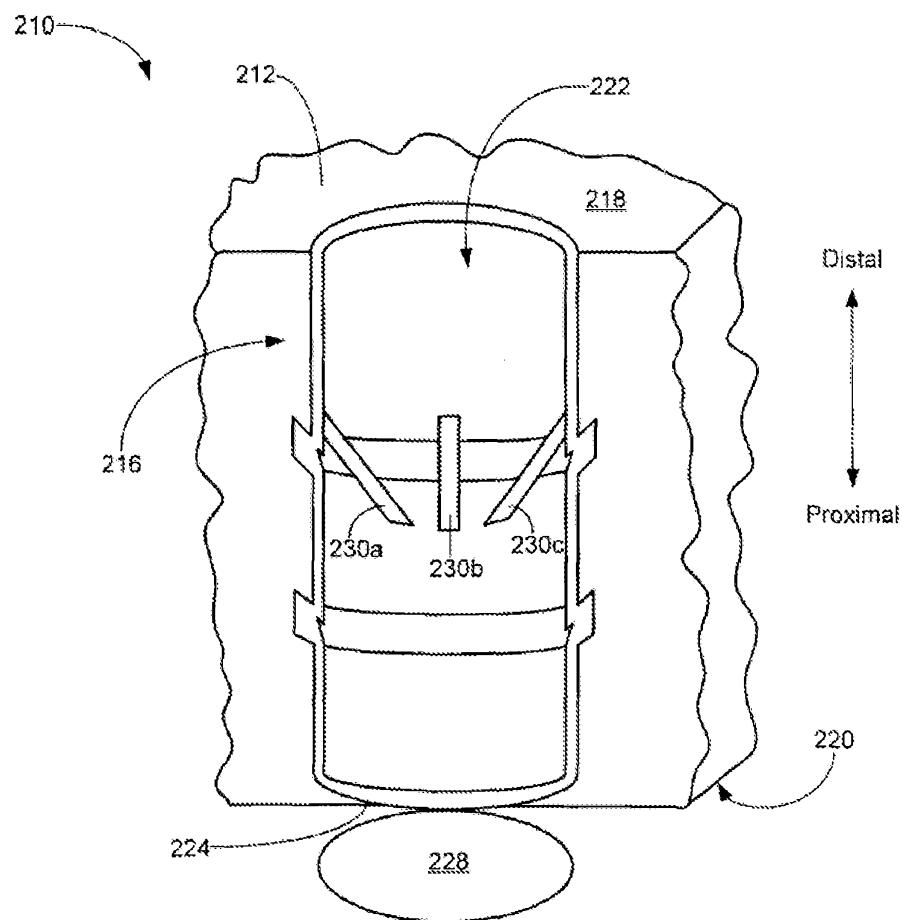

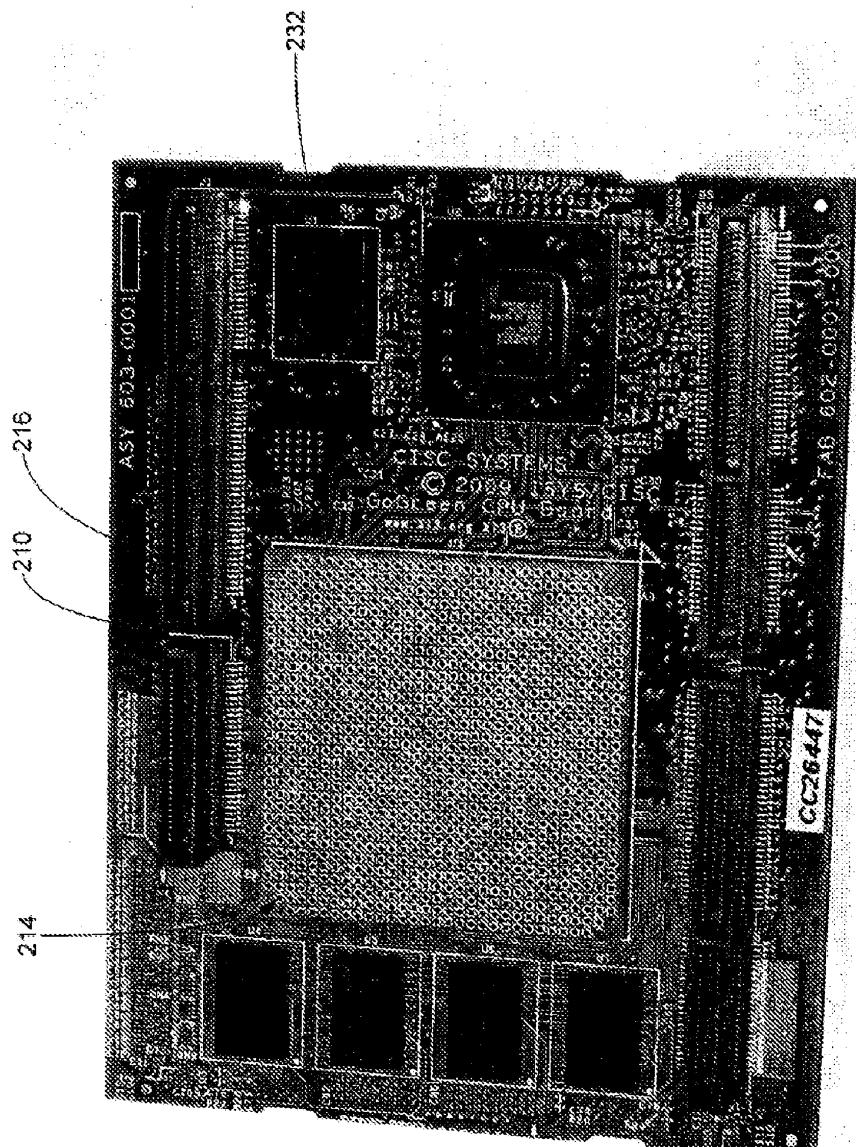

#### IC Connectors

Some aspects of the invention relate to IC Connectors. In particular, some aspects of the invention relate to a PGA to BGA adaptor that can attach an IC (e.g., a CPU) to a circuit board (e.g., a PCB). The described PGA to BGA adaptor can comprise any suitable component that allows it to electrically and physically connect an IC device comprising a PGA to a circuit board through the use of a solder BGA. By way of non-limiting example, Figure 13 illustrates a representative embodiment in which the PGA to BGA adaptor 210 comprises a casing 212 and an array 214 of machined pin sockets 216. In order to provide a better understanding of the described adaptor, each of its aforementioned components is described below in more detail.