**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>7</sup>

G11C 17/00

(45) 공고일자 2005년12월01일

(11) 등록번호 10-0532652

(24) 등록일자 2005년11월24일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2003-0075767 | (65) 공개번호 | 10-2004-0038770 |

| (22) 출원일자 | 2003년10월29일     | (43) 공개일자 | 2004년05월08일     |

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2002-00316720 | 2002년10월30일 | 일본(JP) |

|------------|--------------------|-------------|--------|

|           |                                            |

|-----------|--------------------------------------------|

| (73) 특허권자 | 가부시끼가이샤 도시바<br>일본국 도쿄도 미나토구 시바우라 1초메 1방 1고 |

|-----------|--------------------------------------------|

|          |                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------|

| (72) 발명자 | 나까무라히로시<br>일본도쿄도미나토구시바우라1초메1방1고가부시끼가이샤도시바본사지<br>적재산부내<br><br>야마무라도시오<br>일본도쿄도미나토구시바우라1초메1방1고가부시끼가이샤도시바본사지<br>적재산부내 |

|----------|--------------------------------------------------------------------------------------------------------------------|

|          |            |

|----------|------------|

| (74) 대리인 | 장수길<br>구영창 |

|----------|------------|

**심사관 : 조명관**

**(54) 반도체 메모리**

**요약**

후세대 칩 내에는 병렬 동작이 가능한 복수의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7이 배치된다. 메모리 셀 어레이 Array0, Array4, 메모리 셀 어레이 Array1, Array5, 메모리 셀 어레이 Array2, Array6, 및 메모리 셀 어레이 Array3, Array7은 각각 1개의 셀 어레이 블록을 구성한다. 동작의 성공 또는 실패를 나타내는 Pass/Fail 신호는 셀 어레이 블록마다 출력된다. 셀 어레이 블록의 수는 전세대 칩의 메모리 셀 어레이의 수 또는 셀 어레이 블록의 수와 같은 것이 바람직하다.

**대표도**

도 1

**색인어**

반도체 기판, 메모리 셀, NAND 셀

**명세서**

## 도면의 간단한 설명

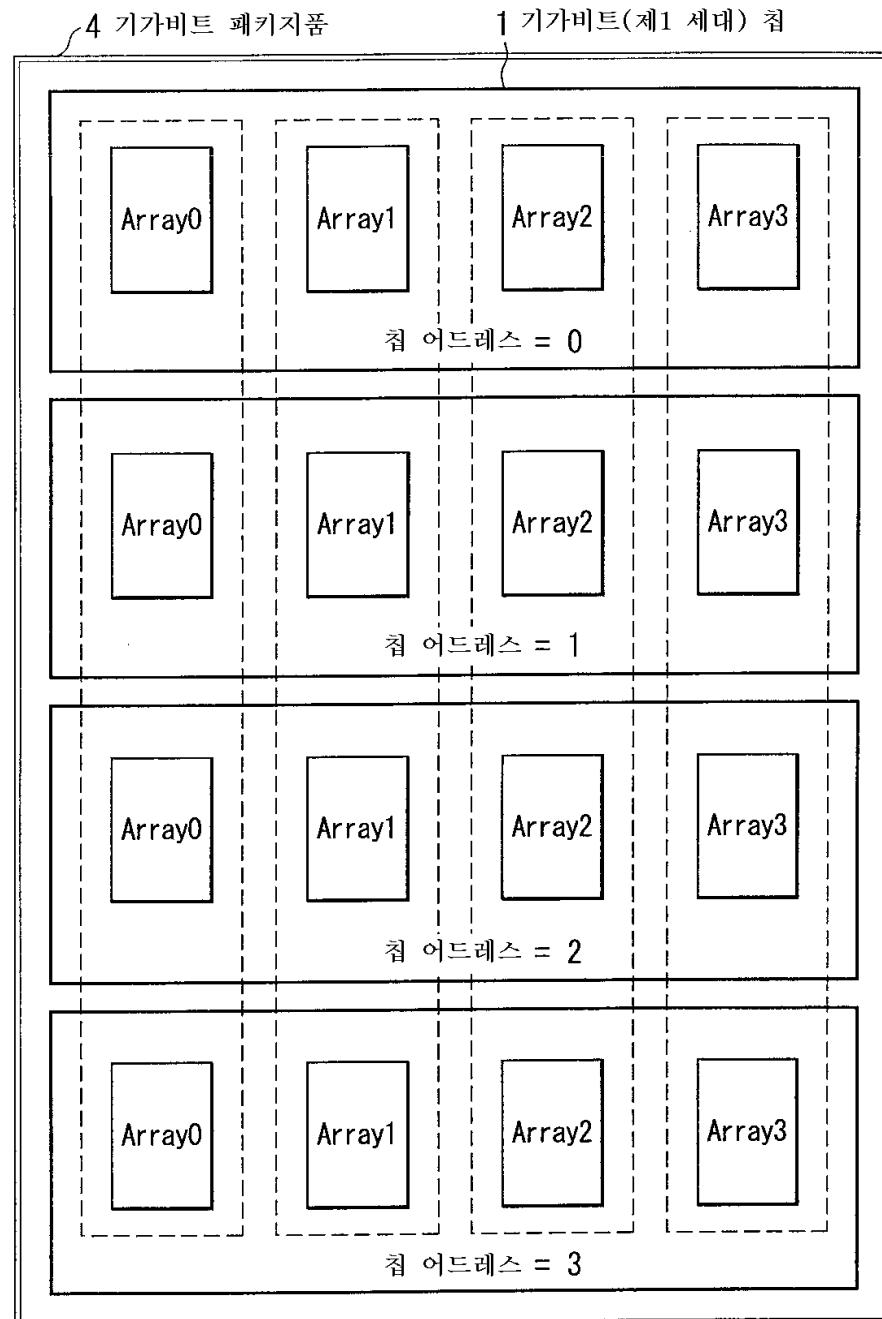

도 1은 제1 세대의 1개의 칩을 탑재한 패키지품을 도시하는 도면.

도 2는 제1 세대의 2개의 칩을 탑재한 패키지품을 도시하는 도면.

도 3은 본 발명의 예에 따른 EEPROM의 주요부를 도시하는 블록도.

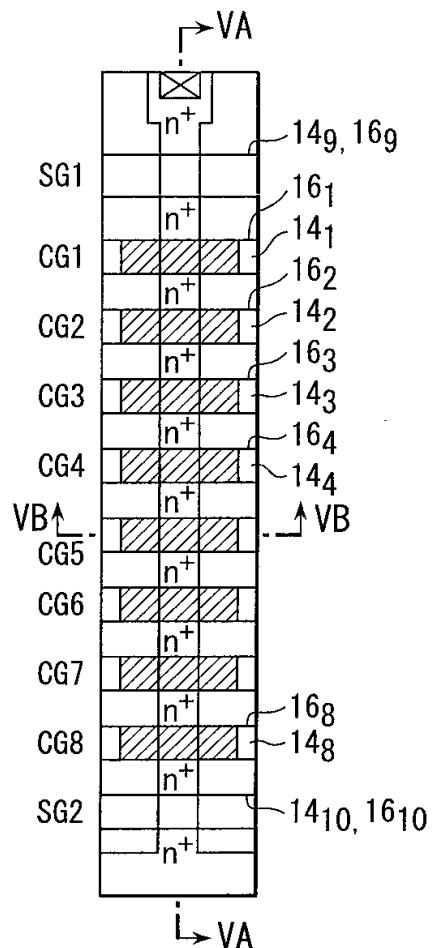

도 4A 및 도 4B는 NAND 셀의 예를 도시하는 도면.

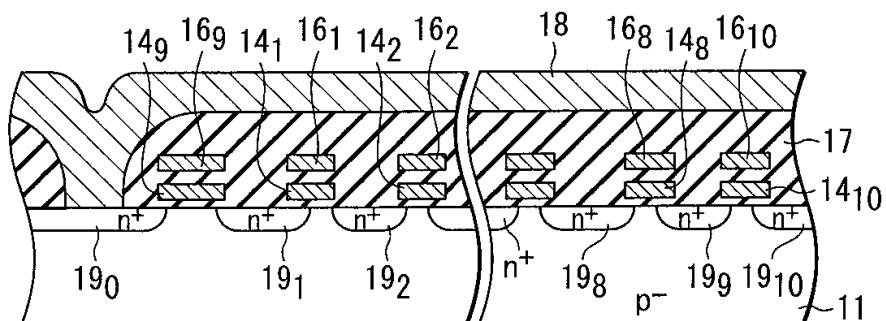

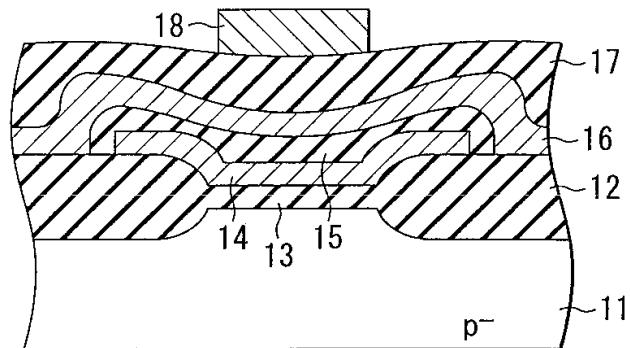

도 5A 및 도 5B는 NAND 셀의 구조예를 도시하는 단면도.

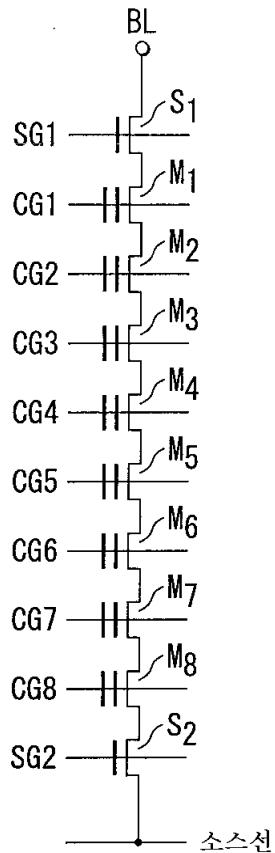

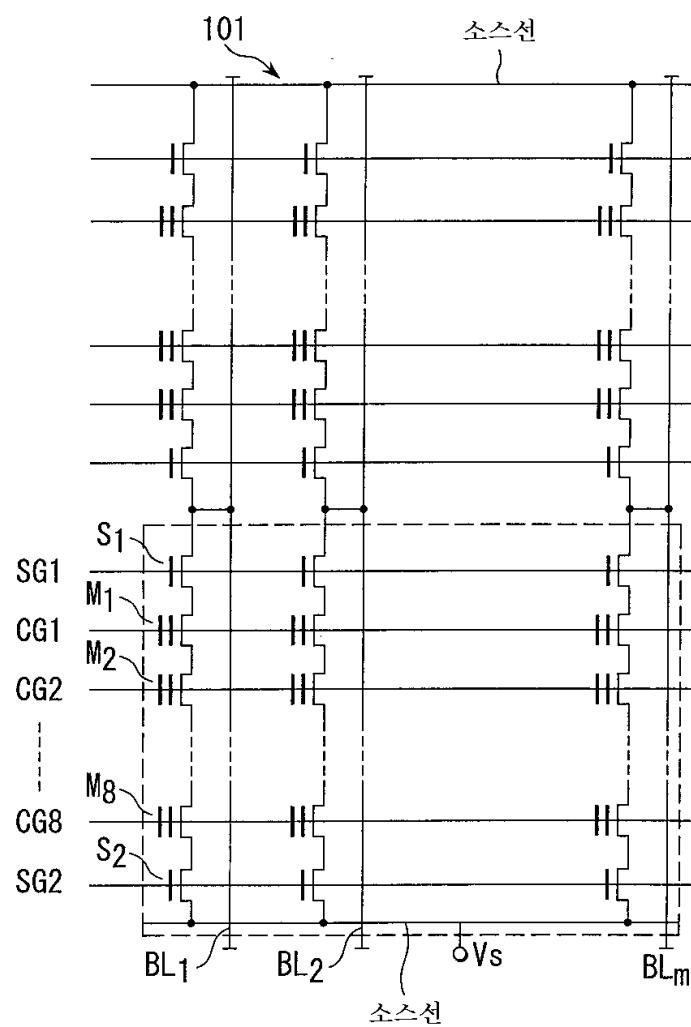

도 6은 NAND 셀 어레이의 회로예를 도시하는 회로도.

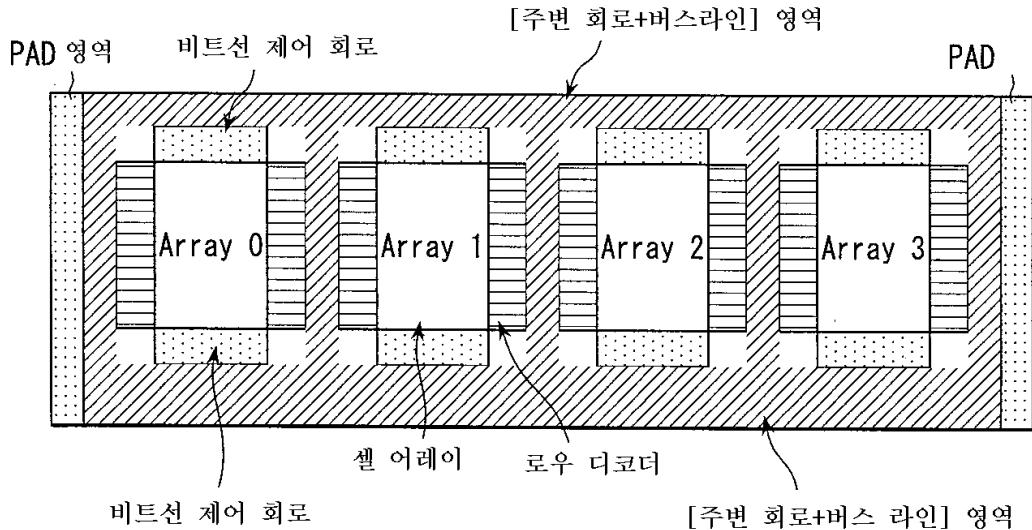

도 7은 NAND 셀형 EEPROM의 칩 레이아웃의 예를 도시하는 도면.

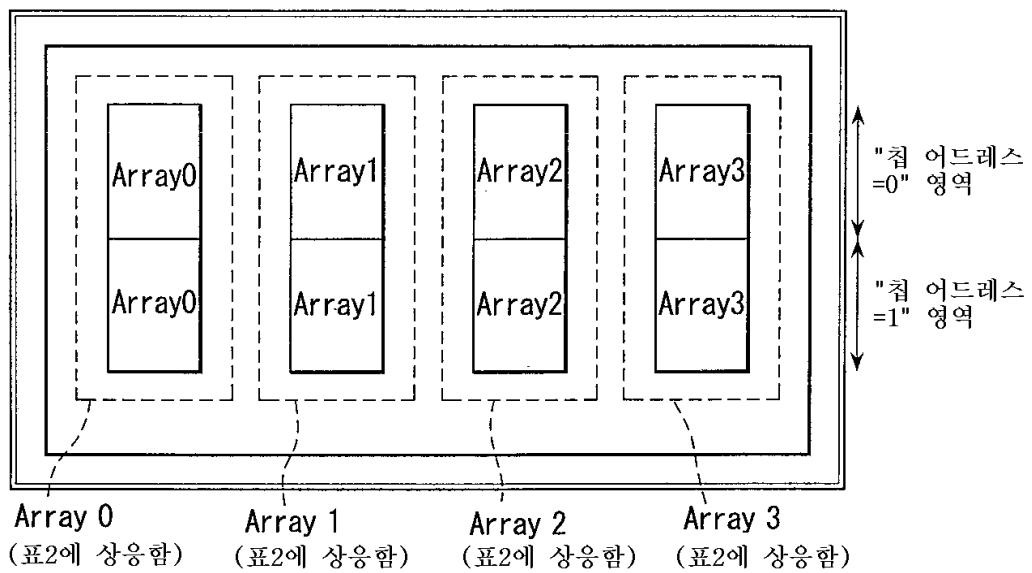

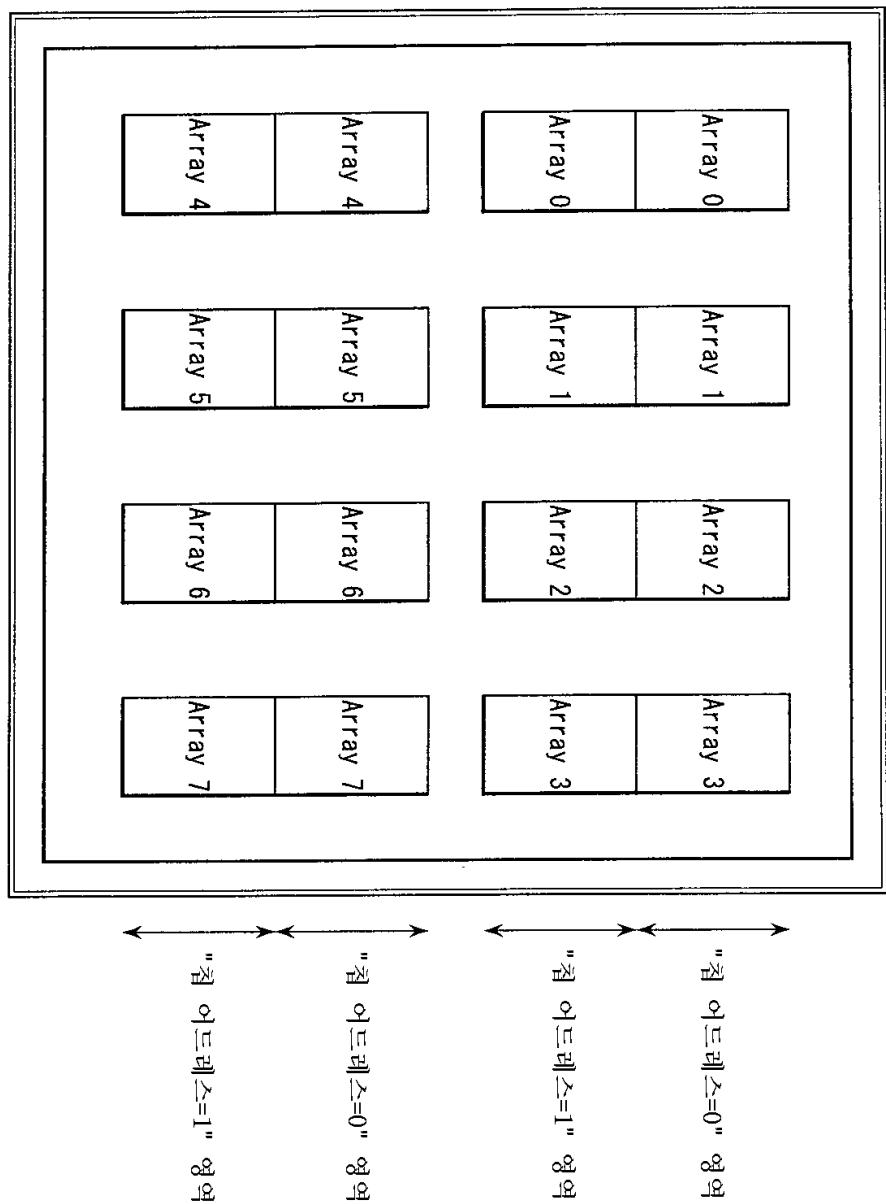

도 8은 외부 장치로부터 도 2의 패키지품을 본 경우의 칩 이미지를 도시하는 도면.

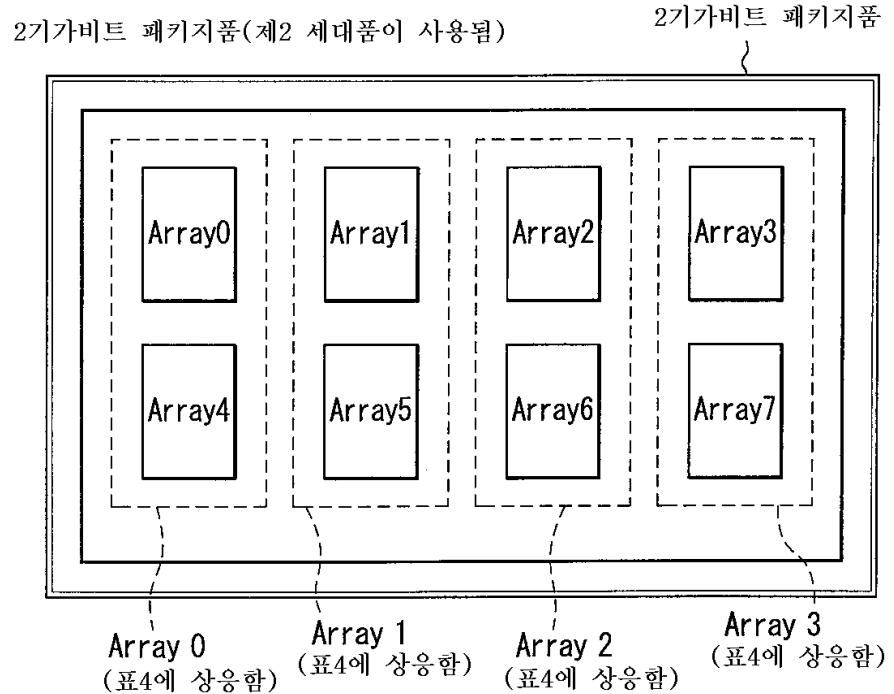

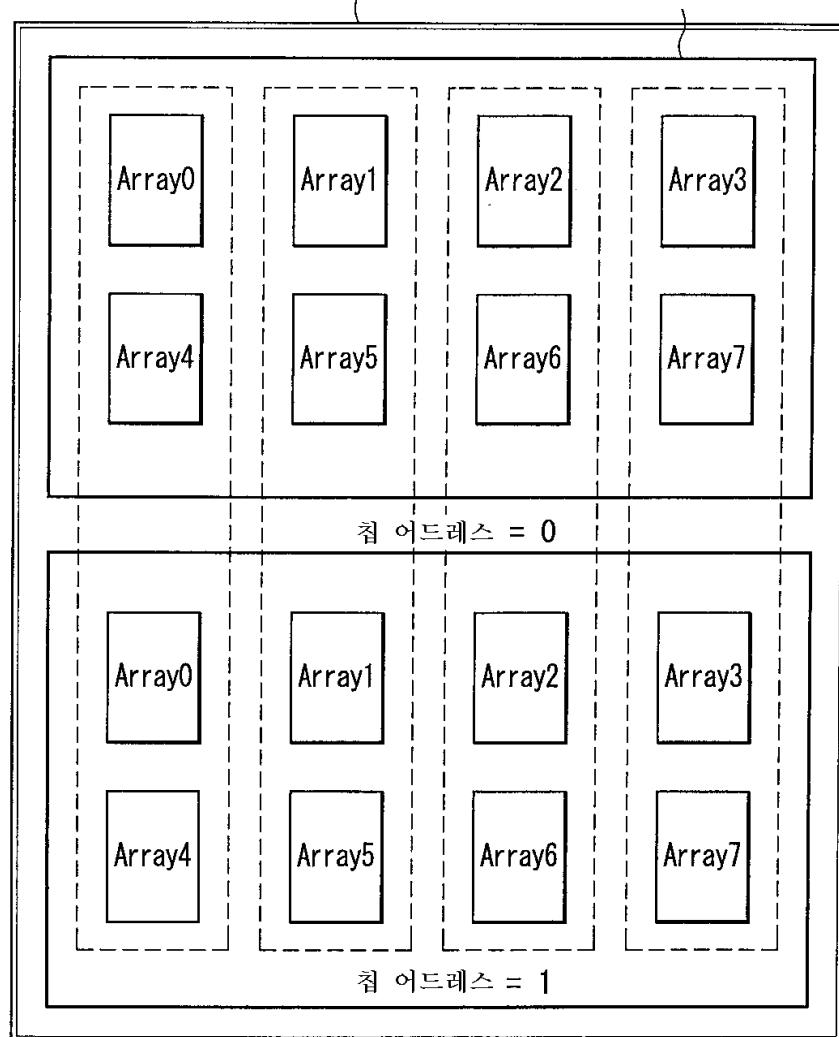

도 9는 제2 세대의 1개의 칩을 탑재한 패키지품을 도시하는 도면.

도 10은 제1 세대의 4개의 칩을 탑재한 패키지품을 도시하는 도면.

도 11은 제2 세대의 2개의 칩을 탑재한 패키지품을 도시하는 도면.

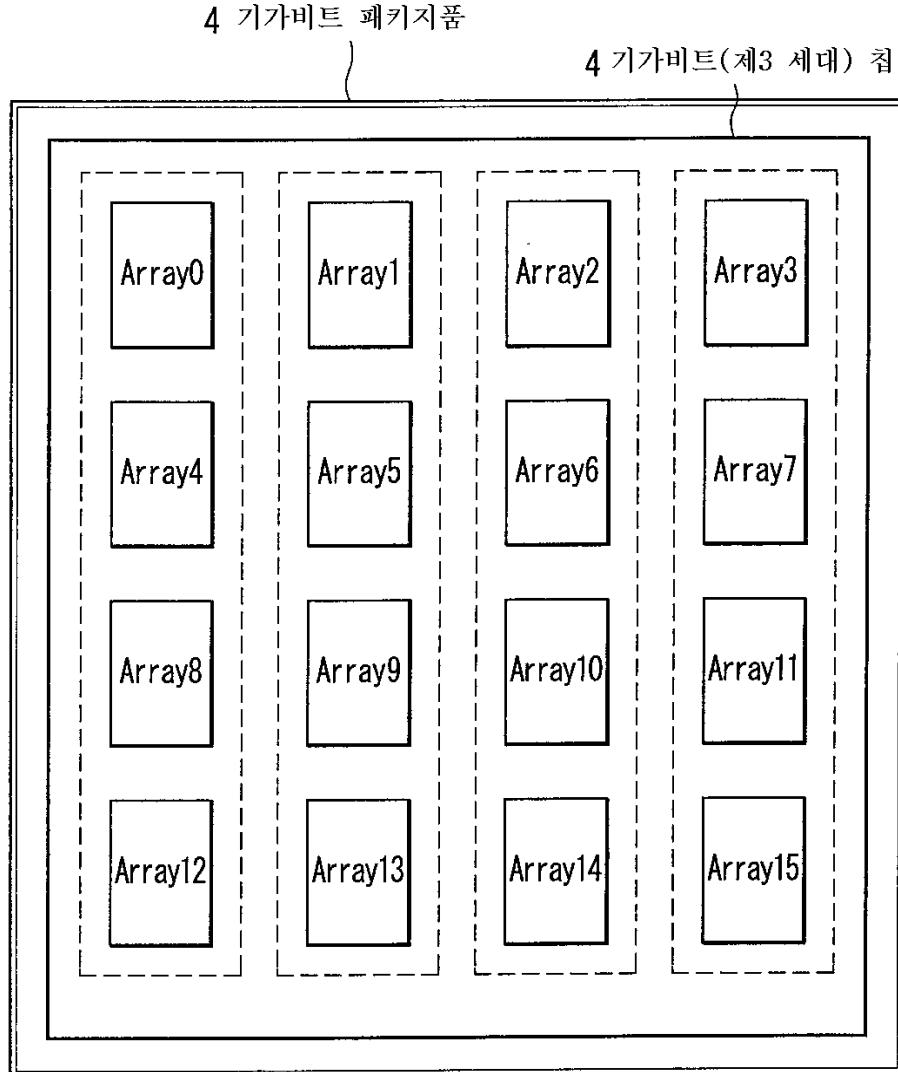

도 12는 제3 세대의 1개의 칩을 탑재한 패키지품을 도시하는 도면.

도 13은 제2 세대의 2개의 칩을 탑재한 패키지품을 도시하는 도면.

도 14는 외부 장치로부터 도 13의 패키지품을 본 경우의 칩 이미지를 도시하는 도면.

도 15는 제3 세대의 1개의 칩을 탑재한 패키지품을 도시하는 도면.

## <도면의 주요 부분에 대한 부호의 설명>

101 : 메모리 셀 어레이

102 : 비트선 제어 회로

103 : 컬럼 디코더

104 : 어드레스 버퍼

105 : 로우 디코더

106 : 데이터 입출력 버퍼

107 : 기판 전위 제어 회로

109 : 기입용 고전압 발생 회로

110 : 기입용 중간 전압 발생 회로

## 발명의 상세한 설명

## 발명의 목적

### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 특히 병렬 동작을 행하는 것이 가능한 복수의 메모리 셀 어레이를 갖는 불휘발성 반도체 메모리에 관한 것이다.

종래, 반도체 메모리 중 하나로서 전기적으로 재기입이 가능한 EEPROM이 알려져 있다. 그 중에서도 메모리 셀을 복수 개 직렬 접속하여 NAND 셀 블록을 구성하는 NAND 셀형 EEPROM은 고집적화를 할 수 있는 것으로서 주목받고 있다(예를 들면, 일본 특개평 9-82923호 공보를 참조).

NAND 셀형 EEPROM 중 하나의 메모리 셀은 반도체 기판 상에 절연막을 개재하여 부유 게이트(전하 축적층)와 제어 게이트가 적층된 FET-MOS 구조를 갖는다. 그리고, 복수개의 메모리 셀이 인접하는 것끼리 소스·드레인을 공용하는 형태로 직렬 접속되어 NAND 셀을 구성하고, 이것을 일 단위로서 비트선에 접속하는 것이다.

이러한 NAND 셀이 매트릭스 배열되어 메모리 셀 어레이가 구성된다. 메모리 셀 어레이에는 p형 기판 또는 p형 웨л 내에 집적 형성된다.

메모리 셀 어레이의 열 방향으로 배열한 NAND 셀의 일 단축의 드레인은 각각 선택 게이트 트랜지스터를 개재하여 비트선에 공통 접속되고, 그 타단축의 소스는 각각 선택 게이트 트랜지스터를 개재하여 공통 소스선에 접속된다. 메모리 트랜지스터의 제어 게이트 및 선택 게이트 트랜지스터의 게이트 전극은 메모리 셀 어레이의 행 방향에 각각 제어 게이트선(워드선), 선택 게이트선으로서 공통 접속된다.

이 NAND 셀형 EEPROM의 동작은 다음과 같다.

데이터 기입의 동작은 주로 비트선 컨택트로부터 가장 멀어져 있는 위치의 메모리 셀부터 순서대로 행한다.

우선, 데이터 기입 동작이 개시되면, 기입 데이터에 따라, 비트선에는 0V("1"-데이터 기입 비트선) 또는 전원 전압 Vcc("0"-데이터 기입 비트선)가 인가되고, 비트선 컨택트측의 선택 게이트선에는 Vcc가 인가된다. 이 경우, "1"-데이터 기입 비트선에 접속된 선택 NAND 셀에서는 선택 게이트 트랜지스터를 개재하여 NAND 셀 내 채널부가 0V로 고정된다.

한편, "1"-데이터 기입 비트선에 접속된 선택 NAND 셀에서는 NAND 셀 내 채널부는 선택 게이트 트랜지스터를 통하여, [Vcc-Vtsg(Vtsg는 선택 게이트 트랜지스터의 임계값 전압)]까지 충전된 후에 부유 상태가 된다. 계속해서, 선택 NAND 셀 내의 선택 메모리 셀의 제어 게이트선이 0V→Vpp(=20V 정도: 기입용 고전압), 선택 NAND 셀 내의 다른 제어 게이트선이 0V→Vmrg(=10V 정도: 중간 전압)가 된다.

"1"-데이터 기입 비트선에 접속된 선택 NAND 셀에서는 NAND 내 채널부가 0V에 고정되어 있기 때문에, 선택 NAND 셀 내의 선택 메모리 셀의 게이트(=Vpp 전위)와 채널부(=0V)에 큰 전위차(=20V 정도)가 발생하여, 채널부로부터 부유 게이트에 전자 주입이 생긴다. 이에 의해, 그 선택된 메모리 셀의 임계값은 플러스 방향으로 시프트하고, "1"-데이터의 기입이 완료된다.

"0"-데이터 기입 비트선에 접속된 선택 NAND 셀에서는 NAND 내 채널부가 부유 상태에 있다. 이 때문에, 선택 NAND 셀 내의 제어 게이트선과 채널부 사이의 용량 커플링의 영향에 의해 제어 게이트선 전압의 상승(0V→Vpp, Vmg)에 따라, 채널부 전위가 부유 상태를 유지한 채로 [Vcc-Vtsg] 전위→Vmch(=8V 정도)로 상승한다. 이 때에는 선택 NAND 셀 내의 선택 메모리 셀의 게이트(=Vpp 전위)와 채널부(=Vmch) 사이의 전위차가 12V 정도로 비교적 작기 때문에, 전자 주입이 발생하지 않는다. 따라서, 선택 메모리 셀의 임계값은 변화하지 않고, 마이너스의 상태로 유지된다.

데이터 소거는 선택된 NAND 셀 블록 내의 모든 메모리 셀에 대하여 동시에 행해진다. 즉, 선택된 NAND 셀 블록 내의 모든 제어 게이트를 0V로 하고, 비트선, 소스선, p형 웨л(혹은 p형 기판), 비선택 NAND 셀 블록 중 제어 게이트 및 모든 선택 게이트에 20V 정도의 고전압을 인가한다. 이에 의해, 선택 NAND 셀 블록 중 모든 메모리 셀에서 부유 게이트의 전자가 p형 웨л(혹은 p형 기판)로 방출되어, 임계값 전압은 마이너스 방향으로 시프트한다.

데이터 판독 동작은 선택된 메모리 셀의 제어 게이트를 0V로 하고, 그 이외의 메모리 셀의 제어 게이트 및 선택 게이트를 판독용 중간 전압 Vread( $\leq 4V$ )로 하여 선택 메모리 셀에서 전류가 흐르는지의 여부를 검출함으로써 행해진다.

이상과 같은 NAND 셀형 EEPROM은 통상 기입, 소거 등의 동작이 종료한 후에, 이 동작이 성공하였는지 또는 실패하였는지를 나타내는 Pass/Fail 신호를 출력하는 기능을 갖고 있다. 즉, 예를 들면 기입/소거 동작이 종료한 후에 Pass/Fail 신호를 칩 밖으로 출력하기 위한 커맨드가 입력되면, I/O 패드로부터 Pass/Fail 신호가 출력된다.

또한, 도 1에 도시한 바와 같이 최근의 NAND형 EEPROM은 1칩 내에 복수의 메모리 셀 어레이 Array0, Array1, Array2, Array3을 구비하고, 또한 고속 동작을 실현하기 위해서, 이들 복수의 메모리 셀 어레이 Array0, Array1, Array2, Array3이 병렬 동작하도록 구성되어 있다.

이 경우, NAND형 EEPROM에는, 예를 들면 기입/소거 동작이 종료한 후에, 모든 메모리 셀 어레이에 대하여 기입/소거 동작이 성공하였는지, 또는 적어도 1개의 메모리 셀 어레이에 대하여 기입/소거 동작이 실패하였는지를 나타내는 Pass/Fail 신호, 즉 칩 전체의 Pass/Fail 신호를 출력하는 기능이 부가된다. 또한, 복수의 메모리 셀 어레이 각각에 대하여 기입/소거 동작이 성공하였는지, 또는 실패하였는지를 나타내는 복수의 Pass/Fail 신호, 즉 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능이 부가된다.

표 1은 도 1의 불휘발성 반도체 메모리에서의 Pass/Fail 신호의 데이터 입출력 단자 I/00~I/07에의 할당의 일례를 나타낸다.

[표 1]

(a) com-A

|      | 스테이터스      | 출력                          |

|------|------------|-----------------------------|

| I/00 | 칩 스테이터스-I  | Pass → 0 Fail → 1           |

| I/01 | 사용하지 않음    | 0                           |

| I/02 | 사용하지 않음    | 0                           |

| I/03 | 사용하지 않음    | 0                           |

| I/04 | 사용하지 않음    | 0                           |

| I/05 | 사용하지 않음    | 0                           |

| I/06 | Ready/Busy | Busy → 0 Ready → 1          |

| I/07 | 기입 보호      | Protect → 0 Not Protect → 1 |

## [표 2]

(b) com-B

|      | 스테이터스      | 출력          |                 |

|------|------------|-------------|-----------------|

| I/00 | 칩 스테이터스-I  | Pass → 0    | Fail → 1        |

| I/01 | Array (0)  | Pass → 0    | Fail → 1        |

| I/02 | Array (1)  | Pass → 0    | Fail → 1        |

| I/03 | Array (2)  | Pass → 0    | Fail → 1        |

| I/04 | Array (3)  | Pass → 0    | Fail → 1        |

| I/05 | 사용하지 않음    | 0           |                 |

| I/06 | Ready/Busy | Busy → 0    | Ready → 1       |

| I/07 | 기입 보호      | Protect → 0 | Not Protect → 1 |

표 1 및 표 2에서부터 알 수 있듯이, 통상 불휘발성 반도체 메모리는 칩 전체의 Pass/Fail 신호를 출력하는 기능(표 1)을 가짐과 함께, 메모리 셀 어레이마다 Pass/Fail 신호를 출력하는 기능(표 2)도 갖고 있다.

그리고, 예를 들면 표 1의 기능을 실현하기 위해서는 커맨드 com-A를 칩에 인가하면 되고, 또한 표 2의 기능을 실현하기 위해서는 커맨드 com-B를 칩에 인가하면 된다.

그런데, 도 1에 도시한 바와 같이, 패키지품에 필요한 메모리 용량이 1칩으로 충분한 경우(패키지품=1기가비트, 메모리 칩 용량=1기가비트)에는 통상 패키지품 내에는 1개의 칩만을 넣지만, 도 2에 도시한 바와 같이 패키지품에 필요한 메모리 용량이 1칩으로는 부족한 경우(패키지품=2기가비트, 메모리 칩 용량=1기가비트)에는 패키지품 내에는 복수칩, 본 예에서는 2개의 칩을 넣을 필요가 있다.

또한, 도 2의 불휘발성 반도체 메모리에서의 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7에의 할당은 도 1의 반도체 메모리의 경우와 마찬가지로, 표 1 및 표 2에 나타낸 바와 같다.

즉, 2개의 칩의 선택은 칩 어드레스에 의해 행한다. 그리고, 선택된 칩에 대하여, 표 1 또는 표 2에 기초한 스테이터스 하에서, Pass/Fail 신호의 출력 동작이 실행된다.

도 1 및 도 2에 도시한 패키지품에 사용되는 칩을 제1 세대로 한 경우, 제2 세대 칩은 디자인 룰의 축소 등에 의해 통상 제1 세대가 갖는 메모리 용량의 2배 이상의 메모리 용량을 갖는다. 따라서, 예를 들면 도 2에 도시한 패키지품에 제2 세대 칩을 사용하면 패키지품 내에는 1개의 칩만을 넣으면 되기 때문에 칩 비용의 저감을 도모할 수 있다.

## 발명이 이루고자 하는 기술적 과제

그러나, 종래의 불휘발성 반도체 메모리는 Pass/Fail 신호의 출력 모드로서는 칩 전체의 Pass/Fail 신호의 출력 모드와, 메모리 셀 어레이마다의 Pass/Fail 신호의 출력 모드로 이루어지는 2 종류의 출력 모드밖에 가지고 있지는 않다. 이것은 메모리 칩의 세대가 진행되어도 동일하였다. 한편, 메모리 칩의 세대가 1개 진행하면, 1칩 내에 배치되는 병렬 동작 가능한 메모리 셀 어레이 수는 2배 이상으로 증가한다.

이 때문에, 예를 들면 제2 세대 칩에 대한 메모리 셀 어레이마다의 Pass/Fail 신호의 출력에서는 표 2에 나타낸 바와 같은 제1 세대 칩에 대한 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7에의 할당을 그대로 사용할 수 없다.

따라서, 제2 세대 칩에서의 Pass/Fail 신호를 출력하는 시스템은 제1 세대 칩에서의 그것과는 다르게 되기 때문에, 동일한 패키지품에 대하여 메모리 칩을 단순하게 제1 세대에서부터 제2 세대로 치환할 수는 없게 된다.

이와 같이, 종래는 동일 패키지품에 사용하는 칩을 제1 세대에서부터 제2 세대로 치환한다는 것은 칩 비용의 저감을 도모함에 있어서 매우 유효하게 된다. 그러나, 제1 세대 칩에서의 Pass/Fail 신호를 출력하는 시스템과 제2 세대 칩에서의 Pass/Fail 신호를 출력하는 시스템과의 사이에는 호환성이 없기 때문에, 결과적으로 동일 패키지품에 사용하는 칩을 제1 세대에서 제2 세대로 치환하는 것이 곤란해진다는 문제가 있었다.

따라서, Pass/Fail 신호를 출력하는 시스템에 대하여 전세대 칩과 후세대 칩과의 사이에 호환성을 갖게 함으로써 동일 패키지품에 대하여 전세대 칩에서부터 후세대 칩으로의 치환을 쉽게 하여, 칩 비용의 저감을 도모하는 것이 기대된다.

### 발명의 구성 및 작용

본 발명의 예에 따른 반도체 메모리는 매트릭스 형태로 배치되는 복수의 메모리 셀 유닛으로 구성되는 복수의 메모리 셀 어레이를 구비하며, 상기 복수의 메모리 셀 어레이에는 2개 이상의 메모리 셀 어레이로 이루어지는 복수의 셀 어레이 블록을 구성하고, 셀 어레이 블록마다 동작의 성공 또는 실패를 나타내는 제1 Pass/Fail 신호를 출력한다.

이하, 도면을 참조하여, 본 발명의 예에 따른 반도체 메모리에 대하여 상세히 설명한다.

#### (1) 개요

도 3은 본 발명의 예에 따른 NAND 셀형 EEPROM의 주요부를 도시하고 있다.

메모리 셀 어레이(101)에 대하여, 데이터 기입, 판독, 재기입 및 검증 판독을 행하기 위해서, 비트선 제어 회로(102)가 형성되어 있다. 이 비트선 제어 회로(102)는 데이터 입출력 버퍼(106)에 연결되어, 어드레스 버퍼(104)로부터의 어드레스 신호를 받는 컬럼 디코더(103)의 출력을 입력으로서 받는다.

또한, 메모리 셀 어레이(101)에 대하여 제어 게이트 및 선택 게이트를 제어하기 위해 로우 디코더(105)가 형성된다. 기판 전위 제어 회로(107)는 메모리 셀 어레이(101)가 형성되는 p형 기판(또는, p형 웰)의 전위를 제어한다. 또한, 데이터 기입 동작 시에 기입용 고전압 발생 회로(109)는 기입용 고전압 Vpp( $\leq 20V$ )를 발생하고, 기입용 중간 전압 발생 회로(110)는 중간 전압 Vmg( $\leq 10V$ )를 발생한다.

판독용 중간 전압 발생 회로(111)는 데이터 판독 시에 판독용 중간 전압 Vread를 발생한다. 또한, 소거용 고전압 발생 회로(112)는 소거 동작 시에 소거용 고전압 Vpp( $\leq 20V$ )를 발생한다.

비트선 제어 회로(102)는 주로 CMOS 플립플롭으로 이루어지고, 기입을 위한 데이터의 래치나 비트선의 전위를 판독하기 위한 감지 동작, 또한 기입 후의 검증 판독을 위한 감지 동작, 또한 재기입 데이터의 래치를 행한다.

도 4A 및 도 4B는 메모리 셀 어레이의 1개의 NAND 셀 부분의 평면도와 등가 회로도, 도 5A는 도 4A의 A-A'선을 따르는 단면도, 도 5B는 도 4A의 B-B'선을 따르는 단면도이다.

소자 분리 산화막(12)으로 둘러싸인 p형 실리콘 기판(또는 p형 웰)(11)에, 복수의 NAND 셀로 이루어지는 메모리 셀 어레이가 형성되어 있다. 1개의 NAND 셀에 주목하여 설명하면, 이 예에서는 8개의 메모리 셀 M1~M8이 직렬 접속되어 1개의 NAND 셀을 구성하고 있다.

메모리 셀은 실리콘 기판(11) 상에 형성된다. 메모리 셀은 게이트 절연막(13) 상의 부유 게이트 전극(14( $14_1, 14_2, \dots, 14_8$ ))과, 중간 절연막(15) 상의 제어 게이트 전극(16( $16_1, 16_2, \dots, 16_8$ ))으로 구성된다. 제어 게이트 전극(16( $16_1, 16_2, \dots, 16_8$ ))은 워드선으로서 기능한다.

n형 확산층( $19_0, 19_1, \dots, 19_{10}$ )은 메모리 셀의 소스/드레인으로 된다. n형 확산층( $19_0, 19_1, \dots, 19_{10}$ )은 서로 인접하는 메모리 셀끼리 공용되고, 그 결과 복수의 메모리 셀이 직렬 접속되어 NAND 셀이 구성된다.

NAND 셀의 드레인측 및 소스측에는 각각 선택 게이트 전극( $14_9$ ,  $16_9$ ,  $14_{10}$ ,  $16_{10}$ )이 형성된다. 선택 게이트 전극( $14_9$ ,  $16_9$ ,  $14_{10}$ ,  $16_{10}$ )은 메모리 셀의 부유 게이트 전극( $14(14_1, 14_2, \dots, 14_8)$ ) 및 제어 게이트 전극( $16(16_1, 16_2, \dots, 16_8)$ )과 동시에 형성된다.

메모리 셀 및 선택 트랜지스터는 CVD 산화막(17)에 의해 피복된다. 비트선(18)은 CVD 산화막(17) 상에 배치되고, NAND 셀의 일단, 즉 드레인측 확산층(19)에 접속된다.

제어 게이트 전극( $16(16_1, 16_2, \dots, 16_8)$ )은 제어 게이트선 CG1, CG2, …, CG8이 되고, 선택 게이트 전극( $14_9$ ,  $16_9$ ,  $14_{10}$ ,  $16_{10}$ )은 선택 게이트선 SG1, SG2가 된다.

도 6은 매트릭스 형태로 배치된 NAND 셀로 구성되는 메모리 셀 어레이의 등가 회로를 도시하고 있다.

제어 게이트선 CG1, CG2, …, CG8 및 선택 게이트선 SG1, SG2가 연장되는 방향으로 배치되는 복수의 NAND 셀 유닛은 1개의 블록을 구성한다. 구체적으로는, 도 6의 파선으로 둘러싸인 영역이 1개의 블록이 된다. 통상의 판독/기입 동작에서는, 복수의 블록 중 1개만이 선택된다. 선택된 블록은 선택 블록이 된다.

도 7은 NAND 셀형 EEPROM의 칩 구성의 일례를 도시하고 있다.

NAND 셀형 EEPROM의 칩은 메모리 셀 어레이, 비트선 제어 회로, 로우 디코더 회로, 패드 영역 및 [주변 회로+버스 라인] 영역을 포함하고 있다.

NAND 셀형 EEPROM의 칩 구성은, 상술된 바와 같이 복수의 요소로 구성되지만, 이하(도 8 이후)의 설명에는 간단히 하기 위해, 칩 외형과 셀 어레이만을 나타내는 것으로 한다.

### (1) 실시예 1

#### 2기가비트 패키지품에 대한 칩의 치환

패키지품에 필요한 메모리 용량이 2기가비트인 경우에 대해 생각한다.

제1 세대의 EEPROM 칩은, 예를 들면 도 1에 도시한 바와 같이, 4개의 메모리 셀 어레이 Array0, Array1, Array2, Array3을 구비하고, 칩 전체의 메모리 용량은 1기가비트로 되어 있다.

이 경우, 도 1에 도시한 바와 같이, 패키지품에 필요한 메모리 용량이 1기가비트이면, 패키지품 내에는 1개의 EEPROM 칩을 넣으면 충분하다. 그러나, 본 예에서는 패키지품에 필요한 메모리 용량은 2기가비트이기 때문에, 도 2에 도시한 바와 같이, 패키지품 내에는 2개의 EEPROM 칩을 내장해야만 한다.

2개의 EEPROM 칩의 선택은 칩 어드레스에 의해 실행된다. 선택된 EEPROM 칩에서는 커맨드 com-A가 칩에 인가되면, 표 1에 나타내는 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7에의 할당에 따라 칩 전체의 Pass/Fail 신호가 출력된다. 또한, 커맨드 com-B가 칩에 인가되면, 표 2에 나타내는 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7에의 할당에 따라 메모리 셀 어레이마다의 Pass/Fail 신호가 출력된다.

그런데, 제1 세대(제1 디자인 률을 사용한 세대)보다도 후의 제2 세대(제1 디자인 률보다도 작은 제2 디자인 률을 사용한 세대)에서는 1개의 EEPROM 칩이 갖는 메모리 용량은 제1 세대의 EEPROM 칩의 메모리 용량보다도 커진다.

예를 들면, 제1 세대의 EEPROM 칩의 최대 메모리 용량이 1기가비트인 경우에는 제2 세대의 EEPROM 칩의 최대 메모리 용량은 2기가비트가 된다. 이 경우에는, 도 9에 도시한 바와 같이, 2기가비트 패키지품에 대하여 제1 세대의 2개의 EEPROM 칩을 제2 세대의 1개의 EEPROM 칩으로 치환하는 것이 가능하게 된다.

통상, 일정한 메모리 용량(예를 들면, 1 비트)당 칩 비용은 제1 세대 칩보다도 제2 세대 칩쪽이 작아지기 때문에, 이 치환에 의해 패키지품의 비용의 저하를 실현할 수 있다.

그러나, 제1 세대 칩을 제2 세대 칩으로 치환할 때에 주의해야만 하는 점은 시스템의 호환성이다.

NAND 셀형 EEPROM에는 통상, 칩의 Pass/Fail 상태를 출력하는 기능이 구비되어 있고, 예를 들면 기입/소거 동작 후에, 이를 동작이 성공하였는지, 또는 실패하였는지를 나타내는 Pass/Fail 신호를 출력하는 것이 가능하게 되어 있다. 이 Pass/Fail 신호는 Pass/Fail 출력용 커맨드가 칩에 입력된 후, I/O 패드로부터 출력된다.

즉, Pass/Fail 신호 출력 시의 흐름으로는, ① Pass/Fail 출력용 커맨드 입력→② Pass/Fail 신호의 출력이 된다.

표 3 및 표 4는 도 9의 제2 세대의 EEPROM 칩에서의 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7에의 할당의 일례를 나타내고 있다.

### [표 3]

(a) com-A

|      | 스테이터스      | 출력                          |

|------|------------|-----------------------------|

| I/00 | 칩 스테이터스-I  | Pass → 0 Fail → 1           |

| I/01 | 사용하지 않음    | 0                           |

| I/02 | 사용하지 않음    | 0                           |

| I/03 | 사용하지 않음    | 0                           |

| I/04 | 사용하지 않음    | 0                           |

| I/05 | 사용하지 않음    | 0                           |

| I/06 | Ready/Busy | Busy → 0 Ready → 1          |

| I/07 | 기입 보호      | Protect → 0 Not Protect → 1 |

### [표 4]

(b) com-B

|      | 스테이터스                           | 출력                          |

|------|---------------------------------|-----------------------------|

| I/00 | 칩 스테이터스-I                       | Pass → 0 Fail → 1           |

| I/01 | Array (0) 또는<br>Array (4) 스테이터스 | Pass → 0 Fail → 1           |

| I/02 | Array (1) 또는<br>Array (5) 스테이터스 | Pass → 0 Fail → 1           |

| I/03 | Array (2) 또는<br>Array (6) 스테이터스 | Pass → 0 Fail → 1           |

| I/04 | Array (3) 또는<br>Array (7) 스테이터스 | Pass → 0 Fail → 1           |

| I/05 | 사용하지 않음                         | 0                           |

| I/06 | Ready/Busy                      | Busy → 0 Ready → 1          |

| I/07 | 기입 보호                           | Protect → 0 Not Protect → 1 |

표 3 및 표 4의 예에서는 사용하는 데이터 입출력 단자는 I/O0~I/O7의 8개이고, 데이터 입출력 단자 I/O0~I/O7로부터 출력되는 데이터는 최대로 8 비트로 되어 있다. 이것은 본 발명에서의 칩의 치환을 이해하기 쉽게 하기 위한 것으로, 제1 세대의 EEPROM칩(표 1 및 표 2)에 맞춘 것이다.

이하의 설명에서는 이와 같이 8개의 데이터 입출력 단자 I/O0~I/O7을 사용하는 예(8 비트 출력)에 대하여 설명하지만, 본 발명은 이 경우에 한정되는 것은 아니고, 예를 들면 1 비트 출력, 2 비트 출력, 4 비트 출력, 16 비트 출력, 32 비트 출력 등의 경우에 응용하는 것도 가능하다.

표 3은 칩 전체의 Pass/Fail 신호를 출력하는 경우의 스테이터스를 나타내고 있다. 이 경우에는 Pass/Fail 출력용 커맨드로서 com-A가 칩에 인가된다.

칩 전체의 Pass/Fail 신호의 출력 동작에서는 칩 내의 모든 메모리 셀 어레이에 대하여 소정의 동작이 성공한 경우에는 Pass 신호(="0")를 출력하고, 칩 내 중 적어도 1개의 메모리 셀 어레이에 대하여 소정의 동작이 실패한 경우에는 Fail 신호(="1")를 출력한다. 칩 전체의 Pass/Fail 신호는 데이터 입출력 단자 I/O0으로부터 출력된다.

칩 전체의 Pass/Fail 신호는, 예를 들면 도 9의 EEPROM 칩의 경우, 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7로부터 각각 출력되는 Pass/Fail 신호의 논리합(OR)을 취함으로써 얻어진다(Pass="0", Fail="1"인 경우).

표 3에서의 데이터 입출력 단자 I/O0~I/O7의 스테이터스는 표 1에서의 데이터 입출력 단자 I/O0~I/O7의 스테이터스와 일치하고 있다. 예를 들면, 어느 하나의 경우도, 칩 전체의 Pass/Fail 신호는 데이터 입출력 단자 I/O0으로부터 출력된다.

따라서, 제2 세대의 EEPROM에, 칩 전체의 Pass/Fail 신호를 출력하는 기능을 형성하는 것에 관해서는 제1 세대 칩과 제2 세대 칩과의 사이에서 호환성이 유지되어 있고, 도 2에 도시하는 2개의 제1 세대칩을 이용한 2기가비트 패키지품을, 도 9에 도시하는 하나의 제2 세대칩을 이용한 2기가비트 패키지품으로 치환할 수 있다.

표 4는 칩 전체의 Pass/Fail 신호를 출력함과 함께, 복수의 메모리 셀 어레이로 이루어지는 셀 어레이 블록마다 Pass/Fail 신호를 출력하는 경우의 스테이터스를 나타내고 있다. 이 경우에는 Pass/Fail 출력용 커맨드로서 com-B가 칩에 인가된다.

복수의 메모리 셀 어레이로 이루어지는 셀 어레이 블록마다의 Pass/Fail 신호의 출력 동작에서는, 셀 어레이 블록 내의 모든 메모리 셀 어레이에 대하여 소정의 동작이 성공한 경우에는 그 셀 어레이 블록으로부터 Pass 신호(="0")를 출력하고, 셀 어레이 블록 내 중 적어도 1개의 메모리 셀 어레이에 대하여 소정의 동작이 실패한 경우에는 그 셀 어레이 블록으로부터 Fail 신호(="1")를 출력한다. 셀 어레이 블록마다의 Pass/Fail 신호는 데이터 입출력 단자 I/O1~I/O4로부터 출력된다.

셀 어레이 블록마다의 Pass/Fail 신호는, 예를 들면 도 9의 EEPROM 칩의 경우, 1개의 셀 어레이 블록을 구성하는 2개의 메모리 셀 어레이 Array0, Array4로부터 각각 출력되는 Pass/Fail 신호의 논리합(OR)을 취함으로써 얻어진다(Pass="0", Fail="1"인 경우). 다른 셀 어레이 블록에 대해서도 마찬가지이다.

메모리 셀 어레이 Array0, Array4로 이루어지는 셀 어레이 블록의 Pass/Fail 신호는 데이터 입출력 단자 I/O1로부터 출력되고, 메모리 셀 어레이 Array1, Array5로 이루어지는 셀 어레이 블록의 Pass/Fail 신호는 데이터 입출력 단자 I/O2로부터 출력되고, 메모리 셀 어레이 Array2, Array6으로 이루어지는 셀 어레이 블록의 Pass/Fail 신호는 데이터 입출력 단자 I/O3으로부터 출력되고, 메모리 셀 어레이 Array3, Array7로 이루어지는 셀 어레이 블록의 Pass/Fail 신호는 데이터 입출력 단자 I/O4로부터 출력된다.

표 4에서의 데이터 입출력 단자 I/O0~I/O7의 스테이터스는 표 2에서의 데이터 입출력 단자 I/O0~I/O7의 스테이터스와 일치하고 있다. 예를 들면, 어느 하나의 경우에도 Pass/Fail 신호는 데이터 입출력 단자 I/O0~I/O4로부터 출력된다.

따라서, 제2 세대의 EEPROM에 칩 전체의 Pass/Fail 신호를 출력하는 기능을 형성함과 함께, 복수의 메모리 셀 어레이로 이루어지는 셀 어레이 블록마다의 Pass/Fail 신호를 출력하는 기능을 형성하는 경우에는 제1 세대 칩과 제2 세대 칩과의 사이에서 호환성이 유지되어 있고, 도 2에 도시하는 2개의 제1 세대 칩을 이용한 2기가비트 패키지품을 도 9에 도시하는 1개의 제2 세대 칩을 이용한 2기가비트 패키지품으로 치환할 수 있다.

여기서, 예를 들면 2기가비트 패키지품에 대하여, 제1 세대의 2개의 칩(1개의 칩의 메모리 용량은 1기가비트)으로부터 제2 세대의 1개의 칩(1개의 칩의 메모리 용량은 2기가비트)으로 치환하는 경우에, 양 세대 간에서 시스템의 호환성을 확보하기 위한 원리에 대하여 설명한다.

우선, 2기가비트 패키지품 내에 제1 세대의 2개의 칩을 탑재하는 시스템의 경우에는, 도 2에 도시한 바와 같이, 1 비트의 칩 어드레스에 의해 칩의 선택을 행한다. Pass/Fail 신호는 선택된 칩만으로부터 출력된다. 이 때의 선택된 칩에서의 데이터 입출력 단자 I/O0~I/O7의 스테이터스는, 예를 들면 표 2에 도시된 바와 같다.

그런데, 패키지품에 접속된 외부 장치로부터 패키지품을 본 경우에는 도 2의 패키지품은 도 8에 도시한 바와 같은 칩 이미지가 된다. 즉, 도 2의 패키지품은 도 8의 패키지품과 같다고 간주할 수 있다. 도 8에서는 패키지품 내에는 1개의 칩이 탑재되고, 그 칩 내에는 4개의 메모리 셀 어레이 Array0, Array1, Array2, Array3이 배치된다. 또한, 1개의 메모리 셀 어레이 Arrayi(i=0, 1, 2, 3)는 2개의 영역을 구비하고, 그 2개의 영역은 칩 어드레스에 의해 선택된다. 표 2의 스테이터스 하에서, 4개의 메모리 셀 어레이 Array0, Array1, Array2, Array3으로부터는 Pass/Fail 신호가 출력된다.

도 8에서, 4개의 메모리 셀 어레이(점선으로 둘러싼 부분) Array0, Array1, Array2, Array3을, 각각 셀 어레이 블록이라고 생각하고, 1개의 메모리 셀 어레이 Arrayi 내의 2개의 영역을, 각각 독립된 메모리 셀 어레이라고 생각하면, 도 8의 패키지품은 제2 세대 칩을 사용한 도 9의 패키지품과 같아진다.

단, 도 9의 패키지품에서는 도 8의 칩 어드레스에 대응하지는 않고, 또한 1칩 내에는 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7이 존재한다.

통상, 기입, 소거, 판독 등의 동작에서는 고속화를 실현하기 위해서 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7은 병렬 동작한다. 이 때문에, 제2 세대 칩에서 메모리 셀 어레이마다의 Pass/Fail 신호의 출력 형식을 채용하면, 적어도 8개의 Pass/Fail 신호를 출력하기 위해 8개의 데이터 입출력 단자가 필요하게 된다.

이 경우에는, 표 2에 나타내는 데이터 입출력 단자의 스테이터스와 같은 스테이터스를 채용할 수 없고, 제1 세대 칩과 제2 세대 칩과의 사이에서 시스템의 호환성을 확보할 수 없다.

그래서, 도 9에 도시한 바와 같은 제2 세대 칩에서는 2개의 메모리 셀 어레이를 포함하는 셀 어레이 블록(점선으로 둘러싼 부분)으로부터 1개의 Pass/Fail 신호를 출력하는 시스템을 구성한다.

이 경우에는, 도 9에서의 4개의 셀 어레이 블록으로부터 4개의 Pass/Fail 신호가 출력되게 되기 때문에 표 4에 나타낸 바와 같은 데이터 입출력 단자 I/O0~I/O7의 스테이터스에 의해 Pass/Fail 신호를 출력할 수 있다. 즉, 제1 세대 칩과 제2 세대 칩과의 사이에서 시스템의 호환성을 확보할 수 있다.

또, 셀 어레이 블록으로부터 1개의 Pass/Fail 신호를 출력하는 시스템이란, 예를 들면 셀 어레이 블록을 구성하는 복수의 메모리 셀 어레이로부터 각각 출력되는 Pass/Fail 신호의 논리합(OR)을 취하고, 이것을 셀 어레이 블록의 Pass/Fail 신호로 하는 시스템을 말한다(Pass="0", Fail="1"인 경우).

본 예에서는 제2 세대 칩의 메모리 셀 어레이의 수(메모리 용량)가 제1 세대 칩의 메모리 셀 어레이의 수(메모리 용량)의 2배가 되는 경우에 대하여 설명하였지만, 본 발명은 일반적으로, 메모리 셀 어레이의 수가 n(n은 자연수)배가 되는 경우에 적용할 수 있다. 이 경우에는 셀 어레이 블록 내의 메모리 셀 어레이의 수는 모든 셀 어레이 블록 사이에서 같아진다.

또한, 이들의 경우에 한하지 않고, 본 발명은 제2 세대 칩의 메모리 셀 어레이의 수가 제1 세대 칩의 메모리 셀 어레이의 수보다도 단순히 많아지는 경우에도 응용할 수 있다. 이 경우에는 셀 어레이 블록 내의 메모리 셀 어레이의 수는 일정해지지 않는다.

본 예에서는 셀 어레이 블록으로부터는 그 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호의 논리합을 취한 신호가 출력되지만, Pass="1", Fail="0"인 경우에는 논리곱(엔드)이 된다.

또한, 본 예에서는 셀 어레이 블록으로부터는 그 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호의 논리합 또는 논리곱을 취한 1개의 신호를 출력하지만, 이에 대신하여 그 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호를 선택적으로 출력하도록 해도 된다.

이상과 같이, 본 발명에 따르면, 칩 전체의 Pass/Fail 신호를 출력하는 기능 및 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능 외에, 복수의 메모리 셀 어레이로 이루어지는 셀 어레이 블록을 신규로 설정하고, 셀 어레이 블록마다의 Pass/Fail 신호를 출력하는 기능을 새롭게 설치하고 있다.

따라서, Pass/Fail 신호를 출력하는 시스템에 관하여 전세대 칩과 후세대 칩과의 사이에 호환성을 갖게 할 수 있기 때문에, 동일 패키지품에 대하여 전세대 칩으로부터 후세대 칩으로의 치환을 쉽게 하여 칩 비용의 절감을 도모할 수 있다.

다음에, 상술한 본 발명의 불휘발성 반도체 메모리에, 추가로 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가하는 예에 대하여 설명한다.

표 5는 도 9의 제2 세대의 EEPROM 칩에서의 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7로의 할당의 일례를 나타내고 있다.

### [표 5]

(c) com-C

|      | 스테이터스           | 출력       |          |

|------|-----------------|----------|----------|

| I/00 | Array (0) 스테이터스 | Pass → 0 | Fail → 1 |

| I/01 | Array (1) 스테이터스 | Pass → 0 | Fail → 1 |

| I/02 | Array (2) 스테이터스 | Pass → 0 | Fail → 1 |

| I/03 | Array (3) 스테이터스 | Pass → 0 | Fail → 1 |

| I/04 | Array (4) 스테이터스 | Pass → 0 | Fail → 1 |

| I/05 | Array (5) 스테이터스 | Pass → 0 | Fail → 1 |

| I/06 | Array (6) 스테이터스 | Pass → 0 | Fail → 1 |

| I/07 | Array (7) 스테이터스 | Pass → 0 | Fail → 1 |

동일 패키지품에 대하여, 제1 세대 칩으로부터 제2 세대 칩으로의 치환만을 고려한 경우에는, 예를 들면 도 2에 도시하는 제1 세대 칩에서의 데이터 입출력 단자 I/O0~I/O7의 스테이터스(표 1 및 표 2)에 대하여, 도 9에 도시한 제2 세대 칩에서의 데이터 입출력 단자 I/O0~I/O7의 스테이터스(표 3 및 표 4)를 규정하면 충분하다.

그러나, 예를 들면 도 9에 도시하는 제2 세대 칩의 특징 중 하나는 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7을 병렬 동작시킴으로 인한 고속 동작 기능에 있다.

이 고속 동작 기능을 실현적인 것으로 하기 위해서는, 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7을 병렬 동작시킴과 함께, 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가하는 것이 중요하게 된다.

그래서, 도 9에 도시하는 제2 세대의 EEPROM 칩에 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가한다. 이 기능을 실현하기 위해서는, 예를 들면 Pass/Fail 출력용 커맨드로서 com-C를 칩에 인가하면 된다.

이 경우, 예를 들면 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7에의 할당은 표 5에 도시된 바와 같다. 즉, 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7로부터 출력되는 8개의 Pass/Fail 신호는 8개의 데이터 입출력 단자 I/O0~I/O7로부터 출력된다.

이와 같이, 본 예에서는 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가하고 있기 때문에, 동일 패키지 품에 대하여 제1 세대 칩으로부터 제2 세대 칩으로의 치환을 용이하게 할 수 있음과 함께, 제2 세대 칩에서의 고속 동작 기능을 실현할 수 있다.

다음에, 상술한 본 발명의 불휘발성 반도체 메모리의 변형예에 대하여 설명한다.

상술한 예에서는, 셀 어레이 블록으로부터는 그 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호의 논리 합 또는 논리곱을 취한 1개의 신호를 출력하였지만, 본 예에서는 그 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호를 선택적으로 출력한다.

이와 같이, 본 예에서는 셀 어레이 블록 내의 선택된 1개의 메모리 셀 어레이의 Pass/Fail 신호를 셀 어레이 블록마다 출력한다.

표 6~표 9는 도 9의 제2 세대의 EEPROM 칩에서의 Pass/Fail 신호의 데이터 입출력 단자 I/O0~I/O7로의 할당의 일례를 나타내고 있다.

### [표 6]

(a) com-A

|      | 스테이터스      | 출력                          |

|------|------------|-----------------------------|

| I/00 | 첨 스테이터스-I  | Pass → 0 Fail → 1           |

| I/01 | 사용하지 않음    | 0                           |

| I/02 | 사용하지 않음    | 0                           |

| I/03 | 사용하지 않음    | 0                           |

| I/04 | 사용하지 않음    | 0                           |

| I/05 | 사용하지 않음    | 0                           |

| I/06 | Ready/Busy | Busy → 0 Ready → 1          |

| I/07 | 기입 보호      | Protect → 0 Not Protect → 1 |

커맨드 com-A가 입력된 경우에는 칩 전체의 Pass/Fail 신호가 출력된다. 이 때의 데이터 입출력 단자 I/O0~I/O7의 스테이터스는 표 6에 나타낸 바와 같다.

[표 7]

## (b) com-B

|      | 스테이터스            | 출력          |                 |

|------|------------------|-------------|-----------------|

| I/00 | 칩 스테이터스-I        | Pass → 0    | Fail → 1        |

| I/01 | Array (0) Status | Pass → 0    | Fail → 1        |

| I/02 | Array (1) Status | Pass → 0    | Fail → 1        |

| I/03 | Array (2) Status | Pass → 0    | Fail → 1        |

| I/04 | Array (3) Status | Pass → 0    | Fail → 1        |

| I/05 | 사용하지 않음          | 0           |                 |

| I/06 | Ready/Busy       | Busy → 0    | Ready → 1       |

| I/07 | 기입 보호            | Protect → 0 | Not Protect → 1 |

커맨드 com-B가 입력된 경우에는 셀 어레이 블록마다의 Pass/Fail 신호가 출력된다. 이 때의 데이터 입출력 단자 I/00~I/07의 스테이터스는 표 7에 도시된 바와 같다.

4개의 셀 어레이 블록 내의 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7 중 4개의 메모리 셀 어레이 Array0, Array1, Array2, Array3이 선택된다. 이를 선택된 메모리 셀 어레이 Array0, Array1, Array2, Array3의 Pass/Fail 신호가 셀 어레이 블록마다 출력된다.

[표 8]

## (c) com-C

|      | 스테이터스            | 출력          |                 |

|------|------------------|-------------|-----------------|

| I/00 | 칩 스테이터스-I        | Pass → 0    | Fail → 1        |

| I/01 | Array (4) Status | Pass → 0    | Fail → 1        |

| I/02 | Array (5) Status | Pass → 0    | Fail → 1        |

| I/03 | Array (6) Status | Pass → 0    | Fail → 1        |

| I/04 | Array (7) Status | Pass → 0    | Fail → 1        |

| I/05 | 사용하지 않음          | 0           |                 |

| I/06 | Ready/Busy       | Busy → 0    | Ready → 1       |

| I/07 | 기입 보호            | Protect → 0 | Not Protect → 1 |

커맨드 com-C가 입력된 경우에는 셀 어레이 블록마다의 Pass/Fail 신호가 출력된다. 이 때의 데이터 입출력 단자 I/00~I/07의 스테이터스는 표 8에 나타낸 바와 같다.

4개의 셀 어레이 블록 내 중 8개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7 중 4개의 메모리 셀 어레이 Array4, Array5, Array6, Array7이 선택된다. 이를 선택된 메모리 셀 어레이 Array4, Array5, Array6, Array7의 Pass/Fail 신호가 셀 어레이 블록마다 출력된다.

[표 9]

(d) com-D

|      | 스테이터스            | 출력       |          |

|------|------------------|----------|----------|

| I/00 | Array (0) Status | Pass → 0 | Fail → 1 |

| I/01 | Array (1) Status | Pass → 0 | Fail → 1 |

| I/02 | Array (2) Status | Pass → 0 | Fail → 1 |

| I/03 | Array (3) Status | Pass → 0 | Fail → 1 |

| I/04 | Array (4) Status | Pass → 0 | Fail → 1 |

| I/05 | Array (5) Status | Pass → 0 | Fail → 1 |

| I/06 | Array (6) Status | Pass → 0 | Fail → 1 |

| I/07 | Array (7) Status | Pass → 0 | Fail → 1 |

커맨드 com-D가 입력된 경우에는 메모리 셀 어레이마다의 Pass/Fail 신호가 출력된다. 이 때의 데이터 입출력 단자 I/O0~I/O7의 스테이터스는 표 9에 도시된 바와 같다.

본 예에서는 표 6의 스테이터스는 표 1의 스테이터스와 동일하다. 또한, 표 7 및 표 8의 스테이터스는 표 2의 스테이터스와 동일하다. 따라서, 동일 패키지품에 대하여 제1 세대 칩으로부터 제2 세대 칩으로의 치환을 용이하게 할 수 있다. 또한, 표 9에 나타낸 바와 같은 메모리 셀 어레이마다의 Pass/Fail 신호의 출력 기능을 형성하면, 제2 세대 칩에서의 고속 동작 기능을 실현할 수 있다.

이상, 본 발명의 설명을 행하였지만, 본 발명은 상술한 예에 한정되는 것은 아니고 여러가지 변경 가능하다.

상술한 예에서는 제1 세대의 EEPROM 칩이 4개의 메모리 셀 어레이를 구비하고, 제2 세대의 EEPROM 칩이 8개의 메모리 셀 어레이를 갖는 경우에, 동일 패키지품에 대하여 제1 세대의 2개의 칩을 제2 세대의 1개의 칩으로 치환하는 예에 대하여 설명하였다.

이에 대하여, 예를 들면 본 발명은 제1 세대의 EEPROM 칩이 4개의 메모리 셀 어레이를 갖고, 제2 세대의 EEPROM 칩이 8개의 메모리 셀 어레이를 갖고, 제3 세대의 EEPROM 칩이 16개의 메모리 셀 어레이를 갖는 경우에, 동일 패키지품에 대하여, 제1 세대의 4개의 칩을 제2 세대의 2개의 칩으로 치환하고, 또는 제2 세대의 2개의 칩을 제3 세대의 1개의 칩으로 치환하는 경우에도 적용할 수 있다.

## (2) 실시예 2

### 4기가비트 패키지품에 대한 칩의 치환

도 10은 4기가비트 패키지품에 제1 세대 칩을 4개 탑재한 예를 나타내고 있다. 도 11은 4기가비트 패키지품에 제2 세대 칩을 2개 탑재한 예를 나타내고 있다. 도 12는 4기가비트 패키지품에 제3 세대 칩을 1개 탑재한 예를 나타내고 있다.

이와 같이, 동일 패키지품에 대하여 제1 세대 칩으로부터 제2 세대 칩으로의 치환을 실행하고, 또한 제2 세대 칩으로부터 제3 세대 칩으로의 치환을 실행할 수 있다.

여기서, 제1 세대 칩은 4개의 메모리 셀 어레이와 1기가비트의 메모리 용량을 구비하고, 제2 세대 칩은 8개의 메모리 셀 어레이와 2기가비트의 메모리 용량을 구비하고, 제3 세대 칩은 16개의 메모리 셀 어레이와 4기가비트의 메모리 용량을 갖는 것으로 한다.

도 10에 도시하는 제1 세대의 EEPROM 칩은 도 2에 도시하는 제1 세대의 EEPROM 칩과 마찬가지로, 표 1에 나타내는 칩 전체의 Pass/Fail 신호를 출력하는 기능 및 표 2에 나타내는 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 갖고 있다.

도 11에 도시하는 제2 세대의 EEPROM 칩은 도 9에 도시하는 제2 세대의 EEPROM 칩과 마찬가지로, 표 3 또는 표 6에 나타내는 칩 전체의 Pass/Fail 신호를 출력하는 기능 및 표 4 또는 표 7, 표 8에 나타내는 셀 어레이 블록마다의 Pass/Fail 신호를 출력하는 기능을 갖고 있다. 또한, 도 11에 도시한 제2 세대의 EEPROM 칩에는, 도 9에 도시한 제2 세대의 EEPROM 칩과 마찬가지로, 표 5 또는 표 9에 나타내는 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가해도 된다.

도 12에 도시하는 제3 세대의 EEPROM 칩은 표 10에 나타내는 칩 전체의 Pass/Fail 신호를 출력하는 기능 및 표 11에 나타내는 셀 어레이 블록마다의 Pass/Fail 신호를 출력하는 기능을 갖고 있다.

표 11의 기능은 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호의 논리합 또는 논리곱을 취하는 것이지만, 표 7 및 표 8의 경우와 마찬가지로, 선택된 메모리 셀 어레이의 Pass/Fail 신호를 출력하는 기능으로 해도 된다.

### [표 10]

(a) com-A

|      | 스테이터스      | 출력                          |

|------|------------|-----------------------------|

| I/00 | 칩 스테이터스-I  | Pass → 0 Fail → 1           |

| I/01 | 사용하지 않음    | 0                           |

| I/02 | 사용하지 않음    | 0                           |

| I/03 | 사용하지 않음    | 0                           |

| I/04 | 사용하지 않음    | 0                           |

| I/05 | 사용하지 않음    | 0                           |

| I/06 | Ready/Busy | Busy → 0 Ready → 1          |

| I/07 | 기입 보호      | Protect → 0 Not Protect → 1 |

[표 11]

(b) com-B

|      | 스테이터스                                                                        | 출력                          |

|------|------------------------------------------------------------------------------|-----------------------------|

| I/00 | 칩 스테이터스-I<br>Array (0),<br>Array (4),<br>Array (8) 또는<br>Array (12)<br>스테이터스 | Pass → 0 Fail → 1           |

| I/01 | Array (1),<br>Array (5),<br>Array (9) 또는<br>Array (13)<br>스테이터스              | Pass → 0 Fail → 1           |

| I/02 | Array (2),<br>Array (6),<br>Array (10) 또는<br>Array (14)<br>스테이터스             | Pass → 0 Fail → 1           |

| I/03 | Array (3),<br>Array (7),<br>Array (11) 또는<br>Array (15)<br>스테이터스             | Pass → 0 Fail → 1           |

| I/04 | 사용하지 않음                                                                      | 0                           |

| I/05 | Ready/Busy                                                                   | Busy → 0 Ready → 1          |

| I/06 | 기입 보호                                                                        | Protect → 0 Not Protect → 1 |

| I/07 |                                                                              |                             |

또한, 도 12에 도시하는 제3 세대의 EEPROM 칩에는 표 12 및 표 13에 나타내는 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가해도 된다.

[표 12]

(c) com-C

|      | 스테이터스            | 출력                |

|------|------------------|-------------------|

| I/00 | Array (0) Status | Pass → 0 Fail → 1 |

| I/01 | Array (1) Status | Pass → 0 Fail → 1 |

| I/02 | Array (2) Status | Pass → 0 Fail → 1 |

| I/03 | Array (3) Status | Pass → 0 Fail → 1 |

| I/04 | Array (4) Status | Pass → 0 Fail → 1 |

| I/05 | Array (5) Status | Pass → 0 Fail → 1 |

| I/06 | Array (6) Status | Pass → 0 Fail → 1 |

| I/07 | Array (7) Status | Pass → 0 Fail → 1 |

[표 13]

(d) com-D

|      | 스테이터스            | 출력       |          |

|------|------------------|----------|----------|

| I/00 | Array (8) 스테이터스  | Pass → 0 | Fail → 1 |

| I/01 | Array (9) 스테이터스  | Pass → 0 | Fail → 1 |

| I/02 | Array (10) 스테이터스 | Pass → 0 | Fail → 1 |

| I/03 | Array (11) 스테이터스 | Pass → 0 | Fail → 1 |

| I/04 | Array (12) 스테이터스 | Pass → 0 | Fail → 1 |

| I/05 | Array (13) 스테이터스 | Pass → 0 | Fail → 1 |

| I/06 | Array (14) 스테이터스 | Pass → 0 | Fail → 1 |

| I/07 | Array (15) 스테이터스 | Pass → 0 | Fail → 1 |

도 12에서는, 16개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7, Array8, Array9, Array10, Array11, Array12, Array13, Array14, Array15에 대하여, 데이터 입출력 단자 I/O0~I/O7은 8개밖에 없기 때문에, 표 12 및 표 13에 나타낸 바와 같이, 메모리 셀 어레이마다의 Pass/Fail 신호는 2회(com-C, com-D)로 판독한다.

표 12 및 표 13의 기능은 셀 어레이 블록 내의 선택된 복수의 메모리 셀 어레이의 Pass/Fail 신호를 셀 어레이 블록마다 출력하는 기능으로 할 수 있다.

도 13은 4기가비트 패키지품에, 제2 세대 칩을 2개 탑재한 예를 나타내고 있다. 도 14는 외부 장치로부터 도 13의 패키지 품을 본 경우의 칩 이미지를 나타내고 있다. 도 15는 4기가비트 패키지품에 제3 세대 칩을 1개 탑재한 예를 나타내고 있다.

도 13에 도시하는 제2 세대의 EEPROM 칩은 도 9에 도시하는 제2 세대의 EEPROM 칩과 마찬가지로, 표 3 또는 표 6에 나타내는 칩 전체의 Pass/Fail 신호를 출력하는 기능 및 표 4 또는 표 7, 표 8에 나타내는 셀 어레이 블록마다의 Pass/Fail 신호를 출력하는 기능을 갖고 있다. 또한, 도 11에 도시하는 제2 세대의 EEPROM 칩에는 도 9에 도시하는 제2 세대의 EEPROM 칩과 마찬가지로, 표 5 또는 표 9에 나타내는 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가해도 된다.

도 15에 도시하는 제3 세대의 EEPROM 칩은 표 14에 나타내는 칩 전체의 Pass/Fail 신호를 출력하는 기능 및 표 15에 나타내는 셀 어레이 블록마다의 Pass/Fail 신호를 출력하는 기능을 갖고 있다.

표 15의 기능은 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호의 논리합 또는 논리곱을 취하는 것이지만, 표 7 및 표 8의 경우와 마찬가지로, 선택된 메모리 셀 어레이의 Pass/Fail 신호를 출력하는 기능으로 해도 된다.

[표 14]

(a) com-A

|      | 스테이터스      | 출력                          |

|------|------------|-----------------------------|

| I/00 | 칩 스테이터스-I  | Pass → 0 Fail → 1           |

| I/01 | 사용하지 않음    | 0                           |

| I/02 | 사용하지 않음    | 0                           |

| I/03 | 사용하지 않음    | 0                           |

| I/04 | 사용하지 않음    | 0                           |

| I/05 | 사용하지 않음    | 0                           |

| I/06 | Ready/Busy | Busy → 0 Ready → 1          |

| I/07 | 기입 보호      | Protect → 0 Not Protect → 1 |

[표 15]

(b) com-B

|      | 스테이터스                                                            | 출력                          |

|------|------------------------------------------------------------------|-----------------------------|

| I/00 | 칩 스테이터스-I                                                        | Pass → 0 Fail → 1           |

| I/01 | Array (0),<br>Array (4),<br>Array (8) 또는<br>Array (12)<br>스테이터스  | Pass → 0 Fail → 1           |

| I/02 | Array (1),<br>Array (5),<br>Array (9) 또는<br>Array (13)<br>스테이터스  | Pass → 0 Fail → 1           |

| I/03 | Array (2),<br>Array (6),<br>Array (10) 또는<br>Array (14)<br>스테이터스 | Pass → 0 Fail → 1           |

| I/04 | Array (3),<br>Array (7),<br>Array (11) 또는<br>Array (15)<br>스테이터스 | Pass → 0 Fail → 1           |

| I/05 | 사용하지 않음                                                          | 0                           |

| I/06 | Ready/Busy                                                       | Busy → 0 Ready → 1          |

| I/07 | 기입 보호                                                            | Protect → 0 Not Protect → 1 |

또한, 도 15에 도시하는 제3 세대의 EEPROM 칩에는 표 16 및 표 17에 나타내는 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 부가해도 된다.

[표 16]

(c) com-C

|      | 스테이터스           | 출력                |

|------|-----------------|-------------------|

| I/00 | Array (0) 스테이터스 | Pass → 0 Fail → 1 |

| I/01 | Array (1) 스테이터스 | Pass → 0 Fail → 1 |

| I/02 | Array (2) 스테이터스 | Pass → 0 Fail → 1 |

| I/03 | Array (3) 스테이터스 | Pass → 0 Fail → 1 |

| I/04 | Array (4) 스테이터스 | Pass → 0 Fail → 1 |

| I/05 | Array (5) 스테이터스 | Pass → 0 Fail → 1 |

| I/06 | Array (6) 스테이터스 | Pass → 0 Fail → 1 |

| I/07 | Array (7) 스테이터스 | Pass → 0 Fail → 1 |

[표 17]

(d) com-D

|      | 스테이터스            | 출력                |

|------|------------------|-------------------|

| I/00 | Array (8) 스테이터스  | Pass → 0 Fail → 1 |

| I/01 | Array (9) 스테이터스  | Pass → 0 Fail → 1 |

| I/02 | Array (10) 스테이터스 | Pass → 0 Fail → 1 |

| I/03 | Array (11) 스테이터스 | Pass → 0 Fail → 1 |

| I/04 | Array (12) 스테이터스 | Pass → 0 Fail → 1 |

| I/05 | Array (13) 스테이터스 | Pass → 0 Fail → 1 |

| I/06 | Array (14) 스테이터스 | Pass → 0 Fail → 1 |

| I/07 | Array (15) 스테이터스 | Pass → 0 Fail → 1 |

도 15에서는 16개의 메모리 셀 어레이 Array0, Array1, Array2, Array3, Array4, Array5, Array6, Array7, Array8, Array9, Array10, Array11, Array12, Array13, Array14, Array15에 대하여, 데이터 입출력 단자 I/O0~I/O7은 8개밖에 없기 때문에, 표 16 및 표 17에 나타낸 바와 같이, 메모리 셀 어레이마다의 Pass/Fail 신호는 2회(com-C, com-D)로 판독한다.

본 예에서는, 또한 표 15의 셀 어레이 블록 내의 복수의 메모리 셀 어레이의 Pass/Fail 신호의 논리합 또는 논리곱을 취하는 기능과, 표 16 및 표 17의 메모리 셀 어레이마다의 Pass/Fail 신호를 출력하는 기능을 조합해도 된다.

[표 18]

(e) com-E

|      | 스테이터스                            | 출력                |

|------|----------------------------------|-------------------|

| I/00 | Array (0) 또는<br>Array (8) 스테이터스  | Pass → 0 Fail → 1 |

| I/01 | Array (1) 또는<br>Array (9) 스테이터스  | Pass → 0 Fail → 1 |

| I/02 | Array (2) 또는<br>Array (10) 스테이터스 | Pass → 0 Fail → 1 |

| I/03 | Array (3) 또는<br>Array (11) 스테이터스 | Pass → 0 Fail → 1 |

| I/04 | Array (4) 또는<br>Array (12) 스테이터스 | Pass → 0 Fail → 1 |

| I/05 | Array (5) 또는<br>Array (13) 스테이터스 | Pass → 0 Fail → 1 |

| I/06 | Array (6) 또는<br>Array (14) 스테이터스 | Pass → 0 Fail → 1 |

| I/07 | Array (7) 또는<br>Array (15) 스테이터스 | Pass → 0 Fail → 1 |

표 18의 기능은, 예를 들면 도 15의 메모리 셀 어레이 Array0, Array8의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array0, Array8로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서, 데이터 입출력 단자 I/O0으로부터 출력한 것이다.

마찬가지로, 메모리 셀 어레이 Array1, Array9의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array1, Array9로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서, 데이터 입출력 단자 I/O1로부터 출력한다.

메모리 셀 어레이 Array2, Array10의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array2, Array10으로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서, 데이터 입출력 단자 I/O2로부터 출력한다.

메모리 셀 어레이 Array3, Array11의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array3, Array11로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서 데이터 입출력 단자 I/O3으로 출력한다.

메모리 셀 어레이 Array4, Array12의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array4, Array12로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서 데이터 입출력 단자 I/O4로부터 출력한다.

메모리 셀 어레이 Array5, Array13의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array5, Array13으로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서 데이터 입출력 단자 I/O5로부터 출력한다.

메모리 셀 어레이 Array6, Array14의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array6, Array14로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서, 데이터 입출력 단자 I/O6으로부터 출력한다.

메모리 셀 어레이 Array7, Array15의 Pass/Fail 신호의 논리합 또는 논리곱을 취하고, 그 결과를 메모리 셀 어레이 Array7, Array15로 이루어지는 셀 어레이 블록의 Pass/Fail 출력으로서, 데이터 입출력 단자 I/O7로부터 출력한다.

(3) 기타

상술한 예에서는 1개의 NAND 셀을 구성하는 직렬 접속된 메모리 셀의 수가 8개의 경우에 대하여 설명하였지만, 1개의 NAND 셀은 8개가 아니고, 예를 들면 2, 4, 16, 32, 64개 등이어도 된다.

본 발명은 2개의 선택 트랜지스터 사이에 1개의 메모리 셀만이 배치되는 소위 3tr-NAND 셀에도 적용할 수 있다.

상술한 예에서는 NAND 셀형 EEPROM에 대하여 설명을 행하였지만, 본 발명은 NAND 셀형 EEPROM 이외의 디바이스, 예를 들면 NOR 셀형 EEPROM, DINOR 셀형 EEPROM, AND 셀형 EEPROM, 선택 트랜지스터가 내장된 NOR 셀형 EEPROM 등에도 적용할 수 있다.

또, DINOR 셀형 EEPROM의 상세에 관해서는, 예를 들면 "H. Onoda et al., IEDM Tech. Digest, 1992, pp.599-602"에, AND 셀형 EEPROM의 상세에 대해서는, 예를 들면 "H.Kume et al., IEDM Tech. Digest, 1992, pp.991-993"에 기재되어 있다.

본 발명은 주로 전기적으로 재기입이 가능한 불휘발성 반도체 메모리에 적용되지만, 예를 들면 그 외의 불휘발성 반도체 메모리, DRAM이나 SRAM 등에도 적용할 수 있다고 생각된다.

### 발명의 효과

이상, 실시예를 이용하여 본 발명의 설명을 행하였지만, 본 발명은 그 요지를 일탈하지 않는 범위에서 여러가지 변경 가능하다.

본 발명의 예에 따르면, 칩 동작에 관한 Pass/Fail 결과를 출력함에 있어서, 칩 전체의 Pass/Fail 신호, 메모리 셀 어레이마다의 Pass/Fail 신호 외에, 칩 내의 복수의 메모리 셀 어레이로 이루어지는 셀 어레이 블록마다의 Pass/Fail 신호를 출력 가능하게 하였다. 이에 의해, 후세대 칩 내에 셀 어레이 블록을 1개 이상 형성함으로써 동일 패키지품에 대하여 전세대 칩으로부터 후세대 칩으로의 치환이 가능하게 된다.

또, 전세대 칩으로부터 후세대 칩으로의 치환에 있어서는 후세대 칩 내의 셀 블록의 수는 전세대 칩 내의 메모리 셀 어레이의 수 또는 셀 블록의 수와 동일하게 하는 것이 바람직하다.

이 치환이 가능해짐으로써, 칩 비용이 낮은 후세대 칩을 대용량 패키지품에 대하여 사용할 수 있어, 그 결과 저렴한 패키지품을 실현할 수 있다.

상술한 실시예는 모든 점에서 예시이며 제한적인 것은 아니라고 생각되어야 한다. 본 발명의 범위는 상기한 실시예의 설명이 아니라 특허 청구 범위에 의해 정의되며, 또한 특허 청구의 범위와 균등한 의미 및 범위 내에서의 모든 변경을 포함하는 것으로 의도되어야 한다.

### (57) 청구의 범위

#### 청구항 1.

매트릭스 형태로 배치되는 복수의 메모리 셀 유닛으로 구성되는 복수의 메모리 셀 어레이를 포함하며,

상기 복수의 메모리 셀 어레이에는 2개 이상의 메모리 셀 어레이로 이루어지는 복수의 셀 어레이 블록을 구성하고, 셀 어레이 블록마다 동작의 성공 또는 실패를 나타내는 제1 Pass/Fail 신호를 출력하는 반도체 메모리.

#### 청구항 2.

제1항에 있어서,

상기 동작은 상기 복수의 메모리 셀 어레이에 대하여 병렬로 실행되는 반도체 메모리.

### 청구항 3.

제1항에 있어서,

상기 동작은 기입/소거 동작인 반도체 메모리.

### 청구항 4.

제1항에 있어서,

상기 제1 Pass/Fail 신호는 상기 2개 이상의 메모리 셀 어레이의 모든 동작이 성공하였는지, 또는 상기 2개 이상의 메모리 셀 어레이 중 적어도 1개의 동작이 실패하였는지를 나타내는 Pass/Fail 신호인 반도체 메모리.

### 청구항 5.

제4항에 있어서,

상기 복수의 메모리 셀 어레이의 모든 동작이 성공하였는지, 또는 상기 복수의 메모리 셀 어레이 중 적어도 1개의 동작이 실패하였는지를 나타내는 칩 전체의 제2 Pass/Fail 신호를 출력하는 반도체 메모리.

### 청구항 6.

제1항에 있어서,

상기 제1 Pass/Fail 신호는 상기 2개 이상의 메모리 셀 어레이 중 선택된 1개의 메모리 셀 어레이에 대하여, 동작이 성공하였는지, 또는 실패하였는지를 나타내는 Pass/Fail 신호인 반도체 메모리.

### 청구항 7.

제6항에 있어서,

상기 복수의 메모리 셀 어레이의 모든 동작이 성공하였는지, 또는 상기 복수의 메모리 셀 어레이 중 적어도 1개의 동작이 실패하였는지를 나타내는 칩 전체의 제2 Pass/Fail 신호를 출력하는 반도체 메모리.

### 청구항 8.

제7항에 있어서,

상기 제1 Pass/Fail 신호를 출력할지, 또는 상기 제2 Pass/Fail 신호를 출력할지는 커맨드 신호에 의해 결정되는 반도체 메모리.

### 청구항 9.

제4항에 있어서,

메모리 셀 어레이마다 동작의 성공 또는 실패를 나타내는 메모리 셀 어레이마다의 제2 Pass/Fail 신호를 출력하는 반도체 메모리.

#### 청구항 10.

제9항에 있어서,

상기 제1 Pass/Fail 신호를 출력할지, 또는 상기 제2 Pass/Fail 신호를 출력할지는 커맨드 신호에 의해 결정되는 반도체 메모리.

#### 청구항 11.

제6항에 있어서,

메모리 셀 어레이마다 동작의 성공 또는 실패를 나타내는 메모리 셀 어레이마다의 제2 Pass/Fail 신호를 출력하는 반도체 메모리.

#### 청구항 12.

제11항에 있어서,

상기 제1 Pass/Fail 신호를 출력할지, 또는 상기 제2 Pass/Fail 신호를 출력할지는 커맨드 신호에 의해 결정되는 반도체 메모리.

#### 청구항 13.

제4항에 있어서,

셀 어레이 블록마다 상기 2개 이상의 메모리 셀 어레이 중 적어도 n개(n은 복수)의 메모리 셀 어레이의 동작의 성공 또는 실패를 나타내는 적어도 n개의 제2 Pass/Fail 신호를 출력하는 반도체 메모리.

#### 청구항 14.

제13항에 있어서,

상기 제1 Pass/Fail 신호를 출력할지, 또는 상기 제2 Pass/Fail 신호를 출력할지는 커맨드 신호에 의해 결정되는 반도체 메모리.

#### 청구항 15.

제6항에 있어서,

셀 어레이 블록마다, 상기 2개 이상의 메모리 셀 어레이 중 적어도 n개(n은 복수)의 메모리 셀 어레이의 동작의 성공 또는 실패를 나타내는 적어도 n개의 제2 Pass/Fail 신호를 출력하는 반도체 메모리.

**청구항 16.**

제15항에 있어서,

상기 제1 Pass/Fail 신호를 출력할지, 또는 상기 제2 Pass/Fail 신호를 출력할지는 커맨드 신호에 의해 결정되는 반도체 메모리.

**청구항 17.**

제1항에 있어서,

상기 복수의 메모리 셀 유닛 각각은 1개 이상의 메모리 셀을 포함하는 반도체 메모리.

**청구항 18.**

제17항에 있어서,

상기 메모리 셀은 전기적으로 데이터의 재기입이 가능한 불휘발성 메모리인 반도체 메모리.

**청구항 19.**

제1항에 있어서,

상기 복수의 메모리 셀 유닛 각각은 NAND 셀형을 포함하는 반도체 메모리.

**도면**

도면1

## 도면2

2기가 비트 패키지품(제1 세대품이 사용됨)

도면3

도면4a

도면4b

도면5a

도면5b

도면6

## 도면7

1기가 비트(제1 세대)칩의 구조

## 도면8

외부 장치에서 도15의 패키지풀을 본 경우의 칩 이미지

## 도면9

## 도면10

4 기가비트 패키지품(제1 세대품이 사용됨)

## 도면11

4기가비트 패키지품(제2 세대품이 사용됨)

4 기가비트 패키지품

2 기가비트(제2 세대) 칩

## 도면12

4 기가비트 패키지품(제3 세대품이 사용됨)

## 도면13

4 기가비트 패키지품(제2 세대품이 사용됨)

4 기가비트 패키지품

2 기가비트(제2 세대) 칩

## 도면 14

도면15

4 기가비트 패키지품(제3 세대품이 사용됨)