(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6218408号

(P6218408)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

H04N 5/367 (2011.01)

H04N 5/235 (2006.01)H04N 5/367

H04N 5/235

請求項の数 8 (全 11 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-60492 (P2013-60492)    |

| (22) 出願日  | 平成25年3月22日 (2013.3.22)        |

| (65) 公開番号 | 特開2014-187516 (P2014-187516A) |

| (43) 公開日  | 平成26年10月2日 (2014.10.2)        |

| 審査請求日     | 平成28年3月17日 (2016.3.17)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100090273<br>弁理士 國分 孝悦                     |

| (72) 発明者  | 奥沢 昌彦<br>東京都大田区下丸子3丁目30番2号 キヤノン株式会社内       |

| (72) 発明者  | 松岡 正明<br>東京都大田区下丸子3丁目30番2号 キヤノン株式会社内       |

審査官 鈴木 明

最終頁に続く

(54) 【発明の名称】画像処理装置、画像処理方法及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

欠陥画素の位置情報を示す第1の欠陥画素データと、前記第1の欠陥画素データとは異なる時に検出された第2の欠陥画素データとを記憶する記憶手段と、

入力された画像データに対し、前記第1の欠陥画素データに対応した画素のフラグを特定の値に置換する第1のフラグ付加処理手段と、

前記第1のフラグ付加処理手段によってフラグが置換された画像データに対して、前記第2の欠陥画素データに対応した画素のフラグを前記特定の値に置換する第2のフラグ付加処理手段と、

前記第2のフラグ付加処理手段によってフラグが置換された画像データにおいて、フラグが前記特定の値である画素に対して欠陥画素補正を行う補正手段とを有することを特徴とする画像処理装置。

## 【請求項 2】

欠陥画素の位置情報を示す第1の欠陥画素データを記憶する記憶手段と、

入力された画像データに対し、前記第1の欠陥画素データに対応した画素のフラグを特定の値に置換する第1のフラグ付加処理手段と、

前記第1のフラグ付加処理手段によってフラグが置換された画像データに対して、前記第1の欠陥画素データとは異なる第2の欠陥画素データを検出する検出手段と、

前記第1のフラグ付加処理手段によってフラグが置換された画像データに対して、前記検出手段によって検出された第2の欠陥画素データに対応した画素のフラグを前記特定の

10

20

値に置換する第2のフラグ付加処理手段と、

前記第2のフラグ付加処理手段によってフラグが置換された画像データにおいて、フラグが前記特定の値である画素に対して欠陥画素補正を行う補正手段とを有することを特徴とする画像処理装置。

【請求項3】

前記第1のフラグ付加処理手段は、前記第1の欠陥画素データに対応していない画素のフラグが前記特定の値であった場合は、当該画素のフラグを前記特定の値とは異なる値に置換することを特徴とする請求項1又は2に記載の画像処理装置。

【請求項4】

前記第1のフラグ付加処理手段は、前記第1の欠陥画素データに対応していない画素のフラグが前記特定の値であった場合は、当該画素のフラグを前記特定の値と隣接した値に置換することを特徴とする請求項3に記載の画像処理装置。 10

【請求項5】

欠陥画素の位置情報を示す第1の欠陥画素データと、前記第1の欠陥画素データとは異なる時に検出された第2の欠陥画素データとを記憶する画像処理装置の画像処理方法であって、

入力された画像データに対し、前記第1の欠陥画素データに対応した画素のフラグを特定の値に置換する第1のフラグ付加処理工程と、

前記第1のフラグ付加処理工程においてフラグが置換された画像データに対して、前記第2の欠陥画素データに対応した画素のフラグを前記特定の値に置換する第2のフラグ付加処理工程と、 20

前記第2のフラグ付加処理工程においてフラグが置換された画像データにおいて、フラグが前記特定の値である画素に対して欠陥画素補正を行う補正工程とを有することを特徴とする画像処理方法。

【請求項6】

欠陥画素の位置情報を示す第1の欠陥画素データを記憶する画像処理装置の画像処理方法であって、

入力された画像データに対し、前記第1の欠陥画素データに対応した画素のフラグを特定の値に置換する第1のフラグ付加処理工程と、

前記第1のフラグ付加処理工程においてフラグが置換された画像データに対して、前記第1の欠陥画素データとは異なる第2の欠陥画素データを検出する検出工程と、 30

前記第1のフラグ付加処理工程においてフラグが置換された画像データに対して、前記検出工程において検出された第2の欠陥画素データに対応した画素のフラグを前記特定の値に置換する第2のフラグ付加処理工程と、

前記第2のフラグ付加処理工程においてフラグが置換された画像データにおいて、フラグが前記特定の値である画素に対して欠陥画素補正を行う補正工程とを有することを特徴とする画像処理方法。

【請求項7】

欠陥画素の位置情報を示す第1の欠陥画素データと、前記第1の欠陥画素データとは異なる時に検出された第2の欠陥画素データとを記憶する画像処理装置を制御するためのプログラムであって、 40

入力された画像データに対し、前記第1の欠陥画素データに対応した画素のフラグを特定の値に置換する第1のフラグ付加処理工程と、

前記第1のフラグ付加処理工程においてフラグが置換された画像データに対して、前記第2の欠陥画素データに対応した画素のフラグを前記特定の値に置換する第2のフラグ付加処理工程と、

前記第2のフラグ付加処理工程においてフラグが置換された画像データにおいて、フラグが前記特定の値である画素に対して欠陥画素補正を行う補正工程とをコンピュータに実行させることを特徴とするプログラム。

【請求項8】

欠陥画素の位置情報を示す第1の欠陥画素データを記憶する画像処理装置を制御するためのプログラムであって、

入力された画像データに対し、前記第1の欠陥画素データに対応した画素のフラグを特定の値に置換する第1のフラグ付加処理工程と、

前記第1のフラグ付加処理工程においてフラグが置換された画像データに対して、前記第1の欠陥画素データとは異なる第2の欠陥画素データを検出する検出工程と、

前記第1のフラグ付加処理工程においてフラグが置換された画像データに対して、前記検出工程において検出された第2の欠陥画素データに対応した画素のフラグを前記特定の値に置換する第2のフラグ付加処理工程と、

前記第2のフラグ付加処理工程においてフラグが置換された画像データにおいて、フラグが前記特定の値である画素に対して欠陥画素補正を行う補正工程とをコンピュータに実行させることを特徴とするプログラム。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、特に、欠陥画素を補正するために用いて好適な画像処理装置、画像処理方法及びプログラムに関する。

【背景技術】

【0002】

近年、ビデオカメラやデジタルスチルカメラなどでCCDやCMOS等の固体撮像素子が広く利用されている。これらの半導体デバイスは、撮像素子に入射した光を電気信号に変換し、画像データを生成するためのものである。ところが、製造過程で生じた結晶の欠陥などが原因で、入射した光を正常な電気信号に変換できなくなる欠陥画素が発生することがあり、こうした欠陥画素は歩留まりの低下を招く一因となっている。こうした問題に対して、製造工程で検出した欠陥画素の位置情報をメモリに記録しておき、撮影時に欠陥画素の位置情報を参照して補正することにより、正常な画像データを生成することが一般的に行われている。 20

【0003】

一方で、製造工程の検査時には正常であったと判定された画素であっても、宇宙線や経時変化などの要因で発生する欠陥画素もあり、これらの欠陥画素についても適宜検出し、補正することが望まれている。このような場合、製造工程で検出した欠陥画素の位置情報や、その後に生じた欠陥画素を検出した位置情報といった複数の欠陥画素データが存在することになるが、1つのデータにまとめてから欠陥画素補正を行うという方法が一般的に行われている。 30

【0004】

このような技術として、例えば特許文献1に記載の方法のように、欠陥画素を検出するごとに記憶されているデータを更新していく方法が知られている。特許文献1に記載の方法は、電源ON時またはOFF時に欠陥画素の検出モードに入り、検出した欠陥画素の位置が登録されているデータに存在するか否かを毎回確認する。その結果、すでに登録されている欠陥画素データに存在しない画素位置であった場合は、新しいデータとして追記していくというものである。 40

【0005】

また、欠陥画素を補正するために注目画素が欠陥画素か否かを判断するための簡単な方法として、例えば特許文献2に記載の方法のように欠陥画素であった場合は特定の値に置換するという方法が知られている。例えば、注目画素が欠陥画素であった場合は画素の値を値0などに置換し、注目画素が欠陥画素ではなく、画素の値が0であった場合には欠陥画素と区別するために値1などに置換する。こうすることにより、欠陥画素補正処理では、注目画素の画素値を見て欠陥画素か否かを簡単に判定することができるようしている。

【先行技術文献】

**【特許文献】****【0006】**

【特許文献1】特開平8-18873号公報

【特許文献2】特開2010-21858号公報

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

上記の特許文献1の手法は、例えば2種類の欠陥画素データを1つのデータにまとめる場合、前述の通り、新たに検出した欠陥画素のデータは電源ON時または電源OFF時などの適当なタイミングでROMに記憶するように構成することが通常行われている。欠陥画素補正を行う場合は、読み出す欠陥画素データが画素の配列順に並んでいるほうが都合がよいので、実際には欠陥画素データをメモリから読み出し、データの並び順を考慮しながら1つのデータにまとめることが必要となってくる。このようなことから、欠陥画素データをまとめてFLASH ROMなどの不揮発性メモリに記録する方式は、前述のように処理のオーバーヘッドが大きくなるという問題点を抱えている。

10

**【0008】**

さらに、工場出荷後に検出した欠陥画素データを1つのデータにまとめて不揮発性メモリへ記憶する場合、記録動作中にカメラのバッテリーを抜かれたりするとデータを破壊してしまう可能性がある。このとき、製造工程時に検出した欠陥画素データを失ってしまうないように、工場出荷後に検出した欠陥画素データは工場出荷時に検出したデータとは別領域に記録しておき、カメラの起動時にこれらの欠陥画素データをまとめることが一般的である。しかしながら、このような方式でもカメラを起動してから撮影可能な状態になるまでに多くの時間がかかるてしまい、起動完了までカメラの使用者が待たされるという問題点があった。

20

**【0009】**

また、特許文献2に記載されている欠陥画素の画素値を特定の値に置換する方法は、欠陥画素データを1つのデータにまとめることを前提とした技術ではない。したがって、工場出荷前に検出欠陥画素データと工場出荷後に検出された欠陥画素データとがある場合には対応できない。例えば、最初に工場出荷時の欠陥画素データに対して特許文献2に記載の処理を行うことを考えると、欠陥画素の画素値を0に置換し、画素値が0である正常画素の場合は1に置換する処理が行われる。次に、この処理を行った画像データに対して工場出荷後に検出した欠陥画素に対しても同様の処理を行うと、最初の処理で欠陥画素として置換した画素値0が1に置換されてしまい、欠陥画素ではないとみなされてしまう。良好な欠陥画素の補正結果を得るために、工場出荷時の欠陥画素データに加えて、その後に発生した欠陥画素を検出した結果を使用することが通常行われていることから、特許文献2に記載の技術は、前述した問題に対する改善が必要となる。

30

**【0010】**

本発明は前述の問題点に鑑み、検出時が異なる複数の欠陥画素データを用いて、簡単にかつ正確に欠陥画素補正を行うことができるようすることを目的としている。

**【課題を解決するための手段】**

40

**【0011】**

本発明の画像処理装置は、欠陥画素の位置情報を示す第1の欠陥画素データと、前記第1の欠陥画素データとは異なる時に検出された第2の欠陥画素データとを記憶する記憶手段と、入力された画像データに対し、前記第1の欠陥画素データに対応した画素のフラグを特定の値に置換する第1のフラグ付加処理手段と、前記第1のフラグ付加処理手段によってフラグが置換された画像データに対して、前記第2の欠陥画素データに対応した画素のフラグを前記特定の値に置換する第2のフラグ付加処理手段と、前記第2のフラグ付加処理手段によってフラグが置換された画像データにおいて、フラグが前記特定の値である画素に対して欠陥画素補正を行う補正手段とを有することを特徴とする。

**【発明の効果】**

50

**【0012】**

本発明によれば、欠陥画素データが複数種類あった場合でもデータを1つにまとめることを不要にし、簡単かつ正確に欠陥画素を補正することができる。

**【図面の簡単な説明】****【0013】**

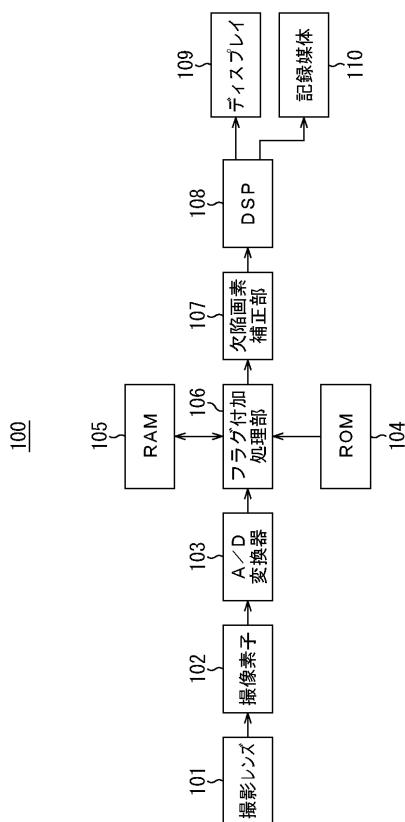

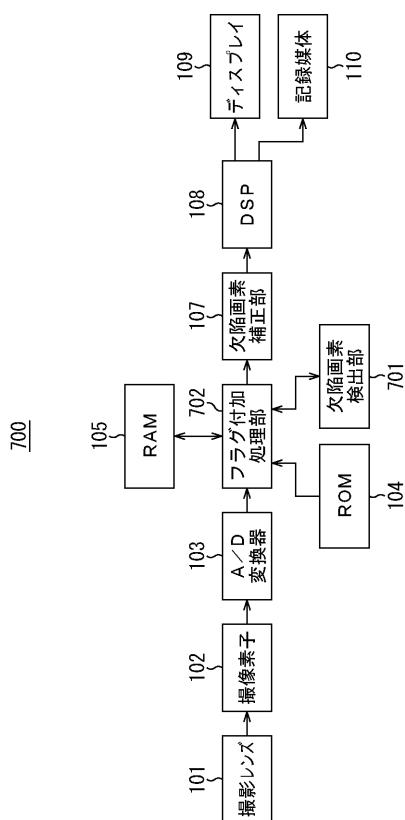

【図1】本発明の第1の実施形態に係る撮像装置の構成例を示すブロック図である。

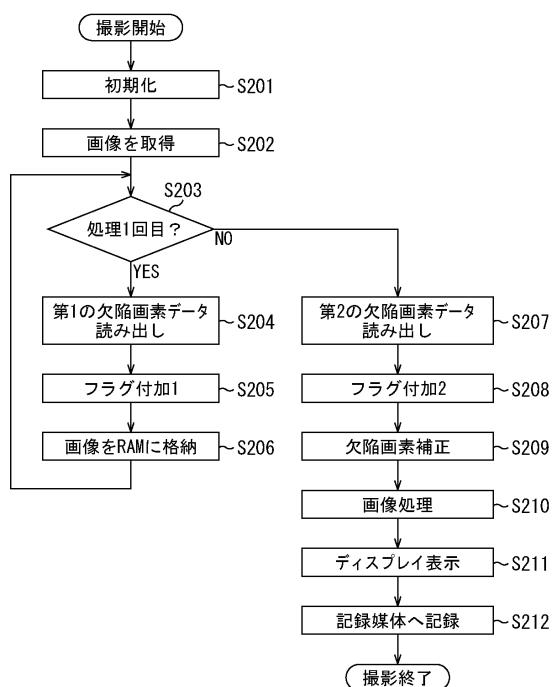

【図2】本発明の第1の実施形態に係る撮影処理手順の一例を示すフローチャートである。

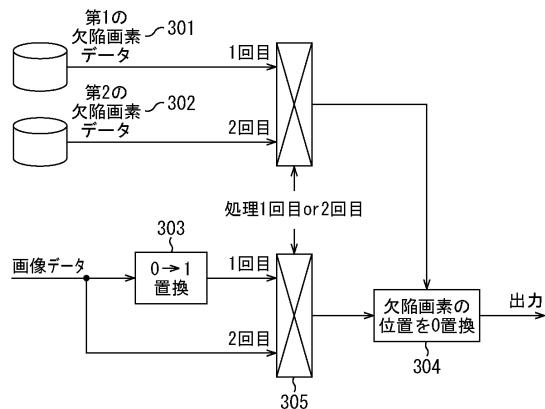

【図3】本発明の第1の実施形態に係るフラグ付加処理の動作を説明する図である。

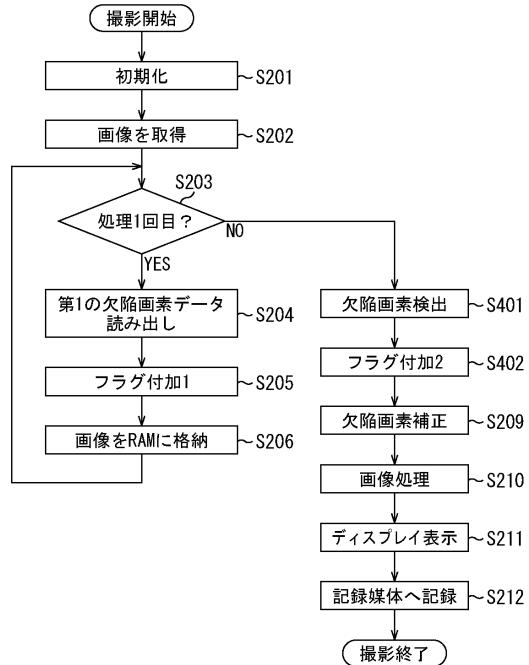

【図4】本発明の第3の実施形態に係る撮影処理手順の一例を示すフローチャートである。

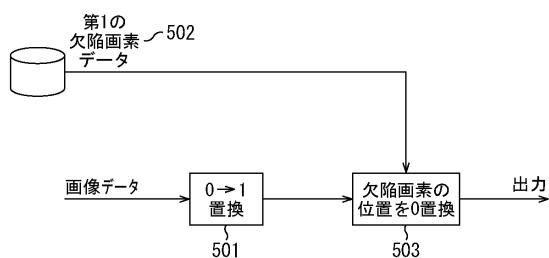

【図5】本発明の第2の実施形態に係る1回目のフラグ付加処理の動作を説明する図である。

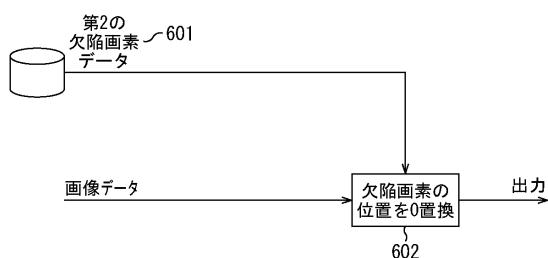

【図6】本発明の第2の実施形態に係る2回目のフラグ付加処理の動作を説明する図である。

【図7】本発明の第3の実施形態に係る撮像装置の構成例を示すブロック図である。

**【発明を実施するための形態】****【0014】**

以下、本発明の実施形態について、図面を参照しながら説明する。

**(第1の実施形態)**

20

図1は、本実施形態に係る撮像装置100の構成例を示すブロック図である。

図1において、撮像装置100は、撮影レンズ101、撮像素子102、A/D変換器103、ROM104、RAM105、フラグ付加処理部106、欠陥画素補正部107、DSP108、ディスプレイ109及び記録媒体110を有している。

**【0015】**

撮影レンズ101は、被写体の映像を入射し、撮像素子102はその映像を受光する。撮像素子102としては、例えばCMOSセンサやCCDセンサが一般的に利用されている。A/D変換器103は、撮像素子102で受光した光をデジタル信号に変換する。ROM104には、製造工程及び出荷後に検出された欠陥画素の位置情報を示す欠陥画素データや画像処理に必要なパラメータ等が記憶されている。また、ROM104には、後述する処理を実行させるための制御プログラムも記憶されている。RAM105は、処理を行うために画像データなどを一時的に記憶しておくためのものである。

30

**【0016】**

フラグ付加処理部106は、ROM104に記憶されている欠陥画素のデータをもとに、フラグを付加する。欠陥画素補正部107は、フラグ付加処理部106によりフラグが付加された画素について欠陥画素を補正する。DSP108は、各種画像処理を行う構成であり、ホワイトバランス補正やJPEGなどへの画像フォーマット変換等を行う。ディスプレイ109は、撮影された画像を表示する。記録媒体110は、DSP108で生成された画像データを記録する。

**【0017】**

40

次に、上記の構成における本実施形態の撮影動作について、図2を参照しながら説明する。

図2は、本実施形態に係る撮像装置100による撮影処理手順の一例を示すフローチャートである。

まず、撮影モードに移行すると処理を開始し、撮像素子102へのクロックの供給や欠陥画素補正部107へのパラメータの設定、欠陥画素データの読み出し開始アドレスの設定など、必要な初期化を行う(S201)。そして、撮影者により不図示のシャッターボタンが押下されることにより撮像素子102から画像データを取得する(S202)。

**【0018】**

次に、フラグ付加処理部106は、1回目のフラグ付加処理であるか否かを判定する(

50

S 2 0 3)。この判定の結果、1回目のフラグ付加処理である場合は、フラグ付加処理部 1 0 6 は、製造工程などで検出された欠陥画素の情報である第1の欠陥画素データを R O M 1 0 4 から読み出す(S 2 0 4)。その後、取得した画像データに対して、第1の欠陥画素データに基づいて第1のフラグ付加処理を行う(S 2 0 5)。なお、第1のフラグ付加処理の詳細については後述する。そして、フラグが付加された画像データを R A M 1 0 5 に格納する(S 2 0 6)。そして、S 2 0 3 に戻る。

#### 【0019】

次に、S 2 0 6 で格納した画像データを R A M 1 0 5 から読み出し、第2の欠陥画素データに基づいてフラグ付加処理を行うことになる。ここで、S 2 0 3 の判定の結果、2回目のフラグ付加処理である場合は、フラグ付加処理部 1 0 6 は、出荷後に新たに検出された第2の欠陥画素データを R O M 1 0 4 から読み出す(S 2 0 7)。そして、画像データに対して第2のフラグ付加処理を行う(S 2 0 8)。なお、第2のフラグ付加処理の詳細については後述する。

#### 【0020】

欠陥画素補正部 1 0 7 は、注目している画素の値が欠陥画素を意味する特定の値であるか否かをすべての画素に対して判定し、欠陥画素であった場合には欠陥画素補正を行い、すべての画素に対し、有効な画素データを生成する(S 2 0 9)。その後、S 2 0 9 で欠陥画素補正されたデータに対し、D S P 1 0 8 はホワイトバランス補正等の各種画像処理を行う(S 2 1 0)。

#### 【0021】

次に、D S P 1 0 8 は、各種画像処理が施されたデータに係る画像をディスプレイ 1 0 9 へ表示する(S 2 1 1)。そして、記録媒体 1 1 0 へ画像データを記録し(S 2 1 2)、撮影処理を終了する。

#### 【0022】

次に、S 2 0 5 及び S 2 0 8 におけるフラグ付加処理の動作について、図 3 を参照しながら詳細に説明する。フラグ付加処理では、欠陥画素であることを示すフラグとして画素値を特定のフラグ値に置き換えるが、本実施形態ではフラグ値を 0 として処理を行う。

#### 【0023】

入力画像の中にフラグ値 0 の画素があると、その後の処理で欠陥画素として扱われてしまうため、1回目のフラグ付加処理で、そのような画素をフラグ値 0 と異なる値にしなければならない。したがって、S 2 0 5 では、処理 3 0 3 で入力画素値がフラグ値 0 と同じ値であるか否かを確認し、フラグ値 0 とは異なる値(以下、フラグ置換値)に置換しておく。

#### 【0024】

なお、画質に与える影響を考慮するとフラグ置換値はフラグ値に隣接した値であることが好ましい。例えば、1画素あたり 1 4 b i t の場合に 0 である画素値を 1 に置換したとしても、1 4 b i t 階調のうち 1 階調変化した画像の違いを認識することは非常に難しく、画質に与える影響はほとんどないといえる。本実施形態では、フラグ置換値を 1 として説明を行う。

#### 【0025】

また、S 2 0 5 の 1 回目のフラグ付加処理では、第1の欠陥画素データ 3 0 1 を取得して、処理 3 0 4 で注目画素が欠陥画素であった場合は画素値をフラグ値 0 に置換する。このように、1回目のフラグ付加処理を終了した時点において、画素値がフラグ値 0 である場合は欠陥画素であること示している。

#### 【0026】

次に、2回目のフラグ付加処理を行うが、処理 3 0 3 と同じ処理を行うと1回目で付加したフラグがクリアされてしまうため、セレクタ 3 0 5 を切り替えて処理 3 0 3 を行わないようとする。すなわち、第2の欠陥画素データ 3 0 2 を取得して画素値をフラグ値 0 に置換する処理のみを行う。これにより、2回目のフラグ付加処理の終了時点で、第1の欠陥画素データ及び第2の欠陥画素データの位置にフラグが値 0 として画像データに付加さ

10

20

30

40

50

れている。その後の欠陥画素補正処理では画素値がフラグ値 0 であったら欠陥画素として処理を行うことができる。このように 2 種類の欠陥画素のデータが存在することを意識せずに処理することが可能となる。

#### 【0027】

以上のように本実施形態によれば、複数の種類の欠陥画素データがあった場合でも、フラグを順次付加していくことにより、複数の欠陥画素データをマージしたものと同等の効果を得ることができ、回路構成を簡単にすることが可能となる。本実施形態のように一度欠陥画素のフラグを付加した画像データを RAM に格納し、2 回目のフラグ付加処理でも 1 回目のフラグ付加処理と同じ回路を使用することによってさらに回路規模を削減することが可能となる。

10

#### 【0028】

なお、本実施形態では、フラグ値を 0 として説明しているが、これに限ったことではなく他の値でもよい。また、本実施形態では、欠陥画素のデータを 2 種類として説明しているが、これに限ったことではなく複数種類の欠陥画素データがある場合にも対応できる。さらに多くの欠陥画素のデータがある場合には、入力画像に欠陥画素のフラグとして使用する値があった場合に他の値に置き換える処理 303 は 1 回目のフラグ付加処理のみ行い、2 回目以降のフラグ付加処理では処理 303 を行わないようにすればよい。

#### 【0029】

##### (第 2 の実施形態)

以下、本実施形態について、図 5 および図 6 を参照しながら説明する。なお、本実施形態に係る撮像装置の基本的な構成及び撮影処理手順についてはそれぞれ図 1 及び図 2 と同様であるため、説明は省略する。

20

#### 【0030】

第 1 の実施形態では、1 回目のフラグ付加処理を行った後に画像データを RAM105 に格納しているが、RAM やメモリのバンド幅が厳しいような状況や容量を節約したい状況などもありえる。また、RAM やメモリに格納せずにフラグ付加処理により欠陥画素データのマージを行いたい場合もある。このような場合は、1 回目のフラグ付加処理用の回路と 2 回目のフラグ付加処理用の回路とをそれぞれ用意し、1 回目のフラグ付加処理により出力されるデータを 2 回目のフラグ付加処理で入力するように処理すればよい。

#### 【0031】

30

例えば、1 回目のフラグ付加処理の回路を、図 5 に示すような構成とすることができる。1 回目のフラグ付加処理は、フラグ置換値に置換する処理 501 を行い、ROM104 から読み出した第 1 の欠陥画素データ 502 に基づき、欠陥画素の位置をフラグ値に置換する処理 503 を行う。

#### 【0032】

さらに、2 回目のフラグ付加処理の回路を、図 6 に示すような構成とすることができ、1 回目のフラグ付加処理により出力される画像データを入力するようとする。1 回目のフラグ付加処理で、もともとの画像データにあったフラグ値 0 と同じ値の画素は隣接した他の値に置換されているため、2 回目のフラグ付加処理は処理 501 に相当する処理は必要ない。このため、2 回目のフラグ付加処理では、ROM104 から読み出した第 2 の欠陥画素データ 601 に基づいて欠陥画素の位置をフラグ値に置き換える処理 602 を行うのみでよい。このようにすることにより、2 回目のフラグ付加処理が終了した時点で第 1 の欠陥画素に対応するフラグと第 2 の欠陥画素に対応するフラグとが付加された状態となる。

40

#### 【0033】

以上のように本実施形態によれば、1 回目のフラグ付加処理を行う回路と 2 回目のフラグ付加処理を行う回路とをそれぞれ用意することにより、画像データを一旦メモリ等に格納させずに複数の欠陥画素データのマージと同等の効果を得ることが可能となる。

#### 【0034】

##### (第 3 の実施形態)

50

以下、本実施形態について、図3および図4および図7を参照しながら説明する。大きな構成としては第1の実施形態と同様であるが、本実施形態では第1のフラグ付加処理の出力結果をもとに欠陥画素の検出を行い、検出結果に基づいて第2のフラグ付加処理をリアルタイムに行う。

#### 【0035】

図7は、本実施形態に係る撮像装置700の構成例を示すブロック図である。

なお、第1の実施形態で説明した図1と同一の構成については、同じ符号を付しており、その構成の説明は省略する。なお、ROM104には、後述する欠陥画素検出部701により検出された欠陥画素データも記憶されるものとする。

#### 【0036】

欠陥画素検出部701は、経時変化等で発生した欠陥画素を検出するためのものである。フラグ付加処理部702は、ROM104に予め記憶されている欠陥画素データと、欠陥画素検出部701で検出された欠陥画素データとをもとに、フラグを付加する。

#### 【0037】

次に、上記の構成における本実施形態の撮影動作について、図4を参照しながら説明する。

図4は、本実施形態に係る撮像装置700による撮影処理手順の一例を示すフローチャートである。本実施形態における1回目の欠陥画素のフラグ付加処理は、ROM104に格納されている製造工程時に検出された第1の欠陥画素データを読み出してフラグを付加するものであり、第1の実施形態で図3に示した例と同じである。

#### 【0038】

まず、S201～S206までの処理は、図2と同様であるため、説明は省略する。S203の判定の結果、2回目のフラグ付加処理である場合は、欠陥画素検出部701は、RAM105から画像データを読み出し、1回目のフラグ付加処理でフラグを付加した画像データに対して欠陥画素検出を行う(S401)。欠陥画素検出の方法としては、例えば、着目画素の画素値とその近傍画素の画素値とを比較し、着目画素との差分が閾値以内となる近傍画素が存在しなければ、着目画素を欠陥画素と判断することが考えられる。欠陥画素検出は、第1の欠陥画素データを補うものであり、リアルタイムに欠陥画素の検出を行うことによって、第1の欠陥画素データの作成後に発生した欠陥画素を検出する。また、欠陥画素検出が行われる画像データには、S205すでに欠陥画素を示すフラグが付加されているため、例えば工場出荷時に検出されていた欠陥画素を回避しながら検出を行うことも可能である。つまり、S205すでに欠陥画素を示すフラグが付加されている画素が着目画素の近傍に存在していた場合には、この画素を着目画素との比較対象から排除して、欠陥画素の検出を行えば良い。

#### 【0039】

次に、フラグ付加処理部702は、欠陥画素であると検出された画素にフラグを付加する(S402)。この処理は第1の実施形態で図3に示した例と同じであるため、説明は省略する。このように、S402の処理を終えた時点で、第1の欠陥画素データとリアルタイムに欠陥画素検出された結果とがフラグとして付加されている。したがって、注目している画素の値が欠陥画素を意味する特定の値であるか否かを判定し、欠陥画素であった場合は欠陥画素補正を行い、有効な画素データを生成することができる。S210～S212までの処理は、図2と同様であるため、説明は省略する。

#### 【0040】

以上のように本実施形態によれば、予め検出されていた欠陥画素データとリアルタイムに検出された欠陥画素データといった複数の欠陥画素データがあった場合においても、フラグを順次付加していく。これにより、これらの欠陥画素データをマージしたものと同等の効果を得ることができ、簡単な構成で実現することが可能となる。なお、フラグ付加処理については、第2の実施形態と同様に、1回目のフラグ付加処理を行う構成を図5に示すような構成にし、2回目のフラグ付加処理を行う構成を図6に示す構成にしてもよい。

#### 【0041】

10

20

30

40

50

## (その他の実施形態)

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ（またはCPUやMPU等）がプログラムを読み出して実行する処理である。

## 【符号の説明】

## 【0042】

- |     |          |

|-----|----------|

| 101 | 撮影レンズ    |

| 102 | 撮像素子     |

| 103 | A/D変換器   |

| 104 | ROM      |

| 105 | RAM      |

| 106 | フラグ付加処理部 |

| 107 | 欠陥画素補正部  |

| 108 | DSP      |

| 109 | ディスプレイ   |

| 110 | 記録媒体     |

10

【図1】

【図2】

【図3】

【 図 4 】

【 図 5 】

【 四 7 】

【 図 6 】

---

フロントページの続き

(56)参考文献 特開2007-295312(JP,A)

特開2003-348607(JP,A)

特開平08-018873(JP,A)

特開2010-021858(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30-5/378

H04N 5/222-5/257