## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

|                                                                                               |                                                                        |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| (51) Int. Cl. <sup>6</sup><br>G11C 11/413                                                     | (45) 공고일자 2001년08월07일<br>(11) 등록번호 10-0296612<br>(24) 등록일자 2001년05월11일 |

| (21) 출원번호 10-1998-0020816<br>(22) 출원일자 1998년06월05일<br>(30) 우선권주장 97-274437 1997년10월07일 일본(JP) | (65) 공개번호 특 1999-0036519<br>(43) 공개일자 1999년05월25일                      |

|                                                                                               |                                                                        |

|                          |                                          |

|--------------------------|------------------------------------------|

| (73) 특허권자 미쓰비시덴키 가부시키가이샤 | 다니구찌 이찌로오, 기타오카 다카시                      |

|                          | 일본국 도쿄도 지요다쿠 마루노우치 2쵸메 2반 3고             |

| (72) 발명자 츠키카와 야스히코       | 일본 도쿄도 지요다쿠 마루노우치 2쵸메 2반 3고 미쓰비시 덴키 가부시키 |

|                          | 가이샤 내                                    |

| (74) 대리인 김창세             |                                          |

**심사관 : 황은택****(54) 출력버퍼의 출력전류를 크게 할 수 있는 반도체 기억장치****요약**

본 발명은 반도체 기억 장치의 출력 버퍼의 출력 트랜지스터(18)가 형성되는 웨л 영역을 3중 웨л(triple well)에 의해 전기적으로 기판과 분리시킨다. 출력 트랜지스터는 도통시에 출력 트랜지스터가 형성되는 웨л의 전위를 출력 트랜지스터의 소스 전위를 추종하도록 제어해서, 기판 바이어스 효과에 의한 임계값의 증대를 억제하여 보다 큰 출력 전류를 얻을 수 있다.

**대표도****도3****명세서****도면의 간단한 설명**

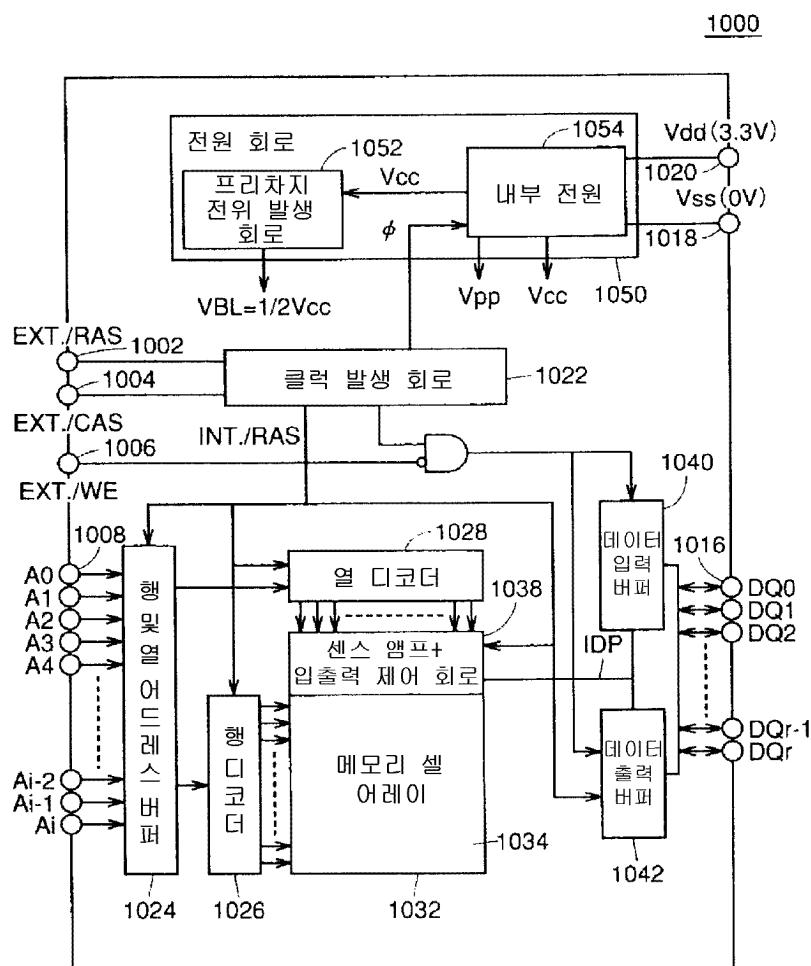

- 도 1은 본 발명의 반도체 기억 장치(1000)의 전체 구성을 나타내는 개략적인 블럭도,

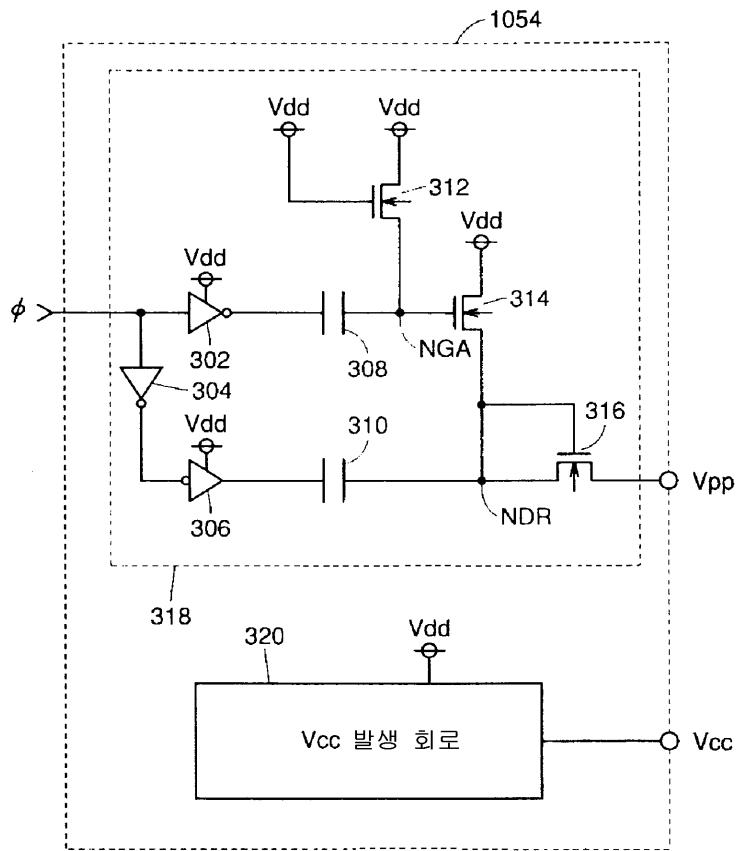

도 2는 도 1의 반도체 기억 장치(1000)에 있어서의 내부 전원(1054)을 상세하게 나타내는 회로도,

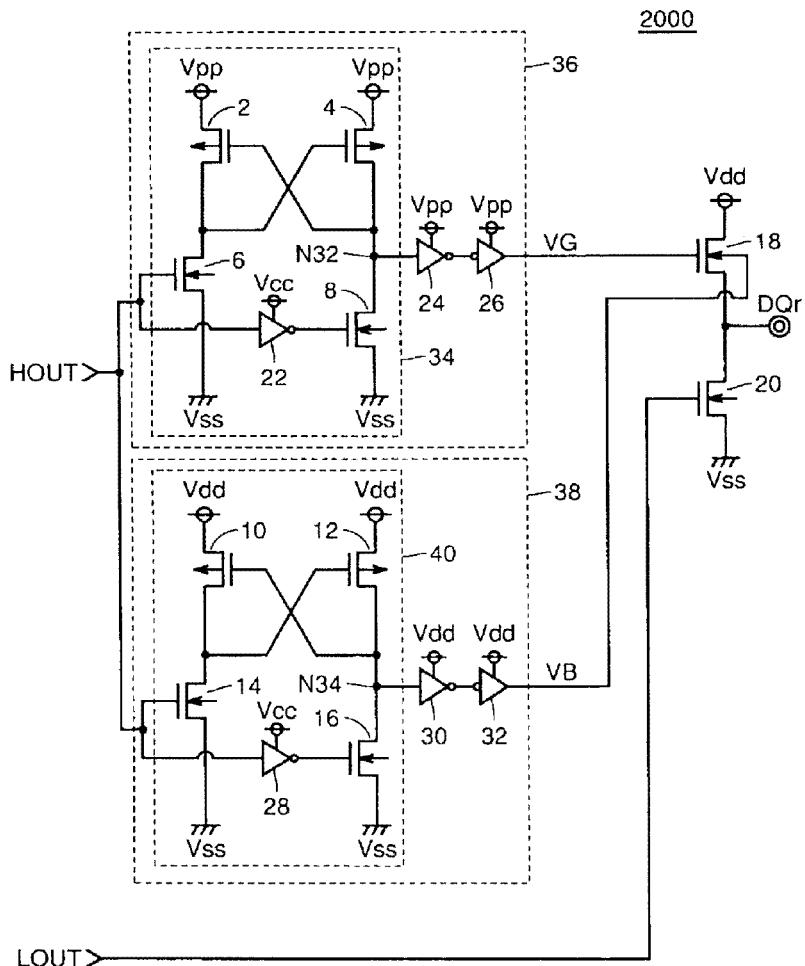

도 3은 본 발명의 실시예 1에 있어서의 출력 버퍼 회로(2000)의 회로도,

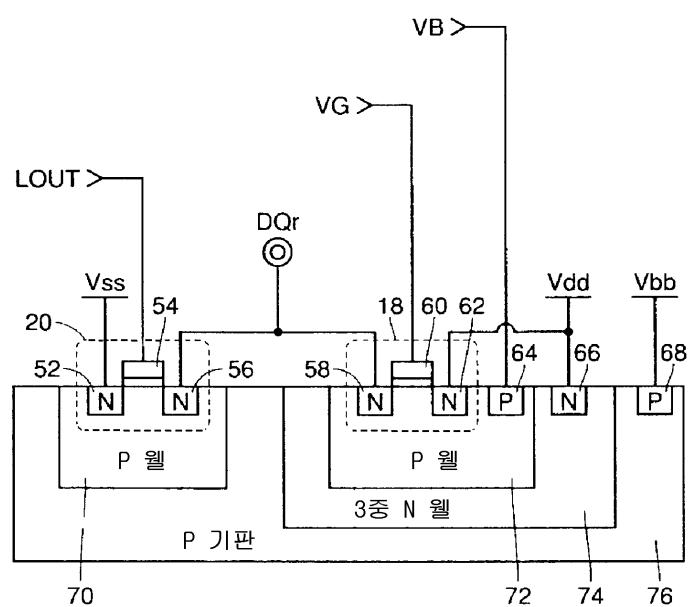

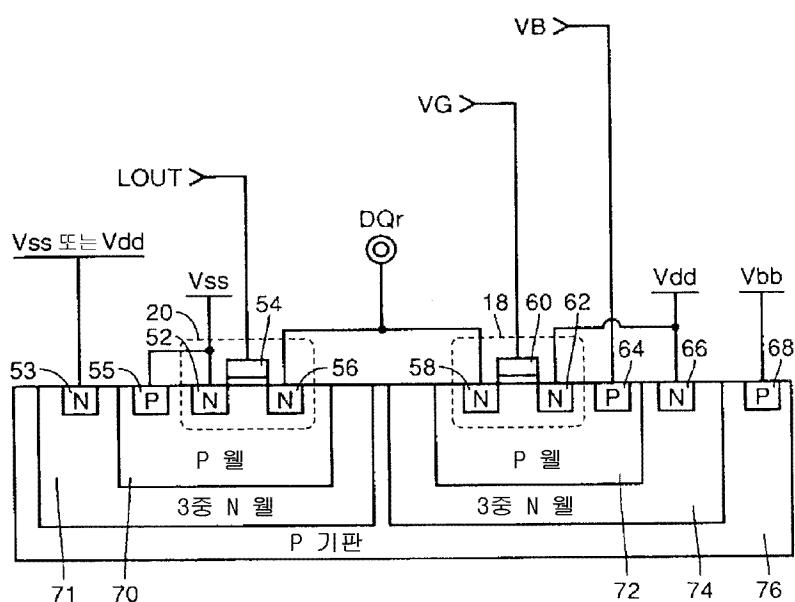

도 4는 도 3의 출력 버퍼 회로(2000)의 출력 트랜지스터부의 실시예 1에 있어서의 단면 구조를 설명하기 위한 개념도,

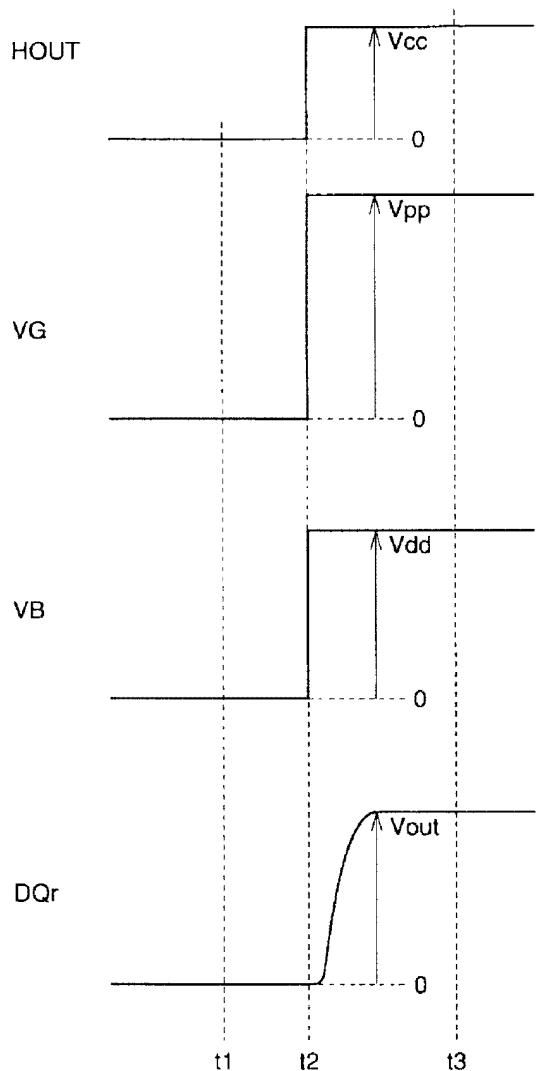

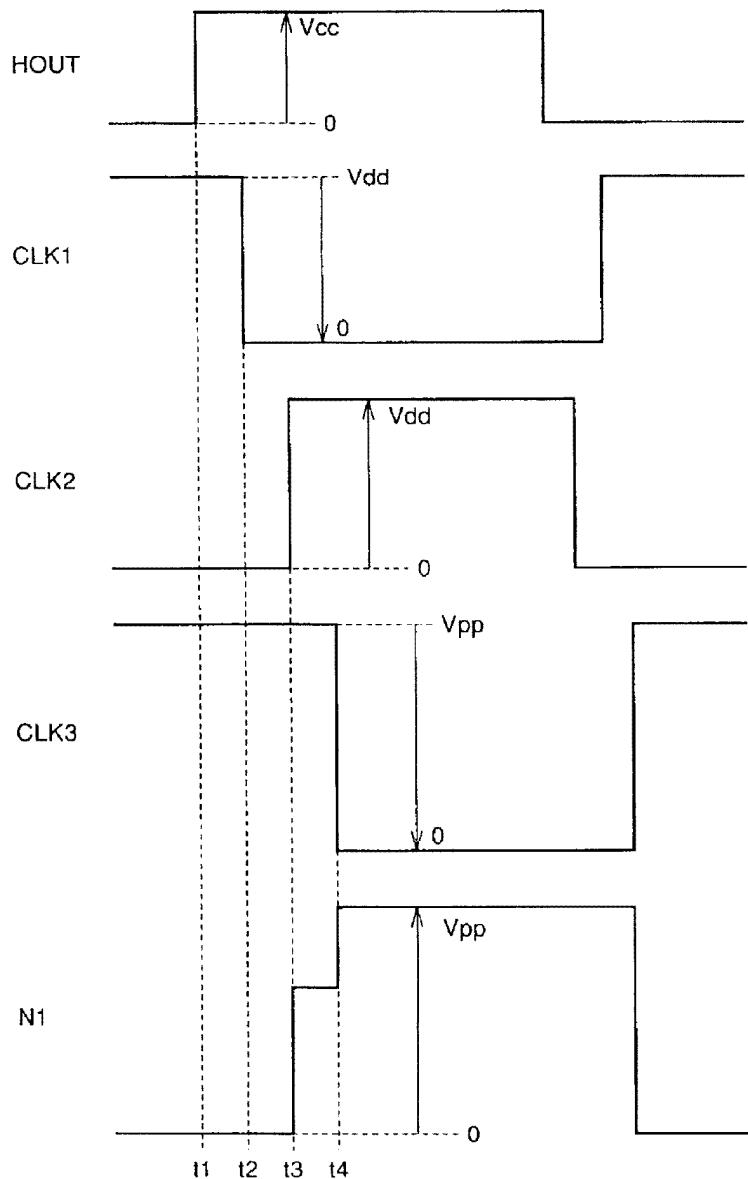

도 5는 도 3의 출력 버퍼 회로(2000)의 동작을 설명하는 동작 파형도,

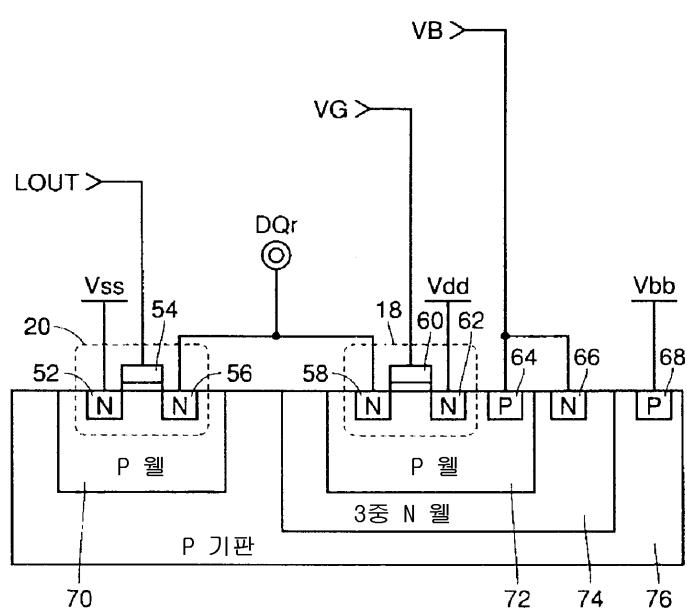

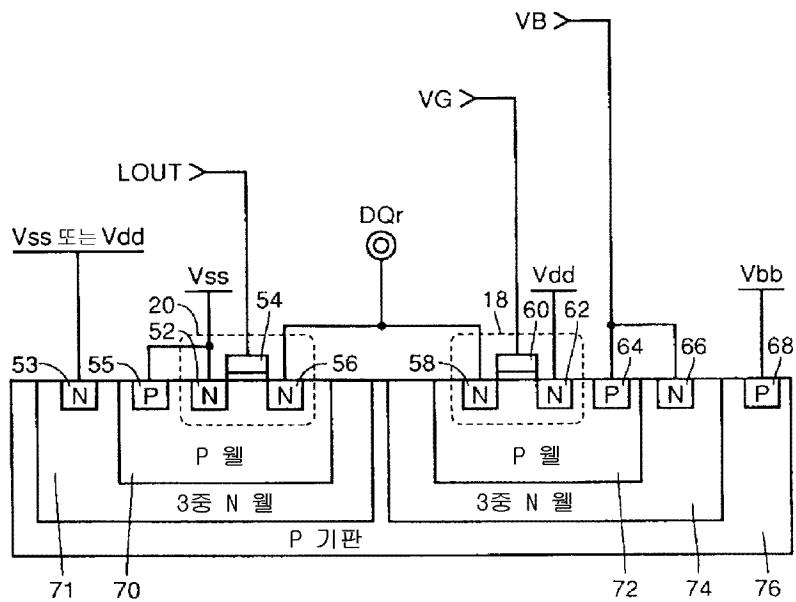

도 6은 도 3의 출력 버퍼 회로(2000)의 출력 트랜지스터부의 실시예 1의 변형예 1에 있어서의 단면 구조를 설명하기 위한 개념도,

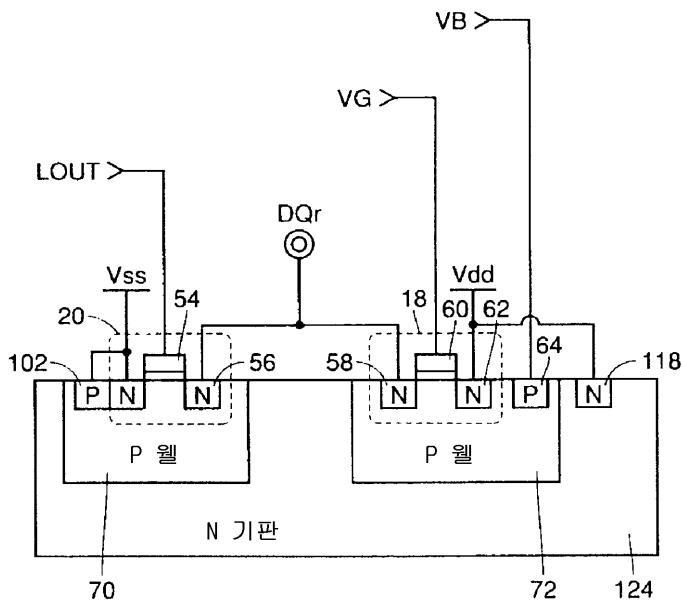

도 7은 도 3의 출력 버퍼 회로(2000)의 출력 트랜지스터부의 실시예 1의 변형예 2에 있어서의 단면 구조를 설명하기 위한 개념도,

도 8은 도 3의 출력 버퍼 회로(2000)의 출력 트랜지스터부의 실시예 1의 변형예 3에 있어서의 단면 구조를 설명하기 위한 개념도,

도 9는 도 3의 출력 버퍼 회로(2000)의 출력 트랜지스터부의 실시예 1의 변형예 4에 있어서의 단면 구조를 설명하기 위한 개념도.

도 10은 본 발명의 실시예 2에 있어서의 출력 버퍼 회로(3000)의 회로도,

도 11은 도 10의 출력 버퍼 회로(3000)의 동작을 설명하는 동작 파형도,

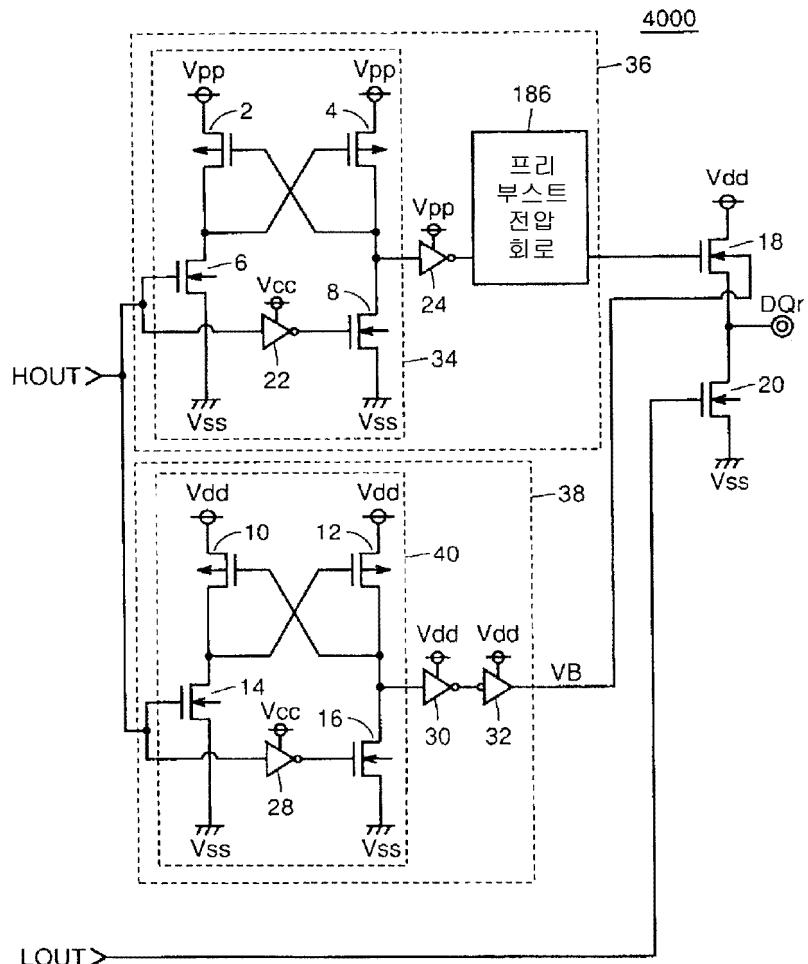

도 12는 본 발명의 실시예 3에 있어서의 출력 버퍼 회로(4000)의 회로도,

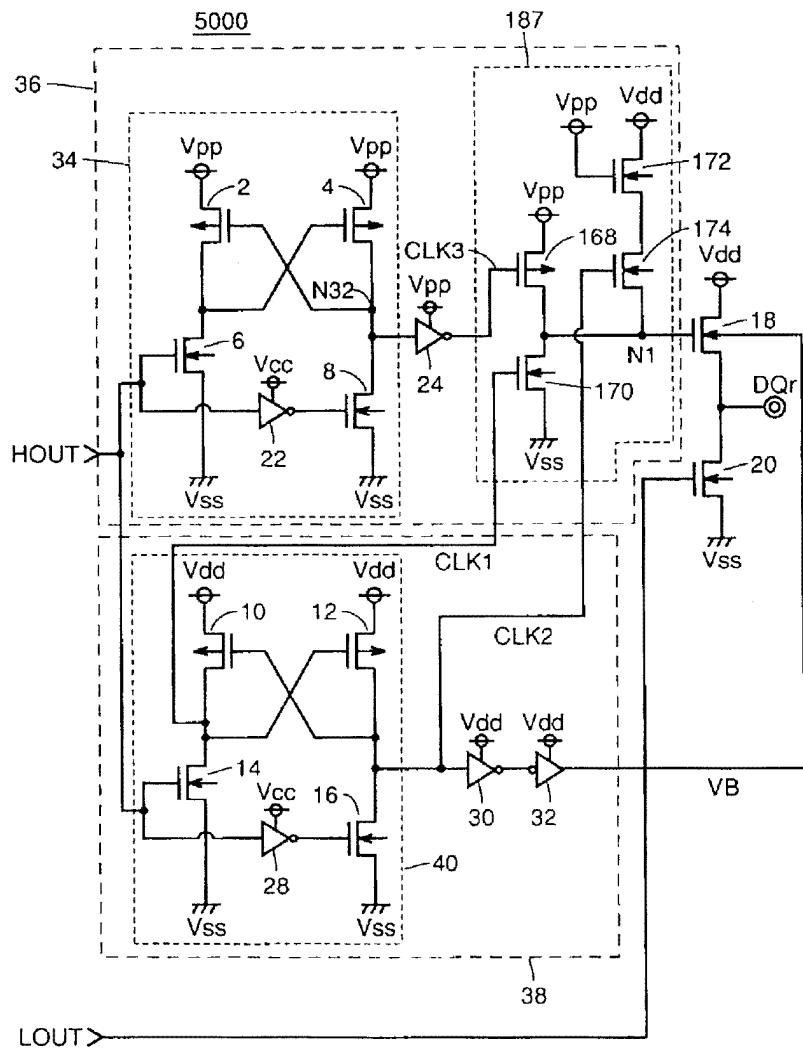

도 13은 본 발명의 실시예 4에 있어서의 출력 버퍼 회로(5000)의 회로도,

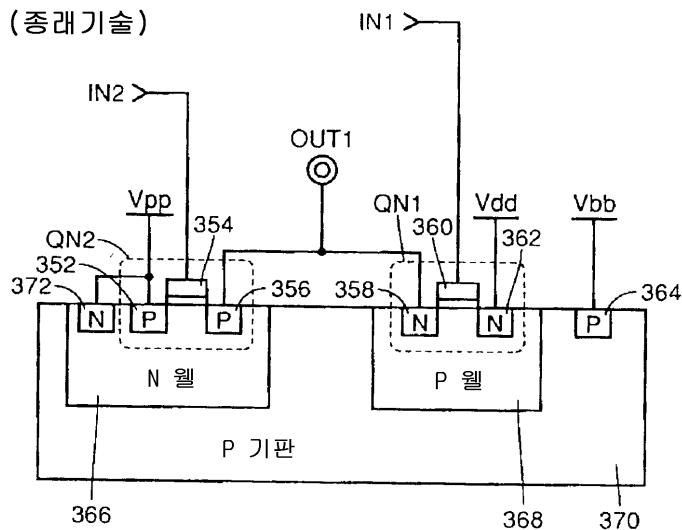

- 도 14는 종래의 반도체 기억 장치에 있어서의 출력 버퍼 회로의 회로도,

도 15는 도 14의 출력 버퍼 회로의 출력 트랜지스터부의 단면 구조를 설명하기 위한 개념도,

도 16은 도 14의 출력 버퍼 회로의 동작을 설명하는 동작 파형도,

도 17은 종래의 프리부스트 회로의 회로도,

도 18은 도 17의 프리부스트 회로의 단면 구조를 설명하기 위한 개념도.

#### 도면의 주요 부분에 대한 부호의 설명

|                                             |                |

|---------------------------------------------|----------------|

| 18, 20, 176, 178, 210, 212 ; N 채널 MOS 트랜지스터 |                |

| 34, 40, 188, 220 ; 레벨 변환 회로                 | 36 ; 구동 회로     |

| 38 ; 기판 전위 구동 회로                            | 186 ; 프리부스트 회로 |

| 1000 ; 반도체 기억 장치                            |                |

| 2000, 3000, 4000 ; 출력 버퍼 회로                 |                |

#### **발명의 상세한 설명**

##### **발명의 목적**

##### **발명이 속하는 기술분야 및 그 분야의 종래기술**

본 발명은 반도체 기억 장치에 관한 것으로, 보다 특정적으로는, 기억 데이터에 대응하는 신호를 출력하는 출력 버퍼 회로를 구비하는 반도체 기억 장치의 구성에 관한 것이다.

반도체 기억 장치의 고속화가 진행함에 따라, 반도체 기억 장치의 출력 버퍼 회로의 구동 능력을 크게 할 필요가 있다.

도 14는 종래의 반도체 기억 장치에 이용되는 출력 버퍼 회로의 기본 구성을 나타내는 제 1 예의 회로도이다.

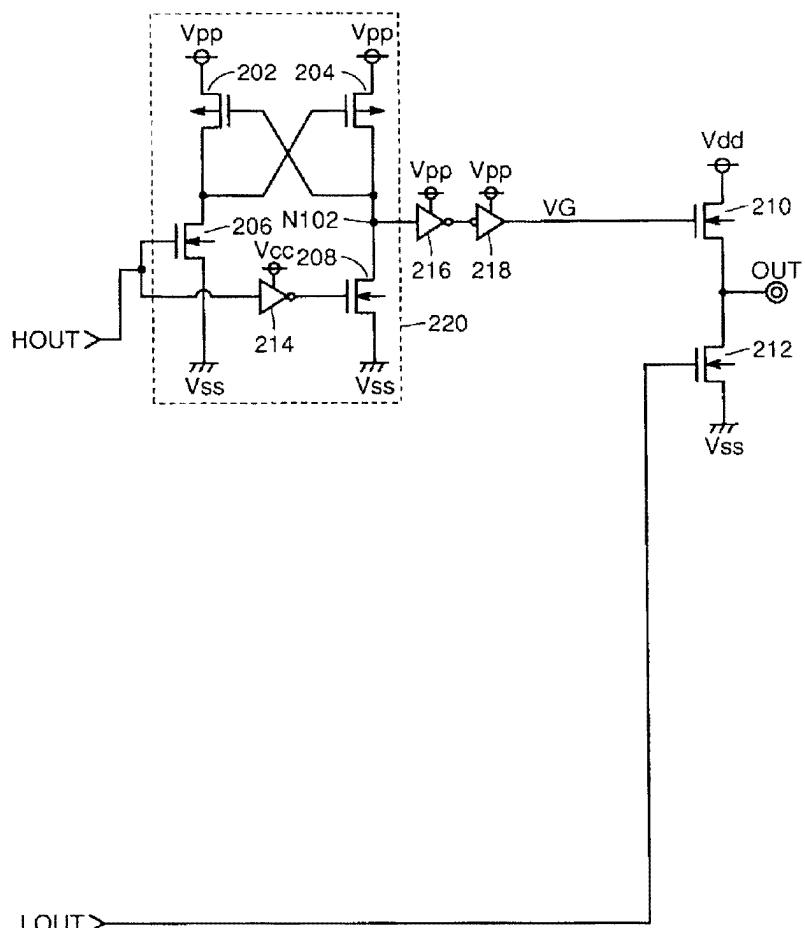

도 14에 도시하는 출력 버퍼 회로는 출력 단자 OUT와, 출력되는 기억 데이터에 따라 생성되는 제 1 내부 제어 신호 HOUT를 수신하여 그 'H' 레벨을 외부 전원 전위 Vdd로부터 강압된 내부 강압 전위 Vcc로부터 반도체 장치 내부에서 생성되는 내부 승압 전위 Vpp로 하는 레벨 변환 회로(220)와, 레벨 변환 회로(220)의 출력을 수신하는 직렬로 접속된 인버터(216, 218)와, 인버터(218)의 출력을 게이트에서 수신하며, 외부 전원 전위 Vdd와 출력 단자 OUT 사이에 결합된 N 채널 MOS 트랜지스터(210)와, 출력되는 기억 데이터에 따라 생성되는 제 2 내부 제어 신호 LOUT를 게이트에서 수신하며, 출력 단자 OUT와 접지 전위 Vss 사이에 결합된 N 채널 MOS 트랜지스터(212)를 구비한다.

레벨 변환 회로(220)는 제 1 내부 제어 신호 HOUT를 게이트에서 수신하는 N 채널 MOS 트랜지스터(206)와, 제 1 내부 제어 신호 HOUT를 수신하여 반전하는 인버터(214)와, 인버터(214)의 출력을 게이트에서 수신하는 N 채널 MOS 트랜지스터(208)를 포함한다.

N 채널 MOS 트랜지스터(206, 208)의 소스는 모두 접지 전위 Vss로 결합되어 있다.

레벨 변환 회로(220)는 내부 승압 전위 Vpp와 N 채널 MOS 트랜지스터(206)의 드레인 사이에 결합되며, 게이트에서 N 채널 MOS 트랜지스터(208)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(202)와, 내부 승압 전위 Vpp와 N 채널 MOS 트랜지스터(208)의 드레인 사이에 결합되며, 게이트에서 N 채널 MOS 트랜지스터(206)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(204)를 더 포함한다.

레벨 변환 회로(220)는 N 채널 MOS 트랜지스터(208)의 드레인이 접속되는 노드 N102로부터 출력 신호, 즉, 제 1 내부 제어 신호 HOUT과 동상(同相)이면서 'H' 레벨이 내부 승압 전위 Vpp로 되는 신호를 인버터(216)에 대하여 출력한다.

다음에 도 14에 도시하는 종래의 출력 버퍼 회로의 출력 트랜지스터인 N 채널 MOS 트랜지스터(210, 212)의 구조를 설명한다.

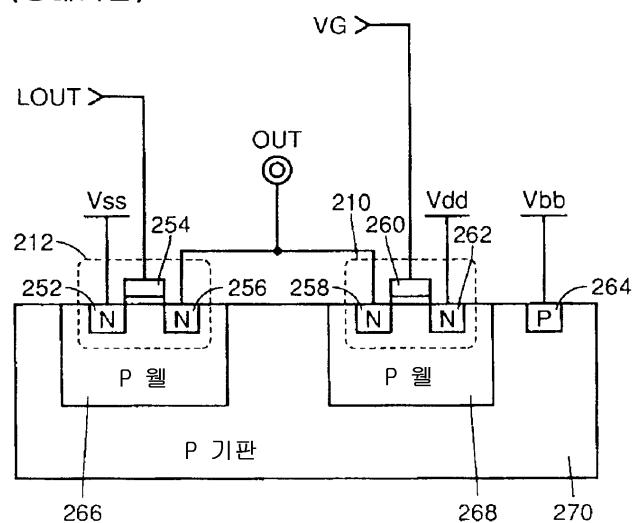

도 15는 도 14의 종래의 출력 버퍼 회로의 출력 트랜지스터(210, 212)의 단면 구조를 설명하기 위한 개념도이다.

도 15를 참조하면, 종래의 반도체 기억 장치에서는 P형 실리콘 기판(270)의 주표면 상에 제 1 P 웨이영역(266)과, 제 2 P 웨이영역(268)이 형성되고, 제 1 P 웨이영역(266)내와 제 2 P 웨이영역(268)내에는 각각 N 채널 MOS 트랜지스터(212, 210)가 각각 형성되어 있다.

N 채널 MOS 트랜지스터(212)는 N형 불순물 영역인 소스(252), 드레인(256)과 게이트 전극(254)을 포함한다. N 채널 MOS 트랜지스터(210)는 N형 불순물 영역인 소스(258), 드레인(262)과 게이트 전극(260)을 포함한다.

통상, 다이나믹 랜덤 액세스 메모리(이후 DRAM이라고 칭함)에 있어서는 P형 실리콘 기판에 접지 전위보다 낮은 전위가 공급되고 있다. 도 15에서는 P형 실리콘 기판(270)의 주표면 상에 P형 불순물 영역(264)이 형성되어 있어, P형 불순물 영역(264)을 거쳐 P형 실리콘 기판(270)에는 부(負)전위 Vbb가 공급

되고 있다.

DRAM에 있어서는, P형 실리콘 기판을 부전압으로 하는 것은 입력 신호의 언더슈트(undershoot)시에 전하가 기판으로 유입하는 것을 방지하여 메모리 셀의 데이터 파괴를 방지하는 기능을 갖는 점이나, 또는 비트선의 부유 용량으로 되는 PN 접합 용량을 작게 하여 회로를 고속 동작시킬 수 있는 기능을 갖는 점에서 대단히 중요하다.

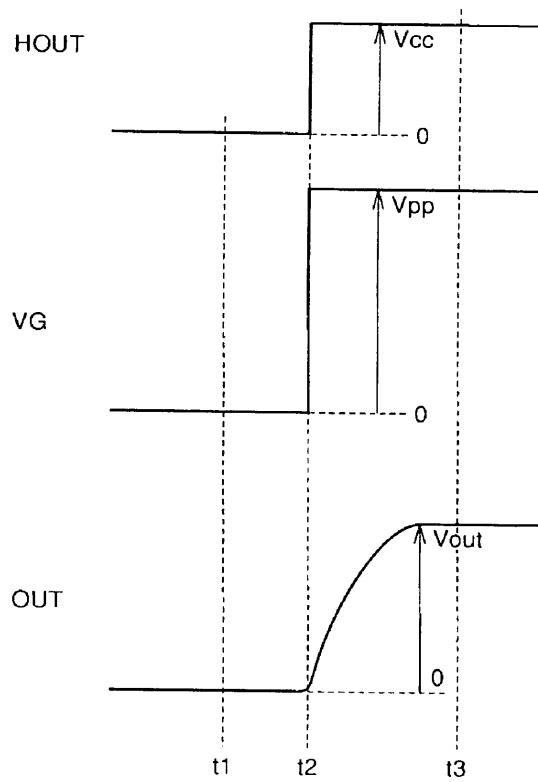

도 16은 도 14에 도시하는 출력 버퍼 회로의 동작을 설명하는 동작 파형도이다.

도 14, 도 16을 참조하면, 제 2 내부 제어 신호  $L_{OUT} = 'L'$  상태인 경우를 고려한다. 이 때, N 채널 MOS 트랜지스터(212)는 비도통 상태이다.

출력 단자 OUT의 레벨이 초기에 0 V일 때를 고려하면 시각  $t_1$ 에 있어서, 제 1 내부 제어 신호  $H_{OUT}$ 는 ' $L$ ' 레벨이고, N 채널 MOS 트랜지스터(206)는 비도통 상태이다.

이 때 인버터(214)에 의해 제 1 내부 제어 신호  $H_{OUT}$ 의 반전 신호가 게이트에 인가되기 때문에 N 채널 MOS 트랜지스터(208)는 도통 상태로 되어, 노드 N102는 ' $L$ ' 레벨로 된다.

노드 N102의 전위를 게이트에서 수신하는 P 채널 MOS 트랜지스터(202)는 도통 상태로 되어 P 채널 MOS 트랜지스터(204)의 게이트에 승압 전위  $V_{pp}$ 를 인가한다. 그 결과 P 채널 MOS 트랜지스터(204)는 비도통 상태로 되어 레벨 변환 회로의 출력인 노드 N102의 전위는 ' $L$ ' 레벨로 확정된다. 그 결과 직렬로 접속된 인버터(216, 218)에 의해 N 채널 MOS 트랜지스터(210)의 게이트 전위  $VG$ 는 ' $L$ ' 레벨로 된다.

시각  $t_2$ 에 있어서, 제 1 내부 제어 신호  $H_{OUT}$ 가 0 V로부터 내부 강압 전위  $V_{cc}$ 까지 상승하면, 그에 따라 N 채널 MOS 트랜지스터(206)가 도통 상태로 되고, 또한 제 1 내부 제어 신호  $H_{OUT}$ 는 인버터(214)에 의해 반전되기 때문에, 이것을 게이트에서 수신하는 N 채널 MOS 트랜지스터(208)는 비도통 상태로 된다. 따라서 P 채널 MOS 트랜지스터(204)의 게이트에는 N 채널 MOS 트랜지스터(206)를 통하여 ' $L$ ' 레벨이 인가되어 P 채널 MOS 트랜지스터(204)는 도통 상태로 되고, 노드 N102의 전위는 내부 승압 전위  $V_{pp}$ 까지 상승한다.

P 채널 MOS 트랜지스터(202)는 게이트 전위인 노드 N102의 전위가 ' $H$ ' 레벨로 되기 때문에 비도통 상태로 된다. 그 결과 레벨 변환 회로(220)의 출력인 노드 N102의 전위는 내부 승압 전위  $V_{pp}$ 로 확정되고, 제 1 내부 제어 신호  $H_{OUT}$ 의 ' $H$ ' 레벨이 내부 강압 전위  $V_{cc}$ 로부터 내부 승압 전위  $V_{pp}$ 로 변환된다. 이 전위가 인버터(216, 218)에 의해 전달되어 N 채널 MOS 트랜지스터(210)의 게이트 전위  $VG$ 는 0 V로부터 내부 승압 전위  $V_{pp}$ 로 상승한다. 이에 따라 N 채널 MOS 트랜지스터(210)는 도통하여 출력 단자 OUT의 전위를 상승시키기 시작한다.

시각  $t_3$ 에 있어서는 반도체 기억 장치 외부로부터 출력 단자 OUT으로 접속되는 부하 용량이 충분하게 충전되어 출력 단자 OUT의 전위가 안정한 상태로 된다.

여기서, 시각  $t_2 \sim t_3$ 에 있어서 출력 단자 OUT을 통하여 반도체 기억 장치가 외부에 접속된 부하 용량을 충전하는 전류는 N 채널 MOS 트랜지스터(210)에 의해서 공급되고,

$$IDS = K' (V_{gs} - V_{th})^2$$

에 의해 주어진다( $V_{gs}$ : 게이트-소스간 전위차,  $V_{th}$ : 임계값 전압,  $K'$ : 정수). 따라서, 출력 단자 OUT로부터 반도체 기억 장치 외부에 공급되는 전류는 N 채널 MOS 트랜지스터(210)의 임계값 전압  $V_{th}$ 의 영향을 받아서  $V_{th}$ 가 커지면 공급 전류  $IDS$ 는 작아진다.

그러나, 시각  $t_3$ 에 있어서는, N 채널 MOS 트랜지스터(210)의 임계값  $V_{th}$ 는 기판 바이어스 효과에 의해서 커진다.

그 이유를 이하에 설명한다. 시각  $t_3$ 에 있어서는 N 채널 MOS 트랜지스터(210)의 소스 전위는 출력 단자 OUT의 전위로서  $V_{out}$ 인데 반하여, N 채널 MOS 트랜지스터(210)의 기판부는 앞서 설명한 바와 같이 부전압 전위  $V_{bb}$ 로 되어 있기 때문에  $t_3$ 에 있어서의 N 채널 MOS 트랜지스터(210)의 소스-기판간 전위차  $V_{sb}$ 는 대단히 커진다.

일반적으로 MOS 트랜지스터의 소스-기판간 전위차  $V_{sb}$ 가 커지면 기판 바이어스 효과에 의해 MOS 트랜지스터의 임계값 전압  $V_{th}$ 는 커진다. 그 때문에, 소스-기판간 전위차  $V_{sb}$ 가 큰, 시각  $t_3$ 에 있어서는, N 채널 MOS 트랜지스터(210)의  $V_{th}$ 는 커진다. 이상이 그 이유이다.

여기에서, 수학식 1로부터 임계값 전압  $V_{th}$ 가 큰 경우에도, MOS 트랜지스터의 게이트-소스간 전위차  $V_{gs}$ 를 그만큼 크게 취하면 출력 전류  $IDS$ 를 크게 할 수 있다. 따라서, 종래는 출력 단자 OUT가 ' $H$ ' 레벨을 출력할 때에 N 채널 MOS 트랜지스터(210)의 게이트 전위  $VG$ 를 충분히 높게 함으로써, 즉 승압 전위  $V_{pp}$ 를 충분히 높게 설정함으로써 출력 단자 OUT의 출력 전류를 크게 얻어지도록 하여 왔다.

그러나, 최근의 반도체 기억 장치의 고집적화에 의해 MOS 트랜지스터가 미세화가 진행하고, 그것에 따른 MOS 트랜지스터의 게이트 산화막의 두께도 매년 감소하는 추세에 있다. 이 때문에, 게이트 산화막의 내압(耐壓)을 낮추고 게이트 전압을 높게 설정하면, MOS 트랜지스터의 신뢰성에 영향을 미칠 가능성이 있다. 따라서, 승압 전위  $V_{pp}$ 는 이 후에는 그다지 높게 할 수 없다.

한편, 내부 승압 전위  $V_{pp}$ 는 반도체 기억 장치 내부에서 외부 전원 전위  $V_{dd}$ 를 기준으로 차지 펌프 회로(charge pump circuit)에 의해 생성되어 있다.

이 차지 펌프 회로는 반도체 기억 장치 상에 형성된 캐패시터를 이용하여 소정의 주파수에서 내부 승압 노드로 전하를 올리는 것에 의해 고전위를 얻는다.

따라서 내부 승압 전위  $V_{pp}$ 에 의해 소비되는 소비 전류가 증가하면 상기 캐패시터의 용량을 크게 하든가, 또는 상기 소정의 주파수를 보다 높은 주파수로 하지 않으면 안 된다. 그러나, 캐패시터의 용량을 크게 하기 위해서는 반도체 기판상에 큰 면적을 필요로 하여 반도체 기억 장치의 비용 증대로 이어진다. 한편, 소정의 주파수를 높게 하는 것에도 한계가 있어 전하의 전송 효율이 나빠지게 된다.

따라서, 일본 특허 공개 평성 제 9-139077에 있어서는, 외부 전원과 내부 승압 노드의 양쪽으로부터 전류를 부하에 공급하는 프리부스트 회로(pre-boost circuit)가 제안되어 있다.

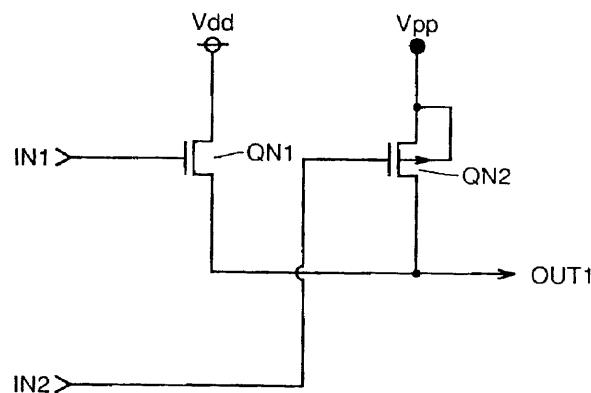

도 17은 상기 프리부스트 회로의 구성을 나타내는 회로도이다.

도 17을 참조하면, N 채널 MOS 트랜지스터 QN1은 외부 전원 전위  $V_{dd}$ 와 노드 OUT1 사이에 결합되고, 게이트에 내부 제어 신호 IN1이 입력되고 있다. 또한, P 채널 MOS 트랜지스터 QN2는 내부 승압 전위  $V_{pp}$ 와 노드 OUT1 사이에 결합되고, 게이트에 내부 제어 신호 IN2가 입력되고 있으며, 기판부는 내부 승압 전위  $V_{pp}$ 에 결합되어 있다.

이 회로는 노드 OUT1을 내부 승압 전위  $V_{pp}$ 까지 승압할 때에, P 채널 MOS 트랜지스터 QN2를 도통 상태로 하기 전에, N 채널 MOS 트랜지스터 QN1을 도통하여 노드 OUT1을 외부 전원 전위  $V_{dd}$ 까지 프리부스트해 놓고, 그런 후에 P 채널 MOS 트랜지스터 QN2를 도통 상태로 함으로써 내부 승압 전위  $V_{pp}$ 로부터 노드 OUT1로 흐르는 전류를 삭감하여 내부 승압 전위  $V_{pp}$ 에서의 소비 전류를 억제하는 것을 목적으로 하는 것이다.

그러나, 도 17의 회로에 있어서는, 특히 DRAM에 사용함에 있어 전원의 턴 온(turn-on)시 등에 있어서 승압 전위  $V_{pp}$ 의 레벨이 불안정한 상태에서는 동작이 불안정하게 될 가능성 있다. 이하, 이 상태에 대하여 설명한다.

도 18은 도 17의 프리부스트 회로를 DRAM에 사용하였을 때의 구조를 나타내는 단면도이다.

도 18을 참조하면, P형 실리콘 기판(370) 상에 N 웨이 영역(366)과 P 웨이 영역(368)이 형성되고, N 웨이 영역(366)내에는 P 채널 MOS 트랜지스터 QN2가 형성되며, P 웨이 영역(368)내에는 N 채널 MOS 트랜지스터 QN1이 형성되어 있다.

P형 실리콘 기판(370)은 P형 불순물 영역(364)을 거쳐 부전위  $V_{bb}$ 가 공급되고, N 웨이 영역(366)은 N형 불순물 영역(372)을 통해 내부 승압 전위  $V_{pp}$ 가 공급되고 있다. P 채널 MOS 트랜지스터 QN2의 소스인 P형 불순물 영역(352)은 내부 승압 전위  $V_{pp}$ 와 결합되고, P 채널 MOS 트랜지스터 QN2의 드레인인 P형 불순물 영역(356)은 N 채널 MOS 트랜지스터 QN1의 소스인 N형 불순물 영역(358)과 함께 노드 OUT1에 접속된다.

P 채널 MOS 트랜지스터 QN2의 게이트인 게이트 전극(354)에는 내부 제어 신호 IN2가 입력되고, N 채널 MOS 트랜지스터 QN1의 게이트인 게이트 전극(360)에는 내부 제어 신호 IN1이 입력된다.

여기서, 반도체 기억 장치의 전원의 턴 온 직후나, 단자에 외부 장애가 주어진 경우에는 내부 승압 전위  $V_{pp}$ 를 발생하고 있는 차지 펌프 회로가 불안정해져 외부 전원 전위  $V_{dd}$ 보다 내부 승압 전위  $V_{pp}$ 가 낮게 되는 경우를 생각할 수 있다.

이러한 경우에 내부 제어 신호 IN1이 N 채널 MOS 트랜지스터 QN1을 도통시키는 상태이면, 노드 OUT1은 외부 전원 전위  $V_{dd}$ 로 되어 P형 불순물 영역(356)과 N 웨이 영역(366) 사이의 PN 접합에 순방향의 바이어스가 걸린다. 그러면, P형 불순물 영역(356)과 N 웨이 영역(366)과 P형 실리콘 기판(370)에 의해 형성되어 있는 기생 PNP형 바이폴라 트랜지스터가 도통하여 P형 불순물 영역(356)으로부터 P형 실리콘 기판(370)으로 향하여 전류가 흐를 가능성이 있다. 이러한 상태는, DRAM에 있어서는 메모리 셀의 데이터가 상실될 가능성으로 이어짐과 동시에, 래치업(latch up)을 일으킬 가능성으로도 이어진다.

이와 같이, 웨이의 전위를 반도체 장치 내부에서 발생하는 전위로 할 때에는, 예기치 않은 사태를 맞이하여, 회로 구성상에 있어서도 대책을 세워 놓는 것이 중요하다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 내부 승압 전위  $V_{pp}$ 를 높게 하는 것을 억제하면서, 출력 단자로부터 충분한 전류를 공급할 수 있는 반도체 기억 장치를 제공하는 것이다.

본 발명의 다른 목적은 출력 버퍼 회로부에 있어서 출력 트랜지스터를 구동할 때에 내부 승압 전위  $V_{pp}$ 에서의 소비 전류를 억제하는 실용적인 수단을 이용함으로써 차지 펌프 회로부를 소형화할 수 있어 침면적이 보다 작은 반도체 기억 장치를 제공하는 것이다.

### 발명의 구성 및 작용

본 발명은 요약하면, 반도체 기억 장치에 있어서 출력 단자와, 제 1 MOS 트랜지스터와, 제 1 구동 회로와, 제 2 구동 회로를 구비한다.

제 1 MOS 트랜지스터는 출력 단자에 외부 전원으로부터 전류를 공급한다. 제 1 구동 회로는 제 1 MOS 트랜지스터의 게이트 전위를 제 1 내부 제어 신호에 대응하여 구동한다. 제 2 구동 회로는 제 1 MOS 트랜지스터의 기판부의 전위를 내부 제어 신호에 따라 구동한다.

본 발명의 다른 국면에 따르면, 반도체 기억 장치에 있어서, 출력 단자와, 승압 회로와, 제 1 MOS 트랜지스터와, 제 3 스위칭 회로와, 제 4 스위칭 회로와, 전류 제한 수단을 구비한다.

승압 회로는 외부 전원 전위보다 더 고전위인 승압 전위를 발생한다. 제 1 MOS 트랜지스터는 출력 단자에 제 1 내부 제어 신호에 따라 외부 전원으로부터 전류를 공급한다. 제 3 스위칭 회로는 승압 회로로부터 전류를 공급받아 제 1 MOS 트랜지스터의 게이트에 제 1 내부 제어 신호에 따라 전류를 공급한다. 제 4 스위칭 회로는 외부 전원으로부터 전류 제한 수단을 거쳐 전류를 공급받아 제 1 MOS 트랜지스터의 게이트에 제 1 내부 제어 신호에 따라 전류를 공급한다. 전류 제한 수단은 승압 전위가 소정의 전위로 승압되어 있지 않은 기간 동안에는 외부 전원으로부터 제 1 MOS 트랜지스터의 게이트로 흐르는 전류를 제한한다.

따라서, 본 발명의 주된 효과는 출력 버퍼 회로의 출력 트랜지스터가 전류를 공급할 때에, 출력 트랜지스터의 기판부의 전위를 적절하게 제어함으로써 출력 트랜지스터의 임계값 전압의 증가를 억제하여 출력 트랜지스터의 출력 전류를 보다 크게 할 수 있다.

본 발명의 다른 효과는 출력 단자로부터 'H' 레벨을 출력할 때에 출력 트랜지스터의 게이트를 구동하는 전류를 내부 승압 전위  $V_{pp}$  발생 회로와 함께 외부 전원으로부터도 공급한다. 그 때문에 내부 승압 전위  $V_{pp}$  발생 회로에서의 소비 전류를 작게 할 수 있고 내부 승압을 행하는 차지 범프 회로를 소형화할 수 있어, 반도체 기억 장치의 칩 면적을 작게 할 수 있다.

본 발명의 상기 및 그 밖의 목적, 특징, 국면 및 이익 등을 첨부 도면을 참조로 하여 설명하는 이하의 상세한 실시예로부터 더욱 명백해질 것이다.

### 바람직한 실시예의 설명

(실시예 1)

이하, 본 발명의 실시예 1의 반도체 기억 장치(1000)에 대하여 설명한다. 또 이하 동일한 구성 요소에는 동일한 부호 및 동일한 기호를 기록하고 그 설명은 반복하지 않는다.

도 1은 본 발명에 있어서의 반도체 기억 장치 전체의 구성을 나타내는 개략적인 블럭도이다. 이 전체 구성은 이하 설명하는 실시예 모두에 적용할 수 있는 대표적인 일례이다.

도 1을 참조하면, 이 반도체 기억 장치(1000)는 제어 신호 입력 단자(1002~1006)와, 어드레스 신호 입력 단자군(1008)과, 데이터 신호 입출력 단자군(1016)과, 접지 단자(1018)와, 전원 단자(1020)를 구비한다.

또한, 이 반도체 기억 장치(1000)는 클럭 발생 회로(1022)와, 행 및 열 어드레스 버퍼(1024)와, 행 디코더(1026)와, 열 디코더(1028)와, 메모리 매트(memory mat)(1032)와, 데이터 입력 버퍼(1040) 및 데이터 출력 버퍼(1042)를 구비하고, 메모리 매트(1032)는 메모리 셀 어레이(1034) 및 센스 앰프 + 입출력 제어 회로(1038)를 포함한다.

클럭 발생 회로(1022)는 제어 신호 입력 단자(1002, 1004)를 거쳐 외부로부터 인가되는 외부 행 어드레스 스트로브 신호 EXT. /RAS, 외부 열 어드레스 스트로브 신호 EXT. /CAS에 근거하여 소정의 동작 모드를 선택해서 반도체 기억 장치 전체의 동작을 제어한다.

행 및 열 어드레스 버퍼(1024)는 어드레스 신호 입력 단자군(1008)을 거쳐 외부로부터 인가되는 어드레스 신호 A0~Ai(단, i는 자연수임)에 근거하여 행 어드레스 신호 RA0~RAi 및 열 어드레스 신호 CA0~CAi를 생성하고, 생성된 신호 RA0~RAi 및 CA0~CAi를 각각 행 디코더(1026) 및 열 디코더(1028)에 인가한다.

메모리 매트(1032)는 각각이 1 비트의 데이터를 기억하는 복수의 메모리 셀을 포함한다. 각 메모리 셀은 행 어드레스 및 열 어드레스에 의해 결정되는 소정의 어드레스에 배치된다.

행 디코더(1026)는 메모리 셀 어레이(1034)의 열 어드레스를 지정한다.

센스 앰프 + 입출력 제어 회로(1038)는 행 디코더(1026) 및 열 디코더(1028)에 의해 지정된 어드레스의 메모리 셀을 데이터 신호 입출력선쌍 IDP의 한쪽 단부에 접속한다. 데이터 신호 입출력선쌍 IDP의 다른 쪽 단부는 데이터 입력 버퍼(1040) 및 데이터 출력 버퍼(1042)에 접속된다.

데이터 입력 버퍼(1040)는 기입 모드시에 제어 신호 입력 단자(1006)를 거쳐 외부로부터 인가되는 신호 EXT. /WE에 응답하여 데이터 신호 입력 단자군(1016)으로부터 입력된 데이터를 데이터 신호 입출력선쌍 IDP를 거쳐 선택된 메모리 셀에 인가한다.

데이터 출력 버퍼(1042)는 판독 모드시에 선택된 메모리 셀로부터의 판독 데이터를 데이터 입출력 단자군(1016)에 출력한다.

전원 회로(1050)는 외부 전원 전위  $V_{dd}$ 와 접지 전위  $V_{ss}$ 를 수신하여 반도체 기억 장치의 동작에 필요한 여러 가지의 내부 전원 전위를 공급한다.

즉, 전원 회로(1050)는 외부 전원 전위  $V_{dd}$ 와 접지 전위  $V_{ss}$ 를 수신하여 외부 전원 전위  $V_{dd}$ 를 강압한 내부 강압 전위  $V_{cc}$ 와, 승압한 내부 승압 전위  $V_{pp}$ 를 출력하는 내부 전원 회로(1054)와, 메모리 셀 어레이(1034) 중에 포함되는 비트선쌍에 대한 프리차지 전위  $V_{BL}$ 을 공급하는 프리차지 전위 발생 회로(1052)를 포함한다.

도 2는 도 1에 도시한 반도체 기억 장치(1000)에 구비된 내부 전원(1054)의 구성을 나타내는 회로도이다.

도 2를 참조하면, 내부 전원(1054)은 외부 전원 전위  $V_{dd}$ 로부터 내부 승압 전위  $V_{pp}$ 를 발생하는 차지 펌프 회로(charge pump circuit)(318)와, 외부 전원 전위  $V_{dd}$ 로부터 내부 강압 전위  $V_{cc}$ 를 발생하는  $V_{cc}$  발생 회로(320)를 포함한다.

차지 펌프 회로(318)는 반도체 기억 장치 상의 클럭 발생 회로(1022)에서 발생된 클럭 신호  $\phi$ 를 수신하는 인버터(302, 304)와, 인버터(304)의 출력을 수신하는 인버터(306)를 갖는다.

인버터(302, 306)의 출력은 캐패시터(308, 310)의 전극에 각각 접속된다. 캐패시터(308)의 다른쪽 전극은 트랜지스터(312)에 의해 노드 NGA에서 외부 전원과 다이오드 접속된다. 트랜지스터(314)의 게이트는 노드 NGA의 전위를 수신한다. 캐패시터(310)의 다른쪽 전극은 노드 NDR에서 내부 승압 전위 Vpp와 트랜지스터(316)에 의해 다이오드 접속된다. 트랜지스터(314)는 외부 전원 전위 Vdd와 노드 NDR 사이에 접속된다.

노드 NGA의 전위는 클럭 신호  $\phi$ 가 'H'로부터 'L'로 변화하는 것에 따라 캐패시터(308)의 기능에 의해 외부 전원 전위 Vdd보다 높은 전위로 상승되고, 그 결과 트랜지스터(314)는 도통 상태로 되어 노드 NDR의 전위는 외부 전원 전위 Vdd로 된다.

다음에 클럭 신호  $\phi$ 가 'L'로부터 'H'로 변화하면, 그 변화에 따라 트랜지스터(314)는 비도통 상태로 됨과 동시에 캐패시터(310)의 기능에 의해 노드 NDR의 전위는 외부 전원 전위 Vdd만큼 더 상승된다. 이 때 다이오드의 역할을 하는 트랜지스터(316)를 거쳐 차지 펌프 회로(318)가 내부 승압 전위 Vpp를 향해 전류를 공급한다.

이 회로에 있어서는 차지 펌프 회로의 캐패시터(310)의 용량을 C, 펌핑 주파수를 f, 트랜지스터(316)의 임계값 전압을 Vth로 하면, 발생 전류 Ipp는,

$$Ipp = fC(2Vdd - Vth - Vpp)$$

로 주어진다.

수학식 2로부터, 필요한 발생 전류 Ipp가 작으면 차지 펌프 회로의 C는 작게 하는 것이 가능하다는 것을 알 수 있다.

도 3은 본 발명의 실시예 1의 반도체 기억 장치(1000)에 이용되는 출력 버퍼 회로(2000)의 기본 구성을 나타내는 회로도이다.

출력 버퍼 회로(2000)는 도 1에 있어서의 데이터 출력 버퍼(1042)의 1 비트분으로 마련되고, 입력 신호로서 클럭 발생 회로(1022)로부터의 제어 신호나 입출력 제어 회로(1038)로부터의 판독 데이터를 바탕으로 생성된 서로 상보인 제 1 내부 신호 HOUT과 제 2 내부 신호 LOUT를 수신한다.

도 3을 참조하면, 출력 버퍼 회로(2000)는 출력 단자 DQr과, 외부 전원 전위 Vdd와 출력 단자 DQr 사이에 결합되는 N 채널 MOS 트랜지스터(18)와, 접지 전위 Vss와 출력 단자 DQr 사이에 결합되고 게이트에서 제 2 내부 제어 신호 LOUT를 수신하는 N 채널 MOS 트랜지스터(20)와, 제 1 내부 제어 신호 HOUT를 수신하여 N 채널 MOS 트랜지스터(18)의 게이트를 구동하는 신호 VG를 출력하는 구동 회로(36)와, 제 1 내부 제어 신호 HOUT를 수신하여 N 채널 MOS 트랜지스터(18)의 기판부를 구동하는 신호 VB를 출력하는 기판 전위 구동 회로(38)를 구비한다.

구동 회로(36)는 제 1 내부 제어 신호 HOUT의 'H' 레벨을 내부 강압 전위 Vcc로부터 내부 승압 전위 Vpp로 하는 레벨 변환 회로(34)와, 레벨 변환 회로(34)의 출력을 수신하여 N 채널 MOS 트랜지스터(18)의 게이트를 구동하는 직렬로 접속된 인버터(24, 26)를 포함한다.

레벨 변환 회로(34)는 제 1 내부 제어 신호 HOUT를 게이트에서 수신하는 N 채널 MOS 트랜지스터(6)와, 제 1 내부 제어 신호 HOUT를 수신하여 반전하는 인버터(22)와, 인버터(22)의 출력을 게이트에서 수신하는 N 채널 MOS 트랜지스터(8)를 구비한다.

N 채널 MOS 트랜지스터(6, 8)의 소스는 모두 접지 전위 Vss에 결합되어 있다.

레벨 변환 회로(34)는 내부 승압 전위 Vpp와 N 채널 MOS 트랜지스터(6)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(8)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(2)와, 내부 승압 전위 Vpp와 N 채널 MOS 트랜지스터(8)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(6)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(4)를 더 구비한다.

레벨 변환 회로(34)는 N 채널 MOS 트랜지스터(8)의 드레인이 접속되는 노드 N32로부터 출력 신호 즉, 내부 제어 신호 HOUT과 동상이면서 'H' 레벨이 내부 승압 전위 Vpp로 되는 신호를 인버터(24)에 대하여 출력한다.

기판 전위 구동 회로(38)는 제 1 내부 제어 신호 HOUT의 'H' 레벨을 내부 강압 전위 Vcc로부터 외부 전원 전위 Vdd로 하는 레벨 변환 회로(40)와, 레벨 변환 회로(40)의 출력을 수신하여 N 채널 MOS 트랜지스터(18)의 기판부를 구동하는 직렬로 접속된 인버터(30, 32)를 포함한다.

레벨 변환 회로(40)는 제 1 내부 제어 신호 HOUT를 게이트에서 수신하는 N 채널 MOS 트랜지스터(14)와, 제 1 내부 제어 신호 HOUT를 수신하여 반전하는 인버터(28)와, 인버터(28)의 출력을 게이트에서 수신하는 N 채널 MOS 트랜지스터(16)를 구비한다.

N 채널 MOS 트랜지스터(14, 16)의 소스는 모두 접지 전위 Vss에 결합되어 있다.

레벨 변환 회로(40)는 외부 전원 전위 Vdd와 N 채널 MOS 트랜지스터(14)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(16)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(10)와, 외부 전원 전위 Vdd와 N 채널 MOS 트랜지스터(16)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(14)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(12)를 더 구비한다.

레벨 변환 회로(40)는 N 채널 MOS 트랜지스터(16)의 드레인이 접속되는 노드 N34로부터 출력 신호 즉,

제 1 내부 제어 신호 HOUT과 동상이면서 'H' 레벨이 외부 전원 전위 Vdd로 되는 신호를 인버터(30)에 대하여 출력한다.

다음에 출력 버퍼(2000)의 출력 트랜지스터인 N 채널 MOS 트랜지스터(18, 20)의 단면 구조를 설명한다.

도 4는 N 채널 MOS 트랜지스터(18, 20)의 단면 구조를 설명하기 위한 개념도이다.

도 4를 참조하면, 실시예 1의 반도체 기억 장치에서는 P형 실리콘 기판(76)의 주표면 상에는 제 1 P 웨爾 영역(70)과 N 웨爾 영역(74)이 형성되고, N 웨爾 영역(74)내에는 제 2 P 웨爾 영역(72)이 형성되어 있다.

P 웨爾 영역(70, 72)내에는 각각 N 채널 MOS 트랜지스터(20, 18)가 형성되어 있다.

N 채널 MOS 트랜지스터(20)는 N형 불순물 영역인 소스(52), 드레인(56)과 게이트 전극(54)을 포함한다. N 채널 MOS 트랜지스터(18)는 N형 불순물 영역인 소스(58), 드레인(62)과 게이트 전극(60)을 포함한다.

N 채널 MOS 트랜지스터(20)의 소스(52)는 접지 전위 Vss에 결합되고, 게이트 전극(54)에는 제 2 내부 제어 신호 LOUT가 입력되어 있다. N 채널 MOS 트랜지스터(20)의 드레인(56)은 N 채널 MOS 트랜지스터(18)의 소스(58)와 함께 출력 단자 DQr과 접속되어 있다. N 채널 MOS 트랜지스터(18)의 드레인은 외부 전원 전위 Vdd와 결합된다.

P형 실리콘 기판(76)의 주표면 상에는 P형 불순물 영역(68)이 형성되고, P형 불순물 영역(68)을 거쳐 P형 실리콘 기판(76)에는 부전위 Vbb가 공급되고 있다.

또한 도 4에 있어서는, N 웨爾 영역(74)은 N형 불순물 영역(66)을 거쳐 외부 전원 전위 Vdd와 결합되어 있어, 이것 때문에 P 웨爾 영역(72)은 P 웨爾 영역(70) 및 P형 실리콘 기판(76)과 전기적으로 분리된다.

도 5는 도 3에 도시하는 출력 버퍼 회로(2000)의 동작을 설명하는 동작 파형도이다.

도 3, 도 4 및 도 5를 참조하면, 내부 제어 신호 LOUT가 'L' 상태인 경우를 고려한다. 이 때, N 채널 MOS 트랜지스터(20)는 비도통 상태이다.

출력 단자 OUT의 레벨이 초기에 0 V일 때를 고려한다.

시각 t1에 있어서, 제 1 내부 제어 신호 HOUT는 'L' 레벨이고, N 채널 MOS 트랜지스터(6)는 비도통 상태이다. 이 때 인버터(22)에 의해 내부 제어 신호 HOUT의 반전 신호가 게이트에 인가되기 때문에 N 채널 MOS 트랜지스터(8)는 도통 상태로 되어 노드 N32는 'L' 레벨로 된다. 노드 N32의 전위를 게이트에서 수신한 P 채널 MOS 트랜지스터(2)는 도통 상태로 되어 P 채널 MOS 트랜지스터(4)의 게이트로 승압 전위 Vpp를 인가한다. 그 결과 P 채널 MOS 트랜지스터(4)는 비도통 상태로 되어 레벨 변환 회로(34)의 출력인 노드 N32의 전위는 'L' 레벨로 확정된다. 그리고 직렬로 접속된 인버터(24, 26)에 의해 N 채널 MOS 트랜지스터(18)의 게이트 전극(60)의 전위 VG는 'L' 레벨로 된다.

한편, 기판 전위 구동 회로(38)에 있어서는, 내부 제어 신호 HOUT='L'이기 때문에 N 채널 MOS 트랜지스터(14)는 비도통 상태이고, 인버터(28)에 의해 그 반전 신호가 게이트에 입력되어 있는 N 채널 MOS 트랜지스터(16)는 도통 상태로 된다. 그리고, 노드 N34는 'L' 레벨로 된다. 노드 N34의 전위를 게이트에서 수신한 P 채널 MOS 트랜지스터(10)는 도통 상태로 되어 P 채널 MOS 트랜지스터(12)의 게이트로 외부 전원 전위 Vdd를 인가한다. 그 결과 P 채널 MOS 트랜지스터(12)는 비도통 상태로 되어 레벨 변환 회로(40)의 출력인 노드 N34의 전위는 'L' 레벨로 확정된다. 그리고, 직렬로 접속된 인버터(30, 32)에 의해 N 채널 MOS 트랜지스터(18)의 기판부의 전위(P 웨爾 영역(72)의 전위) VB는 'L' 레벨, 즉 접지 전위 Vss로 된다.

이상으로부터, 시각 t1에 있어서는 N 채널 MOS 트랜지스터(18)는 비도통 상태로 되어 출력 단자 DQr의 전위는 초기 상태인 0 V인 채로 있다.

다음에, 시각 t2에 있어서 제 1 내부 제어 신호 HOUT가 0 V로부터 내부 강압 전위 Vcc까지 상승하면, 그에 따라 구동 회로(36)에 있어서 N 채널 MOS 트랜지스터(6)가 도통 상태로 되고, 또한, 제 1 내부 제어 신호 HOUT는 인버터(22)에 의해 반전되기 때문에, 이것을 게이트에서 수신하는 N 채널 MOS 트랜지스터(8)는 비도통 상태로 된다. 따라서, P 채널 MOS 트랜지스터(4)의 게이트에는 N 채널 MOS 트랜지스터(6)를 통해 'L' 레벨이 인가되고 P 채널 MOS 트랜지스터(4)는 도통 상태로 되어 노드 N32의 전위는 내부 승압 전위 Vpp로 상승한다. 노드 N32에 게이트가 접속되어 있는 P 채널 MOS 트랜지스터(2)는 이에 따라 비도통 상태로 된다.

따라서, 레벨 변환 회로(34)의 출력인 노드 N32의 전위는 'H' 레벨로 확정되어 승압 전위 Vpp로 된다. 즉, 제 1 내부 제어 신호 HOUT의 'H' 레벨이 내부 강압 전위 Vcc로부터 내부 승압 전위 Vpp로 변환된다. 이 전위가 인버터(24, 26)에 의해 N 채널 MOS 트랜지스터(18)의 게이트 전극(60)에 입력되어 그 게이트 전위 VG는 0 V로부터 내부 승압 전위 Vpp로 상승한다. 이에 따라 N 채널 MOS 트랜지스터(18)는 도통하여 출력 단자 DQr의 전위를 상승시키기 시작하는 것은 종래 기술에서 설명한 도 14의 출력 버퍼 회로의 경우와 마찬가지이다.

본 발명의 실시예 1의 경우에는, 시각 t2에 있어서, 동시에 기판 전위 구동 회로(38)에 의해 N 채널 MOS 트랜지스터(18)의 기판부(P 웨爾 영역(72))의 전위가 구동되는 점에서 종래 기술의 출력 버퍼 회로의 경우와 상이하다. 이하, 그 동작에 대하여 설명한다.

제 1 내부 제어 신호 HOUT의 상승에 따라 기판 전위 구동 회로(38)에 있어서, N 채널 MOS 트랜지스터(14)가 도통 상태로 되고, 또한, 제 1 내부 제어 신호 HOUT는 인버터(28)에 의해 반전되기 때문에, 이것을 게이트에서 수신하는 N 채널 MOS 트랜지스터(16)는 비도통 상태로 된다. 따라서, P 채널 MOS 트랜지스터(12)의 게이트에는 N 채널 MOS 트랜지스터(14)를 통해 'L' 레벨이 인가되어 P 채널 MOS 트랜지스터(12)는 도통 상태로 되고, 노드 N34의 전위는 외부 전원 전위 Vdd로 상승한다. 노드 N34에 게이트가 접속되어 있는 P 채널 MOS 트랜지스터(10)는 이에 따라 비도통 상태로 된다.

따라서, 레벨 변환 회로(40)의 출력인 노드 N34의 전위는 'H' 레벨로 확정되어 외부 전원 전위 Vdd로 된

다. 즉, 제 1 내부 제어 신호 HOUT의 'H' 레벨이 내부 강압 전위 Vcc로부터 외부 전원 전위 Vdd로 변환된다. 이 전위가 인버터(30, 32)에 의해 N 채널 MOS 트랜지스터(18)의 기판부(P 웨이 영역(72))에 인가되어 그 기판 전위 VB는 0 V로부터 외부 전원 전위 Vdd로 상승한다.

시각 t3에 있어서는, 반도체 기억 장치 외부에서 출력 단자 DQr에 접속되는 부하 용량이 N 채널 MOS 트랜지스터(18)의 도통에 의해 충분히 충전되어 출력 DQr의 전위가 안정한 상태로 된다.

그런데, 여기서 t2~t3에 있어서, N 채널 MOS 트랜지스터(18)가 출력 단자에 공급하는 전류는 수학식 1에 의해 주어지지만, 본 발명의 실시예 1의 경우에서 N 채널 MOS 트랜지스터(18)의 기판부(P 웨이 영역(72))의 전위는 외부 전원 전위 Vdd로 되기 때문에 기판 바이어스 효과의 영향이 도 14의 종래 예의 경우보다 작아서 그 결과 전류 IDS를 크게 하는 것이 가능해진다. 그 결과 내부 승압 전위 Vpp를 종래 이상으로 상승시킬 필요가 없어진다.

또한, 도 4에 있어서 기판 전위 VB가 외부 전원 전위 Vdd로 되어 있기 때문에 P 웨이 영역(72)의 전위는 외부 전원 전위 Vdd로 되어 N형 불순물 영역(58) 사이가 순방향으로 되므로, 이 부분의 PN 접합에 의해 N 채널 MOS 트랜지스터(18)와는 별도로, 또한 전류를 출력 단자 DQr을 향해 공급하게 된다. 그 결과, 출력 단자 DQr로부터 반도체 기억 장치 외부를 향해 보다 큰 전류를 공급하는 것이 가능해진다.

#### (실시예 1의 변형 예 1)

본 발명의 실시예 1의 반도체 기억 장치에서는 도 3에 도시하는 N 채널 MOS 트랜지스터(18)와 N 채널 MOS 트랜지스터(20)의 기판부를 전기적으로 분리하는 방법이 실시예 1의 경우와 상이하다.

도 6은 실시예 1의 변형 예 1에 있어서의 N 채널 MOS 트랜지스터(18, 20)의 단면 구조를 설명하기 위한 개념도이다.

도 6에서는 P형 실리콘 기판(76) 상에 형성된 N 웨이 영역(74)이 N 채널 MOS 트랜지스터(18)의 기판 전위를 인가하고 있는 P 웨이 영역(72)과 불순물 영역(64, 66)을 거쳐 접속되어 있고, 그 전위가 기판 전위 VB로 되어 있는 점이 실시예 1의 경우와 상이하다.

이 경우에서도 실시예 1의 경우와 마찬가지의 효과를 기대할 수 있다.

#### (실시예 1의 변형 예 2)

본 발명의 실시예 1의 변형 예 2도, 변형 예 1과 마찬가지로 도면 3에 도시하는 N 채널 MOS 트랜지스터(18)와 N 채널 MOS 트랜지스터(20)의 기판부를 전기적으로 분리하는 방법이 상이한 경우이다.

도 7은 실시예 1의 변형 예 2에 있어서의 N 채널 MOS 트랜지스터(18, 20)의 단면 구조를 설명하기 위한 개념도이다.

도 7에서는 반도체 기억 장치의 기판에 N형 실리콘 기판(124)을 사용하고 있다. N 채널 MOS 트랜지스터(20, 18)가 각각 형성되어 있는 영역인 P 웨이 영역(70, 72)는 모두 N형 실리콘 기판(124) 상에 마련되어 있다. 그리고, N형 실리콘 기판(124)에는 N형 불순물 영역(118)을 통해 외부 전원 전위 Vdd가 공급되고 있고, 또, P 웨이 영역(70)에는 P형 불순물 영역(102)을 통해 접지 전위 Vss가 공급되고 있다. 이상의 점에서 실시예 1의 경우와 상이하다.

이 경우에서도 실시예 1의 경우와 마찬가지의 효과를 기대할 수 있다.

#### (실시예 1의 변형 예 3)

도 8은 실시예 1의 변형 예 3에 있어서의 N 채널 MOS 트랜지스터(18, 20)의 단면 구조를 설명하기 위한 개념도이다.

실시예 1의 변형 예 3의 반도체 기억 장치는 변형 예 1과 마찬가지로서, 도 3에 도시하는 N 채널 MOS 트랜지스터(18)와, N 채널 MOS 트랜지스터(20)의 기판부를 전기적으로 분리하는 방법이 상이하다.

구체적으로는, 변형 예 3의 반도체 기억 장치는 이하의 점에서 실시예 1의 경우와 상이하다.

도 8에서는 제 2 N 웨이 영역(71)이 P형 실리콘 기판(76)의 주표면 상에 형성되어 있다. 그리고 N 채널 MOS 트랜지스터(20)가 형성되어 있는 영역인 P 웨이 영역(70)은 제 2 N 웨이 영역(71)내에 형성된다.

P 웨이 영역(70)내에 형성된 P형 불순물 영역(55)을 거쳐 P 웨이 영역(70)에는 접지 전위 Vss가 인가되고 있다.

제 2 N 웨이 영역(71)내에는 N형 불순물 영역(53)이 형성되어 있고, 제 2 N 웨이 영역(71)에는 N형 불순물 영역(53)을 거쳐 외부 전원 전위 Vdd 또는 접지 전위 Vss가 인가되고 있다.

이 경우에서도, 실시예 1의 경우와 마찬가지의 효과를 기대할 수 있다.

또한, 제 2 N 웨이 영역(71)의 전위를 외부 전원 전위 Vdd로 고정하는 경우는 N 웨이 영역(74)과 제 2 N 웨이 영역(71)은 분리하지 않고 동일한 N 웨이 영역으로 하는 것도 가능하다.

#### (실시예 1의 변형 예 4)

도 9는 실시예 1의 변형 예 4에 있어서의 N 채널 MOS 트랜지스터(18, 20)의 단면 구조를 설명하기 위한 개념도이다.

실시예 1의 변형 예 4의 반도체 기억 장치는 변형 예 1과 마찬가지로서, 도 3에 도시하는 N 채널 MOS 트랜지스터(18, 20)의 단면 구조를 설명하기 위한 개념도이다.

지스터(18)와, N 채널 MOS 트랜지스터(20)의 기판부를 전기적으로 분리하는 방법이 상이하다.

구체적으로는, 변형 예 4의 반도체 기억 장치는 이하의 점에서 실시 예 1의 경우와 상이하다.

도 9에서는 제 2 N 웨爾 영역(71)이 P형 실리콘 기판(76)의 주표면 상에 형성되어 있다. 그리고, N 채널 MOS 트랜지스터(20)가 형성되어 있는 영역인 P 웨爾 영역(70)은 제 2 N 웨爾 영역(71)내에 형성된다.

P 웨爾 영역(70)내에 형성된 P형 불순물 영역(55)을 거쳐 P 웨爾 영역(70)에는 접지 전위 Vss가 인가되고 있다.

제 2 N 웨爾 영역(71)내에는 N형 불순물 영역(53)이 형성되어 있고, 제 2 N 웨爾 영역(71)에는 N형 불순물 영역(53)을 거쳐 외부 전원 전위 Vdd 또는 접지 전위 Vss가 인가되고 있다(이상은 도 8에 도시하는 변형 예 3과 동일하다).

또한, 도 9에서는 P형 실리콘 기판(76) 상에 형성된 N 웨爾 영역(74)이 N 채널 MOS 트랜지스터(18)의 기판 전위를 인가하고 있는 P 웨爾 영역(72)과, 불순물 영역(64, 66)을 거쳐 접속되어 있고 그 전위는 기판 전위 VB로 되어 있다.

이 경우에서도, 실시 예 1의 경우와 마찬가지의 효과를 기대할 수 있다.

#### (실시 예 2)

본 발명의 실시 예 2의 반도체 기억 장치에서는 내부 승압 전위 Vpp를 발생하는 회로와 함께 외부 전원으로부터도 그 출력 버퍼 회로 부분의 출력 트랜지스터의 게이트를 충전하는 전류를 공급하여 내부 승압 전위 Vpp의 전압을 발생하는 회로의 소비 전류를 억제하는 것을 가능하게 하는 것을 목적으로 한다.

도 10은 본 발명의 실시 예 2의 반도체 기억 장치에 이용되는 출력 버퍼 회로(3000)의 기본 구성을 나타내는 회로도이다.

실시 예 2에 있어서의 반도체 기억 장치의 전체 구성은 실시 예 1의 경우와 마찬가지로서, 출력 버퍼 회로(3000)는 도 1에 있어서의 데이터 출력 버퍼(1042)의 1 비트분으로 마련되고, 입력 신호로서 클럭 발생 회로(1022)나 입출력 제어 회로(1038)로부터의 판독 데이터를 바탕으로 생성된 서로 상보인 제 1 내부 신호 HOUT과 제 2 내부 신호 LOUT를 수신하는 점은 실시 예 1의 경우와 마찬가지이다.

도 10를 참조하면, 출력 버퍼 회로(3000)는 출력 단자 DQr과, 외부 전원 전위 Vdd와 출력 단자 DQr 사이에 결합되는 N 채널 MOS 트랜지스터(176)와, 접지 전위 Vss와 출력 단자 DQr 사이에 결합되어 게이트에서 제 2 내부 제어 신호 LOUT를 수신하는 N 채널 MOS 트랜지스터(178)와, 제 1 내부 제어 신호 HOUT를 수신하여 그 'H' 레벨을 내부 승압 전위 Vpp로 하는 레벨 변환 회로(188)와, 레벨 변환 회로(188)의 출력을 수신하는 인버터(182)와, 인버터(182)의 출력인 신호 CLK3을 수신하여 그에 따라 출력 트랜지스터인 N 채널 MOS 트랜지스터(176)의 게이트 전위를 제어하는 프리부스트 회로(186)를 구비한다.

레벨 변환 회로(188)는 제 1 내부 제어 신호 HOUT를 게이트에서 수신하는 N 채널 MOS 트랜지스터(156)와, 제 1 내부 제어 신호 HOUT를 수신하여 반전하는 인버터(180)와, 인버터(180)의 출력을 게이트에서 수신하는 N 채널 MOS 트랜지스터(158)를 구비한다.

N 채널 MOS 트랜지스터(156, 158)의 소스는 모두 접지 전위 Vss로 결합되어 있다.

레벨 변환 회로(188)는 내부 승압 전위 Vpp와 N 채널 MOS 트랜지스터(156)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(158)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(152)와, 내부 승압 전위 Vpp와 N 채널 MOS 트랜지스터(158)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(156)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(154)를 더 구비한다.

N 채널 MOS 트랜지스터(158)의 드레인이 접속되는 노드 N2는 레벨 변환 회로(188)의 출력으로 되어, 제 1 내부 제어 신호 HOUT과 동상이면서 'H' 레벨이 내부 승압 전위 Vpp로 되는 신호를 인버터(182)에 대하여 출력한다.

프리부스트 회로(186)는 제 1 내부 제어 신호 HOUT를 게이트에서 수신하는 N 채널 MOS 트랜지스터(164)와, 제 1 내부 제어 신호 HOUT를 수신하여 반전하는 인버터(184)와, 인버터(184)의 출력을 게이트에서 수신하는 N 채널 MOS 트랜지스터(166)를 구비한다.

N 채널 MOS 트랜지스터(164, 166)의 소스는 모두 접지 전위 Vss로 결합되어 있다.

프리부스트 회로(186)는 외부 전원 노드 Vdd와 N 채널 MOS 트랜지스터(164)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(166)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(160)와, 외부 전원 전위 Vdd와 N 채널 MOS 트랜지스터(166)의 드레인 사이에 결합되어 게이트에서 N 채널 MOS 트랜지스터(164)의 드레인의 전위를 수신하는 P 채널 MOS 트랜지스터(162)를 더 구비한다.

N 채널 MOS 트랜지스터(166)의 드레인은 제 1 내부 제어 신호 HOUT과 동상이면서 'H' 레벨이 외부 전원 전위 Vdd로 되는 신호 CLK2를 출력한다.

한편, N 채널 MOS 트랜지스터(164)의 드레인은 제 1 내부 제어 신호 HOUT과 역상(逆相)이면서 'H' 레벨이 외부 전원 전위 Vdd로 되는 신호 CLK1을 출력한다.

프리부스트 회로(186)는 신호 CLK1을 게이트에서 수신하고 프리부스트 회로(186)의 출력인 노드 N1의 전위와 접지 전위 Vss 사이에 결합되는 N 채널 MOS 트랜지스터(170)와, 내부 승압 전위 Vpp와 노드 N1의 전위 사이에 결합되어 게이트에서 신호 CLK3을 수신하는 P 채널 MOS 트랜지스터(168)와, 외부 전원 전위 Vdd와 노드 N1의 전위 사이에 직렬로 결합되고 각각 게이트에서 내부 승압 전위 Vpp 및 신호 CLK2를 수신하는 N 채널 MOS 트랜지스터(172, 174)를 더 구비한다.

도 11은 도 10에 도시하는 출력 버퍼 회로(3000)에 포함되는 프리부스트 회로(186)의 동작을 설명하는 동작 파형도이다.

도 11을 참조하면, 시각 t1에 있어서 내부 제어 신호 HOUT가 'L'로부터 'H'로 상승하면 N 채널 MOS 트랜지스터(164)는 도통 상태로 되고 신호 CLK1은 그에 따라 시각 t2에 'H'로부터 'L'로 하강한다.

이 때, N 채널 MOS 트랜지스터(170)는 비도통 상태로 되어 노드 N1은 접지 전위 Vss로부터 단락된다.

다음에, N 채널 MOS 트랜지스터(166)가 비도통 상태로 되고, P 채널 MOS 트랜지스터(162)가 도통 상태, P 채널 MOS 트랜지스터(160)가 비도통 상태로 되기 때문에 신호 CLK2는 시각 t3에서 'L'로부터 'H'로 상승한다. 이에 따라 N 채널 MOS 트랜지스터(174)가 도통 상태로 되기 때문에 노드 N1의 전위는 상승한다.

N 채널 MOS 트랜지스터(172)는 내부 승압 전위 Vpp를 게이트에서 수신하고 외부 전원 전위 Vdd와 N 채널 MOS 트랜지스터(174)의 드레인을 결합하고 있기 때문에 노드 N1의 전위는 시각 t3에 있어서 외부 전원 전위 Vdd 부근까지 상승한다. 그러나, 그대로는 출력 트랜지스터(176)를 구동하는데 충분한 전위가 못된다.

또한 시각 t4에 있어서, 레벨 변환 회로(188), 인버터(182)가 동작한 결과로서 신호 CLK3이 'H'로부터 'L'로 하강한다. 이에 따라 P 채널 MOS 트랜지스터(168)가 도통 상태로 되어 노드 N1의 전위는 내부 승압 전위 Vpp까지 더 상승한다.

이상으로부터, 노드 N1의 전위를 상승시킬 때, 미리 N 채널 MOS 트랜지스터(172, 174)를 통해 외부 전원으로부터 노드 N1에 전류를 공급하여 일정 전위까지 노드 N1의 전위를 공급시키고, 그 후에 P 채널 MOS 트랜지스터(168)를 통해 내부 승압 전위 Vpp를 인가하는 승압 전원으로부터 노드 N1에 전류가 공급되기 때문에 내부 승압 전위 Vpp를 인가하는 승압 전원의 소비 전류를 작게 할 수 있다.

본 발명자가 실시한 회로 시뮬레이션에 의하면, 1회의 노드 N1의 상승시에 내부 승압 전위 Vpp를 인가하는 승압 전원으로부터 공급되는 전하는 본 회로의 적용에 의해 3.8pC로부터 3.0pC로 감소하여 약 21% 정도 소비 전류를 저감하는 효과가 있다는 것을 알았다. 이 효과는 모든 출력 단자에 대응하는 출력 버퍼 회로에 있어서 기대할 수 있는 것이기 때문에, 반도체 기억 장치 전체에서는 승압 전위 Vpp를 발생하는 회로의 저소비 전류화에 큰 효과를 갖고, 내부 승압 전위 Vpp를 발생하는 차지 펌프 회로의 소형화에 공헌할 수 있다.

또한, 프리부스트 회로(186)는 N 채널 MOS 트랜지스터(172)의 동작에 의해서 만일, 승압 전위 Vpp가 외부 전원 전위 Vdd보다 낮게 된 경우는 그에 따라 외부 전원으로부터 노드 N1로 공급되는 전류가 제한되기 때문에 실시예 2의 반도체 기억 장치는 신뢰성이 높은 것으로 된다.

### (실시예 3)

도 12는 실시예 3의 반도체 기억 장치에 이용되는 출력 버퍼 회로(4000)의 기본 구성을 나타내는 회로도이다.

실시예 3의 반도체 기억 장치의 전체 구성은 실시예 1에 있어서의 반도체 기억 장치의 전체 구성과 마찬가지로서, 출력 버퍼 회로(4000)는 도 1에 있어서의 데이터 출력 버퍼(1042)의 1 비트분으로 마련되고, 입력 신호로서 클럭 발생 회로(1022)로부터의 제어 신호나 입출력 제어 회로(1038)로부터의 판독 데이터를 바탕으로 생성된 서로 상보인 제 1 내부 신호 HOUT과 제 2 내부 신호 LOUT를 수신하는 점은 실시예 1의 경우와 동일하다.

도 12의 출력 버퍼 회로(4000)는 도 3의 실시예 1의 출력 버퍼 회로와는 출력 트랜지스터인 N 채널 MOS 트랜지스터(18)의 게이트 전압을 인가하고 있는 인버터(26) 대신에 실시예 2에 있어서의 프리부스트 회로(186)를 마련한 구성으로 되어 있는 점에서 실시예 1의 경우와 상이하다.

도 12를 참조하면, 출력 버퍼 회로(4000)는 출력 단자 DQr과, 외부 전원 전위 Vdd와 출력 단자 DQr 사이에 결합되는 N 채널 MOS 트랜지스터(18)와, 접지 전위 Vss와 출력 단자 DQr 사이에 결합되어 게이트에서 제 2 내부 제어 신호 LOUT를 수신하는 N 채널 MOS 트랜지스터(20)와, 제 1 내부 제어 신호 HOUT를 수신하여 N 채널 MOS 트랜지스터(18)의 게이트를 구동하는 신호 VG를 출력하는 구동 회로(36)와, 제 1 내부 제어 신호 HOUT를 수신하여 N 채널 MOS 트랜지스터(18)의 기판부를 구동하는 신호 VB를 출력하는 기판 전위 구동 회로(38)를 구비한다.

구동 회로(36)는 제 1 내부 제어 신호 HOUT의 'H' 레벨을 내부 강압 전위 Vcc로부터 내부 승압 전위 Vpp로 하는 레벨 변환 회로(34)와, 레벨 변환 회로(34)의 출력을 수신하는 인버터(24)와, 인버터(24)의 출력을 수신하여 N 채널 MOS 트랜지스터(18)의 게이트를 구동하는 프리부스트 회로(186)를 포함한다.

레벨 변환 회로(34)와 기판 전위 구동 회로(38)의 구성은 실시예 1과 마찬가지이기 때문에 설명은 반복하지 않는다.

이 구성으로 하면, 실시예 1과 실시예 2의 쌍방 효과를 동시에 받을 수 있기 때문에, 기판 바이어스 효과를 작게 할 수 있고, 내부 승압 전위 Vpp를 높게 하는 것을 억제하면서, 출력 단자로부터 충분한 전류를 공급할 수 있음과 동시에, 내부 승압 전위 Vpp를 발생하는 차지 펌프 회로에서 소비되는 전류를 저감할 수 있다.

### (실시예 4)

도 13은 실시예 4의 반도체 기억 장치에 이용되는 출력 버퍼 회로(5000)의 기본 구성을 나타내는 회로도이다.

실시예 4의 반도체 기억 장치의 전체 구성은 실시예 1에 있어서의 반도체 기억 장치의 전체 구성과 마찬가지이고, 출력 버퍼 회로(5000)는 도 1에 있어서의 데이터 출력 버퍼(1042)의 1 비트분으로 마련되고, 입력 신호로서 클럭 발생 회로(1022)로부터의 제어 신호나 임출력 제어 회로(1038)로부터의 판독 데이터를 바탕으로 생성된 서로 상보인 제 1 내부 신호 HOUT과 제 2 내부 신호 LOUT를 수신하는 점은 실시예 1의 경우와 동일하다.

도 13의 출력 버퍼 회로(5000)는 도 3의 실시예 1의 출력 버퍼 회로에 있어서, 출력 트랜지스터인 N 채널 MOS 트랜지스터(18)의 게이트 전압을 인가하고 있는 인버터(26) 대신에, 프리부스트 회로(187)를 마련한 구성으로 되어 있다. 그리고 또한, 출력 버퍼 회로(5000)에서는, 프리부스트 회로(187)는 기판 전위 구동 회로(38) 중에 포함되는 레벨 변환 회로(40)의 출력 신호를 사용하는 구성으로 되어 있다. 이러한 구성으로 함으로써 실시예 3에 이용되는 출력 버퍼 회로(4000)에 비해 소자의 수(a number of element)를 저감하고 있다.

도 13을 참조하면, 출력 버퍼 회로(5000)는 출력 단자 DQr과, 외부 전원 전위 Vdd와 출력 단자 DQr 사이에 결합되는 N 채널 MOS 트랜지스터(18)와, 접지 전위 Vss와 출력 단자 DQr 사이에 결합되어 게이트에서 제 2 내부 제어 신호 LOUT를 수신하는 N 채널 MOS 트랜지스터(20)와, 제 1 내부 제어 신호 HOUT를 수신하여 N 채널 MOS 트랜지스터(18)의 게이트의 전위를 구동하는 구동 회로(36)와, 제 1 내부 제어 신호 HOUT를 수신하여 N 채널 MOS 트랜지스터(18)의 기판부의 전위를 구동하는 기판 전위 구동 회로(38)를 포함한다.

기판 전위 구동 회로(38)는 제 1 내부 제어 신호 HOUT의 'H' 레벨을 내부 강압 전위 Vcc로부터 외부 전원 전위 Vdd로 하는 레벨 변환 회로(40)와, 레벨 변환 회로(40)의 출력을 수신하는 직렬로 접속되는 인버터(30, 32)를 포함한다. 구동 회로(34)는 제 1 내부 제어 신호 HOUT의 'H' 레벨을 내부 강압 전위 Vcc로부터 내부 승압 전위 Vpp로 하는 레벨 변환 회로(34)와, 레벨 변환 회로(34)의 출력을 수신하는 인버터(24)와, 인버터(24)의 출력을 받음과 동시에 레벨 변환 회로(40)의 출력을 수신하여 N 채널 MOS 트랜지스터(18)의 게이트를 구동하는 프리부스트 회로(187)를 포함한다.

즉, 제 1 내부 제어 신호 HOUT과 동상인 레벨 변환 회로(40)의 출력 신호 CLK2를, 기판 구동 회로(38) 중의 인버터(30)가 수신함과 동시에, 프리부스트 회로(187) 중의 N 채널 MOS 트랜지스터(174)가 게이트에서 수신한다. 또한, 제 1 내부 제어 신호 HOUT과 역상의 레벨 변환 회로(40)의 출력 신호 CLK1을 프리부스트 회로(187) 중의 N 채널 MOS 트랜지스터(170)가 게이트에서 수신하는 구성으로 되어 있다.

레벨 변환 회로(34, 40)와, 기판 전위 구동 회로(38)의 개별적인 구성은 실시예 1과 마찬가지이고, 또한, 프리부스트 회로(187)에 포함되는 MOS 트랜지스터(168~174)의 구성은 실시예 2에 있어서의 프리부스트 회로(186)와 마찬가지이기 때문에 설명은 반복하지 않는다.

도 13의 구성으로 하면, 실시예 1과 실시예 2의 쌍방 효과를 동시에 얻을 수 있기 때문에, 기판 바이어스 효과를 작게 할 수 있어 내부 승압 전위 Vpp를 높게 하는 것을 억제하면서 충분한 전류를 공급할 수 있음과 동시에 내부 승압 전위 Vpp를 발생하는 차지 펌프 회로에서 소비되는 전류를 저감할 수 있다.

또한, 실시예 3에 비해 소자 수를 저감하고 있기 때문에 반도체 기억 장치의 칩 사이즈를 보다 작게 할 수 있다.

### 발명의 효과

본 발명의 주된 효과는 출력 버퍼 회로의 출력 트랜지스터가 전류를 공급할 때에, 출력 트랜지스터의 기판부의 전위를 적절하게 제어함으로써 출력 트랜지스터의 임계값 전압의 증가를 억제하여 출력 트랜지스터의 출력 전류를 보다 크게 할 수 있다.

본 발명의 다른 효과는 출력 단자로부터 'H' 레벨을 출력할 때에 출력 트랜지스터의 게이트를 구동하는 전류를 내부 승압 전위 Vpp 발생 회로와 함께 외부 전원으로부터도 공급한다. 그 때문에 내부 승압 전위 Vpp 발생 회로에서의 소비 전류를 작게 할 수 있고 내부 승압을 행하는 차지 범프 회로가 소형화될 수 있어, 반도체 기억 장치의 칩 면적을 작게 할 수 있다.

이상 본 발명자에 의해서 이루어진 발명을 상기 실시예에 따라 구체적으로 설명하였지만, 본 발명은 상기 실시예에 한정되는 것이 아니고, 그 요지를 이탈하지 않는 범위에서 여러 가지로 변경 가능한 것은 물론이다.

### (57) 청구의 범위

#### 청구항 1

반도체 기판상에 형성되는 반도체 기억 장치에 있어서,

출력 단자와,

외부 전원으로부터 상기 출력 단자에 전류를 공급하는 제 1 MOS 트랜지스터와,

제 1 내부 제어 신호의 활성화에 따라, 상기 제 1 MOS 트랜지스터를 도통 상태로 하기 위해, 상기 제 1 MOS 트랜지스터의 게이트 전위를 구동하는 제 1 구동 수단과,

상기 제 1 내부 제어 신호가 비활성인 동안에는, 상기 제 1 MOS 트랜지스터의 기판부의 전위를 제 1 전위 레벨로 하고, 상기 제 1 내부 제어 신호의 활성화에 따라, 상기 제 1 MOS 트랜지스터의 출력 전류를

증대시키도록 상기 기판부의 전위를 제 2 전위 레벨로 구동하는 제 2 구동 수단을 포함하는 반도체 기억 장치.

## 청구항 2

제 1 항에 있어서,

상기 제 2 구동 수단(38)은,

상기 제 1 MOS 트랜지스터(18)가 비도통시에는, 상기 제 1 MOS 트랜지스터의 기판-소스간의 전위차가 소정의 전위차가 되도록 상기 제 1 MOS 트랜지스터의 기판부의 전위를 구동하고,

상기 제 1 MOS 트랜지스터가 도통시에는, 상기 제 1 MOS 트랜지스터의 기판-소스간의 전위차가 상기 소정의 전위차보다 작아지도록 상기 제 1 MOS 트랜지스터의 기판부의 전위를 구동하는 반도체 기억 장치.

## 청구항 3

반도체 기억 장치에 있어서,

출력 단자(DQr)와,

외부 전원 전위(Vdd)보다 더 고전위인 승압 전위(Vpp)를 발생하는 승압 수단(318)과,

상기 출력 단자에, 제 1 내부 제어 신호(HOUT)에 따라 외부 전원으로부터 전류를 공급하는 제 1 MOS 트랜지스터(176)와,

상기 제 1 MOS 트랜지스터의 게이트에 상기 제 1 내부 제어 신호에 따라 전류를 공급하는 제 3 스위칭 수단(168)과,

상기 제 1 MOS 트랜지스터(176)의 게이트에 상기 제 1 내부 제어 신호에 따라 전류를 공급하는 제 4 스위칭 수단(174)과,

전류 제한 수단(172)을 포함하며,

상기 제 3 스위칭 수단은,

상기 승압 수단으로부터 전류를 공급받고,

상기 제 4 스위칭 수단은,

상기 외부 전원으로부터 상기 전류 제한 수단을 거쳐 전류 공급을 받으며,

상기 전류 제한 수단은,

상기 승압 전위(Vpp)가 소정의 전위로 승압되어 있지 않는 기간 동안에는, 상기 외부 전원으로부터 상기 제 1 MOS 트랜지스터(18)의 게이트로 흐르는 전류를 제한하는

반도체 기억 장치.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면11

도면12

## 도면 13

## 도면14

(종래기술)

## 도면15

(종래기술)

## 도면16

(종래기술)

## 도면17

(종래기술)

## 도면18