(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6500200号

(P6500200)

(45) 発行日 平成31年4月17日(2019.4.17)

(24) 登録日 平成31年3月29日(2019.3.29)

(51) Int.Cl.

H01L 27/10 (2006.01)

G11C 17/06 (2006.01)

F 1

H01L 27/10 431

G11C 17/06

請求項の数 13 (全 47 頁)

(21) 出願番号 特願2015-35858 (P2015-35858)

(22) 出願日 平成27年2月25日 (2015.2.25)

(65) 公開番号 特開2016-157873 (P2016-157873A)

(43) 公開日 平成28年9月1日 (2016.9.1)

審査請求日 平成29年12月11日 (2017.12.11)

(73) 特許権者 511229547

株式会社フローディア

東京都小平市小川東町1丁目30番9号

(74) 代理人 100137800

弁理士 吉田 正義

(74) 代理人 100148253

弁理士 今枝 弘充

(74) 代理人 100148079

弁理士 梅村 裕明

(72) 発明者 葛西 秀男

東京都小平市小川東町1丁目30番9号

株式会社フローディア内

(72) 発明者 谷口 泰弘

東京都小平市小川東町1丁目30番9号

株式会社フローディア内

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のワード線および複数のビット線の各交差箇所にアンチヒューズメモリが配置された半導体記憶装置であって、

各前記アンチヒューズメモリは、

メモリゲート絶縁膜を介してメモリゲート電極が設けられ、ウエルに形成された一方の拡散領域にビット線コンタクトを介して前記ビット線が接続されたメモリキャパシタと、

前記メモリゲート電極と前記ワード線との間に設けられ、前記ワード線からの電圧がワード線コンタクトを経由して前記メモリゲート電極に印加される一方、前記メモリゲート電極および前記ワード線へ印加される電圧値により前記メモリゲート電極から前記ワード線への電圧印加が遮断される整流素子とを備えており、

2個以上の前記アンチヒューズメモリで1個の前記ビット線コンタクトを共有していることを特徴とする半導体記憶装置。

## 【請求項 2】

1個の前記ワード線コンタクトに対して、2個以上の前記アンチヒューズメモリが接続されている

ことを特徴とする請求項1に記載の半導体記憶装置。

## 【請求項 3】

複数のワード線および複数のビット線の各交差箇所にアンチヒューズメモリが配置された半導体記憶装置であって、

10

20

各前記アンチヒューズメモリは、

メモリゲート絶縁膜を介してメモリゲート電極が設けられ、ウエルに形成された一方の拡散領域にビット線コンタクトを介して前記ビット線が接続されたメモリキャパシタと、

前記メモリゲート電極と前記ワード線との間に設けられ、前記ワード線からの電圧がワード線コンタクトを経由して前記メモリゲート電極に印加される一方、前記メモリゲート電極および前記ワード線へ印加される電圧値により前記メモリゲート電極から前記ワード線への電圧印加が遮断される整流素子とを備えており、

2個以上の前記アンチヒューズメモリで1個の前記ワード線コンタクトを共有していることを特徴とする半導体記憶装置。

**【請求項 4】**

10

互いに隣接する4個の前記アンチヒューズメモリで1個の前記ビット線コンタクトを共有するとともに、互いに隣接する4個の前記アンチヒューズメモリで1個の前記ワード線コンタクトを共有する

ことを特徴とする請求項1～3のいずれか1項に記載の半導体記憶装置。

**【請求項 5】**

1個の前記ビット線コンタクトに接続される4個の前記アンチヒューズメモリは、各々電気的に独立に制御できる前記ワード線に接続され、

1個の前記ワード線コンタクトに接続される4個の前記アンチヒューズメモリは、各々電気的に独立に制御できる前記ビット線に接続されている

ことを特徴とする請求項4に記載の半導体記憶装置。

20

**【請求項 6】**

各前記ビット線は、前記ビット線コンタクトを介して2個以上の前記アンチヒューズメモリに電圧を印加し、各前記ワード線は、前記ワード線コンタクトを介して2個以上の前記アンチヒューズメモリに電圧を印加する

ことを特徴とする請求項1～5のいずれか1項に記載の半導体記憶装置。

**【請求項 7】**

末端に配置された一方向に並ぶ各前記ワード線コンタクトには、それぞれ2個の前記アンチヒューズメモリが接続されており、

中央領域に配置された残りの前記ワード線コンタクトには、それぞれ4個の前記アンチヒューズメモリが接続されている

30

ことを特徴とする請求項1～6のいずれか1項に記載の半導体記憶装置。

**【請求項 8】**

一方向に並ぶ複数の前記アンチヒューズメモリで、1個の前記ビット線コンタクトを共有するとともに、異なる前記ビット線コンタクトに接続された隣接する2個の前記アンチヒューズメモリで、1個の前記ワード線コンタクトを共有する

ことを特徴とする請求項1～3のいずれか1項に記載の半導体記憶装置。

**【請求項 9】**

一方向に並ぶ複数の前記アンチヒューズメモリで、1個の前記ワード線コンタクトを共有するとともに、異なる前記ワード線コンタクトに接続された隣接する2個の前記アンチヒューズメモリで、1個の前記ビット線コンタクトを共有する

40

ことを特徴とする請求項1～3のいずれか1項に記載の半導体記憶装置。

**【請求項 10】**

前記アンチヒューズメモリは、

前記メモリキャパシタにデータを書き込むときには、前記ワード線に印加された電圧が前記整流素子を介して前記メモリゲート電極に印加され、該メモリゲート電極と前記ビット線との電圧差により前記メモリゲート絶縁膜が絶縁破壊し、

前記メモリキャパシタにデータを書き込まないときには、前記メモリゲート電極が前記ワード線よりも電圧が高いと、前記メモリキャパシタの前記メモリゲート電極から前記ワード線への電圧印加を遮断する

ことを特徴とする請求項1～9のいずれか1項に記載の半導体記憶装置。

50

**【請求項 1 1】**

前記アンチヒューズメモリの前記整流素子は、P型半導体領域とN型半導体領域とが接合したPN接合ダイオードの半導体接合構造からなり、前記P型半導体領域が前記ワード線コンタクトを介して前記ワード線に接続され、前記N型半導体領域が前記メモリゲート電極に接続されている。

ことを特徴とする請求項1～10のいずれか1項に記載の半導体記憶装置。

**【請求項 1 2】**

前記アンチヒューズメモリは、前記整流素子を構成する前記P型半導体領域と前記N型半導体領域とが、前記メモリゲート電極と一体形成されている

ことを特徴とする請求項11に記載の半導体記憶装置。

10

**【請求項 1 3】**

前記アンチヒューズメモリの前記整流素子は、N型MOS (Metal-Oxide-Semiconductor)トランジスタまたはP型MOSトランジスタからなり、一端のソース領域が前記メモリゲート電極に接続されるとともに、他端のドレイン領域が前記ワード線に接続され、整流素子ゲート電極が前記ワード線または前記メモリゲート電極のいずれか一方に接続されており、チャネルを非導通状態とすることで前記メモリゲート電極から前記ワード線への電圧印加を遮断する

ことを特徴とする請求項1～9のいずれか1項に記載の半導体記憶装置。

**【発明の詳細な説明】****【技術分野】**

20

**【0001】**

本発明は半導体記憶装置に関し、例えばアンチヒューズメモリが行列状に配置された半導体記憶装置に適用して好適なものである。

**【背景技術】****【0002】**

従来、絶縁膜を破壊することにより、1回限りデータの書き込みを行えるアンチヒューズメモリとしては、米国特許第6,667,902号明細書（特許文献1）に示すような構成を有したアンチヒューズメモリが知られている。この特許文献1に示すアンチヒューズメモリは、スイッチトランジスタと、メモリキャパシタとがウエル上に並んで形成された2トランジスタ構成からなる。

30

**【0003】**

実際上、トランジスタ構成でなるスイッチトランジスタには、ウエル上にスイッチゲート絶縁膜を介してスイッチゲート電極が形成されており、スイッチゲート電極にワード線が接続されるとともに、ウエル表面に形成した一方の拡散領域にピット線が接続されている。また、スイッチトランジスタと対をなすメモリキャパシタには、ウエル上にメモリゲート絶縁膜を介してメモリゲート電極が形成されており、スイッチゲート電極に接続されたワード線とは別の書き込みワード線が当該メモリゲート電極に接続されている。

**【0004】**

データ書き込み動作時、メモリキャパシタは、書き込みワード線からメモリゲート電極に印加される破壊ワード電圧と、スイッチトランジスタのピット線に印加される絶縁破壊ピット電圧との電圧差によりメモリゲート絶縁膜が絶縁破壊し、ウエルと絶縁されていたメモリゲート電極が、メモリゲート絶縁膜の絶縁破壊により、ウエルの表面、即ちメモリチャネルが形成される領域と電気的に繋がり得る。

40

**【0005】**

そして、データ読み出し動作時、読みたいピット線に接続された書き込みワード線に電圧を印加すると、メモリゲート絶縁膜が破壊している場合には、書き込みワード線に印加した電圧がメモリチャネルを介してスイッチトランジスタの他方の拡散領域に印加される。またスイッチトランジスタは、スイッチゲート電極に接続されたワード線、および拡散領域に接続されたピット線からそれぞれ印加される電圧によりオン状態となり、対となるメモリキャパシタでのメモリゲート電極と、メモリチャネルとの電気的な繋がり状態を、

50

ビット線に印加した電圧の変化を基に判断し、データの書き込み有無を判別し得る。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許第6,667,902号明細書

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、かかる構成でなる従来のアンチヒューズメモリでは、メモリキャパシタとは別に独立したスイッチトランジスタを設けていることから、当該メモリキャパシタに破壊ワード電圧を印加する制御回路とは別に、スイッチトランジスタをオンオフ動作させるためのスイッチ制御回路が必要となり、その分、小型化が図り難いという問題があつた。

【0008】

また、このようなアンチヒューズメモリが行列状に配置された半導体記憶装置では、特定のアンチヒューズメモリのメモリゲート絶縁膜を絶縁破壊させ、他のアンチヒューズメモリのメモリゲート絶縁膜を絶縁破壊させないとき、行列状に配置されたアンチヒューズメモリに対してそれぞれ最適な電圧を印加する必要があるため、各アンチヒューズメモリに対する電圧を印加するための配線を効率良くレイアウトして全体としても小型化を図る工夫も必要となる。

【0009】

そこで、本発明は以上の点を考慮してなされたもので、従来よりも小型化を図り得る半導体記憶装置を提案することを目的とする。

【課題を解決するための手段】

【0010】

かかる課題を解決するため本発明の半導体記憶装置は、複数のワード線および複数のビット線の各交差箇所にアンチヒューズメモリが配置された半導体記憶装置であつて、各前記アンチヒューズメモリは、メモリゲート絶縁膜を介してメモリゲート電極が設けられ、ウエルに形成された一方の拡散領域にビット線コンタクトを介して前記ビット線が接続されたメモリキャパシタと、前記メモリゲート電極と前記ワード線との間に設けられ、前記ワード線からの電圧がワード線コンタクトを経由して前記メモリゲート電極に印加される一方、前記メモリゲート電極および前記ワード線へ印加される電圧値により前記メモリゲート電極から前記ワード線への電圧印加が遮断される整流素子とを備えており、2個以上の前記アンチヒューズメモリで1個の前記ビット線コンタクトを共有していることを特徴とする。

【0011】

また、本発明の半導体記憶装置は、複数のワード線および複数のビット線の各交差箇所にアンチヒューズメモリが配置された半導体記憶装置であつて、各前記アンチヒューズメモリは、メモリゲート絶縁膜を介してメモリゲート電極が設けられ、ウエルに形成された一方の拡散領域にビット線コンタクトを介して前記ビット線が接続されたメモリキャパシタと、前記メモリゲート電極と前記ワード線との間に設けられ、前記ワード線からの電圧がワード線コンタクトを経由して前記メモリゲート電極に印加される一方、前記メモリゲート電極および前記ワード線へ印加される電圧値により前記メモリゲート電極から前記ワード線への電圧印加が遮断される整流素子とを備えており、2個以上の前記アンチヒューズメモリで1個の前記ワード線コンタクトを共有していることを特徴とする。

【発明の効果】

【0012】

本発明によれば、従来のような制御回路を用いずに、メモリキャパシタのメモリゲート電極およびワード線へ印加される電圧値によって整流素子によりメモリゲート電極からワード線への電圧印加を遮断するようにしたことから、従来のようなメモリキャパシタへの

10

20

30

40

50

電圧印加を選択的に行うスイッチトランジスタや、さらにスイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要になり、その分、小型化を図り得る。

**【0013】**

また、本発明によれば、1個のビット線コンタクトおよびまたは1個のワード線コンタクトを、少なくとも2個以上のアンチヒューズメモリで共有していることから、アンチヒューズメモリ毎にビット線コンタクトやワード線コンタクトを設ける場合に比べて、小型化を図り得る。

**【図面の簡単な説明】**

**【0014】**

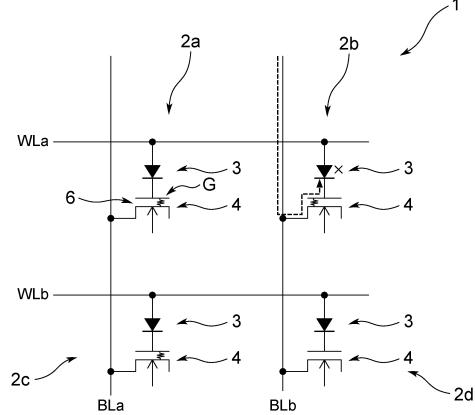

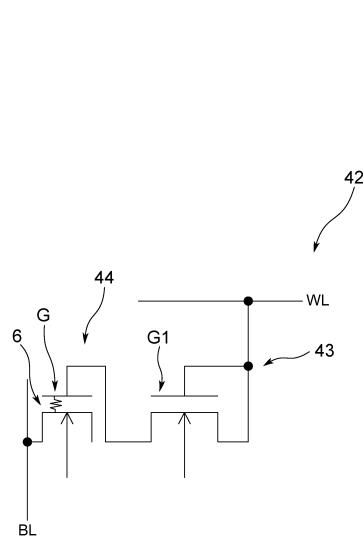

【図1】本発明の半導体記憶装置の基本的な回路構成を示す回路図である。 10

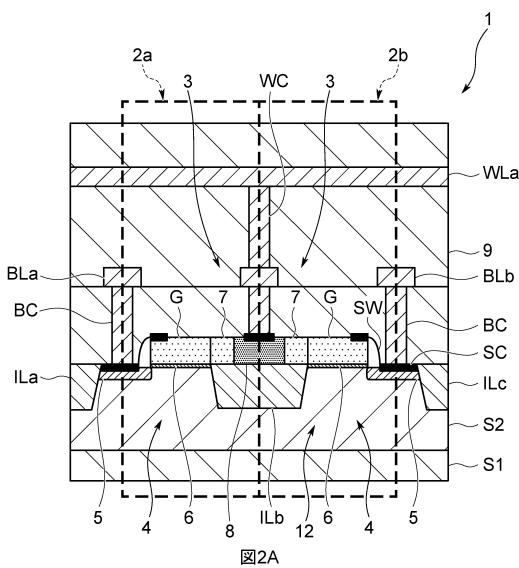

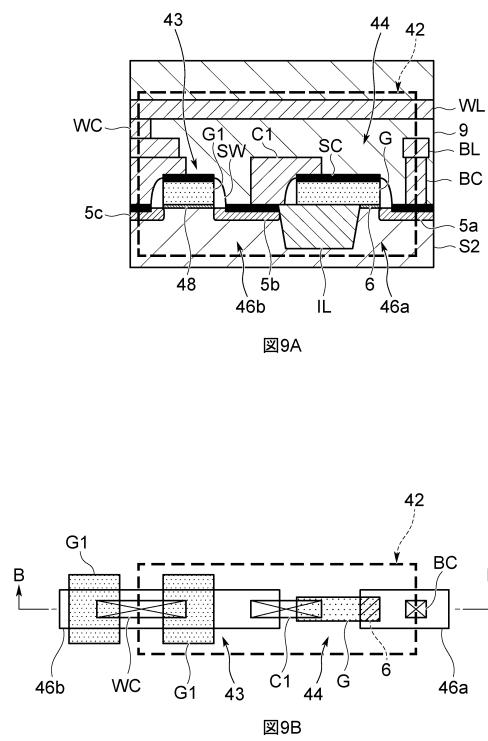

【図2】図2Aは、2個のアンチヒューズメモリが並列に配置されている箇所での断面構成を示す概略図であり、図2Bは、図2Aに示した2個のアンチヒューズメモリの平面レイアウトを示す概略図である。

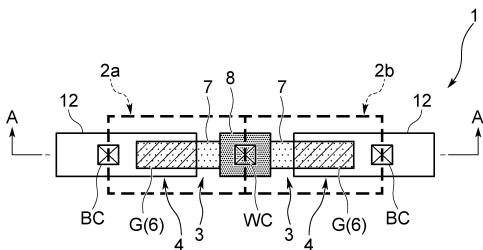

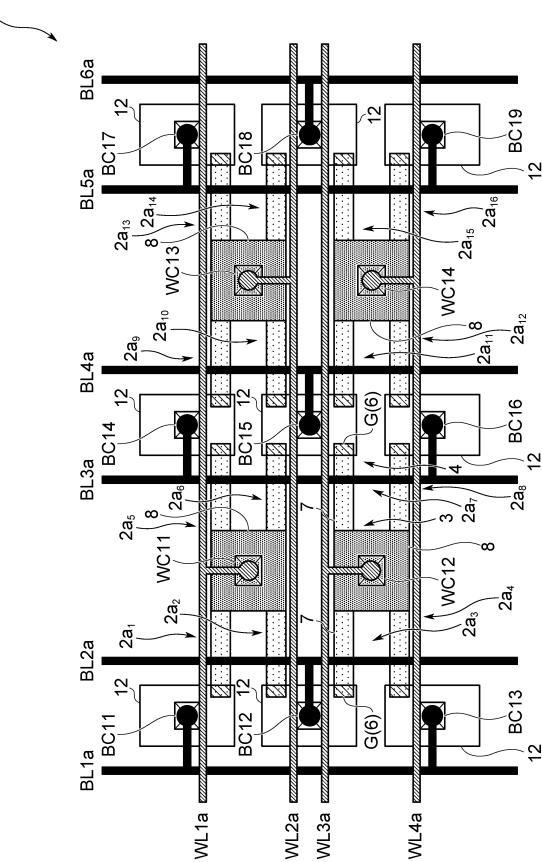

【図3】4個のアンチヒューズメモリで、1個のワード線コンタクトおよび1個のビット線コンタクトを共有するときの平面レイアウト(1)を示す概略図である。

【図4】ワード線およびビット線の平面レイアウト(1)を示す概略図である。

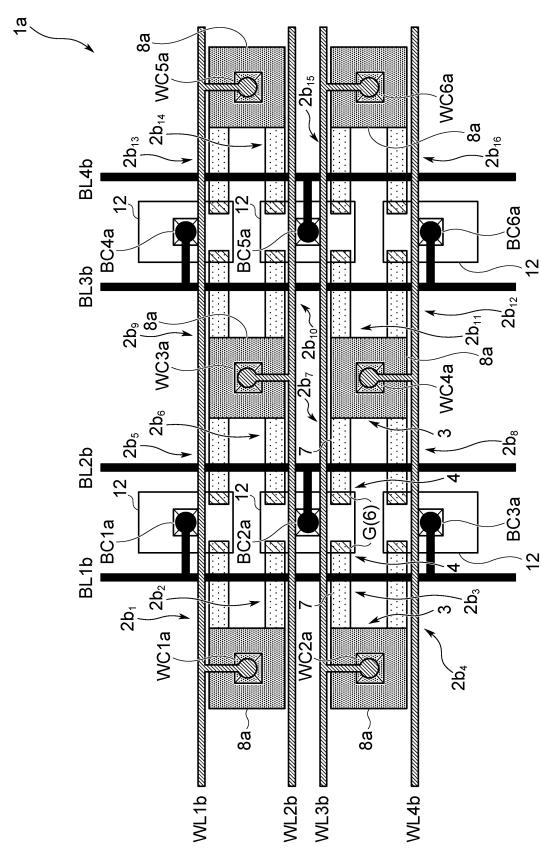

【図5】他の実施の形態によるワード線およびビット線の平面レイアウト(1)を示す概略図である。

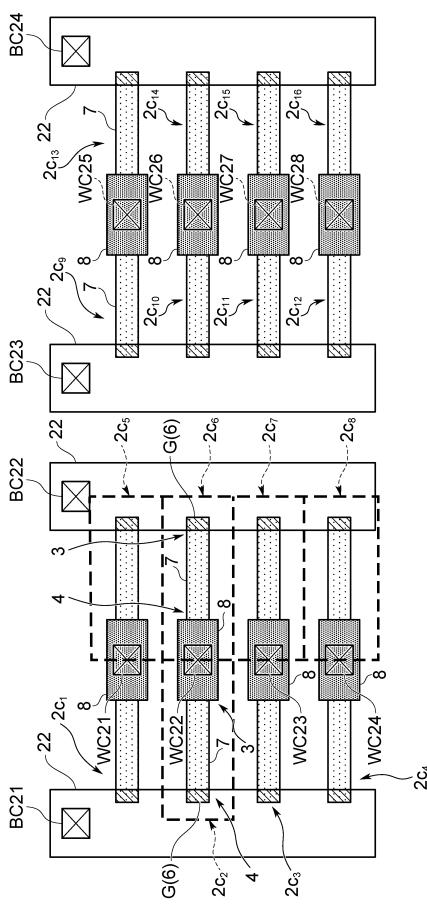

【図6】行方向に並ぶ2個のアンチヒューズメモリで1個のワード線コンタクトを共有し、列方向に並ぶ複数のアンチヒューズメモリで1個のビット線コンタクトを共有するときの平面レイアウト(1)を示す概略図である。 20

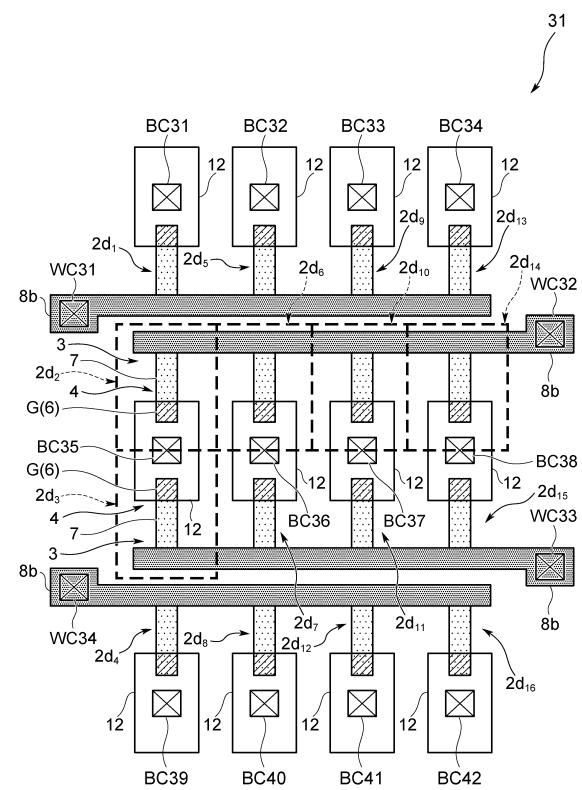

【図7】行方向に並ぶ複数のアンチヒューズメモリで1個のワード線コンタクトを共有し、列方向に並ぶ2個のアンチヒューズメモリで1個のビット線コンタクトを共有するときの平面レイアウト(1)を示す概略図である。

【図8】N型MOSトランジスタ構成の整流素子を備えた他の実施の形態によるアンチヒューズメモリの回路構成を示す回路図である。

【図9】図9Aは、図8に示したアンチヒューズメモリの断面構成を示す概略図であり、図9Bは、図9Aに示したアンチヒューズメモリの平面レイアウトを示す概略図である。

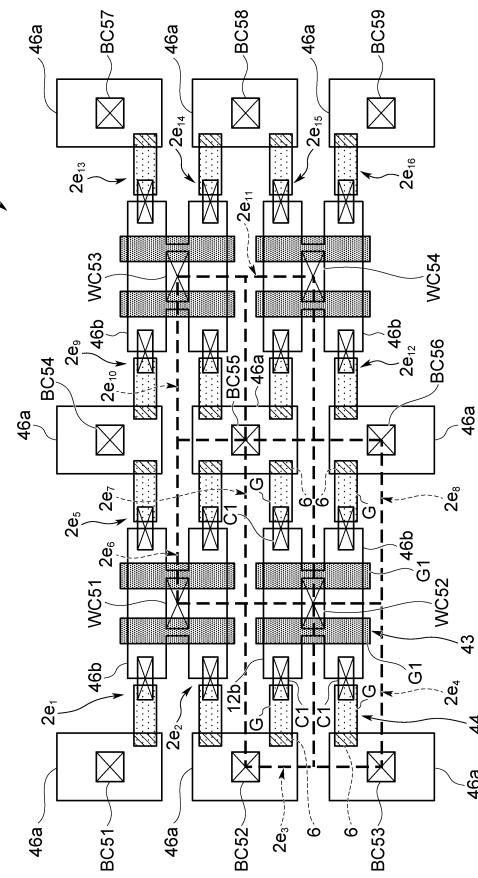

【図10】4個のアンチヒューズメモリで、1個のワード線コンタクトおよび1個のビット線コンタクトを共有するときの平面レイアウト(2)を示す概略図である。 30

【図11】ワード線およびビット線の平面レイアウト(2)を示す概略図である。

【図12】他の実施の形態によるワード線およびビット線の平面レイアウト(2)を示す概略図である。

【図13】他の実施の形態によるコンタクトの平面レイアウト(1)を示す概略図である。

【図14】行方向に並ぶ2個のアンチヒューズメモリで1個のワード線コンタクトを共有し、列方向に並ぶ複数のアンチヒューズメモリで1個のビット線コンタクトを共有するときの平面レイアウト(2)を示す概略図である。

【図15】他の実施の形態によるコンタクトの平面レイアウト(2)を示す概略図である。 40

【図16】行方向に並ぶ複数のアンチヒューズメモリで1個のワード線コンタクトを共有し、列方向に並ぶ2個のアンチヒューズメモリで1個のビット線コンタクトを共有するときの平面レイアウト(2)を示す概略図である。

【図17】P型MOSトランジスタ構成の整流素子を備えた他の実施の形態によるアンチヒューズメモリの回路構成を示した概略図である。

【図18】図18Aは、他の実施の形態のアンチヒューズメモリの断面構成を示す概略図であり、図18Bは、図18Aに示したアンチヒューズメモリの平面レイアウトを示す概略図である。

**【発明を実施するための形態】**

**【0015】**

以下図面に基づいて本発明の実施の形態を詳述する。

以下、本発明を実施するための形態について説明する。なお、説明は以下に示す順序とする。

< 1 . 行列状にアンチヒューズメモリが設けられた本発明の半導体記憶装置の基本的概念 >

1 - 1 . 基本構成

1 - 2 . データの書き込み動作

1 - 3 . データの読み出し動作

1 - 4 . 上記構成による半導体記憶装置の作用および効果

< 2 . 4個のアンチヒューズメモリで、1個のワード線コンタクトおよび1個のビット線コンタクトを共有する場合について >

2 - 1 . 平面レイアウトの構成について

2 - 2 . ビット線およびワード線の平面レイアウトの構成について

< 3 . 他の実施の形態によるビット線およびワード線の平面レイアウトの構成について >

< 4 . 2個のアンチヒューズメモリで、1個のワード線コンタクトを共有し、列方向に並んだ複数のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について >

< 5 . 行方向に並んだ複数のアンチヒューズメモリで、1個のワード線コンタクトを共有し、2個のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について >

< 6 . N型MOS ( Metal-Oxide-Semiconductor ) トランジスタからなる整流素子を有したアンチヒューズメモリ >

6 - 1 . 基本構成

6 - 2 . データの書き込み動作

6 - 3 . 上記構成による半導体記憶装置の作用および効果

< 7 . 4個のアンチヒューズメモリで、1個のワード線コンタクトおよび1個のビット線コンタクトを共有する場合について >

7 - 1 . 平面レイアウトの構成について

7 - 2 . ビット線およびワード線の平面レイアウトの構成について

< 8 . 他の実施の形態によるビット線およびワード線の平面レイアウトの構成について >

< 9 . 2個のアンチヒューズメモリで、1個のワード線コンタクトを共有し、列方向に並んだ複数のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について >

< 10 . 行方向に並んだ複数のアンチヒューズメモリで、1個のワード線コンタクトを共有し、2個のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について >

< 11 . 他の実施の形態 >

11 - 1 . P型MOSトランジスタからなる整流素子を有したアンチヒューズメモリ

11 - 2 . トランジスタ構成の整流素子を備えたアンチヒューズメモリにおける他の実施の形態による構成

11 - 3 . その他

【 0 0 1 6 】

( 1 ) 行列状にアンチヒューズメモリが設けられた本発明の半導体記憶装置の基本的概念

( 1 - 1 ) 基本構成

図 1 において、1は本発明の半導体記憶装置を示し、例えば4個のアンチヒューズメモリ2a,2b,2c,2dが行列状に配置された構成を有する。この場合、半導体記憶装置1は、行方向に並ぶアンチヒューズメモリ2a,2b ( 2c,2d ) にてワード線WLa ( WLb ) を共有しているとともに、列方向に並ぶアンチヒューズメモリ2a,2c ( 2b,2d ) にてビット線BLa ( BLb ) を共有している。各アンチヒューズメモリ2a,2b,2c,2dは、全て同一構成を有していることから、ここでは例えば1行1列目のアンチヒューズメモリ2aに着目して説明する。実際上、アンチヒューズメモリ2aは、PN接合ダイオードの半導体接合構造を有した整流素子3と、メモリゲート電極Gおよびビット線BLaの電圧差により絶縁破壊されるメモリゲート絶縁膜6を備

10

20

30

40

50

えたメモリキャパシタ4とから構成されている。

**【0017】**

この実施の形態の場合、整流素子3は、P型半導体領域とN型半導体領域とが接合された構成を有しており、P型半導体領域がワード線WLaに接続されるとともに、N型半導体領域がメモリキャパシタ4のメモリゲート電極Gに接続されている。これにより、アンチヒューズメモリ2aは、ワード線WLaから整流素子3を介してメモリキャパシタ4のメモリゲート電極Gへ電圧が印加される一方、当該メモリゲート電極Gからワード線WLaへの電圧印加が整流素子3で逆方向バイアスの電圧となり、整流素子3によってメモリゲート電極Gからワード線WLaへの電圧印加が遮断され得る。

**【0018】**

このようなアンチヒューズメモリ2a,2b,2c,2dは、データ書き込み動作時、ワード線WLa,WLbに印加された電圧が整流素子3を介してメモリキャパシタ4のメモリゲート電極Gに印加され、メモリキャパシタ4においてメモリゲート電極Gとビット線BLa,BLaとの間に大きな電圧差が生じると、メモリキャパシタ4のメモリゲート絶縁膜6が絶縁破壊し、当該メモリキャパシタ4にデータが書き込まれ得る。

**【0019】**

ここで半導体記憶装置1に設けられる本発明のアンチヒューズメモリ2a,2b,2c,2dについて詳細に説明する。なお、ここでは、図1において、例えば1行目に並んでいる2個のアンチヒューズメモリ2a,2bに着目して以下説明する。図2Aに示すように、半導体記憶装置1は、例えばSiからなるP型またはN型のウエルS2が、半導体基板S1上に形成されており、当該ウエルS2の表面に絶縁部材でなる整流素子形成層ILbが形成されている。また、ウエルS2の表面には、整流素子形成層ILbを挟むようにして、当該整流素子形成層ILbから所定間隔を設けて絶縁部材でなる素子分離層ILa,ILcが形成されている。

**【0020】**

この場合、半導体記憶装置1は、整流素子形成層ILbおよび一の素子分離層ILa間に一のアンチヒューズメモリ2aのメモリキャパシタ4が形成され、整流素子形成層ILbおよび他の素子分離層ILc間に他のアンチヒューズメモリ2bのメモリキャパシタ4が形成され得る。

**【0021】**

実際上、整流素子形成層ILbおよび一の素子分離層ILa間に、当該素子分離層ILaに隣接するようにしてウエルS2の表面に一の拡散領域5が形成されており、この拡散領域5および整流素子形成層ILb間のウエルS2上にメモリゲート絶縁膜6を介してメモリゲート電極Gが配置されたメモリキャパシタ4が形成されている。

**【0022】**

また、整流素子形成層ILbおよび他の素子分離層ILc間にも、当該素子分離層ILcに隣接するようにしてウエルS2の表面に他の拡散領域5が形成されており、この拡散領域5および整流素子形成層ILb間のウエルS2上にメモリゲート絶縁膜6を介してメモリゲート電極Gが配置されたメモリキャパシタ4が形成されている。

**【0023】**

各拡散領域5には、シリサイドSC上にビット線コンタクトBCがそれぞれ立設しており、当該ビット線コンタクトBCの先端に、対応したビット線BLa,BLbがそれぞれ接続されている。これにより例えばアンチヒューズメモリ2aのメモリキャパシタ4には、ビット線BLaからビット線コンタクトBCを介して拡散領域5に所定電圧が印加され得る。かかる構成に加えて、整流素子形成層ILbには、表面に整流素子3が形成されている。この実施の形態の場合、整流素子形成層ILbの表面には、P型半導体領域8と、当該P型半導体領域8の両側に形成されたN型半導体領域7とが設けられており、一のN型半導体領域7およびP型半導体領域8による半導体接合構造によって、PN接合ダイオードの整流素子3が形成されている。

**【0024】**

この場合、各アンチヒューズメモリ2a,2bでは、メモリキャパシタ4のメモリゲート電極GがN型半導体により形成されており、当該メモリゲート電極Gの端部と、整流素子形成層ILb上に形成された整流素子3のN型半導体領域7の端部とが一体形成されている。また、ア

10

20

30

40

50

ンチヒューズメモリ2a,2bは、これら整流素子3のN型半導体領域7およびP型半導体領域8と、メモリキャパシタ4の各メモリゲート電極Gとが同じ配線層（同層）に形成されており、整流素子3のN型半導体領域7およびP型半導体領域8と、メモリキャパシタ4のメモリゲート電極Gとが、同じ膜厚に形成されている。

#### 【 0 0 2 5 】

これにより、アンチヒューズメモリ2a,2bでは、整流素子3のN型半導体領域7、P型半導体領域8、およびメモリキャパシタ4のメモリゲート電極Gの各接合表面に段差がなく全体として薄型化が図られている。また、アンチヒューズメモリ2a,2bでは、整流素子3のN型半導体領域7、P型半導体領域8、およびメモリキャパシタ4のメモリゲート電極Gを同じ成膜工程にて形成できることから、N型半導体領域7、P型半導体領域8、およびメモリキャパシタ4のメモリゲート電極Gをそれぞれ別々に形成する場合に比して製造プロセスの簡略化を図れる。10

#### 【 0 0 2 6 】

また、整流素子3には、P型半導体領域8のシリサイドSCにワード線コンタクトWCが立設されており、ビット線BLa,BLa上方に配置されたワード線WLaが、ワード線コンタクトWCを介してP型半導体領域8に接続されている。かくして、例えばアンチヒューズメモリ2aでは、メモリゲート電極Gに対し相対的に正の電圧がワード線WLaに印加されると、当該ワード線WLaからの電圧が、ワード線コンタクトWC、整流素子3のP型半導体領域8およびN型半導体領域7を順次介して各メモリキャパシタ4のメモリゲート電極Gに印加される。一方、アンチヒューズメモリ2aでは、ワード線WLaに対し相対的に正の電圧がメモリキャパシタ4のメモリゲート電極Gに印加されると、当該メモリゲート電極Gからの電圧が、整流素子3において逆方向バイアスの電圧となり、N型半導体領域7およびP型半導体領域8間で遮断され得る。なお、ウエルS2上に形成されたビット線コンタクトBCや、ワード線コンタクトWC、整流素子3、メモリゲート電極G、ビット線BLa,BLb、ワード線WLaは層間絶縁層9により覆われている。20

#### 【 0 0 2 7 】

なお、図2Aとの対応部分に同一符号を付して示す図2Bは、図2Aに示したアンチヒューズメモリ2a,2bが設けられた領域における平面レイアウトの構成を示す。なお、図2Aは図2BのA - A'での側断面構成となる。図2Bに示すように、半導体記憶装置1は、各ビット線コンタクトBCが、ウエルS2の対応する活性領域12に配置されている。隣接するアンチヒューズメモリ2a,2bにそれぞれ設けた長方形状のN型半導体領域7は、矩形状のP型半導体領域8の中心位置に配置されたワード線コンタクトWCを中心に左右対称に配置されている。また、各N型半導体領域7は、一端がP型半導体領域8の辺に接合しており、当該P型半導体領域8から活性領域12に向けて伸びた長手方向を有し、先端部に接合されたメモリゲート電極Gが、対応する活性領域12と対向配置されている。そして、メモリゲート電極Gと活性領域12との対向領域には、それぞれアンチヒューズメモリ2a,2bのメモリゲート絶縁膜6が形成されている。30

#### 【 0 0 2 8 】

因みに、このような構成を有する半導体記憶装置1は、フォトリソグラフィ技術、酸化やCVD (Chemical Vapor Deposition) 等の成膜技術、エッチャング技術およびイオン注入法を利用した一般的な半導体製造プロセスにより形成できるため、ここではその説明は省略する。40

#### 【 0 0 2 9 】

##### ( 1 - 2 ) データの書き込み動作

次に、かかる構成を有した半導体記憶装置1において、例えば2行1列目のアンチヒューズメモリ2cにのみデータを書き込む際のデータ書き込み動作について説明する。なお、ここでは、データを書き込むアンチヒューズメモリ2cを書き込み選択メモリとも呼び、データを書き込まないアンチヒューズメモリ2a,2b,2dを書き込み非選択メモリとも呼ぶ。この場合、図1に示すように、半導体記憶装置1には、書き込み選択メモリとなるアンチヒューズメモリ2cが接続されたビット線BLa（以下、書き込み選択ビット線とも呼ぶ）に0[V]50

の破壊ビット電圧が印加され、書き込み非選択メモリとなるアンチヒューズメモリ2b,2dのみが接続されたビット線BLb（以下、書き込み非選択ビット線とも呼ぶ）に3[V]の非破壊ビット電圧が印加され得る。

#### 【0030】

また、この際、半導体記憶装置1には、書き込み選択メモリとなるアンチヒューズメモリ2cが接続されたワード線WLb（以下、書き込み選択ワード線とも呼ぶ）に5[V]の破壊ワード電圧が印加され、書き込み非選択メモリとなるアンチヒューズメモリ2a,2bのみが接続されたワード線WLa（以下、書き込み非選択ワード線とも呼ぶ）に0[V]の非破壊ワード電圧が印加され得る。アンチヒューズメモリ（書き込み選択メモリ）2cでは、書き込み選択ワード線となるワード線WLbから整流素子3のP型半導体領域8に5[V]の破壊ワード電圧が印加されるとともに、書き込み選択ビット線となるビット線BLaからメモリキャパシタ4の一端の拡散領域5に0[V]の破壊ビット電圧が印加され得る。10

#### 【0031】

これにより、アンチヒューズメモリ2cでは、整流素子3からメモリキャパシタ4のメモリゲート電極Gに破壊ワード電圧が印加されるとともに、ビット線BLaから拡散領域5に0[V]が印加され、その結果、メモリキャパシタ4のチャネル（図示せず）がオン状態となり、チャネル電位がビット線BLaの電位と同電位となる。かくして、アンチヒューズメモリ2cでは、例えば整流素子3のPN接合ダイオードのビルトインポテンシャルを0.7[V]とした場合、チャネルとメモリゲート電極Gの電位差が4.3[V]となることから、メモリゲート電極G下部のメモリゲート絶縁膜6が絶縁破壊されて、メモリゲート電極Gと拡散領域5とがチャネルを介して低抵抗で導通状態となり、データが書き込まれた状態となり得る。20

#### 【0032】

一方、5[V]の破壊ワード電圧が印加されるワード線（書き込み選択ワード線）WLbに接続されているものの、データが書き込まれない他の列のアンチヒューズメモリ2dでは、メモリキャパシタ4の一端にある拡散領域5にビット線（書き込み非選択ビット線）BLbを介して3[V]の非破壊ビット電圧が印加されることから、メモリキャパシタ4においてメモリゲート電極Gと拡散領域5との電圧差が1.3[V]（ビルトインポテンシャル0.7[V]を考慮）と小さくなる。このため、このアンチヒューズメモリ2dでは、仮にメモリキャパシタ4においてメモリゲート電極G下部のメモリゲート絶縁膜6が絶縁破壊されていないときでも、当該メモリゲート絶縁膜6が絶縁破壊されずに絶縁状態のままとなり、データが書き込まれない状態が維持され得る。30

#### 【0033】

また、3[V]の非破壊ビット電圧が印加されるビット線（書き込み非選択ビット線）BLbに接続され、データが書き込まれない他のアンチヒューズメモリ2bでは、メモリゲート絶縁膜6が絶縁破壊されていないとき、ワード線（書き込み非選択ワード線）WLaから整流素子3を介してメモリゲート電極Gに0[V]の非破壊ワード電圧が印加されることから、メモリキャパシタ4において、メモリゲート電極Gと、ビット線BLbが接続した拡散領域5との電圧差が3[V]と小さくなる。

#### 【0034】

このため、このアンチヒューズメモリ2bでは、仮にメモリキャパシタ4においてメモリゲート電極G下部のメモリゲート絶縁膜6が絶縁破壊されていないときでも、当該メモリゲート絶縁膜6が絶縁破壊されずに絶縁状態のままとなり、データが書き込まれない状態が維持され得る。40

#### 【0035】

なお、ビット線（書き込み非選択ビット線）BLbから3[V]の非破壊ビット電圧が印加されるアンチヒューズメモリ2bでは、例えばメモリキャパシタ4のメモリゲート絶縁膜6が既に絶縁破壊されている場合でも、ワード線（書き込み非選択ワード線）WLaに0[V]の非破壊ワード電圧が印加されているため、メモリキャパシタ4にチャネルが形成されず、当該ビット線BLbの3[V]の非破壊ビット電圧がメモリキャパシタ4で遮断される。これにより、このアンチヒューズメモリ2dでは、非破壊ビット電圧が、絶縁破壊されたメモリゲー50

ト絶縁膜6を介してメモリゲート電極Gへ印加されることはない。

**【0036】**

しかしながら、メモリゲート絶縁膜6の絶縁破壊された箇所が、例えばビット線（書き込み非選択ビット線）BLbが接続されている拡散領域5に極めて近い箇所であったときには、ビット線BLbの電位がメモリキャパシタ4のチャネルで遮断できず、当該拡散領域5に印加された3[V]の非破壊ビット電圧がメモリゲート電極Gに印加されてしまう虞もある。

**【0037】**

このような場合であっても、本発明のアンチヒューズメモリ2bでは、N型半導体領域7およびP型半導体領域8による半導体接合構造によってPN接合ダイオードである整流素子3が、メモリキャパシタ4のメモリゲート電極Gと、ワード線WLaとの間に設けられていることにより、メモリゲート電極Gから整流素子3に3[V]の非破壊ビット電圧が印加されても、当該整流素子3においてN型半導体領域7からP型半導体領域8への逆方向バイアスの電圧となり、当該整流素子3によってメモリゲート電極Gからワード線WLaへの電圧印加を確実に遮断し得る。

10

**【0038】**

なお、仮に、このような整流素子3による遮断機能が無い場合には、アンチヒューズメモリ2bを介してビット線BLbの3[V]の非破壊ビット電圧が、ワード線WLaに伝わってしまう。この場合、アンチヒューズメモリ2bを介してワード線WLaに印加された3[V]の電圧が、ワード線WLaを介して、当該ワード線WLaを共有する他のアンチヒューズメモリ2aのメモリゲート電極Gにまで伝わってしまう。そのため、アンチヒューズメモリ2aのメモリゲート絶縁膜6が既に破壊されていた場合には、ビット線BLaとワード線WLaとがショートして同電位になろうとし、その結果、一のビット線BLaと、他のビット線BLbとが所望の電位を保てなくなってしまい、アンチヒューズメモリに対する正常なデータ書き込み動作が行えなくなってしまうという問題が生じる。

20

**【0039】**

因みに、0[V]の非破壊ワード電圧が印加されるワード線（書き込み非選択ワード線）WLaと、同じく0[V]の非破壊ビット電圧が印加されるビット線（書き込み非選択ビット線）BLaとに接続される、データを書き込まないアンチヒューズメモリ2aでは、メモリキャパシタ4においてメモリゲート電極Gと拡散領域5との電圧差が0[V]となるため、仮にメモリゲート絶縁膜6が絶縁破壊されていないときでも、当該メモリゲート絶縁膜6が絶縁破壊されずに絶縁状態のままとなり、データが書き込まれない状態が維持され得る。かくして、半導体記憶装置1では、行列状に配置されたアンチヒューズメモリ2a,2b,2c,2dのうち、所望するアンチヒューズメモリ2cにだけデータを書き込むことができる。

30

**【0040】**

**(1-3) データの読み出し動作**

次に、図1に示す半導体記憶装置1において、例えば2行1列目のアンチヒューズメモリ2cのデータを読み出す場合について説明する。この場合、読み出し選択メモリとなるアンチヒューズメモリ2cが接続されたビット線BLa（以下、読み出し選択ビット線とも呼ぶ）と、データを読み出さない読み出し非選択メモリとなるアンチヒューズメモリ2b,2dのみが接続されたビット線BLb（以下、読み出し非選択ビット線とも呼ぶ）は、初めに1.2[V]の電圧に充電される。この際、読み出し選択メモリたるアンチヒューズメモリ2cが接続されたワード線WLb（以下、読み出し選択ワード線とも呼ぶ）には、1.2[V]の読み出し選択ワード電圧が印加されるとともに、読み出し非選択メモリとなるアンチヒューズメモリ2a,2bのみが接続されたワード線WLa（以下、読み出し非選択ワード線とも呼ぶ）には、0[V]の読み出し非選択ワード電圧が印加される。

40

**【0041】**

その後、読み出し選択ビット線BLbには0[V]の読み出し選択ビット電圧が印加される。これにより、読み出し選択メモリたるアンチヒューズメモリ2cには、ワード線WLbから整流素子3のP型半導体領域8に1.2[V]の読み出し選択ワード電圧が印加されるとともに、ビット線BLaからメモリキャパシタ4の一端の拡散領域5に0[V]の読み出し選択ビット電圧

50

が印加され得る。

**【 0 0 4 2 】**

この際、読み出し選択メモリとなるアンチヒューズメモリ2cは、メモリキャパシタ4のメモリゲート絶縁膜6が絶縁破壊されてデータが書き込まれた状態にあるとき、ワード線WLbの1.2[V]の読み出し選択ワード電圧によって、整流素子3にてP型半導体領域8からN型半導体領域7に順方向バイアスの電圧がかかる。これにより、アンチヒューズメモリ2cでは、ワード線WLbの読み出し選択ワード電圧が、整流素子3からメモリキャパシタ4を介してビット線BLaに印加され得る。

**【 0 0 4 3 】**

その結果、ビット線BLaには、1.2[V]の読み出し選択ワード電圧がアンチヒューズメモリ(読み出し選択メモリ)2cにてビルトインポテンシャル分低下された電圧が印加され得る。これにより、ビット線BLaでは、アンチヒューズメモリ2cを介してワード線WLbと電気的に接続されることにより、0[V]の読み出し選択ビット電圧が0.5[V]となり、電圧値が変化し得る。

**【 0 0 4 4 】**

因みに、読み出し選択メモリとなるアンチヒューズメモリ2cにおいて、メモリキャパシタ4のメモリゲート絶縁膜6が絶縁破壊されておらずデータが書き込まれていないときには、メモリキャパシタ4によって、ワード線WLbとビット線BLaとの電気的な接続が遮断されることになる。これにより、ビット線BLaでは、0[V]の読み出し選択ビット電圧が変化することなく、0[V]の状態をそのまま維持し得る。

**【 0 0 4 5 】**

このように半導体記憶装置1では、ビット線(読み出し選択ビット線)BLaに印加されている読み出し選択ビット電圧が変化したか否かを検知することにより、読み出し選択メモリとなるアンチヒューズメモリ2cにデータが書き込まれているか否かを判断し得る。

**【 0 0 4 6 】**

なお、ビット線(読み出し選択ビット線)BLaに接続され、かつデータを読み出さないアンチヒューズメモリ2aでは、ワード線(読み出し非選択ワード線)WLaに0[V]の読み出し非選択ワード電圧が印加されていることから、仮にメモリキャパシタ4のメモリゲート絶縁膜6が絶縁破壊されても、ビット線(読み出し選択ビット線)BLaの電圧変化に寄与することはない。

**【 0 0 4 7 】**

因みに、例えばデータを読み出すアンチヒューズメモリ2cによってビット線(読み出し選択ビット線)BLaの電圧値が0.5[V]になっているとき、この読み出し選択ビット線BLaを共有する、データを読み出さない他のアンチヒューズメモリ2aにてメモリキャパシタ4のメモリゲート絶縁膜6が絶縁破壊されても、当該アンチヒューズメモリ2aでは、整流素子3に逆方向バイアスの電圧がかかることになるため、0.5[V]の読み出し選択ビット電圧が整流素子3にて遮断され、ワード線(読み出し非選択ワード線)WLaに印加されてしまうことを防止し得る。

**【 0 0 4 8 】**

また、0[V]の読み出し非選択ワード電圧が印加されたワード線(読み出し非選択ワード線)WLbと、1.2[V]の読み出し非選択ビット電圧が印加されたビット線(読み出し非選択ビット線)BLbとに接続されたアンチヒューズメモリ2bでも、仮にメモリゲート絶縁膜6が絶縁破壊されても、整流素子3にて逆方向バイアスの電圧になるため、ワード線(読み出し非選択ワード線)WLbからビット線(読み出し非選択ビット線)BLbへの電圧印加を整流素子3によって遮断し得る。

**【 0 0 4 9 】**

さらに、1.2[V]の読み出し選択ワード電圧が印加されたワード線(読み出し選択ワード線)WLbと、1.2[V]の読み出し非選択ビット電圧が印加されたビット線(読み出し非選択ビット線)BLbとに接続されたアンチヒューズメモリ2dでは、仮にメモリゲート絶縁膜6が絶縁破壊されても、ワード線(読み出し選択ワード線)WLbおよびビット線(読み

10

20

30

40

50

み出し非選択ビット線)BL<sub>b</sub>の電圧値が同じであることから、1.2[V]の読み出し選択ワード電圧が変動することもなく、他のアンチヒューズメモリ2cの読み出し動作に影響を与えることは無い。かくして半導体記憶装置1では、行列状に配置されたアンチヒューズメモリ2a,2b,2c,2dのうち、所望するアンチヒューズメモリ2cのデータだけを読み出すことができる。

#### 【0050】

##### (1-4) 上記構成による半導体記憶装置の作用および効果

以上の構成において、例えばアンチヒューズメモリ2cでは、ウエルS2上にメモリゲート絶縁膜6を介してメモリゲート電極Gが設けられ、ウエルS2表面に形成された一方の拡散領域5にビット線コンタクトBCを介してビット線BL<sub>a</sub>が接続されたメモリキャパシタ4と、メモリゲート電極Gとワード線WL<sub>b</sub>との間に設けられ、ワード線WL<sub>b</sub>からの電圧がワード線コンタクトWCを経由してメモリゲート電極Gへ印加される一方、メモリゲート電極Gからワード線コンタクトWCへの電圧印加が逆方向バイアスの電圧となり、メモリゲート電極Gからワード線コンタクトWCへの電圧印加を遮断する整流素子3とを設けるようにした。10

#### 【0051】

また、アンチヒューズメモリ2cでは、メモリキャパシタ4にデータを書き込むとき、書き込み選択ワード線WL<sub>a</sub>に印加された書き込み破壊ワード電圧が、整流素子3を介してメモリキャパシタ4のメモリゲート電極Gに印加され、当該メモリゲート電極Gと書き込み選択ビット線BL<sub>a</sub>との電圧差により、メモリキャパシタ4のメモリゲート絶縁膜6が絶縁破壊するようにした。20

#### 【0052】

一方、データを書き込まないデータ非書き込み動作のアンチヒューズメモリ2bでは、メモリキャパシタ4に接続されたビット線BL<sub>b</sub>に高電圧の非破壊ビット電圧が印加された際に、例えばメモリキャパシタ4のメモリゲート絶縁膜6が絶縁破壊されていても、書き込み非選択ワード線WL<sub>b</sub>に0[V]の非破壊ワード電圧が印加されているため、メモリキャパシタ4にチャネルが形成されず、書き込み非選択ビット線BL<sub>b</sub>からワード線WL<sub>a</sub>への電圧印加をメモリキャパシタ4で遮断できる。

#### 【0053】

この際、本発明のアンチヒューズメモリ2bでは、例えば書き込み非選択ビット線BL<sub>b</sub>が接続されている拡散領域5に極めて近い箇所でメモリゲート絶縁膜6の絶縁破壊が生じ、仮に書き込み非選択ビット線BL<sub>b</sub>の電位がメモリキャパシタ4のチャネルで遮断できず、書き込み非選択ビット線BL<sub>b</sub>からメモリキャパシタ4のメモリゲート電極Gに非破壊ビット電圧が印加されてしまっても、当該非破壊ビット電圧が整流素子3で逆方向バイアスの電圧となるため、当該整流素子3によってメモリゲート電極Gからワード線WL<sub>a</sub>への電圧印加を確実に遮断できる。30

#### 【0054】

このように本発明のアンチヒューズメモリ2bでは、(i)書き込み非選択ワード線WL<sub>b</sub>に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ4にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子3を逆方向バイアス状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。40

#### 【0055】

従って、アンチヒューズメモリ2bでは、従来のような制御回路を用いずに、メモリゲート電極Gおよびワード線WL<sub>a</sub>へ印加される電圧値によって、メモリゲート電極Gからワード線WL<sub>a</sub>への電圧印加が逆方向バイアスの電圧となるような半導体接合構造の整流素子3を設け、当該整流素子3によってメモリゲート電極Gからワード線WL<sub>a</sub>への電圧印加を遮断するようにしたことから、従来のようなメモリキャパシタへの電圧印加を選択的に行うスイッチトランジスタや、スイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要になり、その分、小型化を図り得る。50

## 【0056】

なお、アンチヒューズメモリ $2a_1, 2b_1, 2c_1, 2d_1$ は、図2Aに示したように、整流素子3のP型半導体領域8およびN型半導体領域7が、メモリキャパシタ4のメモリゲート電極Gと同層に形成されていることから、単層構造でなるメモリキャパシタ4のメモリゲート電極Gを形成する一般的な半導体製造プロセスを利用して、メモリゲート電極Gを形成する製造工程で整流素子3のP型半導体領域8およびN型半導体領域7も形成できる。

## 【0057】

(2) 4個のアンチヒューズメモリで、1個のワード線コンタクトおよび1個のビット線コンタクトを共有する場合について

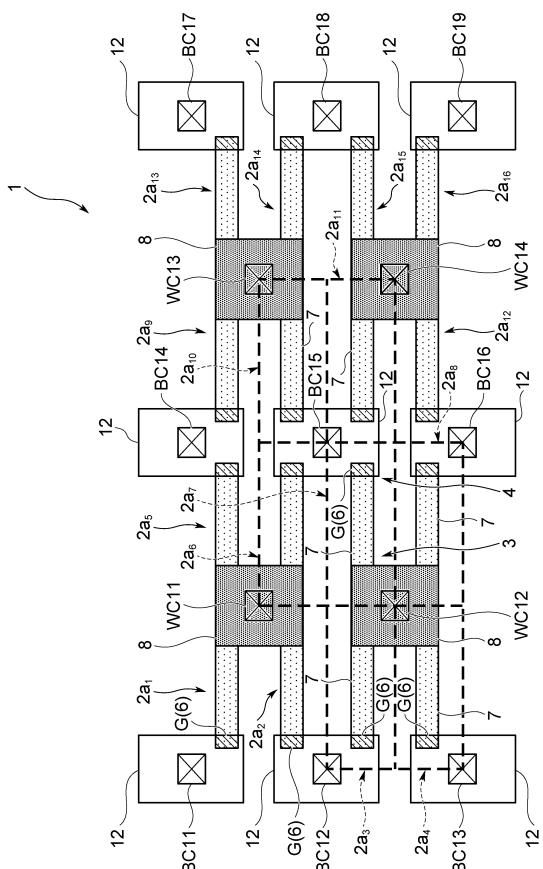

## (2-1) 平面レイアウトの構成について

次に上述したアンチヒューズメモリが行列状に配置された半導体記憶装置1の平面レイアウトの構成について説明する。図2Bとの対応部分に同一符号を付して示す図3は、例えば合計16個のアンチヒューズメモリ $2a_1, 2a_2, 2a_3, 2a_4, 2a_5, 2a_6, 2a_7, 2a_8, 2a_9, 2a_{10}, 2a_{11}, 2a_{12}, 2a_{13}, 2a_{14}, 2a_{15}, 2a_{16}$ を4行4列に配置したときの平面レイアウトの構成を示している。この場合、半導体記憶装置1において、アンチヒューズメモリ $2a_1, 2a_2, 2a_3, 2a_4, 2a_5, 2a_6, 2a_7, 2a_8, 2a_9, 2a_{10}, 2a_{11}, 2a_{12}, 2a_{13}, 2a_{14}, 2a_{15}, 2a_{16}$ は全て同一構成を有しており、上述した図2Aおよび図2Bと同様に、それぞれ整流素子3とメモリキャパシタ4とを有している。また、ワード線コンタクトWC11, WC12, WC13, WC14についても全て同一構成でなることから、ここでは、例えばワード線コンタクトWC12に着目して以下説明する。

## 【0058】

この場合、ワード線コンタクトWC12が立設するP型半導体領域8は、矩形状に形成されており、互いに隣接する4個のアンチヒューズメモリ $2a_3, 2a_4, 2a_7, 2a_8$ で共有されている。実際上、ワード線コンタクトWC12が立設したP型半導体領域8には、列方向に隣接する2個のアンチヒューズメモリ $2a_3, 2a_4$ の各N型半導体領域7が一辺に接合され、同じく列方向に隣接する2個のアンチヒューズメモリ $2a_7, 2a_8$ の各N型半導体領域7が、当該一辺と対向する他辺に接合されている。

## 【0059】

ここで、例えばアンチヒューズメモリ $2a_7$ に着目すると、P型半導体領域8とN型半導体領域7とが接合されていることで、PN接合ダイオードの整流素子3を形成している。これにより、ワード線コンタクトWC12は、P型半導体領域8を共有する4個のアンチヒューズメモリ $2a_3, 2a_4, 2a_7, 2a_8$ の各整流素子3に対して、ワード線（図示せず）からの所定のワード電圧を一律に印加し得る。

## 【0060】

なお、これら4個のアンチヒューズメモリ $2a_3, 2a_4, 2a_7, 2a_8$ の各N型半導体領域7は、P型半導体領域8から遠ざかるように行方向に向けてそれぞれ延びており、先端部に接合された各メモリゲート電極Gが、それぞれ異なる活性領域12に配置されている。また、N型半導体領域7の先端部に一体形成された各メモリゲート電極Gと、活性領域12とが対向した各領域には、各アンチヒューズメモリ $2a_3, 2a_4, 2a_7, 2a_8$ のメモリゲート絶縁膜6が形成されている。

## 【0061】

次に、ビット線コンタクトBC11, BC12, BC13, BC14, BC15, BC16, BC17, BC18, BC19について以下説明する。この実施の形態の場合、半導体記憶装置1には、合計9個のビット線コンタクトBC11, BC12, BC13, BC14, BC15, BC16, BC17, BC18, BC19が3行3列で配置されている。各ビット線コンタクトBC11, BC12, BC13, BC14, BC15, BC16, BC17, BC18, BC19は、それぞれ異なる活性領域12に配置されており、ビット線（図示せず）からの所定のビット電圧を、対応する活性領域12にそれぞれ印加し得る。

## 【0062】

ここで、これら9個のビット線コンタクトBC11, BC12, BC13, BC14, BC15, BC16, BC17, BC18, BC19のうち、中央領域に配置されたビット線コンタクトBC15が配置された活性領域12には、異なるP型半導体領域8に接続され、かつ互いに隣接する4個のアンチヒューズメモリ $2a_6$

10

20

30

40

50

, $2a_7, 2a_{10}, 2a_{11}$ が設けられている。これにより、中央領域に配置されたビット線コンタクトBC15は、互いに隣接する4個のアンチヒューズメモリ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ にて共有され、ビット線からの所定のビット電圧を、これら4個のアンチヒューズメモリ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ に対して一律に印加し得るようになされている。

#### 【 0 0 6 3 】

この場合、中央のビット線コンタクトBC15が立設した活性領域12には、当該ビット線コンタクトBC15を中心に、アンチヒューズメモリ $2a_6, 2a_7$ とアンチヒューズメモリ $2a_{10}, 2a_{11}$ とが左右対称に配置されている。具体的に、ビット線コンタクトBC15が立設した活性領域12の一辺側には、列方向に隣接する2個のアンチヒューズメモリ $2a_6, 2a_7$ の各メモリゲート電極Gが対向配置され、これらアンチヒューズメモリ $2a_6, 2a_7$ の各メモリゲート絶縁膜6が形成されている。またこの活性領域12の他辺側には、同じく列方向に隣接する他のアンチヒューズメモリ $2a_{10}, 2a_{11}$ の各メモリゲート電極Gが対向配置され、これらアンチヒューズメモリ $2a_{10}, 2a_{11}$ の各メモリゲート絶縁膜6が形成されている。10

#### 【 0 0 6 4 】

因みに、半導体記憶装置1の平面レイアウトにおいて角部に配置された4個のビット線コンタクトBC11, BC13, BC17, BC19には、それぞれ対応する1個のアンチヒューズメモリ $2a_1, 2a_4, 2a_{13}, 2a_{16}$ のみが接続されている。かくして、これら角部に配置された各ビット線コンタクトBC11, BC13, BC17, BC19では、それぞれ対応する1個のアンチヒューズメモリ $2a_1, 2a_4, 2a_{13}, 2a_{16}$ に対してだけビット電圧を印加し得る。20

#### 【 0 0 6 5 】

また、半導体記憶装置1の平面レイアウトにおいて末端に並んだビット線コンタクトBC1, BC12, BC13, BC14, BC16, BC17, BC18, BC19のうち、角部以外に配置された、例えばビット線コンタクトBC12には、2個のアンチヒューズメモリ $2a_2, 2a_3$ のみが接続されている。そして、角部以外に配置されたその他のビット線コンタクトBC14, BC16, BC18にも、それぞれ対応する2個のアンチヒューズメモリ $2a_5, 2a_9, 2a_8, 2a_{12}, 2a_{14}, 2a_{15}$ のみが接続されている。このように、半導体記憶装置1において、角部以外に配置されたその他のビット線コンタクトBC12, BC14, BC16, BC18では、共有するアンチヒューズメモリ数が2個となり、また、中央領域に配置されたビット線コンタクトBC15では、共有するアンチヒューズメモリ数が4個となるため、各ビット線コンタクト毎に1個のアンチヒューズメモリを設ける場合に比して小型化を図り得る。30

#### 【 0 0 6 6 】

以上の構成において、図3に示す半導体記憶装置1のアンチヒューズメモリ $2a_1, 2a_2, 2a_3, 2a_4, 2a_5, 2a_6, 2a_7, 2a_8, 2a_9, 2a_{10}, 2a_{11}, 2a_{12}, 2a_{13}, 2a_{14}, 2a_{15}, 2a_{16}$ では、上述した「(1-4)上記構成による半導体記憶装置の作用および効果」と同様に、従来のような制御回路を用いずに、メモリキャパシタ4のメモリゲート電極Gおよびワード線へ印加される電圧値によって整流素子3によりメモリゲート電極Gからワード線への電圧印加を遮断でき、かくして、従来のようなメモリキャパシタへの電圧印加を選択的に行うスイッチトランジスタや、さらにスイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要になり、その分、小型化を図り得る。

#### 【 0 0 6 7 】

そして、例えば、本発明の半導体記憶装置1におけるアンチヒューズメモリ $2a_7$ では、上述した「(1-4)上記構成による半導体記憶装置の作用および効果」と同様に、(i)ワード線(書き込み非選択ワード線)に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ4にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子3を逆方向バイアス状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。40

#### 【 0 0 6 8 】

また、図3に示す半導体記憶装置1では、互いに隣接する4個のアンチヒューズメモリ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ で1個のビット線コンタクトBC15を共有するとともに、例えば互いに隣接

する4個のアンチヒューズメモリ $2a_3, 2a_4, 2a_7, 2a_8$ で1個のワード線コンタクトWC12を共有するようにしたことにより、各アンチヒューズメモリ毎にビット線コンタクトおよびワード線コンタクトをそれぞれ個別に設ける場合に比して装置全体として小型化を図り得る。

#### 【 0 0 6 9 】

( 2 - 2 ) ビット線およびワード線の平面レイアウトの構成について

次に、図3に示した半導体記憶装置1におけるビット線およびワード線の平面レイアウトについて以下説明する。図3との対応部分に同一符号を付して示す図4のように、半導体記憶装置1には、1列目のビット線コンタクトBC11, BC12, BC13のうち、1行目のビット線コンタクトBC11と3行目のビット線コンタクトBC13とに対して1列目のビット線BL1aが接続されており、これらビット線コンタクトBC11, BC13間の2行目のビット線コンタクトBC12に対して他の2列目のビット線BL2aが接続されている。これにより、半導体記憶装置1は、例えば1列目のビット線BL1aによって、P型半導体領域8がそれぞれ異なる2個のアンチヒューズメモリ $2a_1, 2a_4$ に対して所定のビット電圧を一律に印加し得、さらに2列目のビット線BL2aによって、P型半導体領域8がそれぞれ異なる2個のアンチヒューズメモリ $2a_2, 2a_3$ に対して、1列目のビット線BL1aとは異なる所定のビット電圧を印加し得る。

10

#### 【 0 0 7 0 】

また、2列目のビット線コンタクトBC14, BC15, BC16では、1行目のビット線コンタクトBC14と3行目のビット線コンタクトBC16とに対して3列目のビット線BL3aが接続されており、これらビット線コンタクトBC14, BC16間の2行目のビット線コンタクトBC15に対して4列目のビット線BL4aが接続されている。これにより、半導体記憶装置1は、例えば3列目のビット線BL3aによって、P型半導体領域8がそれぞれ異なる4個のアンチヒューズメモリ $2a_5, 2a_9, 2a_8, 2a_{12}$ に対して所定のビット電圧を一律に印加し得、さらに4列目のビット線BL4aによって、P型半導体領域8がそれぞれ異なる4個のアンチヒューズメモリ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ に対して、3列目のビット線BL3aとは異なる所定のビット電圧を印加し得る。

20

#### 【 0 0 7 1 】

さらに、3列目のビット線コンタクトBC17, BC18, BC19では、1行目のビット線コンタクトBC17と3行目のビット線コンタクトBC19とに対して5列目のビット線BL5aが接続され、これらビット線コンタクトBC17, BC19間の2行目のビット線コンタクトBC18に対して6列目のビット線BL6aが接続されている。これにより、半導体記憶装置1は、例えば5列目のビット線BL5aによって、P型半導体領域8がそれぞれ異なる2個のアンチヒューズメモリ $2a_{13}, 2a_{16}$ に対して所定のビット電圧を一律に印加し得、さらに6列目のビット線BL6aによって、P型半導体領域8がそれぞれ異なる2個のアンチヒューズメモリ $2a_{14}, 2a_{15}$ に対して、5列目のビット線BL5aとは異なる所定のビット電圧を印加し得る。

30

#### 【 0 0 7 2 】

かかる構成に加えて、ワード線コンタクトWC11, WC12, WC13, WC14にはそれぞれ異なるワード線WL1a, WL2a, WL3a, WL4aが接続されており、各ワード線WL1a, WL2a, WL3a, WL4aによって、各ワード線コンタクトWC11, WC12, WC13, WC14毎に異なるワード電圧を印加し得る。この実施の形態の場合、例えば1行目のワード線WL1aは、1行1列目のワード線コンタクトWC11に接続されており、当該ワード線コンタクトWC11を共有する4個のアンチヒューズメモリ $2a_1, 2a_2, 2a_5, 2a_6$ に所定のワード電圧を一律に印加し得る。また、他のワード線WL2a, WL3a, WL4aも同様に、対応したワード線コンタクトWC13, WC12, WC14を介してそれぞれ4個のアンチヒューズメモリ $2a_9, 2a_{10}, 2a_{13}, 2a_{14}, 2a_3, 2a_4, 2a_7, 2a_8, 2a_{11}, 2a_{12}, 2a_{15}, 2a_{16}$ に対して所定のワード電圧を一律に印加し得る。

40

#### 【 0 0 7 3 】

ここで、例えば1個のビット線コンタクトBC15に接続された4個のアンチヒューズメモリ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ に着目すると、当該ビット線コンタクトBC15に接続された4個のアンチヒューズメモリ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ には、各々電気的に独立に制御できるワード線WL1a, WL2a, WL3a, WL4aが接続されており、各ワード線WL1a, WL2a, WL3a, WL4aによりそれぞれ異なるワード電圧を印加し得る。また、例えば1個のワード線コンタクトWC12に接続された4個のアンチヒューズメモリ $2a_3, 2a_4, 2a_7, 2a_8$ に着目すると、当該ワード線コンタクトWC12に接

50

続された4個のアンチヒューズメモリ $2a_3, 2a_4, 2a_7, 2a_8$ には、各々電気的に独立に制御できるビット線BL1a, BL2a, BL3a, BL4aが接続されており、各ビット線BL1a, BL2a, BL3a, BL4aによりそれぞれ異なるビット電圧を印加し得る。

#### 【0074】

そして、このような半導体記憶装置1では、ビット線BL1a, BL2a, BL3a, BL4a, BL5a, BL6aおよびワード線WL1a, WL2a, WL3a, WL4aに印加する電圧を適宜調整することにより、上述した「(1-2)データの書き込み動作」により、例えば所定位置のアンチヒューズメモリ $2a_1$ にのみデータを書き込むことができるとともに、上述した「(1-3)データの読み出し動作」により、例えば所定位置のアンチヒューズメモリ $2a_1$ におけるデータを読み出すことができる。

10

#### 【0075】

因みに、図4における半導体記憶装置1では、アンチヒューズメモリ数が16個であるため、例えばワード線WL1aが1つのワード線コンタクトWC11にだけ接続された構成となっている。しかしながら、アンチヒューズメモリ数をさらに増やした場合には、例えば1列目のワード線WL1aと2列目のワード線WL2aとが、行方向に並ぶ複数のワード線コンタクトに対して順次交互に接続された構成となる。例えば1行1列目のワード線コンタクトWC11に接続されている一のワード線WL1aは、1行3列目のワード線コンタクトや、1行5列目のワード線コンタクト等にも接続され、一方、1行2列目のワード線コンタクトWC13に接続されている他のワード線WL2aは、1行4列目のワード線コンタクトや、1行6列目のワード線コンタクト等にも接続された構成となる。

20

#### 【0076】

(3)他の実施の形態によるビット線およびワード線の平面レイアウトの構成について

図4では、一例として、合計16個のアンチヒューズメモリ $2a_1, 2a_2, 2a_3, 2a_4, 2a_5, 2a_6, 2a_7, 2a_8, 2a_9, 2a_{10}, 2a_{11}, 2a_{12}, 2a_{13}, 2a_{14}, 2a_{15}, 2a_{16}$ を4行4列に配置し、これらアンチヒューズメモリ $2a_1, 2a_2, 2a_3, 2a_4, 2a_5, 2a_6, 2a_7, 2a_8, 2a_9, 2a_{10}, 2a_{11}, 2a_{12}, 2a_{13}, 2a_{14}, 2a_{15}, 2a_{16}$ の配置位置に合わせてビット線BL1a, BL2a, BL3a, BL4a, BL5a, BL6aおよびワード線WL1a, WL2a, WL3a, WL4aを配置させた半導体記憶装置1について示した。

20

#### 【0077】

ここで、図4に示す半導体記憶装置1では、ビット線コンタクトBC11, BC12, BC13の列を一端側に設け、ビット線コンタクトBC17, BC18, BC19の列を他端側に設けている。この場合、一端側にある1行1列目のビット線コンタクトBC11と、同じく一端側にある3行1列目のビット線コンタクトBC13とには、それぞれ1個のアンチヒューズメモリ $2a_1$  ( $2a_4$ ) のみが接続された構成となり、また、同じく一端側にある2行1列目のビット線コンタクトBC12には、2個のアンチヒューズメモリ $2a_2, 2a_3$ が接続された構成となる。

30

#### 【0078】

従って、一端側のビット線コンタクトBC11, BC13に接続される1列目のビット線BL1aは、各ビット線コンタクトBC11, BC13を介して合計2個のアンチヒューズメモリ $2a_1, 2a_4$ のみが接続されることになる。また、同じく一端側のビット線コンタクトBC12に接続される2列目のビット線BL2aも、ビット線コンタクトBC12を介して2個のアンチヒューズメモリ $2a_2, 2a_3$ のみが接続されることになる。

40

#### 【0079】

そして、同様に他端側にあるビット線コンタクトBC17, BC18, BC19の列でも、ビット線コンタクトBC17 (BC19) に1個のアンチヒューズメモリ $2a_{13}$  ( $2a_{16}$ ) が接続され、残りのビット線コンタクトBC18に2個のアンチヒューズメモリ $2a_{14}, 2a_{15}$ が接続された構成となる。そのため、他端側のビット線コンタクトBC17, BC19に接続される5列目のビット線BL5aにも、各ビット線コンタクトBC17, BC19を介して合計2個のアンチヒューズメモリ $2a_{13}, 2a_{16}$ のみが接続されることになり、同じく他端側のビット線コンタクトBC18に接続される6列目のビット線BL6aにも、ビット線コンタクトBC18を介して2個のアンチヒューズメモリ $2a_{14}, 2a_{15}$ のみが接続されることになる。かくして、末端に配置されたビット線コンタクトBC11, BC12, BC13 (BC17, BC18, BC19) の列に対して設けたビット線BL1a, BL2a (BL5a, BL6a) では

50

、接続されるアンチヒューズメモリ数が2個となる。

#### 【0080】

その一方で、中央領域に配置されたビット線BL3aには、ビット線コンタクトBC14,BC16を介して合計4個のアンチヒューズメモリ $2a_5, 2a_9, 2a_8, 2a_{12}$ が接続され、同じく中央領域に配置されたビット線BL4aには、ビット線コンタクトBC15を介して4個のアンチヒューズメモリ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ が接続されている。そのため、図4に示した半導体記憶装置1において、行アドレスと列アドレスとによる制御を効率良く行うためには、例えば1列目のビット線BL1aと5列目のビット線BL5aとをショートさせて同じビット電圧で動作するアンチヒューズメモリ数を4個とし、さらに2列目のビット線BL2aと6列目のビット線BL6aもショートさせて同じビット電圧で動作するアンチヒューズメモリ数を4個として、中央領域のビット線BL3a,BL4aに接続されるアンチヒューズメモリ数（この場合、4個）に合わせることが望ましい。

10

#### 【0081】

すなわち、半導体記憶装置1では、1列目のビット線BL1aに各ビット線コンタクトBC11,B C13を介してそれぞれ接続された合計2個のアンチヒューズメモリ $2a_1, 2a_4$ と、5列目のビット線BL5aにビット線コンタクトBC17,BC19を介してそれぞれ接続された合計2個のアンチヒューズメモリ $2a_{13}, 2a_{16}$ とを合わせた合計4個のアンチヒューズメモリ $2a_1, 2a_4, 2a_{13}, 2a_{16}$ を、1列目のビット線BL1aと5列目のビット線BL5aとの2本で動作させることが望ましい。

#### 【0082】

同様にして2列目のビット線BL2aにビット線コンタクトBC12を介して接続された2個のアンチヒューズメモリ $2a_2, 2a_3$ と、6列目のビット線BL6aにビット線コンタクトBC18を介して接続された2個のアンチヒューズメモリ $2a_{14}, 2a_{15}$ とを合わせた合計4個のアンチヒューズメモリ $2a_2, 2a_3, 2a_{14}, 2a_{15}$ も、2列目のビット線BL2aと6列目のビット線BL6aとの2本で動作させることが望ましい。

20

#### 【0083】

ここで、半導体記憶装置1では、例えば1列目のビット線BL1aと5列目のビット線BL5aとの2本でアンチヒューズメモリ $2a_1, 2a_4, 2a_{13}, 2a_{16}$ に対して一律に所定のビット電圧を印加する場合、4個のアンチヒューズメモリ $2a_5, 2a_9, 2a_8, 2a_{12}$ （ $2a_6, 2a_7, 2a_{10}, 2a_{11}$ ）を1本の構成で動作させる3列目のビット線BL3aや4列目のビット線BL4aとは容量が異なることになる。そのため、半導体記憶装置1では、データの読み出し動作時に、例えば読み出し速度の低下等の問題が生じる虞がある。

30

#### 【0084】

そこで、このような問題点を解決するために、図4との対応部分に同一符号を付して示す図5に示すように、半導体記憶装置1aでは、一端側にワード線コンタクトWC1a,WC2aの列を配置するとともに、他端側にワード線コンタクトWC5a,WC6aの列を配置し、さらに、一端側のワード線コンタクトWC1a,WC2aの列と、中央のワード線コンタクトWC3a,WC4aの列との間に一のビット線コンタクトBC1a,BC2a,BC3aの列を設け、他端側のワード線コンタクトWC5a,WC6aの列と、中央のワード線コンタクトWC3a,WC4aの列との間に他のビット線コンタクトBC4a,BC5a,BC6aの列を設けるようにした。

40

#### 【0085】

また、半導体記憶装置1aでは、一端側のワード線コンタクトWC1a,WC2aの列と、中央のワード線コンタクトWC3a,WC4aの列との間にある一のビット線コンタクトBC1a,BC2a,BC3aの列のうち、1行目のビット線コンタクトBC1aと3行目のビット線コンタクトBC3aとに1列目のビット線BL1bを接続させ、2行目のビット線コンタクトBC2aに2列目のビット線BL2bを接続させ得る。

#### 【0086】

これにより、半導体記憶装置1aでは、1行目のビット線コンタクトBC1aに接続された2個のアンチヒューズメモリ $2b_1, 2b_5$ と、3行目のビット線コンタクトBC3aに接続された2個のアンチヒューズメモリ $2b_4, 2b_8$ との合計4個のアンチヒューズメモリ $2b_1, 2b_5, 2b_4, 2b_8$ を、1列目にある1本のビット線BL1bに接続させることができ、かくして、1本の構成でなるビッ

50

ト線BL1bによって4個のアンチヒューズメモリ $2b_1, 2b_5, 2b_4, 2b_8$ を動作させることができる。

#### 【 0 0 8 7 】

また、この半導体記憶装置1aでは、2行目のビット線コンタクトBC2aに接続された4個のアンチヒューズメモリ $2b_2, 2b_3, 2b_6, 2b_7$ を、2列目にある1本のビット線BL2bに接続させることができ、かくして、1本の構成でなるビット線BLbによって4個のアンチヒューズメモリ $2b_2, 2b_3, 2b_6, 2b_7$ を動作させることができる。

#### 【 0 0 8 8 】

同様に、半導体記憶装置1aでは、他端側のワード線コンタクトWC5a, WC6aの列と、中央のワード線コンタクトWC3a, WC4aの列との間にある他のビット線コンタクトBC4a, BC5a, BC6aの列でも、1行目のビット線コンタクトBC4aと3行目のビット線コンタクトBC6aとに3列目のビット線BL3bを接続させ、2行目のビット線コンタクトBC5aに4列目のビット線BL4bを接続させ得る。

10

#### 【 0 0 8 9 】

これにより、半導体記憶装置1aでは、1行目のビット線コンタクトBC4aに接続された2個のアンチヒューズメモリ $2b_9, 2b_{13}$ と、3行目のビット線コンタクトBC6aに接続された2個のアンチヒューズメモリ $2b_{12}, 2b_{16}$ との合計4個のアンチヒューズメモリ $2b_9, 2b_{13}, 2b_{12}, 2b_{16}$ を、3列目にある1本のビット線BL3bに接続させることができ、かくして、1本の構成でなるビット線BLbによって4個のアンチヒューズメモリ $2b_9, 2b_{13}, 2b_{12}, 2b_{16}$ を動作させることができる。

20

#### 【 0 0 9 0 】

また、この半導体記憶装置1aでは、2行目のビット線コンタクトBC5aに接続された4個のアンチヒューズメモリ $2b_{10}, 2b_{11}, 2b_{14}, 2b_{15}$ を、4列目にある1本のビット線BL4bに接続させることができ、かくして、1本の構成でなるビット線BL4bによって4個のアンチヒューズメモリ $2b_{10}, 2b_{11}, 2b_{14}, 2b_{15}$ を動作させることができる。

#### 【 0 0 9 1 】

かくして、半導体記憶装置1aでは、図4に示した半導体記憶装置1とは異なり、ビット線同士の接続が不要となり、ビット線BL1b, BL2b, BL3b, BL4bを全て1本の構成とし得、全て同じ容量に設定し得ることから、データの読み出し動作時に、例えば読み出し速度の低下等の問題発生を防止し得る。

30

#### 【 0 0 9 2 】

なお、この半導体記憶装置1aにおいて、1行目のワード線コンタクトWC1a, WC3a, WC5aの行には、1列目のワード線コンタクトWC1aと3列目のワード線コンタクトWC5aと同じワード線WL1bが接続され、2列目のワード線コンタクトWC3aに当該ワード線WL1bとは異なる他のワード線WL2bが接続され得る。また、2行目のワード線コンタクトWC2a, WC4a, WC6aの行には、1列目のワード線コンタクトWC2aと3列目のワード線コンタクトWC6aと同じワード線WL3bが接続され、2列のワード線コンタクトWC4aに当該ワード線WL3bとは異なる他のワード線WL4bが接続され得る。

#### 【 0 0 9 3 】

そして、このような半導体記憶装置1aでも、例えば2行1列目のビット線コンタクトBC2aや、2行2列目のビット線コンタクトBC5aにそれぞれ4個のアンチヒューズメモリ $2b_2, 2b_3, 2b_6, 2b_7$  ( $2b_{10}, 2b_{11}, 2b_{14}, 2b_{15}$ ) が接続された構成を実現し得、上述した実施の形態と同様に小型化を図り得る。また、この半導体記憶装置1aでも、例えば1行2列目のワード線コンタクトWC3aや、2行2列目のワード線コンタクトWC4aにそれぞれ4個のアンチヒューズメモリ $2b_5, 2b_6, 2b_9, 2b_{10}$  ( $2b_7, 2b_8, 2b_{11}, 2b_{12}$ ) を接続させた構成を実現し得、上述した実施の形態と同様に小型化を図り得る。

40

#### 【 0 0 9 4 】

因みに、この場合にも、例えば中央領域にある1個のビット線コンタクトBC2aに接続された4個のアンチヒューズメモリ $2b_2, 2b_3, 2b_6, 2b_7$ に着目すると、当該ビット線コンタクトBC2aに接続された4個のアンチヒューズメモリ $2b_2, 2b_3, 2b_6, 2b_7$ には、各々電気的に独立に

50

制御できるワード線WL1b,WL2b,WL3b,WL4bが接続されており、各ワード線WL1b,WL2b,WL3b,WL4bによりそれぞれ異なるワード電圧を印加し得る。また、例えば1個のワード線コンタクトWC3aに接続された4個のアンチヒューズメモリ $2b_5, 2b_6, 2b_9, 2b_{10}$ に着目すると、当該ワード線コンタクトWC3aに接続された4個のアンチヒューズメモリ $2b_5, 2b_6, 2b_9, 2b_{10}$ には、各々電気的に独立に制御できるビット線BL1b,BL2b,BL3b,BL4bが接続されており、各ビット線BL1b,BL2b,BL3b,BL4bによりそれぞれ異なるビット電圧を印加し得る。

#### 【 0 0 9 5 】

そして、この半導体記憶装置1aでも、ビット線BL1b,BL2b,BL3b,BL4bおよびワード線WL1b,WL2b,WL3b,WL4bに印加する電圧を適宜調整することにより、上述した「(1-2)データの書き込み動作」により、例えば所定位置のアンチヒューズメモリ $2b_1$ にのみデータを書き込むことができるとともに、上述した「(1-3)データの読み出し動作」により所定位置のアンチヒューズメモリ $2b_1$ におけるデータを読み出すこともできる。10

#### 【 0 0 9 6 】

以上の構成によれば、半導体記憶装置1aでは、末端に配置された一方向（この場合、行方向）に並ぶ各ビット線コンタクトBC1a,BC4a（BC3a,BC6a）にそれぞれ2個のアンチヒューズメモリ $2b_1, 2b_5, 2b_9, 2b_{13}$ （ $2b_4, 2b_8, 2b_{12}, 2b_{16}$ ）を接続し、また、末端に配置された他方向（この場合、列方向）に並ぶ各ワード線コンタクトWC1a,WC2a（WC5a,WC6a）にも、それぞれ2個のアンチヒューズメモリ $2b_1, 2b_2, 2b_3, 2b_4$ （ $2b_{13}, 2b_{14}, 2b_{15}, 2b_{16}$ ）を接続するようにした。さらに、この半導体記憶装置1aでは、中央領域に配置された残りのビット線コンタクトBC2a（BC5a）に4個のアンチヒューズメモリ $2b_2, 2b_3, 2b_6, 2b_7$ （ $2b_{10}, 2b_{11}, 2b_{14}, 2b_{15}$ ）を接続し、また、中央領域に配置されたワード線コンタクトWC3a（WC4a）に4個のアンチヒューズメモリ $2b_5, 2b_6, 2b_9, 2b_{10}$ （ $2b_7, 2b_8, 2b_{11}, 2b_{12}$ ）を接続するようにした。20

#### 【 0 0 9 7 】

これにより、半導体記憶装置1aでは、ビット線コンタクトBC1a～BC6aおよびワード線コンタクトWC1a～WC6aを2個以上のアンチヒューズメモリで共有できる分、装置全体として小型化を実現でき、さらには、例えば1本のビット線BL1bに対して接続されるアンチヒューズメモリ数を同じ数（この場合、4個）にして全て同じ容量に設定し得、かくしてデータの読み出し動作時、読み出し速度の低下等の問題発生を防止し得る。

#### 【 0 0 9 8 】

因みに、図5に示す半導体記憶装置1aはアンチヒューズメモリ数を16個とした場合について述べたが、アンチヒューズメモリ数をさらに増やした場合には、例えば1列目のワード線WL1bと2列目のワード線WL2bとが、行方向に並ぶ複数のワード線コンタクトに対して順次交互に接続された構成となる。例えば、1行1列目のワード線コンタクトWC1aに接続されているワード線WL1bは、1行3列目のワード線コンタクトWC5aの他、1行5列目のワード線コンタクト等にも接続され、一方、1行2列目のワード線コンタクトWC3aに接続されているワード線WL2bは、1行4列目のワード線コンタクトや、1行6列目のワード線コンタクト等にも接続された構成となる。

#### 【 0 0 9 9 】

また、図5に示した半導体記憶装置1aにおいて、アンチヒューズメモリ数を16個以上に増やした場合には、ビット線コンタクトBC1a,BC4a,...（BC3a,BC6a,...）が両末端において行方向に並び、一方の末端から列方向に向けて、ビット線コンタクト行と、ワード線コンタクト行とが順次交互に配置され、さらに1行に並ぶビット線コンタクト数をn個としたとき、1行に並ぶワード線コンタクト数が（n+1）個となる。なお、アンチヒューズメモリ数が16個の半導体記憶装置1aを示した図5では、1行に並ぶビット線コンタクト数が2個となり、1行に並ぶワード線コンタクト数が3個となっている。40

#### 【 0 1 0 0 】

(4) 2個のアンチヒューズメモリで、1個のワード線コンタクトを共有し、列方向に並んだ複数のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について

図3との対応部分に同一符号をして示す図6は、例えば合計16個のアンチヒューズメ50

モリ $2c_1, 2c_2, 2c_3, 2c_4, 2c_5, 2c_6, 2c_7, 2c_8, 2c_9, 2c_{10}, 2c_{11}, 2c_{12}, 2c_{13}, 2c_{14}, 2c_{15}, 2c_{16}$ を4行4列に配置した半導体記憶装置21の平面レイアウトの構成を示している。この場合、半導体記憶装置21において、アンチヒューズメモリ $2c_1, 2c_2, 2c_3, 2c_4, 2c_5, 2c_6, 2c_7, 2c_8, 2c_9, 2c_{10}, 2c_{11}, 2c_{12}, 2c_{13}, 2c_{14}, 2c_{15}, 2c_{16}$ は全て同一構成を有しており、上述した図2Aおよび図2Bと同様に、それぞれ整流素子3とメモリキャパシタ4とを有している。また、ワード線コンタクトWC21, WC22, WC23, WC24, WC25, WC26, WC27, WC28についても全て同一構成でなることから、ここでは、例えばワード線コンタクトWC22に着目して以下説明する。

#### 【0101】

この場合、ワード線コンタクトWC22が立設するP型半導体領域8は、矩形状に形成されており、行方向に隣接する2個のアンチヒューズメモリ $2c_2, 2c_6$ で共有されている。実際上、ワード線コンタクトWC22が立設したP型半導体領域8には、アンチヒューズメモリ $2c_2$ のN型半導体領域7が一辺に接合され、当該アンチヒューズメモリ $2c_2$ と行方向に隣接する他のアンチヒューズメモリ $2c_6$ のN型半導体領域7が、当該一辺と対向する他辺に接合されている。

10

#### 【0102】

ここで、例えばアンチヒューズメモリ $2c_2$ に着目すると、P型半導体領域8とN型半導体領域7とが接合されていることで、PN接合ダイオードの整流素子3を形成している。これにより、ワード線コンタクトWC22は、P型半導体領域8を共有する2個のアンチヒューズメモリ $2c_2, 2c_6$ の各整流素子3に対して、ワード線からの所定のワード電圧を一律に印加し得る。

#### 【0103】

なお、これら2個のアンチヒューズメモリ $2c_2, 2c_6$ の各N型半導体領域7は、P型半導体領域8から遠ざかるように行方向に向けてそれぞれ延びており、先端部に接合された各メモリゲート電極Gが、それぞれ異なる活性領域22に配置されている。また、N型半導体領域7の先端部に一体形成された各メモリゲート電極Gと、活性領域22とが対向した各領域には、各アンチヒューズメモリ $2c_2, 2c_6$ のメモリゲート絶縁膜6が形成されている。

20

#### 【0104】

次に、ビット線コンタクトBC21, BC22, BC23, BC24について以下説明する。この実施の形態の場合、半導体記憶装置21には、合計4個のビット線コンタクトBC21, BC22, BC23, BC24が行方向に並んで配置されている。各ビット線コンタクトBC21, BC22, BC23, BC24は、それ異なる活性領域22に配置されており、ビット線（図示せず）からの所定のビット電圧を、対応する活性領域22にそれぞれ印加し得るようになされている。

30

#### 【0105】

この場合、半導体記憶装置21では、1列目のビット線コンタクトBC21が配置された活性領域22と、2列目のビット線コンタクトBC22が配置された活性領域22との間に、行列状に配置された8個のアンチヒューズメモリ $2c_1, 2c_2, 2c_3, 2c_4, 2c_5, 2c_6, 2c_7, 2c_8$ が形成されている。1列目のビット線コンタクトBC21が配置された活性領域22には、列方向に並ぶ4個のアンチヒューズメモリ $2c_1, 2c_2, 2c_3, 2c_4$ が形成されており、一方、2列目のビット線コンタクトBC22が配置された活性領域22には、列方向に並ぶアンチヒューズメモリ $2c_5, 2c_6, 2c_7, 2c_8$ が形成されている。

40

#### 【0106】

また、半導体記憶装置21では、2列目のビット線コンタクトBC22が配置された活性領域22と、3列目のビット線コンタクトBC23が配置された活性領域22とが並走しており、上記同様に、3列目のビット線コンタクトBC23および4列目のビット線コンタクトBC24の各活性領域22間にも、8個のアンチヒューズメモリ $2c_9, 2c_{10}, 2c_{11}, 2c_{12}, 2c_{13}, 2c_{14}, 2c_{15}, 2c_{16}$ が行列状に配置され得る。

#### 【0107】

なお、この実施の形態の場合、これら4個のビット線コンタクトBC21, BC22, BC23, BC24は、全て同一構成を有することから、ここではビット線コンタクトBC22に着目して以下説明する。この場合、ビット線コンタクトBC22が配置された活性領域22は、列方向に並んだ4個のアンチヒューズメモリ $2c_5, 2c_6, 2c_7, 2c_8$ に沿って列方向に延びた長方形状でなり、こ

50

これら列方向に並んだ4個のアンチヒューズメモリ $2c_5, 2c_6, 2c_7, 2c_8$ の各メモリゲート電極Gが設けられた構成を有する。これにより、このビット線コンタクトBC22は、それぞれ異なるワード線コンタクトWC21, WC22, WC23, WC24に接続され、かつ列方向に並んだ4個のアンチヒューズメモリ $2c_5, 2c_6, 2c_7, 2c_8$ に対し、活性領域22を介してビット線からの所定のビット電圧を一律に印加し得るようになされている。

#### 【0108】

以上の構成において、図6に示す半導体記憶装置21のアンチヒューズメモリ $2c_1, 2c_2, 2c_3, 2c_4, 2c_5, 2c_6, 2c_7, 2c_8, 2c_9, 2c_{10}, 2c_{11}, 2c_{12}, 2c_{13}, 2c_{14}, 2c_{15}, 2c_{16}$ では、上述した「(1-4)上記構成による半導体記憶装置の作用および効果」と同様に、従来のような制御回路を用いずに、メモリキャパシタ4のメモリゲート電極Gおよびワード線へ印加される電圧値によって整流素子3によりメモリゲート電極Gからワード線への電圧印加を遮断でき、かくして、従来のようなメモリキャパシタへの電圧印加を選択的に行うスイッチトランジスタや、さらにスイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要になり、その分、小型化を図り得る。10

#### 【0109】

そして、例えば、本発明の半導体記憶装置21におけるアンチヒューズメモリ $2a_6$ では、上述した「(1-4)上記構成による半導体記憶装置の作用および効果」と同様に、(i)ワード線(書き込み非選択ワード線)に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ4にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子3を逆方向バイアス状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。20

#### 【0110】

また、図6に示す半導体記憶装置21では、列方向に並んだ4個のアンチヒューズメモリ $2c_5, 2c_6, 2c_7, 2c_8$ で1個のビット線コンタクトBC22を共有するとともに、例えば行方向にて隣接する2個のアンチヒューズメモリ $2c_2, 2c_6$ で1個のワード線コンタクトWC22を共有するようにしたことにより、各アンチヒューズメモリ毎にビット線コンタクトおよびワード線コンタクトをそれぞれ個別に設ける場合に比して装置全体として小型化を図り得る。

#### 【0111】

(5) 行方向に並んだ複数のアンチヒューズメモリで、1個のワード線コンタクトを共有し、2個のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について30

図3との対応部分に同一符号を付して示す図7は、例えば合計16個のアンチヒューズメモリ $2d_1, 2d_2, 2d_3, 2d_4, 2d_5, 2d_6, 2d_7, 2d_8, 2d_9, 2d_{10}, 2d_{11}, 2d_{12}, 2d_{13}, 2d_{14}, 2d_{15}, 2d_{16}$ を4行4列に配置した半導体記憶装置31の平面レイアウトの構成を示している。この場合、半導体記憶装置31において、アンチヒューズメモリ $2d_1, 2d_2, 2d_3, 2d_4, 2d_5, 2d_6, 2d_7, 2d_8, 2d_9, 2d_{10}, 2d_{11}, 2d_{12}, 2d_{13}, 2d_{14}, 2d_{15}, 2d_{16}$ は全て同一構成を有しており、上述した図2Aおよび図2Bと同様に、それぞれ整流素子3とメモリキャパシタ4とを有している。また、ワード線コンタクトWC31, WC32, WC33, WC34についても全て同一構成でなることから、ここでは、例えばワード線コンタクトWC32に着目して以下説明する。40

#### 【0112】

この場合、ワード線コンタクトWC32は、行方向に延びた長手方向を有するP型半導体領域8bに配置されており、当該P型半導体領域8bに沿って行方向に配置された4個のアンチヒューズメモリ $2d_2, 2d_6, 2d_{10}, 2d_{14}$ で共有され得る。実際上、ワード線コンタクトWC32が立設したP型半導体領域8bには、行方向に並んだ4個のアンチヒューズメモリ $2d_2, 2d_6, 2d_{10}, 2d_{14}$ の各N型半導体領域7が一辺に接合されている。

#### 【0113】

ここで、例えばアンチヒューズメモリ $2d_2$ に着目すると、P型半導体領域8bとN型半導体領域7とが接合されていることで、PN接合ダイオードの整流素子3を形成している。これにより、ワード線コンタクトWC32は、P型半導体領域8bを共有する4個のアンチヒューズメモリ $2d_2, 2d_6, 2d_{10}, 2d_{14}$ の各整流素子3に対して、ワード線からの所定のワード電圧を一律に50

印加し得る。

**【 0 1 1 4 】**

なお、これら4個のアンチヒューズメモリ $2d_2, 2d_6, 2d_{10}, 2d_{14}$ の各N型半導体領域7は、P型半導体領域8bから遠ざかるように列方向に向けてそれぞれ延びており、先端部に接合された各メモリゲート電極Gが、それぞれ異なる活性領域12に配置されている。また、N型半導体領域7の先端部に一体形成された各メモリゲート電極Gと、活性領域12とが対向した各領域には、各アンチヒューズメモリ $2d_2, 2d_6, 2d_{10}, 2d_{14}$ のメモリゲート絶縁膜6が形成されている。

**【 0 1 1 5 】**

この場合、半導体記憶装置31では、この2行目のワード線コンタクトWC32が立設したP型半導体領域8bと、3行目のワード線コンタクトWC33が立設したP型半導体領域8bとが並走するように配置されており、これら2個のP型半導体領域8b間に、8個のアンチヒューズメモリ $2d_2, 2d_3, 2d_6, 2d_7, 2d_{10}, 2d_{11}, 2d_{14}, 2d_{15}$ が行列状に配置され得る。

**【 0 1 1 6 】**

因みに、この実施の形態の場合、半導体記憶装置31では、2行目のワード線コンタクトWC32が立設したP型半導体領域8bの他辺に対し、1行目のワード線コンタクトWC31が立設したP型半導体領域8bの一辺が並走するように隣接されている。この1行目のワード線コンタクトWC31が立設したP型半導体領域8bの他辺には、行方向に並んだ4個のアンチヒューズメモリ $2d_1, 2d_5, 2d_9, 2d_{13}$ の各N型半導体領域7が接合されている。

**【 0 1 1 7 】**

また、半導体記憶装置31では、3行目のワード線コンタクトWC33が立設したP型半導体領域8bの他辺に対し、4行目のワード線コンタクトWC34が立設したP型半導体領域8bの一辺が並走するように隣接されている。この4行目のワード線コンタクトWC34が立設したP型半導体領域8bの他辺には、行方向に並んだ4個のアンチヒューズメモリ $2d_4, 2d_8, 2d_{12}, 2d_{16}$ の各N型半導体領域7が接合されている。

**【 0 1 1 8 】**

次に、ピット線コンタクトBC31, BC32, BC33, BC34, BC35, BC36, BC37, BC38, BC39, BC40, BC41, BC42について以下説明する。この実施の形態の場合、半導体記憶装置31には、合計12のピット線コンタクトBC31, BC32, BC33, BC34, BC35, BC36, BC37, BC38, BC39, BC40, BC41, BC42が3行4列で配置されている。これらピット線コンタクトBC31, BC32, BC33, BC34, BC35, BC36, BC37, BC38, BC39, BC40, BC41, BC42は、それぞれ異なる活性領域12に配置されており、ピット線（図示せず）からの所定のピット電圧を、対応する活性領域12にそれぞれ印加し得るようになされている。

**【 0 1 1 9 】**

ここで、中央領域に配置された行方向に並ぶピット線コンタクトBC35, BC36, BC37, BC38は全て同一構成を有していることから、そのうち、例えばピット線コンタクトBC35に着目して以下説明する。この場合、ピット線コンタクトBC35が配置された活性領域12には、異なるP型半導体領域8bに接続され、かつ列方向に並ぶ2個のアンチヒューズメモリ $2d_2, 2d_3$ が設けられている。これにより、ピット線コンタクトBC35は、これら2個のアンチヒューズメモリ $2d_2, 2d_3$ にて共有され、ピット線からの所定のピット電圧を、これら2個のアンチヒューズメモリ $2d_2, 2d_3$ に対して一律に印加し得るようになされている。

**【 0 1 2 0 】**

実際上、このピット線コンタクトBC35が立設した活性領域12には、当該ピット線コンタクトBC35を中心に、アンチヒューズメモリ $2d_2$ とアンチヒューズメモリ $2d_3$ とが上下対称に配置されている。具体的に、ピット線コンタクトBC35が立設した活性領域12の一辺側には、一のアンチヒューズメモリ $2d_2$ のメモリゲート電極Gが対向配置され、当該アンチヒューズメモリ $2d_2$ のメモリゲート絶縁膜6が形成されている。また、この活性領域12の他辺側にも、同じく他のアンチヒューズメモリ $2d_3$ のメモリゲート電極Gが対向配置され、当該アンチヒューズメモリ $2d_3$ のメモリゲート絶縁膜6が形成されている。

**【 0 1 2 1 】**

10

20

30

40

50

因みに、半導体記憶装置31の平面レイアウトにおいて、末端にて行方向に配置された4個のビット線コンタクトBC31,BC32,BC33,BC34 ( BC39,BC40,BC41,BC42 ) には、それぞれ対応する1個のアンチヒューズメモリ $2d_1, 2d_5, 2d_9, 2d_{13}$  ( $2d_4, 2d_8, 2d_{12}, 2d_{16}$ ) のみが接続されている。かくして、これら末端にて行方向に配置された各ビット線コンタクトBC31,BC32,BC33,BC34 ( BC39,BC40,BC41,BC42 ) では、それぞれ対応する1個のアンチヒューズメモリ $2d_1, 2d_5, 2d_9, 2d_{13}$  ( $2d_4, 2d_8, 2d_{12}, 2d_{16}$ ) に対してだけビット電圧を印加し得る。

#### 【 0 1 2 2 】

このように、末端の各ビット線コンタクトBC31,BC32,BC33,BC34,BC39,BC40,BC41,BC42では、それぞれ1個のアンチヒューズメモリ $2d_1, 2d_5, 2d_9, 2d_{13}, 2d_4, 2d_8, 2d_{12}, 2d_{16}$ に対してだけ所定のビット電圧を印加し得ることになるものの、中央領域に配置された各ビット線コンタクトBC35,BC36,BC37,BC38では、それぞれ対応する2個のアンチヒューズメモリ $2d_2, 2d_3, 2d_6, 2d_7, 2d_{10}, 2d_{11}, 2d_{14}, 2d_{15}$ に対して所定のビット電圧を一律に印加し得ることから、2個のアンチヒューズメモリ $2d_2, 2d_3, 2d_6, 2d_7, 2d_{10}, 2d_{11}, 2d_{14}, 2d_{15}$ で1個のビット線コンタクトBC35,BC36,BC37,BC38を共有させる分だけ装置全体としては小型化を図り得る。10

#### 【 0 1 2 3 】

以上の構成において、図7に示す半導体記憶装置31のアンチヒューズメモリ $2d_1, 2d_2, 2d_3, 2d_4, 2d_5, 2d_6, 2d_7, 2d_8, 2d_9, 2d_{10}, 2d_{11}, 2d_{12}, 2d_{13}, 2d_{14}, 2d_{15}, 2d_{16}$ では、上述した「(1-4)上記構成による半導体記憶装置の作用および効果」と同様に、従来のような制御回路を用いずに、メモリキャパシタ4のメモリゲート電極Gおよびワード線へ印加される電圧値によって整流素子3によりメモリゲート電極Gからワード線への電圧印加を遮断でき、かくして、従来のようなメモリキャパシタへの電圧印加を選択的に行うスイッチトランジスタや、さらにスイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要になり、その分、小型化を図り得る。20

#### 【 0 1 2 4 】

そして、例えば、本発明の半導体記憶装置31におけるアンチヒューズメモリ $2d_2$ では、上述した「(1-4)上記構成による半導体記憶装置の作用および効果」と同様に、(i)ワード線(書き込み非選択ワード線)に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ4にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子3を逆方向バイアス状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。30

#### 【 0 1 2 5 】

また、図7に示す半導体記憶装置31では、例えば一方向(この場合、行方向)に並ぶ4個のアンチヒューズメモリ $2d_2, 2d_6, 2d_{10}, 2d_{14}$ で1個のワード線コンタクトWC32を共有するとともに、例えば互いに隣接する2個のアンチヒューズメモリ $2d_2, 2d_3$ で1個のビット線コンタクトBC35を共有するようにしたことにより、各アンチヒューズメモリ毎にビット線コンタクトおよびワード線コンタクトをそれぞれ個別に設ける場合に比して装置全体として小型化を図り得る。40

#### 【 0 1 2 6 】

(6) N型MOS(Metal-Oxide-Semiconductor)トランジスタからなる整流素子を有したアンチヒューズメモリ

##### (6-1) 基本構成

上述した実施の形態においては、整流素子として、P型半導体領域とN型半導体領域による半導体接合構造を備え、逆方向バイアスの電圧によりメモリゲート電極からの電圧を遮断するダイオード型の整流素子3を適用する場合について述べたが、本発明はこれに限らず、例えば、整流素子ゲート電極とドレイン領域とソース領域による半導体接合構造を備え、逆方向バイアスの電圧により、メモリキャパシタのメモリゲート電極からの電圧を遮断するMOSトランジスタ型の整流素子を適用してもよい。

#### 【 0 1 2 7 】

10

20

30

40

50

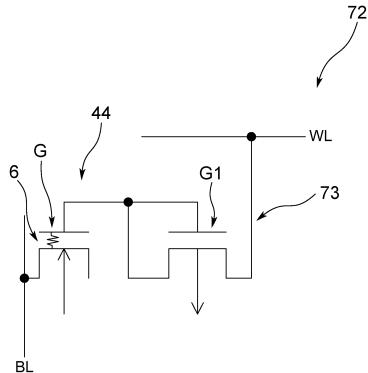

ここで、図8は、N型MOSトランジスタの半導体接合構造を有した整流素子43と、ワード線WLおよびビット線BLの電圧差により絶縁破壊されるメモリゲート絶縁膜6を備えたメモリキャパシタ44とを有するアンチヒューズメモリ42を示す。この場合、メモリキャパシタ44には、一端の拡散領域にビット線BLが接続されており、メモリゲート電極Gに整流素子43が接続されている。整流素子43は、整流素子ゲート電極G1と、ドレイン領域とがワード線WLに接続されるとともに、ソース領域がメモリキャパシタ44のメモリゲート電極Gに接続された構成を有する。これにより整流素子43は、ワード線WLからオフ電圧が印加される限り、当該整流素子43のトランジスタがオフ動作し、メモリゲート電極Gからワード線WLへの電圧印加を遮断し得るようになされている。

## 【0128】

10

実際上、図9Aに示すように、アンチヒューズメモリ42は、例えばSiからなるP型またはN型のウエルS2の表面に、絶縁部材でなる素子分離層ILが形成された構成を有する。また、ウエルS2には、素子分離層ILの一方の領域に整流素子43が形成されており、当該素子分離層ILの他方の領域にメモリキャパシタ44が形成されている。実際上、素子分離層ILの一方側のウエルS2には、当該素子分離層ILに隣接するように一方の拡散領域5bが表面に形成されており、当該拡散領域5bと所定間隔を空けて他方の拡散領域5cが表面に形成されている。

## 【0129】

20

これら拡散領域5b,5c間のウエルS2の表面には、ゲート絶縁膜48を介して整流素子ゲート電極G1が形成されており、ドレイン領域となる他方の拡散領域5cと、整流素子ゲート電極G1とに亘ってワード線コンタクトWCが立設されている。なお、この実施の形態の場合、ワード線コンタクトWCは、ドレイン領域となる他方の拡散領域5c表面のシリサイドSCから、整流素子ゲート電極G1のサイドウォールを介して、当該整流素子ゲート電極G1表面のシリサイドSCに亘って形成されており、さらに先端部にワード線WLが接続された構成を有する。これにより、ワード線コンタクトWCは、ワード線WLから印加されたワード電圧を、整流素子43のドレイン領域となる拡散領域5cと、整流素子ゲート電極G1との両方に対し印加し得る。

## 【0130】

30

また、素子分離層ILの他方側のウエルS2には、当該素子分離層ILと所定間隔を空けて拡散領域5aが表面に形成されており、先端にビット線BLが接続されたビット線コンタクトBCが、当該拡散領域5a表面のシリサイドSC上に立設されている。さらに、素子分離層ILと拡散領域5aと間の表面に、メモリゲート絶縁膜6を介してメモリゲート電極Gが形成されている。ここで、メモリゲート電極Gは、素子分離層IL上の一部領域からメモリゲート絶縁膜6上に亘って形成されており、両側壁にサイドウォールSWを有する。

## 【0131】

40

また、このアンチヒューズメモリ42では、整流素子43のソース領域となる一方の拡散領域5bから、素子分離層IL上のメモリゲート電極Gに亘って、コンタクトC1が形成されており、整流素子43の拡散領域5bと、メモリキャパシタ44のメモリゲート電極GとがコンタクトC1によって電気的に接続されている。かくして、整流素子43は、ワード線WLからオフ電圧が印加される限り、当該整流素子43のチャネルが非導通状態となり、メモリゲート電極Gからワード線WLへの電圧印加を遮断し得るようになされている。

## 【0132】

また、このようなMOSトランジスタ構成の整流素子43を備えたアンチヒューズメモリ42は、整流素子43の整流素子ゲート電極G1と、メモリキャパシタ44のメモリゲート電極Gとが同じ配線層（同層）に形成されており、さらに、整流素子ゲート電極G1の膜厚と、メモリキャパシタ44のメモリゲート電極Gとが同じ膜厚に形成されている。これにより、アンチヒューズメモリ42でも、全体として薄型化が図られている。なお、ウエルS2上に形成されたビット線コンタクトBCや、ワード線コンタクトWC、コンタクトC1、整流素子ゲート電極G1、メモリゲート電極G、ビット線BL、ワード線WLは層間絶縁層9により覆われている。

## 【0133】

50

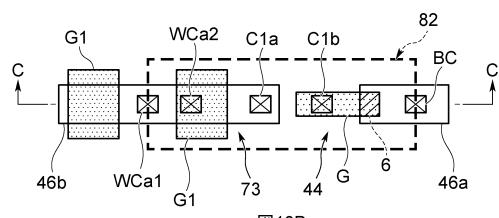

なお、図9Aとの対応部分に同一符号を付して示す図9Bは、図9Aに示したアンチヒューズメモリ42が設けられた領域における平面レイアウトの構成を示す。なお、図9Aは図9BのB-B'での側断面構成となる。図9Bに示すように、アンチヒューズメモリ42は、ビット線コンタクトBCが、ウエルS2の対応する一の活性領域46aに配置され、ワード線コンタクトWCが、ウエルの対応する他の活性領域46bに配置されている。メモリキャパシタ44は、メモリゲート電極Gの一部が一の活性領域46aと対向配置され、メモリゲート電極Gと活性領域46aとの対向領域にメモリゲート絶縁膜6が形成され得る。また、他の活性領域46aには、整流素子43の整流素子ゲート電極G1が形成されており、さらに、アンチヒューズメモリ42と隣接する他のアンチヒューズメモリ(図示せず)における整流素子43の整流素子ゲート電極G1も形成されている。

10

#### 【0134】

因みに、このような構成を有するアンチヒューズメモリ42は、フォトリソグラフィ技術、酸化やCVD(Chemical Vapor Deposition)等の成膜技術、エッチング技術およびイオン注入法を利用した一般的な半導体製造プロセスにより形成できるため、ここではその説明は省略する。

#### 【0135】

##### (6-2) データの書き込み動作

ここで、行列状に並んだアンチヒューズメモリ42のうち、所定のアンチヒューズメモリ42にだけデータを書き込む場合には、図1に示した半導体記憶装置1と同様に、データを書き込むアンチヒューズメモリ42が接続されたビット線BLには0[V]の破壊ビット電圧が印加され、データを書き込まないアンチヒューズメモリ42のみが接続されたビット線BLには3[V]の非破壊ビット電圧が印加され得る。

20

#### 【0136】

また、この際、データを書き込むアンチヒューズメモリ42が接続されたワード線WLには、5[V]の破壊ワード電圧が印加され、データが書き込まれないアンチヒューズメモリ42のみが接続されたワード線WLには、0[V]の非破壊ワード電圧が印加され得る。なお、アンチヒューズメモリ42が形成されたウエルには、破壊ビット電圧と同じ0[V]が印加され得る。

#### 【0137】

従って、例えばデータを書き込むアンチヒューズメモリ42では、例えばビット線BLに0[V]の破壊ビット電圧が印加され、ワード線WLに5[V]の破壊ワード電圧が印加され得る。この際、整流素子43は、ワード線WLから整流素子ゲート電極G1に5[V]の破壊ワード電圧が印加されているため、整流素子ゲート電極G1およびソース領域の電圧差によりオン動作し、その結果、ドレイン領域からソース領域に順方向バイアスの電圧がかかり、ドレイン領域からソース領域を介して、閾値電圧分( $V_{th}$ 分)下がった破壊ワード電圧をメモリキャパシタ44のメモリゲート電極Gに印加し得る。この際、メモリキャパシタ44は、メモリゲート電極Gの破壊ワード電圧と、ビット線BLの破壊ビット電圧との関係からオン動作しチャネルが形成されて、チャネルにビット線BLの電位が誘導され得る。

30

#### 【0138】

これによりメモリキャパシタ44には、メモリゲート電極Gとチャネルとの間に破壊ビット電圧および破壊ワード電圧による電圧差が生じ得る。かくして、データが書き込まれるアンチヒューズメモリ42では、メモリキャパシタ44においてメモリゲート電極G下部のメモリゲート絶縁膜6が絶縁破壊され、メモリゲート電極Gと拡散領域が低抵抗で導通状態となり、メモリキャパシタ44にデータが書き込まれた状態となり得る。

40

#### 【0139】

一方、ビット線BLに3[V]の非破壊ビット電圧が印加されるとともに、ワード線WLに0[V]の非破壊ワード電圧が印加される、データが書き込まれないアンチヒューズメモリ42では、例えばメモリキャパシタ44のメモリゲート絶縁膜6が既に絶縁破壊されているとき、ビット線BLの3[V]の非破壊ビット電圧がメモリキャパシタ44のメモリゲート電極Gを介して整流素子43のソース領域まで印加され得る。この際、アンチヒューズメモリ42では

50

、ワード線WLに0[V]の非破壊ワード電圧が印加されているため、整流素子43の整流素子ゲート電極G1とドレイン領域とが0[V]となり、当該整流素子43がオフ状態（非導通状態）となる（第二の遮断機構）。

#### 【0140】

また、メモリキャパシタ44のメモリゲート電極Gと、整流素子43のソース領域との間の配線の電位は、外部から供給されないため、定常状態ではウエル電位と同電位となり0[V]と考えて良い。そのため、メモリキャパシタ44に接続されたビット線BLに高電圧の非破壊ビット電圧（この場合、3[V]）が印加された際には、例えばメモリキャパシタ44のメモリゲート絶縁膜6が絶縁破壊されていても、ワード線（書き込み非選択ワード線）WLに0[V]の非破壊ワード電圧が印加されているため、メモリキャパシタ44にチャネルが形成されず、ビット線（書き込み非選択ビット線）BLからワード線WLへの電圧印加をメモリキャパシタ44でも遮断できる（第一の遮断機構）。

10

#### 【0141】

このため、このアンチヒューズメモリ42では、例えば非破壊ビット電圧（3[V]）が印加されるビット線（書き込み非選択ビット線）BLが接続されている拡散領域5aに極めて近い箇所でメモリゲート絶縁膜6の絶縁破壊が生じ、仮に書き込み非選択ビット線BLの電位がメモリキャパシタ44のチャネルで遮断できず、書き込み非選択ビット線BLからメモリキャパシタ44のメモリゲート電極Gに非破壊ビット電圧が印加されてしまっても、当該メモリゲート電極Gと接続された整流素子43がオフ状態（非導通状態）にあるため、当該整流素子43によってメモリゲート電極Gからワード線WLへの電圧印加を確実に遮断できる。このように、アンチヒューズメモリ42では、ビット線BLから印加される3[V]の非破壊ビット電圧をも、メモリキャパシタ44のチャネルオフ動作（第一の遮断機構）と、整流素子43のオフ動作（第二の遮断機構）とで遮断でき、当該非破壊ビット電圧がワード線WLに伝わることを確実に防止し得る。

20

#### 【0142】

因みに、ワード線WLから5[V]の破壊ワード電圧が印加され、かつビット線BLから3[V]の非破壊ビット電圧が印加される、データが書き込まれないアンチヒューズメモリ42では、整流素子43からメモリキャパシタ44のメモリゲート電極Gに、閾値電圧分下がった破壊ワード電圧が印加されるものの、メモリゲート電極Gとチャネルおよび拡散領域との電圧差が小さくなるため、仮にメモリキャパシタ44においてメモリゲート絶縁膜6が絶縁破壊していないときでも、当該メモリゲート絶縁膜6が絶縁破壊されずに絶縁状態のままでなり、データが書き込まれない状態が維持され得る。

30

#### 【0143】

なお、このような構成を有したアンチヒューズメモリ42が行列状に配置された半導体記憶装置でも、上述した「（1-3）データの読み出し動作」により所望のアンチヒューズメモリ42のデータを読み出すことができるため、ここではその説明は省略する。

#### 【0144】

##### （6-3）上記構成による半導体記憶装置の作用および効果

以上の構成において、データを書き込まないアンチヒューズメモリ42でも、図2において上述したアンチヒューズメモリ2a,2bと同様に、メモリキャパシタ44に接続されたビット線BLに高電圧の非破壊ビット電圧が印加された際、例えばメモリキャパシタ44のメモリゲート絶縁膜6が絶縁破壊されていても、整流素子43のチャネルをオフ状態（非導通状態）とさせることで、メモリキャパシタ44のメモリゲート電極Gからワード線WLへの非破壊ビット電圧の印加を遮断するようにした。

40

#### 【0145】

従って、アンチヒューズメモリ42でも、図2において上述したアンチヒューズメモリ2a,2bと同様に、従来のような制御回路を用いずに、メモリゲート電極Gおよびワード線WLの電圧値によって、メモリゲート電極Gからワード線WLへの電圧印加をオフ動作で遮断するトランジスタ構成の整流素子43を設けるようにしたことから、メモリキャパシタ44への各電圧印加を選択的に行うスイッチトランジスタや、スイッチトランジスタにオンオフ動作

50

を行わせるためのスイッチ制御回路が不要となり、その分、小型化を図り得る。

#### 【0146】

また、このようなアンチヒューズメモリ42でも、(i)ワード線（書き込み非選択ワード線）に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ44にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子43をオフ状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。

#### 【0147】

(7) 4個のアンチヒューズメモリで、1個のワード線コンタクトおよび1個のビット線コンタクトを共有する場合について 10

##### (7-1) 平面レイアウトの構成について

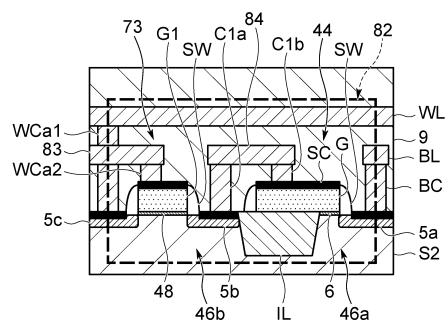

次に上述したアンチヒューズメモリ42が行列状に配置された半導体記憶装置の平面レイアウトの構成について説明する。図9Bとの対応部分に同一符号を付して示す図10は、例えば合計16個のアンチヒューズメモリ $2e_1, 2e_2, 2e_3, 2e_4, 2e_5, 2e_6, 2e_7, 2e_8, 2e_9, 2e_{10}, 2e_{11}, 2e_{12}, 2e_{13}, 2e_{14}, 2e_{15}, 2e_{16}$ を4行4列に配置したときの平面レイアウトの構成を示している。この場合、半導体記憶装置41において、アンチヒューズメモリ $2e_1, 2e_2, 2e_3, 2e_4, 2e_5, 2e_6, 2e_7, 2e_8, 2e_9, 2e_{10}, 2e_{11}, 2e_{12}, 2e_{13}, 2e_{14}, 2e_{15}, 2e_{16}$ は全て同一構成を有しており、上述した図9Aおよび図9Bと同様に、それぞれ整流素子43とメモリキャパシタ44とを有している。また、ワード線コンタクトWC51, WC52, WC53, WC54についても全て同一構成である 20

ことから、ここでは、例えばワード線コンタクトWC52に着目して以下説明する。

#### 【0148】

この場合、ワード線コンタクトWC52が立設する活性領域46bは、互いに隣接する4個のアンチヒューズメモリ $2e_3, 2e_4, 2e_7, 2e_8$ で共有されている。実際に、ワード線コンタクトWC52が立設した活性領域46bには、列方向に隣接する2個のアンチヒューズメモリ $2e_3, 2e_4$ で共有する整流素子ゲート電極G1と、同じく列方向に隣接する2個のアンチヒューズメモリ $2e_7, 2e_8$ で共有する整流素子ゲート電極G1とが形成されている。ワード線コンタクトWC52は、これら2個の整流素子ゲート電極G1と、活性領域46bとに亘って形成されている。これにより、ワード線コンタクトWC52は、これらアンチヒューズメモリの $2e_3, 2e_4, 2e_7, 2e_8$ の各整流素子ゲート電極G1と、これらアンチヒューズメモリの $2e_3, 2e_4, 2e_7, 2e_8$ の整流素子43における各ドレイン領域とに、ビット線からのビット電圧を一律に印加し得る。 30

#### 【0149】

なお、ワード線コンタクトWC52が立設した活性領域46bには、各アンチヒューズメモリ $2e_3, 2e_4, 2e_7, 2e_8$ の整流素子43のソース領域に、それぞれコンタクトC1を介して、各アンチヒューズメモリ $2e_3, 2e_4, 2e_7, 2e_8$ のメモリゲート電極Gが接続されている。

#### 【0150】

次に、ビット線コンタクトBC51, BC52, BC53, BC54, BC55, BC56, BC57, BC58, BC59について以下説明する。この実施の形態の場合、半導体記憶装置41には、合計9個のビット線コンタクトBC51, BC52, BC53, BC54, BC55, BC56, BC57, BC58, BC59が3行3列で配置されている。各ビット線コンタクトBC51, BC52, BC53, BC54, BC55, BC56, BC57, BC58, BC59は、それぞれ異なる活性領域46aに配置されており、ビット線（図示せず）からの所定のビット電圧を、対応する活性領域46aにそれぞれ印加し得るようになされている。 40

#### 【0151】

ここで、これら9個のビット線コンタクトBC51, BC52, BC53, BC54, BC55, BC56, BC57, BC58, BC59のうち、中央領域に配置されたビット線コンタクトBC55が配置された活性領域46aには、異なる活性領域46bに接続され、かつ互いに隣接する4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ が設けられている。これにより、中央領域に配置されたビット線コンタクトBC55は、互いに隣接する4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ にて共有され、ビット線からの所定のビット電圧を、これら4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ に対して一律に印加し得るようになされている。 50

**【 0 1 5 2 】**

この場合、中央のビット線コンタクトBC55が立設した活性領域46aには、当該ビット線コンタクトBC55を中心に、アンチヒューズメモリ $2e_6, 2e_7$ とアンチヒューズメモリ $2e_{10}, 2e_{11}$ とが左右対称に配置されている。具体的に、ビット線コンタクトBC55が立設した活性領域46aの一辺側には、列方向に隣接する2個のアンチヒューズメモリ $2e_6, 2e_7$ の各メモリゲート電極Gが対向配置され、これらアンチヒューズメモリ $2e_6, 2e_7$ の各メモリゲート絶縁膜6が形成されている。またこの活性領域46aの他辺側には、同じく列方向に隣接する他のアンチヒューズメモリ $2e_{10}, 2e_{11}$ の各メモリゲート電極Gが対向配置され、これらアンチヒューズメモリ $2e_{10}, 2e_{11}$ の各メモリゲート絶縁膜6が形成されている。

**【 0 1 5 3 】**

10

因みに、半導体記憶装置41の平面レイアウトにおいて角部に配置された4個のビット線コンタクトBC51, BC53, BC57, BC59には、それぞれ対応する1個のアンチヒューズメモリ $2e_1, 2e_4, 2e_{13}, 2e_{16}$ のみが接続されている。かくして、これら角部に配置された各ビット線コンタクトBC51, BC53, BC57, BC59では、それぞれ対応する1個のアンチヒューズメモリ $2e_1, 2e_4, 2e_{13}, 2e_{16}$ に対してだけビット電圧を印加し得る。

**【 0 1 5 4 】**

20

また、半導体記憶装置41の平面レイアウトにおいて末端に沿って並んだビット線コンタクトBC51, BC52, BC53, BC54, BC56, BC57, BC58, BC59のうち、角部以外に配置されたビット線コンタクトBC52には、2個のアンチヒューズメモリ $2e_2, 2e_3$ のみが接続されている。そして、角部以外に配置されたその他のビット線コンタクトBC54, BC56, BC58にも、それぞれ対応する2個のアンチヒューズメモリ $2e_5, 2e_9, 2e_8, 2e_{12}, 2e_{14}, 2e_{15}$ のみが接続されている。このように、半導体記憶装置41において、角部以外に配置されたその他のビット線コンタクトBC52, BC54, BC56, BC58では、共有するアンチヒューズメモリ数が2個となり、また、中央領域に配置されたビット線コンタクトBC55では、共有するアンチヒューズメモリ数が4個となるため、各ビット線コンタクト毎に1個のアンチヒューズメモリを設ける場合に比して小型化を図り得る。

**【 0 1 5 5 】**

30

以上の構成において、図10に示す半導体記憶装置41のアンチヒューズメモリ $2e_1, 2e_2, 2e_3, 2e_4, 2e_5, 2e_6, 2e_7, 2e_8, 2e_9, 2e_{10}, 2e_{11}, 2e_{12}, 2e_{13}, 2e_{14}, 2e_{15}, 2e_{16}$ では、上述した「(6-3)上記構成による半導体記憶装置の作用および効果」と同様に、従来のような制御回路を用いずに、メモリゲート電極Gおよびワード線WLの電圧値によって、メモリゲート電極Gからワード線WLへの電圧印加をオフ動作で遮断するトランジスタ構成の整流素子43を設けるようにしたことから、メモリキャパシタ44への各電圧印加を選択的に行うスイッチトランジスタや、スイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要となり、その分、小型化を図り得る。

**【 0 1 5 6 】**

40

そして、例えば、半導体記憶装置41におけるアンチヒューズメモリ $2e_4$ では、上述した「(6-3)上記構成による半導体記憶装置の作用および効果」と同様に、(i)ワード線(書き込み非選択ワード線)に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ44にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子43をオフ状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。

**【 0 1 5 7 】**

また、図10に示す半導体記憶装置41では、互いに隣接する4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ で1個のビット線コンタクトBC55を共有するとともに、例えば互いに隣接する4個のアンチヒューズメモリ $2e_3, 2e_4, 2e_7, 2e_8$ で1個のワード線コンタクトWC52を共有するようにしたことにより、各アンチヒューズメモリ毎にビット線コンタクトおよびワード線コンタクトをそれぞれ個別に設ける場合に比して装置全体として小型化を図り得る。

50

## 【0158】

(7-2) ビット線およびワード線の平面レイアウトの構成について

次に、図10に示した半導体記憶装置41におけるビット線およびワード線の平面レイアウトについて以下説明する。図10との対応部分に同一符号を付して示す図11のように、半導体記憶装置41には、1列目のビット線コンタクトBC51,BC52,BC53のうち、1行目のビット線コンタクトBC51と3行目のビット線コンタクトBC53に対して1列目のビット線BL1cが接続されており、これらビット線コンタクトBC51,BC53間の2行目のビット線コンタクトBC52に対して他の2列目のビット線BL2cが接続されている。これにより、半導体記憶装置41は、例えば1列目のビット線BL1cによって、整流素子43の活性領域46bがそれぞれ異なる2個のアンチヒューズメモリ $2e_1, 2e_4$ に対して所定のビット電圧を一律に印加し得、さらに2列目のビット線BL2cによって、整流素子43の活性領域46bがそれぞれ異なる2個のアンチヒューズメモリ $2e_2, 2e_3$ に対して、1列目のビット線BL1cとは異なる所定のビット電圧を印加し得る。

## 【0159】

また、2列目のビット線コンタクトBC54,BC55,BC56では、1行目のビット線コンタクトBC54と3行目のビット線コンタクトBC56に対して3列目のビット線BL3cが接続されており、これらビット線コンタクトBC54,BC56間の2行目のビット線コンタクトBC55に対して4列目のビット線BL4cが接続されている。これにより、半導体記憶装置41は、例えば3列目のビット線BL3cによって、整流素子43の活性領域46bがそれぞれ異なる4個のアンチヒューズメモリ $2e_5, 2e_9, 2e_8, 2e_{12}$ に対して所定のビット電圧を一律に印加し得、さらに4列目のビット線BL4cによって、整流素子43の活性領域46bがそれぞれ異なる4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ に対して、3列目のビット線BL3cとは異なる所定のビット電圧を印加し得る。

## 【0160】

さらに、3列目のビット線コンタクトBC57,BC58,BC59でも、1行目のビット線コンタクトBC57と3行目のビット線コンタクトBC59に対して5列目のビット線BL5cが接続され、これらビット線コンタクトBC57,BC59間の2行目のビット線コンタクトBC58に対して6列目のビット線BL6cが接続されている。これにより、半導体記憶装置41は、例えば5列目のビット線BL5cによって、整流素子43の活性領域46bがそれぞれ異なる2個のアンチヒューズメモリ $2e_{13}, 2e_{16}$ に対して所定のビット電圧を一律に印加し得、さらに6列目のビット線BL6cによって、整流素子43の活性領域46bがそれぞれ異なる2個のアンチヒューズメモリ $2e_{14}, 2e_{15}$ に対して、5列目のビット線BL5cとは異なる所定のビット電圧を印加し得る。

## 【0161】

かかる構成に加えて、ワード線コンタクトWC51,WC52,WC53,WC54にはそれぞれ異なるワード線WL1c,WL2c,WL3c,WL4cが接続されており、各ワード線WL1c,WL2c,WL3c,WL4cによって、各ワード線コンタクトWC51,WC52,WC53,WC54毎に異なるワード電圧を印加し得る。この実施の形態の場合、例えば1行目のワード線WL1cは、1行1列目のワード線コンタクトWC51に接続されており、当該ワード線コンタクトWC51を共有する4個のアンチヒューズメモリ $2e_1, 2e_2, 2e_5, 2e_6$ に所定のワード電圧を一律に印加し得る。また、他のワード線WL2c,WL3c,WL4cも同様に、対応したワード線コンタクトWC53,WC52,WC54を介してそれぞれ4個のアンチヒューズメモリ $2e_9, 2e_{10}, 2e_{13}, 2e_{14}, 2e_3, 2e_4, 2e_7, 2e_8, 2e_{11}, 2e_{12}, 2e_{15}, 2e_{16}$ に対して所定のワード電圧を一律に印加し得る。

## 【0162】

ここで、例えば中央領域にある1個のビット線コンタクトBC55に接続された4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ に着目すると、当該ビット線コンタクトBC55に接続された4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ には、各々電気的に独立に制御できるワード線WL1c,WL2c,WL3c,WL4cが接続されており、各ワード線WL1c,WL2c,WL3c,WL4cによりそれぞれ異なるワード電圧を印加し得る。また、例えば1個のワード線コンタクトWC52に接続された4個のアンチヒューズメモリ $2e_3, 2e_4, 2e_7, 2e_8$ に着目すると、当該ワード線コンタクトWC52に接続された4個のアンチヒューズメモリ $2e_3, 2e_4, 2e_7, 2e_8$ には、各々電気的に

独立に制御できるビット線BL1c,BL2c,BL3c,BL4cが接続されており、各ビット線BL1c,BL2c,BL3c,BL4cによりそれぞれ異なるビット電圧を印加し得る。

#### 【 0 1 6 3 】

そして、このような半導体記憶装置41では、ビット線BL1c,BL2c,BL3c,BL4c,BL5c,BL6cおよびワード線WL1c,WL2c,WL3c,WL4cに印加する電圧を適宜調整することにより、上述した「(6-2)データの書き込み動作」により、例えば所定位置のアンチヒューズメモリ $2e_1$ にのみデータを書き込むことができるとともに、上述した「(1-3)データの読み出し動作」により、例えば所定位置のアンチヒューズメモリ $2e_1$ におけるデータを読み出すことができる。

#### 【 0 1 6 4 】

因みに、図11における半導体記憶装置41では、アンチヒューズメモリ数が16個であるため、例えばワード線WL1cが1つのワード線コンタクトWC51にだけ接続された構成となっている。しかしながら、アンチヒューズメモリ数をさらに増やした場合には、例えば1列目のワード線WL1cと2列目のワード線WL2cとが、行方向に並ぶ複数のワード線コンタクトに対して順次交互に接続された構成となる。例えば1行1列目のワード線コンタクトWC51に接続されているワード線WL1cは、1行3列目のワード線コンタクトや、1行5列目のワード線コンタクト等にも接続され、一方、1行2列目のワード線コンタクトWC53に接続されているワード線WL2cは、1行4列目のワード線コンタクトや、1行6列目のワード線コンタクト等にも接続された構成となる。

#### 【 0 1 6 5 】

(8)他の実施の形態によるビット線およびワード線の平面レイアウトの構成について

図11では、一例として、合計16個のアンチヒューズメモリ $2e_1, 2e_2, 2e_3, 2e_4, 2e_5, 2e_6, 2e_7, 2e_8, 2e_9, 2e_{10}, 2e_{11}, 2e_{12}, 2e_{13}, 2e_{14}, 2e_{15}, 2e_{16}$ を4行4列に配置し、これらアンチヒューズメモリ $2e_1, 2e_2, 2e_3, 2e_4, 2e_5, 2e_6, 2e_7, 2e_8, 2e_9, 2e_{10}, 2e_{11}, 2e_{12}, 2e_{13}, 2e_{14}, 2e_{15}, 2e_{16}$ の配置位置に合わせてビット線BL1c,BL2c,BL3c,BL4c,BL5c,BL6cおよびワード線WL1c,WL2c,WL3c,WL4cを配置させた半導体記憶装置41について示した。

#### 【 0 1 6 6 】

ここで、図11に示す半導体記憶装置41では、ビット線コンタクトBC51,BC52,BC53の列を一端側に設け、ビット線コンタクトBC57,BC58,BC59の列を他端側に設けている。この場合、一端側にある1行1列目のビット線コンタクトBC51と、同じく一端側にある3行1列目のビット線コンタクトBC53とには、それぞれ1個のアンチヒューズメモリ $2e_1$ ( $2e_4$ )のみが接続された構成となり、また、同じく一端側にある2行1列目のビット線コンタクトBC52には、2個のアンチヒューズメモリ $2e_2, 2e_3$ が接続された構成となる。

#### 【 0 1 6 7 】

従って、一端側のビット線コンタクトBC51,BC53に接続される1列目のビット線BL1cは、各ビット線コンタクトBC51,BC53を介して合計2個のアンチヒューズメモリ $2e_1, 2e_4$ のみが接続されることになる。また、同じく一端側のビット線コンタクトBC52に接続される2列目のビット線BL2cも、ビット線コンタクトBC52を介して2個のアンチヒューズメモリ $2e_2, 2e_3$ のみが接続されることになる。

#### 【 0 1 6 8 】

そして、同様に他端側にあるビット線コンタクトBC57,BC58,BC59の列でも、ビット線コンタクトBC57(BC59)に1個のアンチヒューズメモリ $2e_{13}$ ( $2e_{16}$ )が接続され、残りのビット線コンタクトBC58に2個のアンチヒューズメモリ $2e_{14}, 2e_{15}$ が接続された構成となる。そのため、他端側のビット線コンタクトBC57,BC59に接続される5列目のビット線BL5cにも、各ビット線コンタクトBC57,BC59を介して合計2個のアンチヒューズメモリ $2e_{13}, 2e_{16}$ のみが接続されることになり、同じく他端側のビット線コンタクトBC58に接続される6列目のビット線BL6cにも、ビット線コンタクトBC58を介して2個のアンチヒューズメモリ $2e_{14}, 2e_{15}$ のみが接続されることになる。かくして、末端に配置されたビット線コンタクトBC51,BC52,BC53(BC57,BC58,BC59)の列に対して設けたビット線BL1c,BL2c(BL5c,BL6c)では、接続されるアンチヒューズメモリ数が2個となる。

10

20

30

40

50

## 【0169】

その一方で、中央領域に配置されたビット線BL3cには、ビット線コンタクトBC54, BC56を介して合計4個のアンチヒューズメモリ $2e_5, 2e_9, 2e_8, 2e_{12}$ が接続され、同じく中央領域に配置されたビット線BL4cには、ビット線コンタクトBC55を介して4個のアンチヒューズメモリ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ が接続されている。そのため、図11に示した半導体記憶装置41において、行アドレスと列アドレスとによる制御を効率良く行うためには、例えば1列目のビット線BL1aと5列目のビット線BL5aとをショートさせて同じビット電圧で動作するアンチヒューズメモリ数を4個とし、さらに2列目のビット線BL2aと6列目のビット線BL6aもショートさせて同じビット電圧で動作するアンチヒューズメモリ数を4個として、中央領域のビット線BL3c, BL4cに接続されるアンチヒューズメモリ数（この場合、4個）に合わせることが望ましい。10

## 【0170】

すなわち、半導体記憶装置41では、1列目のビット線BL1cに各ビット線コンタクトBC51, BC53を介してそれぞれ接続された合計2個のアンチヒューズメモリ $2e_1, 2e_4$ と、5列目のビット線BL5cにビット線コンタクトBC57, BC59を介してそれぞれ接続された合計2個のアンチヒューズメモリ $2e_{13}, 2e_{16}$ とを合わせた合計4個のアンチヒューズメモリ $2e_1, 2e_4, 2e_{13}, 2e_6$ を、1列目のビット線BL1cと5列目のビット線BL5cとの2本で動作させことが望ましい。

## 【0171】

同様にして2列目のビット線BL2aにビット線コンタクトBC12を介して接続された2個のアンチヒューズメモリ $2a_2, 2a_3$ と、6列目のビット線BL6aにビット線コンタクトBC18を介して接続された2個のアンチヒューズメモリ $2a_{14}, 2a_{15}$ とを合わせた合計4個のアンチヒューズメモリ $2a_2, 2a_3, 2a_{14}, 2a_{15}$ も、2列目のビット線BL2aと6列目のビット線BL6aとの2本で動作させることが望ましい。20

## 【0172】

ここで、半導体記憶装置41では、例えば1列目のビット線BL1cと5列目のビット線BL5cとの2本でアンチヒューズメモリ $2e_1, 2e_4, 2e_{13}, 2e_{16}$ に対して一律に所定のビット電圧を印加する場合、4個のアンチヒューズメモリ $2e_5, 2e_9, 2e_8, 2e_{12}$ （ $2e_6, 2e_7, 2e_{10}, 2e_{11}$ ）を1本の構成で動作させる3列目のビット線BL3cや4列目のビット線BL4cとは容量が異なることになる。そのため、半導体記憶装置41では、データの読み出し動作時に、例えば読み出し速度の低下等の問題が生じる虞がある。30

## 【0173】

そこで、このような問題点を解決するために、図11との対応部分に同一符号を付して示す図12に示すように、半導体記憶装置41aでは、一端側にワード線コンタクトWC51a, WC52aの列を配置するとともに、他端側にワード線コンタクトWC55a, WC56aの列を配置し、さらに、一端側のワード線コンタクトWC51a, WC52aの列と、中央のワード線コンタクトWC53a, WC54aの列との間に一のビット線コンタクトBC51a, BC52a, BC53aの列を設け、他端側のワード線コンタクトWC55a, WC56aの列と、中央のワード線コンタクトWC53a, WC54aの列との間に他のビット線コンタクトBC54a, BC55a, BC56aの列を設けるようにした。

## 【0174】

また、半導体記憶装置41aでは、一端側のワード線コンタクトWC51a, WC52aの列と、中央のワード線コンタクトWC53a, WC54aの列との間にある一のビット線コンタクトBC51a, BC52a, BC53aの列のうち、1行目のビット線コンタクトBC51aと3行目のビット線コンタクトBC53aとに1列目のビット線BL1dを接続させ、2行目のビット線コンタクトBC52aに2列目のビット線BL2dを接続させ得る。40

## 【0175】

これにより、半導体記憶装置41aでは、1行目のビット線コンタクトBC51aに接続された2個のアンチヒューズメモリ $2f_1, 2f_5$ と、3行目のビット線コンタクトBC53aに接続された2個のアンチヒューズメモリ $2f_4, 2f_8$ との合計4個のアンチヒューズメモリ $2f_1, 2f_5, 2f_4, 2f_8$ を、1列目にある1本のビット線BL1dに接続させることができ、かくして、1本の構成でなるビット線BL1dによって4個のアンチヒューズメモリ $2f_1, 2f_5, 2f_4, 2f_8$ を動作させることができ50

きる。

**【 0 1 7 6 】**

また、この半導体記憶装置41aでは、2行目のビット線コンタクトBC52aに接続された4個のアンチヒューズメモリ $2f_2, 2f_3, 2f_6, 2f_7$ を、2列目にある1本のビット線BL2dに接続させることができ、かくして、1本の構成でなるビット線BL2dによって4個のアンチヒューズメモリ $2f_2, 2f_3, 2f_6, 2f_7$ を動作させることができる。

**【 0 1 7 7 】**

同様に、半導体記憶装置41aでは、他端側のワード線コンタクトWC55a, WC56aの列と、中央のワード線コンタクトWC53a, WC54aの列との間に他のビット線コンタクトBC54a, BC55a, BC56aの列でも、1行目のビット線コンタクトBC54aと3行目のビット線コンタクトBC56aとに3列目のビット線BL3dを接続させ、2行目のビット線コンタクトBC55aに4列目のビット線BL4dを接続させ得る。

10

**【 0 1 7 8 】**

これにより、半導体記憶装置41aでは、1行目のビット線コンタクトBC54aに接続された2個のアンチヒューズメモリ $2f_9, 2f_{13}$ と、3行目のビット線コンタクトBC56aに接続された2個のアンチヒューズメモリ $2f_{12}, 2f_{16}$ との合計4個のアンチヒューズメモリ $2f_9, 2f_{13}, 2f_{12}, 2f_{16}$ を、3列目にある1本のビット線BL3dに接続させることができ、かくして、1本の構成でなるビット線BL3dによって4個のアンチヒューズメモリ $2f_9, 2f_{13}, 2f_{12}, 2f_{16}$ を動作させることができる。

20

**【 0 1 7 9 】**

また、この半導体記憶装置41aでは、2行目のビット線コンタクトBC55aに接続された4個のアンチヒューズメモリ $2f_{10}, 2f_{11}, 2f_{14}, 2f_{15}$ を、4列目にある1本のビット線BL4dに接続させることができ、かくして、1本の構成でなるビット線BL4dによって4個のアンチヒューズメモリ $2f_{10}, 2f_{11}, 2f_{14}, 2f_{15}$ を動作させることができる。

20

**【 0 1 8 0 】**

かくして、半導体記憶装置41aでは、図11に示した半導体記憶装置41とは異なり、ビット線同士の接続が不要となり、ビット線BL1d, BL2d, BL3d, BL4dを全て1本の構成とし得、全て同じ容量に設定し得ることから、データの読み出し動作時に、例えば読み出し速度の低下等の問題発生を防止し得る。

30

**【 0 1 8 1 】**

なお、この半導体記憶装置41aにおいて、1行目のワード線コンタクトWC51a, WC53a, WC55aの行には、1列目のワード線コンタクトWC51aと3列目のワード線コンタクトWC55aと同じワード線WL1dが接続され、2列目のワード線コンタクトWC53aに当該ワード線WL1dとは異なる他のワード線WL2dが接続され得る。また、2行目のワード線コンタクトWC52a, WC54a, WC56aの行には、1列目のワード線コンタクトWC52aと3列目のワード線コンタクトWC56aと同じワード線WL3dが接続され、2列のワード線コンタクトWC54aに当該ワード線WL3dとは異なる他のワード線WL4dが接続され得る。

30

**【 0 1 8 2 】**

そして、このような半導体記憶装置41aでも、例えば2行1列目のビット線コンタクトBC52aや、2行2列目のビット線コンタクトBC55aにそれぞれ4個のアンチヒューズメモリ $2f_2, 2f_3, 2f_6, 2f_7$  ( $2f_{10}, 2f_{11}, 2f_{14}, 2f_{15}$ ) が接続された構成を実現し得、上述した実施の形態と同様に小型化を図り得る。また、この半導体記憶装置41aでも、例えば1行2列目のワード線コンタクトWC53aや、2行2列目のワード線コンタクトWC54aにそれぞれ4個のアンチヒューズメモリ $2f_5, 2f_6, 2f_9, 2f_{10}$  ( $2f_7, 2f_8, 2f_{11}, 2f_{12}$ ) を接続させた構成を実現し得、上述した実施の形態と同様に小型化を図り得る。

40

**【 0 1 8 3 】**

因みに、この場合にも、例えば中央領域にある1個のビット線コンタクトBC52aに接続された4個のアンチヒューズメモリ $2f_2, 2f_3, 2f_6, 2f_7$ に着目すると、当該ビット線コンタクトBC52aに接続された4個のアンチヒューズメモリ $2f_2, 2f_3, 2f_6, 2f_7$ には、各々電気的に独立に制御できるワード線WL1d, WL2d, WL3d, WL4dが接続されており、各ワード線WL1d, WL2d, WL3

50

d, WL4dによりそれぞれ異なるワード電圧を印加し得る。また、例えば1個のワード線コンタクトWC53aに接続された4個のアンチヒューズメモリ $2f_5, 2f_6, 2f_9, 2f_{10}$ に着目すると、当該アンチヒューズメモリワード線コンタクトWC53aに接続された4個のアンチヒューズメモリ $2f_5, 2f_6, 2f_9, 2f_{10}$ には、各々電気的に独立に制御できるピット線BL1d, BL2d, BL3d, BL4dが接続されており、各ピット線BL1d, BL2d, BL3d, BL4dによりそれぞれ異なるピット電圧を印加し得る。

#### 【 0 1 8 4 】

そして、この半導体記憶装置41aでも、ピット線BL1d, BL2d, BL3d, BL4dおよびワード線WL1d, WL2d, WL3d, WL4dに印加する電圧を適宜調整することにより、上述した「(6-2)データの書き込み動作」により、例えば所定位置のアンチヒューズメモリ $2f_1$ にのみデータを書き込むことができるとともに、上述した「(1-3)データの読み出し動作」により所定位置のアンチヒューズメモリ $2f_1$ におけるデータを読み出すこともできる。

10

#### 【 0 1 8 5 】

以上の構成によれば、半導体記憶装置41aでは、末端に配置された一方向（この場合、行方向）に並ぶ各ピット線コンタクトBC51a, BC54a (BC53a, BC56a) にそれぞれ2個のアンチヒューズメモリ $2f_1, 2f_5, 2f_9, 2f_{13}$  ( $2f_4, 2f_8, 2f_{12}, 2f_{16}$ ) を接続し、また、末端に配置された他方向（この場合、列方向）に並ぶ各ワード線コンタクトWC51a, WC52a (WC55a, WC56a) にも、それぞれ2個のアンチヒューズメモリ $2f_1, 2f_2, 2f_3, 2f_4$  ( $2f_{13}, 2f_{14}, 2f_{15}, 2f_{16}$ ) を接続するようにした。さらに、この半導体記憶装置41aでは、中央領域に配置された残りのピット線コンタクトBC52a (BC55a) に4個のアンチヒューズメモリ $2f_2, 2f_3, 2f_6, 2f_7$  ( $2f_{10}, 2f_{11}, 2f_{14}, 2f_{15}$ ) を接続し、また、中央領域に配置されたワード線コンタクトWC53a (WC54a) に4個のアンチヒューズメモリ $2f_5, 2f_6, 2f_9, 2f_{10}$  ( $2f_7, 2f_8, 2f_{11}, 2f_{12}$ ) を接続するようにした。

20

#### 【 0 1 8 6 】

これにより、半導体記憶装置41aでは、ピット線コンタクトBC51a～BC56aおよびワード線コンタクトWC51a～WC56aを2個以上のアンチヒューズメモリで共有できる分、装置全体として小型化を実現でき、さらには、例えば1本のピット線BL1dに対して接続されるアンチヒューズメモリ数を同じ数（この場合、4個）にして全て同じ容量に設定し得、かくしてデータの読み出し動作時、読み出し速度の低下等の問題発生を防止し得る。

30

#### 【 0 1 8 7 】

因みに、図12に示す半導体記憶装置41aはアンチヒューズメモリ数を16個とした場合について述べたが、アンチヒューズメモリ数をさらに増やした場合には、例えば1列目のワード線WL1dと2列目のワード線WL2dとが、行方向に並ぶ複数のワード線コンタクトに対して順次交互に接続された構成となる。例えば、1行1列目のワード線コンタクトWC51aに接続されているワード線WL1dは、1行3列目のワード線コンタクトWC55aの他、1行5列目のワード線コンタクト等にも接続され、一方、1行2列目のワード線コンタクトWC53aに接続されているワード線WL2dは、1行4列目のワード線コンタクトや、1行6列目のワード線コンタクト等にも接続された構成となる。

30

#### 【 0 1 8 8 】

また、図12に示した半導体記憶装置41aにおいて、アンチヒューズメモリ数を16個以上に増やした場合には、ピット線コンタクトBC51a, BC54a, … (BC53a, BC56a, ...) が両末端において行方向に並び、一方の末端から列方向に向けて、ピット線コンタクト行と、ワード線コンタクト行とが順次交互に配置され、さらには1行に並ぶピット線コンタクト数をn個としたとき、1行に並ぶワード線コンタクト数が(n+1)個となる。なお、アンチヒューズメモリ数が16個の半導体記憶装置41aを示した図12では、1行に並ぶピット線コンタクト数が2個となり、1行に並ぶワード線コンタクト数が3個となっている。

40

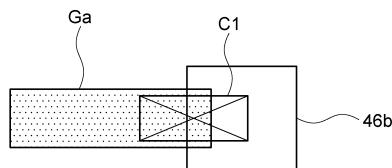

#### 【 0 1 8 9 】

因みに、上述した実施の形態においては、図10に示すように、例えばアンチヒューズメモリ $2e_4$ において整流素子43の活性領域46bと、メモリキャパシタ44のメモリゲート電極Gとが離れているものの、活性領域46bからメモリゲート電極Gに亘ってコンタクトC1を形

50

成して、当該活性領域46bおよびメモリゲート電極GをコンタクトC1により電気的に接続させた場合について述べたが、本発明はこれに限らず、図13に示すように、整流素子の活性領域46b上にメモリゲート電極Gaを形成し、当該活性領域46bからメモリゲート電極Gaに亘ってコンタクトC1を形成するようにしてもよい。

#### 【0190】

また、図15に示すように、整流素子43の活性領域46bと、メモリキャパシタ44のメモリゲート電極Gとを離しつつ、活性領域46bにおける整流素子43のソース領域にコンタクトC2を設け、メモリゲート電極Gにも他のコンタクトC3を設けて、これらコンタクトをC2,C3を配線54により接続するようにしてもよい。

#### 【0191】

(9) 2個のアンチヒューズメモリで、1個のワード線コンタクトを共有し、列方向に並んだ複数のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について

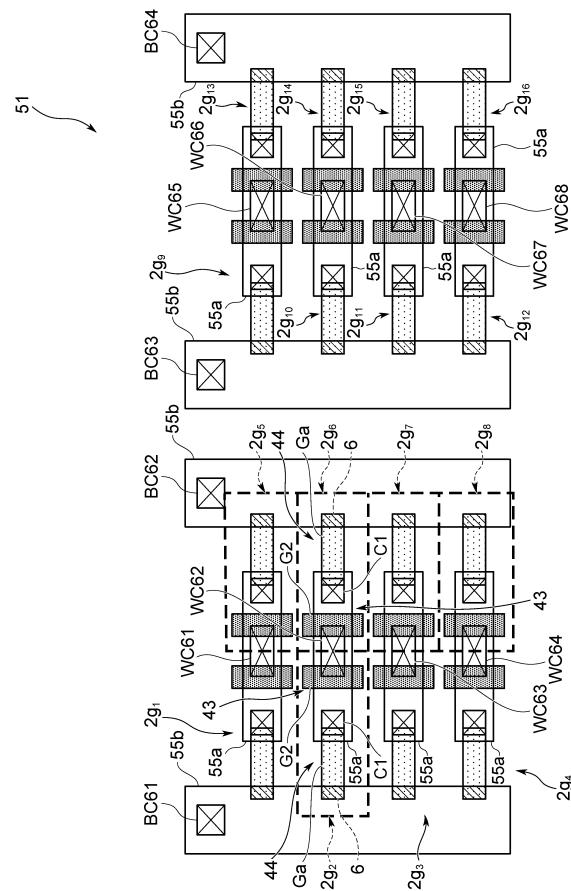

図10との対応部分に同一符号を付して示す図14は、例えば合計16個のアンチヒューズメモリ $2g_1, 2g_2, 2g_3, 2g_4, 2g_5, 2g_6, 2g_7, 2g_8, 2g_9, 2g_{10}, 2g_{11}, 2g_{12}, 2g_{13}, 2g_{14}, 2g_{15}, 2g_{16}$ を4行4列に配置した半導体記憶装置51の平面レイアウトの構成を示している。この場合、半導体記憶装置51において、アンチヒューズメモリ $2g_1, 2g_2, 2g_3, 2g_4, 2g_5, 2g_6, 2g_7, 2g_8, 2g_9, 2g_{10}, 2g_{11}, 2g_{12}, 2g_{13}, 2g_{14}, 2g_{15}, 2g_{16}$ は全て同一構成を有しており、上述した図9Aおよび図9Bと同様に、それぞれ整流素子43とメモリキャパシタ44とを有している。また、ワード線コンタクトWC61, WC62, WC63, WC64, WC65, WC66, WC67, WC68についても全て同一構成でなることから、ここでは、例えばワード線コンタクトWC62に着目して以下説明する。

#### 【0192】

この場合、ワード線コンタクトWC62が立設する整流素子43の活性領域55aは、矩形状に形成されており、行方向に隣接する2個のアンチヒューズメモリ $2g_2, 2g_6$ で共有されている。実際上、ワード線コンタクトWC62が立設した整流素子43の活性領域55aには、アンチヒューズメモリ $2g_2$ の整流素子ゲート電極G2と、当該アンチヒューズメモリ $2g_2$ と行方向に隣接する他のアンチヒューズメモリ $2g_6$ の整流素子ゲート電極G2とが形成されている。

#### 【0193】

ここで、例えばアンチヒューズメモリ $2g_2$ に着目すると、活性領域55aにある整流素子43のドレイン領域と、整流素子ゲート電極G2とに亘ってワード線コンタクトWC62が立設しており、ワード線コンタクトWC62を介してこれらドレイン領域および整流素子ゲート電極G2に対し所定のワード電圧を一律に印加し得る。また、アンチヒューズメモリ $2g_2$ では、活性領域55aにある整流素子43のソース領域と、メモリキャパシタ44のメモリゲート電極Gaとに亘ってコンタクトC1が立設されており、当該コンタクトC1によって、整流素子43のソース領域とメモリキャパシタ44のメモリゲート電極Gaとが電気的に接続されている。

#### 【0194】

なお、このワード線コンタクトWC62は、アンチヒューズメモリ $2g_2$ と行方向に隣接する他のアンチヒューズメモリ $2g_6$ における整流素子43のドレイン領域と、整流素子ゲート電極G2とに亘っても立設されている。これによりワード線コンタクトWC62は、これら2個のアンチヒューズメモリ $2g_2, 2g_6$ に対して、ワード線からの所定のワード電圧を一律に印加し得る。

#### 【0195】

因みに、これら2個のアンチヒューズメモリ $2g_2, 2g_6$ の各メモリゲート電極Gaは、活性領域55aから遠ざかるように行方向に向けてそれぞれ延びてあり、先端部分がそれぞれ異なる活性領域55bに配置されている。また、各メモリゲート電極Gaと、活性領域55bとが対向した各領域には、各アンチヒューズメモリ $2g_2, 2g_6$ のメモリゲート絶縁膜6が形成されている。

#### 【0196】

次に、ビット線コンタクトBC61, BC62, BC63, BC64について以下説明する。この実施の形態の場合、半導体記憶装置51には、合計4個のビット線コンタクトBC61, BC62, BC63, BC64が行方向に並んで配置されている。各ビット線コンタクトBC61, BC62, BC63, BC64は、それぞ

10

20

30

40

50

れ異なる活性領域55bに配置されており、ビット線（図示せず）からの所定のビット電圧を、対応する活性領域55bにそれぞれ印加し得るようになされている。

### 【0197】

この場合、半導体記憶装置51では、1列目のビット線コンタクトBC61が配置された活性領域55bと、2列目のビット線コンタクトBC62が配置された活性領域55bとの間に、行列状に配置された8個のアンチヒューズメモリ $2g_1, 2g_2, 2g_3, 2g_4, 2g_5, 2g_6, 2g_7, 2g_8$ が形成されている。1列目のビット線コンタクトBC61が配置された活性領域55bには、列方向に並ぶ4個のアンチヒューズメモリ $2g_1, 2g_2, 2g_3, 2g_4$ が形成されており、一方、2列目のビット線コンタクトBC62が配置された活性領域55bには、列方向に並ぶアンチヒューズメモリ $2g_5, 2g_6, 2g_7, 2g_8$ が形成されている。10

### 【0198】

また、半導体記憶装置51では、2列目のビット線コンタクトBC62が配置された活性領域55bと、3列目のビット線コンタクトBC63が配置された活性領域55bとが並走しており、上記同様に、3列目のビット線コンタクトBC63および4列目のビット線コンタクトBC64の各活性領域55b間にも、8個のアンチヒューズメモリ $2g_9, 2g_{10}, 2g_{11}, 2g_{12}, 2g_{13}, 2g_{14}, 2g_{15}, 2g_{16}$ が行列状に配置され得る。

### 【0199】

なお、この実施の形態の場合、これら4個のビット線コンタクトBC61, BC62, BC63, BC64は、全て同一構成を有することから、ここではビット線コンタクトBC62に着目して以下説明する。この場合、ビット線コンタクトBC62が配置された活性領域55bは、列方向に並んだ4個のアンチヒューズメモリ $2g_5, 2g_6, 2g_7, 2g_8$ に沿って列方向に延びた長方形形状でなり、これら列方向に並んだ4個のアンチヒューズメモリ $2g_5, 2g_6, 2g_7, 2g_8$ の各メモリゲート電極Gaが設けられた構成を有する。これにより、このビット線コンタクトBC62は、それぞれ異なるワード線コンタクトWC61, WC62, WC63, WC64に接続され、かつ列方向に並んだ4個のアンチヒューズメモリ $2g_5, 2g_6, 2g_7, 2g_8$ に対し、活性領域55bを介してビット線からの所定のビット電圧を一律に印加し得るようになされている。20

### 【0200】

以上の構成において、図14に示す半導体記憶装置51のアンチヒューズメモリ $2g_1, 2g_2, 2g_3, 2g_4, 2g_5, 2g_6, 2g_7, 2g_8, 2g_9, 2g_{10}, 2g_{11}, 2g_{12}, 2g_{13}, 2g_{14}, 2g_{15}, 2g_{16}$ では、上述した「(6-3)上記構成による半導体記憶装置の作用および効果」と同様に、従来のような制御回路を用いずに、メモリキャパシタ44のメモリゲート電極Gaおよびワード線へ印加される電圧値によって整流素子43によりメモリゲート電極Gaからワード線への電圧印加を遮断でき、かくして、従来のようなメモリキャパシタへの電圧印加を選択的に行うスイッチトランジスタや、さらにスイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要になり、その分、小型化を図り得る。30

### 【0201】

そして、例えば、半導体記憶装置51におけるアンチヒューズメモリ $2g_6$ では、上述した「(6-3)上記構成による半導体記憶装置の作用および効果」と同様に、(i)ワード線（書き込み非選択ワード線）に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ44にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子43をオフ状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。40

### 【0202】

また、図14に示す半導体記憶装置51では、列方向に並んだ4個のアンチヒューズメモリ $2g_5, 2g_6, 2g_7, 2g_8$ で1個のビット線コンタクトBC62を共有するとともに、例えば行方向にて隣接する2個のアンチヒューズメモリ $2g_2, 2g_6$ で1個のワード線コンタクトWC62を共有するようにしたことにより、各アンチヒューズメモリ毎にビット線コンタクトおよびワード線コンタクトをそれぞれ個別に設ける場合に比して装置全体として小型化を図り得る。

### 【0203】

10

20

30

40

50

なお、上述した実施の形態の場合においては、図14に示すように、整流素子43の活性領域55aと、メモリキャパシタ44のメモリゲート電極Gaとを重ね、これら活性領域55aにおける整流素子43のソース領域と、メモリゲート電極Gaとに亘ってコンタクトC1を形成した場合について述べたが、本発明はこれに限らず、図15に示すように、整流素子43の活性領域55aと、メモリキャパシタ44のメモリゲート電極Gとを離しつつ、活性領域55aにおける整流素子43のソース領域にコンタクトC2を設け、メモリゲート電極Gにも他のコンタクトC3を設けて、これらコンタクトをC2,C3を配線54により接続するようにもよい。

#### 【0204】

因みに、上述した図9Bでは、活性領域46aと、メモリキャパシタ44のメモリゲート電極Gとが離れて配置されており、これら活性領域46bおよびメモリゲート電極Gを1個のコンタクトC1で接続させた構成としているが、このような接続構成については、図14に示した半導体記憶装置51でも用いることができる。この場合には、例えばアンチヒューズメモリ $2g_6$ における活性領域55aと、メモリゲート電極Gaとを離して配置させ、これら活性領域55aおよびメモリゲート電極Gaを1個のコンタクトC1で接続させた構成となり得る。

#### 【0205】

(10) 行方向に並んだ複数のアンチヒューズメモリで、1個のワード線コンタクトを共有し、2個のアンチヒューズメモリで、1個のビット線コンタクトを共有する場合について

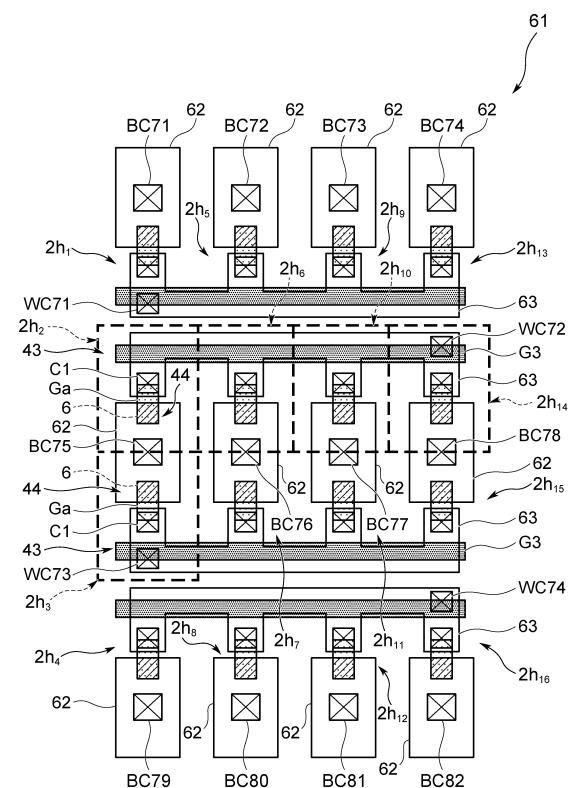

図10との対応部分に同一符号を付して示す図16は、例えば合計16個のアンチヒューズメモリ $2h_1, 2h_2, 2h_3, 2h_4, 2h_5, 2h_6, 2h_7, 2h_8, 2h_9, 2h_{10}, 2h_{11}, 2h_{12}, 2h_{13}, 2h_{14}, 2h_{15}, 2h_{16}$ を4行4列に配置した半導体記憶装置61の平面レイアウトの構成を示している。この場合、半導体記憶装置61において、アンチヒューズメモリ $2h_1, 2h_2, 2h_3, 2h_4, 2h_5, 2h_6, 2h_7, 2h_8, 2h_9, 2h_{10}, 2h_{11}, 2h_{12}, 2h_{13}, 2h_{14}, 2h_{15}, 2h_{16}$ は全て同一構成を有しており、上述した図9Aおよび図9Bと同様に、それぞれ整流素子43とメモリキャパシタ44とを有している。また、ワード線コンタクトWC71, WC72, WC73, WC74についても全て同一構成でなることから、ここでは、例えばワード線コンタクトWC72に着目して以下説明する。

#### 【0206】

この場合、ワード線コンタクトWC72は、行方向に延びた長手方向を有する活性領域63に配置されており、当該活性領域63に沿って行方向に配置された4個のアンチヒューズメモリ $2h_2, 2h_6, 2h_{10}, 2h_{14}$ で共有され得る。実際上、ワード線コンタクトWC72が立設した活性領域63には、行方向に並んだ4個のアンチヒューズメモリ $2h_2, 2h_6, 2h_{10}, 2h_{14}$ の各整流素子43におけるドレイン領域およびソース領域が形成され、さらにこれら4個のアンチヒューズメモリ $2h_2, 2h_6, 2h_{10}, 2h_{14}$ にて共有される整流素子ゲート電極G3が形成されている。

#### 【0207】

この場合、整流素子ゲート電極G3は、行方向に延びる活性領域63の長手方向と並走するように、行方向に延びる長手方向を有しており、活性領域63を上下に分断し得るように配置されている。これにより活性領域63には、整流素子ゲート電極G3を境に、メモリキャパシタ44に近い一方の領域にソース領域が形成され、他方の領域にドレイン領域が形成され得る。活性領域55aには、整流素子43のドレイン領域と、整流素子ゲート電極G3とに亘ってワード線コンタクトWC72が立設しており、ワード線コンタクトWC72を介してこれらドレイン領域および整流素子ゲート電極G3に対し所定のワード電圧を印加し得る。

#### 【0208】

なお、この場合、ワード線コンタクトWC72が立設する整流素子ゲート電極G3および活性領域63のドレイン領域は、活性領域63に沿って配置された4個のアンチヒューズメモリ $2h_2, 2h_6, 2h_{10}, 2h_{14}$ に共有されていることから、ワード線コンタクトWC72によって、これら4個のアンチヒューズメモリ $2h_2, 2h_6, 2h_{10}, 2h_{14}$ に対して、ワード線からの所定のワード電圧を一律に印加し得る。

#### 【0209】

ここで、例えばアンチヒューズメモリ $2h_2$ に着目すると、活性領域63にある整流素子43のソース領域と、メモリキャパシタ44のメモリゲート電極Gaとに亘ってコンタクトC1が立

10

20

30

40

50

設されており、当該コンタクトC1によって、整流素子43のソース領域と、メモリゲート電極Gaとが電気的に接続されている。なお、これらアンチヒューズメモリ $2h_2, 2h_3$ の各メモリゲート電極Gaは、同じ活性領域62に配置されており、当該活性領域62との対向した各領域に各アンチヒューズメモリ $2h_2, 2h_3$ のメモリゲート絶縁膜6が形成されている。

#### 【0210】

因みに、この半導体記憶装置61では、この2行目のワード線コンタクトWC72が立設した活性領域63と、3行目のワード線コンタクトWC73が立設した活性領域63とが並走するように配置されており、これら並走する2個の活性領域63間に、8個のアンチヒューズメモリ $2h_2, 2h_3, 2h_6, 2h_7, 2h_{10}, 2h_{11}, 2h_{14}, 2h_{15}$ が行列状に配置され得る。

#### 【0211】

また、この実施の形態の場合、半導体記憶装置61では、2行目のワード線コンタクトWC72が立設した活性領域63における整流素子43のドレイン領域に対し、1行目のワード線コンタクトWC71が立設した活性領域63における整流素子43のドレイン領域が並走するように隣接されている。この1行目のワード線コンタクトWC71が立設した活性領域63における整流素子43のソース領域は、行方向に並んだ4個のアンチヒューズメモリ $2h_1, 2h_5, 2h_9, 2h_{13}$ のメモリゲート電極GaとコンタクトC1を介して接続されている。また、3行目のワード線コンタクトWC73が立設した活性領域63における整流素子43のドレイン領域に対しても、4行目のワード線コンタクトWC74が立設した活性領域63における整流素子のドレイン領域が並走するように隣接されている。この4行目のワード線コンタクトWC74が立設した活性領域63における整流素子43のソース領域は、行方向に並んだ4個のアンチヒューズメモリ $2h_4, 2h_8, 2h_{12}, 2h_{16}$ のメモリゲート電極GaとコンタクトC1を介して接続されている。

#### 【0212】

次に、ビット線コンタクトBC71, BC72, BC73, BC74, BC75, BC76, BC77, BC78, BC79, BC80, BC81, BC82について以下説明する。この実施の形態の場合、半導体記憶装置61には、合計12のビット線コンタクトBC71, BC72, BC73, BC74, BC75, BC76, BC77, BC78, BC79, BC80, BC81, BC82が3行4列で配置されている。これらビット線コンタクトBC71, BC72, BC73, BC74, BC75, BC76, BC77, BC78, BC79, BC80, BC81, BC82は、それぞれ異なる活性領域62に配置されており、ビット線（図示せず）からの所定のビット電圧を、対応する活性領域62にそれぞれ印加し得るようになされている。

#### 【0213】

ここで、中央領域に配置された行方向に並ぶビット線コンタクトBC75, BC76, BC77, BC78は全て同一構成を有していることから、そのうち、例えばビット線コンタクトBC75に着目して以下説明する。この場合、ビット線コンタクトBC75が配置された活性領域62には、異なるワード線コンタクトWC72, WC73に接続され、かつ列方向に並ぶ2個のアンチヒューズメモリ $2h_2, 2h_3$ が設けられている。これにより、ビット線コンタクトBC75は、これら2個のアンチヒューズメモリ $2h_2, 2h_3$ にて共有され、ビット線からの所定のビット電圧を、これら2個のアンチヒューズメモリ $2h_2, 2h_3$ に対して一律に印加し得るようになされている。

#### 【0214】

実際上、このビット線コンタクトBC75が立設した活性領域62には、当該ビット線コンタクトBC75を中心に、アンチヒューズメモリ $2h_2$ とアンチヒューズメモリ $2h_3$ とが上下対称に配置されている。具体的に、ビット線コンタクトBC75が立設した活性領域62の一辺側には、一のアンチヒューズメモリ $2h_2$ のメモリゲート電極Gaが対向配置され、当該アンチヒューズメモリ $2h_2$ のメモリゲート絶縁膜6が形成されている。また、この活性領域62の他辺側にも、同じく他のアンチヒューズメモリ $2h_3$ のメモリゲート電極Gaが対向配置され、当該アンチヒューズメモリ $2h_3$ のメモリゲート絶縁膜6が形成されている。

#### 【0215】

因みに、半導体記憶装置61の平面レイアウトにおいて、末端にて行方向に配置された4個のビット線コンタクトBC71, BC72, BC73, BC74 (BC79, BC80, BC81, BC82) には、それぞれ対応する1個のアンチヒューズメモリ $2h_1, 2h_5, 2h_9, 2h_{13}$  ( $2h_4, 2h_8, 2h_{12}, 2h_{16}$ ) のみが接続されている。かくして、これら末端にて行方向に配置された各ビット線コンタクトBC71, BC7

10

20

30

40

50

2,BC73,BC74 ( BC79,BC80,BC81,BC82 ) では、それぞれ対応する1個のアンチヒューズメモリ $2h_1,2h_5,2h_9,2h_{13}$  ( $2h_4,2h_8,2h_{12},2h_{16}$ ) に対してだけビット電圧を印加し得る。

#### 【 0 2 1 6 】

このように、末端の各ビット線コンタクトBC71,BC72,BC73,BC74,BC79,BC80,BC81,BC82では、それぞれ1個のアンチヒューズメモリ $2h_1,2h_5,2h_9,2h_{13},2h_4,2h_8,2h_{12},2h_{16}$ に対してだけ所定のビット電圧を印加し得ることになるものの、中央領域に配置された各ビット線コンタクトBC75,BC76,BC77,BC78では、それぞれ対応する2個のアンチヒューズメモリ $2h_2,2h_3,2h_6,2h_7,2h_{10},2h_{11},2h_{14},2h_{15}$ に対して所定のビット電圧を一律に印加し得ることから、2個のアンチヒューズメモリ $2h_2,2h_3,2h_6,2h_7,2h_{10},2h_{11},2h_{14},2h_{15}$ で1個のビット線コンタクトBC75,BC76,BC77,BC78を共有させる分だけ装置全体としては小型化を図り得る。10

#### 【 0 2 1 7 】

以上の構成において、図16に示す半導体記憶装置61のアンチヒューズメモリ $2h_1,2h_2,2h_3,2h_4,2h_5,2h_6,2h_7,2h_8,2h_9,2h_{10},2h_{11},2h_{12},2h_{13},2h_{14},2h_{15},2h_{16}$ では、上述した「(6-3)上記構成による半導体記憶装置の作用および効果」と同様に、従来のような制御回路を用いずに、メモリキャパシタ44のメモリゲート電極Gaおよびワード線へ印加される電圧値によって整流素子43によりメモリゲート電極Gaからワード線への電圧印加を遮断でき、かくして、従来のようなメモリキャパシタへの電圧印加を選択的に行うスイッチトランジスタや、さらにスイッチトランジスタにオンオフ動作を行わせるためのスイッチ制御回路が不要になり、その分、小型化を図り得る。20

#### 【 0 2 1 8 】

そして、例えば、半導体記憶装置61におけるアンチヒューズメモリ $2h_2$ では、上述した「(6-3)上記構成による半導体記憶装置の作用および効果」と同様に、(i)ワード線(書き込み非選択ワード線)に0[V]の非破壊ワード電圧を印加することにより、メモリキャパシタ44にチャネルを形成しないことによる第一の遮断機構と、(ii)整流素子43をオフ状態にして非破壊ビット電圧を遮断する第二の遮断機構との二重の遮断機構を設けることができ、これにより正常なデータの書き込み動作を実行し得ることから、データ読み出し時における誤動作も確実に防止し得る。

#### 【 0 2 1 9 】

また、図16に示す半導体記憶装置61では、例えば一方向(この場合、行方向)に並ぶ4個のアンチヒューズメモリ $2h_2,2h_6,2h_{10},2h_{14}$ で1個のワード線コンタクトWC72を共有するとともに、例えば互いに隣接する2個のアンチヒューズメモリ $2h_2,2h_3$ で1個のビット線コンタクトBC75を共有するようにしたことにより、各アンチヒューズメモリ毎にビット線コンタクトおよびワード線コンタクトをそれぞれ個別に設ける場合に比して装置全体として小型化を図り得る。30

#### 【 0 2 2 0 】

因みに、図16に示す半導体記憶装置61でも、例えばアンチヒューズメモリ $2h_2$ において、整流素子43の活性領域63と、メモリキャパシタ44のメモリゲート電極Gaとを離し、活性領域63に設けた一のコンタクトと、メモリゲート電極Gaに設けた他のコンタクトとを配線により接続する構成としてもよい。また、図9Bに示した構成のように、整流素子43の活性領域63と、メモリキャパシタ44のメモリゲート電極Gaとを離し、これら活性領域63およびメモリゲート電極Gaを1個のコンタクトC1で接続させた構成としてもよい。40

#### 【 0 2 2 1 】

##### ( 1 1 ) 他の実施の形態

###### ( 1 1 - 1 ) P型MOSトランジスタからなる整流素子を有したアンチヒューズメモリ

上述した「(6)N型MOS(Metal-Oxide-Semiconductor)トランジスタからなる整流素子を有したアンチヒューズメモリ」においては、N型MOSトランジスタでなる整流素子43を設けたアンチヒューズメモリ42について述べたが、本発明はこれに限らず、図8との対応部分に同一符号を付して示す図17のように、P型MOSトランジスタでなる整流素子73を設けたアンチヒューズメモリ72を適用してもよい。この場合、アンチヒューズメモリ72は、50

P型MOSトランジスタの半導体接合構造を有した整流素子73と、ビット線BLおよびメモリゲート電極G間の電圧差により絶縁破壊されるメモリゲート絶縁膜6を備えたメモリキャパシタ44とを備える。

#### 【0222】

この場合、メモリキャパシタ44には、一端の拡散領域にビット線BLが接続されており、メモリゲート電極Gに整流素子73が接続されている。整流素子73は、整流素子ゲート電極G1と、ドレイン領域とがメモリキャパシタ44のメモリゲート電極Gに接続されるとともに、ウエルがウエル制御端子に接続され、さらにソース領域がワード線WLに接続された構成を有する。これにより整流素子73は、ワード線WLからオン電圧が印加されない限りオフ動作するため、メモリゲート電極Gからワード線WLへの電圧印加を遮断し得るようになされている。10

#### 【0223】