(12)

## Patentschrift

(21) Aktenzeichen: 11 2012 007 290.1

(51) Int Cl.: **H01L 29/786** (2006.01)

(22) Anmelddatum: 05.10.2012

**H01L 27/12** (2006.01)

(45) Veröffentlichungstag

der Patenterteilung: 29.06.2017

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**2011227022** 14.10.2011 JP

(72) Erfinder:

Yamazaki, Shunpei, Atsugi-shi, Kanagawa-ken,

JP; Honda, Tatsuya, Nigata-shi, JP; Shimazu,

Takashi, Nagoya-shi, Aichi-ken, JP; Nonaka,

Yusuke, Atsugi-shi, Kanagawa-ken, JP; Tsubuku,

Masashi, Atsugi-shi, Kanagawa-ken, JP

(62) Teilung aus:

**11 2012 004 307.3**

(56) Ermittelter Stand der Technik:

US **2011 / 0 017 990** A1

(73) Patentinhaber:

Semiconductor Energy Laboratory Co., Ltd.,

Atsugi-shi, Kanagawa-ken, JP

(74) Vertreter:

Grünecker Patent- und Rechtsanwälte PartG

mbB, 80802 München, DE

(54) Bezeichnung: Halbleitervorrichtung

(57) Hauptanspruch: Halbleitervorrichtung, die umfasst:

einen Oxidhalbleiterfilm (106) über einem Substrat (102);

eine Source-Elektrode (108a) und eine Drain-Elektrode

(108b) über dem Oxidhalbleiterfilm (106);

einen Gate-Isolierfilm (110) über dem Oxidhalbleiterfilm

(106), wobei der Gate-Isolierfilm (110) ein Oxid, das Silizium

enthält, umfasst; und

eine Gate-Elektrode (112) über dem Gate-Isolierfilm (110),

wobei der Oxidhalbleiterfilm (106) umfasst:

einen ersten Bereich (106a), in dem eine Konzentration von

Silizium niedriger als oder gleich 1,0 Atom-% ist; und

ein Paar von zweiten Bereichen (106e, 106f), wobei jeder

von dem Paar von zweiten Bereichen einen Dotierstoff um-

fasst,

wobei der erste Bereich (106a) an einer Grenzfläche zwi-

schen dem Oxidhalbleiterfilm (106) und dem Gate-Isolierfilm

(110) liegt und in Kontakt mit dem Gate-Isolierfilm (110) ist,

und

wobei der erste Bereich (106a) einen Kristallbereich um-

fasst.

**Beschreibung**

## Technisches Gebiet

**[0001]** Die vorliegende Erfindung betrifft eine Halbleitervorrichtung und ein Verfahren zum Herstellen der Halbleitervorrichtung.

**[0002]** In dieser Beschreibung bedeutet eine Halbleitervorrichtung im Allgemeinen eine Vorrichtung, die durch Anwenden von Halbleitercharakteristiken arbeiten kann, und eine elektrooptische Vorrichtung, eine Halbleiter-Schaltung und ein elektronisches Gerät sind alle Halbleitervorrichtungen.

## Stand der Technik

**[0003]** Eine Technik zum Ausbilden von Transistoren unter Verwendung eines Halbleiterdünffilms, der über einem Substrat ausgebildet ist, welches eine isolierende Oberfläche aufweist, hat Aufmerksamkeit erregt. Der Transistor wird in einem breiten Bereich von elektronischen Geräten verwendet, wie z. B. einer integrierten Schaltung (integrated circuit: IC) oder einer Bildanzeigevorrichtung (Anzeigevorrichtung). Als Halbleiterdünffilm, der für den Transistor verwendbar ist, ist beispielsweise ein Halbleitermaterial auf Silizium-Basis weithin bekannt; des Weiteren hat ein Oxidhalbleiter als weiteres Material Aufmerksamkeit erregt.

**[0004]** Beispielsweise ist ein Transistor offenbart, dessen aktive Schicht ein amorphes Oxid aufweist, welches Indium (In), Gallium (Ga) und Zink (Zn) enthält (siehe Patentdokument 1).

**[0005]** Transistoren, die Oxidhalbleiter aufweisen, haben bessere Eigenschaften im Durchlasszustand (on-state characteristics) (Durchlassstrom (on-state current)) als Transistoren, die amorphes Silizium aufweisen. Um die Transistoren, die Oxidhalbleiter aufweisen, für hochleistungsfähige Vorrichtungen anzuwenden, fordert man, dass derartige Transistoren weiter verbesserte Eigenschaften haben. Somit sind Techniken zur Kristallisierung von Oxidhalbleitern entwickelt worden (siehe Patentdokument 2). In Patentdokument 2 ist eine Technik offenbart, bei der ein Oxidhalbleiter durch eine Wärmebehandlung kristallisiert wird.

[Referenz]

[Patentdokument]

**[0006]**

[Patentdokument 1] Japanische Patentoffenlegungsschrift Nr. JP 2006-165528 A

[Patentdokument 2] Japanische Patentoffenlegungsschrift Nr. JP 2008-311342 A

**[0007]** Die US 2011/0017990 A1 beschreibt einen Dünnschicht-Transistor und einen Prozess zu seiner Herstellung. Ein erster Oxidhalbleiterfilm wird auf einem zweiten Oxidhalbleiterfilm gebildet, um einen Kanalfilm zu bilden. Source und Drain werden gebildet, so dass sie Kontakt zu jeweils zwei gegenüberliegenden Seiten des Kanalfilms bilden. Der Gate-Isolierfilm und das Gate werden nacheinander gebildet.

## Offenbarung der Erfindung

**[0008]** In dem Fall, in dem ein Transistor mit obenliegendem Gate (top-gate transistor), der einen Oxidhalbleiterfilm aufweist, ausgebildet wird, wird ein Gate-Isolierfilm über dem Oxidhalbleiterfilm ausgebildet. Wenn der Gate-Isolierfilm ausgebildet wird, kann ein Bestandteil des Gate-Isolierfilms in den Oxidhalbleiterfilm eindringen, über dem der Gate-Isolierfilm ausgebildet wird.

**[0009]** Beispielsweise werden in dem Fall, in dem ein Siliziumoxid-(SiO<sub>x</sub>, x = 2 oder mehr)Film als Gate-Isolierfilm nach dem Ausbilden eines Oxidhalbleiterfilms durch ein Sputterverfahren ausgebildet wird, Silizium, das ein Bestandteil des Siliziumoxides ist, und ein Edelgaselement wie z. B. Argon, das beim Sputtern verwendet wird, zusammen in den Oxidhalbleiterfilm implantiert. Solches Silizium bricht eine Bindung zwischen Bestandteilen des Oxidhalbleiterfilms (einem Indiumatom und einem Sauerstoffatom (In-O-Bindung)) auf und wird als Verunreinigungselement in dem Oxidhalbleiterfilm eingeschlossen. Das Verunreinigungselement kann mit einer hohen Konzentration besonders in der Nähe der Grenzfläche zwischen dem Oxidhalbleiterfilm und dem Gate-Isolierfilm enthalten sein. In der Nähe der Grenzfläche zwischen dem Oxidhalbleiterfilm und dem Gate-Isolierfilm wird ein Kanalbildungsbereich ausgebildet; somit wird dann, wenn ein Verunreinigungselement wie z. B. Silizium enthalten ist, der Widerstand des Oxidhalbleiterfilms erhöht. Als Ergebnis wird der Durchlass-

strom, der eine der elektrischen Eigenschaften eines Transistors ist, verringert. Wie oben beschrieben worden ist, wird das Verunreinigungselement, das in dem Oxidhalbleiterfilm verbleibt, zu einer Ursache, die elektrische Eigenschaften des Transistors beeinflusst.

**[0010]** Ferner wird in dem Fall, in dem der Oxidhalbleiterfilm einen Kristallbereich aufweist, eine Bindung in dem Kristallbereich des Oxidhalbleiterfilms durch das Eindringen des Bestandteils des Gate-Isolierfilms in den Oxidhalbleiterfilm aufgebrochen; somit werden mehr amorphe Bereiche in dem Oxidhalbleiterfilm in der Nähe des Gate-Isolierfilms ausgebildet.

**[0011]** Angesichts der obigen Probleme ist eine Aufgabe, die Konzentration eines Verunreinigungselements, das in einem Oxidhalbleiterfilm in der Nähe eines Gate-Isolierfilms enthalten ist, zu verringern. Eine weitere Aufgabe ist, die Kristallinität des Oxidhalbleiterfilms in der Nähe des Gate-Isolierfilms zu verbessern. Außerdem ist eine weitere Aufgabe, eine Halbleitervorrichtung mit stabilen elektrischen Eigenschaften unter Verwendung des Oxidhalbleiterfilms bereitzustellen.

**[0012]** Die Erfindung stellt eine Halbleitervorrichtung nach einem der Ansprüche 1 oder 2 bereit. Vorteilhafte Weiterbildungen werden in den abhängigen Ansprüchen beschrieben.

**[0013]** Entsprechend einer Ausführungsform der vorliegenden Erfindung, die offenbart wird, kann die Konzentration eines Verunreinigungselements, das in dem Oxidhalbleiterfilm in der Nähe des Gate-Isolierfilms enthalten ist, verringert werden. Des Weiteren kann die Kristallinität des Oxidhalbleiterfilms in der Nähe des Gate-Isolierfilms verbessert werden. Außerdem kann eine Halbleitervorrichtung mit stabilen elektrischen Eigenschaften bereitgestellt werden.

#### Kurze Beschreibung der Zeichnungen

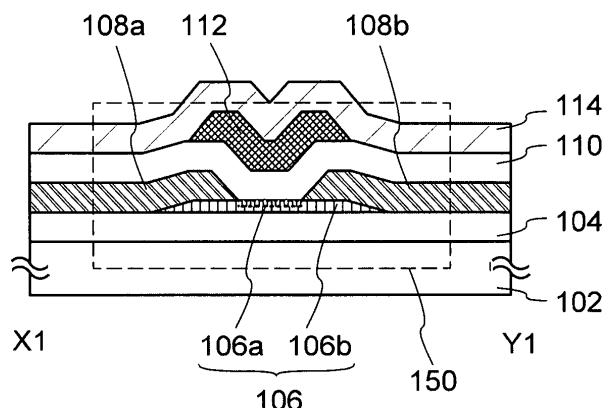

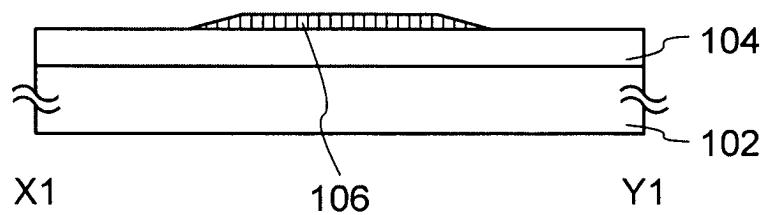

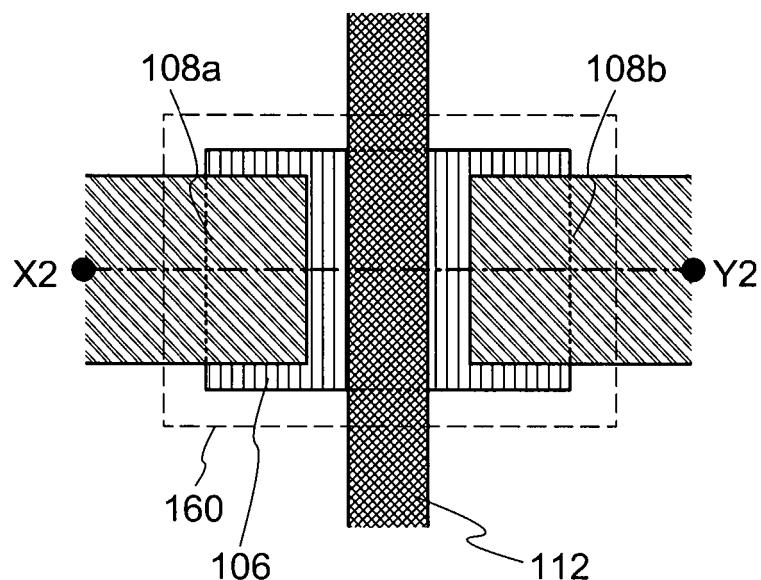

**[0014]** **Fig. 1A** und **Fig. 1B** sind eine Draufsicht und eine Querschnittsansicht, die eine Ausführungsform einer Halbleitervorrichtung zeigen.

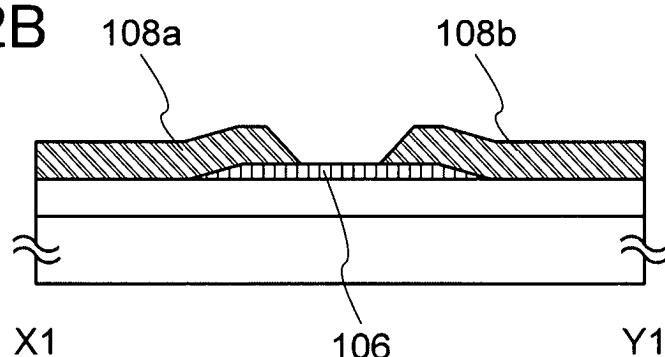

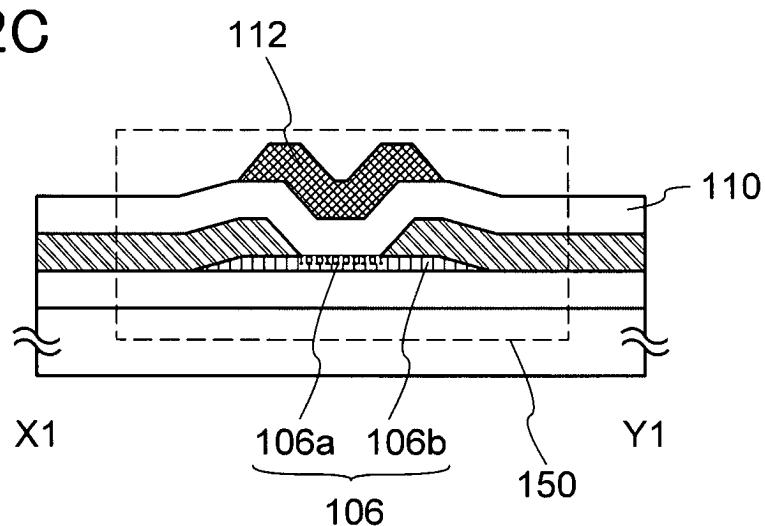

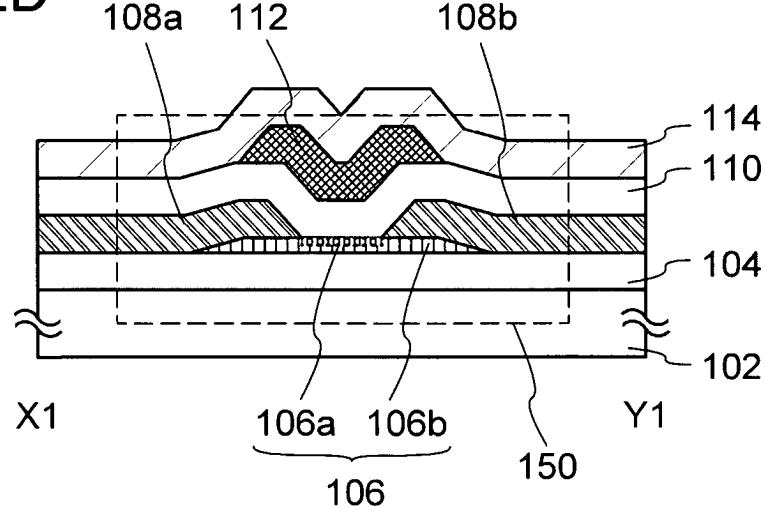

**[0015]** **Fig. 2A** bis **Fig. 2D** sind Querschnittsansichten, die ein Beispiel für einen Herstellungsprozess einer Halbleitervorrichtung zeigen.

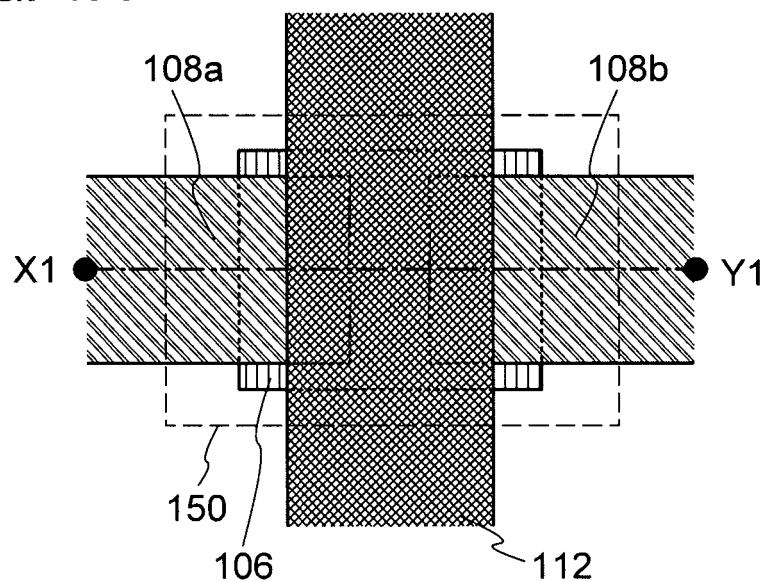

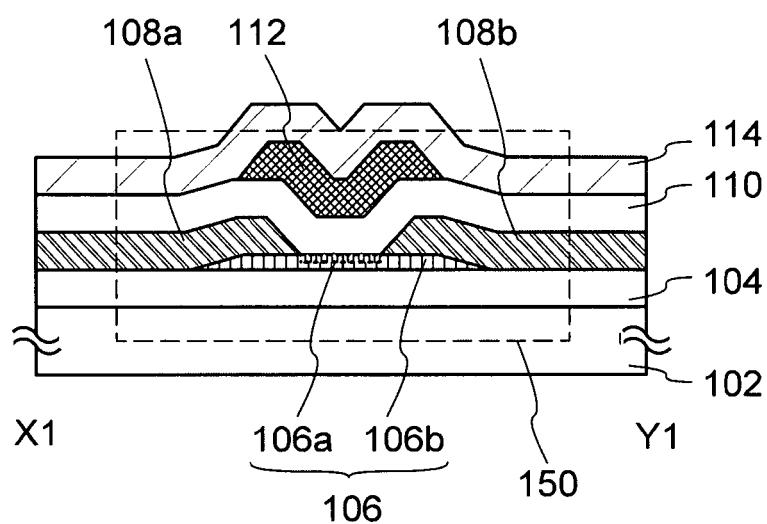

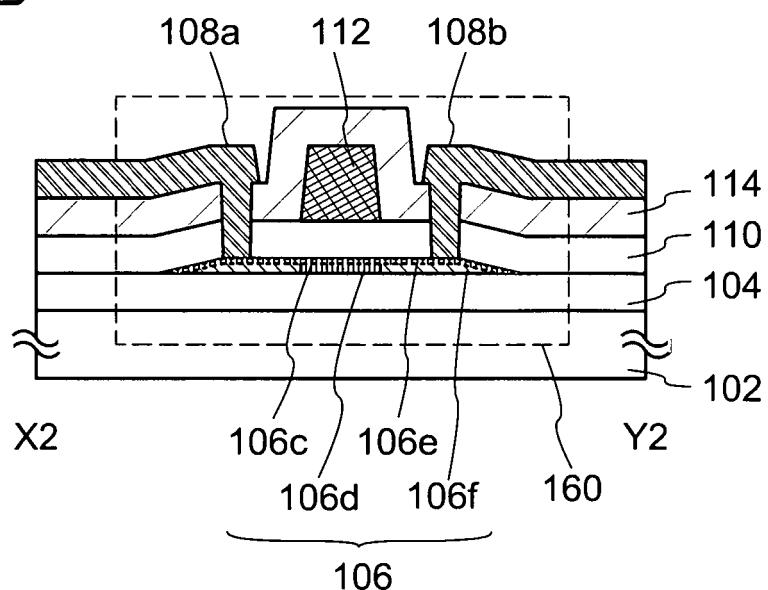

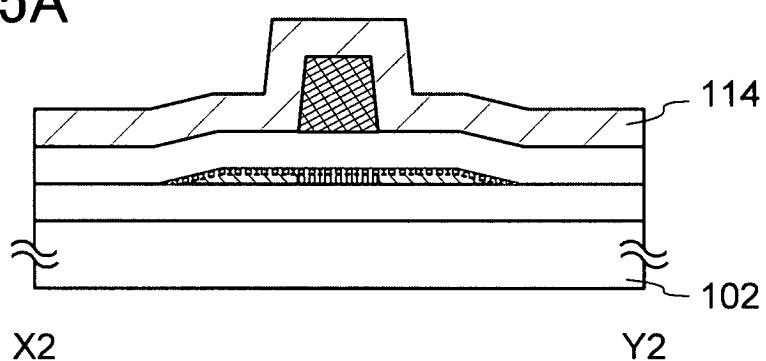

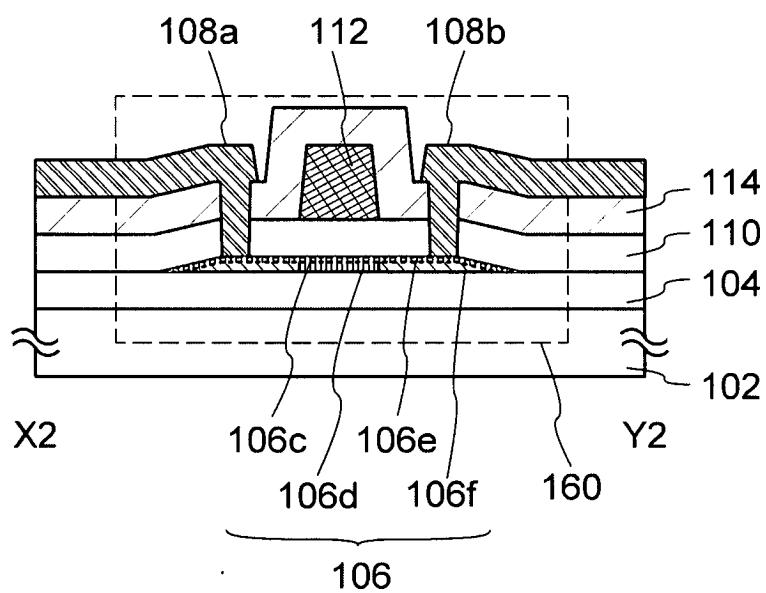

**[0016]** **Fig. 3A** und **Fig. 3B** sind eine Draufsicht und eine Querschnittsansicht, die eine Ausführungsform einer Halbleitervorrichtung zeigen.

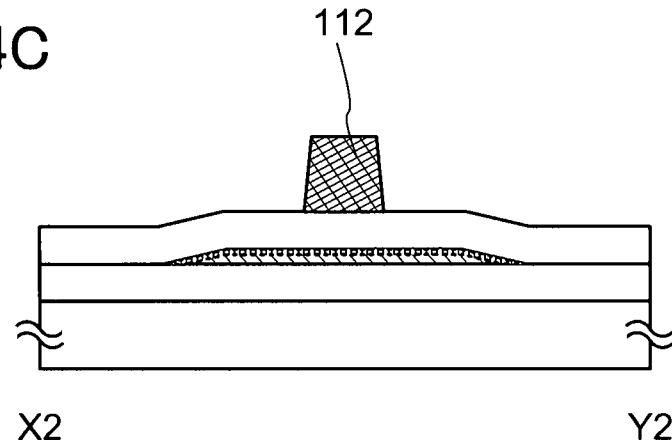

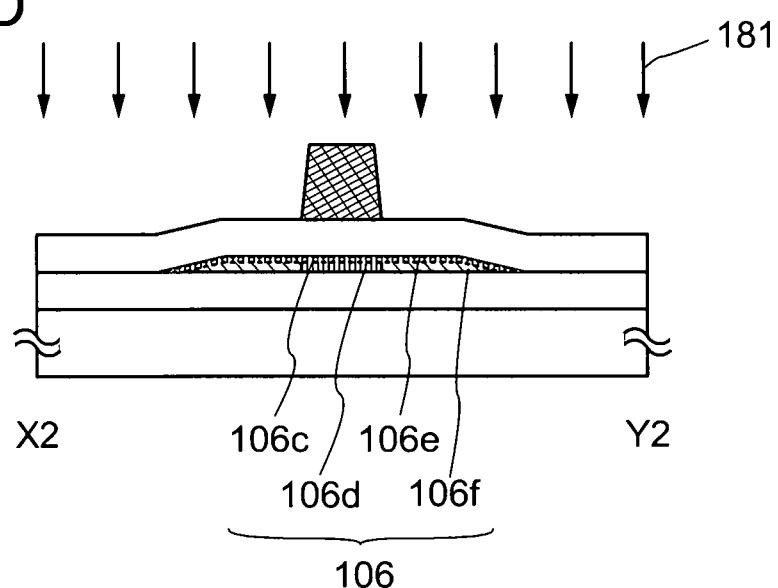

**[0017]** **Fig. 4A** bis **Fig. 4D** sind Querschnittsansichten, die ein Beispiel für einen Herstellungsprozess einer Halbleitervorrichtung zeigen.

**[0018]** **Fig. 5A** und **Fig. 5B** sind Querschnittsansichten, die ein Beispiel für einen Herstellungsprozess einer Halbleitervorrichtung zeigen.

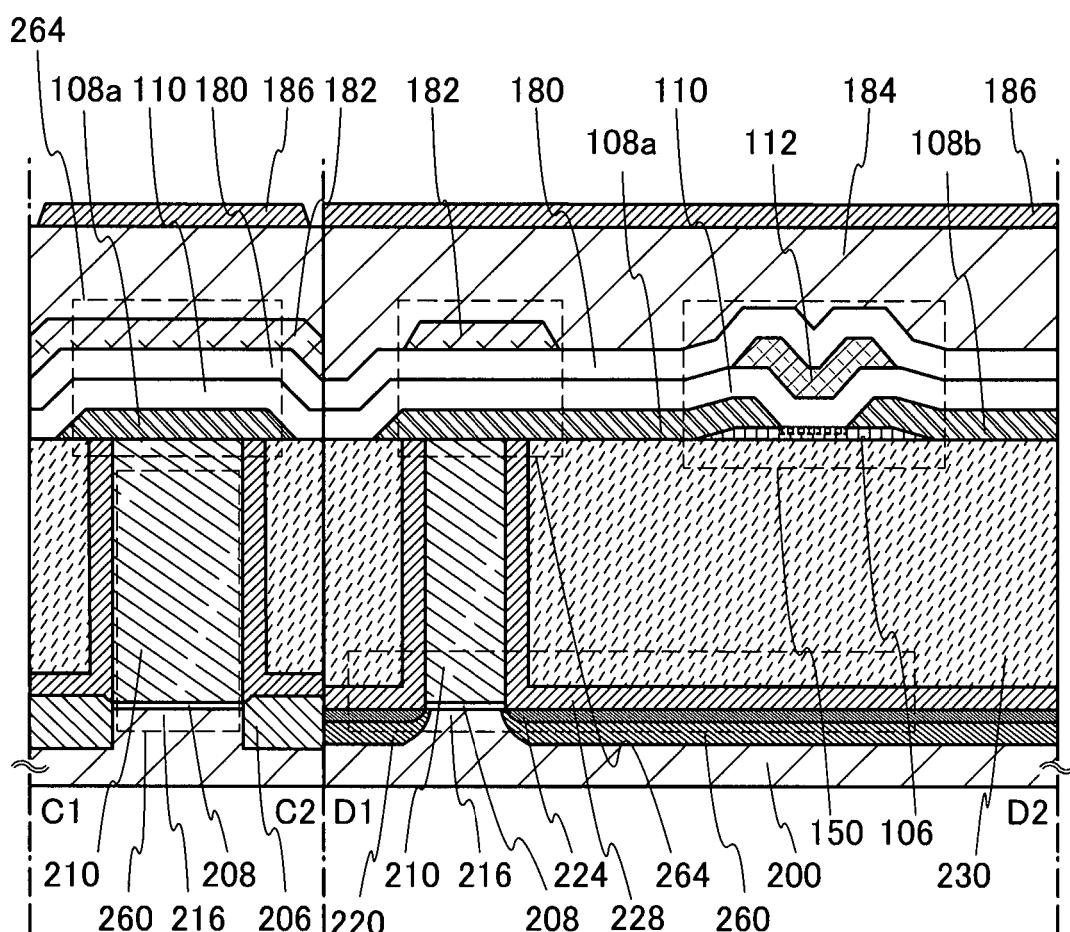

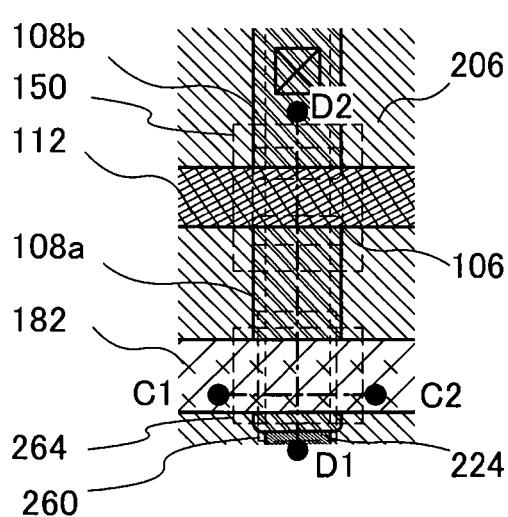

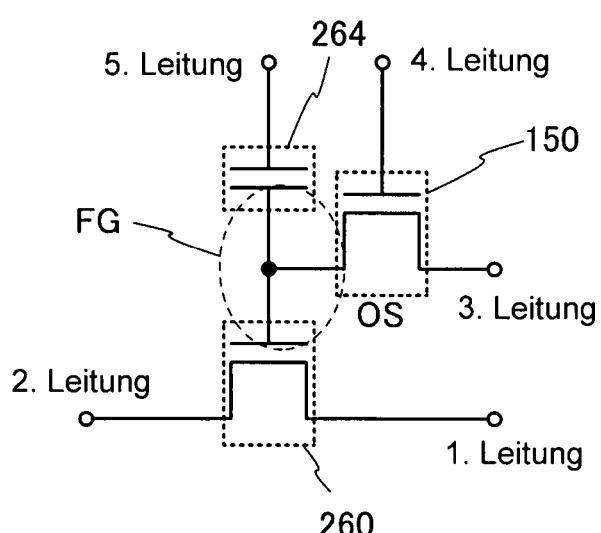

**[0019]** **Fig. 6A** bis **Fig. 6C** zeigen eine Ausführungsform einer Halbleitervorrichtung.

**[0020]** **Fig. 7A** und **Fig. 7B** zeigen eine Ausführungsform einer Halbleitervorrichtung.

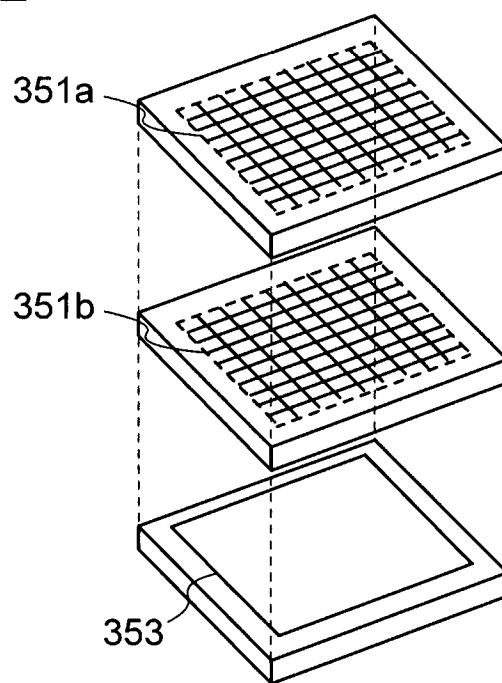

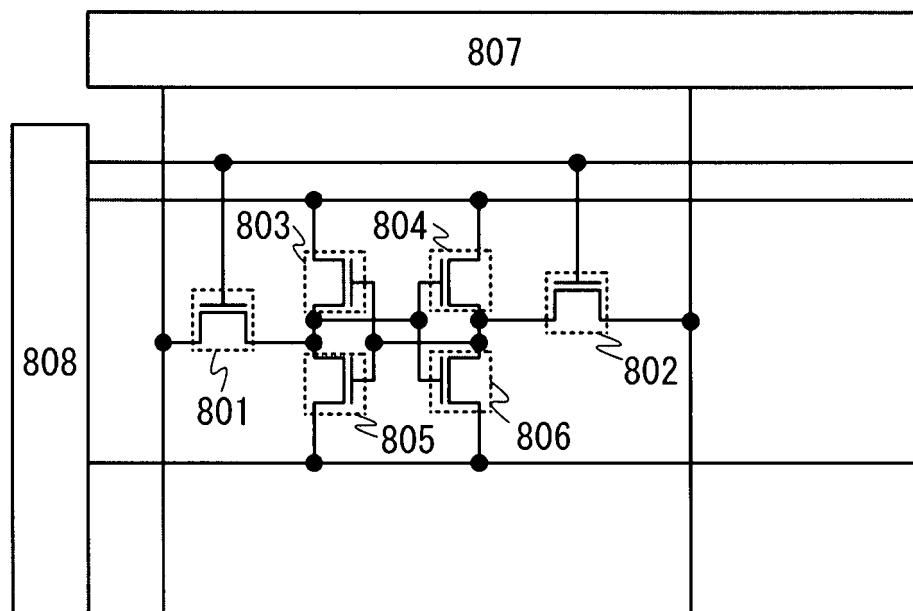

**[0021]** **Fig. 8A** und **Fig. 8B** zeigen eine Ausführungsform einer Halbleitervorrichtung.

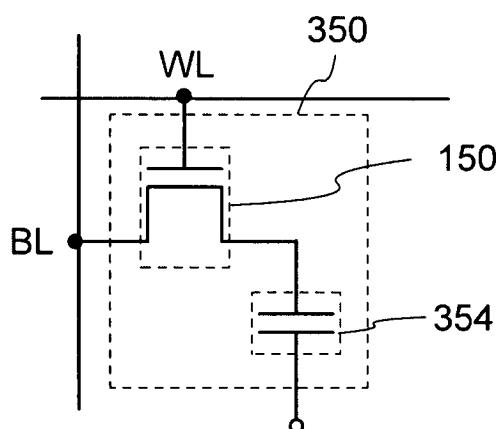

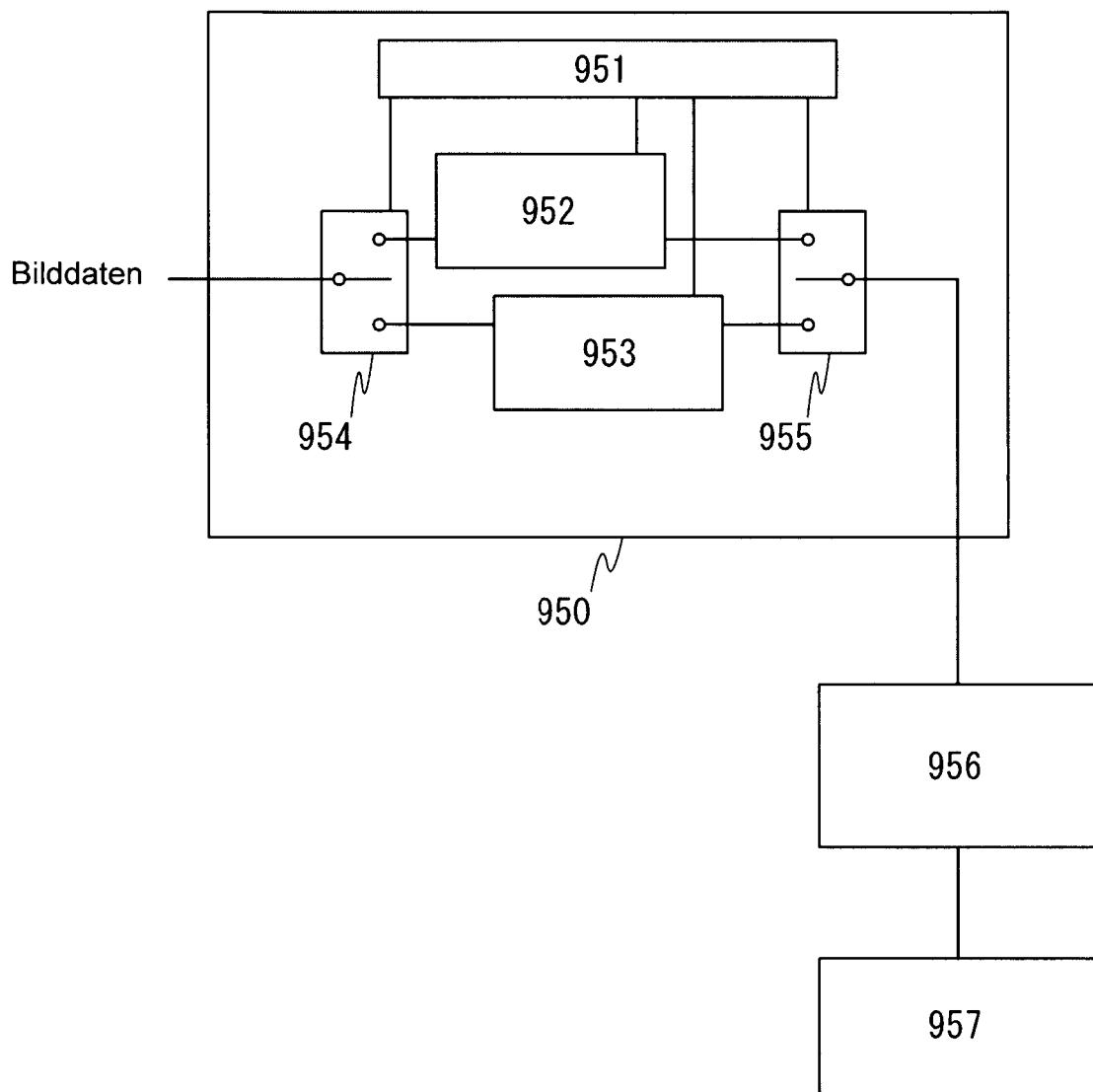

**[0022]** **Fig. 9** zeigt eine Ausführungsform einer Halbleitervorrichtung.

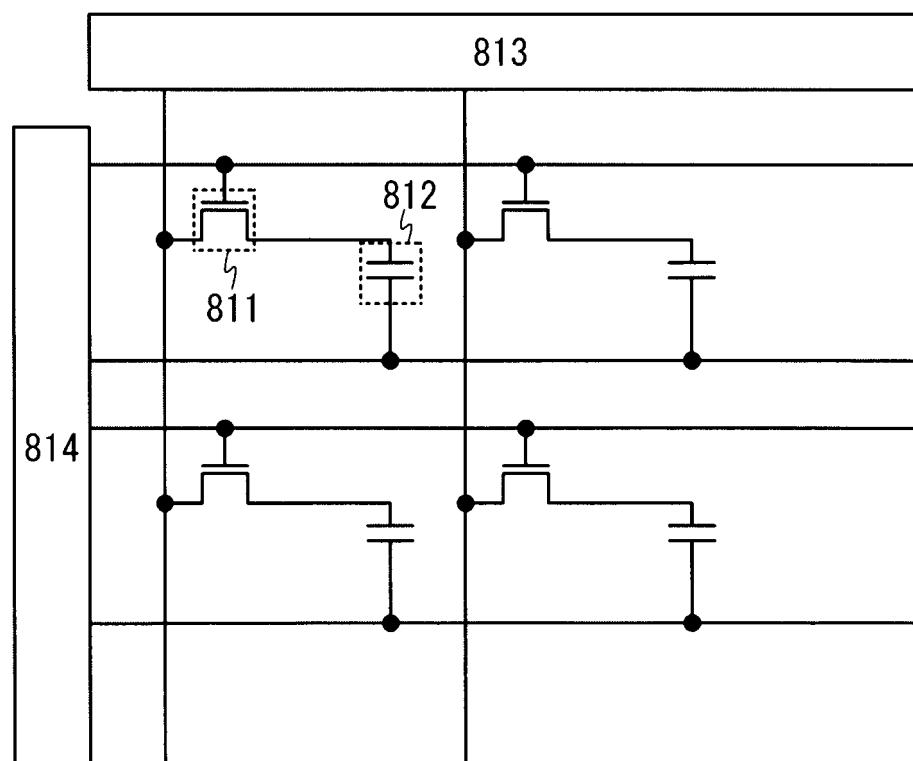

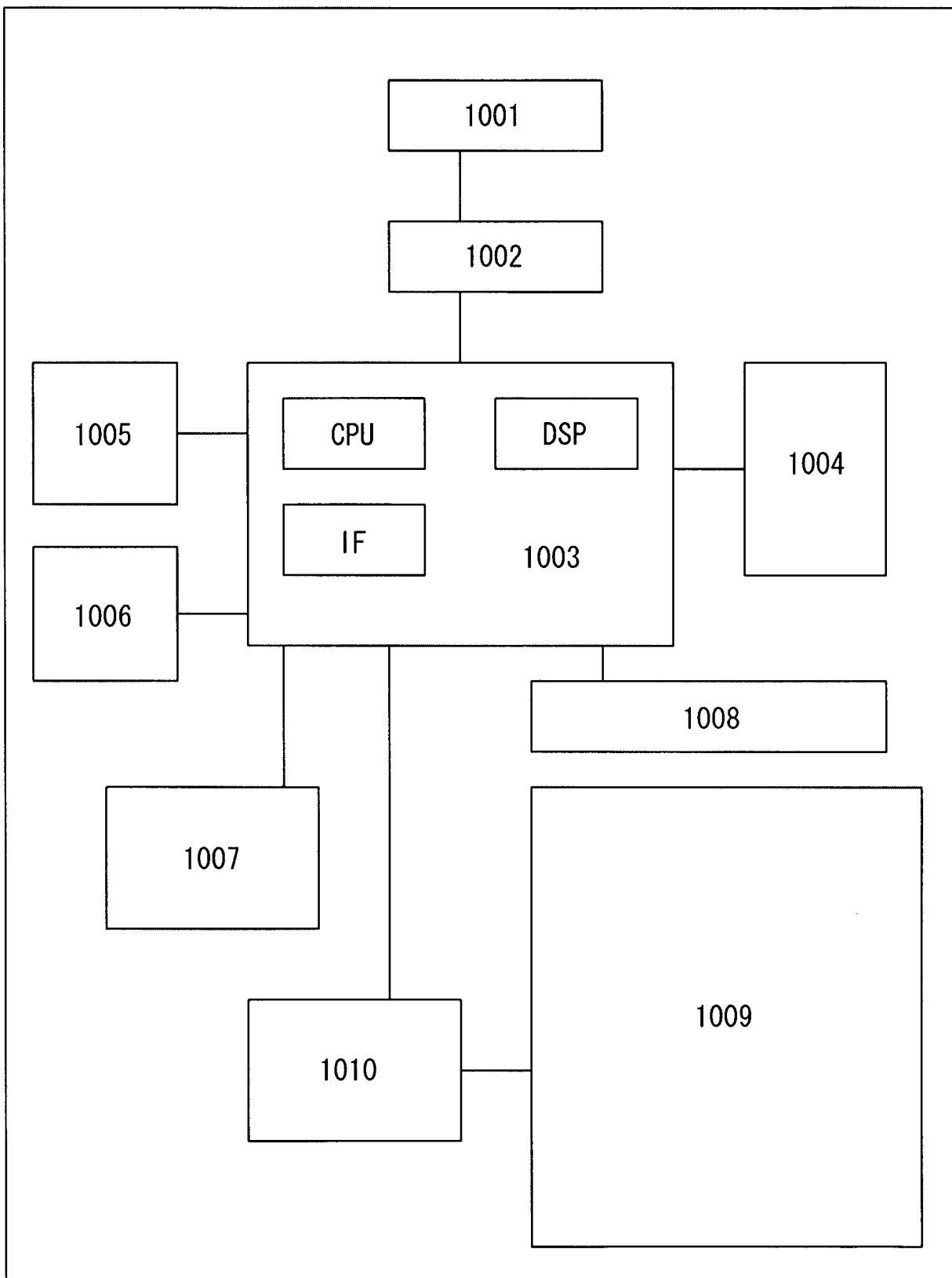

**[0023]** **Fig. 10** zeigt eine Ausführungsform einer Halbleitervorrichtung.

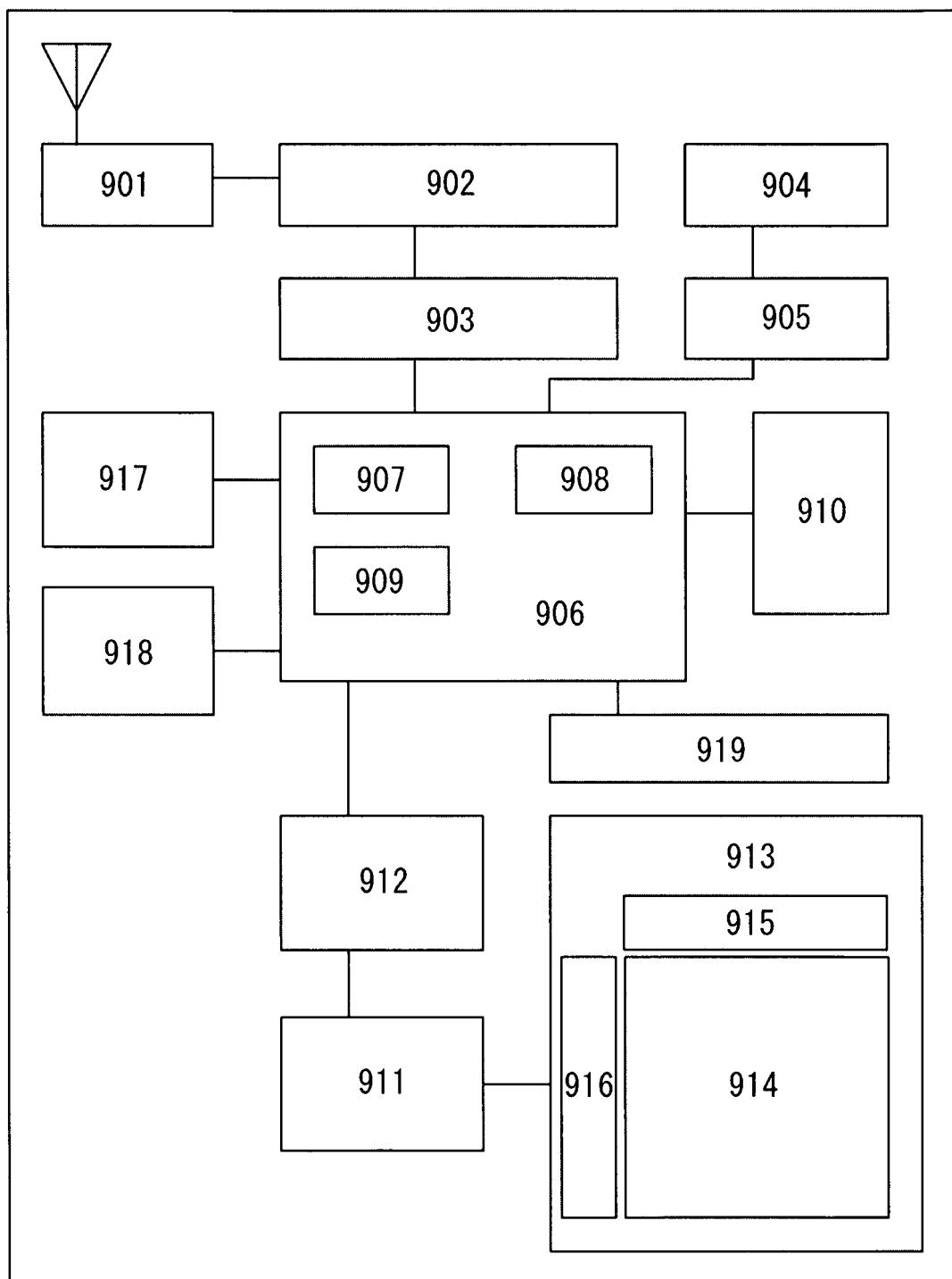

**[0024]** **Fig. 11** zeigt eine Ausführungsform einer Halbleitervorrichtung.

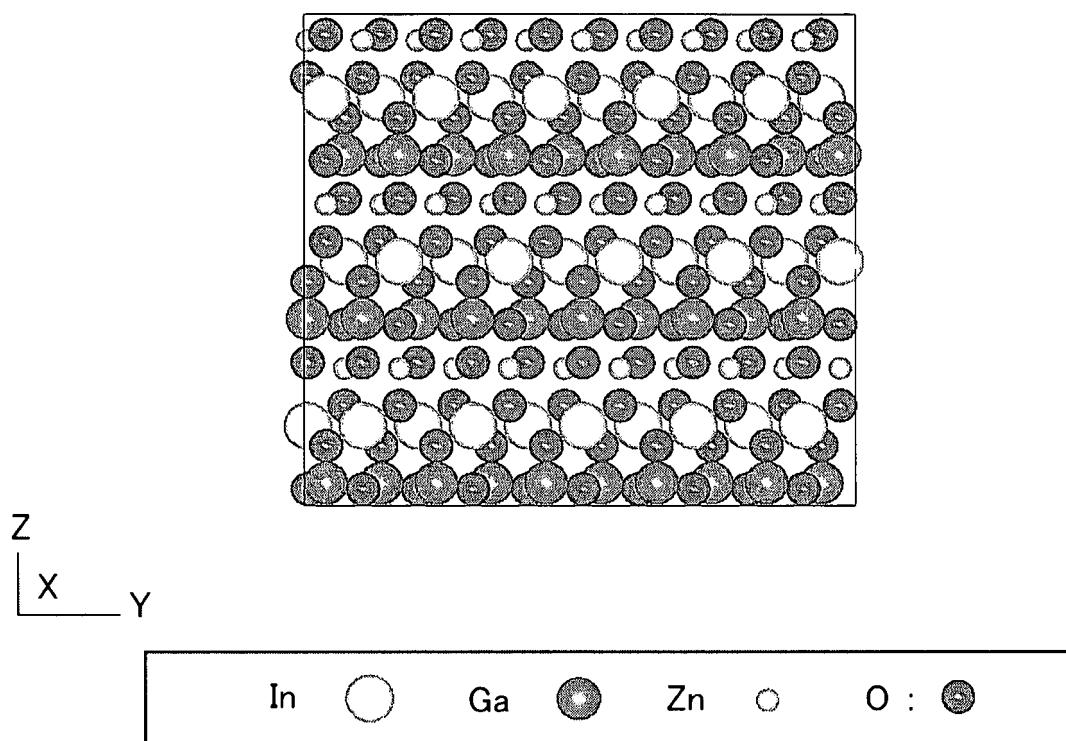

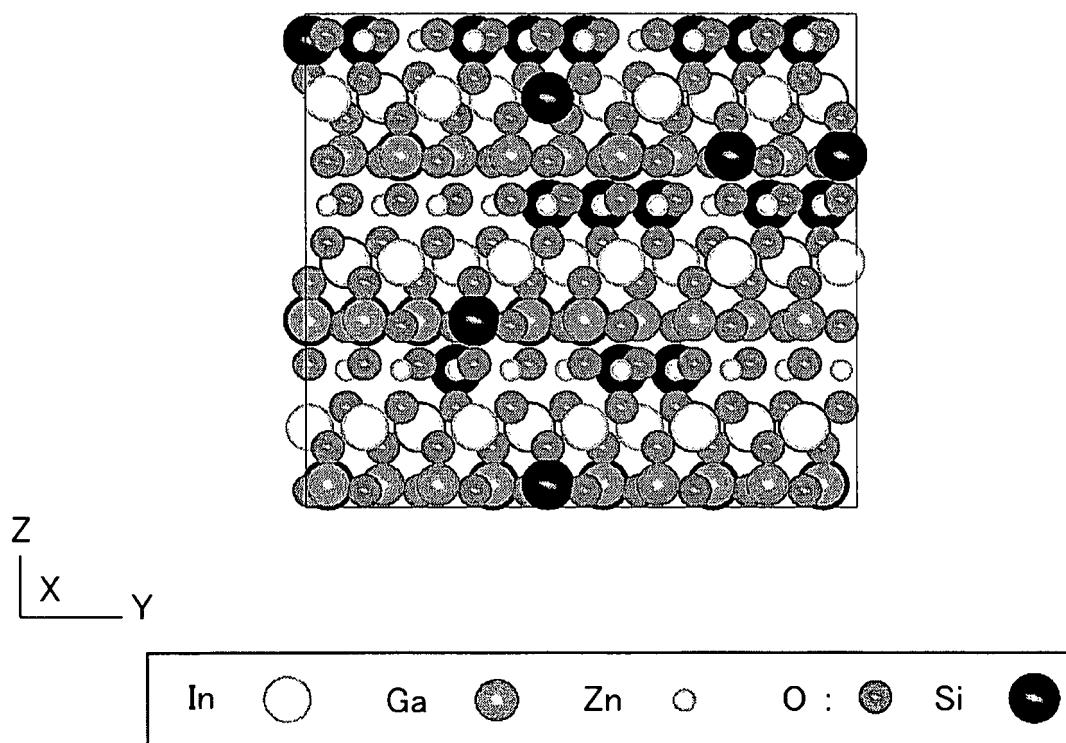

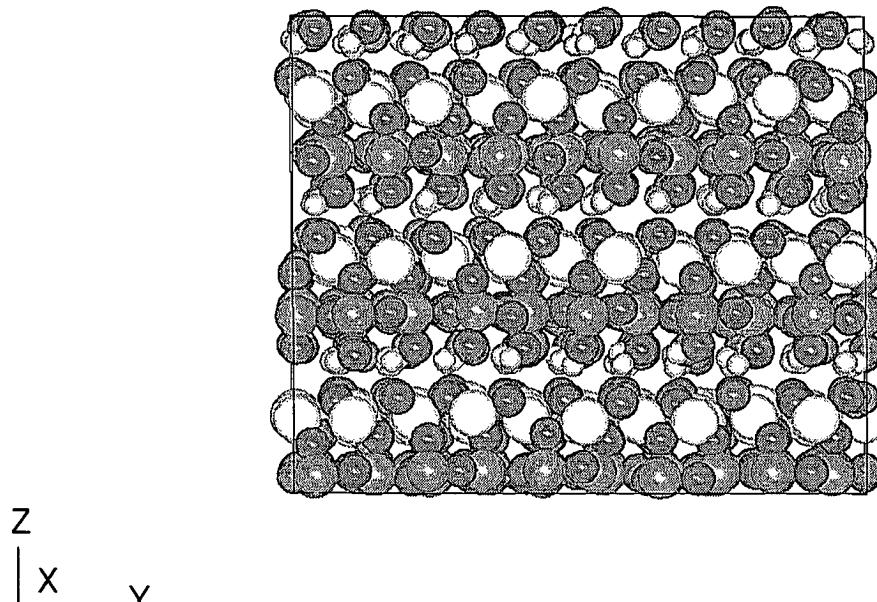

**[0025]** **Fig. 12A** und **Fig. 12B** sind Modelldiagramme für Berechnung.

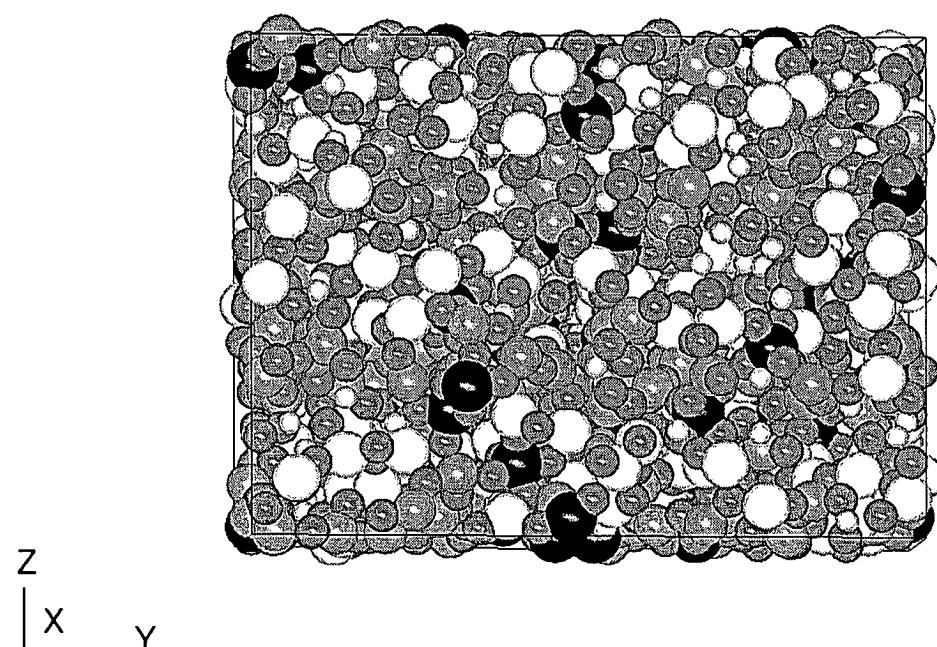

**[0026]** **Fig. 13A** und **Fig. 13B** sind Modelldiagramme für Berechnung.

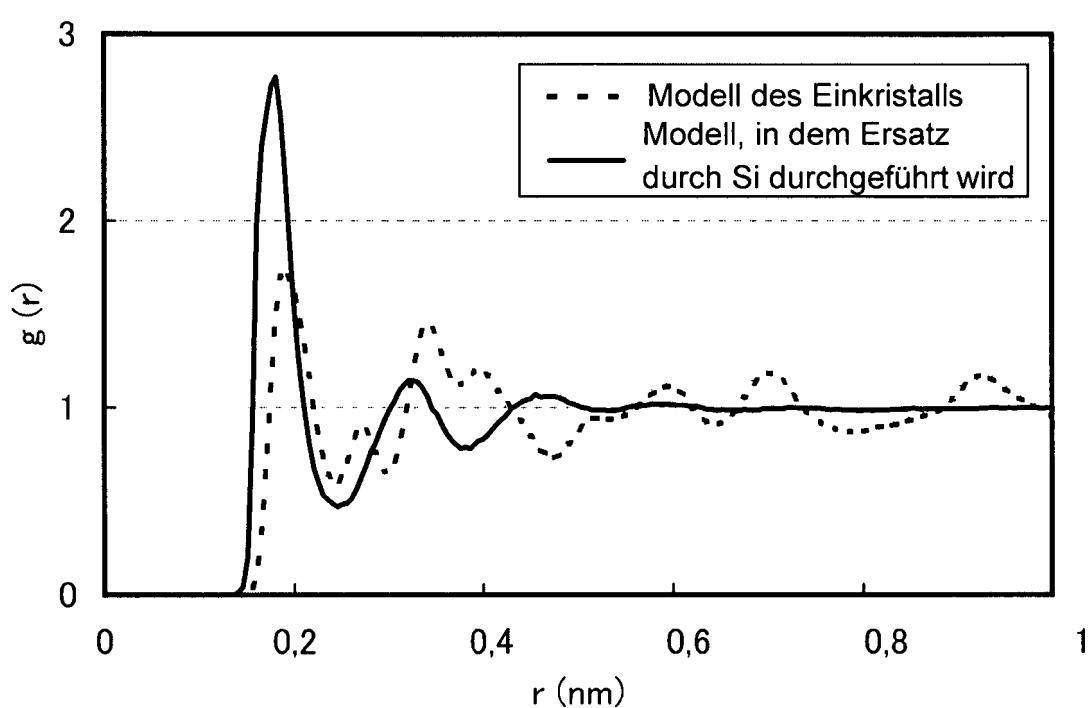

**[0027]** **Fig. 14** zeigt Berechnungsergebnisse.

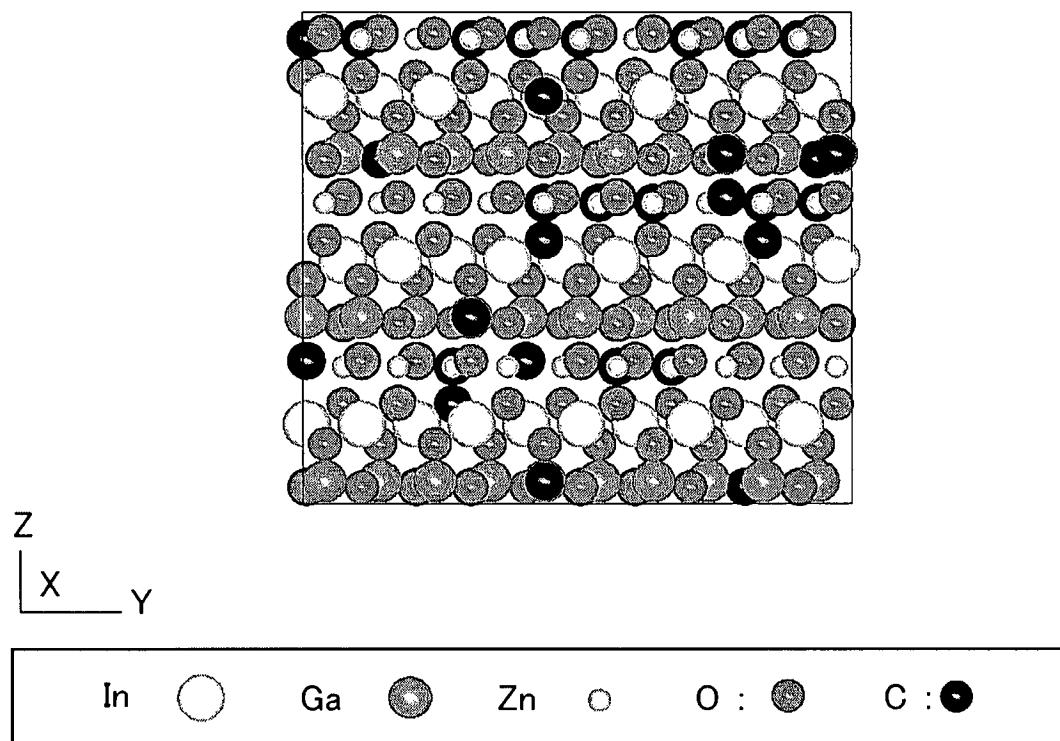

**[0028]** **Fig. 15A** und **Fig. 15B** sind Modelldiagramme für Berechnung.

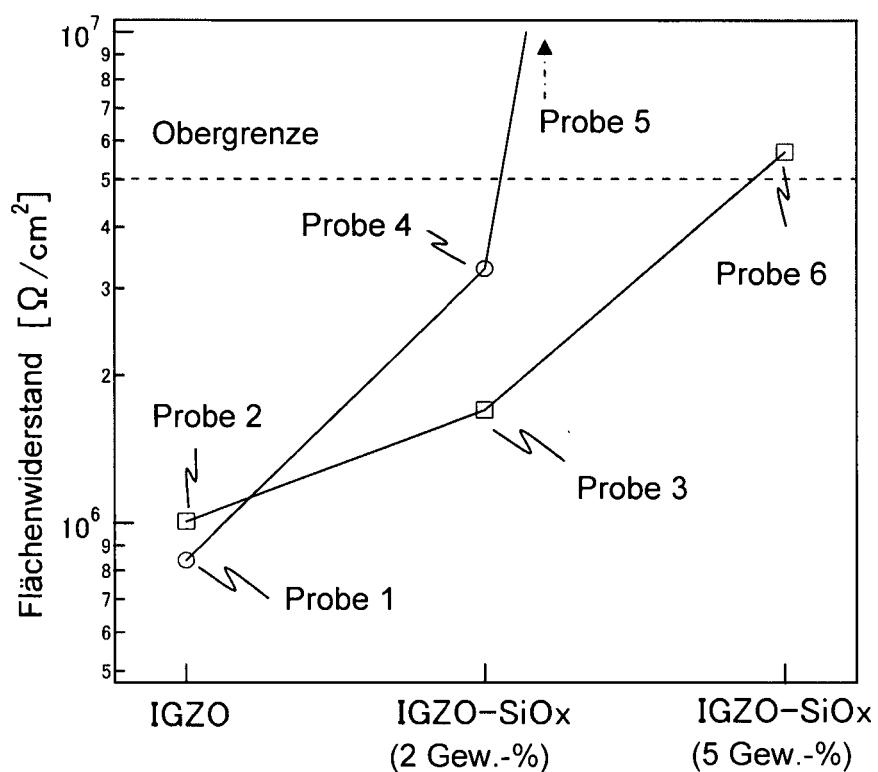

**[0029]** Fig. 16 zeigt Berechnungsergebnisse.

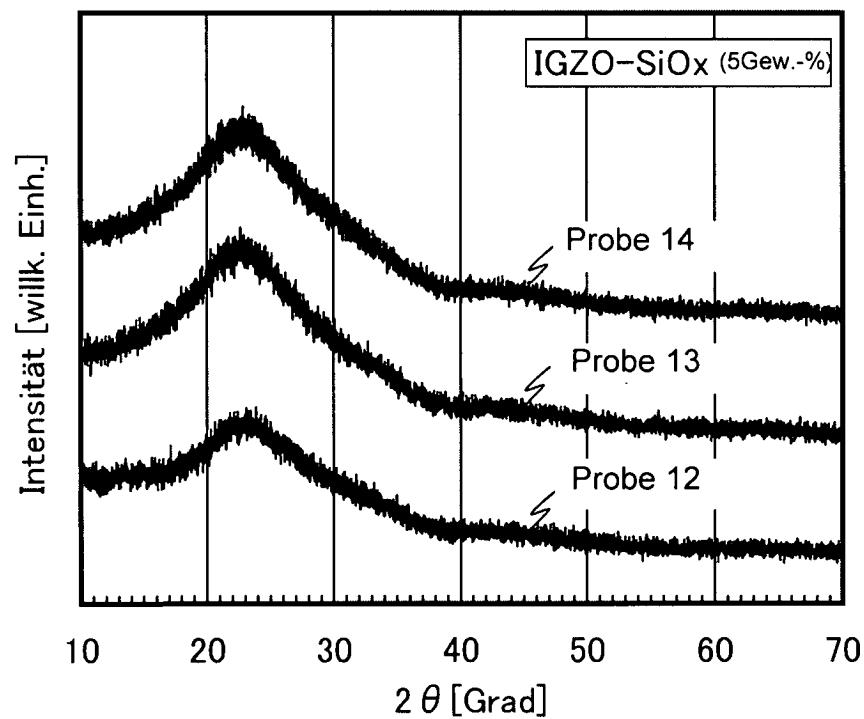

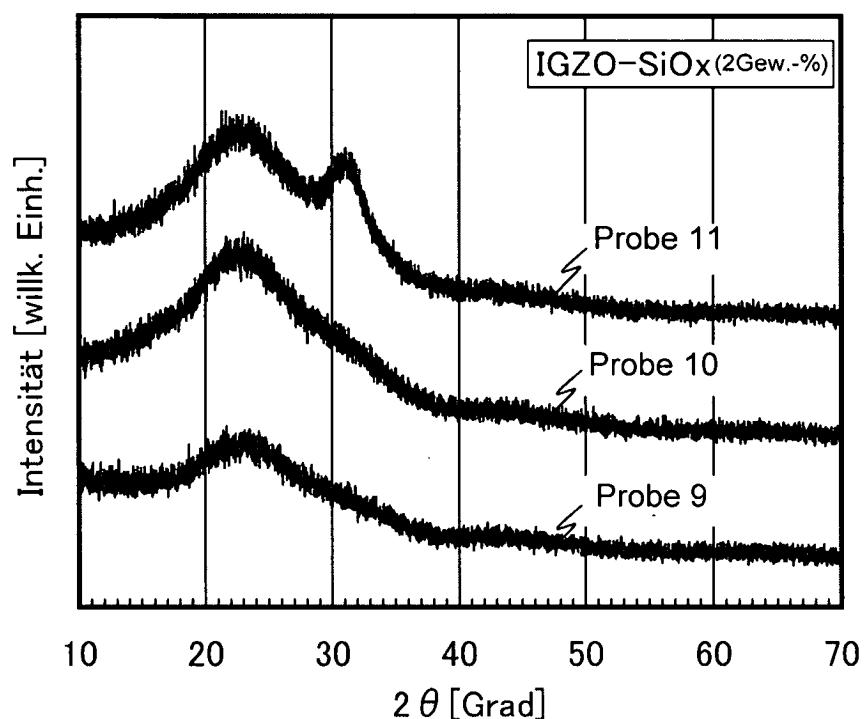

**[0030]** Fig. 17 zeigt Messergebnisse entsprechend dem Beispiel der vorliegenden Erfindung.

**[0031]** Fig. 18A und Fig. 18B zeigen Messergebnisse entsprechend dem Beispiel der vorliegenden Erfindung.

#### Beste Art zum Ausführen der Erfindung

**[0032]** Nachstehend werden Ausführungsformen der Erfindung, die in dieser Beschreibung offenbart wird, mit Bezug auf die beiliegenden Zeichnungen beschrieben. Es sei angemerkt, dass die vorliegende Erfindung nicht auf die folgende Beschreibung beschränkt ist und sich einem Fachmann auf dem einschlägigen Gebiet ohne Weiteres erschließt, dass Modi und Details auf verschiedene Weisen modifiziert werden können, ohne vom Wesen und Umfang der vorliegenden Erfindung abzugehen. Daher sollte die Erfindung nicht so verstanden werden, dass sie auf die Beschreibung bei den folgenden Ausführungsformen beschränkt ist.

**[0033]** Es sei angemerkt, dass die Position, die Größe, der Bereich oder dergleichen von jeder Struktur in den Zeichnungen und dergleichen in einigen Fällen für ein leichtes Verständnis nicht genau dargestellt ist. Die offenbare Erfindung ist daher nicht notwendigerweise auf die Position, die Größe, den Bereich oder dergleichen, die in den Zeichnungen und dergleichen offenbart ist, begrenzt.

**[0034]** In dieser Beschreibung und dergleichen werden Ordnungszahlen wie z. B. „erster“, „zweiter“ und „dritter“ verwendet, um eine Verwechslung von Komponenten zu vermeiden, wobei diese Begriffe die Komponenten numerisch nicht einschränken sollen.

**[0035]** Es sei angemerkt, dass in dieser Beschreibung und dergleichen der Begriff wie z. B. „über“ oder „unter“ nicht notwendig bedeutet, dass eine Komponente „direkt auf“ oder „direkt unter“ einer anderen Komponente angeordnet ist. Zum Beispiel kann der Ausdruck „eine Gate-Elektrode über einer Gate-Isolierschicht“ den Fall bedeuten, in dem zwischen der Gate-Isolierschicht und der Gate-Elektrode eine weitere Komponente angeordnet ist.

**[0036]** Darüber hinaus begrenzt in dieser Beschreibung und dergleichen der Begriff wie z. B. „Elektrode“ oder „Leitung“ keine Funktion einer Komponente. Beispielsweise wird eine „Elektrode“ bisweilen als Teil einer „Leitung“ verwendet, und umgekehrt. Des Weiteren kann der Begriff „Elektrode“ oder „Leitung“ denjenigen Fall beinhalten, in dem eine Vielzahl von „Elektroden“ oder „Leitungen“ auf integrierte Weise gebildet sind.

**[0037]** Funktionen von „Source“ und „Drain“ werden bisweilen gegeneinander ausgetauscht, wenn beispielsweise ein Transistor von entgegengesetzter Polarität verwendet wird oder wenn die Richtung des Stromflusses im Schaltungsbetrieb geändert wird. Somit können die Begriffe „Source“ und „Drain“ in dieser Beschreibung und dergleichen gegeneinander ausgetauscht werden.

**[0038]** Es sei angemerkt, dass in dieser Beschreibung und dergleichen der Begriff „elektrisch verbunden“ denjenigen Fall beinhaltet, in dem Komponenten durch ein Objekt verbunden sind, das eine beliebige elektrische Funktion aufweist. Es ist keine besondere Beschränkung hinsichtlich eines Objekts vorhanden, das eine beliebige elektrische Funktion aufweist, solange elektrische Signale zwischen Komponenten, die durch das Objekt verbunden sind, gesendet und empfangen werden können. Beispiele für ein „Objekt, das eine beliebige elektrische Funktion aufweist“, sind ein Schaltelement wie z. B. ein Transistor, ein Widerstand, eine Spule, ein Kondensator und ein Element mit einer Vielzahl von Funktionen wie auch eine Elektrode und eine Leitung.

#### (Ausführungsform 1)

**[0039]** Bei dieser Ausführungsform werden eine Ausführungsform einer Halbleitervorrichtung und eine Ausführungsform eines Verfahrens zum Herstellen der Halbleitervorrichtung anhand von Fig. 1A, Fig. 1B und Fig. 2A bis Fig. 2D beschrieben.

**<Beispiel für eine Struktur einer Halbleitervorrichtung>**

**[0040]** Als Beispiel für eine Halbleitervorrichtung ist ein Transistor mit obenliegendem Gate (top-gate transistor) in Fig. 1A und Fig. 1B gezeigt. Fig. 1A ist eine Draufsicht, und Fig. 1B ist eine Querschnittsansicht entlang der gestrichelten Linie X1-Y1 in Fig. 1A. Es sei angemerkt, dass einige Komponenten eines Transistors 150 (z. B. ein Gate-Isolierfilm 110) der Einfachheit halber in Fig. 1A wegfallen.

**[0041]** Der Transistor **150** in **Fig. 1A** und **Fig. 1B** beinhaltet über einem Substrat **102** einen Basis-Isolierfilm **104**, einen Oxidhalbleiterfilm **106**, der über dem Basis-Isolierfilm **104** ausgebildet ist und einen Bereich **106a** und einen Bereich **106b** aufweist, eine Source-Elektrode **108a** und eine Drain-Elektrode **108b**, die über dem Basis-Isolierfilm **104** und dem Oxidhalbleiterfilm **106** ausgebildet sind, den Gate-Isolierfilm **110**, der über dem Oxidhalbleiterfilm **106**, der Source-Elektrode **108a** und der Drain-Elektrode **108b** ausgebildet ist, und eine Gate-Elektrode **112**, die in Kontakt mit dem Gate-Isolierfilm **110** steht und zumindest mit dem Oxidhalbleiterfilm **106** überlappt. Außerdem ist ein Zwischenschicht-Isolierfilm **114** über dem Transistor **150** ausgebildet.

**[0042]** Die Dicke des Oxidhalbleiterfilms **106** ist größer als 5 nm und kleiner als oder gleich 200 nm, bevorzugt größer als oder gleich 10 nm und kleiner als oder gleich 30 nm. Außerdem hat der Oxidhalbleiterfilm **106** vorzugsweise eine Struktur mit Kristallinität (z. B. eine Einkristallstruktur, eine mikrokristalline Struktur oder dergleichen).

**[0043]** Wie in **Fig. 1B** gezeigt ist, verjüngt sich vorzugsweise ein Endbereich des Oxidhalbleiterfilms **106** unter einem Winkel von 20° bis 50°. Wenn der Oxidhalbleiterfilm **106** einen senkrechten Endbereich hat, wird Sauerstoff mit höherer Wahrscheinlichkeit von dem Endbereich des Oxidhalbleiterfilms **106** abgegeben; somit werden wahrscheinlich Sauerstofffehlstellen (oxygen vacancies) erzeugt. Wenn der Oxidhalbleiterfilm **106** einen sich verjüngenden Endbereich hat, wird eine Erzeugung von Sauerstofffehlstellen unterdrückt, und daher kann eine Erzeugung von Leckstrom des Transistors **150** verringt werden.

**[0044]** Bei dieser Ausführungsform ist der Oxidhalbleiterfilm **106** vorzugsweise ein Film aus einem kristallinen Oxidhalbleiter mit Ausrichtung bezüglich der c-Achse (c-axis aligned crystalline oxide semiconductor film: CAAC-OS-Film). Es sei angemerkt, dass der CAAC-OS-Film später ausführlich bei einem Herstellungsverfahren des Transistors **150** beschrieben wird.

**[0045]** Für den Gate-Isolierfilm **110** wird vorzugsweise ein Oxid, das Silizium enthält und eine ausreichende Spannungsfestigkeit (withstand voltage) und ausreichende isolierende Eigenschaften aufweist, verwendet. In dem Fall, in dem der Gate-Isolierfilm **110** eine einschichtige Struktur hat, kann beispielsweise ein Isolierfilm wie z. B. ein Siliziumoxidfilm verwendet werden.

**[0046]** Alternativ kann der Gate-Isolierfilm **110** eine gestapelte Struktur aufweisen. In dem Fall, in dem der Gate-Isolierfilm **110** eine gestapelte Struktur aufweist, kann ein Oxid, das Silizium enthält, über einem Galliumoxid, einem Aluminiumoxid, einem Siliziumnitrid, einem Siliziumoxynitrid, einem Aluminiumoxynitrid, einem Yttriumoxid, einem Lanthanoxid, einem Siliziumnitridoxid oder dergleichen gestapelt werden. Alternativ kann ein Oxid, das Silizium enthält, über einem Material mit hohem k, wie z. B. Hafniumoxid, Hafniumsilikat ( $\text{HfSi}_x\text{O}_y$  ( $x > 0, y > 0$ )), Hafniumsilikat, dem Stickstoff zugesetzt worden ist ( $\text{HfSiO}_x\text{N}_y$  ( $x > 0, y > 0$ )) oder Hafniumaluminat ( $\text{HfAl}_x\text{O}_y$  ( $x > 0, y > 0$ )) gestapelt werden.

**[0047]** Im Fall der Verwendung eines Oxides, das Silizium enthält, als der Gate-Isolierfilm **110** kann ein Teil des enthaltenen Sauerstoffs von dem Isolierfilm abgegeben werden, wenn der Isolierfilm erwärmt wird. Daher kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, und Sauerstofffehlstellen in dem Oxidhalbleiterfilm **106** können gefüllt werden. Insbesondere enthält vorzugsweise der Gate-Isolierfilm **110** eine große Menge an Sauerstoff, die zumindest seine Stöchiometrie überschreitet. Beispielsweise wird ein Film von Siliziumoxid, das durch die Formel  $\text{SiO}_{2+\alpha}$  ( $\alpha > 0$ ) dargestellt wird, vorzugsweise als der Gate-Isolierfilm **110** verwendet. Wenn ein derartiger Siliziumoxidfilm als der Gate-Isolierfilm **110** verwendet wird, kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, so dass der Transistor **150**, bei dem der Oxidhalbleiterfilm **106** verwendet wird, vorteilhafte Transistoreigenschaften aufweisen kann.

**[0048]** Jedoch könnte im Fall der Verwendung eines Siliziumoxidfilms als der Gate-Isolierfilm **110** Silizium, das ein Bestandteil des Gate-Isolierfilms **110** ist, als Verunreinigung in den Oxidhalbleiterfilm **106** aufgenommen werden. Silizium oder dergleichen, das ein Bestandteil des Gate-Isolierfilms **110** ist, dringt in den Oxidhalbleiterfilm **106** ein und dient als Verunreinigung, die die Eigenschaften des Transistors beeinflusst.

**[0049]** Ferner dringt in dem Fall, in dem der Oxidhalbleiterfilm **106** ein CAAC-OS-Film ist, Silizium oder dergleichen, das ein Bestandteil des Gate-Isolierfilms **110** ist, in den Oxidhalbleiterfilm **106** ein, und eine Bindung in dem Kristallbereich in dem Oxidhalbleiterfilm **106** wird aufgebrochen. Deshalb werden mehr amorphe Bereiche in dem Oxidhalbleiterfilm **106** in der Nähe des Gate-Isolierfilms **110** ausgebildet.

**[0050]** Insbesondere dringen wahrscheinlich Verunreinigungen wie z. B. Silizium in den Oxidhalbleiterfilm **106** in der Nähe des Gate-Isolierfilms **110** ein. Ein Kanalbildungsbereich des Transistors **150** wird in dem Oxidhal-

leiterfilm **106** in der Nähe der Grenzfläche zu dem Gate-Isolierfilm **110** ausgebildet; somit könnten die Eigenschaften des Transistors **150** verändert werden, wenn Verunreinigungen wie z. B. Silizium in die Nähe der Grenzfläche zwischen dem Oxidhalbleiterfilm **106** und dem Gate-Isolierfilm **110** eindringen.

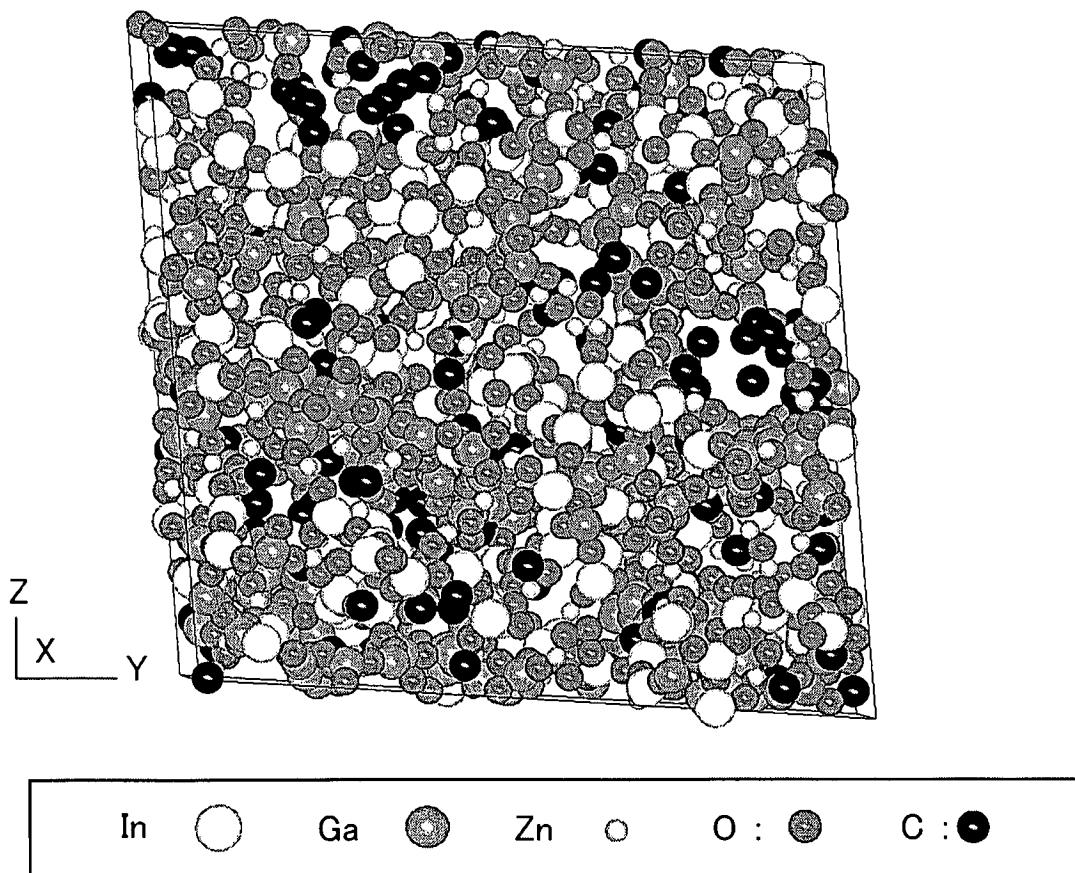

**[0051]** Die Veränderung der Struktur des Oxidhalbleiterfilms **106**, die auftritt, wenn  $\text{SiO}_2$ , ein Oxid, das Silizium enthält, als Verunreinigung zugesetzt wird, wurde durch klassische Moleküldynamikrechnung (classical molecular dynamics calculation) untersucht. Die Ergebnisse werden anhand von **Fig. 12A**, **Fig. 12B**, **Fig. 13A**, **Fig. 13B** und **Fig. 14** beschrieben. Es sei angemerkt, dass eine Simulationssoftware „SCIGRESS ME“, die von Fujitsu Limited hergestellt wird, für die klassische Moleküldynamikrechnung verwendet wurde. Ein empirisches Potential, das die Wechselwirkung zwischen Atomen charakterisiert, wird bei dem klassischen Moleküldynamikverfahren definiert, so dass die Kraft, die auf jedes Atom einwirkt, geschätzt wird. Newtonsches Gesetz der Bewegung wird numerisch gelöst, wodurch Bewegung (zeitabhängige Veränderung (time-dependent change)) jedes Atoms deterministisch verfolgt werden kann.

**[0052]** Nachstehend werden Berechnungsmodelle und Berechnungsbedingungen beschrieben. Es sei angemerkt, dass in dieser Berechnung das Born-Mayer-Huggins-Potential verwendet wurde.

**[0053]** Eine Einkristallstruktur von  $\text{InGaZnO}_4$ , das 1680 Atome hat (siehe **Fig. 12A**) und eine Struktur von  $\text{InGaZnO}_4$ , das 1680 Atome hat, wobei 20 Atome eines jeden von In, Ga und Zn durch Silizium-(Si-)Atome ersetzt werden (Siehe **Fig. 12B**), wurden als Berechnungsmodelle ausgebildet. In dem Modell in **Fig. 12B**, in dem Ersatz durch Silizium (Si) durchgeführt wird, sind Siliziumatome mit 3,57 Atom-% (2,34 Gew.-%) enthalten. Ferner ist die Dichte des Modells des Einkristalls in **Fig. 12A**  $6,36 \text{ g/cm}^3$ , und die Dichte des Modells in **Fig. 12B**, in dem Ersatz durch Si durchgeführt wird, ist  $6,08 \text{ g/cm}^3$ .

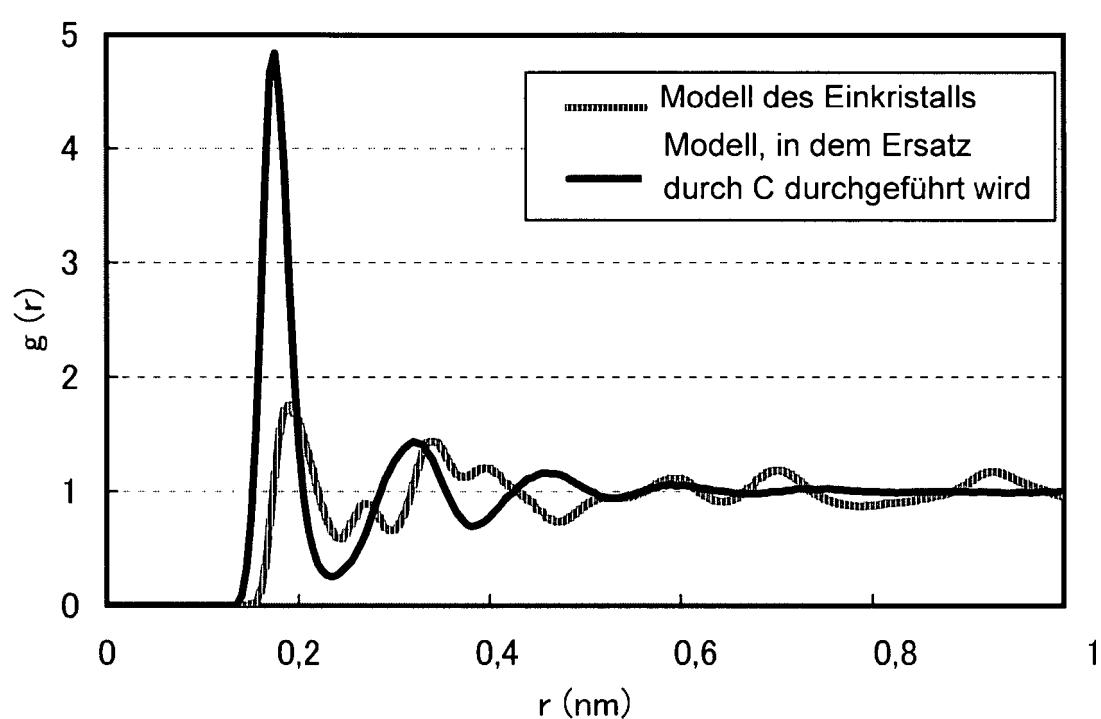

**[0054]** Bei  $1727^\circ\text{C}$ , was niedriger als der Schmelzpunkt des  $\text{InGaZnO}_4$ -Einkristalls ist (ca.  $2000^\circ\text{C}$  laut der Schätzung durch die klassische Moleküldynamikrechnung), wurde eine Strukturentspannung 150 ps lang (Zeitschrittbreite  $0,2 \text{ fs} \times 750000$  Schritte) mit einem konstanten Druck (1 Atom) an den Berechnungsmodellen in **Fig. 12A** und **Fig. 12B** durch die klassische Moleküldynamikrechnung durchgeführt. Die radialen Verteilungsfunktionen  $g(r)$  der zwei Strukturen wurden berechnet. Es sei angemerkt, dass die radiale Verteilungsfunktion  $g(r)$  eine Funktion ist, die die Wahrscheinlichkeitsdichte von Atomen darstellt, die in einer Entfernung von  $r$  von einem Atom existieren. Wenn die Korrelation zwischen Atomen verschwindet, nähert sich  $g(r)$  an 1 an.

**[0055]** **Fig. 13A** und **Fig. 13B** zeigen letzte Strukturen, die durch die klassische Moleküldynamikrechnung an den obigen zwei Berechnungsmodellen für 150 ps erhalten wurden. Zusätzlich zeigt **Fig. 14** die radiale Verteilungsfunktion  $g(r)$  bei jeder Struktur.

**[0056]** Das Modell des Einkristalls in **Fig. 13A** ist stabil und bewahrt die Kristallstruktur auch bei der letzten Struktur, während das Modell in **Fig. 13B**, in dem Ersatz durch Si durchgeführt wird, instabil ist. Es kann beobachtet werden, dass die Kristallstruktur mit der Zeit verzerrt wird und sich in eine amorphe Struktur verändert. Wenn die radialen Verteilungsfunktionen  $g(r)$  der Strukturmodelle in **Fig. 14** miteinander verglichen werden, findet man, dass das Einkristallmodell auch in einer großen Entfernung Peaks aufweist und eine Fernordnung (long-range order) aufweist. Im Gegensatz dazu findet man, dass in dem Modell, in dem Ersatz durch Si durchgeführt wird, der Peak in einer Entfernung von 0,6 nm verschwindet, und das Modell, in dem Ersatz durch Si durchgeführt wird, keine Fernordnung aufweist.

**[0057]** Die obigen Berechnungsergebnisse deuten darauf hin, dass dann, wenn Silizium (Si) in  $\text{InGaZnO}_4$  enthalten ist,  $\text{InGaZnO}_4$  wahrscheinlich amorph wird. Ferner wird derartiges  $\text{InGaZnO}_4$  laut der obigen Ergebnisse nicht kristallisiert, auch wenn  $\text{InGaZnO}_4$ , das Silizium (Si) enthält, bei hoher Temperatur erwärmt wird.

**[0058]** Dann wurde eine Veränderung der Struktur des Oxidhalbleiterfilms **106**, die auftritt, wenn Kohlenstoffatome (C) zugesetzt werden, durch die klassische Moleküldynamikrechnung untersucht. Die Ergebnisse werden anhand von **Fig. 12A**, **Fig. 15A**, **Fig. 15B** und **Fig. 16** beschrieben. Es sei angemerkt, dass die Simulationssoftware „SCIGRESS ME“, die von Fujitsu Limited hergestellt wird, für die klassische Moleküldynamikrechnung verwendet wurde.

**[0059]** Berechnungsmodelle und Berechnungsbedingungen sind wie folgt. Es sei angemerkt, dass in dieser Berechnung das Born-Mayer-Huggins-Potential verwendet wurde. Des Weiteren wurde für die Wechselwirkung zwischen Kohlenstoffatomen (C) ein Lennard-Jones-Potential verwendet.

**[0060]** Eine Einkristallstruktur von  $\text{InGaZnO}_4$ , das 1680 Atome hat (siehe **Fig. 12A**) und eine Struktur von  $\text{InGaZnO}_4$ , das 1680 Atome hat, wobei 20 Atome eines jeden von In, Ga und Zn durch Kohlenstoffatome (C) ersetzt werden und 80 Atome von Sauerstoff (O) durch Kohlenstoffatome (C) ersetzt werden (siehe **Fig. 15A**), wurden als Berechnungsmodelle ausgebildet. In dem Modell in **Fig. 15A**, in dem Ersatz durch C durchgeführt wird, sind Kohlenstoffatome (C) mit 8,33 Atom-% enthalten. Ferner ist die Dichte des Modells des Einkristalls in **Fig. 12A** 6,36 g/cm<sup>3</sup>, und die Dichte des Modells in **Fig. 15A**, in dem Ersatz durch C durchgeführt wird, ist 5,89 g/cm<sup>3</sup>.

**[0061]** Bei 1727°C, was niedriger als der Schmelzpunkt des  $\text{InGaZnO}_4$ -Einkristalls ist (ca. 2000°C laut der Schätzung durch die klassische Moleküldynamikrechnung), wurde eine Strukturentspannung 150 ps lang (Zeitschrittbreite 0,2 fs × 750000 Schritte) mit einem konstanten Druck (1 Atom) an den Berechnungsmodellen in **Fig. 12A** und **Fig. 15A** durch die klassische Moleküldynamikrechnung durchgeführt. Die radialen Verteilungsfunktionen  $g(r)$  der zwei Strukturen wurden gerechnet. Es sei angemerkt, dass die radiale Verteilungsfunktion  $g(r)$  eine Funktion ist, die die Wahrscheinlichkeitsdichte von Atomen darstellt, die in einer Entfernung von  $r$  von einem Atom existieren. Wenn die Korrelation zwischen Atomen verschwindet, nähert sich  $g(r)$  an 1 an.

**[0062]** **Fig. 13A** und **Fig. 15B** zeigen letzte Strukturen, die durch die klassische Moleküldynamikrechnung an den obigen zwei Berechnungsmodellen für 150 ps erhalten wurden. Die radiale Verteilungsfunktion  $g(r)$  bei jeder Struktur ist in **Fig. 16** gezeigt.

**[0063]** Das Modell des Einkristalls in **Fig. 13A** ist stabil und bewahrt die Kristallstruktur auch bei der letzten Struktur, während das Modell in **Fig. 15B**, in dem Ersatz durch C durchgeführt wird, instabil ist. Es kann beobachtet werden, dass die Kristallstruktur mit der Zeit verzerrt wird und sich in eine amorphe Struktur verändert. Durch Vergleichen der radialen Verteilungsfunktionen  $g(r)$  der Strukturmodelle miteinander wie in **Fig. 16** findet man, dass das Einkristallmodell auch in einer großen Entfernung Peaks aufweist und die Fernordnung aufweist. Im Gegensatz dazu findet man, dass in dem Modell, in dem Ersatz durch C durchgeführt wird, der Peak in einer Entfernung von 0,7 nm verschwindet, und das Modell, in dem Ersatz durch C durchgeführt wird, keine Fernordnung aufweist.

**[0064]** Die obigen Berechnungsergebnisse deuten darauf hin, dass dann, wenn Kohlenstoff (C) in  $\text{InGaZnO}_4$  enthalten ist,  $\text{InGaZnO}_4$  wahrscheinlich amorph wird. Ferner wird derartiges  $\text{InGaZnO}_4$  laut der obigen Ergebnisse nicht kristallisiert, auch wenn  $\text{InGaZnO}_4$ , das Kohlenstoff (C) enthält, bei hoher Temperatur erwärmt wird.

**[0065]** Daher wird in der Halbleitervorrichtung, die bei dieser Ausführungsform beschrieben wird, das Eindringen von Verunreinigungen wie z. B. Silizium in den Oxidhalbleiterfilm **106** in der Nähe der Grenzfläche zu dem Gate-Isolierfilm **110** unterdrückt. Folglich wird in dem Oxidhalbleiterfilm **106** ein Bereich ausgebildet, in dem die Konzentration von Silizium, das von einer Grenzfläche zu dem Gate-Isolierfilm **110** zum Inneren des Oxidhalbleiterfilms **106** hin verteilt ist, niedriger als oder gleich 1,0 Atom-% ist. Ein derartiger Bereich wird wie in **Fig. 1B** ein Bereich **106a** genannt. Die Siliziumkonzentration in dem Bereich **106a** ist stärker bevorzugt niedriger als oder gleich 0,1 Atom-%. Außerdem wird der Bereich **106a** in Kontakt mit dem Gate-Isolierfilm **110** bereitgestellt und hat eine Dicke von kleiner als oder gleich 5 nm.

**[0066]** Es sei angemerkt, dass, wie in **Fig. 1B**, ein Bereich in dem Oxidhalbleiterfilm **106**, der verschieden von dem Bereich **106a** ist, ein Bereich **106b** genannt wird.

**[0067]** In dem Fall, in dem ferner Verunreinigungen wie z. B. Kohlenstoff in dem Gate-Isolierfilm **110** enthalten sind, könnten solche Verunreinigungen auch in den Oxidhalbleiterfilm **106** eindringen und dienen als Verunreinigungen, wie beim Fall von Silizium. In diesem Fall ist die Konzentration von Kohlenstoff in dem Bereich **106a** niedriger als oder gleich  $1,0 \times 10^{20}$  Atome/cm<sup>3</sup>, bevorzugt niedriger als oder gleich  $1,0 \times 10^{19}$  Atome/cm<sup>3</sup>.

**[0068]** Um zu verhindern, dass Verunreinigungen wie z. B. Silizium in den Oxidhalbleiterfilm **106** eindringen, kann der Gate-Isolierfilm derart ausgebildet werden, dass der Oxidhalbleiterfilm **106** nicht beschädigt wird. In dem Fall, in dem beispielsweise ein Siliziumoxidfilm als der Gate-Isolierfilm **110** durch ein Sputterverfahren ausgebildet wird, kann die Auswirkung von Silizium (das ein Bestandteil des Gate-Isolierfilms **110** ist), das mit dem Oxidhalbleiterfilm **106** kollidiert, verringert werden. Damit man den obigen Effekt erzielen kann, kann man beispielsweise das Folgende verwenden: ein Verfahren, bei dem die Leistung zur Abscheidung des Gate-Isolierfilms **110** niedrig ist, ein Verfahren, bei dem der Druck zur Abscheidung des Gate-Isolierfilms **110** hoch ist, ein Verfahren, bei dem eine Distanz zwischen einem Target und einem Substrat (T-S-Distanz) bei der Abscheidung des Gate-Isolierfilms **110** verlängert wird, oder dergleichen. Jedoch ist ein Verfahren zum Ausbilden des Gate-Isolierfilms **110** nicht auf die obigen Verfahren beschränkt. Beispielsweise kann ein Siliziumoxidfilm, ein

Siliziumoxynitridfilm, ein Siliziumnitridoxidfilm oder dergleichen, der durch ein PE-CVD-Verfahren ausgebildet wird, verwendet werden. Ein PE-CVD-Verfahren wird gegenüber einem Sputterverfahren bevorzugt, weil unter Verwendung des PE-CVD-Verfahrens der Oxidhalbleiterfilm **106**, der als Basisfilm dient, weniger beschädigt wird.

**[0069]** Wie oben beschrieben worden ist, wird die Konzentration von Verunreinigungen wie z. B. Silizium und Kohlenstoff, die in den Bereich **106a** in dem Oxidhalbleiterfilm **106** eindringen, verringert, wodurch eine Veränderung der Eigenschaften des Transistors **150** unterdrückt werden kann. Ferner kann in dem Fall, in dem der Oxidhalbleiterfilm **106** ein CAAC-OS-Film ist, ein Kristallbereich auch in der Nähe des Gate-Isolierfilms **110** ausgebildet werden. Wenn der Transistor **150** unter Verwendung eines derartigen Oxidhalbleiterfilms **106** ausgebildet wird, kann eine Halbleitervorrichtung mit stabilen elektrischen Eigenschaften bereitgestellt werden.

**[0070]** Es sei angemerkt, dass die Details der anderen Komponenten des Transistors anhand von **Fig. 2A** bis **Fig. 2D** beim Beschreiben eines Verfahrens zum Herstellen des Transistors **150** nachstehend beschrieben werden.

#### <Herstellungsverfahren des Transistors **150**>

**[0071]** Nachstehend wird ein Beispiel für ein Verfahren zum Herstellen des Transistors **150** in **Fig. 1A** und **Fig. 1B** dieser Ausführungsform anhand von **Fig. 2A** bis **Fig. 2D** beschrieben.

**[0072]** Zuerst wird das Substrat **102** vorbereitet. Es gibt zwar keine bestimmte Begrenzung auf ein Substrat, das als das Substrat **102** verwendet werden kann, es ist jedoch nötig, dass das Substrat Wärmebeständigkeit aufweist, mit der es später zumindest eine Wärmebehandlung aushalten kann. Beispielsweise kann ein Glassubstrat wie z. B. ein Bariumborosilikatglassubstrat oder ein Alumoborosilikatglassubstrat, ein Keramiksubstrat, ein Quarzsubstrat, ein Saphirsubstrat oder dergleichen verwendet werden. Alternativ kann ein einkristallines Halbleitersubstrat oder ein polykristallines Halbleitersubstrat aus Silizium oder Siliziumkarbid, ein Verbund-Halbleitersubstrat aus Siliziumgermanium oder dergleichen, ein SOI-Substrat oder dergleichen verwendet werden.

**[0073]** Ein flexibles Substrat kann als das Substrat **102** verwendet werden. Im Fall der Verwendung eines flexiblen Substrats kann ein Transistor, der den Oxidhalbleiterfilm **106** beinhaltet, direkt über dem flexiblen Substrat ausgebildet werden. Alternativ kann ein Transistor, der den Oxidhalbleiterfilm **106** beinhaltet, über einem anderen Substrat ausgebildet werden und dann kann der Transistor abgetrennt und zu einem flexiblen Substrat versetzt werden. Damit man den Transistor von dem Substrat abtrennen und zu dem flexiblen Substrat versetzen kann, kann eine Trennschicht zwischen dem Substrat und dem Transistor, der den Oxidhalbleiterfilm **106** beinhaltet, angeordnet werden.

**[0074]** Als Nächstes wird der Basis-Isolierfilm **104** über dem Substrat **102** ausgebildet (siehe **Fig. 2A**). Der Basis-Isolierfilm **104** hat einen Effekt, dass er die Diffusion eines Verunreinigungselementes wie z. B. Wasserstoff oder Feuchtigkeit aus dem Substrat **102** verhindert, und kann mit einer einschichtigen Struktur oder einer gestapelten Struktur, die einen oder mehrere von einem Siliziumnitridfilm, einem Siliziumoxidfilm, einem Siliziumnitridoxidfilm und einem Siliziumoxynitridfilm verwendet, ausgebildet werden.

**[0075]** Darüber hinaus kann als anderer Effekt des Basis-Isolierfilms **104** Sauerstoff zu dem später ausgebildeten Oxidhalbleiterfilm **106** zugeführt werden. Beispielsweise kann in dem Fall, in dem ein Isolierfilm, der ein Oxid enthält, als der Basis-Isolierfilm **104** ausgebildet wird, ein Teil enthaltenen Sauerstoffs durch Erwärmung des Basis-Isolierfilms **104** abgegeben werden. Daher kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, und Sauerstofffehlstellen in dem Oxidhalbleiterfilm **106** können somit gefüllt werden. Insbesondere enthält vorzugsweise der Basis-Isolierfilm **104** eine große Menge an Sauerstoff, die zumindest seine Stöchiometrie überschreitet. Beispielsweise wird ein Film von Siliziumoxid, das durch die Formel  $\text{SiO}_{2+\alpha}$  ( $\alpha > 0$ ) dargestellt wird, vorzugsweise als der Basis-Isolierfilm **104** verwendet. Wenn ein derartiger Siliziumoxidfilm als der Basis-Isolierfilm **104** verwendet wird, kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, so dass der Transistor **150**, bei dem der Oxidhalbleiterfilm **106** verwendet wird, vorteilhafte Transistoreigenschaften aufweisen kann.

**[0076]** Bevor der Basis-Isolierfilm **104** ausgebildet wird, kann eine Plasmabehandlung oder dergleichen an dem Substrat **102** durchgeführt werden. Als Plasmabehandlung kann ein umgekehrtes Sputtern, bei dem ein Argongas eingeführt wird und Plasma erzeugt wird, durchgeführt werden. Das umgekehrte Sputtern ist ein Verfahren, bei dem eine HF-Leistungsquelle zum Anlegen einer Spannung an die Substrat **102**-Seite in einer

Argon-Atmosphäre verwendet wird, so dass Plasma in der Nähe des Substrats **102** erzeugt wird, um eine Oberfläche des Substrats zu modifizieren. Es sei angemerkt, dass statt einer Argon-Atmosphäre eine Stickstoff-Atmosphäre, eine Helium-Atmosphäre, eine Sauerstoff-Atmosphäre oder dergleichen verwendet werden kann. Das umgekehrte Sputtern kann teilchenförmige Substanzen (auch als Partikel oder Staub bezeichnet), die an der Oberfläche des Substrats **102** haften, entfernen.

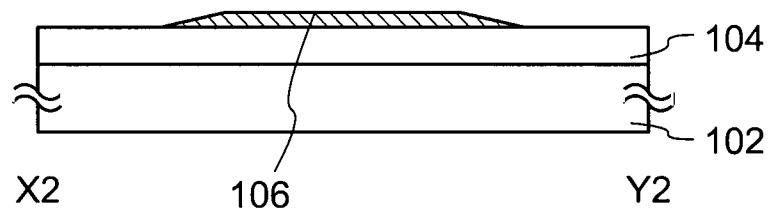

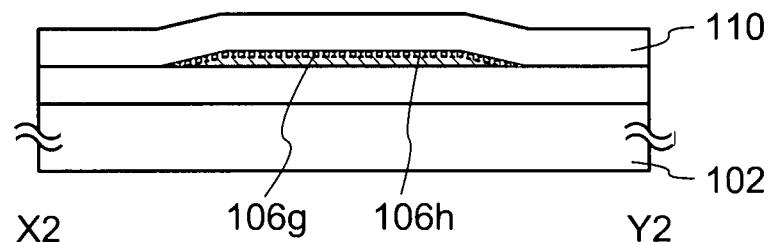

**[0077]** Als Nächstes wird der Oxidhalbleiterfilm **106** über dem Basis-Isolierfilm **104** ausgebildet (siehe Fig. 2A). Der Oxidhalbleiterfilm **106** ist vorzugsweise ein CAAC-OS-Film. Es sei angemerkt, dass der Basis-Isolierfilm **104** und der Oxidhalbleiterfilm **106** vorzugsweise sukzessiv ausgebildet werden, ohne der Luft ausgesetzt zu werden.

**[0078]** Der CAAC-OS-Film, der für den Oxidhalbleiterfilm **106** verwendet werden kann, wird nachstehend detailliert beschrieben.

**[0079]** Der CAAC-OS-Film ist weder vollständig einkristallin noch vollständig amorph. Der CAAC-OS-Film ist ein Oxidhalbleiterfilm mit einer kristallinen/amorphen Mischphasenstruktur, bei der Kristallbereiche in einer amorphen Phase eingeschlossen sind. Es sei angemerkt, dass in den meisten Fällen der Kristallbereich in einen Würfel mit einer Kantenlänge von weniger als 100 nm passt. Aus einem mit einem Transmissionselektronenmikroskop (TEM) erhaltenen Beobachtungsbild wird in dem CAAC-OS-Film eine Grenze zwischen einem amorphen Bereich und einem Kristallbereich nicht deutlich. Außerdem wird mittels TEM in dem CAAC-OS-Film keine Korngrenze erkannt. Folglich ist in dem CAAC-OS-Film eine Verringerung der Elektronenbeweglichkeit, die der Korngrenze zugeschrieben wird, unterdrückt.

**[0080]** Bei jedem der in dem CAAC-OS-Film eingeschlossenen Kristallbereiche ist eine c-Achse in einer Richtung ausgerichtet, die parallel zu einem Normalenvektor einer Oberfläche ist, auf der der CAAC-OS-Film ausgebildet ist, oder parallel zu einem Normalenvektor einer Oberfläche des CAAC-OS-Films ist, eine dreieckige oder hexagonale Atomanordnung, gesehen aus der Richtung, die senkrecht zur a-b-Fläche ist, ist ausgebildet und Metallatome sind in einer geschichteten Weise angeordnet oder Metallatome und Sauerstoffatome sind in einer geschichteten Weise angeordnet, gesehen aus der Richtung, die senkrecht zur c-Achse ist. Es sei angemerkt, dass bei den Kristallbereichen die Richtungen einer a-Achse und einer b-Achse eines Kristallbereichs unterschiedlich von denjenigen eines anderen Kristallbereichs sein können. In dieser Beschreibung und dergleichen umfasst der einfache Ausdruck „senkrecht“ einen Bereich von 85° bis 95°. Außerdem umfasst der einfache Ausdruck „parallel“ einen Bereich von –5° bis 5°.

**[0081]** In dem CAAC-OS-Film ist die Verteilung der Kristallbereiche nicht unbedingt gleichmäßig. Beispielsweise ist in dem Fall, in dem beim Ausbildungsprozess des CAAC-OS-Films das Kristallwachstum von einer Oberflächenseite des Oxidhalbleiterfilms aus stattfindet, der Anteil der Kristallbereiche in der Nähe der Oberfläche des Oxidhalbleiterfilms in einigen Fällen höher als derjenige in der Nähe einer Oberfläche, auf der der Oxidhalbleiterfilm ausgebildet ist.

**[0082]** Da die c-Achsen der in dem CAAC-OS-Film enthaltenen Kristallbereiche in der Richtung ausgerichtet sind, die parallel zu einem Normalenvektor einer Oberfläche, auf der der CAAC-OS-Film ausgebildet ist, oder parallel zu einem Normalenvektor einer Oberfläche des CAAC-OS-Films ist, können sich in Abhängigkeit von der Form des CAAC-OS-Films (der Querschnittsform der Oberfläche, auf der der CAAC-OS-Film ausgebildet ist, oder der Querschnittsform der Oberfläche des CAAC-OS-Films) die Richtungen der c-Achsen voneinander unterscheiden. Es sei angemerkt, dass dann, wenn der CAAC-OS-Film ausgebildet wird, die Richtung der c-Achse des Kristallbereichs eine Richtung ist, die parallel zu einem Normalenvektor der Oberfläche, auf der der CAAC-OS-Film ausgebildet ist, oder parallel zu einem Normalenvektor der Oberfläche des CAAC-OS-Films ist. Der Kristallbereich wird durch die Filmausbildung oder durch eine Behandlung zur Kristallbildung, wie z. B. eine Wärmebehandlung nach der Filmausbildung, gebildet.

**[0083]** Unter Verwendung des CAAC-OS Films in einem Transistor kann eine Veränderung der elektrischen Eigenschaften des Transistors aufgrund von Bestrahlung mit sichtbarem Licht oder UV-Licht verringert werden. Eine Veränderung und Schwankungen der Schwellenspannung können unterdrückt werden. Somit hat der Transistor eine hohe Zuverlässigkeit.

**[0084]** In einem Oxidhalbleiter, der eine Kristallinität besitzt (einem kristallinen Oxidhalbleiter), können Defekte in dem Bulk weiter reduziert werden. Ferner kann dann, wenn die Oberflächenglattheit des kristallinen Oxidhalbleiterfilms erhöht wird, ein Transistor mit obenliegendem Gate (top-gate transistor), der einen derartigen Oxidhalbleiter aufweist, höhere Feld-Effekt-Beweglichkeit erzielen, als ein Transistor, der einen amorphen

Oxidhalbleiter aufweist. Um die Oberflächenglattheit des Oxidhalbleiterfilms zu erhöhen, wird der Oxidhalbleiter vorzugsweise über einer glatten Oberfläche ausgebildet. Insbesondere wird der Oxidhalbleiter vorzugsweise über einer Oberfläche mit einer durchschnittlichen Oberflächenrauheit ( $R_a$ ) von weniger als oder gleich 0,15 nm, bevorzugt weniger als oder gleich 0,1 nm ausgebildet.

**[0085]** Es sei angemerkt, dass die durchschnittliche Oberflächenrauheit ( $R_a$ ) durch eine dreidimensionale Erweiterung einer arithmetischen mittleren Oberflächenrauheit derart, dass sie auf eine gekrümmte Oberfläche angewendet werden kann, erhalten wird. Die  $R_a$  kann als ein "Mittelwert der Absolutwerte der Abweichungen von einer Referenzoberfläche zu einer bestimmten Oberfläche" ausgedrückt werden und ist durch die folgende Formel definiert.

[FORMEL 1]

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

**[0086]** Die bestimmte Oberfläche ist hier eine Oberfläche, die ein Gegenstand der Rauheitsmessung ist, wobei sie ein viereckiges Gebiet ist, das von vier durch die Koordinaten  $(x_1, y_1, f(x_1, y_1))$ ,  $(x_1, y_2, f(x_1, y_2))$ ,  $(x_2, y_1, f(x_2, y_1))$  und  $(x_2, y_2, f(x_2, y_2))$  bezeichneten Punkten dargestellt ist. Darüber hinaus stellt So die Fläche eines Rechtecks, das durch Projizieren der bestimmten Oberfläche auf die x-y Fläche erhalten ist, dar und  $Z_0$  stellt die Höhe der Bezugsoberfläche (die durchschnittliche Höhe der bestimmten Oberfläche) dar. Die  $R_a$  kann unter Verwendung eines Rasterkraftmikroskops (atomic force microscope: AFM) gemessen werden.

**[0087]** Ein Oxidhalbleiter, der für den Oxidhalbleiterfilm **106** verwendet wird, enthält vorzugsweise zumindest Indium (In) oder Zink (Zn). Insbesondere sind vorzugsweise In und Zn enthalten. Als Stabilisator zur Verringerung von Schwankungen der elektrischen Eigenschaften eines Transistors, der den Oxidhalbleiterfilm aufweist, ist vorzugsweise zusätzlich Gallium (Ga) enthalten. Zinn (Sn) ist vorzugsweise als Stabilisator enthalten. Zudem ist vorzugsweise als Stabilisator ein oder mehrere Elemente enthalten, die aus Hafnium (Hf), Zirkonium (Zr), Titan (Ti), Scandium (Sc), Yttrium (Y) und einem Lanthanoidelement (wie z. B. Cer (Ce), Neodym (Nd) oder Gadolinium (Gd)) ausgewählt werden.

**[0088]** Als Oxidhalbleiter kann beispielsweise eines der Folgenden verwendet werden: Indiumoxid, Zinnoxid, Zinkoxid, ein Oxid auf In-Zn-Basis, ein Oxid auf Sn-Zn-Basis, ein Oxid auf Al-Zn-Basis, ein Oxid auf Zn-Mg-Basis, ein Oxid auf Sn-Mg-Basis, ein Oxid auf In-Mg-Basis, ein Oxid auf In-Ga-Basis, ein Oxid auf In-Ga-Zn-Basis (auch als IGZO bezeichnet), ein Oxid auf In-Al-Zn-Basis, ein Oxid auf In-Sn-Zn-Basis, ein Oxid auf Sn-Ga-Zn-Basis, ein Oxid auf Al-Ga-Zn-Basis, ein Oxid auf Sn-Al-Zn-Basis, ein Oxid auf In-Hf-Zn-Basis, ein Oxid auf In-Zr-Zn-Basis, ein Oxid auf In-Ti-Zn-Basis, ein Oxid auf In-Sc-Zn-Basis, ein Oxid auf In-Y-Zn-Basis, ein Oxid auf In-La-Zn-Basis, ein Oxid auf In-Ce-Zn-Basis, ein Oxid auf In-Pr-Zn-Basis, ein Oxid auf In-Nd-Zn-Basis, ein Oxid auf In-Sm-Zn-Basis, ein Oxid auf In-Eu-Zn-Basis, ein Oxid auf In-Gd-Zn-Basis, ein Oxid auf In-Tb-Zn-Basis, ein Oxid auf In-Dy-Zn-Basis, ein Oxid auf In-Ho-Zn-Basis, ein Oxid auf In-Er-Zn-Basis, ein Oxid auf In-Tm-Zn-Basis, ein Oxid auf In-Yb-Zn-Basis, ein Oxid auf In-Lu-Zn-Basis, ein Oxid auf In-Sn-Ga-Zn-Basis, ein Oxid auf In-Hf-Ga-Zn-Basis, ein Oxid auf In-Al-Ga-Zn-Basis, ein Oxid auf In-Sn-Al-Zn-Basis, ein Oxid auf In-Sn-Hf-Zn-Basis und ein Oxid auf In-Hf-Al-Zn-Basis.

**[0089]** Hier hat ein „Oxid auf In-Ga-Zn-Basis“ die Bedeutung eines In, Ga und Zn als Hauptkomponenten enthaltenden Oxides, wobei es keine besondere Einschränkung bezüglich des Verhältnisses von In:Ga:Zn gibt. Das Oxid auf In-Ga-Zn-Basis kann ein Metallelement zusätzlich zu In, Ga und Zn enthalten.

**[0090]** Alternativ kann ein Material, das durch  $InMO_3(ZnO)_m$  ( $m > 0$ , wobei m keine ganze Zahl ist) dargestellt wird, als Oxidhalbleiter verwendet werden. Es sei angemerkt, dass M ein oder mehrere Metallelemente bezeichnet, die aus Ga, Fe, Mn und Co ausgewählt werden, oder das oben als Stabilisator beschriebene Element bezeichnet. Als Alternative dazu kann ein Material als Oxidhalbleiter verwendet werden, das durch eine chemische Formel,  $In_2SnO_5(ZnO)_n$  ( $n > 0$ , wobei n eine natürliche Zahl ist), dargestellt wird.

**[0091]** Beispielsweise kann ein Oxid auf In-Ga-Zn-Basis mit einem Atomverhältnis in dem  $In:Ga:Zn = 1:1:1$ ,  $In:Ga:Zn = 3:1:2$  oder  $In:Ga:Zn = 2:1:3$  oder eines der Oxide, deren Zusammensetzung den obigen Zusammensetzungen nahe ist, verwendet werden.

**[0092]** In einem Herstellungsschritt des Oxidhalbleiterfilms **106** ist bevorzugt, dass möglichst wenig Wasserstoff oder Wasser in dem Oxidhalbleiterfilm **106** enthalten ist. Beispielsweise ist bevorzugt, dass das Substrat **102**, auf dem der Basis-Isolierfilm **104** schon ausgebildet worden ist, in einer Vorheizkammer einer Sputtereinrichtung als Vorbehandlung zum Ausbilden des Oxidhalbleiterfilms **106** vorgeheizt wird, so dass Verunreinigungen wie z. B. Wasser und Feuchtigkeit, die an dem Substrat **102** und dem Basis-Isolierilm **104** adsorbiert sind, entfernt und beseitigt werden. Dann wird der Oxidhalbleiterfilm **106** vorzugsweise in einer Abscheidungskammer, von der verbleibende Feuchtigkeit entfernt wird, ausgebildet.

**[0093]** Zum Entfernen der Feuchtigkeit in der Vorheizkammer und der Abscheidungskammer wird vorzugsweise eine Einfang-Vakuumpumpe, wie z. B. eine Kryopumpe, eine Ionenpumpe oder eine Titan-Sublimationspumpe verwendet. Eine Evakuierungseinrichtung kann ferner eine Turbopumpe, die mit einer Kühlafalle versehen ist, sein. Von der Vorheizkammer und der Abscheidungskammer, die mit der Kryopumpe entleert werden, werden ein Wasserstoffatom, eine Verbindung, die ein Wasserstoffatom enthält, wie z. B. Wasser ( $H_2O$ ) (stärker bevorzugt auch eine Verbindung, die ein Kohlenstoffatom enthält) und dergleichen entfernt, wodurch die Konzentration der Verunreinigungen wie z. B. Wasserstoff oder Feuchtigkeit in dem Oxidhalbleiterfilm **106**, der ausgebildet wird, verringert werden kann.

**[0094]** Es sei angemerkt, dass bei dieser Ausführungsform ein Oxid auf In-Ga-Zn-Basis als der Oxidhalbleiterfilm **106** durch ein Sputterverfahren abgeschieden wird. Der Oxidhalbleiterfilm **106** kann durch ein Sputterverfahren in einer Edelgasatmosphäre (typischerweise Argonatmosphäre), einer Sauerstoffatmosphäre oder einer gemischten Atmosphäre von einem Edelgas und Sauerstoff ausgebildet werden.

**[0095]** Als Target zum Ausbilden eines Oxidfilms auf In-Ga-Zn-Basis als der Oxidhalbleiterfilm **106** durch ein Sputterverfahren kann beispielsweise ein Metalloxidtarget mit einem Atomverhältnis, in dem  $In:Ga:Zn = 1:1:1$ , ein Metalloxidtarget mit einem Atomverhältnis, in dem  $In:Ga:Zn = 3:1:2$ , oder ein Metalloxidtarget mit einem Atomverhältnis, in dem  $In:Ga:Zn = 2:1:3$ , verwendet werden. Jedoch sind ein Material und eine Zusammensetzung eines Targets zum Ausbilden des Oxidhalbleiterfilms **106** nicht auf die Obigen beschränkt.

**[0096]** Wenn ferner der Oxidhalbleiterfilm **106** unter Verwendung des obigen Metalloxidtargets ausgebildet wird, ist die Zusammensetzung des Targets in einigen Fällen unterschiedlich von der Zusammensetzung eines Films, der über dem Substrat ausgebildet wird. Beispielsweise wird dann, wenn das Metalloxidtarget mit einem Molverhältnis, in dem  $In_2O_3:Ga_2O_3:ZnO = 1:1:1$ , verwendet wird, in einigen Fällen das Zusammensetzungsverhältnis des dünnen Oxidhalbleiterfilms **106** zu  $In_2O_3:Ga_2O_3:ZnO = 1:1:0,6$  bis  $1:1:0,8$  [Molverhältnis], was von den Bedingungen zum Ausbilden des Films abhängt. Das liegt daran, dass beim Ausbilden des Oxidhalbleiterfilms **106** ZnO sublimiert wird, oder dass die Sputter-Rate zwischen den Komponenten,  $In_2O_3$ ,  $Ga_2O_3$  und ZnO, variiert.

**[0097]** Folglich muss dann, wenn ein dünner Film mit einem vorteilhaften Zusammensetzungsverhältnis ausgebildet wird, ein Zusammensetzungswert des Metalloxidtargets im Voraus reguliert werden. Damit beispielsweise das Zusammensetzungswert des dünnen Oxidhalbleiterfilms **106**  $In_2O_3:Ga_2O_3:ZnO = 1:1:1$  [Molverhältnis] sein soll, wird das Zusammensetzungswert des Metalloxidtargets auf  $In_2O_3:Ga_2O_3:ZnO = 1:1:1,5$  [Molverhältnis] eingestellt. Mit anderen Worten: der ZnO-Gehalt in dem Metalloxidtarget wird im Voraus erhöht. Das Zusammensetzungswert des Targets ist nicht auf den obigen Wert beschränkt und kann angemessen in Abhängigkeit von den Bedingungen zum Ausbilden des Films oder der Zusammensetzung des auszubildenden dünnen Films reguliert werden. Zudem ist bevorzugt, den ZnO-Gehalt in dem Metalloxidtarget zu erhöhen, weil in diesem Fall die Kristallinität des erhaltenen dünnen Films verbessert wird.

**[0098]** Die relative Dichte des Metalloxidtargets ist 90% bis einschließlich 100%, bevorzugt 95% bis einschließlich 99,9%. Durch Verwendung des Metalloxidtargets mit hoher relativer Dichte kann ein dichter Oxidhalbleiterfilm **106** ausgebildet werden.

**[0099]** Als Sputtergas zum Ausbilden des Oxidhalbleiterfilms **106** ist zu bevorzugen, ein hochreines Gas, von dem eine Verunreinigung wie z. B. Wasserstoff, Wasser, eine Hydroxylgruppe oder ein Hydrid entfernt worden ist, zu verwenden.

**[0100]** Es gibt drei Verfahren zum Ausbilden eines CAAC-OS-Films, wenn der CAAC-OS-Film als der Oxidhalbleiterfilm **106** verwendet wird. Bei einem der Verfahren (einem ersten Verfahren) wird ein Oxidhalbleiterfilm bei einer Temperatur von höher als oder gleich 100°C und niedriger als oder gleich 450°C ausgebildet, wodurch Kristallbereiche, in denen die c-Achsen in der Richtung ausgerichtet sind, die parallel zu einem Normalenvektor einer Oberfläche ist, auf der der Oxidhalbleiterfilm ausgebildet ist, oder parallel zu einem Norma-

lenvektor einer Oberfläche des Oxidhalbleiterfilms ist, in dem Oxidhalbleiterfilm gebildet werden. Beim einem weiteren Verfahren (einem zweiten Verfahren) wird ein Oxidhalbleiterfilm mit einer kleinen Dicke ausgebildet, und dann wird er bei einer Temperatur von höher als oder gleich 200°C und niedriger als oder gleich 700°C erwärmt, wodurch Kristallbereiche, in denen die c-Achsen in der Richtung ausgerichtet sind, die parallel zu einem Normalenvektor einer Oberfläche ist, auf der der Oxidhalbleiterfilm ausgebildet ist, oder parallel zu einem Normalenvektor einer Oberfläche des Oxidhalbleiterfilms ist, in dem Oxidhalbleiterfilm gebildet werden. Bei einem weiteren Verfahren (einem dritten Verfahren) wird ein erster Oxidhalbleiterfilm mit einer kleinen Dicke ausgebildet, dann wird er bei einer Temperatur von höher als oder gleich 200°C und niedriger als oder gleich 700°C erwärmt, und ein zweiter Oxidhalbleiterfilm wird ausgebildet, wodurch Kristallbereiche, in denen die c-Achsen in der Richtung ausgerichtet sind, die parallel zu einem Normalenvektor einer Oberfläche ist, auf der der Oxidhalbleiterfilm ausgebildet ist, oder parallel zu einem Normalenvektor einer Oberfläche des Oxidhalbleiterfilms ist, in dem Oxidhalbleiterfilm gebildet werden.

**[0101]** Beispielsweise wird der CAAC-OS-Film durch ein Sputterverfahren mit einem polykristallinen Oxidhalbleiter-Sputtertarget ausgebildet. Wenn Ionen mit dem Sputtertarget zusammenstoßen, kann ein in dem Sputtertarget enthaltener Kristallbereich entlang einer a-b-Fläche von dem Target abgetrennt werden. Mit anderen Worten: ein gesputtertes Teilchen mit einer Fläche, die parallel zu der a-b-Fläche ist (flachplatteähnliches gesputtertes Teilchen oder pelletähnliches gesputtertes Teilchen) kann von dem Sputtertarget abplatzen. In diesem Fall erreicht das flachplatteähnliche gesputterte Teilchen unter Bewahrung seines Kristallzustandes ein Substrat, wodurch der CAAC-OS-Film ausgebildet werden kann.

**[0102]** Für die Herstellung des CAAC-OS-Films finden vorzugsweise die folgenden Bedingungen Anwendung.

**[0103]** Durch Verringern der Menge an Verunreinigungen, die in den CAAC-OS-Film während der Abscheidung eindringen, kann verhindert werden, dass der Kristallzustand durch die Verunreinigungen aufgebrochen wird. Beispielsweise kann die Konzentration der in der Abscheidungskammer vorhandenen Verunreinigungen (z. B. Wasserstoff, Wasser, Kohlenstoffdioxid oder Stickstoff) verringert werden. Außerdem kann die Konzentration der Verunreinigungen in einem Abscheidungsgas verringert werden. Insbesondere wird ein Abscheidungsgas verwendet, dessen Taupunkt bei –80°C oder niedriger, vorzugsweise bei –100°C oder niedriger liegt.

**[0104]** Durch Erhöhen der Erwärmungstemperatur des Substrats während der Abscheidung tritt wahrscheinlich eine Wanderung eines gesputterten Teilchens auf, nachdem das gesputterte Teilchen eine Oberfläche eines Substrats erreicht hat. Im Besonderen ist die Erwärmungstemperatur des Substrats während der Abscheidung höher als oder gleich 100°C und niedriger als oder gleich 740°C, bevorzugt höher als oder gleich 150°C und niedriger als oder gleich 500°C. Durch Erhöhen der Erwärmungstemperatur des Substrats während der Abscheidung findet dann, wenn das flachplattenähnliche gesputterte Teilchen das Substrat erreicht, auf der Oberfläche des Substrats eine Wanderung statt, derart, dass eine ebene Fläche des flachplattenähnlichen gesputterten Teilchens an dem Substrat haftet.

**[0105]** Außerdem ist bevorzugt, dass der Sauerstoffanteil am Abscheidungsgas erhöht wird und die Leistung optimiert wird, um Plasmaschäden bei der Abscheidung zu verringern. Der Sauerstoffanteil am Abscheidungsgas beträgt 30 Vol.-% oder höher, vorzugsweise 100 Vol.-%.

**[0106]** Es sei angemerkt, dass dann, wenn ein kristalliner (einkristalliner oder mikrokristalliner) Oxidhalbleiterfilm außer einem CAAC-OS-Film als der Oxidhalbleiterfilm **106** ausgebildet wird, es keine besondere Beschränkung bezüglich der Abscheidungstemperatur gibt.

**[0107]** Als Nächstes wird ein leitender Film, der für eine Source-Elektrode und eine Drain-Elektrode (einschließlich einer Leitung, die in derselben Schicht wie die Gate-Elektrode ausgebildet ist) verwendet wird, über dem Basis-Isolierfilm **104** und dem Oxidhalbleiterfilm **106** ausgebildet. Als der leitende Film, der für die Source-Elektrode und die Drain-Elektrode verwendet wird, kann beispielsweise ein Metallfilm, der ein Element enthält, das aus Aluminium, Chrom, Kupfer, Tantal, Titan, Molybdän und Wolfram ausgewählt wird, oder ein Metallnitridfilm, der irgendeines der oben genannten Elemente als seine Komponente enthält (z. B. ein Titan-nitridfilm, ein Molybdän-nitridfilm oder ein Wolfram-nitridfilm), verwendet werden. Alternativ kann der leitende Film eine Struktur aufweisen, bei der ein Film aus einem einen hohen Schmelzpunkt aufweisenden Metall, wie z. B. Titan, Molybdän oder Wolfram, oder ein Nitridfilm aus irgendeinem dieser Elemente (z. B. ein Titan-nitridfilm, ein Molybdän-nitridfilm oder ein Wolfram-nitridfilm) auf der Bodenfläche und/oder der nach oben weisenden Fläche eines Metallfilms aus Aluminium, Kupfer oder dergleichen gestapelt ist. Ferner kann der leitende Film, der für die Source-Elektrode und die Drain-Elektrode verwendet wird, aus einem leitenden Metalloxid ausgebildet werden. Als das leitende Metalloxid kann Indiumoxid ( $In_2O_3$ ), Zinnoxid ( $SnO_2$ ), Zinkoxid ( $ZnO$ ),

Indiumzinnoxid ( $\text{In}_2\text{O}_3\text{-SnO}_2$ ; welches in einigen Fällen zu ITO abgekürzt wird) oder Indiumzinkoxid ( $\text{In}_2\text{O}_3\text{-ZnO}$ ) verwendet werden. Der leitende Film, der für die Source-Elektrode und die Drain-Elektrode verwendet wird, kann unter Verwendung eines der obigen Materialien ausgebildet werden, um eine einschichtige Struktur oder eine gestapelte Struktur aufzuweisen. Bezuglich des Verfahrens zum Ausbilden des leitenden Films gibt es keine besondere Beschränkung, und verschiedene Verfahren zum Ausbilden des Films, wie z. B. ein Verdampfungsverfahren, ein CVD-Verfahren, ein Sputterverfahren und ein Rotationsbeschichtungsverfahren, können verwendet werden.

**[0108]** Als Nächstes wird eine Fotolackmaske über dem leitenden Film durch einen Fotolithografieschritt ausgebildet, und selektives Ätzen wird durchgeführt, so dass die Source-Elektrode **108a** und die Drain-Elektrode **108b** ausgebildet werden. Dann wird die Fotolackmaske entfernt (siehe **Fig. 2B**). Für die Belichtung zum Ausbilden der Fotolackmaske bei dem Fotolithografieschritt kann Ultraviolett, ein KrF-Laser oder ein ArF-Laser verwendet werden.

**[0109]** In diesem Schritt wird eine Kanallänge L des später fertiggestellten Transistors **150** durch eine Distanz zwischen einem unteren Ende der Source-Elektrode **108a** und einem unteren Ende der Drain-Elektrode **108b** bestimmt, die einander über dem Oxidhalbleiterfilm **106** benachbart sind. Wenn eine Belichtung für eine Kanallänge L von weniger als 25 nm durchgeführt wird, kann die Belichtung zum Ausbilden der Fotolackmaske in dem Fotolithographieschritt beispielsweise unter Verwendung von extremem ultraviolettem Licht mit einer extrem kurzen Wellenlänge von mehreren Nanometern bis mehreren zehn Nanometern durchgeführt werden. Bei der Belichtung durch ein extremes ultraviolettes Licht ist die Auflösung hoch und die Fokustiefe ist groß. Die Kanallänge L des später fertiggestellten Transistors **150** kann also verringert werden, wodurch die Betriebsgeschwindigkeit einer Schaltung erhöht werden kann.

**[0110]** Um die Anzahl der Fotomasken in einem Fotolithografieschritt und die Anzahl der Fotolithografieschritte zu reduzieren, kann ein Ätzschritt unter Verwendung einer Mehrtonmaske durchgeführt werden, die eine Belichtungsmaske ist und durch die Licht durchgelassen wird, um eine Vielzahl von Intensitäten aufzuweisen. Eine Fotolackmaske, die unter Verwendung einer Mehrtonmaske ausgebildet wird, weist eine Vielzahl von Dicken auf und kann ferner durch Ätzen in der Form verändert werden; somit kann die Fotolackmaske in einer Vielzahl von Ätzschritten zum Verarbeiten in verschiedene Muster verwendet werden. Daher kann eine Fotolackmaske für mindestens zwei oder mehr Arten unterschiedlicher Muster unter Verwendung einer Mehrtonmaske ausgebildet werden. Infolgedessen kann die Anzahl der Belichtungsmasken reduziert werden, und damit kann auch die Anzahl entsprechender Fotolithografieschritte reduziert werden, wodurch ein Prozess vereinfacht werden kann.

**[0111]** Es sei angemerkt, dass es bevorzugt ist, dass die Ätzbedingungen optimiert werden, um nicht den Oxidhalbleiterfilm **106** beim Ätzen des leitenden Films zu ätzen und teilen. Jedoch ist es schwer, solche Ätzbedingungen zu erreichen, unter denen nur der leitende Film geätzt wird und der Oxidhalbleiterfilm **106** gar nicht geätzt wird. In einigen Fällen wird nur ein Teil des Oxidhalbleiterfilms **106**, z. B. 5% bis 50% der Dicke des Oxidhalbleiterfilms **106** geätzt, so dass der Oxidhalbleiterfilm **106** eine Rille (einen niedrigen Teil) aufweist, wenn der leitende Film geätzt wird.

**[0112]** Als Nächstes wird der Gate-Isolierfilm **110** ausgebildet, um den Oxidhalbleiterfilm **106**, die Source-Elektrode **108a** und die Drain-Elektrode **108b** zu bedecken. Der Gate-Isolierfilm **110** kann eine Dicke von größer als oder gleich 1 nm und kleiner als oder gleich 500 nm aufweisen. Es gibt keine besondere Beschränkung bezüglich des Verfahrens zum Ausbilden des Gate-Isolierfilms **110**. Beispielsweise kann ein Sputterverfahren, ein MBE-Verfahren, ein CVD-Verfahren, ein Laserstrahlverdampfungsverfahren, ein ALD-Verfahren oder der gleichen angemessen zum Ausbilden des Gate-Isolierfilms **110** verwendet werden.

**[0113]** Für den Gate-Isolierfilm **110** wird vorzugsweise ein Oxidisolierfilm mit einer ausreichenden Spannungsfestigkeit und ausreichenden isolierenden Eigenschaften verwendet. In dem Fall, in dem der Gate-Isolierfilm **110** eine einschichtige Struktur hat, kann ein Oxid, das Silizium enthält, wie z. B. ein Siliziumoxidfilm, verwendet werden.

**[0114]** Des Weiteren werden dann, wenn der Gate-Isolierfilm **110** ausgebildet wird, Verunreinigungen wie z. B. Silizium in den Oxidhalbleiterfilm **106** in der Nähe der Grenzfläche zu dem Gate-Isolierfilm **110** aufgenommen. Als Ergebnis wird in dem Oxidhalbleiterfilm **106** der Bereich **106a** in der Nähe der Grenzfläche zu dem Gate-Isolierfilm **110** ausgebildet, wobei ein Bereich in dem Oxidhalbleiterfilm **106** außer dem Bereich **106a** der Bereich **106b** ist.

[0115] Es sei angemerkt, dass die Siliziumkonzentration in dem Bereich **106a** niedriger als oder gleich 1,0 Atom-%, bevorzugt niedriger als oder gleich 0,1 Atom-% beträgt. Der Bereich **106a** ist in Kontakt mit dem Gate-Isolierfilm **110** vorgesehen, um eine Dicke von kleiner als oder gleich 5 nm aufzuweisen.

[0116] Weiterhin dringen in dem Fall, in dem Verunreinigungen wie z. B. Kohlenstoff in dem Gate-Isolierfilm **110** enthalten sind, solche Verunreinigungen auch in den Bereich **106a** in dem Oxidhalbleiterfilm **106** ein und dienen als Verunreinigungen, wie beim Fall von Silizium. In diesem Fall ist die Konzentration von Kohlenstoff in dem Bereich **106a** niedriger als oder gleich  $1,0 \times 10^{20}$  Atome/cm<sup>3</sup>, bevorzugt niedriger als oder gleich  $1,0 \times 10^{19}$  Atome/cm<sup>3</sup>.

[0117] Alternativ kann der Gate-Isolierfilm **110** eine gestapelte Struktur aufweisen. In dem Fall, in dem der Gate-Isolierfilm **110** eine gestapelte Struktur aufweist, kann beispielsweise Galliumoxid, Aluminiumoxid, Siliziumnitrid, Siliziumoxynitrid, Aluminiumoxynitrid, Yttriumoxid, Lanthanoxid, Siliziumnitridoxid oder dergleichen über einem Oxid, das Silizium enthält, gestapelt werden. Alternativ kann ein Material mit hohem k wie z. B. Hafniumoxid, Hafniumsilikat ( $\text{HfSi}_x\text{O}_y$  ( $x > 0, y > 0$ )), Hafniumsilikat, zu dem Stickstoff zugesetzt worden ist ( $\text{HfSiO}_x\text{N}_y$  ( $x > 0, y > 0$ )) oder Hafniumaluminat ( $\text{HfAl}_x\text{O}_y$  ( $x > 0, y > 0$ )) über einem Oxid, das Silizium enthält, gestapelt werden.

[0118] Wenn ein Oxid, das Silizium enthält, als der Gate-Isolierfilm **110** verwendet wird, kann ein Teil von Sauerstoff, der in dem Isolierfilm enthalten ist, durch eine später erwähnte Wärmebehandlung abgegeben werden. Daher kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, und Sauerstofffehlstellen in dem Oxidhalbleiterfilm **106** können gefüllt werden. Insbesondere enthält vorzugsweise der Gate-Isolierfilm **110** eine große Menge an Sauerstoff, die zumindest seine Stöchiometrie überschreitet. Beispielsweise wird ein Film von Siliziumoxid, das durch die Formel  $\text{SiO}_{2+\alpha}$  ( $\alpha > 0$ ) dargestellt wird, vorzugsweise als der Gate-Isolierfilm **110** verwendet. Wenn ein derartiger Siliziumoxidfilm als der Gate-Isolierfilm **110** verwendet wird, kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, so dass der Transistor **150**, bei dem der Oxidhalbleiterfilm **106** verwendet wird, bevorzugte Transistoreigenschaften aufweisen kann.

[0119] Um zu verhindern, dass Verunreinigungen wie z. B. Silizium in den Oxidhalbleiterfilm **106** eindringen, wird der Gate-Isolierfilm **110** derart ausgebildet, dass der Oxidhalbleiterfilm **106** nicht beschädigt wird. In dem Fall, in dem beispielsweise ein Siliziumoxidfilm als der Gate-Isolierfilm **110** durch ein Sputterverfahren ausgebildet wird, kann die Auswirkung von Silizium (das ein Bestandteil des Gate-Isolierfilms **110** ist), das mit dem Oxidhalbleiterfilm **106** kollidiert, verringert werden. Damit man den obigen Effekt erzielen kann, kann man beispielsweise das Folgende verwenden: ein Verfahren, bei dem die Leistung zur Abscheidung des Gate-Isolierfilms **110** niedrig ist, ein Verfahren, bei dem der Druck zur Abscheidung des Gate-Isolierfilms **110** hoch ist, ein Verfahren, bei dem eine Distanz zwischen einem Target und einem Substrat (T-S-Distanz) bei der Abscheidung des Gate-Isolierfilms **110** verlängert wird, oder dergleichen. Jedoch ist ein Verfahren zum Ausbilden des Gate-Isolierfilms **110** nicht auf die obigen Verfahren beschränkt. Beispielsweise kann ein Siliziumoxidfilm, ein Siliziumoxynitridfilm, ein Siliziumnitridoxidfilm oder dergleichen, der durch ein PE-CVD-Verfahren ausgebildet wird, verwendet werden. Ein PE-CVD-Verfahren wird gegenüber einem Sputterverfahren bevorzugt, weil unter Verwendung des PE-CVD-Verfahrens der Oxidhalbleiterfilm **106**, der als Basisfilm dient, weniger beschädigt wird.

[0120] Als Nächstes wird ein leitender Film zum Ausbilden einer Gate-Elektrode (sowie eine Leitung, die in derselben Schicht wie die Gate-Elektrode ausgebildet wird) über dem Gate-Isolierfilm **110** ausgebildet. Der leitende Film für die Gate-Elektrode kann beispielsweise unter Verwendung eines Metallmaterials ausgebildet werden, wie z. B. Molybdän, Titan, Tantal, Wolfram, Aluminium, Kupfer, Neodym oder Scandium oder eines Legierungsmaterials, das eines dieser Materialien als seine Hauptkomponente enthält. Alternativ kann der leitende Film für die Gate-Elektrode unter Verwendung eines leitenden Metalloxides ausgebildet werden. Als das leitende Metalloid kann Indiumoxid ( $\text{In}_2\text{O}_3$ ), Zinnoxid ( $\text{SnO}_2$ ), Zinkoxid ( $\text{ZnO}$ ), Indiumzinnoxid ( $\text{In}_2\text{O}_3\text{-SnO}_2$ ; welches in einigen Fällen zu ITO abgekürzt wird) oder Indiumzinkoxid ( $\text{In}_2\text{O}_3\text{-ZnO}$ ) oder eines dieser Metalloxidmaterialien, das Silizium oder Siliziumoxid enthält, verwendet werden. Die Gate-Elektrode kann unter Verwendung eines der obigen Materialien ausgebildet werden, um eine einschichtige Struktur oder gestapelte Struktur aufzuweisen. Bezüglich des Verfahrens zum Ausbilden des leitenden Films gibt es keine besondere Beschränkung, und verschiedene Verfahren zum Ausbilden des Films wie z. B. ein Verdampfungsverfahren, ein CVD-Verfahren, ein Sputterverfahren und ein Rotationsbeschichtungsverfahren können verwendet werden.

[0121] Als Nächstes wird eine Fotolackmaske über dem leitenden Film durch einen Fotolithografieschritt ausgebildet, und selektives Ätzen wird durchgeführt, so dass die Gate-Elektrode **112** ausgebildet wird. Dann wird die Fotolackmaske entfernt (siehe Fig. 2C). Die Fotolackmaske zum Ausbilden der Gate-Elektrode **112** kann

durch ein Tintenstrahlverfahren ausgebildet werden. Das Ausbilden der Fotolackmaske durch ein Tintenstrahlverfahren braucht keine Fotomaske, und somit können sich die Herstellungskosten ermäßigten. Zum Ätzen der Gate-Elektrode **112** kann Nassätzen und/oder Trockenätzen verwendet werden. Es sei angemerkt, dass dann, wenn die Gate-Elektrode **112** ausgebildet wird, der Transistor **150** fertiggestellt wird.

**[0122]** Anschließend wird der Zwischenschicht-Isolierfilm **114** über dem Gate-Isolierfilm **110** und der Gate-Elektrode **112** ausgebildet (siehe Fig. 2D).

**[0123]** Der Zwischenschicht-Isolierfilm **114** wird vorzugsweise unter Verwendung eines anorganischen Isolierfilms ausgebildet, um eine einschichtige Struktur oder eine gestapelte Struktur eines Oxidisolierfilms, wie z. B. eines Siliziumoxidfilms, eines Siliziumoxynitridfilms, eines Aluminiumoxidfilms, eines Aluminiumoxynitridfilms, eines Galliumoxidfilms oder eines Hafniumoxidfilms, aufzuweisen. Außerdem kann über dem obigen Oxidisolierfilm eine Einzelschicht oder eine gestapelte Schicht eines Nitridisolierfilms wie z. B. eines Siliziumnitridfilms, eines Siliziumnitridoxidfilms, eines Aluminiumnitridfilms oder eines Aluminiumnitridoxidfilms, ausgebildet werden. Beispielsweise werden als gestapelte Schicht ein Siliziumoxidfilm und ein Aluminiumoxidfilm in dieser Reihenfolge über der Gate-Elektrode **112** abgeschieden.

**[0124]** Nach dem Ausbilden des Zwischenschicht-Isolierfilms **114** wird vorzugsweise eine Wärmebehandlung an dem Oxidhalbleiterfilm **106** durchgeführt. Die Temperatur der Wärmebehandlung ist höher als oder gleich 300°C und niedriger als oder gleich 700°C, oder niedriger als die untere Entspannungsgrenze (strain point) eines Substrats.

**[0125]** Die Wärmebehandlung kann in einer Atmosphäre von Stickstoff, Sauerstoff, ultratrockener Luft (Luft, in der der Wassergehalt weniger als oder gleich 20 ppm, bevorzugt weniger als oder gleich 1 ppm, stärker bevorzugt weniger als oder gleich 10 ppb beträgt) oder einem Edelgas (wie z. B. Argon oder Helium) durchgeführt werden. Es sei angemerkt, dass es bevorzugt ist, dass in der Atmosphäre von Stickstoff, Sauerstoff, ultratrockener Luft, einem Edelgas oder dergleichen kein Wasser, Wasserstoff und dergleichen enthalten sind. Es ist auch möglich, dass die Reinheit von Stickstoff, Sauerstoff oder dem Edelgas, der/das in eine Wärmebehandlungseinrichtung eingeleitet wird, auf mehr als oder gleich 6 N (99,9999%), bevorzugt mehr als oder gleich 7 N (99,99999%) (d. h. die Verunreinigungskonzentration beträgt weniger als oder gleich 1 ppm, bevorzugt weniger als oder gleich 0,1 ppm) eingestellt wird.

**[0126]** In dem Fall, in dem eine Wärmebehandlung nach dem Ausbilden des Oxidhalbleiterfilms durchgeführt wird, könnte Sauerstoff, der eine der Hauptkomponentenmaterialien in dem Oxidhalbleiter ist, verringert werden. Jedoch kann während der Wärmebehandlung in diesem Schritt Sauerstoff zu dem Oxidhalbleiterfilm **106** von dem Basis-Isolierfilm **104** oder dem Gate-Isolierfilm **110**, der unter Verwendung eines Silizium enthaltenden Oxides ausgebildet wird, zugeführt werden; somit können Sauerstofffehlstellen in dem Oxidhalbleiterfilm **106** gefüllt werden.

**[0127]** Indem wie oben beschrieben die Wärmebehandlung durchgeführt wird, kann der Oxidhalbleiterfilm **106** hochgereinigt werden, so dass er möglichst wenige Verunreinigungen, die nicht Hauptkomponenten sind, enthält. Der hochgereinigte Oxidhalbleiterfilm **106** enthält äußerst wenig (nahezu null) Ladungsträger, die von einem Donator abgeleitet sind, und seine Ladungsträgerkonzentration beträgt niedriger als  $1 \times 10^{14}/\text{cm}^3$ , bevorzugt niedriger als  $1 \times 10^{12}/\text{cm}^3$ , stärker bevorzugt niedriger als  $1 \times 10^{11}/\text{cm}^3$ . Auf diese Weise kann der Oxidhalbleiterfilm **106**, der zu einem i-Typ-(intrinsischen)Oxidhalbleiter wird, ausgebildet werden.

**[0128]** Durch die obigen Schritte wird der Transistor **150** ausgebildet. Bei dem Transistor **150** ist die Konzentration von Verunreinigungen wie z. B. Silizium, die in den Bereich **106a** des Oxidhalbleiterfilms **106** aufgenommen werden, niedrig. Ferner kann in dem Fall, in dem der Oxidhalbleiterfilm ein CAAC-OS-Film ist, ein Kristallbereich auch in der Nähe der Grenzfläche zwischen dem Oxidhalbleiterfilm und dem Gate-Isolierfilm **110** ausgebildet werden. Deshalb kann der Transistor **150** stabile elektrische Eigenschaften aufweisen.

**[0129]** Über dem Zwischenschicht-Isolierfilm **114** kann ein Planarisierung isolierfilm weiterhin ausgebildet werden. Der Planarisierung isolierfilm kann unter Verwendung eines organischen Materials mit Wärmebeständigkeit ausgebildet werden, und z. B. kann ein Acrylharz, ein Polyimidharz, ein Harz auf Benzocyclobuten-Basis, ein Polyamidharz oder ein Epoxidharz verwendet werden. Zusätzlich zu solchen organischen Materialien kann ein Material mit niedriger Dielektrizitätskonstante (Material mit niedrigem  $\kappa$ ) oder ein Harz auf Siloxan-Basis verwendet werden. Es sei angemerkt, dass der Planarisierung isolierfilm durch Stapeln einer Vielzahl von Isolierfilmen, die aus einem dieser Materialien ausgebildet werden, ausgebildet werden kann.

**[0130]** Die Verfahren und Strukturen dieser Ausführungsform können angemessen mit einem/einer der Verfahren und Strukturen der anderen Ausführungsformen kombiniert werden.

(Ausführungsform 2)

**[0131]** Bei dieser Ausführungsform werden Modifikationsbeispiele für die Halbleitervorrichtung und das Verfahren zum Herstellen der Halbleitervorrichtung der Ausführungsform 1, welche in **Fig. 1A**, **Fig. 1B** und **Fig. 2A bis Fig. 2D** gezeigt sind, anhand von **Fig. 3A**, **Fig. 3B**, **Fig. 4A bis Fig. 4D**, **Fig. 5A** und **Fig. 5B** beschrieben. Es sei angemerkt, dass Teile ähnlich wie diejenige in **Fig. 1A**, **Fig. 1B** und **Fig. 2A bis Fig. 2D** durch die gleichen Bezugszeichen bezeichnet werden, und eine Beschreibung davon wird weggelassen.

<Beispiel für eine Struktur einer Halbleitervorrichtung (Modifikationsbeispiel)>

**[0132]** In **Fig. 3A** und **Fig. 3B** ist ein Transistor mit obenliegendem Gate (top-gate transistor) als Beispiel für eine Halbleitervorrichtung gezeigt. **Fig. 3A** ist eine Draufsicht, und **Fig. 3B** ist eine Querschnittsansicht entlang der gestrichelten Linie X2-Y2 in **Fig. 3A**. Es sei angemerkt, dass einige Komponenten eines Transistors **160** (z. B. ein Gate-Isolierfilm **110**) der Einfachheit halber in **Fig. 3A** weggelassen sind.

**[0133]** Der Transistor **160** in **Fig. 3A** und **Fig. 3B** beinhaltet über einem Substrat **102** einen Basis-Isolierfilm **104**, einen Oxidhalbleiterfilm **106**, der über dem Basis-Isolierfilm **104** ausgebildet ist und einen Bereich **106c**, einen Bereich **106d**, einen Bereich **106e** und einen Bereich **106f** aufweist, den Gate-Isolierfilm **110**, der über dem Oxidhalbleiterfilm **106** ausgebildet ist, eine Gate-Elektrode **112**, die in Kontakt mit dem Gate-Isolierfilm **110** steht und zumindest mit dem Oxidhalbleiterfilm **106** überlappt, einen Zwischenschicht-Isolierfilm **114**, der über dem Gate-Isolierfilm **110** und der Gate-Elektrode **112** ausgebildet ist, und eine Source-Elektrode **108a** und eine Drain-Elektrode **108b**, die über dem Zwischenschicht-Isolierfilm **114** ausgebildet sind und elektrisch mit dem Oxidhalbleiterfilm **106** verbunden sind.

**[0134]** Der Oxidhalbleiterfilm **106** beinhaltet den Bereich **106c** und den Bereich **106d**, die als Kanalbildungsbereich dienen, und den Bereich **106e** und den Bereich **106f**, die als Paar von niederohmigen Bereichen dienen, welche derart bereitgestellt sind, dass der Kanalbildungsbereich dazwischen liegt.

**[0135]** Wie in **Fig. 3B** gezeigt ist, verjüngt sich ferner ein Endbereich des Oxidhalbleiterfilms **106** vorzugsweise unter einem Winkel von 20° bis 50°. Wenn der Oxidhalbleiterfilm **106** einen senkrechten Endbereich hat, wird Sauerstoff mit höherer Wahrscheinlichkeit von dem Endbereich des Oxidhalbleiterfilms **106** abgegeben; somit werden Sauerstofffehlstellen (oxygen vacancies) wahrscheinlich erzeugt. Wenn der Oxidhalbleiterfilm **106** einen sich verjüngenden Endbereich hat, wird eine Erzeugung von Sauerstofffehlstellen unterdrückt, und daher kann eine Erzeugung von Leckstrom des Transistors **160** verringert werden.

**[0136]** Für den Gate-Isolierfilm **110** wird vorzugsweise ein Oxidisolierfilm, der eine ausreichende Spannungsfestigkeit und ausreichende isolierende Eigenschaften aufweist, verwendet. In dem Fall, in dem der Gate-Isolierfilm **110** eine einschichtige Struktur hat, kann beispielsweise ein Oxid, das Silizium enthält, wie z. B. ein Siliziumoxidfilm verwendet werden.

**[0137]** Wenn ein Oxid, das Silizium enthält, als der Gate-Isolierfilm **110** verwendet wird, kann ein Teil des Sauerstoffs, der in dem Isolierfilm enthalten ist, durch eine Wärmebehandlung abgegeben werden. Daher kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, und Sauerstofffehlstellen in dem Oxidhalbleiterfilm **106** können gefüllt werden. Insbesondere enthält vorzugsweise der Gate-Isolierfilm **110** eine große Menge an Sauerstoff, die zumindest seine Stöchiometrie überschreitet. Beispielsweise wird ein Film von Siliziumoxid, das durch die Formel  $\text{SiO}_{2+\alpha}$  ( $\alpha > 0$ ) dargestellt wird, vorzugsweise als der Gate-Isolierfilm **110** verwendet. Wenn ein derartiger Siliziumoxidfilm als der Gate-Isolierfilm **110** verwendet wird, kann Sauerstoff zu dem Oxidhalbleiterfilm **106** zugeführt werden, so dass der Transistor **160**, bei dem der Oxidhalbleiterfilm **106** verwendet wird, vorteilhafte Transistoreigenschaften aufweisen kann.

**[0138]** Jedoch könnte im Fall der Verwendung eines Siliziumoxidfilms als der Gate-Isolierfilm **110** Silizium, das ein Bestandteil des Gate-Isolierfilms **110** ist, als Verunreinigung in den Oxidhalbleiterfilm **106** aufgenommen werden. Silizium, das ein Bestandteil des Gate-Isolierfilms **110** oder dergleichen ist, dringt in den Oxidhalbleiterfilm **106** ein, und dient als Verunreinigung, die die Eigenschaften des Transistors beeinflusst. Ferner dringt in dem Fall, in dem der Oxidhalbleiterfilm **106** ein CAAC-OS-Film ist, ein Bestandteil des Gate-Isolierfilms **110** in den Oxidhalbleiterfilm **106** ein, und eine Bindung in dem Kristallbereich in dem Oxidhalbleiterfilm **106** wird

aufgebrochen. Deshalb werden mehr amorphe Bereiche in dem Oxidhalbleiterfilm **106** in der Nähe des Gate-Isolierfilms **110** ausgebildet.

**[0139]** Insbesondere dringen wahrscheinlich Verunreinigungen wie z. B. Silizium in den Oxidhalbleiterfilm **106** in der Nähe des Gate-Isolierfilms **110** ein. Ein Kanalbildungsbereich des Transistors **160** wird in dem Oxidhalbleiterfilm **106** in der Nähe der Grenzfläche zu dem Gate-Isolierfilm **110** ausgebildet; somit könnten die Eigenschaften des Transistors **150** verändert werden, wenn Verunreinigungen wie z. B. Silizium in die Nähe der Grenzfläche zwischen dem Oxidhalbleiterfilm **106** und dem Gate-Isolierfilm **110** eindringen.

**[0140]** Somit wird in der Halbleitervorrichtung, die bei dieser Ausführungsform beschrieben wird, das Eindringen von Verunreinigungen wie z. B. Silizium in den Oxidhalbleiterfilm **106** in der Nähe der Grenzfläche zu dem Gate-Isolierfilm **110** unterdrückt. Folglich wird in dem Oxidhalbleiterfilm **106** ein Bereich ausgebildet, in dem die Konzentration von Silizium, das von einer Grenzfläche zu dem Gate-Isolierfilm **110** zum Inneren des Oxidhalbleiterfilms **106** hin verteilt wird, niedriger als oder gleich 1,0 Atom-% ist. Ein derartiger Bereich wird in **Fig. 3B** der Bereich **106c** und der Bereich **106e** genannt. Die Konzentrationen von Silizium in dem Bereich **106c** und dem Bereich **106e** sind stärker bevorzugt niedriger als oder gleich 0,1 Atom-%. Außerdem sind der Bereich **106c** und der Bereich **106e** in Kontakt mit dem Gate-Isolierfilm **110** bereitgestellt und haben eine Dicke von kleiner als oder gleich 5 nm.