(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7003003号

(P7003003)

(45)発行日 令和4年1月20日(2022.1.20)

(24)登録日 令和4年1月5日(2022.1.5)

(51)国際特許分類

H 0 2 M 3/07 (2006.01)F I

H 0 2 M 3/07

請求項の数 6 (全20頁)

(21)出願番号 特願2018-117743(P2018-117743)

(22)出願日 平成30年6月21日(2018.6.21)

(65)公開番号 特開2019-221087(P2019-221087)

A)

(43)公開日 令和1年12月26日(2019.12.26)

審査請求日 令和2年11月11日(2020.11.11)

(73)特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74)代理人 100103894

弁理士 家入 健

永松 健一

東京都江東区豊洲三丁目2番24号 ル

ネサスエレクトロニクス株式会社内

審査官 佐藤 匡

最終頁に続く

(54)【発明の名称】 電源回路

## (57)【特許請求の範囲】

## 【請求項1】

外部出力電圧に応じた分圧電圧と、第1基準電圧及び第2基準電圧のそれぞれと、を比較して、比較結果を出力する比較部と、

前記比較部による比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、

前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、

を備え、

前記比較部は、

前記分圧電圧と、前記第1及び第2基準電圧のうち選択された何れかの基準電圧と、を比較して、前記比較部による比較結果として出力するコンパレータと、

前記コンパレータによる比較結果に基づいて、前記第1基準電圧及び前記第2基準電圧の何れかを選択し、前記選択された基準電圧として出力する選択回路と、

を有し、

前記選択回路は、前記分圧電圧が前記選択された基準電圧以上であることを示す比較結果が前記コンパレータから出力された場合に、前記第2基準電圧から前記第2基準電圧よりも高い前記第1基準電圧に選択を切り替えて、前記選択された基準電圧として出力し、かつ、前記分圧電圧が前記選択された基準電圧未満であることを示す比較結果が前記コンパレータから出力された場合に、前記第1基準電圧から前記第2基準電圧に選択を切り替

えて、前記選択された基準電圧として出力する、

電源回路。

【請求項 2】

外部出力電圧に応じた分圧電圧と、第1基準電圧及び第2基準電圧のそれぞれと、を比較して、比較結果を出力する比較部と、

前記比較部による比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、

前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、

前記外部出力電圧の変動幅を測定する測定回路と、

前記測定回路による測定結果に基づいて、前記第1基準電圧及び前記第2基準電圧の値を調整する調整回路と、

を備え、

前記比較部は、

前記分圧電圧と、前記第1及び第2基準電圧のうち選択された何れかの基準電圧と、を比較して、前記比較部による比較結果として出力するコンパレータと、

前記コンパレータによる比較結果に基づいて、前記第1基準電圧及び前記第2基準電圧の何れかを選択し、前記選択された基準電圧として出力する選択回路と、

を有する、

電源回路。

【請求項 3】

外部出力電圧に応じた分圧電圧と、第1基準電圧及び第2基準電圧のそれぞれと、を比較して、比較結果を出力する比較部と、

前記比較部による比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、

前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、

を備え、

前記比較部は、

前記分圧電圧と、前記第1基準電圧と、を比較する第1コンパレータと、

前記分圧電圧と、前記第2基準電圧と、を比較する第2コンパレータと、

前記第1コンパレータ及び前記第2コンパレータのそれぞれの比較結果に応じた電圧を、前記比較部による比較結果として出力する制御回路と、

を有し、

前記制御回路は、

前記第1コンパレータによる比較結果と、前記第2コンパレータによる比較結果との排他的論理和を出力する排他的論理和回路と、

前記排他的論理和回路の出力電圧の立ち上がりに同期して、前記制御回路の出力電圧を反転させるフリップフロップ回路と、

を有する、

電源回路。

【請求項 4】

外部出力電圧に応じた分圧電圧と、第1基準電圧及び第2基準電圧のそれぞれと、を比較して、比較結果を出力する比較部と、

前記比較部による比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、

前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、

前記外部出力電圧の変動幅を測定する測定回路と、

前記測定回路による測定結果に基づいて、前記第1基準電圧及び前記第2基準電圧の値

10

20

30

40

50

を調整する調整回路と、

を備え、

前記比較部は、

前記分圧電圧と、前記第1基準電圧と、を比較する第1コンパレータと、

前記分圧電圧と、前記第2基準電圧と、を比較する第2コンパレータと、

前記第1コンパレータ及び前記第2コンパレータのそれぞれの比較結果に応じた電圧を

、前記比較部による比較結果として出力する制御回路と、

を有する、

電源回路。

**【請求項5】**

外部出力電圧に応じた第1分圧電圧及び第2分圧電圧のうち選択された何れかの分圧電圧と、基準電圧と、を比較するコンパレータと、

前記コンパレータによる比較結果に基づいて、前記第1分圧電圧及び前記第2分圧電圧の何れかを選択し、前記選択された分圧電圧として出力する選択回路と、

前記コンパレータによる比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、

前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、

を備え、

前記選択回路は、前記選択された分圧電圧が前記基準電圧以上であることを示す比較結果が前記コンパレータから出力された場合に、第1分圧電圧から前記第1分圧電圧よりも低い前記第2分圧電圧に選択を切り替えて、前記選択された分圧電圧として出力し、かつ、

前記選択された分圧電圧が前記基準電圧未満であることを示す比較結果が前記コンパレータから出力された場合に、前記第2分圧電圧から前記第1分圧電圧に選択を切り替えて、

前記選択された分圧電圧として出力する、

電源回路。

**【請求項6】**

外部出力電圧に応じた第1分圧電圧及び第2分圧電圧のうち選択された何れかの分圧電圧と、基準電圧と、を比較するコンパレータと、

前記コンパレータによる比較結果に基づいて、前記第1分圧電圧及び前記第2分圧電圧の何れかを選択し、前記選択された分圧電圧として出力する選択回路と、

前記コンパレータによる比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、

前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、

前記外部出力電圧の変動幅を測定する測定回路と、

前記測定回路による測定結果に基づいて、前記第1分圧電圧及び前記第2分圧電圧の値を調整する調整回路と、

を備えた電源回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は電源回路に関し、例えば安定した出力電圧を生成するのに適した電源回路に関する。

**【背景技術】**

**【0002】**

半導体装置では、プロセスの微細化に伴って、各トランジスタの耐圧が低下している。そのため、半導体装置を駆動するための電圧を生成する電源回路は、トランジスタが破壊しないように、リップル成分(変動幅、ゆらぎ)の少ない安定した電圧を生成することが求められている。

## 【0003】

リップル成分を抑制する技術が特許文献1に開示されている。特許文献1に開示された電源回路は、クロック信号により昇圧動作するチャージポンプと、チャージポンプの出力電圧の分圧電圧と基準電圧とを比較するコンパレータと、コンパレータによる比較結果に基づいてチャージポンプへのクロック信号の供給の可否を制御するNAND回路と、を備える。ここで、この電源回路では、コンパレータの速度が、チャージポンプの出力電圧の分圧電圧が基準電圧を上回った時点からコンパレータの出力電圧が反転するまでは速く、かつ、チャージポンプの出力電圧の分圧電圧が基準電圧を下回った時点からコンパレータの出力電圧が反転するまでは遅くなるように制御される。それにより、この電源回路は、負荷への出力電流が小さい場合に、チャージポンプの出力電圧のリップル成分を抑制することができる。

10

## 【先行技術文献】

## 【特許文献】

## 【0004】

【文献】特開2005-278383号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

しかしながら、特許文献1に開示された構成では、コンパレータの速度が、チャージポンプの出力電圧の分圧電圧が基準電圧を下回った時点からコンパレータの出力電圧が反転するまでは遅くなるように制御されるため、負荷への出力電流が大きくなるほど、チャージポンプの出力電圧のリップル成分が大きくなってしまうという問題があった。その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

20

## 【課題を解決するための手段】

## 【0006】

一実施の形態によれば、電源回路は、外部出力電圧に応じた分圧電圧と、第1基準電圧及び第2基準電圧のそれぞれと、を比較して、比較結果を出力する比較部と、前記比較部による比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、を備える。

30

## 【0007】

また、他の実施の形態によれば、電源回路は、外部出力電圧に応じた第1分圧電圧及び第2分圧電圧のうち選択された何れかの分圧電圧と、基準電圧と、を比較するコンパレータと、前記コンパレータによる比較結果に基づいて、前記第1分圧電圧及び前記第2分圧電圧の何れかを選択し、前記選択された分圧電圧として出力する選択回路と、前記コンパレータによる比較結果に基づいてクロック信号の出力の可否を制御する第1イネーブル回路と、前記クロック信号が前記第1イネーブル回路を介して供給された場合に、前記外部出力電圧を昇圧する昇圧回路と、を備える。

## 【発明の効果】

## 【0008】

前記一実施の形態によれば、負荷への出力電流の大きさに関係なく、安定した出力電圧を生成することができる電源回路を提供することができる。

40

## 【図面の簡単な説明】

## 【0009】

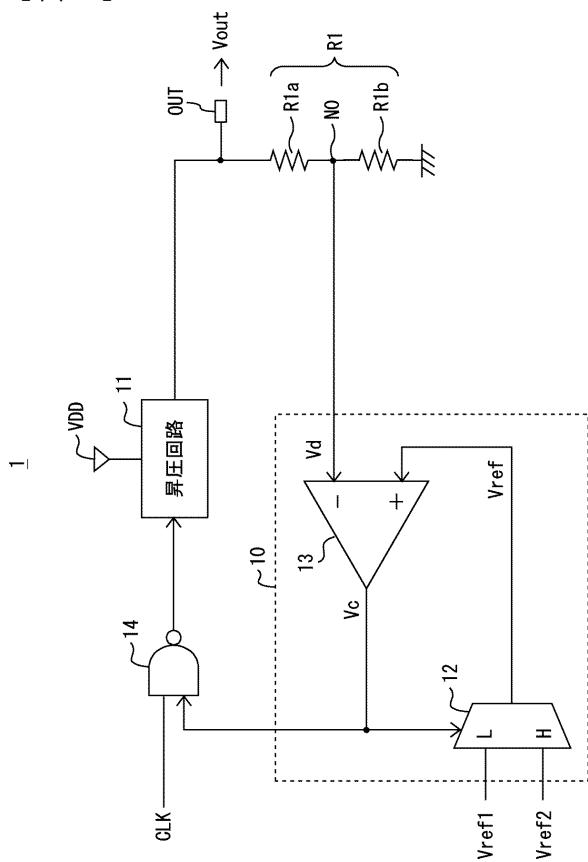

【図1】実施の形態1にかかる電源回路の構成例を示す図である。

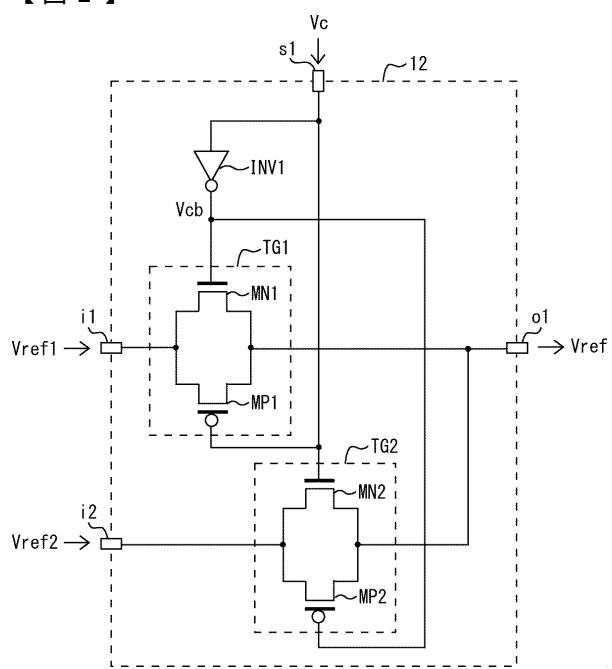

【図2】図1に示す電源回路に設けられた選択回路の具体的な構成例を示す図である。

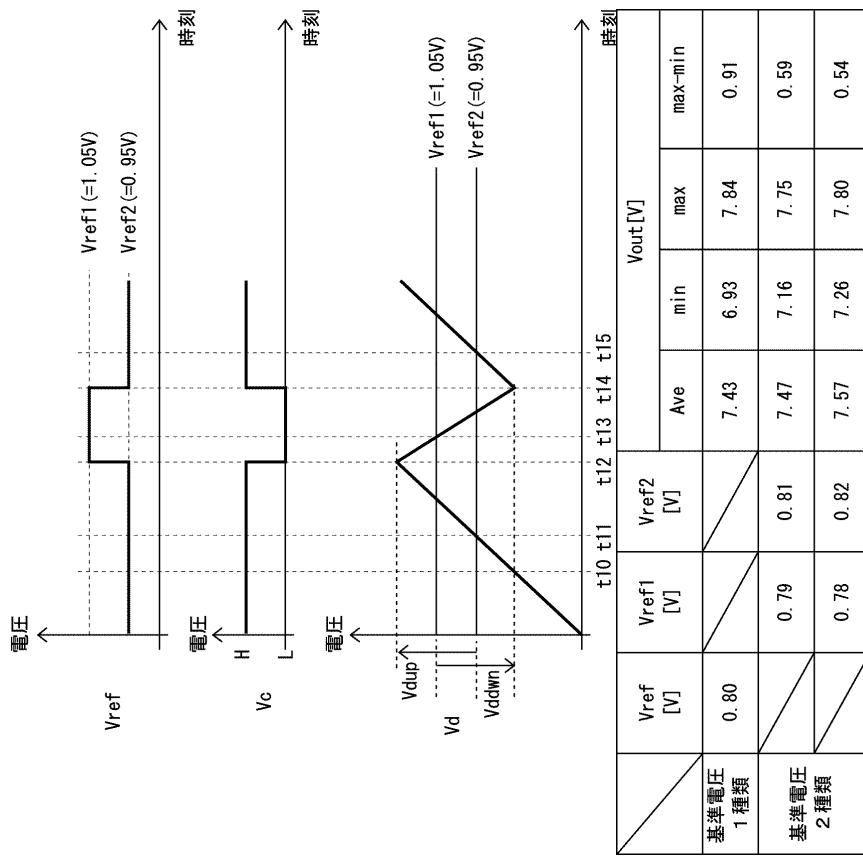

【図3】図1に示す電源回路の動作を示すタイミングチャートである。

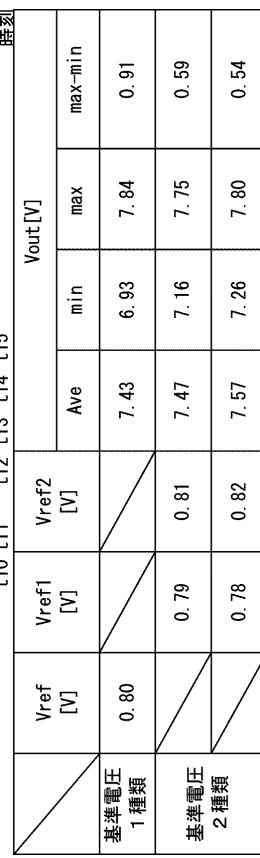

【図4】基準電圧V<sub>ref</sub>に使用される2種類の基準電圧V<sub>ref1</sub>, V<sub>ref2</sub>の設定値と、出力電圧V<sub>out</sub>と、の関係を示す図である。【図5】出力端子OUTに付加される安定化容量の容量値と、出力電圧V<sub>out</sub>と、の関

50

係を示す図である。

【図6】実施の形態1にかかる電源回路の変形例を示す図である。

【図7】実施の形態2にかかる電源回路の構成例を示す図である。

【図8】図7に示す電源回路の動作を示すタイミングチャートである。

【図9】実施の形態2にかかる電源回路の変形例を示す図である。

【図10】実施の形態3にかかる電源回路の構成例を示す図である。

【図11】図10に示す電源回路に設けられた制御回路の具合的な構成例を示す図である。

【図12】図11に示す制御回路の動作を示すタイミングチャートである。

【図13】実施の形態2にかかる電源回路の変形例を示す図である。

【発明を実施するための形態】

10

【0010】

説明の明確化のため、以下の記載及び図面は、適宜、省略、及び簡略化がなされている。また、様々な処理を行う機能ブロックとして図面に記載される各要素は、ハードウェア的には、CPU(Central Processing Unit)、メモリ、その他の回路で構成することができ、ソフトウェア的には、メモリにロードされたプログラムなどによって実現される。したがって、これらの機能ブロックがハードウェアのみ、ソフトウェアのみ、またはそれらの組合せによっていろいろな形で実現できることは当業者には理解されるところであり、いずれかに限定されるものではない。なお、各図面において、同一の要素には同一の符号が付されており、必要に応じて重複説明は省略されている。

【0011】

20

また、上述したプログラムは、様々なタイプの非一時的なコンピュータ可読媒体を用いて格納され、コンピュータに供給することができる。非一時的なコンピュータ可読媒体は、様々なタイプの実体のある記録媒体を含む。非一時的なコンピュータ可読媒体の例は、磁気記録媒体(例えばフレキシブルディスク、磁気テープ、ハードディスクドライブ)、光磁気記録媒体(例えば光磁気ディスク)、CD-ROM(Read Only Memory)、CD-R、CD-R/W、半導体メモリ(例えば、マスクROM、PROM(Programmable ROM)、EPROM(Erasable PROM)、フラッシュROM、RAM(Random Access Memory))を含む。また、プログラムは、様々なタイプの一時的なコンピュータ可読媒体によってコンピュータに供給されてもよい。一時的なコンピュータ可読媒体の例は、電気信号、光信号、及び電磁波を含む。一時的なコンピュータ可読媒体は、電線及び光ファイバ等の有線通信路、又は無線通信路を介して、プログラムをコンピュータに供給できる。

30

【0012】

<実施の形態1>

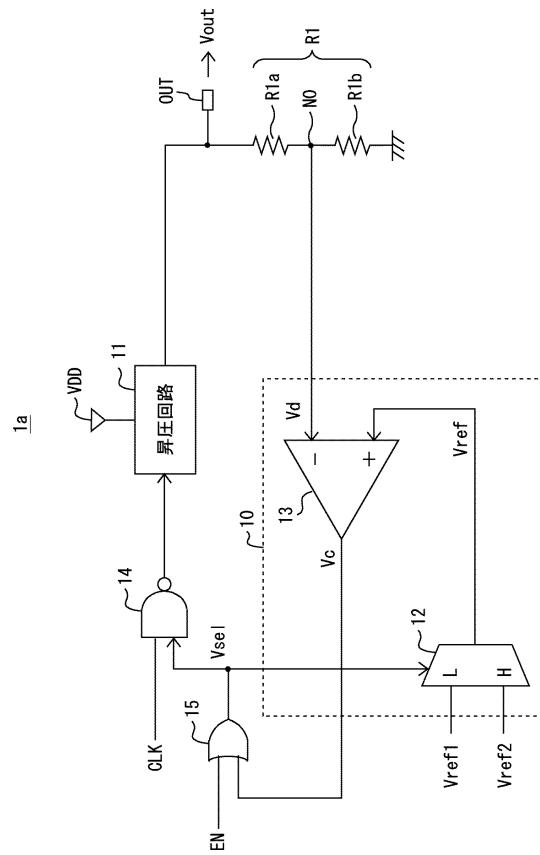

図1は、実施の形態1にかかる電源回路1の構成例を示す図である。

図1に示すように、電源回路1は、昇圧回路11と、選択回路12と、コンパレータ13と、否定論理積回路(以下、NAND回路と称す)14と、抵抗素子R1と、を備える。選択回路12及びコンパレータ13によって比較部10が構成されている。

【0013】

40

昇圧回路11は、所謂チャージポンプであって、クロック信号CLKが供給されることによって電圧Voutを昇圧させる。なお、昇圧回路11は、クロック信号CLKが供給されない場合には、電圧Voutの昇圧を行わない。この場合、電圧Voutは下降する。昇圧回路11の出力電圧Voutは、電源回路1の出力端子OUTを介して外部に出力される。

【0014】

抵抗素子R1は、抵抗素子R1a, R1bによって構成され、電源回路1の出力端子OUTと、接地電圧端子GNDとの間に直列に設けられている。抵抗素子R1は、抵抗素子R1a, R1b間のノードN0の電圧Vdを出力する。換言すると、抵抗素子R1は、電源回路1の出力端子OUTの電圧Voutを、抵抗素子R1a, R1bの抵抗比で分圧して、分圧電圧Vdとして出力する。

50

## 【0015】

選択回路12は、コンパレータ13から出力される電圧 $V_c$ に基づいて、基準電圧 $V_{ref1}$ 及び基準電圧 $V_{ref2}$ の何れかを選択して基準電圧 $V_{ref}$ として出力する。なお、本実施の形態では、基準電圧 $V_{ref1}$ が基準電圧 $V_{ref2}$ よりも大きい場合を例に説明する。

## 【0016】

例えば、コンパレータ13からLレベルの電圧 $V_c$ が出力されている場合、選択回路12は、基準電圧 $V_{ref1}$ を選択して基準電圧 $V_{ref}$ として出力する。それに対し、コンパレータ13からHレベルの電圧 $V_c$ が出力されている場合、選択回路12は、基準電圧 $V_{ref2}$ を選択して基準電圧 $V_{ref}$ として出力する。

10

## 【0017】

## (選択回路12の具体的な構成例)

図2は、選択回路12の具体的な構成例を示す回路図である。

図2に示すように、選択回路12は、インバータINV1と、トランスマスファゲートTG1と、トランスマスファゲートTG2と、を有する。トランスマスファゲートTG1は、PチャネルMOSトランジスタMP1及びNチャネルMOSトランジスタMN1からなる。トランスマスファゲートTG2は、PチャネルMOSトランジスタMP2及びNチャネルMOSトランジスタMN2からなる。

## 【0018】

トランスマスファゲートTG1は、外部から基準電圧 $V_{ref1}$ が供給される選択回路12の入力端子i1と、選択回路12の出力端子o1と、の間に設けられ、コンパレータ13から選択回路12の入力端子s1を介して供給された電圧 $V_c$ 、及び、当該電圧 $V_c$ をインバータINV1によって論理反転させた電圧 $V_{cb}$ に基づいて、オンオフを切り替える。トランスマスファゲートTG1は、外部から基準電圧 $V_{ref2}$ が供給される選択回路12の入力端子i2と、選択回路12の出力端子o1と、の間に設けられ、コンパレータ13から選択回路12の入力端子s1を介して供給された電圧 $V_c$ 、及び、当該電圧 $V_c$ をインバータINV1によって論理反転させた電圧 $V_{cb}$ に基づいて、トランスマスファゲートTG1と相補的にオンオフを切り替える。

20

## 【0019】

具体的には、トランスマスファゲートTG1において、トランジスタMP1, MN1は、選択回路12の入力端子i1と、選択回路12の出力端子o1と、の間に並列に設けられ、それぞれゲートに供給された電圧 $V_c$ ,  $V_{cb}$ に基づいてオンオフを切り替える。トランスマスファゲートTG2において、トランジスタMP2, MN2は、選択回路12の入力端子i2と、選択回路12の出力端子o1と、の間に並列に設けられ、それぞれゲートに供給された電圧 $V_{cb}$ ,  $V_c$ に基づいて、トランジスタMP1, MN1と相補的にオンオフを切り替える。

30

## 【0020】

例えば、コンパレータ13からLレベルの電圧 $V_c$ が出力された場合、トランスマスファゲートTG1はオンし、かつ、トランスマスファゲートTG2はオフする。そのため、選択回路12は、基準電圧 $V_{ref1}$ を基準電圧 $V_{ref}$ として出力端子o1から出力する。それに対し、コンパレータ13からHレベルの電圧 $V_c$ が出力された場合、トランスマスファゲートTG1はオフし、かつ、トランスマスファゲートTG2はオンする。そのため、選択回路12は、基準電圧 $V_{ref2}$ を基準電圧 $V_{ref}$ として出力端子o1から出力する。

40

## 【0021】

なお、選択回路12の構成は、図2に示す構成に限られず、図2に示す構成と同等の機能を実現可能な他の構成に適宜変更可能である。

## 【0022】

図1に戻り、説明を続ける。

コンパレータ13は、分圧電圧 $V_d$ と基準電圧 $V_{ref}$ とを比較して、比較結果である電圧 $V_c$ を出力する。理想的には、コンパレータ13は、電圧 $V_d$ が基準電圧 $V_{ref}$ 以上

50

の場合にLレベルの電圧Vcを出力し、電圧Vdが基準電圧Vref未満の場合にHレベルの電圧Vcを出力する。

【0023】

NAND回路14は、所謂イネーブル回路であって、コンパレータ13の出力電圧Vcに基づいて、昇圧回路11に対してクロック信号CLKを出力するか否かを制御する。例えば、コンパレータ13からLレベルの信号が出力されている場合、NAND回路14は、クロック信号CLKに関わらずHレベルの信号を出力する。つまり、NAND回路14は、昇圧回路11へのクロック信号CLKの供給を停止させる。このとき、昇圧回路11は、出力電圧Voutの昇圧を行わない。それに対し、コンパレータ13からHレベルの信号が出力されている場合、NAND回路14は、昇圧回路11へのクロック信号CLK(厳密に言えば、本例ではクロック信号CLKの反転信号)の供給を行う。このとき、昇圧回路11は、出力電圧Voutを昇圧させる。なお、NAND回路14は、例えば論理積回路(AND回路)など、コンパレータ13の出力電圧Vcに基づいて昇圧回路11へのクロック信号CLKの供給の可否を制御可能な他の回路に適宜変更可能である。

10

【0024】

(電源回路1の動作)

続いて、図3を用いて、電源回路1の動作について説明する。

図3は、電源回路1の動作を示すタイミングチャートである。なお、以下では、昇圧回路11を駆動する電源電圧VDDが2V、昇圧回路11の出力電圧Voutのターゲット電圧が10V、抵抗素子R1a, R1bの抵抗比R1a : R1bが9:1、基準電圧Vref1が1.05V、基準電圧Vref2が0.95Vである場合を例に説明する。

20

【0025】

図3に示すように、昇圧回路11による出力電圧Voutの昇圧開始直後は、出力電圧Voutは、電源電圧VDD(=2V)以上、かつ、ターゲット電圧(=10V)以下を示している(時刻t10)。例えば、出力電圧Voutが5Vを示す場合、出力電圧Voutの分圧電圧Vdは0.5Vを示す。このとき、分圧電圧Vdは、選択回路12によって基準電圧Vref1, Vref2の何れが基準電圧Vrefとして選択されているかに関わらず、基準電圧Vrefよりも小さくなる。そのため、コンパレータ13は、Hレベルの電圧Vcを出力する。

30

【0026】

コンパレータ13からHレベルの電圧Vcが出力されている場合、選択回路12は、基準電圧Vref2(=0.95V)を選択して基準電圧Vrefとして出力する。また、このとき、NAND回路14は、昇圧回路11へのクロック信号CLKの供給を行う。それにより、昇圧回路11は、出力電圧Voutの昇圧を継続する。

【0027】

出力電圧Voutが上昇すると、それに伴って、出力電圧Voutの分圧電圧Vdも上昇する。したがって、しばらくすると、分圧電圧Vdは、基準電圧Vref(=0.95V)に達する(時刻t11)。しかしながら、コンパレータ13は、コンパレータ13のオフセット電圧、コンパレータ13の反応速度、及び、昇圧回路11によって決まる出力電圧Voutの昇圧速度などの影響を受けて、出力電圧VcをHレベルに維持する。

40

【0028】

その後、出力電圧Voutがさらに上昇し、それに伴って、分圧電圧Vdが上昇すると、コンパレータ13は、出力電圧VcをHレベルからLレベルに切り替える(時刻t12)。例えば、出力電圧Voutがターゲット電圧(=10V)を超えて11Vを示す場合、出力電圧Voutの分圧電圧Vdは1.1Vを示す。このとき、分圧電圧Vdは、基準電圧Vref(=1.05V)よりも大きくなるため、コンパレータ13は、Lレベルの電圧Vcを出力する。

【0029】

それにより、選択回路12は、基準電圧Vref2から基準電圧Vref1(=1.05V)に選択を切り替えて基準電圧Vrefとして出力する。また、このとき、NAND回

50

路14は、昇圧回路11へのクロック信号CLKの供給を停止させる。それにより、昇圧回路11は、出力電圧Voutの昇圧を停止させる。それにより、出力電圧Voutは、下降し始める。

【0030】

出力電圧Voutが下降すると、それに伴って、出力電圧Voutの分圧電圧Vdも下降する。したがって、しばらくすると、分圧電圧Vdは、基準電圧Vref(=1.05V)に達する(時刻t13)。しかしながら、コンパレータ13は、コンパレータ13のオフセット電圧、コンパレータ13の反応速度、及び、昇圧回路11の出力電流負荷によって決まる出力電圧Voutの下降速度などの影響を受けて、出力電圧VcをLレベルに維持する。

10

【0031】

その後、出力電圧Voutがさらに下降し、それに伴って、分圧電圧Vdが下降すると、コンパレータ13は、出力電圧VcをLレベルからHレベルに切り替える(時刻t14)。それにより、選択回路12は、基準電圧Vref1から基準電圧Vref2(=0.95V)に選択を切り替えて基準電圧Vrefとして出力する。また、このとき、NAND回路14は、昇圧回路11へのクロック信号CLKの供給を再開させる。それにより、昇圧回路11は、出力電圧Voutの昇圧を再開させる。

【0032】

その後、時刻t15以降では、時刻t11～t15の動作が繰り返される。

20

【0033】

ここで、昇圧回路11のリップル上昇成分は、時刻t11から時刻t12にかけて上昇した分圧電圧Vdの上昇分Vdupに比例する正の値を示す。また、昇圧回路11のリップル下降成分は、時刻t13から時刻t14にかけて下降した分圧電圧Vdの下降分Vddwnに比例する負の値を示す。したがって、昇圧回路11のリップル成分は、リップル上昇成分とリップル下降成分との和、即ち、電圧Vdupと電圧Vddwnとの和に比例する値を示す。しかしながら、電圧Vdupと電圧Vddwnとは、基準電圧Vref1, Vref2間の電位差の分だけ重複している。そのため、昇圧回路11のリップル成分は、その基準電圧Vref1, Vref2間の電位差に比例する値の分だけ抑制される。

【0034】

このように、本実施の形態にかかる電源回路1は、出力電圧Voutの分圧電圧Vdと、選択的に用いられる基準電圧Vref1, Vref2の何れかと、の比較結果に基づいて、昇圧回路11による出力電圧Voutの昇圧の可否を制御している。それにより、本実施の形態にかかる電源回路1は、昇圧回路11のリップル上昇成分及びリップル下降成分を部分的に重複させることができるために、昇圧回路11の全体的なリップル成分を抑制することができる。換言すると、本実施の形態にかかる電源回路1は、負荷への出力電流の大きさに関係なく、安定した出力電圧Voutを生成することができる。

30

【0035】

なお、例えば、特許文献1のように、基準電圧Vrefに使用される電圧が1種類の場合、昇圧回路11のリップル上昇成分とリップル下降成分との重複部分がないため、昇圧回路11の全体的なリップル成分を抑制することはできない。

40

【0036】

図4は、本実施の形態にかかる電源回路1における、基準電圧Vrefに使用される2種類の基準電圧Vref1, Vref2の設定値と、出力電圧Voutとの関係を示す図である。なお、図4には、比較のため、基準電圧Vrefに使用される電圧が1種類の場合における出力電圧Voutも示されている。

【0037】

なお、図4の例では、基準電圧Vrefに使用される電圧が1種類の場合、基準電圧Vrefは0.80Vを示すものとする。また、基準電圧Vrefに使用される電圧が基準電圧Vref1, Vref2の2種類の場合、基準電圧Vref1, Vref2の平均電圧が0.80Vを示すものとする。

50

## 【0038】

図4を参照すると、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合、出力電圧  $V_{out}$  の最小値は6.93V、最大値は7.84V、平均値は7.43V、最大値と最小値の差（即ち、リップル成分）は0.91Vを示している。

## 【0039】

それに対し、基準電圧  $V_{ref}$  に使用される電圧が、0.79Vの基準電圧  $V_{ref1}$ 、及び、0.82Vの基準電圧  $V_{ref2}$  の2種類の場合、出力電圧  $V_{out}$  の最小値は7.16V、最大値は7.75V、平均値は7.47V、最大値と最小値の差（即ち、リップル成分）は0.59Vを示している。この場合、リップル成分は、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合と比較して、約35%抑制されている。

10

## 【0040】

また、基準電圧  $V_{ref}$  に使用される電圧が、0.78Vの基準電圧  $V_{ref1}$ 、及び、0.82Vの基準電圧  $V_{ref2}$  の2種類の場合、出力電圧  $V_{out}$  の最小値は7.26V、最大値は7.80V、平均値は7.57V、最大値と最小値の差（即ち、リップル成分）は0.54Vを示している。この場合、リップル成分は、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合と比較して、約41%抑制されている。

## 【0041】

図5は、本実施の形態にかかる電源回路における、出力端子OUTに付加される安定化容量の容量値と、出力電圧  $V_{out}$  との関係を示す図である。なお、図5には、比較のため、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合における出力電圧  $V_{out}$  も示されている。

20

## 【0042】

なお、図5の例では、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合、基準電圧  $V_{ref}$  が0.80Vを示し、かつ、安定化容量が16pFを示すものとする。また、基準電圧  $V_{ref}$  に使用される電圧が基準電圧  $V_{ref1}$ ,  $V_{ref2}$  の2種類の場合、基準電圧  $V_{ref1}$  が0.78V、基準電圧  $V_{ref2}$  が0.82Vを示すものとする。

## 【0043】

図5を参照すると、基準電圧  $V_{ref}$  に使用される電圧が1種類、かつ、安定化容量が16pFの場合、出力電圧  $V_{out}$  の最小値は6.93V、最大値は7.84V、平均値は7.43V、最大値と最小値の差（即ち、リップル成分）は0.91Vを示している。

30

## 【0044】

それに対し、基準電圧  $V_{ref}$  に使用される電圧が2種類、かつ、安定化容量が16pFの場合、出力電圧  $V_{out}$  の最小値は7.26V、最大値は7.80V、平均値は7.57V、最大値と最小値の差（即ち、リップル成分）は0.54Vを示している。この場合、リップル成分は、既に説明したように、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合と比較して、約41%抑制されている。

## 【0045】

ここで、安定化容量の容量値を8pFまで小さくすると、出力電圧  $V_{out}$  の最小値は7.01V、最大値は7.83V、平均値は7.52V、最大値と最小値の差（即ち、リップル成分）は0.82Vを示す。さらに、安定化容量の容量値を6pFまで小さくすると、出力電圧  $V_{out}$  の最小値は6.88V、最大値は7.95V、平均値は7.50V、最大値と最小値の差（即ち、リップル成分）は1.07Vを示す。したがって、安定化容量の容量値が7pF程度の場合に、出力電圧  $V_{out}$  のリップル成分が0.9V程度になるものと考えられる。

40

## 【0046】

つまり、基準電圧  $V_{ref}$  に使用される電圧が2種類の場合には、安定化容量の容量値を7pF程度にまで小さくしても、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合、かつ、安定化容量が16pFの場合と同等程度のリップル成分に抑えることができる。換言すると、本実施の形態にかかる電源回路11は、基準電圧  $V_{ref}$  に使用される電圧が1種類の場合と比較して、より小さな回路規模で同等のリップル成分の抑制を実現すること

50

ができる。

【0047】

(電源回路1の変形例)

図6は、電源回路1の変形例を電源回路1aとして示す図である。

電源回路1aは、電源回路1と比較して、論理和回路(以下、OR回路と称す)15をさらに備える。

【0048】

OR回路15は、所謂イネーブル回路であって、外部から供給されたイネーブル信号ENと、コンパレータ13から出力された電圧Vcと、の論理和を、電圧Vselとして出力する。なお、イネーブル信号ENは、例えば、昇圧回路11又はその周辺回路の動作の可否を制御するために用いられているイネーブル信号と共に用いられても良い。

10

【0049】

OR回路15は、イネーブル信号ENがHレベルの場合、コンパレータ13の出力電圧Vcに関わらずHレベルの電圧Vselを出力し、イネーブル信号ENがLレベルの場合、コンパレータ13の出力電圧Vcをそのまま電圧Vselとして出力する。この電圧Vselは、電圧Vcの代わりに、選択回路12及びNAND回路14に入力される。

【0050】

例えば、電源起動直後の所定期間、イネーブル信号ENはHレベルに設定される。それにより、コンパレータ13の出力電圧Vcが不安定な場合でも、選択回路12及びNAND回路14に入力される電圧Vselを安定したレベル(Hレベル)に固定することができる。そして、所定期間経過後、コンパレータ13の出力電圧Vcが安定すると、イネーブル信号ENはHレベルからLレベルに切り替わる。それにより、安定したコンパレータ13の出力電圧Vcを、電圧Vselとして、選択回路12及びNAND回路14に入力することができる。

20

【0051】

なお、OR回路15は、イネーブル信号ENに基づいてコンパレータ13の出力電圧Vc及び固定電圧の何れかを電圧Vselとして出力することが可能な他の回路に適宜変更可能である。

【0052】

<実施の形態2>

30

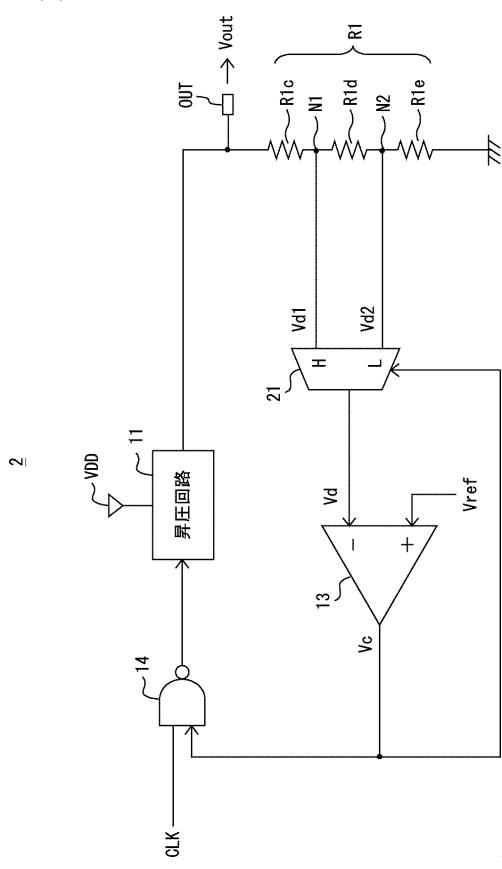

図7は、実施の形態2にかかる電源回路2の構成例を示す図である。電源回路2は、電源回路1と比較して、選択回路12の代わりに選択回路21を備える。また、電源回路2には、基準電圧Vref1, Vref2が供給される代わりに基準電圧Vrefのみが供給されている。さらに、抵抗素子R1は、抵抗素子R1a, R1bの代わりに、抵抗素子R1c, R1d, R1eによって構成されている。以下、具体的に説明する。

【0053】

図7に示すように、電源回路2は、昇圧回路11と、選択回路21と、コンパレータ13と、NAND回路14と、抵抗素子R1と、を備える。

【0054】

抵抗素子R1は、抵抗素子R1c, R1d, R1eによって構成され、電源回路2の出力端子OUTと、接地電圧端子GNDと、の間に直列に設けられている。抵抗素子R1は、抵抗素子R1c, R1d間のノードN1の電圧Vd1を出力するとともに、抵抗素子R1d, R1e間のノードN2の電圧Vd2を出力する。換言すると、抵抗素子R1は、電源回路2の出力端子OUTの電圧Voutを、抵抗素子R1cと抵抗素子R1d, R1eとの抵抗比で分圧して電圧Vd1として出力するとともに、抵抗素子R1c, R1dと抵抗素子R1eとの抵抗比で分圧して電圧Vd2として出力する。

40

【0055】

選択回路21は、コンパレータ13から出力される電圧Vcに基づいて、分圧電圧Vd1及び分圧電圧Vd2の何れかを選択して分圧電圧Vdとして出力する。なお、本実施の形態では、分圧電圧Vd1が分圧電圧Vd2よりも大きい場合を例に説明する。

50

## 【0056】

例えば、コンパレータ13からLレベルの電圧 $V_c$ が出力されている場合、選択回路21は、分圧電圧 $V_d2$ を選択して分圧電圧 $V_d$ として出力する。それに対し、コンパレータ13からHレベルの電圧 $V_c$ が出力されている場合、選択回路21は、分圧電圧 $V_d1$ を選択して分圧電圧 $V_d$ として出力する。

## 【0057】

電源回路2のその他の構成については、電源回路1の場合と同様であるため、その説明を省略する。

## 【0058】

## (電源回路2の動作)

10

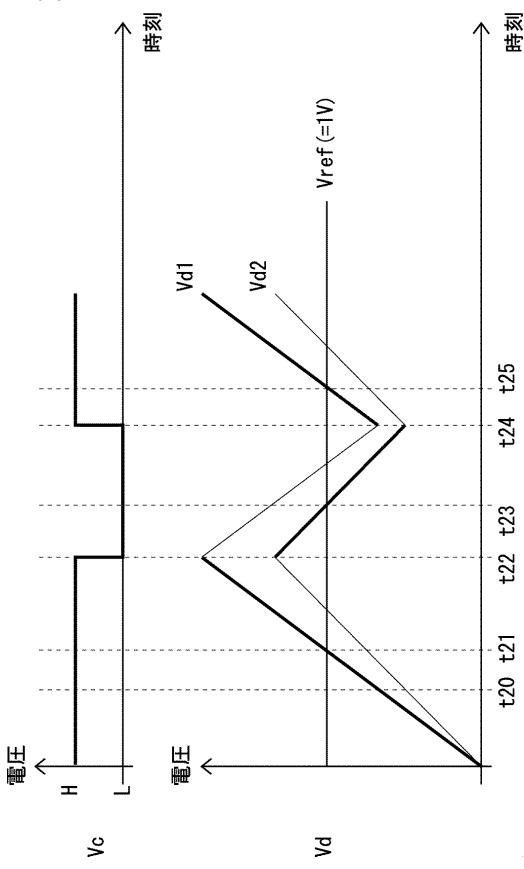

続いて、図8を用いて、電源回路2の動作について説明する。

図8は、電源回路2の動作を示すタイミングチャートである。なお、以下では、昇圧回路11を駆動する電源電圧 $V_{DD}$ が2V、昇圧回路11の出力電圧 $V_{out}$ のターゲット電圧が10V、抵抗素子 $R_{1c}$ ,  $R_{1d}$ ,  $R_{1e}$ の抵抗比 $R_{1c} : R_{1d} : R_{1e}$ が8.95:0.1:0.95、基準電圧 $V_{ref}$ が1Vである場合を例に説明する。

## 【0059】

図8に示すように、昇圧回路11による出力電圧 $V_{out}$ の昇圧開始直後は、出力電圧 $V_{out}$ は、電源電圧 $V_{DD}$ (=2V)以上、かつ、ターゲット電圧(=10V)以下を示している(時刻 $t_{20}$ )。例えば、出力電圧 $V_{out}$ が5Vを示す場合、分圧電圧 $V_d1$ は0.525Vを示し、分圧電圧 $V_d2$ は0.475Vを示す。このとき、基準電圧 $V_{ref}$ (=1V)は、選択回路21によって分圧電圧 $V_d1$ ,  $V_d2$ のうち何れが分圧電圧 $V_d$ として選択されているかに関わらず、分圧電圧 $V_d$ よりも大きくなる。そのため、コンパレータ13は、Hレベルの電圧 $V_c$ を出力する。

20

## 【0060】

コンパレータ13からHレベルの電圧 $V_c$ が出力されている場合、選択回路21は、分圧電圧 $V_d1$ (=0.525V)を選択して分圧電圧 $V_d$ として出力する。また、このとき、NAND回路14は、昇圧回路11へのクロック信号CLKの供給を行う。それにより、昇圧回路11は、出力電圧 $V_{out}$ の昇圧を継続する。

## 【0061】

出力電圧 $V_{out}$ が上昇すると、それに伴って、出力電圧 $V_{out}$ の分圧電圧 $V_d$ (ここでは、 $V_d = V_d1$ )も上昇する。したがって、しばらくすると、分圧電圧 $V_d$ は、基準電圧 $V_{ref}$ (=1V)に達する(時刻 $t_{21}$ )。しかしながら、コンパレータ13は、コンパレータ13のオフセット電圧、コンパレータ13の反応速度、及び、昇圧回路11によって決まる出力電圧 $V_{out}$ の昇圧速度などの影響を受けて、出力電圧 $V_c$ をHレベルに維持する。

30

## 【0062】

その後、出力電圧 $V_{out}$ がさらに上昇し、それに伴って、分圧電圧 $V_d$ が上昇すると、コンパレータ13は、出力電圧 $V_c$ をHレベルからLレベルに切り替える(時刻 $t_{22}$ )。例えば、出力電圧 $V_{out}$ がターゲット電圧(=10V)を超えて11Vを示す場合、分圧電圧 $V_d1$ は1.155Vを示し、分圧電圧 $V_d2$ は1.045Vを示す。このとき、分圧電圧 $V_d$ (=1.155V)は、基準電圧 $V_{ref}$ (=1V)よりも大きくなるため、コンパレータ13は、Lレベルの電圧 $V_c$ を出力する。

40

## 【0063】

それにより、選択回路21は、分圧電圧 $V_d1$ から分圧電圧 $V_d2$ に選択を切り替えて分圧電圧 $V_d$ として出力する。また、このとき、NAND回路14は、昇圧回路11へのクロック信号CLKの供給を停止させる。それにより、昇圧回路11は、出力電圧 $V_{out}$ の昇圧を停止させる。それにより、出力電圧 $V_{out}$ は、下降し始める。

## 【0064】

出力電圧 $V_{out}$ が下降すると、それに伴って、出力電圧 $V_{out}$ の分圧電圧 $V_d$ (ここでは、 $V_d = V_d2$ )も下降する。したがって、しばらくすると、分圧電圧 $V_d$ は、基準

50

電圧  $V_{ref}$  (= 1 V) に達する (時刻  $t_{23}$ )。しかしながら、コンパレータ 13 は、コンパレータ 13 のオフセット電圧、コンパレータ 13 の反応速度、及び、昇圧回路 11 の出力電流負荷によって決まる出力電圧  $V_{out}$  の下降速度などの影響を受けて、出力電圧  $V_c$  を L レベルに維持する。

【0065】

その後、出力電圧  $V_{out}$  がさらに下降し、それに伴って、分圧電圧  $V_d$  が下降すると、コンパレータ 13 は、出力電圧  $V_c$  を L レベルから H レベルに切り替える (時刻  $t_{24}$ )。それにより、選択回路 21 は、分圧電圧  $V_d2$  から分圧電圧  $V_d1$  に選択を切り替えて分圧電圧  $V_d$  として出力する。また、このとき、NAND 回路 14 は、昇圧回路 11 へのクロック信号 CLK の供給を再開させる。それにより、昇圧回路 11 は、出力電圧  $V_{out}$  の昇圧を再開させる。

10

【0066】

その後、時刻  $t_{25}$  以降では、時刻  $t_{21} \sim t_{25}$  の動作が繰り返される。

【0067】

このように、本実施の形態にかかる電源回路 2 は、基準電圧  $V_{ref}$  と、選択的に用いられる分圧電圧  $V_d1$ ,  $V_d2$  の何れかと、の比較結果に基づいて、昇圧回路 11 による出力電圧  $V_{out}$  の昇圧の可否を制御している。それにより、本実施の形態にかかる電源回路 2 は、昇圧回路 11 のリップル上昇成分及びリップル下降成分を部分的に重複させることができるために、昇圧回路 11 の全体的なリップル成分を抑制することができる。換言すると、本実施の形態にかかる電源回路 1 は、負荷への出力電流の大きさに関係なく、安定した出力電圧  $V_{out}$  を生成することができる。

20

【0068】

(電源回路 2 の変形例)

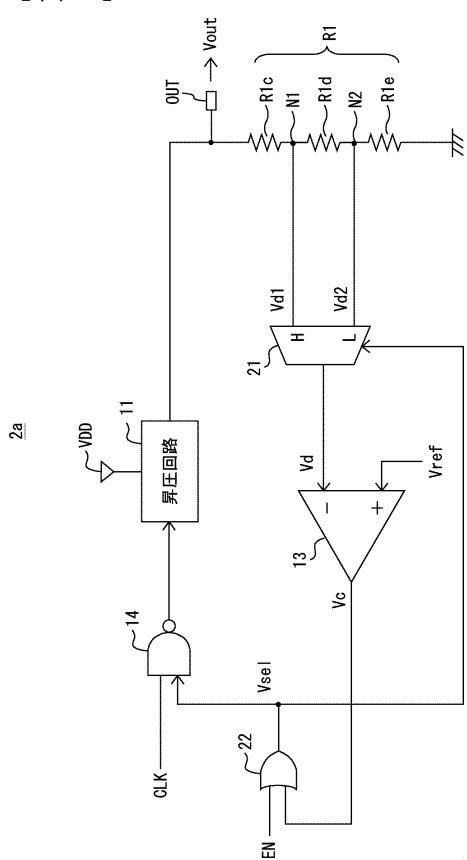

図 9 は、電源回路 2 の変形例を電源回路 2a として示す図である。

電源回路 2a は、電源回路 2 と比較して、論理和回路 (以下、OR 回路と称す) 22 をさらに備える。

【0069】

OR 回路 22 は、所謂イネーブル回路であって、外部から供給されたイネーブル信号 EN と、コンパレータ 13 から出力された電圧  $V_c$  と、の論理和を、電圧  $V_{sel}$  として出力する。なお、イネーブル信号 EN は、例えば、昇圧回路 11 又はその周辺回路の動作の可否を制御するために用いられているイネーブル信号と共に用いられても良い。

30

【0070】

OR 回路 22 は、イネーブル信号 EN が H レベルの場合、コンパレータ 13 の出力電圧  $V_c$  に関わらず H レベルの電圧  $V_{sel}$  を出力し、イネーブル信号 EN が L レベルの場合、コンパレータ 13 の出力電圧  $V_c$  をそのまま電圧  $V_{sel}$  として出力する。この電圧  $V_{sel}$  は、電圧  $V_c$  の代わりに、選択回路 21 及び NAND 回路 14 に入力される。

【0071】

例えば、電源起動直後の所定期間、イネーブル信号 EN は H レベルに設定される。それにより、コンパレータ 13 の出力電圧  $V_c$  が不安定な場合でも、選択回路 21 及び NAND 回路 14 に入力される電圧  $V_{sel}$  のレベルを安定させることができる。そして、所定期間経過後、コンパレータ 13 の出力電圧  $V_c$  が安定すると、イネーブル信号 EN は H レベルから L レベルに切り替わる。それにより、安定したコンパレータ 13 の出力電圧  $V_c$  を、電圧  $V_{sel}$  として、選択回路 21 及び NAND 回路 14 に入力することができる。

40

【0072】

なお、OR 回路 22 は、イネーブル信号 EN に基づいてコンパレータ 13 の出力電圧  $V_c$  及び固定電圧の何れかを電圧  $V_{sel}$  として出力することが可能な他の回路に適宜変更可能である。

【0073】

<実施の形態 3>

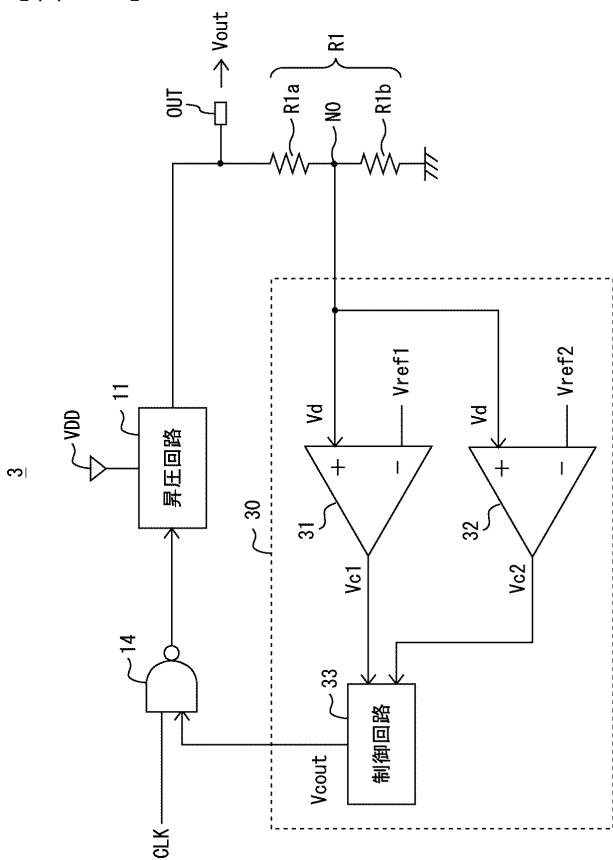

図 10 は、実施の形態 3 にかかる電源回路 3 の構成例を示す図である。電源回路 3 は、電

50

源回路 1 と比較して、比較部 10 の代わりに比較部 30 を備える。比較部 30 は、コンパレータ 31 と、コンパレータ 32 と、制御回路 33 と、を有する。

【 0074 】

コンパレータ 31 は、分圧電圧  $V_d$  と基準電圧  $V_{ref1}$  とを比較して、比較結果である電圧  $V_{c1}$  を出力する。理想的には、コンパレータ 31 は、分圧電圧  $V_d$  が基準電圧  $V_{ref1}$  以上の場合に H レベルの電圧  $V_{c1}$  を出力し、分圧電圧  $V_d$  が基準電圧  $V_{ref1}$  未満の場合に L レベルの電圧  $V_{c1}$  を出力する。

【 0075 】

コンパレータ 32 は、分圧電圧  $V_d$  と基準電圧  $V_{ref2}$  とを比較して、比較結果である電圧  $V_{c2}$  を出力する。理想的には、コンパレータ 32 は、分圧電圧  $V_d$  が基準電圧  $V_{ref2}$  以上の場合に H レベルの電圧  $V_{c2}$  を出力し、分圧電圧  $V_d$  が基準電圧  $V_{ref2}$  未満の場合に L レベルの電圧  $V_{c2}$  を出力する。

10

【 0076 】

制御回路 33 は、コンパレータ 31, 32 のそれぞれから出力された電圧  $V_{c1}$ ,  $V_{c2}$  に応じた電圧  $V_{cout}$  を出力する。

【 0077 】

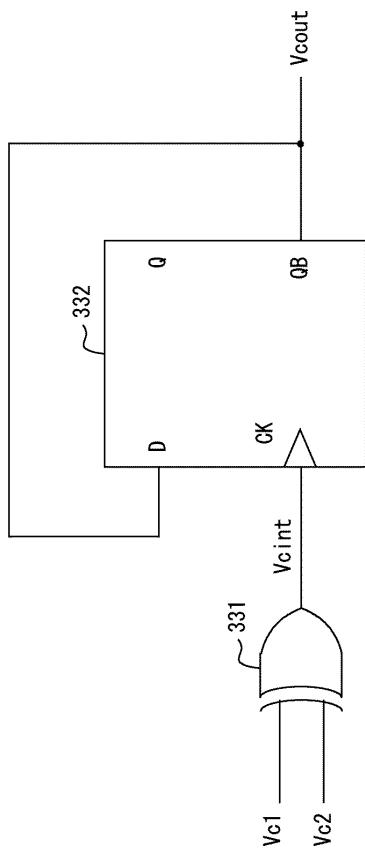

( 制御回路 33 の具体的な構成例 )

図 11 は、制御回路 33 の具体的な構成例を示す図である。

図 11 に示すように、制御回路 33 は、排他的論理和回路 ( X O R 回路 ) 331 と、D フリップフロップ 332 と、を備える。

20

【 0078 】

X O R 回路 331 は、電圧  $V_{c1}$ ,  $V_{c2}$  の排他的論理和を、電圧  $V_{cint}$  として出力する。D フリップフロップ 332 は、電圧  $V_{cint}$  の立ち上がりに同期して電圧  $V_{out}$  を取り込み、論理反転させて電圧  $V_{out}$  として出力する。

【 0079 】

なお、制御回路 33 の構成は、図 11 に示す構成に限られず、図 11 に示す構成と同等の機能を実現可能な他の構成に適宜変更可能である。

【 0080 】

図 10 に戻り、説明を続ける。

N A N D 回路 14 は、制御回路 33 の出力電圧  $V_{cout}$  に基づいて、昇圧回路 11 に対してクロック信号  $C_{LK}$  を出力するか否かを制御する。例えば、制御回路 33 から L レベルの信号が出力されている場合、N A N D 回路 14 は、クロック信号  $C_{LK}$  に関わらず H レベルの信号を出力する。つまり、N A N D 回路 14 は、昇圧回路 11 へのクロック信号  $C_{LK}$  の供給を停止させる。それに対し、コンパレータ 13 から H レベルの信号が出力されている場合、N A N D 回路 14 は、昇圧回路 11 へのクロック信号  $C_{LK}$  ( 厳密に言えば、本例ではクロック信号  $C_{LK}$  の反転信号 ) の供給を行う。このとき、昇圧回路 11 は、出力  $V_{out}$  を昇圧させる。

30

【 0081 】

電源回路 3 のその他の構成については、電源回路 1 の場合と同様であるため、その説明を省略する。

40

【 0082 】

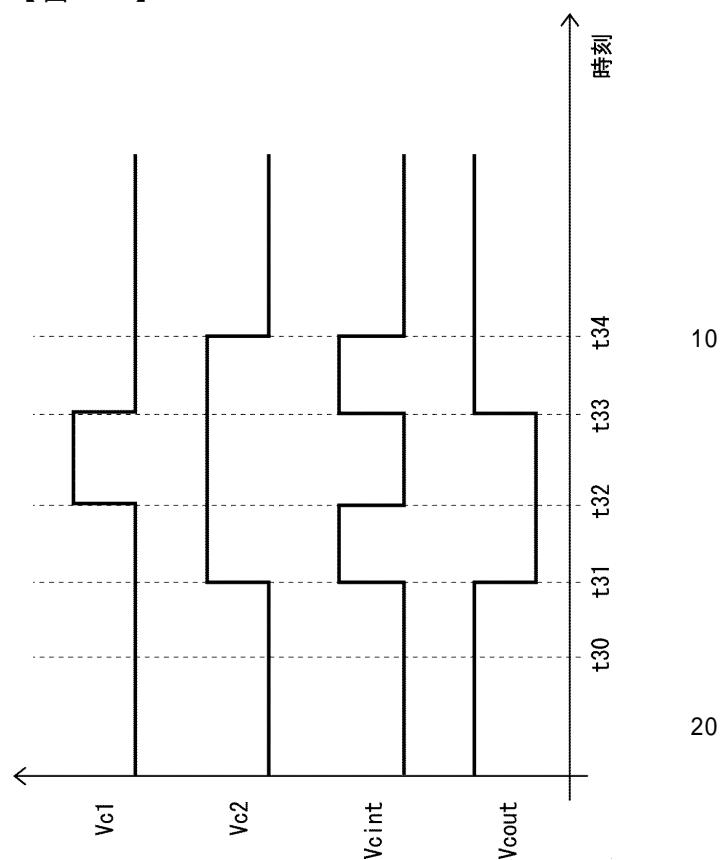

( 電源回路 3 の動作 )

続いて、図 12 を用いて、電源回路 3 の動作について説明する。

図 12 は、電源回路 3 の動作を示すタイミングチャートである。なお、以下では、昇圧回路 11 を駆動する電源電圧  $V_{DD}$  が 2 V、昇圧回路 11 の出力電圧  $V_{out}$  のターゲット電圧が 10 V、抵抗素子  $R_{1a}$ ,  $R_{1b}$  の抵抗比  $R_{1a} : R_{1b}$  が 9 : 1、基準電圧  $V_{ref1}$  が 1.05 V、基準電圧  $V_{ref2}$  が 0.95 V である場合を例に説明する。

【 0083 】

図 12 に示すように、昇圧回路 11 による出力電圧  $V_{out}$  の昇圧開始直後は、出力電圧  $V_{out}$  は、ターゲット電圧 ( = 10 V ) に満たない状態である ( 時刻  $t_{30}$  ) 。そのた

50

め、コンパレータ 3 1, 3 2 は何れも L レベルの電圧  $V_{c1}$ ,  $V_{c2}$  を出力する。このとき、制御回路 3 3 では、XOR 回路 3 3 1 が L レベルの電圧  $V_{cint}$  を出力するため、D フリップフロップ 3 3 2 は、初期値である H レベルの電圧  $V_{cout}$  を出力する。

【 0 0 8 4 】

制御回路 3 3 から H レベルの電圧  $V_{cout}$  が出力されるため、NAND 回路 1 4 は、昇圧回路 1 1 へのクロック信号  $CLK$  の供給を行う。それにより、昇圧回路 1 1 は、出力電圧  $V_{out}$  の昇圧を継続する。

【 0 0 8 5 】

その後、出力電圧  $V_{out}$  が上昇してターゲット電圧を超えると、まず、コンパレータ 3 2 の出力電圧  $V_{c2}$  が L レベルから H レベルに切り替わり（時刻  $t_{31}$ ）、その後、コンパレータ 3 1 の出力電圧  $V_{c1}$  が L レベルから H レベルに切り替わる（時刻  $t_{32}$ ）。それにより、制御回路 3 3 では、XOR 回路 3 3 1 の出力電圧  $V_{cint}$  が L レベルから H レベルに切り替わり（時刻  $t_{31}$ ）、その後、H レベルから L レベルに切り替わる（時刻  $t_{32}$ ）。このとき、D フリップフロップ 3 3 2 は、XOR 回路 3 3 1 の出力電圧  $V_{cint}$  の立ち上がりに同期して出力電圧  $V_{out}$  を H レベルから L レベルに反転させる（時刻  $t_{31}$ ）。

10

【 0 0 8 6 】

制御回路 3 3 から L レベルの電圧  $V_{cout}$  が出力されるため、NAND 回路 1 4 は、昇圧回路 1 1 へのクロック信号  $CLK$  の供給を停止させる。それにより、昇圧回路 1 1 は、出力電圧  $V_{out}$  の昇圧を停止させる。それにより、出力電圧  $V_{out}$  は、下降し始める。

20

【 0 0 8 7 】

その後、出力電圧  $V_{out}$  が下降してターゲット電圧を下回ると、まず、コンパレータ 3 1 の出力電圧  $V_{c1}$  が H レベルから L レベルに切り替わり（時刻  $t_{33}$ ）、その後、コンパレータ 3 2 の出力電圧  $V_{c2}$  が H レベルから L レベルに切り替わる（時刻  $t_{34}$ ）。それにより、制御回路 3 3 では、XOR 回路 3 3 1 の出力電圧  $V_{cint}$  が L レベルから H レベルに切り替わり（時刻  $t_{33}$ ）、その後、H レベルから L レベルに切り替わる（時刻  $t_{34}$ ）。このとき、D フリップフロップ 3 3 2 は、XOR 回路 3 3 1 の出力電圧  $V_{cint}$  の立ち上がりに同期して出力電圧  $V_{out}$  を L レベルから H レベルに反転させる（時刻  $t_{34}$ ）。

【 0 0 8 8 】

30

その後は、時刻  $t_{31} \sim t_{34}$  の動作が繰り返される。

【 0 0 8 9 】

このように、本実施の形態にかかる電源回路 3 は、出力電圧  $V_{out}$  の分圧電圧  $V_d$  と、基準電圧  $V_{ref1}$ ,  $V_{ref2}$  のそれぞれと、の比較結果に基づいて、昇圧回路 1 1 による出力電圧  $V_{out}$  の昇圧の可否を制御している。それにより、本実施の形態にかかる電源回路 3 は、昇圧回路 1 1 のリップル上昇成分及びリップル下降成分を部分的に重複させることができるために、昇圧回路 1 1 の全体的なリップル成分を抑制することができる。換言すると、本実施の形態にかかる電源回路 1 は、負荷への出力電流の大きさに関係なく、安定した出力電圧  $V_{out}$  を生成することができる。

【 0 0 9 0 】

40

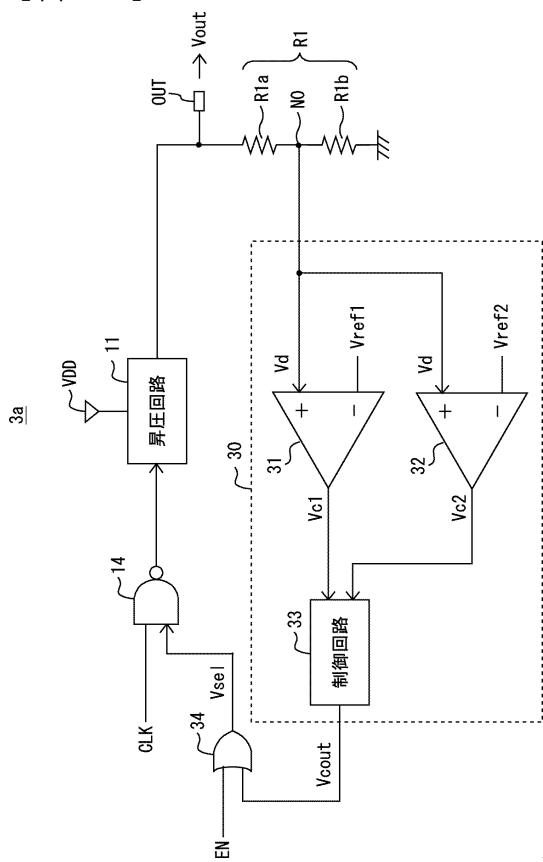

（電源回路 3 の変形例）

図 1 3 は、電源回路 3 の変形例を電源回路 3 a として示す図である。電源回路 3 a は、電源回路 3 と比較して、論理和回路（以下、OR 回路と称す）3 4 をさらに備える。

【 0 0 9 1 】

OR 回路 3 4 は、所謂イネーブル回路であって、外部から供給されたイネーブル信号  $EN$  と、制御回路 3 3 から出力された電圧  $V_{cout}$  と、の論理和を、電圧  $V_{sel}$  として出力する。なお、イネーブル信号  $EN$  は、例えば、昇圧回路 1 1 又はその周辺回路の動作の可否を制御するために用いられているイネーブル信号と共に用いられても良い。

【 0 0 9 2 】

OR 回路 3 4 は、イネーブル信号  $EN$  が H レベルの場合、制御回路 3 3 の出力電圧  $V_{co}$

50

$u_t$  に関わらず H レベルの電圧  $V_{sel}$  を出力し、イネーブル信号  $EN$  が L レベルの場合、制御回路 3 3 の出力電圧  $V_{cout}$  をそのまま電圧  $V_{sel}$  として出力する。この電圧  $V_{sel}$  は、電圧  $V_{cout}$  の代わりに、NAND 回路 1 4 に入力される。

#### 【 0 0 9 3 】

例えば、電源起動直後の所定期間、イネーブル信号  $EN$  は H レベルに設定される。それにより、制御回路 3 3 の出力電圧  $V_{cout}$  が不安定な場合でも、NAND 回路 1 4 に入力される電圧  $V_{sel}$  のレベルを安定させることができる。そして、所定期間経過後、制御回路 3 3 の出力電圧  $V_{cout}$  が安定すると、イネーブル信号  $EN$  は H レベルから L レベルに切り替わる。それにより、安定した制御回路 3 3 の出力電圧  $V_{cout}$  を、電圧  $V_{sel}$  として、NAND 回路 1 4 に入力することができる。

10

#### 【 0 0 9 4 】

なお、OR 回路 3 4 は、イネーブル信号  $EN$  に基づいて制御回路 3 3 の出力電圧  $V_{cout}$  及び固定電圧の何れかを電圧  $V_{sel}$  として出力することが可能な他の回路に適宜変更可能である。

#### 【 0 0 9 5 】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は既に述べた実施の形態に限定されるものではなく、その要旨を逸脱しない範囲において種々の変更が可能であることはいうまでもない。

#### 【 0 0 9 6 】

上記実施の形態 1 ~ 3 では、基準電圧  $V_{ref1}$ ,  $V_{ref2}$  の値が固定されているか、または、分圧電圧  $V_{d1}$ ,  $V_{d2}$  の値が固定されている場合について説明したが、これに限られない。上記実施の形態 1 ~ 3 に係る電源回路 1 ~ 3 は、例えば、出力電圧  $V_{out}$  のリップル成分（変動幅）を測定する測定回路と、測定回路による測定結果に基づいて基準電圧  $V_{ref1}$ ,  $V_{ref2}$  又は分圧電圧  $V_{d1}$ ,  $V_{d2}$  の値を調整する調整回路と、を備えていても良い。それにより、出力電圧  $V_{out}$  のリップル成分をさらに抑制することが可能となる。

20

#### 【 0 0 9 7 】

例えば、上記の実施の形態に係る電源回路では、半導体基板、半導体層、拡散層（拡散領域）などの導電型（p 型もしくは n 型）を反転させた構成としてもよい。そのため、n 型、及び p 型の一方の導電型を第 1 の導電型とし、他方の導電型を第 2 の導電型とした場合、第 1 の導電型を p 型、第 2 の導電型を n 型とすることもできるし、反対に第 1 の導電型を n 型、第 2 の導電型を p 型とすることもできる。

30

#### 【 符号の説明 】

#### 【 0 0 9 8 】

1 ~ 3 電源回路

1 a 電源回路

2 a 電源回路

3 a 電源回路

1 0 比較部

1 1 昇圧回路

1 2 選択回路

1 3 コンパレータ

1 4 否定論理積回路（NAND 回路）

1 5 論理和回路（OR 回路）

2 1 選択回路

2 2 論理和回路（OR 回路）

3 0 比較部

3 1 コンパレータ

3 2 コンパレータ

3 3 制御回路

40

50

## 3 4 論理回路 (OR回路)

## 3 3 1 排他的論理回路 (XOR回路)

## 3 3 2 D フリップフロップ

## INV1 インバータ

MN1, MN2 NチャネルMOSトランジスタ

MP1, MP2 PチャネルMOSトランジスタ

N0, N1, N2 ノード

R1 抵抗素子

R1a, R1b, R1c, R1d, R1e 抵抗素子

TG1 トランスマジックゲート

TG2 トランスマジックゲート

## 【図面】

## 【図1】

## 【図2】

10

20

30

40

50

【図 3】

10

【図 5】

|             |    | Vout [V] |      |      |         |

|-------------|----|----------|------|------|---------|

|             |    | Ave      | min  | max  | max-min |

| 基準電圧<br>1種類 | 16 | 7.43     | 6.93 | 7.84 | 0.91    |

|             | 16 | 7.57     | 7.26 | 7.80 | 0.54    |

|             | 14 | 7.57     | 7.23 | 7.79 | 0.57    |

|             | 12 | 7.55     | 7.18 | 7.81 | 0.63    |

|             | 10 | 7.54     | 7.12 | 7.83 | 0.71    |

|             | 8  | 7.52     | 7.01 | 7.83 | 0.82    |

| 基準電圧<br>2種類 | 6  | 7.50     | 6.88 | 7.95 | 1.07    |

20

【図 4】

30

【図 6】

40

50

【図 7】

【図 8】

10

20

30

40

【図 9】

【図 10】

50

【図 1 1】

33

【図 1 2】

【図 1 3】

3a

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2013-258895 (JP, A)

米国特許出願公開第2006/0261881 (US, A1)

特開2012-100376 (JP, A)

特開2010-124590 (JP, A)

特開2010-057230 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- H02M 3/07