(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5038657号

(P5038657)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月13日(2012.7.13)

(51) Int.Cl.

G 11 C 11/413 (2006.01)

F 1

G 11 C 11/34

K

請求項の数 14 (全 25 頁)

(21) 出願番号 特願2006-174725 (P2006-174725)

(22) 出願日 平成18年6月26日 (2006.6.26)

(65) 公開番号 特開2008-4218 (P2008-4218A)

(43) 公開日 平成20年1月10日 (2008.1.10)

審査請求日 平成21年1月9日 (2009.1.9)

前置審査

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 小松 成亘

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

(72) 発明者 山岡 雅直

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

審査官 堀 拓也

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリ内部に記憶される第1データが入力される第1ポートを有し、前記第1データの書き込み動作の終了を示す第1状態信号を出力するシングルポートメモリと、

外部から第2データが入力される第2ポート及び外部から第3データが入力される第3ポートを有し、前記第2ポートに入力された前記第2データを前記第1ポートに前記第1データとして出力し、前記第3ポートに入力された前記第3データを前記第1ポートに前記第1データとして出力する複数ポート制御回路部とを具備し、

前記第1状態信号は、前記複数ポート制御回路部に入力され、

前記複数ポート制御回路部は、前記第1状態信号に基づいて、前記第1ポートへの前記第2データの出力及び前記第1ポートへの前記第3データの出力を切り替え、

前記複数ポート制御回路部は、前記第2ポート及び前記第3ポートを含めた複数のポートを有し、前記第1ポートに前記第1データとして、前記複数のポートから前記第2データ及び前記第3データを含む複数のデータ信号の出力をを行い、

前記複数ポート制御回路部は、前記第1ポートに対して異なる期間に前記第2データ及び前記第3データを出力するための時分割制御信号生成回路と、前記第1ポートに入力する前記第1データとして、前記第2データまたは前記第3データを選択するセレクタとを有し、

前記時分割制御信号生成回路は、前記セレクタが前記第1データとして、前記複数のデータの何れも選択していないとき、前記第1状態信号に基づき、前記第2データ及び前記

10

20

第3データを前記複数ポート制御回路部に保持する第3期間制御信号を生成することを特徴とする半導体集積回路装置。

【請求項2】

請求項1に記載の半導体集積回路装置であって、

前記複数ポート制御回路部は、第1期間に前記第2データを前記第1ポートに出力し、

第2期間に前記第3データを前記第1ポートに出力し、

前記時分割制御信号生成回路は、前記第1ポートに対して異なる期間に前記第2データ

及び前記第3データを出力するように前記第1期間を示す第1期間制御信号及び前記第2

期間を示す第2期間制御信号を生成し、

前記セレクタは、前記第1期間制御信号及び前記第2期間制御信号に基づき、前記第1

ポートに入力する前記第1データとして、前記第2データまたは前記第3データを選択し

、

前記時分割制御信号生成回路は、前記第1期間制御信号を前記セレクタに入力している

場合において、前記第1状態信号が入力された際に、前記第1期間制御信号の出力を停止

し、前記第2期間制御信号の出力を開始することを特徴とする半導体集積回路装置。

【請求項3】

請求項2に記載の半導体集積回路装置であって、

前記複数ポート制御回路部は、前記第2ポートに接続され、前記第2データが入力される

第1データラッチ回路と、前記第3ポートに接続され、前記第3データが入力される第

2データラッチ回路とを有し、

前記複数ポート制御回路部は、さらに、第3データラッチ回路を含めた複数のデータラ

ッチ回路を有し、

前記時分割制御信号生成回路は、前記セレクタが前記第1データとして、前記複数のデ

ータの何れも選択していないとき、前記第1状態信号に基づき、前記複数のデータ信号が

並列に前記複数のデータラッチ回路に入力される第3期間を示す前記第3期間制御信号を

生成することを特徴とする半導体集積回路装置。

【請求項4】

メモリ内部に記憶される第1データが入力される第1ポートを有し、前記第1データの

書き込み動作の終了を示す第1状態信号を出力するシングルポートメモリと、

外部から第2データが入力される第2ポート及び外部から第3データが入力される第3

ポートを有し、前記第2ポートに入力された前記第2データを前記第1ポートに前記第1

データとして出力し、前記第3ポートに入力された前記第3データを前記第1ポートに前

記第1データとして出力する複数ポート制御回路部とを具備し、

前記第1状態信号は、前記複数ポート制御回路部に入力され、

前記複数ポート制御回路部は、前記第1状態信号に基づいて、前記第1ポートへの前記

第2データの出力及び前記第1ポートへの前記第3データの出力を切り替え、

前記複数ポート制御回路部は、第1期間に前記第2データを前記第1ポートに出力し、

第2期間に前記第3データを前記第1ポートに出力し、

前記複数ポート制御回路部は、さらに、前記第1ポートに対して異なる期間に前記第2

データ及び前記第3データを出力するように前記第1期間を示す第1期間制御信号及び前

記第2期間を示す第2期間制御信号を生成する時分割制御信号生成回路と、前記第1期間

制御信号及び前記第2期間制御信号に基づき、前記第1ポートに入力する前記第1データ

として、前記第2データまたは前記第3データを選択するセレクタとを有し、

前記時分割制御信号生成回路は、前記第1期間制御信号を前記セレクタに入力している

場合において、前記第1状態信号が入力された際に、前記第1期間制御信号の出力を停止

し、前記第2期間制御信号の出力を開始し、

前記複数ポート制御回路部は、前記第2ポートに接続され、前記第2データが入力され

る第1データラッチ回路と、前記第3ポートに接続され、前記第3データが入力される第

2データラッチ回路とを有し、

前記時分割制御信号生成回路は、前記セレクタが前記第1データとして、前記第2データ

として、前記第3データを選択する。

10

20

30

40

50

タ及び前記第3データを選択していないとき、前記第2データが前記第1データラッチ回路に入力され前記第3データが前記第2データラッチ回路に入力される第3期間を示す第3期間制御信号を生成することを特徴とする半導体集積回路装置。

#### 【請求項5】

請求項3に記載の半導体集積回路装置であって、

前記時分割制御信号生成回路は、第1シフトレジスタと、前記第1状態信号に基づき前記第1シフトレジスタからの入力値を出力値として出力する第2シフトレジスタとを有し、

前記第1シフトレジスタの出力値に基づき前記第1期間制御信号を生成し、前記第1状態信号が前記時分割制御信号生成回路に入力された際に、前記第1シフトレジスタに保持された値は前記第2シフトレジスタに転送され、前記第2シフトレジスタの出力値に基づき前記第2期間制御信号を生成することを特徴とする半導体集積回路装置。10

#### 【請求項6】

メモリ内部に記憶される第1データが入力される第1ポートを有し、前記第1データの書き込み動作の終了を示す第1状態信号を出力するシングルポートメモリと、

外部から第2データが入力される第2ポート及び外部から第3データが入力される第3ポートを有し、前記第2ポートに入力された前記第2データを前記第1ポートに前記第1データとして出力し、前記第3ポートに入力された前記第3データを前記第1ポートに前記第1データとして出力する複数ポート制御回路部とを具備し、

前記第1状態信号は、前記複数ポート制御回路部に入力され、20

前記複数ポート制御回路部は、前記第1状態信号に基づいて、前記第1ポートへの前記第2データの出力及び前記第1ポートへの前記第3データの出力を切り替え、

前記複数ポート制御回路部は、第1期間に前記第2データを前記第1ポートに出力し、第2期間に前記第3データを前記第1ポートに出力し、

前記複数ポート制御回路部は、さらに、前記第1ポートに対して異なる期間に前記第2データ及び前記第3データを出力するように前記第1期間を示す第1期間制御信号及び前記第2期間を示す第2期間制御信号を生成する時分割制御信号生成回路と、前記第1期間制御信号及び前記第2期間制御信号に基づき、前記第1ポートに入力する前記第1データとして、前記第2データまたは前記第3データを選択するセレクタとを有し、

前記時分割制御信号生成回路は、前記第1期間制御信号を前記セレクタに入力している場合において、前記第1状態信号が入力された際に、前記第1期間制御信号の出力を停止し、前記第2期間制御信号の出力を開始し。30

前記複数ポート制御回路部は、前記第2ポートに接続され、前記第2データが入力される第1データラッチ回路と、前記第3ポートに接続され、前記第3データが入力される第2データラッチ回路とを有し、

前記時分割制御信号生成回路は、第1シフトレジスタと、前記第1状態信号に基づき前記第1シフトレジスタからの入力値を出力値として出力する第2シフトレジスタとを有し、

前記第1シフトレジスタの出力値に基づき前記第1期間制御信号を生成し、前記第1状態信号が前記時分割制御信号生成回路に入力された際に、前記第1シフトレジスタに保持された値は前記第2シフトレジスタに転送され、前記第2シフトレジスタの出力値に基づき前記第2期間制御信号を生成し。40

前記時分割制御信号生成回路は、前記セレクタが、前記第1シフトレジスタ及び前記第2シフトレジスタの出力値に基づいて、前記第1ポートに入力する第1データとして前記第2データ及び前記第3データを選択していないとき、前記第2データが前記第1データラッチ回路に入力され前記第3データが前記第2データラッチ回路に並列に入力される第3期間を示す第3期間制御信号を生成することを特徴とする半導体集積回路装置。

#### 【請求項7】

請求項2に記載の半導体集積回路装置であって、

前記時分割制御信号生成回路は、第1シフトレジスタと、前記第1状態信号に基づき前50

記第1シフトレジスタに保持された値が転送される第2シフトレジスタとを有し、

前記第1シフトレジスタ及び前記第2シフトレジスタはリングカウンタを形成し、

前記第1シフトレジスタの出力値に基づき前記第1期間制御信号を生成し、前記第1状態信号が前記時分割制御信号生成回路に入力された際に、前記第1シフトレジスタに保持された値は前記第2シフトレジスタに転送され、前記第2シフトレジスタの出力値に基づき前記第2期間制御信号を生成することを特徴とする半導体集積回路装置。

#### 【請求項8】

請求項1に記載の半導体集積回路装置であって、

前記複数ポート制御回路部は、前記第1ポートに前記第1データとして前記第2データが出力される場合には、前記シングルポートメモリに入力する入力アドレス信号の特定のビット値を第1の値に固定し、前記第1ポートに前記第1データとして前記第3データが出力される場合には、前記入力アドレス信号の前記特定のビット値を第2の値に固定し、前記第1の値と前記第2の値は互いに異なることを特徴とする半導体集積回路装置。 10

#### 【請求項9】

請求項1に記載の半導体集積回路装置であって、

前記複数ポート制御回路部は、外部クロックが入力されるクロック入力部を有し、前記クロック入力部から入力される前記外部クロックに基づいて、前記第1ポートに入力する前記第1データの出力を開始することを特徴とする半導体集積回路装置。

#### 【請求項10】

請求項9に記載の半導体集積回路装置であって、

前記複数ポート制御回路部の外部からデータが入力されるポートは前記第2ポート及び前記第3ポートを含めた複数のポートで構成され、

前記第1ポートに前記第1データとして前記複数のポートからデータを出力する時間は前記外部クロックの周期より短いことを特徴とする半導体集積回路装置。 20

#### 【請求項11】

請求項3に記載の半導体集積回路装置であって、

前記時分割制御信号生成回路は、前記第1状態信号を遅延する遅延回路を有し、

前記遅延回路は、前記第1状態信号が入力され、前記第1乃至第3期間のうち、いずれか1つ以上の期間を遅延させることを特徴とする半導体集積回路装置。 30

#### 【請求項12】

請求項3に記載の半導体集積回路装置であって、

前記第1データラッチ回路は、前記複数ポート制御回路部の外部から入力されるデータを保持する回路と、前記シングルポートメモリから読み出され、前記第1ポートを経由し外部へ出力されるデータを保持する回路を有することを特徴とする半導体集積回路装置。 40

#### 【請求項13】

請求項1に記載の半導体集積回路装置であって、

前記シングルポートメモリはSRAMであることを特徴とする半導体集積回路装置。

#### 【請求項14】

請求項1に記載の半導体集積回路装置であって、

前記シングルポートメモリは、前記メモリ内における読み出しおよび書き込み時にワードドライバによって駆動されるワード線と、前記ワード線により活性化したメモリセルから信号が伝達されるビット線と、前記ビット線から伝達された信号を増幅するセンスアンプとを有し、

前記第1状態信号は、前記ワード線の立ち下げ信号、又は前記センスアンプの駆動信号に基づいて生成されることを特徴とする半導体集積回路装置。 40

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体集積回路装置に関し、特に、時分割多ポートメモリ等を搭載した半導体集積回路装置の構成に適用して有効な技術に関する。 50

**【背景技術】****【0002】**

本発明者が検討した技術として、例えば、時分割多ポートメモリ等を搭載した半導体集積回路装置においては、以下の技術が考えられる。

**【0003】**

特許文献1の技術は、小面積のメモリセルを用いる時分割の多ポートメモリでメモリ内部を外部と同じ周波数のクロックで制御し、外部クロック時間がアクセス時間より短くできるようにしたというものである。この時分割多ポートメモリは、ラッチ回路と内部メモリ、マルチプレクサ回路、データ信号分配器、PLL回路の構成により実現されている。PLL回路により生成された、外部クロックより周波数の高いクロック信号で、マルチプレクサ回路とデータ信号分配器、内部メモリ、ラッチ回路を制御し、時分割で複数ポート分のデータの処理を行っている。10

**【0004】**

特許文献2の技術は、信号の入出力を可能とするポートを備えたメモリコアと、このメモリコアに結合され、時分割により上記メモリコアのポートを拡張可能なポート拡張回路とを含むとき、時分割により実現されるポートを切り替え可能なポート切り替え回路を上記ポート拡張回路に設けることにより、ポート数やポート機能にかかわらず、半導体記憶装置のレイアウトを共通化しておいて、ユーザ仕様に応じて、時分割により実現されるポートの設定が可能とされ、それによって時分割方式におけるマルチポートRAMのコスト低減を達成するというものである。内部メモリの動作タイミングを制御する内部クロックは、パルス幅設定可能なディレイ素子により生成されている。20

【特許文献1】特開平8-212784号公報

【特許文献2】特開2005-85344号公報

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

ところで、前記のような半導体集積回路装置の技術について、本発明者が検討した結果、以下のようなことが明らかとなった。

**【0006】**

現在、大規模な半導体集積回路装置には多数のメモリが搭載され、チップ面積全体に占めるメモリの割合は大きい。そのため、メモリの面積削減は半導体集積回路装置全体の面積削減に効果的である。30

**【0007】**

メモリ自身は、データを保持するメモリセルアレイ部分と、アドレスデコーダやワードドライバ、アンプなどの周辺回路の部分から構成される。メモリに占める周辺回路の割合は大きく、周辺回路部分の面積を削減することができれば、半導体集積回路装置において、メモリ全体が占める面積を削減することが可能である。

**【0008】**

例えば、複数のメモリを統合して時分割多ポートメモリとすることで周辺回路部分の面積を削減することができる。これは、統合によりメモリセルアレイ部分の面積は統合前と変わらないが、周辺回路を共有化できるからである。40

**【0009】**

時分割多ポートメモリは、シングルポートSRAMを外部クロックより速く動作させ、外部クロック1サイクルの間に複数ポート分の読み出し、もしくは書き込み要求を時分割で順次処理し、全ての要求動作を終えるので、外部から見た場合、複数の独立したメモリに同時アクセスしているのと同じ効果が得られる。

**【0010】**

従来の時分割多ポートメモリでは、時分割制御のために、PLL回路やインバーターチェーンによるディレイ回路などのクロック生成回路を使用している。しかし、これらのクロック生成回路は面積と消費電力のオーバーヘッドが大きい。50

**【0011】**

そこで、本発明の目的は、時分割多ポートメモリ等を搭載した半導体集積回路装置において、小面積化を図ることができる技術を提供することにある。

**【0012】**

本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

**【課題を解決するための手段】****【0013】**

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

10

**【0014】**

すなわち、本発明による半導体集積回路装置は、複数のメモリセルからなるメモリセルアレイと、そのメモリセルアレイを制御する周辺回路などから構成されるメモリ装置において、メモリ内部で発生する信号を、メモリ装置への入力信号と入出力データの制御に利用し、時分割制御を行うものである。これにより、クロック生成回路を必要とせず、小面積な時分割多ポートメモリを実現することが可能となる。

**【発明の効果】****【0015】**

本発明によれば、シングルポートメモリに時分割でアクセスすることで、小面積な多ポートメモリを構成することが可能になる。

20

**【発明を実施するための最良の形態】****【0016】**

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

**【0017】****(実施の形態1)**

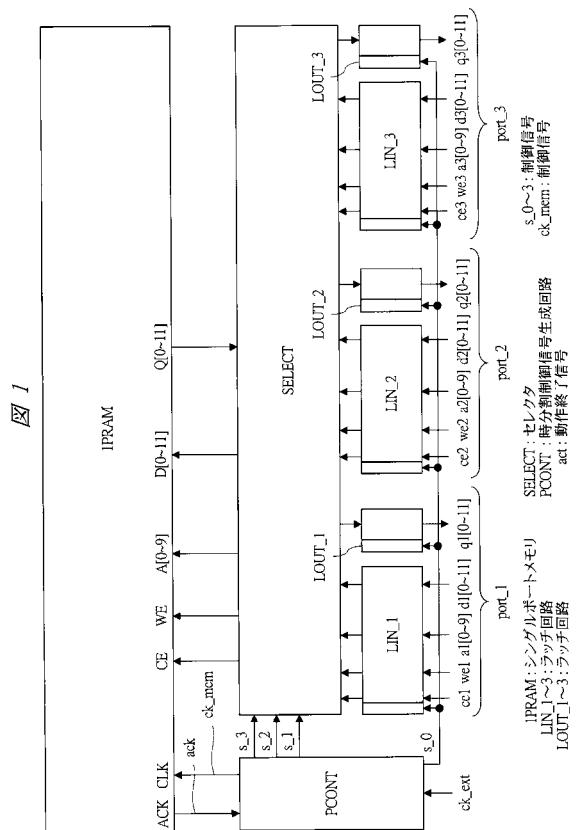

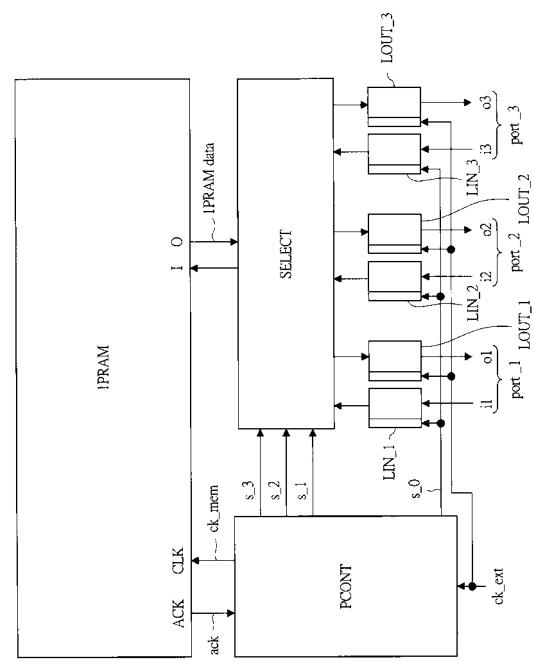

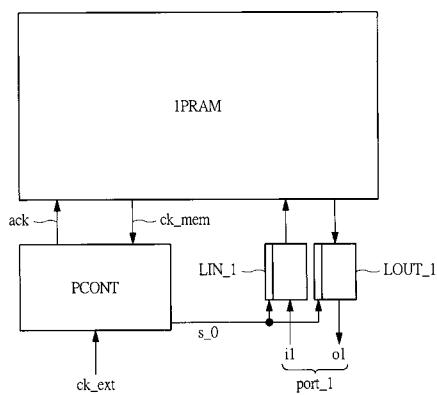

図1は、本発明の実施の形態1による半導体集積回路装置に搭載される時分割多ポートメモリの構成を示すプロック図である。本実施の形態1による半導体集積回路装置は、周知の半導体製造技術により1つの半導体基板上に形成される。

30

**【0018】**

まず、図1により、本発明の実施の形態1による半導体集積回路装置に搭載される時分割多ポートメモリの構成の一例を説明する。この時分割多ポートメモリは、例えば、内部メモリと時分割制御回路などから構成される。内部メモリは、例えば、複数のメモリセルを含むメモリセルアレイと、そのメモリセルアレイを制御する周辺回路などを備えたシングルポートSRAM(1PRAM)である。時分割制御回路は、内部メモリへの入力信号を制御し、内部メモリと複数のポートとの間で入出力データを時分割で制御するものであり、例えば、入力データ用ラッチ回路LIN\_1~3、出力データ用ラッチ回路LOUT\_1~3、セレクタSELECT、時分割制御信号生成回路PCONTなどから構成される。

40

**【0019】**

シングルポートSRAM(1PRAM)を外部クロック信号clk\_extより速く動作させ、外部クロック1サイクルの間に複数ポート分の読み出し、もしくは書き込み要求を時分割で順次処理することで擬似的に多ポートメモリ動作を実現する。

**【0020】**

本実施の形態1では、3個のポート(port\_1~3)がある場合を示しているが、2個または4個以上のポートであってもよい。2つ以上の複数のポートを持つ場合に、同様の回路構成で同等の効果が得られる。

**【0021】**

シングルポートSRAM(1PRAM)は、1ポートのSRAMである。

50

**【 0 0 2 2 】**

入力データ用ラッチ回路 L I N \_ 1 ~ 3 は、それぞれ各ポート p o r t \_ 1 ~ 3 のアドレス信号、制御信号、データ信号などの入力信号を保持するラッチ回路であり、複数のラッチ回路をまとめて表している。

**【 0 0 2 3 】**

出力データ用ラッチ回路 L O U T \_ 1 ~ 3 は、それぞれ各ポート p o r t \_ 1 ~ 3 の出力信号を保持するラッチ回路であり複数のラッチ回路をまとめて表している。

**【 0 0 2 4 】**

セレクタ S E L E C T は、シングルポート S R A M ( 1 P R A M ) とポート p o r t \_ 1 ~ 3 の接続を切り替えるセレクタである。 10

**【 0 0 2 5 】**

時分割制御信号生成回路 P C O N T は、制御信号 s \_ 0 ~ 3 , c k \_ m e m を生成する回路である。

**【 0 0 2 6 】**

外部クロック信号 c k \_ e x t は、本実施の形態 1 による多ポートメモリに外部から入力されるクロック信号である。制御信号 s \_ 0 は、入力データ用ラッチ回路 L I N \_ 1 ~ 3 もしくは出力データ用ラッチ回路 L O U T \_ 1 ~ 3 が、信号を保持もしくは出力するタイミングを制御する制御信号である。制御信号 s \_ 1 ~ 3 は、1 P R A M とポート p o r t \_ 1 ~ 3 の接続を指定する信号であり、制御信号 s \_ 1 ~ 3 のうち、ハイレベルになっている信号に対応するポートがセレクタ S E L E C T で選択され、1 P R A M と接続される。制御信号 c k \_ m e m は、1 P R A M を動作させる動作開始信号である。信号 a c k は、1 P R A M のデータ読み出しもしくは書き込みの動作終了を示す信号である。 20

**【 0 0 2 7 】**

1 P R A Mにおいて、A C K は1 P R A M の動作終了信号出力端子、C L K は1 P R A M のクロック信号入力端子、C E はチップイネイブル信号入力端子、W E は書き込み動作指定ライトイネイブル信号入力端子、A [ 0 ~ 9 ] はアドレス信号入力端子（アドレスが10ビットの場合を示しているがビット数は任意の数でよい）、D [ 0 ~ 1 1 ] はデータ入力信号端子（12ビットの場合を示しているがビット数は任意の数でよい）、Q [ 0 ~ 1 1 ] はデータ出力端子（12ビットの場合を示しているがビット数は任意の数でよい）である。 30

**【 0 0 2 8 】**

各ポート p o r t \_ 1 ~ 3 には、それぞれ入出力信号チップイネイブル信号 c e \_ 1 ~ 3 、ライトイネイブル信号 w e \_ 1 ~ 3 、アドレス指定信号 A \_ 1 ~ 3 [ 0 ~ 9 ] 、入力データ信号 D \_ 1 ~ 3 [ 0 ~ 1 1 ] 、出力データ信号 Q \_ 1 ~ 3 [ 0 ~ 1 1 ] が入力または出力される。なお、アドレス指定信号、入力データ信号、出力データ信号のビット数は任意の数でよい。

**【 0 0 2 9 】**

外部クロック信号 c k \_ e x t が立ち上がる前に制御信号 s \_ 0 がアサートされ、各ポートにアドレス信号、制御信号、書き込みデータなどの信号が入力される。外部クロック信号 c k \_ e x t の立ち上がりにより制御信号 s \_ 1 がアサートされ、第1のポート p o r t \_ 1 のデータが選択され、1 P R A M による第1のポート p o r t \_ 1 のデータの処理が開始される。第1のポート p o r t \_ 1 のデータの処理が終わると、1 P R A M から動作終了信号 a c k が出力され、この動作終了信号 a c k の入力により制御信号 s \_ 2 がアサートされ、第2のポート p o r t \_ 2 のデータが選択され、1 P R A M による第2のポート p o r t \_ 2 のデータの処理が開始される。次に、第2のポート p o r t \_ 2 のデータの処理が終わると、1 P R A M から動作終了信号 a c k が出力され、この動作終了信号 a c k の入力により制御信号 s \_ 3 がアサートされ、第3のポート p o r t \_ 3 のデータが選択され、1 P R A M による第3のポート p o r t \_ 3 のデータの処理が開始される。 40

**【 0 0 3 0 】**

10

20

30

40

50

このようにして、1 P R A Mからの動作終了信号を利用して処理を繰り返していくことで、クロック生成回路を使用することなく順次各ポートのデータを処理することができる。

#### 【 0 0 3 1 】

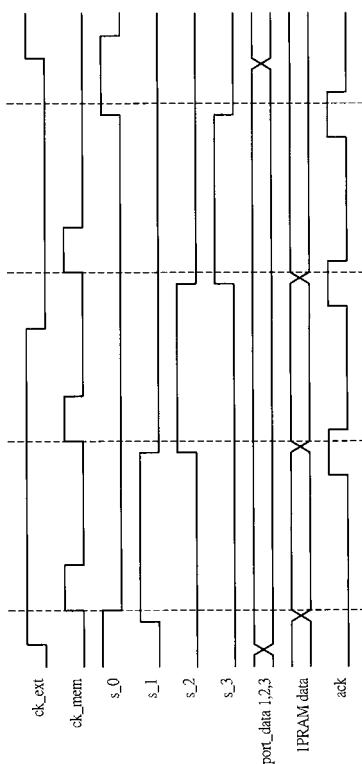

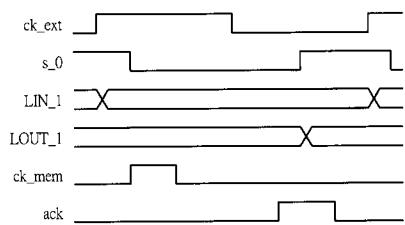

図2は、図1で示した時分割多ポートメモリの動作を示すタイミングチャートである。図2に示すように、外部クロック信号c k \_ e x t が入力される前、制御信号s \_ 0 はハイ、s \_ 1 ~ 3 はロウの状態となっている。外部クロック信号c k \_ e x t の立ち上がりにより、s \_ 0 がロウになり各ポートの入力信号がそれぞれL I N \_ 1 ~ 3 に保持される。同時にs \_ 1 がハイになり、p o r t \_ 1 のデータが1 P R A Mの入出力端子と接続される。

10

#### 【 0 0 3 2 】

c k \_ e x t の立ち上がりにより、P C O N T によってパルス状の制御信号c k \_ m e m が生成される。c k \_ m e m が1 P R A Mに入力されることによって、1 P R A Mが動作し、p o r t \_ 1 のデータが処理される。

#### 【 0 0 3 3 】

処理が終了すると、1 P R A Mは動作終了信号a c k を出力する。a c k がP C O N T に入力され、P C O N T はセレクタ制御信号s \_ 1 ~ 3 のうちハイになっている信号線を、s \_ 1 からs \_ 2 に切り替える。これによりp o r t \_ 1 のデータが1 P R A Mと接続される。

20

#### 【 0 0 3 4 】

a c k の入力により、P C O N T がパルス状の信号c k \_ m e m を生成し、c k \_ m e m が1 P R A Mに入力され、1 P R A Mはp o r t \_ 2 のデータを処理する。

#### 【 0 0 3 5 】

同様にp o r t \_ 3 のデータの処理を終え、全てのポートのデータの処理が終了した後、s \_ 0 はハイになる。s \_ 0 がハイになることでL O U T \_ 1 ~ 3 は保持していた出力データを外部に出力する。

#### 【 0 0 3 6 】

この時分割多ポートメモリは次にc k \_ e x t が入力されるまで、停止状態となる。

#### 【 0 0 3 7 】

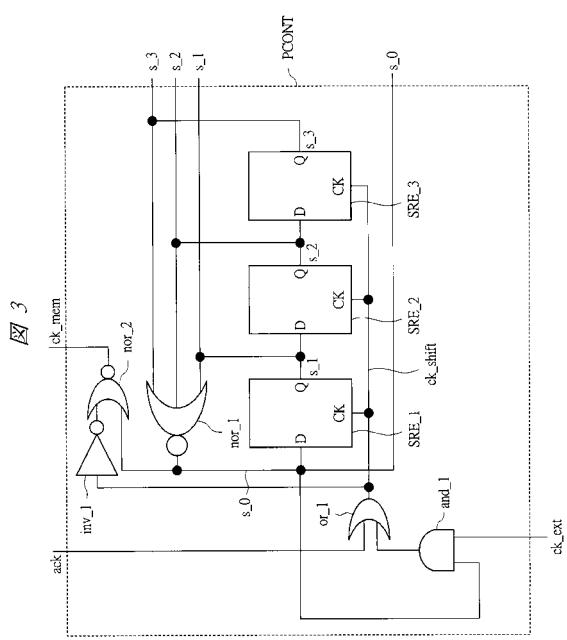

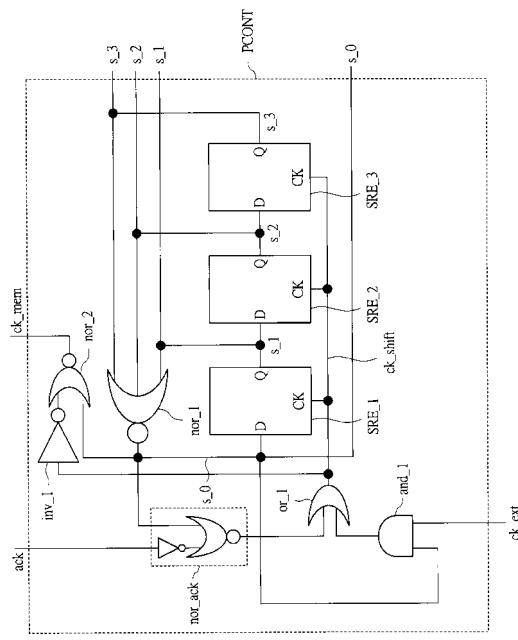

図3は、時分割制御信号生成回路P C O N T の回路構成を示している。S R E \_ 1 , S R E \_ 2 , S R E \_ 3 は、端子C K の入力信号の立ち上がりエッジで入力端子D の値を出力端子Q に出力するシフトレジスタであり、時分割多ポートメモリのポートの数とシフトレジスタの数は等しい。

30

#### 【 0 0 3 8 】

外部クロック信号c k \_ e x t の入力の立ち上がり、もしくは1 P R A Mからの動作終了信号a c k の入力によって信号c k \_ s h i f t とc k \_ m e m が作られる。c k \_ s h i f t はシフトレジスタS R E \_ 1 , S R E \_ 2 , S R E \_ 3 を動作させ、各シフトレジスタの入力値が出力される。c k \_ m e m は1 P R A Mに入力されて1 P R A Mを動作させるクロック信号となる。各シフトレジスタの出力s \_ 1 ~ 3 は、各ポートの入出力信号と1 P R A Mをつなぐセレクタの切り替え信号となっている。

40

#### 【 0 0 3 9 】

A N D回路a n d \_ 1 は、c k \_ e x t から作られる信号を次の内部クロックが入る前に立ち下げる。N O R回路n o r \_ 1 は、全てのポートの動作終了時にs \_ 0 をハイにセットする。N O R回路n o r \_ 2 は、最後のポートのデータ処理動作終了後に出るa c k 信号からc k \_ m e m が生成されるのを抑止する。

#### 【 0 0 4 0 】

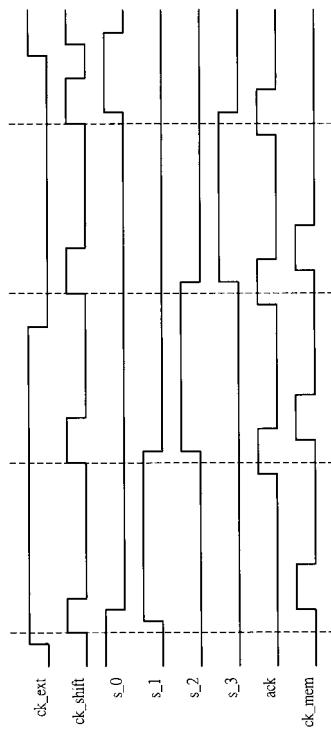

図4は、図3で示した時分割制御信号生成回路P C O N T の動作を示すタイミングチャートである。まず、外部クロック信号c k \_ e x t が入力される。c k \_ e x t と信号s \_ 0 とのA N D が取られ、信号c k \_ s h i f t が立ち上がる。

#### 【 0 0 4 1 】

50

これにより各シフトレジスタが動作し、 $s\_1$ はロウからハイになる。 $s\_1$ がハイになったことで、 $s\_0$ はロウとなり、 $ck\_mem$ が立ち上がる。一方、 $s\_0$ がロウとなつたことで $ck\_shift$ はたち下がり、 $ck\_mem$ もたち下がる。

#### 【0042】

$s\_1$ がハイになり $port\_1$ のデータが選択され、1PRAMに動作開始の制御信号 $ck\_mem$ が入力されることで、 $port\_1$ のデータが処理され、動作終了時に1PRAMから動作終了信号 $ack$ が出力される。

#### 【0043】

$ack$ の入力により $ck\_shift$ が生成され、シフトレジスタを動作させ選択ポートを変更する。また $ack$ の入力により $ck\_mem$ が生成され、1PRAMを動作させる。

10

#### 【0044】

$port\_3$ のデータの動作終了信号 $ack$ によりシフトレジスタが動作すると、全てのシフトレジスタの出力信号 $s\_1 \sim 3$ はロウになり、 $s\_0$ がハイになる。これにより $ck\_mem$ は $ack$ が入ってもロウのままであり、動作は終了する。

#### 【0045】

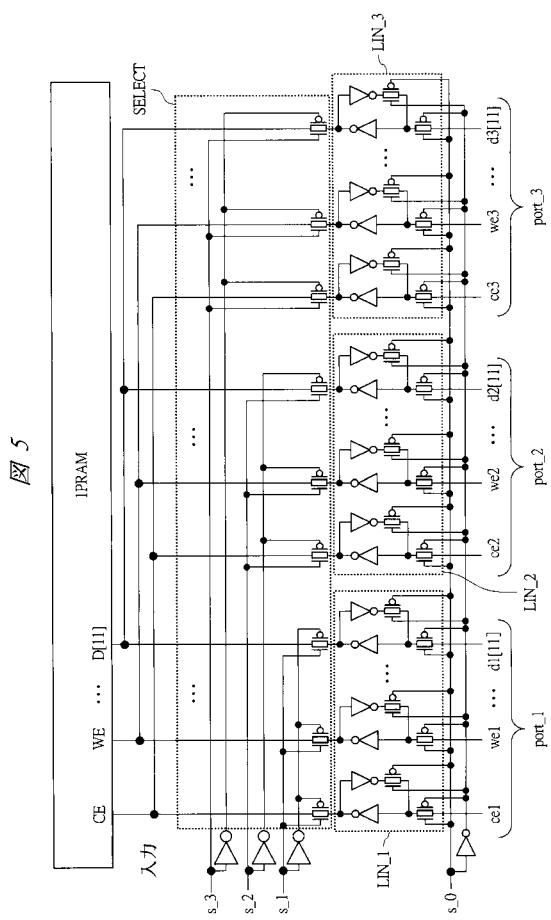

図5は、図1に示した入力データ用ラッチ回路 $LIN\_1 \sim 3$ とセレクタ $SEL\_ECT$ の回路構造を示している。なお、図5において、 $a[0 \sim 9]$ ,  $d[0 \sim 10]$ ,  $A[0 \sim 9]$ ,  $D[0 \sim 10]$ に対応する回路は、 $ce[1 \sim 3]$ ,  $we[1 \sim 3]$ ,  $d[1 \sim 3][11]$ 等に対応する回路と同じであるので、省略して示している。

20

#### 【0046】

$s\_1 \sim 3$ のうち、ハイとなっている信号により1PRAMと接続されるポートが選択される。 $s\_0$ がハイのとき、外部からの信号入力が可能であり、 $s\_0$ がロウのとき、外部とつながるゲートが閉じてデータ保持の状態になる。

#### 【0047】

これらの入力信号には、メモリ動作・非動作制御信号、書き込み・読み出し制御信号、アドレス指定信号、書き込みデータ信号などがある。

#### 【0048】

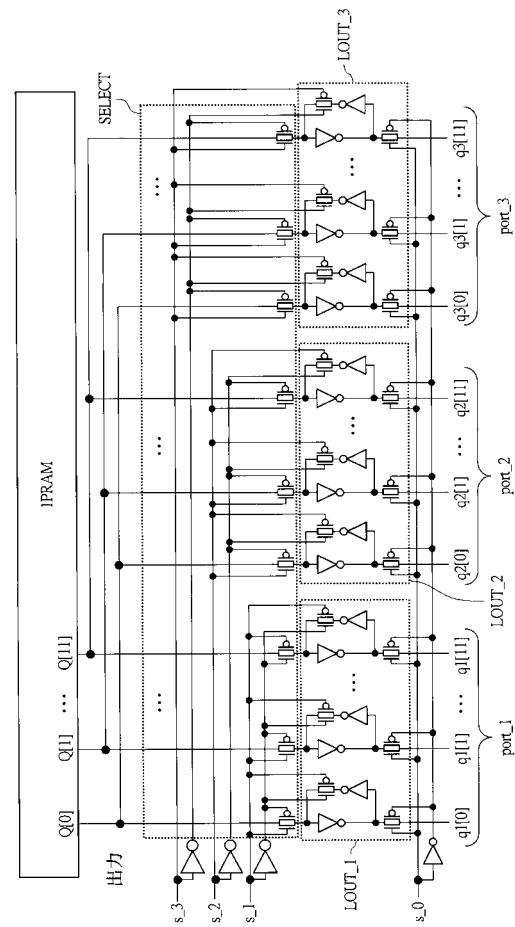

図6は、図1に示した出力データ用ラッチ回路 $LOUT\_1 \sim 3$ とセレクタ $SEL\_ECT$ の回路構造を示している。なお、図6において、 $q[1 \sim 3][2 \sim 10]$ ,  $Q[2 \sim 10]$ に対応する回路は、 $q[1 \sim 3][0, 1, 11]$ ,  $Q[0, 1, 11]$ 等に対応する回路と同じであるので、省略して示している。

30

#### 【0049】

$s\_1 \sim 3$ のうちハイとなっている信号により1PRAMとつながるポートが選択される。選択状態にあるポートのデータが保持されているラッチ部分は1PRAMからのデータ入力を受け付け、非選択状態のとき保持状態になる。 $s\_0$ がハイの時、データは外部へ出力される。出力信号は読み出しデータ信号などである。

#### 【0050】

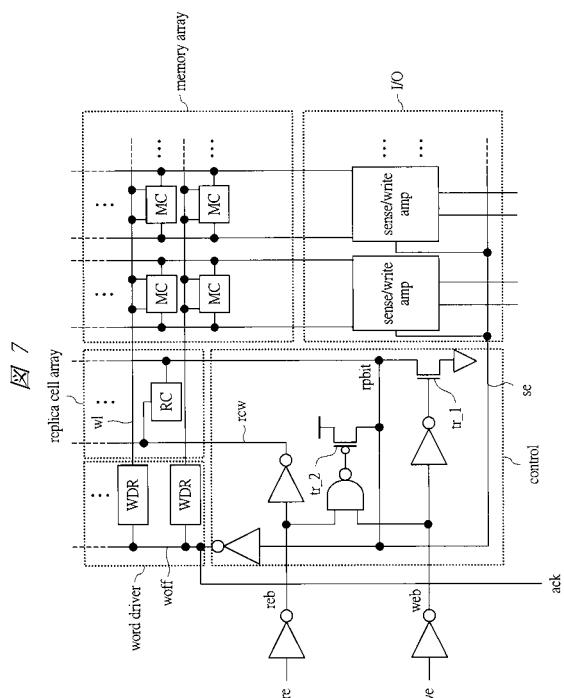

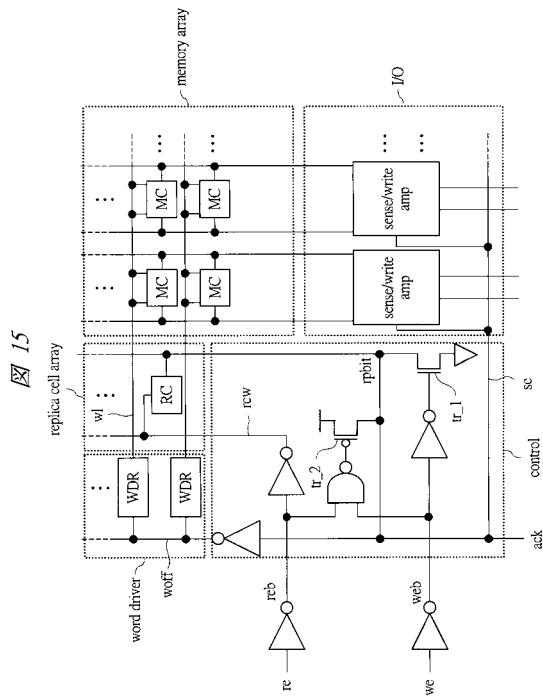

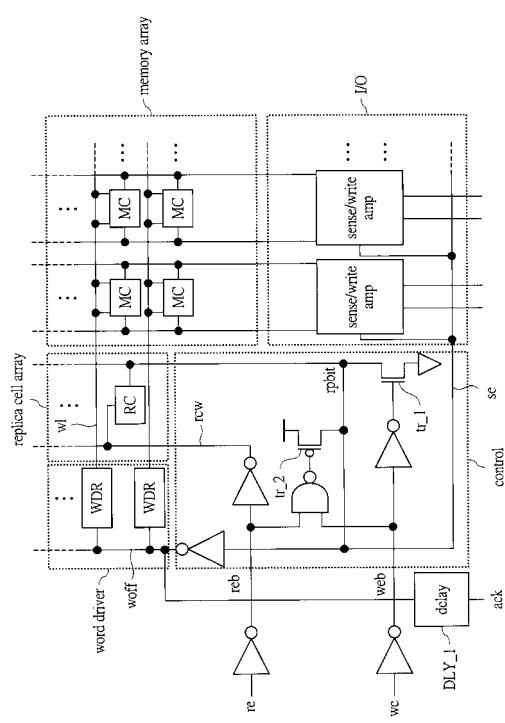

図7は、 $ack$ 信号生成に使用する回路の構造を示す。この回路は、1PRAM内の回路のうち、主要部分だけを示している。

40

#### 【0051】

通常SRAMでは、動作を行うために内部でタイミングを調整する信号が生成されており、ワード線の立ち下げや、センスアンプの動作タイミングに使用されている。本実施例では、タイミング信号を生成する一例として図7の回路を説明するが、異なる回路でタイミングを生成している場合にも同様の信号を用いることで、同様の効果が得られる。

#### 【0052】

$ack$ 信号生成には、1PRAMの内部のワード線立ち下げ信号生成回路を使用する。ワード線立ち下げ信号は、センスアンプ動作信号の生成にも使用されている。ワード線を立ち下げる動作、センスアンプを差動させる動作は、メモリのデータ処理動作終了時に起こる動作であり、動作終了信号に適している。

50

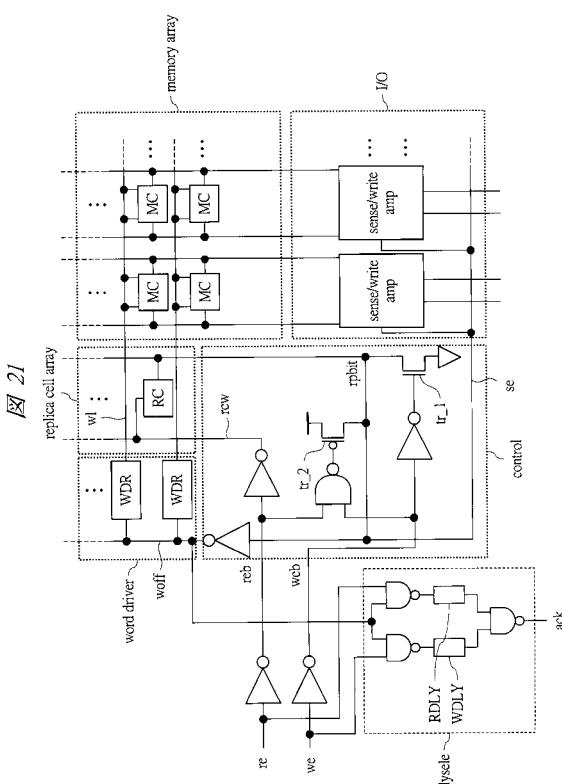

## 【0053】

図7は、1P R A M内の回路のうち、ワード線立ち下げ信号生成に関する回路部分を抜き出した図である。メモリセルアレイ(m e m o r y a r r a y)は、メモリセルが規則的に並びデータを記憶する部分である。I / Oは、ライトアンプ、リードアンプ、バッファなどの回路を含む部分である。レプリカセルアレイ(r e p l i c a c e l l a r r a y)は、ワード線立ち下げ信号やセンスアンプ動作信号をタイミング良く作るために使用されるレプリカセルが並ぶ部分である。ワードドライバ(w o r d d r i v e r)は、ワード線を駆動する部分である。コントロール(c o n t r o l)は、ワード線立ち下げ信号やセンスアンプ動作信号を作る部分である。

## 【0054】

M CはS R A Mメモリセル、R Cはメモリセルと同じ構造を持つレプリカセル、W D Rはワード線ドライバである。r e , w eはリードイネイブル信号、ワードイネイブル信号である。動作原理としては信号w e , r eが共にロウ、w e , r eの反転信号w e b , r e bが共にハイの時、P M O Sトランジスタt r \_ 2はオンであり、信号線r p b i tはハイとなっている。

## 【0055】

w eもしくはr eがハイとなった場合、P M O Sトランジスタt r \_ 2はオフとなる。w eがハイの場合、N M O Sトランジスタt r \_ 1がオンとなりr p b i tの電荷は引き抜かれる。r eがハイの場合、レプリカセルR Cのワード線r c wがハイとなり、r p b i tの電荷はR C内部を通じて引き抜かれる。

## 【0056】

レプリカセルを使用して、実際のメモリセルのb i t線から電荷を抜き出すのと同じ条件を再現することで、r p b i tから電荷を引き抜くのにかかる時間によって実際のメモリセルに対するデータ読み出しや書き出しが終了するタイミングを得られるので、ワード線立ち下げ信号として使用できる。

## 【0057】

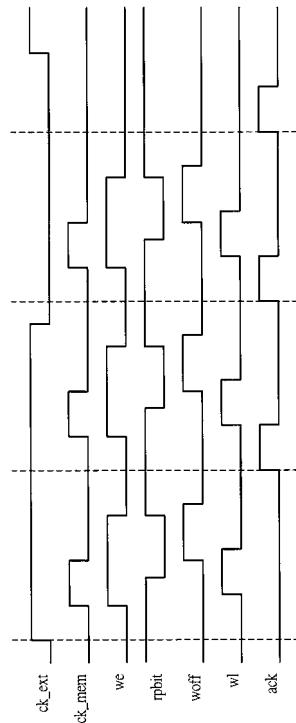

図8は、ワード線立ち下げ信号(a c k信号)生成回路の動作を示すタイミングチャートである。ここでは、ライト(書き込み)動作時の状態を示す。c k \_ m e mが1P R A Mに入力されると、w e信号がハイになる。c k \_ m e mの入力によりワード線w 1は立ち上がる。また、r p b i tの電荷の引き抜きが始まるがこれにはメモリセルに対するライト動作が完了するのと同程度の時間がかかる。r p b i tがロウになることで、w o f fはハイとなり、ワード線w 1は立ち下がる。このw o f f信号をa c k信号として用いることで、メモリセルの動作終了信号を適切なタイミングで出力することが可能である。

## 【0058】

以上の様に、本実施の形態1を用いることで、シングルポートメモリ1P R A Mの内部制御信号を使用して、時分割制御のタイミングを得ることができ、従来の時分割多ポートメモリで必要だった、追加のクロック生成回路を必要とせず、小面積、低消費電力で時分割多ポートメモリを実現できる。

## 【0059】

## (実施の形態2)

本発明の実施の形態2は、図1に示した前記実施の形態1に係る時分割多ポートメモリにおいて、時分割制御信号生成回路P C O N Tの回路構成を変えたものである。

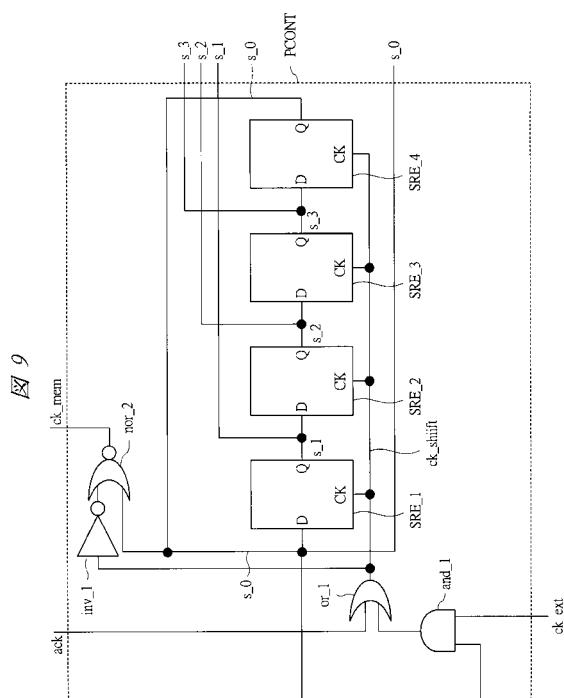

## 【0060】

図9に、本発明の実施の形態2による時分割制御信号生成回路P C O N Tの構成を示す。この回路は、時分割多ポートメモリの動作を実現する回路である。シングルポートS R A M 1P R A Mを外部クロックより速く動作させ、外部クロック1サイクルの間に複数ポートからの読み出し、もしくは書き込み要求を時分割で順次処理することで擬似的に多ポートメモリ動作を実現する。

## 【0061】

本実施の形態2は、前記実施の形態1の時分割制御信号生成回路P C O N Tにおいて、

10

20

30

40

50

シフトレジスタの代わりにリングカウンタを使用した構成となっており、P C O N T以外は前記実施の形態1と同様の構成である。実施の形態1との違いは、シフトレジスタS R E\_1～4の数が、ポート数+1の4つになっていることである。

#### 【0062】

すなわち、ポート数が任意の数Nのとき、シフトレジスタの数はN+1となる。N番目のポートのデータの処理が終了した後、1 P R A Mからの動作終了信号によりシフトレジスタが動作し、出力がs\_0になっているシフトレジスタの出力がハイとなり、全てのポートのデータの処理が終わった後に、s\_0の値をハイにセットすることが可能である。このような回路構造により、実施の形態1(図3)におけるn o r\_1が不要となる。

#### 【0063】

したがって、本実施の形態2を用いることで、小面積、低電力な時分割多ポートメモリが実現でき、ポート数が多いためにn o r\_1への入力が多くなった時に、シフトレジスタを1つ追加するだけによく、高速な時分割多ポートメモリが実現可能である。

#### 【0064】

##### (実施の形態3)

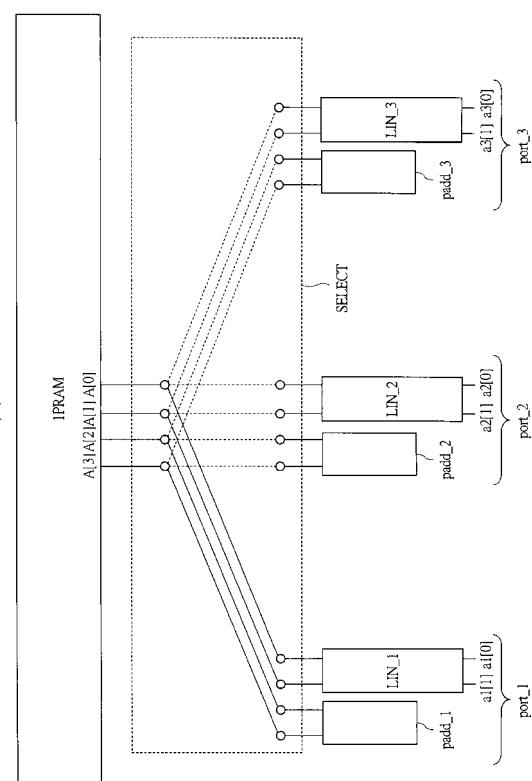

本発明の実施の形態3では、前記実施の形態1とは異なるメモリアドレス指定方法の一例を示す。

#### 【0065】

図10は、本発明の実施の形態3において、入力アドレス信号の一部を各ポートで固定した時分割多ポートメモリを示す概念図である。図10において、p a d d\_1～3は、各ポートの固定アドレス生成回路である。図10では、一例として、1 P R A Mのアドレスは4ビットであり、各ポートのアドレス指定信号は2ビット、残り2ビットは各ポートの固定アドレス生成回路p a d d\_1～3で生成される場合を示す。なお、アドレスのビット数は、これに限定されるものではなく、何ビットでもよい。

#### 【0066】

図10に示すように、固定アドレス生成回路p a d d\_1～3により、1 P R A Mのアドレスのうち数ビットを各ポートで固定することで、各ポートがアクセスできるメモリを限定することができる。そのため、独立したメモリが複数あるのと同じように扱うことが可能である。

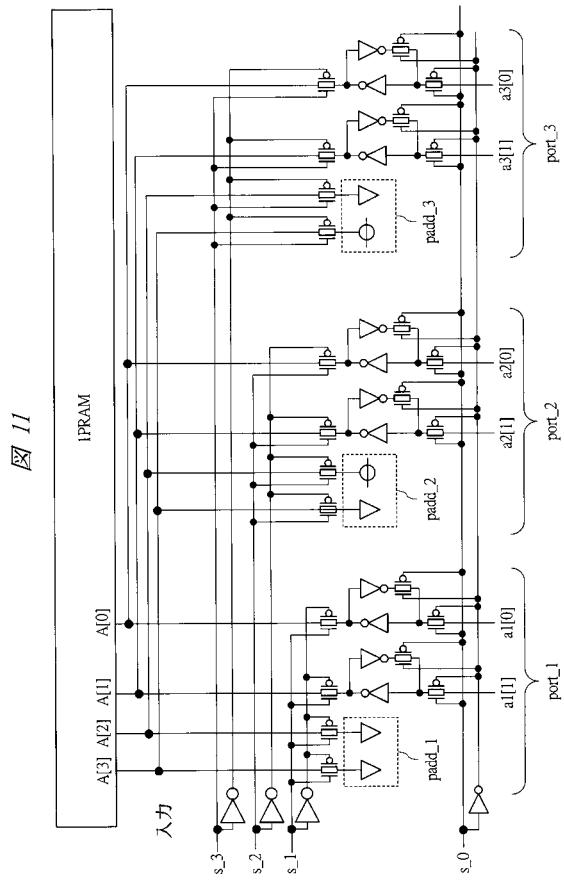

#### 【0067】

図11に、固定アドレス生成回路p a d d\_1～3の具体的な回路例を示す。p a d d\_1～3の内部では、アドレス信号2ビットを各ポート固有の値になるように、ハイかローに固定する。このような構成にすることにより、各ポートがアクセスできるメモリを限定することができる。そして、独立したメモリが複数ある場合と同じように扱うことができ、外部モジュールの信号線と、1 P R A Mとして使用するメモリの構成を変更することなく使用可能となる。

#### 【0068】

##### (実施の形態4)

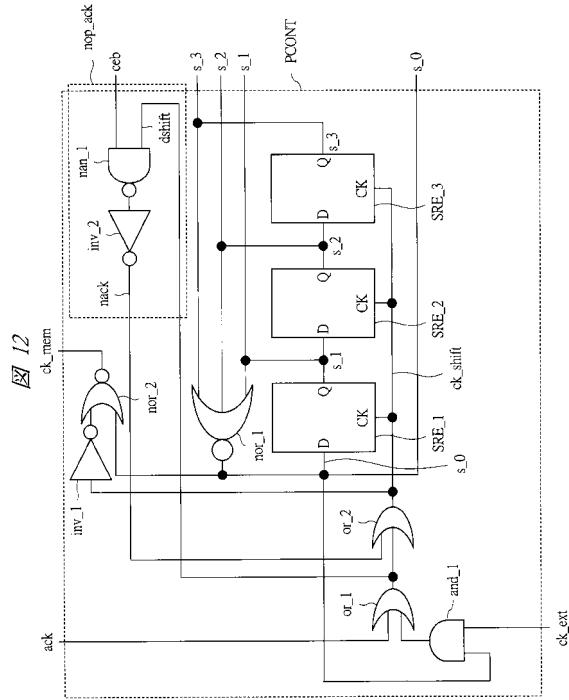

本発明の実施の形態4は、図1に示した前記実施の形態1に係る時分割多ポートメモリについて、時分割制御信号生成回路P C O N Tの回路構成を変えたものである。

#### 【0069】

図12に、本発明の実施の形態4による時分割制御信号生成回路P C O N Tの構成を示す。

#### 【0070】

1 P R A Mに動作／非動作を制御する外部入力信号端子がある場合、あるポートで非動作を選択する信号が入力された時、1 P R A Mの内部制御信号が出力されず、そのポートで動作が終わってしまうことがある。これを避けるために、非動作を選択する信号が入力された場合に、1 P R A Mとの接続を次のポートに切り替え、データ処理の動作を続けるための回路が必要である。これに対する対策を施した回路が図12に示す回路である。

#### 【0071】

10

20

30

40

50

図12に示すように、本実施の形態4は、前記実施の形態1(図3)のPCONTに対して、ポートから1PRAMの非動作選択信号が入った時に、ack信号の代わりとなる信号を生成する回路(nop\_ack, or\_2)を附加した構成となっている。PCONT以外の回路構成は、前記実施の形態1と同様である。

#### 【0072】

回路nop\_ackに入力されている信号cebは、チップの外部から入力されるチップイネイブル信号の反転信号である。チップイネイブル信号は、1PRAMに動作開始信号が入った場合の動作/非動作を制御する信号であり、動作させる場合はハイ、動作させない場合はロウである。信号dshiftはck\_shifを遅らせた信号である。

#### 【0073】

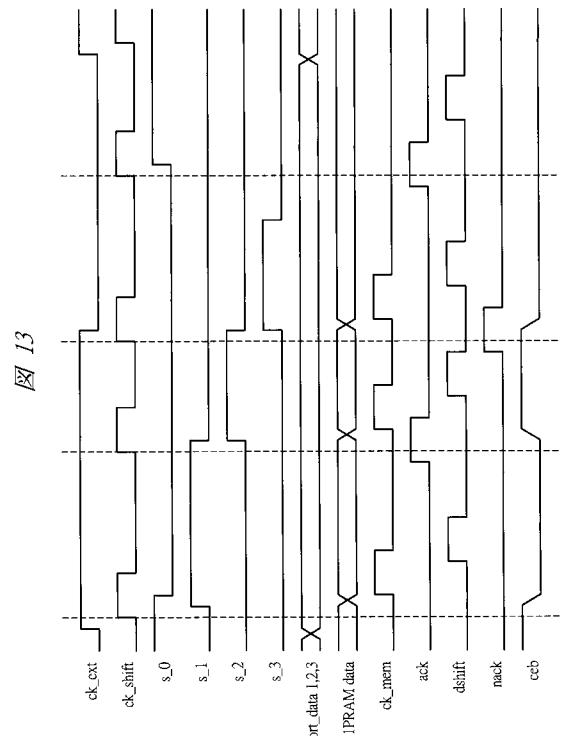

図13に、図12の時分割制御信号生成回路PCONTの動作タイミングチャートを示す。図13のタイミングチャートでは、ポート数が3、port\_2のチップイネイブル信号がロウ、つまり1PRAMに動作要求をしない場合を示す。

#### 【0074】

まず、port\_1からの要求動作が終了した後、1PRAMは動作終了信号ackを出し、信号ck\_shifによってシフトレジスタSRE\_1~3が動き、1PRAMとつながる選択ポートが切り替わり、s\_2がアサートされることによりport\_2が選択されている状態に変化し、ck\_memが1PRAMに入力される。

#### 【0075】

しかし、port\_2のチップイネイブル信号がロウなので1PRAMは動作せずack信号が出ない。

#### 【0076】

一方、ck\_shifを遅らせた信号dshiftがnan\_1に入力され、nan\_1の一方の入力cebが1のため信号nackがハイに立ち上がり、シフトレジスタSRE\_1~3を作動させ、ck\_mem信号を作り次の動作が行われる。

#### 【0077】

したがって、図12に示した時分割制御信号生成回路PCONTにより、複数のポートのうち、動作要求をしないものがあっても、1PRAMの動作が可能になる。

#### 【0078】

#### (実施の形態5)

本発明の実施の形態5は、前記実施の形態1(図1)とは異なる信号を、ラッチLOUT\_1~3の保持データ出力信号として使う構成のものである。本実施の形態5では、外部へのデータ出力制御信号として、外部クロックを使用している。

#### 【0079】

図14に、本実施の形態5による時分割多ポートメモリの構成を示す。入力データ用ラッチ回路LIN\_1~3と出力データ用ラッチ回路LOUT\_1~3以外の構成は前記実施の形態1(図1)と同じである。なお、図14において、i1~3はce1~3, we1~3, a1~3[0~9], d1~3[0~11]に対応し、o1~3はq1~3[0~11]に対応し、IはCE, WE, A[0~9], D[0~11]に対応し、OはQ[0~11]に対応する。

#### 【0080】

実施の形態1では、図3に示したnor\_1の出力信号であるs\_0が立ち上がっている間、データを出力する構成であったのに対して、本実施の形態5では外部クロック信号ck\_extが立ち上がっている間、データを出力する構成となっている。

#### 【0081】

図14では、ポート数が3の場合を示すが、これに限定されるものではない。図14に示すように、各出力ポートの出力データ用のラッチLOUT\_1~3に外部クロック信号ck\_extが入力されている。タイミングチャートとしては、図4の制御信号s\_0をck\_extに置き換えたものとなる。また、LIN\_1~3への入力信号s\_0をck\_extに置き換えることも可能である。

**【0082】**

したがって、本実施の形態5によれば、外部のモジュールのタイミング設計によっては、ラッチのデータ入力、出力のタイミングを最適化することが可能である。

**【0083】**

## (実施の形態6)

本発明の実施の形態6は、前記実施の形態1に対して、`ack`生成回路(図7)と`PONT`(図3)の構成を変えたものである。他の回路構成は前記実施の形態1と同じである。

**【0084】**

図15に、本実施の形態6による時分割多ポートメモリにおける`ack`信号生成回路の構成を示す。図15に示すように、`ack`信号として取り出す信号が実施の形態1と異なり、`rpbbit`信号を`ack`信号として外部に取り出している。10

**【0085】**

図16に、本実施の形態6による時分割多ポートメモリにおける`PONT`回路の構成を示す。図16に示すように、実施の形態1の`PONT`(図3)に対して、点線部分の回路`nor_ack`を附加した構成となっている。`nor_ack`は最後のポートの処理が終わった後、次の外部クロック`ck_ext`が入力され`ck_shift`を立ち上げようとした時に、`ck_shift`が立ち上がったままで、シフトレジスタを動作させることができないということを防ぐためである。

**【0086】**

`woff`が立ち上がった時点ではライト動作は終了しているが、リード動作はセンスアンプによる信号の増幅を行うので、動作がまだ終わっていない可能性がある。一度、立ち下がった`rpbbit`が立ち上がった時点でリード動作であってもライト動作であっても処理は終了しているので、動作終了信号として、より適している。20

**【0087】**

ただし、`nor_ack`回路の追加が必要である。もし、`PRAM`が最後のポートの処理が終わって、次の外部クロック`ck_ext`が入力されるまでに`rpbbit`が立ち下がるような構造であれば、`nor_ack`の回路は不要となる。

**【0088】**

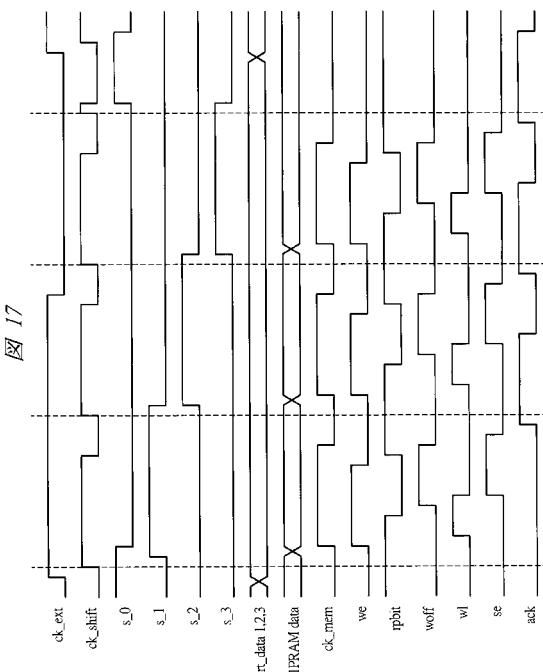

図17に、本発明の実施の形態6による時分割多ポートメモリの動作を示すタイミングチャートを示す。図17に示すように、順次、ポートのデータ処理を行っていき、全てのポートのデータ処理が終了した後、`s_0`がハイになり、`ck_shift`が立ち下げられ、次の外部クロック信号`ck_ext`の入力をきっかけとして、`ck_shift`が立ち上がり、シフトレジスタ`SRE_1~3`を動作させる。30

**【0089】**

`rpbbit`の立ち上がり動作は、読み出し動作時、書き込み動作時ともに動作が全て終了したタイミングで行われるので、`rpbbit`信号を`ack`信号として使用することで、タイミング設計の容易化が可能である。

**【0090】**

## (実施の形態7)

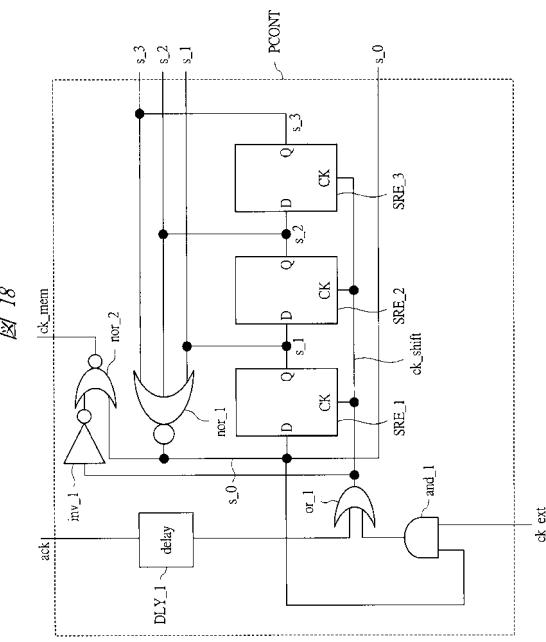

本発明の実施の形態7は、前記実施の形態1の`PONT`(図3)に対して、`ack`信号のタイミング調整のためのディレイ回路を附加した構成となっている。`PONT`以外の構成は実施の形態1の回路と同じ構成である。40

**【0091】**

図18に、本発明の実施の形態7における`PONT`の回路構成を示す。図18に示すように、本実施の形態7は、前記実施の形態1(図3)の`PONT`に対して、ディレイ回路`DLY_1`を附加した構成となっている。

**【0092】**

このような回路構成とすることにより、`PRAM`から出力された`ack`信号のディレイ回路`DLY_1`での遅延によって、`ck_shift`, `ck_mem`の生成タイミング50

の調整が可能となる。

**【0093】**

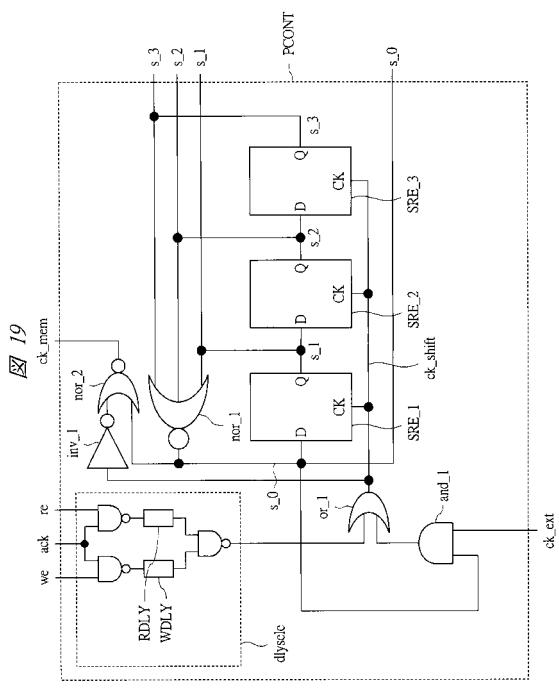

(実施の形態8)

本発明の実施の形態8は、前記実施の形態1のPCONT(図3)に対して、ack信号のタイミング調整のためのディレイを、読み出し動作と書き込み動作で選択可能にする回路を附加したものである。PCONT以外の構成は実施の形態1と同じである。

**【0094】**

書き込み動作と読み出し動作で異なるディレイを使用するのは、書き込み動作と読み出し動作ではワード線を立ち下げるまでの時間が異なることや、読み出し動作にはセンスアンプの動作時間が含まれることから、動作終了までの時間が異なるので、動作終了信号を生成するタイミングをより最適にするためである。

**【0095】**

図19に、本発明の実施の形態8におけるPCONTの回路構成を示す。図19に示すように、本実施の形態8は、前記実施の形態1(図3)のPCONTに対して、点線で囲まれた回路 $dlyse1e$ を附加した構成となっている。図19において、RDLY, WDLYは、それぞれ遅延時間の異なるディレイ回路である。信号weはライトイネイブル信号、信号reはリードイネイブル信号であり、外部からポートに入力される信号である。これらの信号は、1PRAMが書き込み動作をするか、読み出し動作をするかを制御するものである。

**【0096】**

本実施の形態8では、1PRAMは、weがハイ、reがロウの時、書き込み動作を行い、reがハイ、weがロウの時、読み出し動作を行う。図19に示すように、 $dlyse1e$ では、NAND回路の組み合わせにより、書き込み動作の時はWDLYを通過した信号が波形を生成する。読み込み動作の時はRDLYを通過した信号が波形を生成する。

**【0097】**

本実施の形態8によれば、ack信号から生成されるck\_shift、ck\_memについて、書き込み動作または読み出し動作に応じて、それぞれ生成タイミングの調整が可能となる。

**【0098】**

(実施の形態9)

本発明の実施の形態9は、前記実施の形態1のack信号生成回路(図7)に対して、ack信号を遅延させるディレイ回路を1PRAM内部に附加したものである。ack信号生成回路以外の構成は実施の形態1と同じである。

**【0099】**

図20に、本発明の実施の形態9における1PRAM内部のack信号生成回路の構成を示す。図20に示すように、実施の形態1のack信号生成回路(図7)に対して、ディレイ回路 $DLY_1$ が附加された構成となっている。

**【0100】**

本実施の形態9によれば、1PRAM内部のack信号生成回路にディレイ回路を附加することでack信号出力タイミングの調整が容易になる。

**【0101】**

(実施の形態10)

本発明の実施の形態10は、前記実施の形態1のack信号生成回路(図7)に対して、読み出し動作と書き込み動作で異なるack信号のディレイが選択可能な回路を附加したものである。他の回路構成は、前記実施の形態1と同じである。本実施の形態10は、1PRAMの内部に、ack信号の出力タイミングを調整するためのディレイ回路が附加されていることを特徴とする。

**【0102】**

図21に、本実施の形態10における1PRAM内部のack信号発生回路の構成を示す。図21に示すように、前記実施の形態1のack信号生成回路(図7)に対して、回

10

20

30

40

50

路 d l y s e l e を追加し、 a c k 信号の出力タイミングを、書き込みまたは読み出し動作それぞれで異なる出力タイミングに調整することが可能な構成となっている。 R D L Y , W D L Y は、それぞれ遅延時間のことなるディレイ回路である。 N A N D 回路の組み合わせにより、読み出し動作の時には R D L Y を通過した波形が a c k 信号として、書き込み動作の時には W D L Y を通過した波形が a c k 信号として出力される。

#### 【 0 1 0 3 】

本実施の形態 1 0 によれば、読み出し動作と書き込み動作のそれに応じて、 1 P R A M から出力される a c k 信号の出力タイミングの調整が容易となる。

#### 【 0 1 0 4 】

( 実施の形態 1 1 )

10

本発明の実施の形態 1 1 は、前記実施の形態 1 ( 図 1 ) に対して、各ポートのデータ保持回路として、ラッチ回路ではなくフリップフロップ回路を使用したものである。

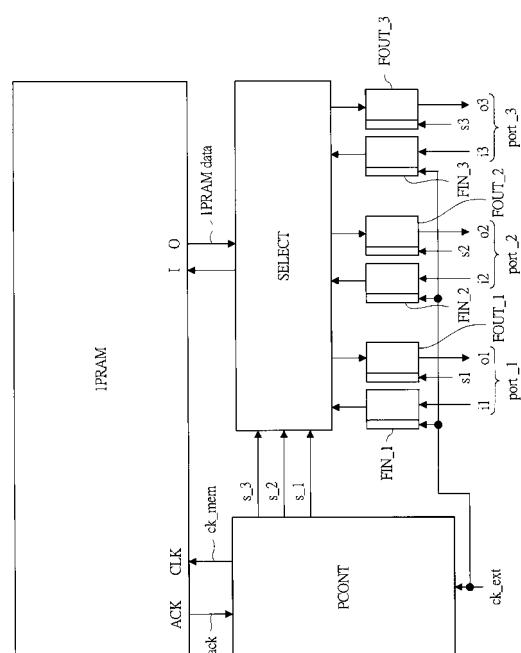

#### 【 0 1 0 5 】

図 2 2 に、本実施の形態 1 1 による時分割多ポートメモリの構成を示す。図 2 2 に示す回路は、ラッチ回路 L I N \_ 1 ~ 3 , L O U T \_ 1 ~ 3 の代わりにフリップフロップ回路 F I N \_ 1 ~ 3 , F O U T \_ 1 ~ 3 を使用した構成となっている。それ以外の回路構成は前記実施の形態 1 ( 図 1 ) と同じである。本実施の形態 1 1 では、内部へのデータ入力制御信号として、外部クロック信号 c k \_ e x t を使用している。また、外部へのデータ出力制御信号として、 s 1 ~ 3 を使用している。

#### 【 0 1 0 6 】

20

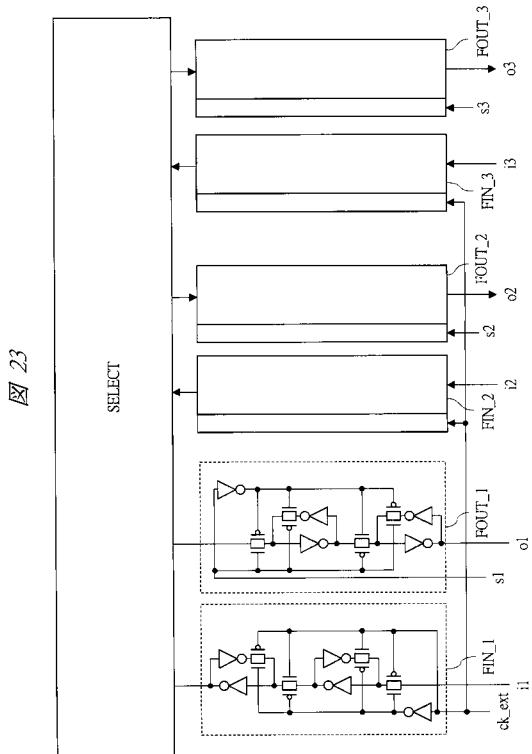

また、図 2 3 に、フリップフロップ回路 F I N \_ 1 ~ 3 , F O U T \_ 1 ~ 3 の詳細な回路図を示す。

#### 【 0 1 0 7 】

なお、図 2 2 および図 2 3 において、 i 1 ~ 3 は c e 1 ~ 3 , w e 1 ~ 3 , a 1 ~ 3 [ 0 ~ 9 ] , d 1 ~ 3 [ 0 ~ 1 1 ] に対応し、 o 1 ~ 3 は q 1 ~ 3 [ 0 ~ 1 1 ] に対応し、 I は C E , W E , A [ 0 ~ 9 ] , D [ 0 ~ 1 1 ] に対応し、 O は Q [ 0 ~ 1 1 ] に対応する。

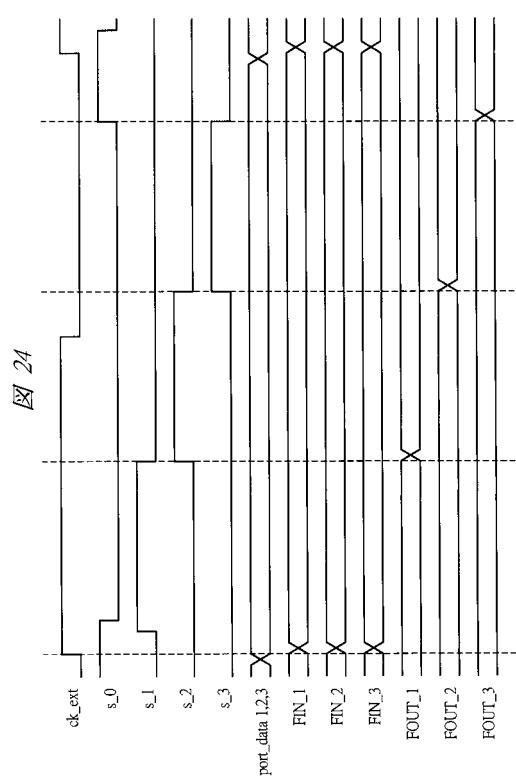

#### 【 0 1 0 8 】

図 2 4 に、 F I N \_ 1 ~ 3 及び F O U T \_ 1 ~ 3 の動作タイミングチャートを示す。図 2 4 に示すように、 c k \_ e x t の立ち上がりで F I N \_ 1 ~ 3 は外部からの入力データを取り込み保持する。 F O U T \_ 1 ~ 3 は、それぞれ s \_ 1 ~ 3 の立下りで 1 P R A M からの出力データを取り込み保持し、外部へ出力する。

30

#### 【 0 1 0 9 】

このように、本実施の形態 1 1 によれば、エッジ動作で記録の取り込み保持を行うので、動作のタイミング設計の容易化が可能である。

#### 【 0 1 1 0 】

( 実施の形態 1 2 )

図 2 5 は、本発明の実施の形態 1 2 による半導体集積回路装置の構成を示すブロック図である。

#### 【 0 1 1 1 】

40

図 2 5 において、 1 P R A M はシングルポートメモリ、 P C O N T は制御信号 s \_ 0 、 c k \_ m e m を生成する回路、 L I N \_ 1 は外部からの入力データ i 1 を c k \_ e x t の立ち上がりで保持するラッチ回路、 L O U T \_ 1 は制御信号 s \_ 0 の立ち上がりで 1 P R A M の出力データ o 1 を保持して外部に出力するラッチ回路である。また、 P C O N T は、例えば、図 3 、図 9 、図 1 2 、図 1 6 、図 1 8 、図 1 9 のような回路構成とする。

#### 【 0 1 1 2 】

信号 c k \_ e x t は外部クロック信号、信号 c k \_ m e m は P C O N T から入力される 1 P R A M の動作開始信号、信号 a c k は 1 P R A M の動作終了信号である。 1 P R A M の動作終了信号 a c k を利用して、 1 P R A M の動作終了後に外部クロックと関係なく L O U T \_ 1 から外部に読み出しデータを出力することが可能な回路構成である。

50

**【0113】**

図26に、図25の回路の動作タイミングチャートを示す。図26に示すように、`c k_ext`の立ち上がりで、ハイだった`s_0`が立ち下げられ、1PRAMの動作開始用の信号`c k_mem`が生成される。`c k_mem`が入力されることで1PRAMが動作を開始し、動作終了時に動作終了信号`ack`を出力し、`s_0`が立ち上がり、`LOUT_1`からデータが出力される。

**【0114】**

したがって、本実施の形態12によれば、メモリの動作終了タイミングに合わせて外部ヘデータを出力することが可能となる。

**【0115】**

10

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

**【0116】**

例えば、前記実施の形態においては、シングルポートメモリ(1PRAM)としてSRAMについて説明したが、これに限定されるものではなく、DRAM、EPROMなどの他のメモリについても適用可能である。

**【図面の簡単な説明】****【0117】**

20

【図1】本発明の実施の形態1において、SRAM内部の信号を利用した時分割多ポートメモリの構成を示すブロック図である。

【図2】本発明の実施の形態1において、SRAM内部の信号を利用した時分割多ポートメモリの動作を示すタイミングチャートである。

【図3】本発明の実施の形態1において、シフトレジスタを利用した時分割制御信号生成回路PCONTの構成を示す回路図である。

【図4】本発明の実施の形態1において、時分割制御信号生成回路PCONTの動作を示すタイミングチャートである。

【図5】本発明の実施の形態1において、時分割多ポートメモリの入力信号のラッチ回路及びセレクタ回路の構成を示す回路図である。

【図6】本発明の実施の形態1において、時分割多ポートメモリの出力信号のラッチ回路及びセレクタ回路の構成を示す回路図である。

30

【図7】本発明の実施の形態1において、時分割制御に利用するSRAM内部のワード線立ち下げ信号生成回路の構成を示す回路図である。

【図8】本発明の実施の形態1において、SRAM内部のワード線立ち下げ信号生成回路の動作を示すタイミングチャートである。

【図9】本発明の実施の形態2において、リングカウンタを利用した時分割制御信号生成回路PCONTの構成を示す回路図である。

【図10】本発明の実施の形態3において、入力アドレス信号の一部を各ポートで固定した時分割多ポートメモリの構成を示す概念図である。

【図11】本発明の実施の形態3において、入力アドレス信号の一部を各ポートで固定した時分割多ポートメモリのラッチ部分の詳細構成を示す回路図である。

40

【図12】本発明の実施の形態4において、書き込み及び読み出し動作要求をしない場合に別のポートに処理を移す回路を付加した時分割制御信号生成回路PCONTの構成を示す回路図である。

【図13】本発明の実施の形態4において、書き込み及び読み出し動作要求をしない場合に別のポートに処理を移す回路を付加した時分割制御信号生成回路PCONTの動作を示すタイミングチャートである。

【図14】本発明の実施の形態5において、外部へのデータ出力制御信号に外部クロックを使用した時分割多ポートメモリの構成を示すブロック図である。

【図15】本発明の実施の形態6において、レプリカビット線を`ack`信号として利用す

50

る S R A M 内部のワード線立ち下げ信号生成回路の構成を示す回路図である。

【図 16】本発明の実施の形態 6において、レプリカビット線を a c k 信号として利用する時分割多ポートメモリの時分割制御信号生成回路 P C O N T の構成を示す回路図である。

【図 17】本発明の実施の形態 6において、レプリカビット線を a c k 信号として利用する時分割多ポートメモリの時分割制御信号生成回路 P C O N T の動作を示すタイミングチャートである。

【図 18】本発明の実施の形態 7において、a c k 信号が c k \_ s h i f t 及び c k \_ m e m を生成するタイミングを調整するディレイ回路を付加した時分割制御信号生成回路 P C O N T の構成を示す回路図である。 10

【図 19】本発明の実施の形態 8において、a c k 信号が c k \_ s h i f t 及び c k \_ m e m を生成するタイミングを書き込み動作、読み出し動作で異なる調整可能な回路を付加した時分割制御信号生成回路 P C O N T の構成を示す回路図である。

【図 20】本発明の実施の形態 9において、S R A M 内部のワード線立ち下げ信号生成回路に a c k 信号を出力するタイミングを調整するディレイ回路を付加した回路の構成を示す回路図である。

【図 21】本発明の実施の形態 10において、S R A M 内部のワード線立ち下げ信号生成回路に a c k 信号を出力するタイミングを書き込み動作、読み出し動作で異なる調整可能な回路を付加した回路の構成を示す回路図である。

【図 22】本発明の実施の形態 11において、外部との入出力信号保持回路にフリップフロップを用いた時分割多ポートメモリの構成を示すブロック図である。 20

【図 23】本発明の実施の形態 11において、入出力信号保持回路の詳細構成を示す回路図である。

【図 24】本発明の実施の形態 11において、外部との入出力信号保持回路にフリップフロップを用いた時分割多ポートメモリの動作を示すタイミングチャートである。

【図 25】本発明の実施の形態 12において、外部へのデータ出力タイミングを S R A M 内部の信号を利用して制御する記憶装置の構成を示すブロック図である。

【図 26】本発明の実施の形態 12において、外部へのデータ出力タイミングを S R A M 内部の信号を利用して制御する記憶装置の動作を示すタイミングチャートである。

#### 【符号の説明】

##### 【 0 1 1 8 】

1 P R A M シングルポート S R A M

S E L E C T セレクタ

P C O N T 時分割制御信号生成回路

L I N \_ 1 ~ 3 入力データ用ラッチ回路

L O U T \_ 1 ~ 3 出力データ用ラッチ回路

p o r t \_ 1 ~ 3 ポート

L A T C H ラッチ回路

S R E \_ 1 ~ 4 シフトレジスタ

a n d \_ 1 A N D ( アンド ) 回路

n a n \_ 1 N A N D ( ナンド ) 回路

o r \_ 1 , o r \_ 2 O R ( オア ) 回路

n o r \_ 1 , n o r \_ 2 N O R ( ノア ) 回路

i n v \_ 1 , i n v \_ 2 インバータ

p a d d \_ 1 ~ 3 固定アドレス生成回路

D L Y \_ 1 ディレイ回路

n o p \_ a c k , n o r \_ a c k , d l y s e l e 回路

t r \_ 1 N M O S トランジスタ

t r \_ 2 P M O S トランジスタ

w 1 ワード線

30

40

50

r p b i t レプリカ回路ビット線

r c w レプリカ回路ワード線

a [ 0 ~ 9 ] 10ビットアドレス信号

d [ 0 ~ 11 ] 12ビット入力データ

q [ 0 ~ 11 ] 12ビット出力データ

c k \_ e x t 外部クロック信号

c k \_ m e m 1 P R A M の動作制御信号

a c k 1 P R A M の動作終了信号

s \_ 0 ~ 3 制御信号

c l k 1 P R A M 内部用クロック信号 10

c e チップイネイブル信号 ( 1 P R A M の動作選択信号 )

c e b c e 反転信号

w e ワードイネイブル信号 ( 書き込み動作選択信号 )

w e b w e 反転信号

r e 読み出し動作指定信号

r e b r e 反転信号

w o f f ワード線立ち下げ信号

c k \_ s h i f t , n a c k , d s h i f t 信号

【図 1】

【図 2】

【図3】

【 四 4 】

【図5】

【 四 6 】

【図7】

【 四 8 】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

図25

【図26】

図26

---

フロントページの続き

(56)参考文献 特表2002-526848(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 413