(12)

## Offenlegungsschrift

(21) Aktenzeichen: 10 2012 111 282.7

(51) Int Cl.: **G11C 11/4074** (2013.01)

(22) Anmeldetag: 22.11.2012

**G05F 1/56** (2013.01)

(43) Offenlegungstag: 29.08.2013

**H02M 3/07** (2013.01)

(30) Unionspriorität:

10-2012-0019832

27.02.2012 KR

(74) Vertreter:

**Kuhnen & Wacker Patent- und

Rechtsanwaltsbüro, 85354, Freising, DE**

(71) Anmelder:

**Samsung Electronics Co., Ltd., Suwon-si,

Kyonggi, KR**

(72) Erfinder:

**Lee, Dong-su, Hwaseong-si, Gyeonggi-do, KR**

**Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen**

(54) Bezeichnung: **Spannungsgenerator, welche an kleine externe Versorgungsspannungen anpassbar sind**

(57) Zusammenfassung: Spannungsgeneratoren (100) können einen Pegel einer hohen Zielspannung in Bezug auf eine niedrige externe Versorgungsspannung erzeugen. Ein Referenzspannungsgenerator (100) umfasst einen Clamp-Regler (110), der von einer ersten Versorgungsspannung (VEXT) betrieben wird, die von einer externen Quelle zugeführt wird, und empfängt eine erste Spannung (VREF), um eine Clamp-Spannung (VREFA<sub>PRE</sub>) zu erzeugen, und einen Pegelverstärker (120), der von einer zweiten Versorgungsspannung (VPPE) betrieben wird, die höher ist als die erste Versorgungsspannung (VEXT), und der die Clamp-Spannung (VREFA<sub>PRE</sub>) empfängt, um eine Referenzspannung (VREFA) zu erzeugen. Die Clamp-Spannung (VREFA<sub>PRE</sub>) kann so eingestellt sein, dass sie einen Spannungspegel aufweist, der in einer erfolgreichen Wiederherstellungsoperation mit Bezug auf eine Speicherzellanordnung in einem Direktzugriffspeicher (DRAM) resultiert.

**Beschreibung****QUERVERWEIS AUF

VERWANDTE ANMELDUNGEN**

**[0001]** Diese Anmeldung beansprucht die Vorzüge der koreanischen Patentanmeldung Nr. 10-2012-0019832, eingereicht am 27. Februar 2012 beim Koreanischen Amt für geistiges Eigentum, deren Offenbarung hiermit in ihrer Gesamtheit durch Bezugnahme aufgenommen ist.

**HINTERGRUND**

**[0002]** Die gegenwärtige Offenbarung bezieht sich auf eine Halbleiterspeichervorrichtung und insbesondere auf Spannungsgenerator, die sogar bei niedriger externer Versorgungsspannung interne Spannung auf einem spezifischen Pegel erzeugen, und auf eine Halbleiterspeichervorrichtung und ein Speichersystem, die die Spannungsgenerator umfassen.

**[0003]** Eine Betriebsumgebung einer Halbleiterspeichervorrichtung neigt dazu, die Leistungsaufnahme durch Verwendung einer niedrigen Betriebsspannung zu reduzieren. Die Halbleiterspeichervorrichtung kann ausgelegt sein, um von einer internen Spannung betrieben zu werden, die von einer Spannung, die von einer externen Quelle bereitgestellt wird, spannungsherabgesetzt ist. Mit der Entwicklung niedriger Leistungsaufnahme von Halbleiterspeichervorrichtungen wird der Pegel einer externen Versorgungsspannung, die eine Betriebsspannung ist, weiter reduziert. Aufgrund der externen Versorgungsspannung eines herabgesetzten Pegels ist auch der Pegel einer internen Spannung weiter herabgesetzt. Wenn der Pegel der internen Spannung unter eine Zielspannung herabgesetzt wird, können die Betriebscharakteristika der Halbleiterspeichervorrichtung verschlechtert werden.

**ZUSAMMENFASSUNG**

**[0004]** Die offenbarten Ausführungsformen sehen Spannungsgeneratoren vor, die eine Referenzspannung eines spezifischen Pegels erzeugen, und eine interne Versorgungsspannung eines spezifischen Pegels sogar bei niedriger externer Versorgungsspannung und eine Halbleiterspeichervorrichtung und ein Speichersystem, die die Spannungsgenerator umfassen.

**[0005]** Gemäß einer Ausführungsform ist ein Referenzspannungsgenerator vorgesehen, der einen Clamp-Regler umfasst, der mit einer ersten Versorgungsspannung betrieben wird, die von einer externen Quelle bereitgestellt wird, und der eine erste Spannung empfängt, um eine Clamp-Spannung zu erzeugen und einen Pegelverstärker, der mit einer zweiten Versorgungsspannung betrieben wird, die

höher ist, als die erste Versorgungsspannung, und der die Clamp-Spannung empfängt, um eine Referenzspannung zu erzeugen.

**[0006]** Der Referenzspannungsgenerator kann in einem Direktzugriffsspeicher (DRAM) enthalten sein und die Clamp-Spannung kann so eingestellt sein, dass sie einen Spannungspegel aufweist, der in einem erfolgreichen Wiederherstellungarbeitsablauf in Bezug auf die Speicherzelldaten in dem DRAM resultiert.

**[0007]** Der Clamp-Regler kann eine erste Vergleichseinheit umfassen, die durch die erste Versorgungsspannung betrieben wird, und die konfiguriert ist, um die erste Spannung mit einer Spannung eines ersten Knotens zu vergleichen, um die Spannung eines zweiten Knotens auszugeben, eine erste Schalteinheit, die von der ersten Versorgungsspannung betrieben wird, und die konfiguriert ist, um als Antwort auf die Spannung des zweiten Knotens, die Clamp-Spannung auszugeben, und eine erste Pegelsteuereinheit, die konfiguriert ist, um die Spannung des ersten Knotens auszugeben, die den gleichen Pegel aufweist wie den Pegel der ersten Spannung, und um einen Pegel der Clamp-Spannung zu regeln.

**[0008]** Die erste Schalteinheit kann ein p-Kanal-Metallocidhalbleiter(PMOS)-Transistor sein, in dem die erste Versorgungsspannung mit einem Source verbunden ist, der zweite Knoten mit einem Gate verbunden ist und die Clamp-Spannung mit einem Drain verbunden ist.

**[0009]** Die erste Pegelsteuereinheit kann einen ersten Widerstand umfassen, der zwischen die Clamp-Spannung und den zweiten Knoten geschaltet ist, und einen zweiten Widerstand, der zwischen den zweiten Knoten und eine Erdungsspannung geschaltet ist.

**[0010]** Der Pegelverstärker kann eine zweite Vergleichseinheit umfassen, die von der zweiten Versorgungsspannung betrieben wird und die Clamp-Spannung mit einer Spannung eines dritten Knotens vergleicht, um eine Spannung eines vierten Knotens auszugeben, eine zweite Schalteinheit, die von der zweiten Versorgungsspannung betrieben wird und als Antwort auf die Spannung des vierten Knotens eine Referenzspannung ausgibt und eine zweite Pegelsteuereinheit zum Ausgeben der Spannung des dritten Knotens, die den gleichen Pegel aufweist, wie ein Pegel der Clamp-Spannung, und zum regeln eines Pegels der Referenzspannung.

**[0011]** Die zweite Schalteinheit kann ein p-Kanal-Metallocidhalbleiter(PMOS)-Transistor sein, in dem die zweite Versorgungsspannung mit einem Source verbunden ist, der vierte Knoten mit einem Gate

verbunden ist, und die Referenzspannung mit einem Drain verbunden ist.

**[0012]** Die zweite Pegelsteuereinheit kann einen dritten Widerstand umfassen, der zwischen die Referenzspannung und den dritten Knoten geschaltet ist und einen vierten Widerstand, der zwischen den dritten Knoten und die Erdungsspannung geschaltet ist.

**[0013]** Der Referenzspannungsgenerator kann weiterhin eine Ladungspumpeinheit umfassen, um die erste Versorgungsspannung zu empfangen, und die zweite Versorgungsspannung durch einen Ladungspumpvorgang auszugeben.

**[0014]** Der Referenzspannungsgenerator kann weiterhin eine Spannungsabfalleinheit umfassen, um eine dritte Versorgungsspannung zu empfangen, die höher ist als die erste Versorgungsspannung, und um die dritte Versorgungsspannung herabzusetzen, um die zweite Versorgungsspannung auszugeben.

**[0015]** Gemäß eines anderen Aspektes der offebarten Ausführungsformen ist ein Direktzugriffsspeicher (DRAM) vorgesehen, dem eine erste externe Versorgungsspannung von einer externen Quelle zugeführt wird, wobei das DRAM eine Vergleichseinheit umfasst, die von einer zweiten Versorgungsspannung betrieben wird, die höher ist als die erste Versorgungsspannung, und die konfiguriert ist, um eine erste Spannung mit einer Spannung eines ersten Knotens zu vergleichen, um eine Spannung eines zweiten Knotens zu erzeugen, eine Schalteinheit, die von der zweiten Versorgungsspannung betrieben wird, und die konfiguriert ist, um als Antwort auf die Spannung des zweiten Knotens eine Referenzspannung auszugeben; und eine Pegelsteuereinheit, die konfiguriert ist, um die Spannung des ersten Knotens auszugeben, die den gleichen Pegel aufweist, wie ein Pegel der ersten Spannung, und um einen Pegel der Referenzspannung zu regeln, wobei die erste Spannung so eingestellt ist, dass sie einen Spannungsspeigel aufweist, der in einer erfolgreichen Wiederherstellungsoperation in Bezug auf die Speicherzelldaten in dem DRAM resultiert.

**[0016]** Gemäß einer anderen Ausführungsform ist ein Direktzugriffsspeicher (DRAM) vorgesehen, dem eine erste externe Versorgungsspannung von einer externen Quelle zugeführt wird, wobei der DRAM einen Spannungsteiler umfasst, der konfiguriert ist, um eine Spannung zwischen einer ersten externen Versorgungsspannung und einer Erdungsspannung aufzuteilen, um eine Clamp-Spannung zu erzeugen und einen Pegelverstärker, der von einer zweiten Versorgungsspannung betrieben wird, die höher ist als die erste Versorgungsspannung, und der konfiguriert ist, um die Clamp-Spannung zu empfangen, um die Referenzspannung zu erzeugen, wobei die Clamp-Spannung so eingestellt ist, dass sie einen minimalen

Spannungspegel aufweist, der in einer erfolgreichen Wiederherstellungsoperation in Bezug auf die Speicherzelldaten in dem DRAM resultiert.

**[0017]** Gemäß einer anderen Ausführungsform ist eine Halbleiterspeichervorrichtung vorgesehen, die einen ersten Referenzspannungsgenerator umfasst, der konfiguriert ist, um eine erste Versorgungsspannung zu empfangen, die von einer externen Quelle zugeführt wird, und, um eine erste Referenzspannung zu erzeugen, einen zweiten Referenzspannungsgenerator, der von einer zweiten Versorgungsspannung betrieben wird, die höher ist als die erste Versorgungsspannung und der konfiguriert ist, um die erste Referenzspannung zu empfangen, um eine Clamp-Spannung und eine zweite Referenzspannung zu erzeugen und einen internen Spannungsgenerator, der von der zweiten Versorgungsspannung betrieben wird und der konfiguriert ist, um die zweite Referenzspannung zu empfangen, um eine interne Versorgungsspannung zu erzeugen.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

**[0018]** Beispielausführungsformen werden durch die folgende detaillierte Beschreibung in Verbindung mit den begleitenden Zeichnungen klarer verstanden, in denen:

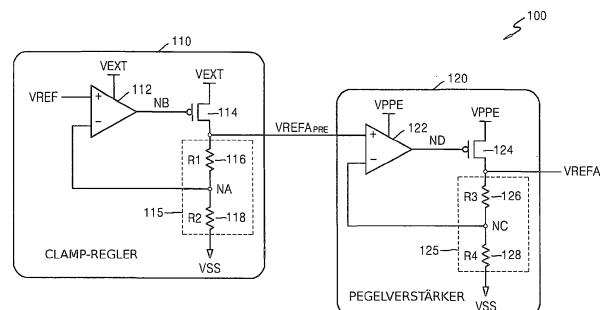

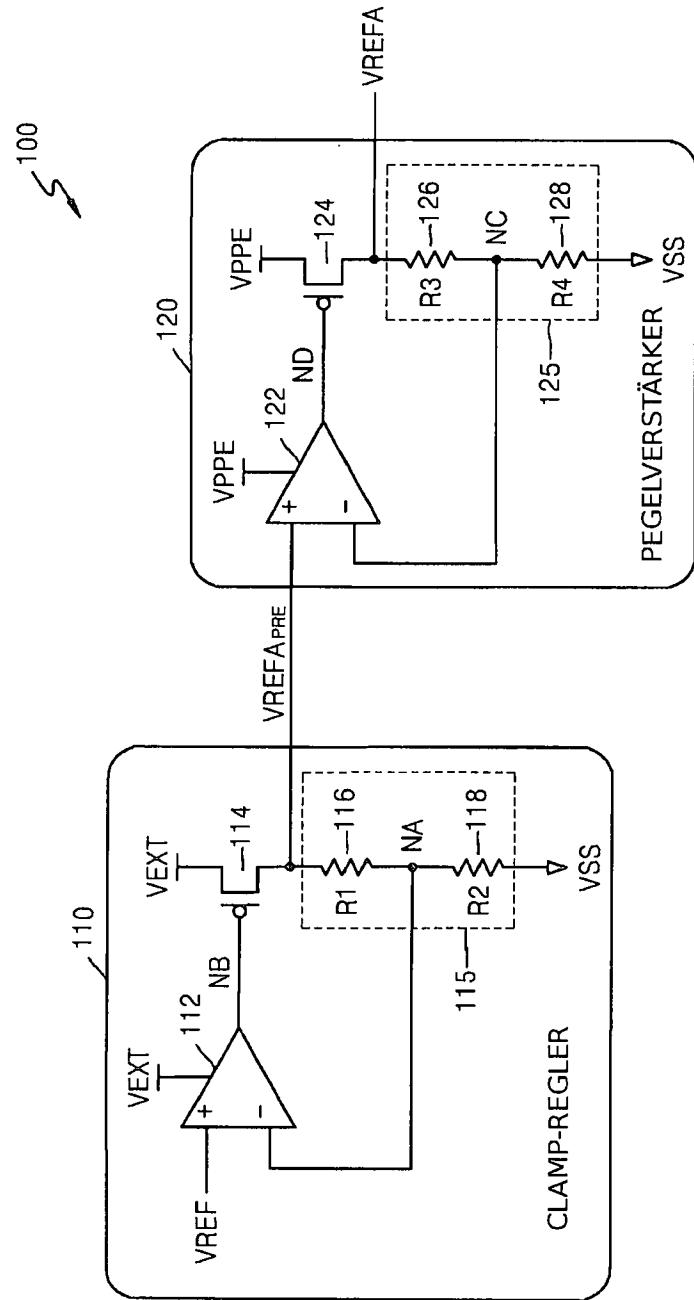

**[0019]** [Fig. 1](#) ein Diagramm zum Beschreiben eines Referenzspannungsgenerators gemäß einer ersten beispielhaften Ausführungsform des erfinderischen Konzeptes ist;

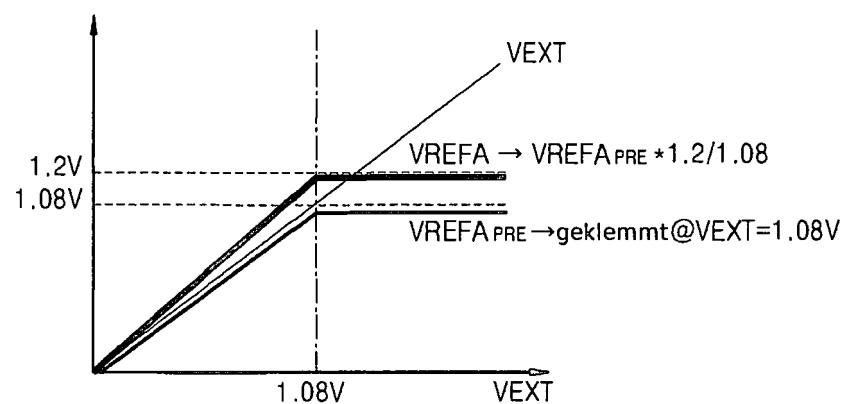

**[0020]** [Fig. 2](#) ein Graph zum Beschreiben eines beispielhaften Arbeitsablaufs eines Referenzspannungsgenerators nach [Fig. 1](#) gemäß einer Ausführungsform ist;

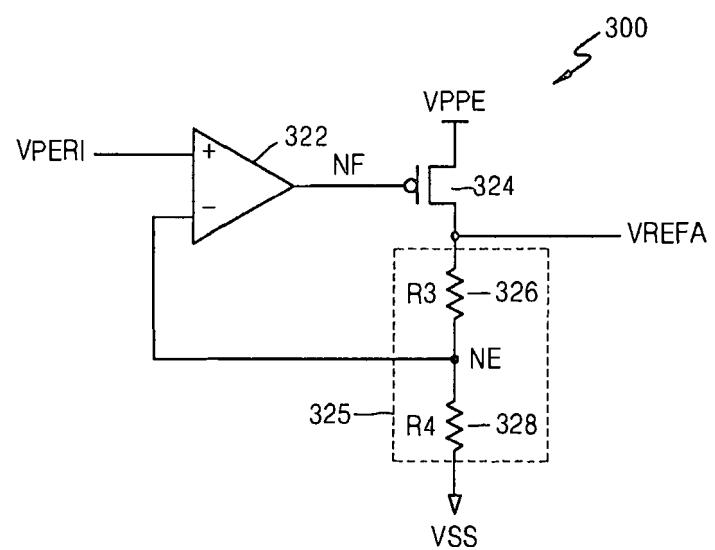

**[0021]** [Fig. 3](#) ein Diagramm zum Beschreiben eines Referenzspannungsgenerators gemäß einer zweiten beispielhaften Ausführungsform ist;

**[0022]** [Fig. 4](#) ein Diagramm zum Beschreiben eines Referenzspannungsgenerators gemäß einer dritten beispielhaften Ausführungsform ist;

**[0023]** [Fig. 5](#) ein Diagramm zum Beschreiben eines Referenzspannungsgenerators gemäß einer vierten beispielhaften Ausführungsform ist;

**[0024]** [Fig. 6](#) ein Diagramm zum Beschreiben eines Referenzspannungsgenerators gemäß einer fünften beispielhaften Ausführungsform ist;

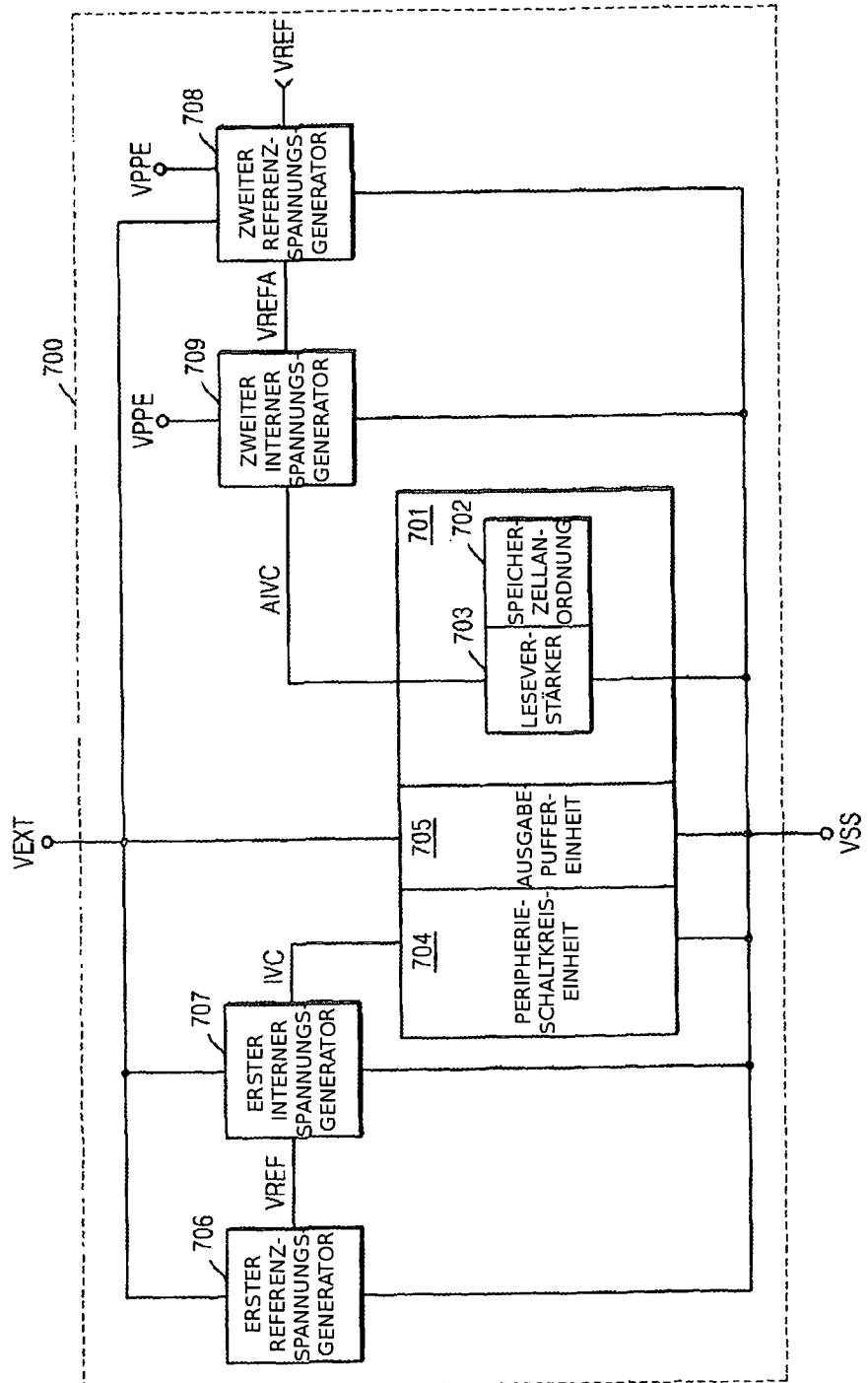

**[0025]** [Fig. 7](#) ein Diagramm zum Beschreiben eines Beispiels eines Direktzugriffsspeichers (DRAM) ist, der einen Referenzspannungsgenerator gemäß verschiedener beispielhafter Ausführungsformen umfasst;

[0026] [Fig. 8](#) ein beispielhaftes Schaltkreisdigramm zum Beschreiben eines ersten Referenzspannungsgenerators nach [Fig. 7](#) gemäß einer Ausführungsform ist;

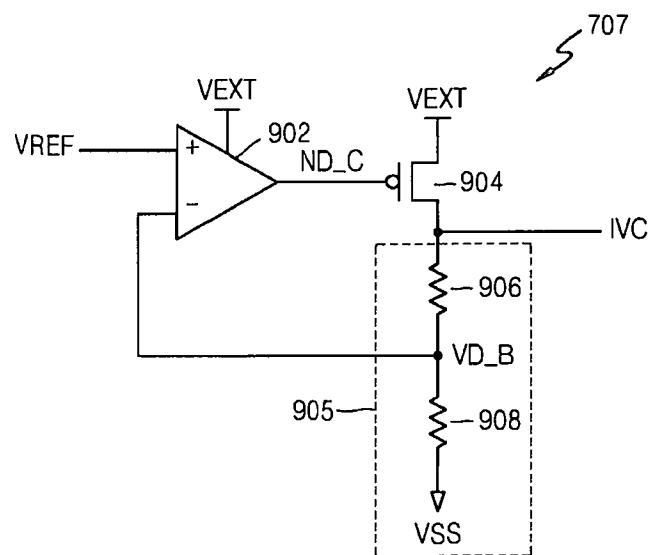

[0027] [Fig. 9](#) ein beispielhaftes Schaltkreisdigramm zum Beschreiben eines ersten internen spannungserzeugenden Schaltkreises nach [Fig. 7](#) gemäß einer Ausführungsform ist;

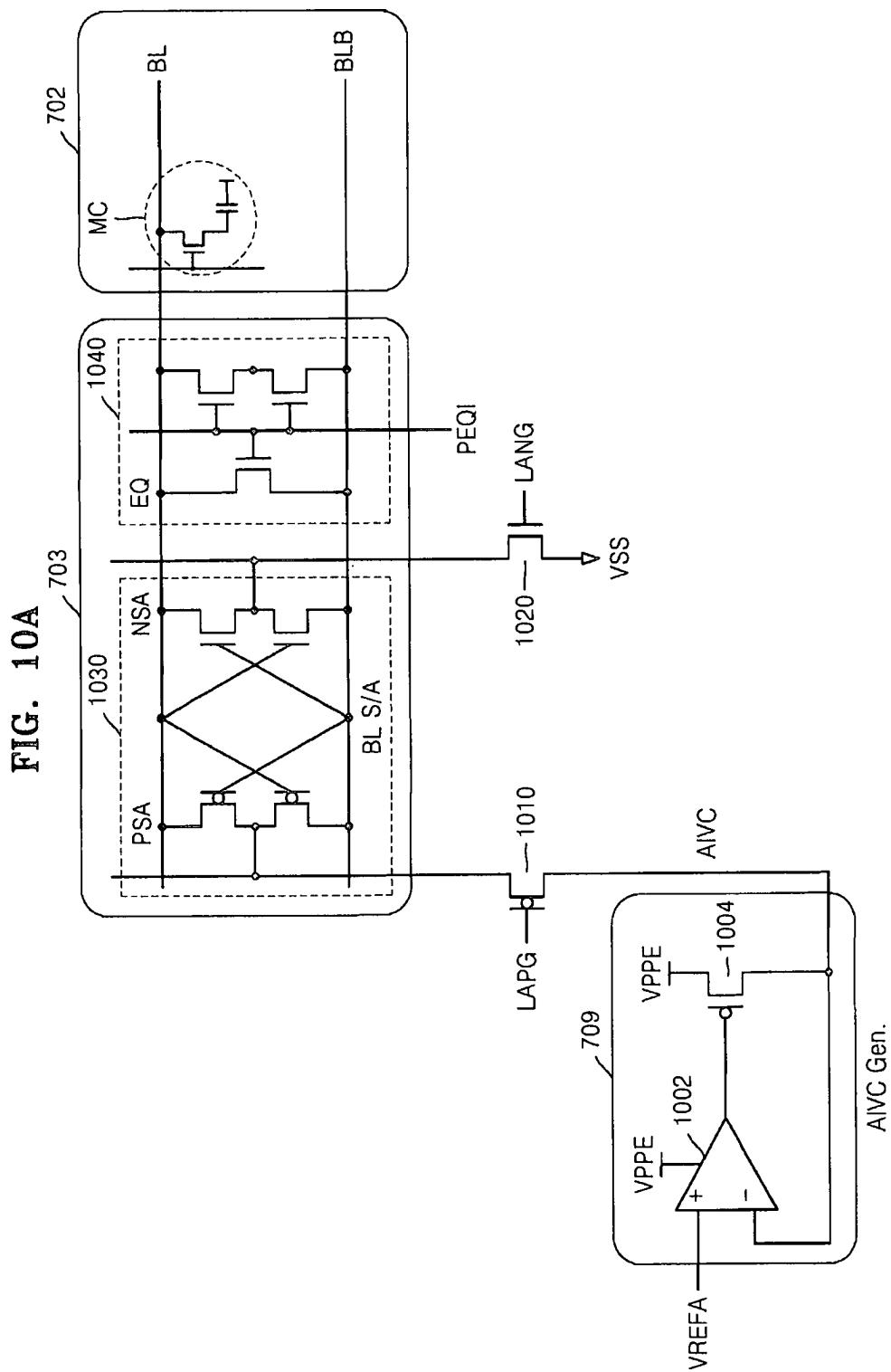

[0028] [Fig. 10A](#) ein beispielhaftes Schaltkreisdigramm zum Beschreiben eines zweiten internen Spannungsgenerators nach [Fig. 7](#) und eines Leseverstärkers eines Kernblocks gemäß einer Ausführungsform ist;

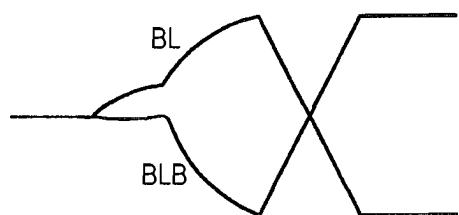

[0029] [Fig. 10B](#) ein beispielhaftes Diagramm zum Beschreiben einer Datenschreiboperation auf einer Bitleitung nach [Fig. 10A](#) gemäß einer Ausführungsform ist;

[0030] [Fig. 11](#) ein Diagramm zum Beschreiben eines anderen Beispieles eines DRAM ist, der einen Referenzspannungsgenerator gemäß verschiedener beispielhafter Ausführungsformen umfasst;

[0031] [Fig. 12](#) ein Diagramm zum Beschreiben einer Halbleiterspeichervorrichtung ist, die einen Referenzspannungsgenerator gemäß verschiedener beispielhafter Ausführungsformen umfasst;

[0032] [Fig. 13](#) ein Diagramm ist, das ein Implementierungsbeispiel eines Speichersystems zeigt, auf das eine Halbleiterspeichervorrichtung nach [Fig. 12](#) gemäß einer Ausführungsform angewendet ist; und

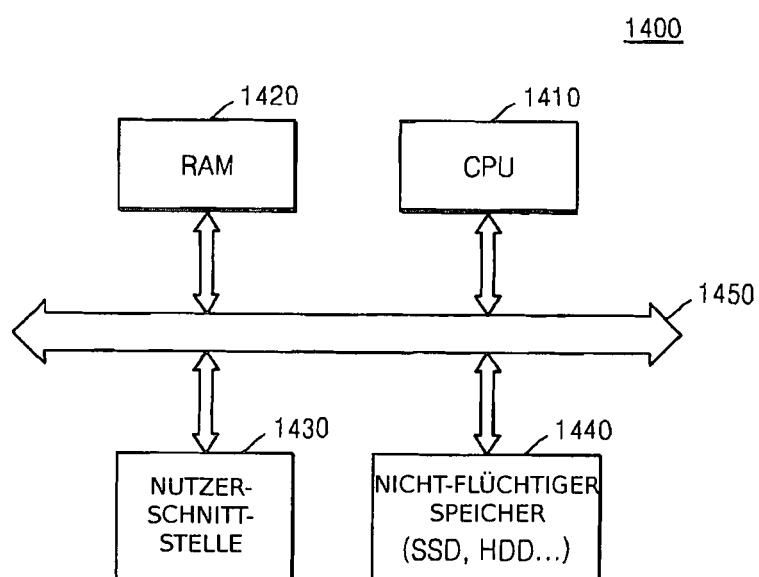

[0033] [Fig. 14](#) ein Blockdiagramm eines Datenverarbeitungssystems ist, das daran installiert ein Speichersystem gemäß einer beispielhaften Ausführungsform aufweist.

## DETAILLIERTE BESCHREIBUNG

[0034] Nachfolgend werden Ausführungsformen unter Bezugnahme auf die begleitenden Zeichnungen beschrieben. Die Ausführungsformen sind vorgesehen, um für diejenigen mit durchschnittlichem Wissen auf dem Fachgebiet die Offenbarung vollständiger zu beschreiben. Verschiedene Veränderungen können an den offenbarten Ausführungsformen vorgenommen werden und die offenbarten Ausführungsformen können verschiedene Formen aufweisen, auch wenn bestimmte beispielhafte Ausführungsformen in den Zeichnungen dargestellt und im Detail beschrieben werden. Diese Ausführungsformen sind nicht dafür vorgesehen, das erfinderische Konzept zu limitieren und es sollte so aufgefasst werden, dass die Ausführungsformen alle Veränderungen, Äquivalente und Substitutionen innerhalb des Sinnes und des Umfangs des erfinderischen Konzeptes umfassen.

Durchgehend beziehen sich in den Zeichnungen gleiche Referenzzeichen auf gleiche Komponenten. In den begleitenden Zeichnungen können Strukturen im Sinne der Klarheit als vergrößert oder übertrieben dargestellt sein.

[0035] Die hier verwendete Terminologie ist ausschließlich für den Zweck des Beschreibens der Offenbarung und ist nicht als limitierend gedacht. Wie hier verwendet sind die Singularformen so gemeint, dass sie auch die Pluralformen umfassen, sofern der Zusammenhang nicht klar auf anderes hinweist. Es ist weiterhin so zu verstehen, dass die Begriffe "umfasst", "beinhaltet" und/oder "aufweist", wenn sie in dieser Beschreibung verwendet werden, das Vorhandensein des bezeichneten Merkmals, der Nummer, des Schrittes, des Arbeitsablaufes, der Komponente, des Elementes oder einer Kombination davon bezeichnen aber, dass sie nicht die Gegenwart oder Hinzufügung eines oder mehrerer anderer Merkmale, Nummern, Schritten, Arbeitsabläufe, Komponenten, Elementen oder Kombinationen davon ausschließen.

[0036] Weiterhin ist es so zu verstehen, dass, wenn auf ein Element als "verbunden" oder "gekoppelt mit" oder "auf" einem anderen Element befindlich Bezug genommen wird, dieses direkt verbunden oder gekoppelt oder auf dem anderen Element befindlich sein kann oder dass zwischengelagerte Elemente zugegen sein können. Im Gegensatz sind keine zwischengelagerten Elemente zugegen, wenn auf eine Element als "direkt verbunden" oder "direkt gekoppelt" zu einem anderen Element Bezug genommen wird. Wie hier verwendet umfasst der Begriff "und/oder" jedes beliebige und alle Kombinationen von einem oder mehreren der damit in Zusammenhang stehenden aufgelisteten Gegenstände und kann als "/" abgekürzt werden.

[0037] Es ist so zu verstehen, dass, auch wenn die Begriffe erstes, zweites, etc. hier verwendet sein können, um verschiedene Elemente zu beschreiben, diese Elemente nicht durch diese Begriffe limitiert sein sollten. Soweit nicht anders angegeben, werden diese Begriffe nur verwendet, um ein Element von einem anderen zu unterscheiden. Zum Beispiel könnte ein erster Chip als ein zweiter Chip benannt werden und auf ähnliche Weise ein zweiter Chip als erster Chip benannt werden ohne von den Lehren der Offenbarung abzuweichen.

[0038] Die hier verwendeten Begriffe, einschließlich technischer und wissenschaftlicher Begriffe, haben die gleiche Bedeutung wie Begriffe, die für gewöhnlich von denen, die über Fähigkeiten auf dem Fachgebiet verfügen, verstanden werden, solange die Begriffe nicht anders definiert sind. Es ist so aufzufassen, dass Begriffe, die in einem gemeinhin verwendeten Wörterbuch definiert sind, Bedeutungen aufweisen, die mit denen in der damit in Zusammenhang stehen-

den Technologie übereinstimmen. Solange die Begriffe nicht ausdrücklich definiert sind, sollten sie nicht ideal oder exzessiv als formelle Bedeutungen analysiert werden.

**[0039]** Eine Halbleiterspeichervorrichtung kann einen internen Spannungsherabsetzer umfassen, der eine interne Versorgungsspannung AIVC aus einer externen Versorgungsspannung VEXT erzeugt. Wenn die Halbleiterspeichervorrichtung als ein Direktzugriffsspeicher (DRAM) implementiert ist, kann die interne Versorgungsspannung AIVC als eine Versorgungsspannung eines Kernblocks verwendet werden, der eine DRAM-Zellenanordnung umfasst.

**[0040]** Unter den Betriebscharakteristika des DRAM kann eine Auffrischungszeit proportional sein zu der menge an Ladung, die in einem Zellknoten gespeichert ist. Der Zellknoten bezieht sich auf einen Knoten zwischen einem DRAM-Zelltransistor und einem Zellkondensator. Die Menge an Ladung, die in dem Zellknoten, Q, gespeichert ist, ist proportional zu einer Zellkapazität C basierend auf  $Q = CV$  und sie ist proportional zu einer internen Spannung IVC, die eine gespeicherte Spannung V ist. Wenn die Größe eines Zellkondensators aufgrund der Segmentierung eines Halbleiterherstellungsprozesses abnimmt, nimmt auch die Zellkapazität ab. Unter solchen Umständen, wo die Zellkapazität abnimmt, muss der Pegel einer internen Versorgungsspannung AIVC hoch sein, um eine Auffrischungszeit zu sichern. Die Auffrischungszeit kann auf einem bestimmten erwünschten Pegel gehalten werden, wenn die interne Versorgungsspannung AIVC, unabhängig von dem Pegel der externen Versorgungsspannung VEXT, konstant auf einem Zielpunktspiegel gehalten wird.

**[0041]** Die interne Versorgungsspannung AIVC wird typischerweise dadurch erzeugt, dass sie von der externen Versorgungsspannung VEXT spannungsherabgesetzt wird. Mit der Entwicklung niedriger Leistungsaufnahme des DRAM wird der Pegel der externen Versorgungsspannung VEXT reduziert. Der reduzierte Pegel der externen Versorgungsspannung VEXT kann niedriger sein als der Zielpunktspiegel der internen Versorgungsspannung AIVC. In diesem Fall kann die interne Versorgungsspannung AIVC, aufgrund der pegelreduzierten externen Versorgungsspannung VEXT, so erzeugt werden, dass sie einen niedrigeren Pegel aufweist, als der Zielpunktspiegel. Aufgrund der internen Versorgungsspannung AIVC eines Pegels, der niedriger ist als der Zielpunktspiegel, ist die Auffrischungszeit des DRAM schwierig zu sichern. Dementsprechend besteht ein Bedarf an Spannungsgeneratoren, die in der Lage sind den Zielpunktspiegel der internen Versorgungsspannung AIVC konstant zu halten, sogar wenn der Pegel der externen Versorgungsspannung VEXT reduziert ist.

**[0042]** [Fig. 1](#) ist ein Diagramm zum Beschreiben eines Referenzspannungsgenerators **100** gemäß einer beispielhaften Ausführungsform.

**[0043]** Mit Bezug auf [Fig. 1](#) kann der Referenzspannungsgenerator **100** einen Clamp-Regler **110** und einen Pegelverstärker **120** umfassen. Der Clamp-Regler **110** wird von einer ersten Versorgungsspannung VEXT betrieben und empfängt eine erste Spannung VREF, um eine Clamp-Spannung VREFA<sub>PRE</sub> zu erzeugen. Die erste externe Versorgungsspannung VEXT kann eine externe Versorgungsspannung sein, zum Beispiel empfangen von einer Spannungsquelle außerhalb einer Halbleiterspeichervorrichtung. Der Pegelverstärker **120** wird von einer zweiten Versorgungsspannung VPPE betrieben und empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, um eine Referenzspannung VREFA zu erzeugen. Die zweite Versorgungsspannung VPPE kann so eingestellt sein, dass sie einen höheren Pegel aufweist, als die erste Versorgungsspannung VEXT. Die zweite Versorgungsspannung VPPE kann auch eine externe Versorgungsspannung sein.

**[0044]** Der Clamp-Regler **110** kann ein Spannungsregelschaltkreis sein, der eine erste Vergleichseinheit **112**, eine erste Schalteinheit **114** und eine erste Pegelsteuereinheit **115** umfasst. Die erste Vergleichseinheit **112** wird von der ersten Versorgungsspannung VEXT betrieben und vergleicht die erste Spannung VREF mit einer Spannung eines ersten Knotens NA, um eine Spannung eines zweiten Knotens NB auszugeben. Die erste Versorgungsspannung VEXT kann zum Beispiel ungefähr 1,1 V betragen. Die erste Spannung VREF kann zum Beispiel ungefähr 0,75 V betragen. Die erste Vergleichseinheit **112** kann einen Logic-Low-Pegel an den zweiten Knoten NB ausgeben, wenn die Spannung des ersten Knotens NA niedriger ist als die erste Spannung VREF. Die erste Vergleichseinheit **112** kann einen Logic-High-Pegel an den zweiten Knoten NB ausgeben, wenn die Spannung des ersten Knotens NA höher ist als die erste Spannung VREF. Die erste Vergleichseinheit **112** kann Schaltkreiselemente umfassen, die einen Komparator bilden, und daher kann hier auf sie als ein Komparatorschaltkreis Bezug genommen werden. Der zweite Knoten NB kann mit der ersten Schalteinheit **114** verbunden sein.

**[0045]** Die erste Schalteinheit **114** kann ein Schaltkreis sein, der zum Beispiel einen p-Kanal-Metall-oxidhalbleiter(PMOS)-Transistor umfasst, der von der ersten Versorgungsspannung VEXT betrieben wird, und der über sein Gate mit dem zweiten Knoten NB verknüpft ist. In dem PMOS-Transistor ist die erste Versorgungsspannung VEXT mit einer Quelle verbunden, der zweite Knoten NB ist mit einem Gate verbunden und ein Drain gibt die Clamp-Spannung VREFA<sub>PRE</sub> aus. Bezuglich der ersten Schalteinheit **114** kann der PMOS-Transistor als Antwort auf die

Spannung des zweiten Knotens NB, die dem Logic-Low-Pegel entspricht, eingeschaltet werden. Die erste Versorgungsspannung VEXT wird durch den eingeschalteten PMOS-Transistor bereitgestellt, um dadurch den Pegel der Clamp-Spannung VREFA<sub>PRE</sub> zu erhöhen. Bezuglich der ersten Schalteinheit 114 kann der PMOS-Transistor als Antwort auf die Spannung des zweiten Knotens NB, die einem Logic-High-Pegel entspricht, ausgeschaltet werden. Der ausgeschaltete PMOS-Transistor hebt den Pegel der Clamp-Spannung VREFA<sub>PRE</sub> nicht an, da er die Versorgung der zweiten Versorgungsspannung VEXT unterbricht.

**[0046]** Zwischen die Clamp-Spannung VREFA<sub>PRE</sub> und die Erdungsspannung VSS kann die erste Pegelsteuereinheit 115 geschaltet sein, auf die auch als der erste Pegelspannungsregelschaltkreis 115 Bezug genommen wird, in dem ein erster Widerstand 116 und ein zweiter Widerstand 118 in Serie geschaltet sein können. Ein Verbindungsknoten zwischen dem ersten Widerstand 116 und dem zweiten Widerstand 118 ist der erste Knoten NA. Aufgrund von Arbeitsabläufen der ersten Vergleichseinheit 112 und der ersten Schalteinheit 114, die in dem Clamp-Regler 110 umfasst ist, wird die Spannung des ersten Knotens NA fast gleich wie die erste Spannung VREF (z. B. die Spannung des ersten Knotens NA ist so konfiguriert, dass sie zu der ersten Spannung VREF konvergiert). Daher kann die Clamp-Spannung VREFA<sub>PRE</sub> durch einen Widerstand R1 des ersten Widerstandes 116 und einem Widerstand R2 des zweiten Widerstandes 118 wie unten bestimmt werden.

$$VREFA_{PRE} = VREF \left( \frac{R1+R2}{R2} \right) \quad (1)$$

**[0047]** Dementsprechend kann der Pegel der Clamp-Spannung VREFA<sub>PRE</sub> durch Anpassen des Widerstandes R1 des ersten Widerstandes 116 und des Widerstandes R2 des zweiten Widerstandes 118 so geregelt werden, dass es einen bestimmten Wert in Bezug auf VREF aufweist. Die Clamp-Spannung VREFA<sub>PRE</sub> kann auf einen minimalen Spannungspiegel eingestellt sein, der in einer erfolgreichen Zellwiederherstellungsoperation resultiert, wenn Daten in eine Speicherzelle MC, die mit einer Bitleitung BL des DRAM verbunden ist, geschrieben werden. Die Clamp-Spannung VREFA<sub>PRE</sub> kann zum Beispiel auf ungefähr 1,08 V eingestellt sein.

**[0048]** Der Pegelverstärker 120 kann ein Spannungsregelschaltkreis sein, der eine zweite Vergleichseinheit 122, eine zweite Schalteinheit 124 und eine zweite Pegelsteuereinheit 125 umfasst. Die zweite Vergleichseinheit 122 wird von der zweiten Versorgungsspannung VPPE betrieben und vergleicht die Clamp-Spannung VREFA<sub>PRE</sub> mit einer Spannung des dritten Knotens NC, um eine Spannung eines vierten Knotens ND auszugeben. Die zweite Versorgungsspannung VPPE kann so einge-

stellt sein, dass sie einen höheren Pegel aufweist, als der Pegel der ersten Versorgungsspannung VEXT. Zum Beispiel kann die erste Versorgungsspannung VEXT ungefähr 1,2 V ist die zweite Versorgungsspannung VPPE zum Beispiel ungefähr 1,6 V sein. Die zweite Vergleichseinheit 122 kann Schaltkreiselemente, die eine Komparator formen, umfassen und daher kann auf sie hier als ein Komparatorschaltkreis Bezug genommen werden.

**[0049]** Die zweite Vergleichseinheit 122 kann einen Logic-Low-Pegel an den vierten Knoten ND ausgeben, wenn die Spannung des dritten Knotens NC niedriger ist als die Clamp-Spannung VREFA<sub>PRE</sub>. Die zweite Vergleichseinheit 122 kann einen Logic-High-Pegel an den vierten Knoten ND ausgeben, wenn die Spannung des dritten Knotens NC höher ist als die Clamp-Spannung VREFA<sub>PRE</sub>. Der vierte Knoten ND kann mit der zweiten Schalteinheit 124 verbunden sein.

**[0050]** Die zweite Schalteinheit 124 kann ein Schaltkreis sein, der z. B. einen PMOS-Transistor, der von der zweiten Versorgungsspannung VPPE betriebene wird und der über sein Gate mit dem vierten Knoten ND verknüpft ist, umfasst. In dem PMOS-Transistor ist die zweite Versorgungsspannung mit einer Quelle verbunden, der vierte Knoten ND ist mit einem Gate verbunden und ein Drain gibt die Referenzspannung VREFA aus. Bezuglich der zweiten Schalteinheit 124 kann der PMOS-Transistor als Antwort auf die Spannung des vierten Knotens, die dem Logic-Low-Pegel entspricht, eingeschaltet werden. Die zweite Versorgungsspannung VPPE wird durch den eingeschalteten PMOS-Transistor bereitgestellt, um somit den Pegel der Referenzspannung VREFA zu erhöhen. Bezuglich der zweiten Schalteinheit 124 kann der PMOS-Transistor als Antwort auf die Spannung des vierten Knotens, die einem Logic-High-Pegel entspricht, ausgeschaltet werden. Der ausgeschaltete PMOS-Transistor hebt den Pegel der Referenzspannung VREFA nicht an, da er die Versorgung der zweiten Versorgungsspannung VPPE unterbricht.

**[0051]** Zwischen die Referenzspannung VREFA und die Erdungsspannung VSS kann eine zweite Pegelsteuereinheit 125 geschaltet sein, auf die auch als zweiter Pegelspannungsregelschaltkreis 115 Bezug genommen wird, in dem ein dritter Widerstand 126 und ein vierter Widerstand 128 in Serie verbunden sein können. Ein Verbindungsknoten zwischen dem dritten Widerstand 126 und dem vierten Widerstand 128 ist der dritte Knoten NC. Aufgrund von Arbeitsabläufen der zweiten Vergleichseinheit 122 und der zweiten Schalteinheit 124, die in dem Pegelverstärker 120 umfasst ist, wird die Spannung des dritten Knotens NC fast gleich zu der Clamp-Spannung VREFA<sub>PRE</sub>. Daher kann die Referenzspannung VREFA durch den Widerstand R3 des dritten Widerstan-

des **126** und den Widerstand R4 des vierte Widerstandes **128** wie unten bestimmt werden.

$$VREFA = VREFA_{PRE} \left( \frac{R3+R4}{R4} \right) \quad (2)$$

**[0052]** Dementsprechend kann der Pegel der Referenzspannung VREFA durch Anpassen des Pegels der Clamp-Spannung VREFA<sub>PRE</sub>, des Widerstandes R3 des dritten Widerstandes **126** und des Widerstandes R4 des vierten Widerstandes **128** so eingestellt werden, dass sie einen bestimmten Wert aufweist. Die Referenzspannung VREFA kann so erzeugt werden, dass sie zum Beispiel 1,2 V beträgt, wenn die Clamp-Spannung VREFA<sub>PRE</sub> zum Beispiel 1,08 V beträgt. Der Pegelverstärker **120** empfängt eine Clamp-Spannung VREFA<sub>PRE</sub>, um eine Referenzspannung VREFA zu erzeugen und eine Verstärkung davon kann als ungefähr 1,2/1,08 berechnet werden. In diesem Beispiel kann die Referenzspannung VREFA so eingestellt werden, dass sie ungefähr gleich ist wie die Referenzspannung VREF, sodass die Referenzspannung VREF aufrecht erhalten wird, sogar wenn die externen Spannungen VEXT und/oder VPPE reduziert werden.

**[0053]** [Fig. 2](#) ist ein Graph zum Beschreiben eines Arbeitsablaufes des Referenzspannungsgenerators **100** aus [Fig. 1](#).

**[0054]** Mit Bezug auf [Fig. 2](#) werden der Pegel der Clamp-Spannung VREFA<sub>PRE</sub> und der Pegel der Referenzspannung VREFA, die entsprechend dem Pegel der Versorgungsspannung VEXT erzeugt werden, gezeigt. Die Clamp-Spannung VREFA<sub>PRE</sub> wird fast gleich zu der ersten Versorgungsspannung VEXT zusammen mit der Anhebung der ersten Versorgungsspannung VEXT erzeugt und wird dann bei ungefähr 1,08 V geklemmt. Die Referenzspannung VREFA wird so erzeugt, dass sie einen Spannungspegel von 1,2/1,08, wie unten, aufweist, das eine Produkt aus der Clamp-Spannung VREFA<sub>PRE</sub> und der Verstärkung des Pegelverstärkers **120**, ist.

$$VREFA = VREFA_{PRE} \cdot \frac{1,2}{1,08} \quad (3)$$

**[0055]** [Fig. 3](#) ist ein Diagramm zum Beschreiben eines Referenzspannungsgenerators **300** gemäß einer zweiten beispielhaften Ausführungsform.

**[0056]** Mit Bezug auf [Fig. 3](#) wird der Referenzspannungsgenerator **300** von der zweiten Versorgungsspannung VPPE betrieben und empfängt eine zweite Spannung VPERI, um eine Referenzspannung VREFA zu erzeugen. Die zweite Versorgungsspannung VPPE kann so eingestellt sein, dass sie einen höheren Pegel aufweist als die erste externe Versorgungsspannung VEXT, die eine externe Versorgungsspannung ist, wie oben mit Bezug auf [Fig. 1](#) beschrieben. Zum Beispiel kann die zweite Versorgungsspannung VPPE auf ungefähr 1,6 V eingestellt sein, wenn die

erste externe Versorgungsspannung VEXT ungefähr 1,2 V beträgt.

**[0057]** Der Referenzspannungsgenerator **300** kann in einer Halbleiterspeichervorrichtung umfasst sein, zum Beispiel einem DRAM. Der DRAM kann etwa einen Kernblock und periphere Schaltkreisblöcke umfassen. Der Kernblock bezieht sich auf einen Block, der eine DRAM-Zellenanordnung umfasst, und die peripheren Schaltkreisblöcke beziehen sich auf die außer dem Kernblock verbleibenden Blöcke. Die zweite Spannung VPERI kann eine von den Spannungen sein, die in den peripheren Schaltkreisblöcken des DRAM verwendet werden. Die zweite Spannung VPERI kann so eingestellt sein, dass sie zum Beispiel ungefähr 1,8 V beträgt. In einer Ausführungsform wird die zweite Spannung VPERI, basierend auf einer ersten externen Versorgungsspannung VEXT, eingestellt.

**[0058]** Der Referenzspannungsgenerator **300** kann eine Vergleichseinheit **322**, eine Schalteinheit **324** und einen Pegelregelschaltkreis oder eine Steuereinheit **325** umfassen. Die Vergleichseinheit **322** wird von der zweiten Versorgungsspannung VPPE betrieben und umfasst einen Schaltkreis, beispielsweise einen Komparator, der konfiguriert ist, um die zweite Spannung VPERI mit einer Spannung eines ersten Knotens NE zu vergleichen, um eine Spannung eines zweiten Knotens NF auszugeben. Die Vergleichseinheit **322** kann einen Logic-Low-Pegel an den zweiten Knoten NF ausgeben, wenn die Spannung des ersten Knotens niedriger ist als die zweite Spannung VPERI. Die Vergleichseinheit **322** kann einen Logic-High-Pegel an den zweiten Knoten NF ausgeben, wenn die Spannung des ersten Knotens NE höher ist als die zweite Spannung VPERI. Der zweite Knoten NF kann mit der Schalteinheit **324** verbunden sein.

**[0059]** Die Schalteinheit **324** kann ein Schaltkreis sein, der zum Beispiel einen PMOS-Transistor umfasst, der von der zweiten Versorgungsspannung VPPE betrieben wird und der über sein Gate mit dem zweiten Knoten NF verknüpft ist. In dem PMOS-Transistor ist die zweite Versorgungsspannung VPPE mit einer Quelle verbunden, der zweite Knoten NF ist mit einem Gate verbunden und ein Drain gibt eine Referenzspannung VREFA aus. Bezuglich der Schalteinheit **324** kann der PMOS-Transistor als Antwort auf die Spannung des zweiten Knotens NF, die einem Logic-Low-Pegel entspricht, eingeschaltet werden. Die zweite Versorgungsspannung VPPE wird durch den eingeschalteten PMOS-Transistor bereitgestellt, um somit den Pegel der Referenzspannung VREFA zu erhöhen. Bezuglich der Schalteinheit **324** kann der PMOS-Transistor als Antwort auf die Spannung des zweiten Knotens NF, die einem Logic-High-Pegel entspricht, ausgeschaltet werden. Der ausgeschaltete PMOS-Transistor erhöht nicht den Pegel der Referenzspannung VREFA, da er die Versor-

gung der zweiten Versorgungsspannung VPPE unterbricht.

**[0060]** Zwischen die Referenzspannung VREFA und die Erdungsspannung VSS kann der Pegelregelschaltkreis **325** geschaltet sein, in dem ein erster Widerstand **326** und ein zweiter Widerstand **328** in Serie verbunden sein können. Ein Verbindungsknoten zwischen dem ersten Widerstand **326** und dem zweiten Widerstand **328** ist der erste Knoten NE. Aufgrund von Arbeitsabläufen der Vergleichseinheit **322** und der Schalteinheit **324** wird die Spannung des ersten Knotens NE fast gleich zu der zweiten Spannung VPERI. Daher kann die Referenzspannung VREFA durch einen Widerstand R3 des ersten Widerstandes **326** und einen Widerstand R4 des zweiten Widerstandes **328** wie unten bestimmt werden.

$$VREFA = VPERI \left( \frac{R3+R4}{R4} \right) \quad (4)$$

**[0061]** Dementsprechend kann der Pegel der Referenzspannung VREFA durch Anpassen des Pegels der zweiten Spannung VPERI, des Widerstandes R3 des ersten Widerstandes **326** und des Widerstandes R2 des zweiten Widerstandes **328** eingestellt werden. Die Referenzspannung VREFA kann so erzeugt werden, dass sie zum Beispiel ungefähr 1,2 V beträgt, wenn die zweite Referenzspannung VPERI beispielsweise ungefähr 1,08 V beträgt.

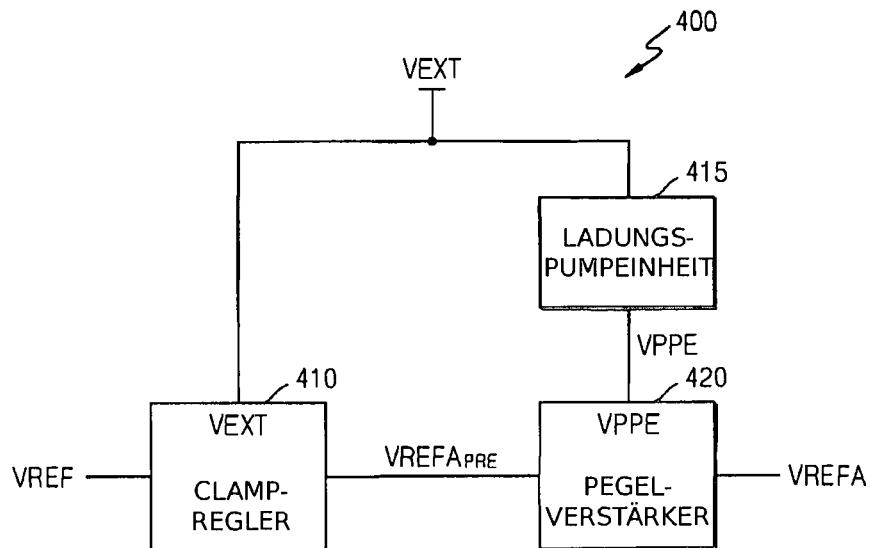

**[0062]** [Fig. 4](#) ist ein Diagramm zum Beschreiben eines Referenzspannungsgenerators **400** gemäß einer dritten Ausführungsform.

**[0063]** Mit Bezug auf [Fig. 4](#) kann der Referenzspannungsgenerator **400** einen Clamp-Regler **410**, eine Ladungspumpeinheit **415** und einen Pegelverstärker **420** umfassen. Der Referenzspannungsgenerator **400** wird von der ersten Versorgungsspannung VEXT betrieben, die eine externe Versorgungsspannung ist, und empfängt die erste Spannung VREF, um eine Clamp-Spannung VREFA<sub>PRE</sub> und die Referenzspannung VREFA zu erzeugen.

**[0064]** Der Clamp-Regler **410** kann im Wesentlichen gleich strukturiert sein wie der Clamp-Regler **110**, der mit Bezug auf [Fig. 1](#) beschrieben ist. Um eine sich wiederholende Beschreibung zu vermeiden, wird eine detaillierte Beschreibung des Clamp-Reglers **410** nicht bereitgestellt. Der Clamp-Regler **410** wird von der ersten Versorgungsspannung VEXT betrieben, beispielsweise ungefähr 1,2 V, und empfängt die erste Spannung VREF von beispielsweise ungefähr 0,75 V, um die Clamp-Spannung VREFA<sub>PRE</sub> von beispielsweise 1,08 V zu erzeugen.

**[0065]** Die Ladungspumpeinheit **415** empfängt die erste Versorgungsspannung VEXT und gibt die zweite Versorgungsspannung VPPE eines höheren Pegels als dem der ersten Versorgungsspannung

VEXT durch einen Ladungspumpvorgang aus. Wenn die erste Versorgungsspannung VEXT ungefähr 1,2 V beträgt, kann die zweite Versorgungsspannung VPPE so eingestellt werden, dass sie zum Beispiel ungefähr 1,6 V beträgt. Die Ladungspumpeinheit **415** kann einen Oszillator und einen Pumpkondensator umfassen. Der Oszillator erzeugt ein oszillierendes Signal und der Pumpkondensator erzeugt eine Pumpspannung aus der ersten Versorgungsspannung VEXT als Antwort auf das oszillierende Signal. Die Ladungspumpeinheit **415** kann eine Pumpsteureinheit umfassen, die den Ladungspumpvorgang stoppt, wenn die Pumpspannung ein vorbestimmtes Spannungspegel erreicht. Die Pumpspannung kann als die zweite Versorgungsspannung VPPE ausgegeben werden.

**[0066]** Der Pegelverstärker **420** wird von der zweiten Versorgungsspannung VPPE betrieben und empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, die von dem Clamp-Regler **410** erzeugt wird, um die Referenzspannung VREFA zu erzeugen. Der Pegelverstärker **420** kann im Wesentlichen gleich strukturiert sein wie der Pegelverstärker **120**, der mit Bezugnahme auf [Fig. 1](#) beschrieben ist. Um sich wiederholende Beschreibung zu vermeiden, wird eine detaillierte Beschreibung des Pegelverstärkers **420** nicht bereitgestellt. Der Pegelverstärker **420** wird von der zweiten Versorgungsspannung VPEE betrieben, die einen Pegel von beispielsweise ungefähr 1,6 V aufweist, und erzeugt in einer Ausführungsform die Referenzspannung VREFA von ungefähr 1,2 V, wenn die Clamp-Spannung VREFA<sub>PRE</sub> ungefähr 1,08 V beträgt. Der Pegelverstärker **420** empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, um die Referenzspannung VREFA zu erzeugen, und eine Verstärkung davon kann als ungefähr 1,2/1,08 berechnet werden.

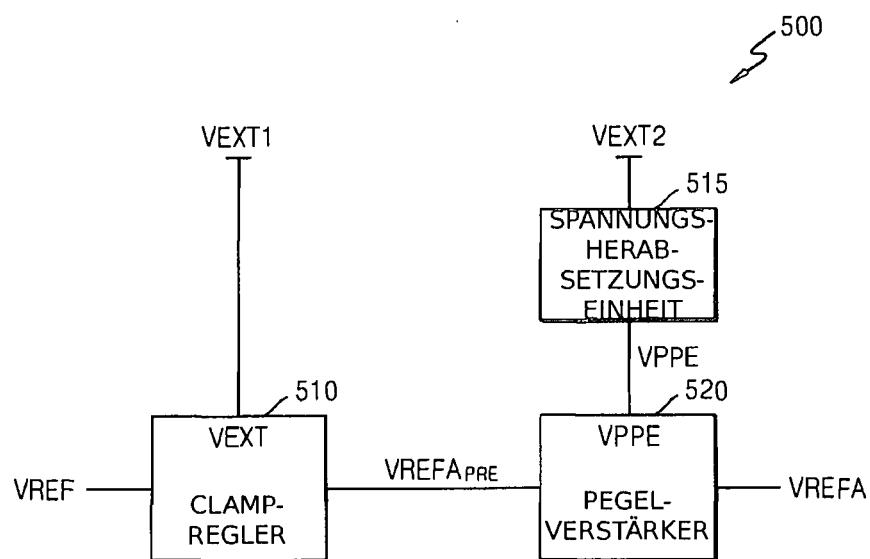

**[0067]** [Fig. 5](#) ist ein Diagramm zum Beschreiben eines Referenzspannungsgenerators **500** gemäß einer vierten Ausführungsform.

**[0068]** Mit Bezug auf [Fig. 5](#) umfasst der Referenzspannungsgenerator **500** einen Clamp-Regler **510**, eine Spannungsherabsetzungseinheit **515** und einen Pegelverstärker **520**. Der Referenzspannungsgenerator **500** wird von einer ersten externen Versorgungsspannung VEXT1 und einer zweiten externen Versorgungsspannung VEXT2 betrieben und empfängt die erste Spannung VREF, um die Clamp-Spannung VREFA<sub>PRE</sub> und die Referenzspannung VREFA zu erzeugen. Der Pegel der ersten externen Versorgungsspannung VEXT1 und der Pegel der zweiten externen Versorgungsspannung VEXT2 können sich voneinander unterscheiden. Die zweite externe Versorgungsspannung VEXT2 kann so eingestellt sein, dass sie einen Pegel aufweist, das höher ist, als das der ersten externen Versorgungsspannung VEXT1.

**[0069]** Der Clamp-Regler **510** kann im Wesentlichen gleich strukturiert sein wie der Clamp-Regler **110**, der mit Bezugnahme auf [Fig. 1](#) beschrieben ist. Um sich wiederholende Beschreibung zu vermeiden wird keine detaillierte Beschreibung des Clamp-Reglers **510** bereitgestellt. Der Clamp-Regler **510** wird von einer ersten externen Versorgungsspannung VEXT1 von zum Beispiel ungefähr 1,2 V betrieben und empfängt die erste Spannung VREF von zum Beispiel ungefähr 0,75 V, um die Clamp-Spannung VREFA<sub>PRE</sub> von zum Beispiel ungefähr 1,08 V zu erzeugen.

**[0070]** Die Spannungsherabsetzungseinheit **515** empfängt die zweite externe Versorgungsspannung VEXT2 und setzt die Spannung herab, um eine zweite Versorgungsspannung VPPE auszugeben. Wenn die zweite externe Versorgungsspannung VEXT2 zum Beispiel ungefähr 2,5 V beträgt, kann die zweite Versorgungsspannung VPPE so eingestellt sein, dass sie zum Beispiel 1,6 V beträgt. Die Spannungsherabsetzungseinheit **515** kann eine Vielzahl von Diodenelementen umfassen, die in Serie zwischen die zweite externe Versorgungsspannung VEXT2 und die zweite Versorgungsspannung VPPE geschaltet sind. Das Diodenelement verursacht eine Spannungsherabsetzung in der Durchleitung, die einem PN-Kontakt-Vorwärtsspannungsabfall Vf entspricht. Zum Beispiel kann für n Diodenelemente die zweite Versorgungsspannung als VEXT2 – n·Vf bestimmt werden.

**[0071]** Die Spannungsherabsetzungseinheit **515** kann eine Vielzahl von MOS-Transistoren umfassen, die in Serie zwischen die zweite externe Versorgungsspannung VEXT2 und die zweite Versorgungsspannung VPPE geschaltet sind. In jedem der MOS-Transistoren können ein Gate und ein Drain davon zusammengeschaltet sein. Jeder von den MOS-Transistoren arbeitet in einem Diodenmodus und verursacht einen Spannungsabfall in der Durchleitung, der einer Schwellenspannung VTN entspricht. Zum Beispiel kann für MOS-Transistoren die zweite Versorgungsspannung VPPE als VEXT2 – n·VTN bestimmt werden.

**[0072]** Der Pegelverstärker **520** wird von der zweiten Versorgungsspannung VPPE betrieben und empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, die in dem Clamp-Regler **510** erzeugt wird, um die Referenzspannung VREFA zu erzeugen. Der Pegelverstärker **520** kann im Wesentlichen gleich strukturiert sein wie der Pegelverstärker **120**, der unter Bezugnahme auf [Fig. 1](#) beschrieben ist. Um sich wiederholende Beschreibung zu vermeiden, wird eine detaillierte Beschreibung des Pegelverstärkers **520** nicht bereitgestellt. In einer Ausführungsform wird der Pegelverstärker **520** von der zweiten Versorgungsspannung von ungefähr 1,6 V betrieben und kann die Referenzspannung VREFA von ungefähr 1,2 V für die Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V erzeugen.

Der Pegelverstärker **520** empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, um die Referenzspannung VREFA zu erzeugen und eine Verstärkung davon kann als ungefähr 1,2/1,08 berechnet werden.

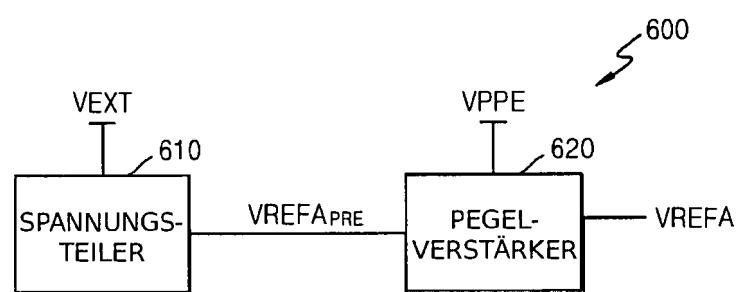

**[0073]** [Fig. 6](#) ist ein Diagramm zum Beschreiben eines Referenzspannungsgenerators **600** gemäß einer fünften Ausführungsform.

**[0074]** Mit Bezug auf [Fig. 6](#) umfasst der Referenzspannungsgenerator **600** einen Spannungsteiler **610** und einen Pegelverstärker **620**. Der Spannungsteiler **610** teilt eine Spannung zwischen der ersten Versorgungsspannung VEXT und der dritten Versorgungsspannung VSS, um die Clamp-Spannung VREFA<sub>PRE</sub> zu erzeugen. Der Spannungsteiler **610** kann einen ersten Widerstand umfassen, der zwischen die erste Versorgungsspannung VEXT und die Clamp-Spannung VREFA<sub>PRE</sub> geschaltet ist, und einen zweiten Widerstand, der zwischen die Clamp-Spannung VREFA<sub>PRE</sub> und die dritte Versorgungsspannung VSS geschaltet ist. Durch Anpassen der Widerstände des ersten Widerstandes und des zweiten Widerstandes kann der Pegel der Clamp-Spannung VREFA<sub>PRE</sub> eingestellt werden. Die erste Versorgungsspannung VEXT kann zum Beispiel ungefähr 1,2 V betragen und die dritte Versorgungsspannung VSS kann eine Erdungsspannung sein. Die Widerstände des ersten Widerstandes und des zweiten Widerstandes können angepasst werden, um die Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V zu erzeugen.

**[0075]** Der Pegelverstärker **620** wird von der zweiten Versorgungsspannung VPPE betrieben, und empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, die von dem Spannungsteiler **610** erzeugt wird, um die Referenzspannung VREFA zu erzeugen. Der Pegelverstärker **620** kann im Wesentlichen gleich strukturiert sein wie der Pegelverstärker **120**, der mit Bezugnahme auf [Fig. 1](#) beschrieben ist. Um sich wiederholende Beschreibung zu vermeiden, wird eine detaillierte Beschreibung des Pegelverstärkers **420** nicht bereitgestellt. In einer Ausführungsform wird der Pegelverstärker **620** von der zweiten Versorgungsspannung VPPE von ungefähr 1,6 V betrieben und kann die Referenzspannung VREFA von ungefähr 1,2 V für die Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V erzeugen. Der Pegelverstärker **620** empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, um die Referenzspannung VREFA zu erzeugen, und eine Verstärkung davon kann als ungefähr 1,2/1,08 berechnet werden.

**[0076]** Die Referenzspannung VREFA, die von den Referenzspannungsgeneratoren gemäß verschiedenen Ausführungsformen erzeugt wird, kann als eine Spannung dienen, die als ein Kriterium zum Erzeugen interner Versorgungsspannungen, die in dem DRAM verwendet werden, agiert.

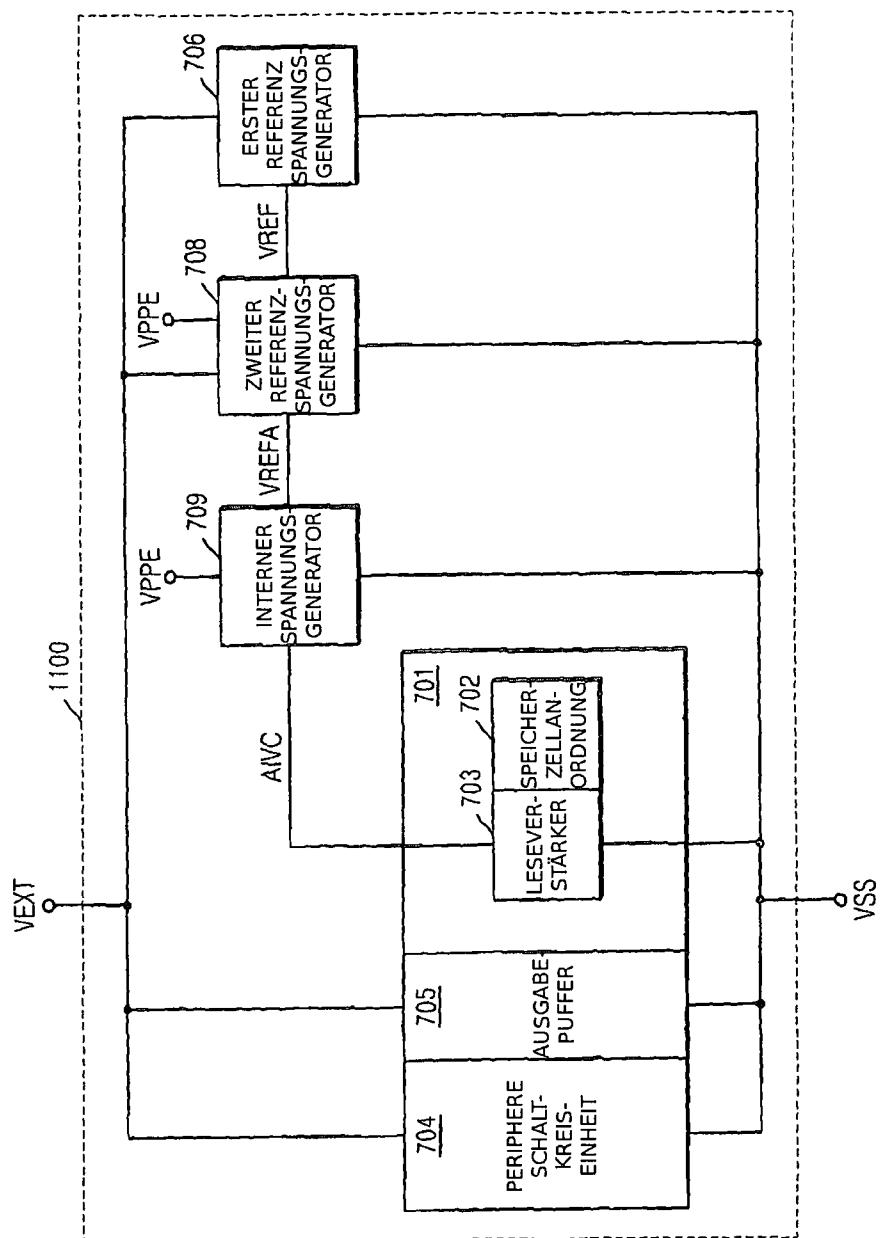

[0077] [Fig. 7](#) ist ein Diagramm zum Beschreiben eines Beispiels eines DRAM **700**, der einen Referenzspannungsgenerator gemäß verschiedener Ausführungsformen umfasst.

[0078] Mit Bezug auf [Fig. 7](#) kann der DRAM **700** einen Kernblock **701**, der eine Speicherzellanordnung **702** und einen Leseverstärker **703** umfasst, eine periphere Schaltkreiseinheit **704** und eine Ausgabepuffereinheit **705** umfassen. Die Speicherzellanordnung **702** kann eine Vielzahl an Word-Leitungen umfassen, eine Vielzahl an Bitleitungen, die sich mit der Vielzahl an Word-Leitungen auf der Vielzahl an Word-Leitungen kreuzen, eine Vielzahl an Speicherzellen, die in der Nähe von Kreuzungen zwischen den Word-Leitungen und den Bitleitungen angeordnet sind, einen Zeilendekoder, der in der Lage ist, eine vorbestimmte Word-Leitung aus der Vielzahl der Word-Leitungen auszuwählen, und einen Spaltendekoder, der in der Lage ist, eine vorbestimmte Bitleitung aus der Vielzahl der Bitleitungen auszuwählen. Der Leseverstärker **703** kann Zelldaten, die aus der Vielzahl von Bitleitungen ausgelesen werden, leseverstärken. Die periphere Schaltkreiseinheit **704** kann einen Adresspuffer, eine Dateneingabepuffer und Steuerschaltkreise umfassen. Die Ausgabepuffereinheit **705** wird von der externen Versorgungsspannung VEXT betrieben und liest die Leseverstärker verstärkten Speicherzeldaten aus.

[0079] Der DRAM **700** kann einen ersten Referenzspannungsgenerator **706**, einen ersten internen Spannungsgenerator **707**, eine zweiten Referenzspannungsgenerator **708** und einen zweiten internen Spannungsgenerator **709** umfassen. Der erste Referenzspannungsgenerator **706** empfängt die externe Versorgungsspannung VEXT, um die erste Referenzspannung VREF zu erzeugen. Der erste interne Spannungsgenerator **707** wird von der externen Versorgungsspannung VEXT betrieben und empfängt die erste Referenzspannung VREF, um eine erste interne Versorgungsspannung IVC zu erzeugen. Die erste interne Versorgungsspannung IVC kann als eine Stromquelle zum Ansteuern der peripheren Schaltkreiseinheit **704** verwendet werden.

[0080] Der zweite Referenzspannungsgenerator **708** wird von der externen Versorgungsspannung VEXT und der zweiten Versorgungsspannung VPPE betrieben und empfängt die erste Referenzspannung VREF, um die zweite Referenzspannung VREFA zu erzeugen. Wie der Referenzspannungsgenerator **100**, der mit Bezugnahme auf [Fig. 1](#) beschrieben ist, kann der zweite Referenzspannungsgenerator **708** den Clamp-Regler **110** und den Pegelverstärker **120** umfassen. Der Clamp-Regler **110** wird von der externen Versorgungsspannung VEXT betrieben und empfängt die erste Referenzspannung VREF, um die Clamp-Spannung VREFA<sub>PRE</sub> zu erzeugen. Der Pegelverstärker **120** wird von der zweiten Versor-

gungsspannung VPPE, die höher ist als eine externe Versorgungsspannung VEXT, betrieben und empfängt die Clamp-Spannung VREFA<sub>PRE</sub>, um die zweite Referenzspannung VREFA zu erzeugen. Der zweite Referenzspannungsgenerator **708** kann gemäß einer der Ausführungsformen des Referenzspannungsgenerators, der mit Bezugnahme auf [Fig. 3](#) bis [Fig. 6](#) beschrieben ist, implementiert sein.

[0081] Der zweite interne Spannungsgenerator **709** wird von der zweiten Versorgungsspannung VPPE betrieben und empfängt die zweite Referenzspannung VREFA, um eine zweite interne Versorgungsspannung AIVC zu erzeugen. Die zweite interne Versorgungsspannung AIVC kann als eine Stromquelle zum Ansteuern des Kernblockes **701** verwendet werden.

[0082] [Fig. 8](#) ist ein Schaltkreisdiagramm zum Beschreiben des ersten Referenzspannungsgenerators **706** aus [Fig. 7](#) gemäß einer beispielhaften Ausführungsform.

[0083] Mit Bezug auf [Fig. 8](#) kann der erste Referenzspannungsgenerator **706** die erste Referenzspannung VREF durch Teilen der externen Versorgungsspannung VEXT erzeugen. Der erste Referenzspannungsgenerator **706** kann eine Biaseinheit **810**, eine Steuereinheit **820** und eine Betriebseinheit **830** umfassen. Die Biaseinheit **810** kann ein Schaltkreis sein, der erste und zweite Widerstände **801** und **802**, die in Serie zwischen die externe Versorgungsspannung VEXT und die Erdungsspannung VSS geschaltet sind, und erste bis dritte n-Kanal-Metallocidhalbleiter(NMOS)-Transistoren **803** bis **805**, umfassen. Eine Erstknotenspannung VREF\_F zwischen dem ersten Widerstand **801** und dem zweiten Widerstand **802** kann an Gate der ersten und zweiten NMOS-Transistoren **803** und **804** angeschlossen sein. Das Gate des dritten NMOS-Transistors **805** kann an die externe Versorgungsspannung VEXT angeschlossen sein. Die externe Versorgungsspannung VEXT wird von dem ersten Widerstand **801**, dem zweiten Widerstand **802** und den ersten bis dritten NMOS-Transistoren **803** bis **805** geteilt, sodass die geteilte Spannung durch die Erstknotenspannung VREF\_F angezeigt werden kann.

[0084] Die Steuereinheit **820** kann die Erstknotenspannung VREF\_F stuern, bis die externe Versorgungsspannung VEXT stabilisiert ist. Die Steuereinheit **820** kann einen PMOS-Transistor **806**, der zwischen die Erstknotenspannung VREF\_F und die Erdungsspannung VSS geschaltet ist, umfassen. Ein Gate des PMOS-Transistors **806** kann an einem zweiten Knoten ND\_A, zwischen dem ersten Widerstand **802** und dem ersten NMOS-Transistor **803**, angeschlossen sein. Der PMOS-Transistor **806** wird in einem anfänglichen Zustand eingeschaltet, bei dem die externe Versorgungsspannung VEXT angelegt

wird, wodurch er die Erstknotenspannung VREF\_F gegenüber der Erdungsspannung VSS stabilisiert. Danach kann der PMOS-Transistor **806** abgeschaltet werden, wenn die externe Versorgungsspannung VEXT konstant mit zum Beispiel ungefähr 1,2 V anliegt.

**[0085]** Die Betriebseinheit **830** kann die erste Referenzspannung VREF als Antwort auf die Erstknotenspannung VREF\_F erzeugen. Die Betriebseinheit **830** kann einen dritten Widerstand **807** und vierte und fünfte NMOS-Transistoren **808** und **809** umfassen, die in Serie zwischen die Erstknotenspannung VREF\_F und die Erdungsspannung VSS geschaltet sind. Ein Gate des vierten NMOS-Transistors **808** ist mit der Erstknotenspannung VREF\_F verbunden und ein Gate des fünften NMOS-Transistors **809** kann mit der externen Versorgungsspannung VEXT verbunden sein. Eine Spannung eines Verbindungsknotens zwischen dem dritten Widerstand **807** und dem vierten NMOS-Transistor **808** kann als die erste Referenzspannung VREF erzeugt werden.

**[0086]** Sobald die externe Versorgungsspannung VEXT zunimmt, nimmt die Erstknotenspannung VREF\_F zu, und die erste Referenzspannung VREF nimmt auch zu. Wenn die Erstknotenspannung VREF\_F zunimmt, kann der vierte NMOS-Transistor **808** eingeschaltet werden, wodurch er die erste Referenzspannung VREF daran hindert zuzunehmen.

**[0087]** Sobald die externe Versorgungsspannung VEXT abfällt, nimmt die Erstknotenspannung VREF\_F ab, und die erste Referenzspannung VREF nimmt auch ab. Wenn die Erstknotenspannung VREF\_F abnimmt, kann der vierte NMOS-Transistor **808** ausgeschaltet werden, wodurch er die erste Referenzspannung am Abfallen hindert.

**[0088]** Daher kann der erste Referenzspannungsgenerator **706** die erste Referenzspannung VREF unabhängig von Veränderungen der externen Versorgungsspannung VEXT stabil erzeugen. Der erste Referenzspannungsgenerator **706** kann die erste Referenzspannung VREF von zum Beispiel ungefähr 0,75 V für die externe Versorgungsspannung VEXT von ungefähr 1,2 V erzeugen. Die erste Referenzspannung VREF kann als die erste Spannung VREF des Referenzspannungsgenerators gemäß verschiedenen Ausführungsformen, die mit Bezugnahme auf [Fig. 1](#) und [Fig. 3](#) bis [Fig. 5](#) beschrieben sind, bereitgestellt werden.

**[0089]** [Fig. 9](#) ist ein Schaltkreisdiagramm zum Beschreiben des ersten internen Spannungsgenerators **707** nach [Fig. 7](#) gemäß einer beispielhaften Ausführungsform.

**[0090]** Mit Bezug auf [Fig. 9](#) wird der erste interne Spannungsgenerator **707** von der externen Versor-

gungsspannung betrieben und empfängt die erste Referenzspannung VREF, um die erste interne Versorgungsspannung IVC zu erzeugen. Der erste interne Spannungsgenerator **707** kann Schaltkreise, die eine Vergleichseinheit **902** bilden, eine Schalteinheit **904** und eine Pegelsteuereinheit **905** umfassen. Die Vergleichseinheit **902** wird von der externen Versorgungsspannung VEXT betrieben, vergleicht die erste Referenzspannung VREF mit einer Spannung des ersten Knotens ND\_B, und gibt ein Vergleichsergebnis an einen zweiten Knoten ND\_C aus. Die externe Versorgungsspannung VEXT kann zum Beispiel ungefähr 1,2 V betragen und die erste Referenzspannung VREF kann zum Beispiel ungefähr 0,75 V betragen. Die Vergleichseinheit **902** kann einen Logic-Low-Pegel an den zweiten Knoten ND\_C ausgeben, wenn die Spannung des ersten Knotens ND\_B niedriger ist als die erste Referenzspannung VREF. Die Vergleichseinheit **902** kann einen Logic-High-Pegel an den zweiten Knoten ND\_C ausgeben, wenn die Spannung des ersten Knotens ND\_B höher ist als die erste Referenzspannung VREF. Der zweite Knoten ND\_C kann mit der Schalteinheit **904** verbunden sein.

**[0091]** In einer Ausführungsform kann die Schalteinheit **904** ein PMOS-Transistor sein, der von einer externen Versorgungsspannung betrieben wird, und der über sein Gate mit dem zweiten Knoten ND\_C verknüpft ist. In dem PMOS-Transistor ist die externe Versorgungsspannung VEXT mit einer Quelle verbunden, der zweite Knoten ND\_C ist mit einem Gate verbunden und ein Drain gibt die interne Versorgungsspannung IVC aus. Die Schalteinheit **904** kann den PMOS-Transistor als Antwort auf eine Spannung des zweiten Knotens ND\_C, die einem Logic-Low-Pegel entspricht, anschalten. Die externe Versorgungsspannung VEXT wird durch den angeschalteten PMOS-Transistor bereitgestellt, wodurch sie den Pegel der internen Versorgungsspannung IVC anhebt. Bezuglich der Schalteinheit **904** kann der PMOS-Transistor als Antwort auf die Spannung des zweiten Knotens ND\_C, die einem Logic-High-Pegel entspricht, ausgeschaltet werden. Der ausgeschaltete PMOS-Transistor hebt der Pegel der internen Versorgungsspannung IVC nicht an, da er die Versorgung der externen Versorgungsspannung VEXT unterbricht.

**[0092]** Zwischen die interne Versorgungsspannung IVC und die Erdungsspannung VSS kann die Pegelsteuereinheit **905**, in der ein erster Widerstand **906** und ein zweiter Widerstand **908** in Serie verbunden sein können, geschaltet sein. Ein Verbindungsknoten zwischen dem ersten Widerstand **906** und dem zweiten Widerstand **908** ist der erste Knoten ND\_B. Aufgrund von Arbeitsabläufen der Vergleichseinheit **902** und der Schalteinheit **904** wird die Spannung des ersten Knotens ND\_B fast gleich wie die erste Referenzspannung VREF. Daher kann die interne Versorgungsspannung IVC durch einen Widerstand des

ersten Widerstandes **906** und einen Widerstand des zweiten Widerstandes **908** bestimmt werden.

**[0093]** [Fig. 10A](#) ist ein Schaltkreisdiagramm zum Beschreiben des zweiten internen Spannungsgenerators **709** nach [Fig. 7](#) und des Leseverstärkers **703** des Kernblocks **701** gemäß einer beispielhaften Ausführungsform.

**[0094]** Mit Bezug auf [Fig. 10A](#) wird der zweite interne Spannungsgenerator **709** von der zweiten Versorgungsspannung VPPE betrieben, und empfängt die zweite Referenzspannung VREFA, die von dem zweiten Referenzspannungsgenerator **708** erzeugt wird, um die zweite interne Versorgungsspannung AIVC zu erzeugen. Der zweite interne Spannungsgenerator **709** kann eine Vergleichseinheit **1002** und eine Betriebseinheit **1004** umfassen.

**[0095]** Die Vergleichseinheit **1002** vergleicht die zweite Referenzspannung VREFA mit der zweiten internen Versorgungsspannung AIVC und gibt ein Vergleichsergebnis aus. Die Vergleichseinheit **1002** kann einen Logic-Low-Pegel ausgeben, wenn die zweite interne Versorgungsspannung AIVC niedriger ist als die zweite Referenzspannung VREFA. Die Vergleichseinheit **1002** kann einen Logic-High-Pegel ausgeben, wenn die zweite interne Versorgungsspannung AIVC höher ist als die zweite Referenzspannung VREFA. Eine Ausgabe der Vergleichseinheit **1002** kann mit der Betriebseinheit **1004** verbunden sein.

**[0096]** Die Betriebseinheit **1004** wird von der zweiten Versorgungsspannung VPPE betrieben, und erzeugt die zweite interne Versorgungsspannung AIVC als Antwort auf eine Ausgabe der Vergleichseinheit **1002**. Die Betriebseinheit **1004** kann zum Beispiel ein PMOS-Transistor sein, der über sein Gate mit der Ausgabe der Vergleichseinheit **1002** verknüpft ist. In dem PMOS-Transistor ist die zweite Versorgungsspannung VPPE mit einer Quelle verbunden, die Ausgabe der Vergleichseinheit **1002** ist mit einem Gate verbunden und eine Drain gibt die zweite interne Versorgungsspannung AIVC aus. Bezuglich der Betriebseinheit **1004** kann der PMOS-Transistor als Antwort auf die Logic-Low-Pegel-Ausgabe von der Vergleichseinheit **1002** eingeschaltet werden. Die zweite Versorgungsspannung VPPE wird durch den eingeschalteten PMOS-Transistor bereitgestellt, wodurch sie den Pegel der zweiten internen Versorgungsspannung AIVC anhebt. Für die Betriebseinheit **1004** wird der PMOS-Transistor als Antwort auf die Logic-High-Pegel-Ausgabe der Vergleichseinheit **1002** ausgeschaltet. Der ausgeschaltete PMOS-Transistor hebt den Pegel der zweiten internen Versorgungsspannung AIVC nicht an, da er die Versorgung mit der zweiten Versorgungsspannung VPPE unterbricht.

**[0097]** Daher kann der zweite interne Spannungsgenerator **709** die zweite interne Versorgungsspannung AIVC eines Pegels, der fast gleich ist wie das der zweiten Referenzspannung VREFA, erzeugen. In einer Ausführungsform kann die zweite interne Versorgungsspannung AIVC bei ungefähr 1,2 V erzeugt werden, wenn die zweite Stromspannung VPPE ungefähr 1,6 V beträgt und die zweite Referenzspannung VREFA, die von dem zweiten Referenzspannungsgenerator **708** erzeugt wird, ungefähr 1,2 V beträgt.

**[0098]** Der Leseverstärker **703** kann eine Abtastungseinheit **1030** und eine Ausgleichseinheit **1040** umfassen. Die Abtastungseinheit **1030** kann Daten auf einer Bitleitung BL und einer ergänzenden Bitleitung BLB der Speicherzellanordnung **702** leseverstärken. Die Abtasteinheit **1030** kann eine erste Abtasteinheit PSA und eine zweite Abtasteinheit NSA umfassen, die zwischen die Bitleitung BL und die ergänzende Bitleitung BLB geschaltet sind. Die erste Abtasteinheit PSA kann PMOS-Transistoren umfassen, deren Gate zwischen der Bitleitung BL und der ergänzenden Bitleitung BLB zwischengeschaltet sind. Die zweite Abtasteinheit NSA kann NMOS-Transistoren umfassen, deren Gate zwischen der Bitleitung BL und der ergänzenden Bitleitung BLB zwischengeschaltet sind. Die Ausgleichseinheit **703** kann NMOS-Transistoren umfassen, die zwischen die Bitleitung BL und die ergänzende Bitleitung BLB geschaltet sind, und die auf ein Bitleitungs-ausgleichendes Signal PEQI antworten.

**[0099]** Die erste Abtasteinheit PSA wird von der zweiten internen Versorgungsspannung AIVC betrieben, die von dem zweiten internen Spannungsgenerator **709** erzeugt wird und die zweite Abtasteinheit NSA wird von der Erdungsspannung VSS betrieben. Die zweite interne Versorgungsspannung AIVC wird der ersten Abtasteinheit PSA durch eine erste Schalteinheit **1010** bereitgestellt, die auf eine erstes Aktivierungssignal LAPG anspricht und die Erdungsspannung VSS wird der zweiten Abtasteinheit NSA durch eine zweite Schalteinheit **1020** bereitgestellt, die auf ein zweites Aktivierungssignal LANG anspricht.

**[0100]** Die zweite interne Versorgungsspannung AIVC, die die Abtasteinheit **1030** ansteuert, kann ein wichtiges Element einer Zellwiederherstellungsoperation sein, wenn Daten in eine Speicherzelle MC, die mit der Bitleitung BL verbunden ist, geschrieben werden. Insbesondere, wie in [Fig. 10B](#) gezeigt, muss die zweite interne Versorgungsspannung AIVC einen bestimmten Spannungspiegel halten, wenn ein vorangegangener Logic-Pegel der Bitleitung BL und der ergänzenden Bitleitung BLB ungekehrt ist, und der umgekehrte Logic-Pegel in die Speicherzelle MC geschrieben wird. Sogar wenn der Pegel der externen Versorgungsspannung VEXT reduziert wird, um die Leistungsaufnahme des DRAM zu reduzieren, kann

die zweite interne Versorgungsspannung AIVC konstant auf einem Zielspannungspegel erzeugt werden.

**[0101]** Der zweite interne Spannungsgenerator **709** kann die zweite interne Versorgungsspannung AIVC erzeugen, die fast gleich ist wie die zweite Referenzspannung VREFA. In einer Ausführungsform kann der zweite Referenzspannungsgenerator **708** die Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V, die höher ist als die erste Referenzspannung VREF, sogar erzeugen, wenn die erste Referenzspannung VREF aufgrund des Herabsetzens der externen Versorgungsspannung VEXT auf ungefähr 1,2 V mit ungefähr 0,75 V erzeugt wird. Der Pegel der Clamp-Spannung VREFA<sub>PRE</sub> kann auf einen minimalen Spannungspegel eingestellt werden, der in einer erfolgreichen Zellwiederherstellungsoperation resultiert, wenn Daten in die Speicherzelle MC, die mit der Bitleitung BL des DRAM verbunden ist, geschrieben werden. Der zweite Referenzspannungsgenerator **708** kann die zweite Referenzspannung VREFA von ungefähr 1,2 V unter Verwendung der Clamp-Spannung VREFA<sub>PRE</sub> erzeugen. Daher kann die zweite interne Versorgungsspannung AIVC mit einem Spannungspegel von ungefähr 1,2 V erzeugt werden, was in einer erfolgreichen Zellwiederherstellungsoperation resultiert. Unabhängig vom Pegel der externen Versorgungsspannung VEXT kann die zweite interne Versorgungsspannung AIVC mit der Zielspannung (z. B. 1,2 V) in einer Situation, in der die Zellkapazität der Speicherzelle MC abnimmt, eine Auffrischungszeit sichern.

**[0102]** [Fig. 11](#) ist ein Diagramm zum Beschreiben eines anderen Beispiels eines DRAM **1000**, der einen Referenzspannungsgenerator gemäß verschiedener Ausführungsformen umfasst.

**[0103]** Mit Bezug auf [Fig. 11](#) kann der DRAM **1100** den Kernblock **701** umfassen, der die Speicherzellanordnung **702** und den Leseverstärker **703** umfasst, die periphere Schaltkreiseinheit **704**, die Ausgabepuffereinheit **705**, den ersten Referenzspannungsgenerator **706** und den zweiten Referenzspannungsgenerator **708**. Der DRAM **1100** kann einen einzelnen internen Spannungsgenerator **709** umfassen, der im Wesentlichen gleich strukturiert sein kann wie der zweite interne Spannungsgenerator **709** nach [Fig. 7](#). Allerdings umfasst der DRAM **1100**, anders als der DRAM **700** nach [Fig. 7](#), nicht den ersten internen Spannungsgenerator **707**, der die periphere Schaltkreiseinheit **704** ansteuert.

**[0104]** Um den Niedrigverbrauchsleistungscharakteristika des DRAM **1100** zu entsprechen kann die externe Versorgungsspannung VEXT auf z. B. 1,2 V oder weniger herabgesetzt werden. In diesem Fall können die periphere Schaltkreiseinheit **704** und die Ausgabepuffereinheit **705** so konfiguriert sein, dass sie mit der herabgesetzten externen Versorgungs-

spannung VEXT verbunden sind und sie können mit VEXT betrieben werden. Die periphere Schaltkreiseinheit **704** kann zum Beispiel einen Adresspuffer, eine Dateneingangspuffer und Steuerschaltkreise umfassen. Die Ausgabepuffereinheit **705** wird mit der externen Versorgungsspannung VEXT betrieben und liest die leseverstärkten Speicherzelldaten aus.

**[0105]** Der erste Referenzspannungsgenerator **706** empfängt die externe Versorgungsspannung VEXT, und erzeugt die erste Referenzspannung VREF. Der zweite Referenzspannungsgenerator **708** wird mit der externen Versorgungsspannung VEXT und der zweiten Versorgungsspannung VPPE betrieben, und empfängt die erste Referenzspannung VREF, um die zweite Referenzspannung VREFA zu erzeugen.

**[0106]** Wie der Referenzspannungsgenerator **100**, der mit Bezugnahme auf [Fig. 1](#) beschrieben ist, kann der zweite Referenzspannungsgenerator **708** den Clamp-Regler **110** und den Pegelverstärker **120** umfassen. Der Clamp-Regler **110** wird mit der externen Versorgungsspannung VEXT betrieben, und empfängt die erste Referenzspannung VREF, um die Clamp-Spannung VREFA<sub>PRE</sub> zu erzeugen. In einer Ausführungsform kann der zweite Referenzspannungsgenerator **708** die Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V, die höher ist als die erste Referenzspannung VREF, sogar erzeugen, wenn die erste Referenzspannung VREF aufgrund des Reduzierens der externen Versorgungsspannung VEXT auf 1,2 V oder weniger mit 0,75 V oder weniger, erzeugt wird. Der Pegel der Clamp-Spannung VREFA<sub>PRE</sub> kann auf einen minimalen Spannungspegel eingestellt werden, das in einer erfolgreichen Zellwiederherstellungsoperation resultiert, wenn Daten in die Speicherzelle MC, die mit der Bitleitung BL des DRAM verbunden ist, geschrieben werden. In einer Ausführungsform wird der Pegelverstärker **120** mit der zweiten Versorgungsspannung VPPE betrieben, die höher ist als die externe Versorgungsspannung VEXT, und erzeugt unter Verwendung der Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V die zweite Referenzspannung VREFA von ungefähr 1,2 V. Der zweite Referenzspannungsgenerator **708** kann zum Beispiel auch gemäß einer der Ausführungsformen des Referenzspannungsgenerators, der mit Bezugnahme auf [Fig. 3](#) bis [Fig. 6](#) beschrieben ist, implementiert sein.

**[0107]** Der interne Spannungsgenerator **709** wird mit der zweiten Versorgungsspannung VPPE betrieben, und empfängt die zweite Referenzspannung VREFA, um die zweite interne Versorgungsspannung AIVC zu erzeugen. Der interne Spannungsgenerator **709** kann die zweite interne Versorgungsspannung AIVC erzeugen, die gleich ist wie die zweite Referenzspannung VREFA. In einer Ausführungsform kann die zweite interne Versorgungsspannung bei ungefähr 1,2 V erzeugt werden, was ein Ziel-

spannungspiegel ist. Die zweite interne Versorgungsspannung AIVC kann als eine Stromquelle zum Betreiben des Kernblocks **701** verwendet werden. Die zweite interne Versorgungsspannung AIVC hat einen Ziellspannungspegel, das in einer erfolgreichen Zellwiederherstellungsoperation resultiert, wenn Daten in die Speicherzelle MC, die mit der Bitleitung BL verbunden ist, geschrieben werden. Die zweite interne Versorgungsspannung AIVC von ungefähr 1,2 V kann eine Auffrischungszeit der Speicherzelle MC, unabhängig vom Pegel der externen Versorgungsspannung VEXT, sichern.

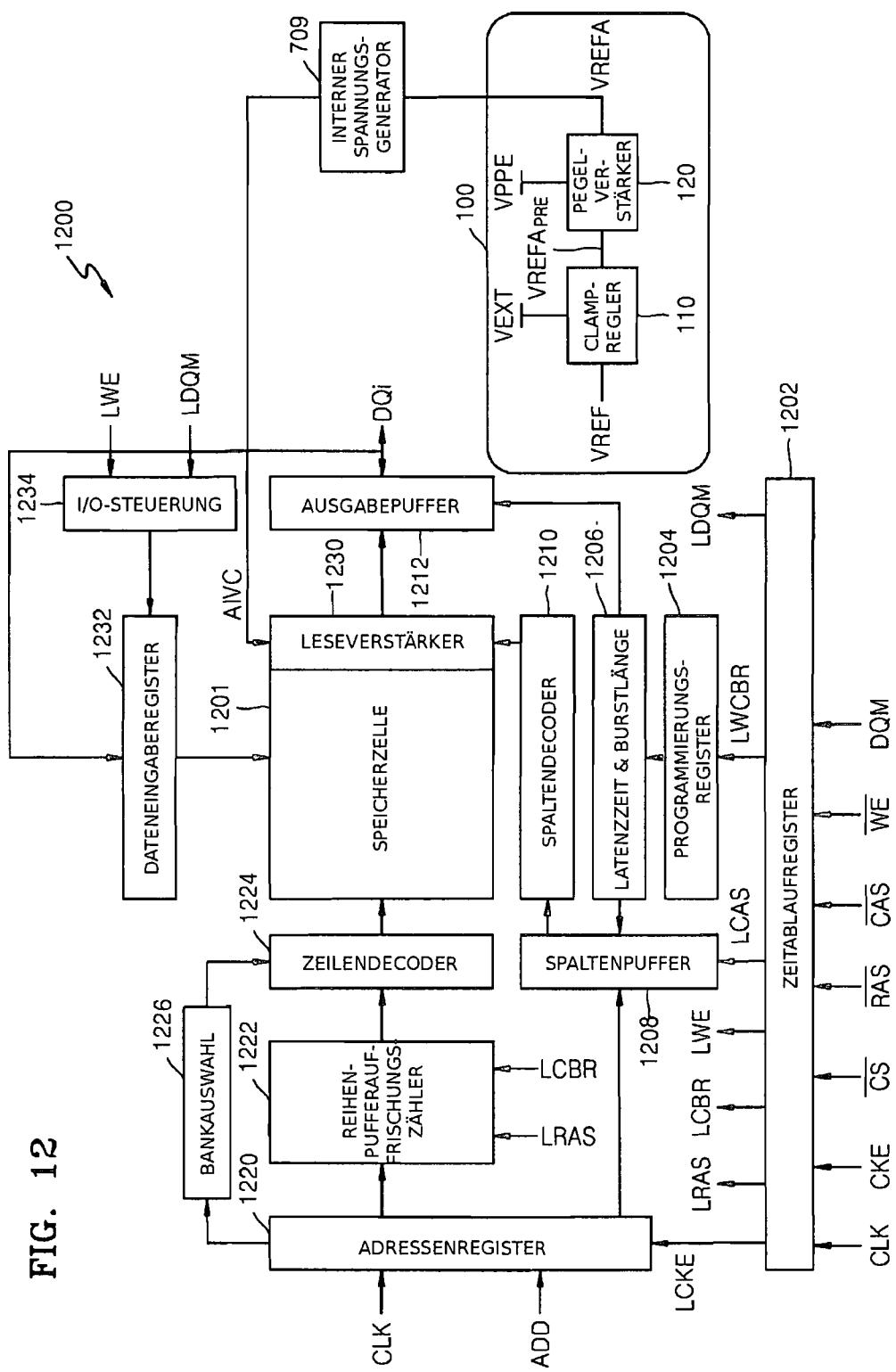

**[0108]** Die Referenzspannungsgenerator gemäß den Ausführungsformen, die hier offenbart sind, können von einer Halbleiterspeichervorrichtung, die in [Fig. 12](#) gezeigt ist, umfasst sein, z. B. einem Double Date Rate Synchronous Dynamic Random Access Memory (DDR-SDRAM).

**[0109]** Mit Bezug auf [Fig. 12](#) kann ein DDR-SDRAM **1200** eine Speicherzellanordnung **1201** umfassen, die DRAM-zellen und verschiedene Schaltkreisblöcke zum Betrieb der DRAM-zellen umfasst. Zum Beispiel kann ein Zeitablaufregister **1202** aktiviert werden, wenn ein Chipauswahlsignal CS von einem inaktiven Pegel (z. B. Logic-High) zu einem aktiven Pegelverstärker (z. B. Logic-Low) wechselt. Das Zeitablaufregister **1202** empfängt ein Kommandosignal, beispielsweise ein Uhrensignal CLK, ein Uhrenaktivierungssignal CKE, ein Chipauswahlsignal CSB, ein Zeilenadressenabtastsignal RASB, ein Spaltenadressenabtastsignal CASB, ein Schreibaktivierungssignal WEB, ein Dateneingabe/-ausgabe-maskensignal DQM etc., verarbeitet das empfangene Kommandosignal und erzeugt verschiedene interne Kommandosignale LRLS, LCBR, LWE, LCAS, LW-CBR und LDQM zum Steuern der Schaltkreisblöcke.

**[0110]** Einige der internen Kommandosignale, die in dem Zeitablaufregister **1202** erzeugt werden, werden in einem Programmierungsregister **1204** gespeichert. Zum Beispiel Latenzzeitinformationen und Burstlängeninformationen, die mit einer Datenausgabe in Zusammenhang stehen, können in dem Programmierungsregister **1204** gespeichert werden. Die internen Kommandosignale, die in dem Programmierungsregister **1204** gespeichert sind, können einer Latenzzeit-Burstlängensteuereinheit **1206** zur Verfügung gestellt werden, die dann ein Steuersignal zum Steuern der Latenzzeit oder Burstlänge der Datenausgabe für einen Spaltendekoder **1210** oder für einen Ausgabepuffer **1212** bereitstellt.

**[0111]** Ein Adressenregister **1220** kann ein Adressensignal ADD von einer externen Quelle empfangen. Ein Zeilenadresssignal kann dem Zeilendekoder **1224** durch eine Zeilenadresspuffer **1222** zur Verfügung gestellt werden. Das Spaltenadresssignal kann dem Spaltendekoder **1210** durch einen Spal-

tenadresspuffer **1208** zur Verfügung gestellt werden. Weiterhin kann der Zeilenadresspuffer **1222** ein Auffrischungssignal, das von einem Auffrischungszähler als Antwort auf Auffrischungsbefehle LRAS und LCBR erzeugt wird, empfangen und dem Zeilendekoder **1224** eines von dem Zeilenadressensignal und dem Auffrischungsadressensignal zur Verfügung stellen. Das Adressenregister **1220** kann ein Banksignal zum Auswählen einer Bank für eine Bankauswahleinheit **1226** bereitstellen.

**[0112]** Der Zeilendekoder **1224** dekodiert die Zeilenadressensignal- oder die Auffrischungsadressensignaleingabe von dem Zeilenadresspuffer **1222** und aktiviert eine Word-Leitung der Speicherzellanordnung **1201**. Der Spaltendekoder **1210** dekodiert ein Spaltenadresssignal und wählt eine Bitleitung der Speicherzellanordnung **1201** aus. Zum Beispiel wird eine Spaltenauswahlleitung auf eine Halbleiterspeichervorrichtung **1200** angewendet, sodass eine Auswahl durch eine Spaltenauswahlleitung ausgeführt werden kann.

**[0113]** Ein Leseverstärker **1230** verstärkt die Daten einer Speicherzelle, die von dem Zeilendekoder **1224** und dem Spaltendekoder **1210** ausgewählt ist und stellt die verstärkten Daten für den Ausgabepuffer **1212** bereit. Daten zum Schreiben in eine Datenzelle werden für die Speicherzellanordnung **1201** durch ein Dateneingaberegister **1232** bereitgestellt und ein Eingabe-/Ausgabeccontroller **1234** kann eine Datenweitergabeoperation durch das Datenregister **1232** steuern.

**[0114]** Der Referenzspannungsgenerator, wie in [Fig. 1](#) gezeigt, kann den Clamp-Regler **110** und den Pegelverstärker **120** umfassen. Der Clamp-Regler **110** wird von der externen Versorgungsspannung VEXT betrieben, und empfängt die erste Referenzspannung VREF, um die Clamp-Spannung VREFA<sub>PRE</sub> zu erzeugen. In einer Ausführungsform kann der zweite Referenzspannungsgenerator **708** die Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V, die höher ist als die erste Referenzspannung VREF, sogar erzeugen, wenn die erste Referenzspannung VREF aufgrund der Reduktion der externen Versorgungsspannung VEXT auf 1,2 V oder weniger mit 0,75 V oder weniger, erzeugt wird. Das Pegel der Clamp-Spannung VREFA<sub>PRE</sub> kann auf einen minimalen Spannungspegel eingestellt sein, das in einer erfolgreichen Wiederherstellungsoperation resultiert, wenn Daten in die Speicherzelle MC, die mit der Bitleitung BL des DRAM verbunden ist, geschrieben werden. In einer Ausführungsform wird der Pegelverstärker **120** von der zweiten Versorgungsspannung VPPE betrieben, die höher ist als eine externe Versorgungsspannung VEXT, und erzeugt unter Verwendung der Clamp-Spannung VREFA<sub>PRE</sub> von ungefähr 1,08 V die zweite Referenzspannung VREFA von ungefähr 1,2 V. Der Referenzspannungsgenera-

tor **100** kann auch gemäß einer der Ausführungsformen des Referenzspannungsgenerators, der mit Bezugnahme auf [Fig. 3](#) bis [Fig. 6](#) beschrieben ist, implementiert sein. Die zweite Referenzspannung VREFA kann ein Referenzspannungspegel zum Erzeugen einer internen Versorgungsspannung aufweisen, die den Leseverstärker **1230** ansteuert (z. B. durch einen internen Spannungsgenerator **700**). Die interne Versorgungsspannung AIVC hat einen Zielspannungspegel, das in einer erfolgreichen Wiederherstellungsoperation resultiert, wenn Daten in die Speicherzelle MC geschrieben werden, die mit der Bitleitung BL verbunden ist. In einer Ausführungsform kann eine interne Versorgungsspannung AIVC von ungefähr 1,2 V, die Auffrischungszeit der Speicherzelle MC, unabhängig vom Pegel der externen Versorgungsspannung VEXT, sichern.

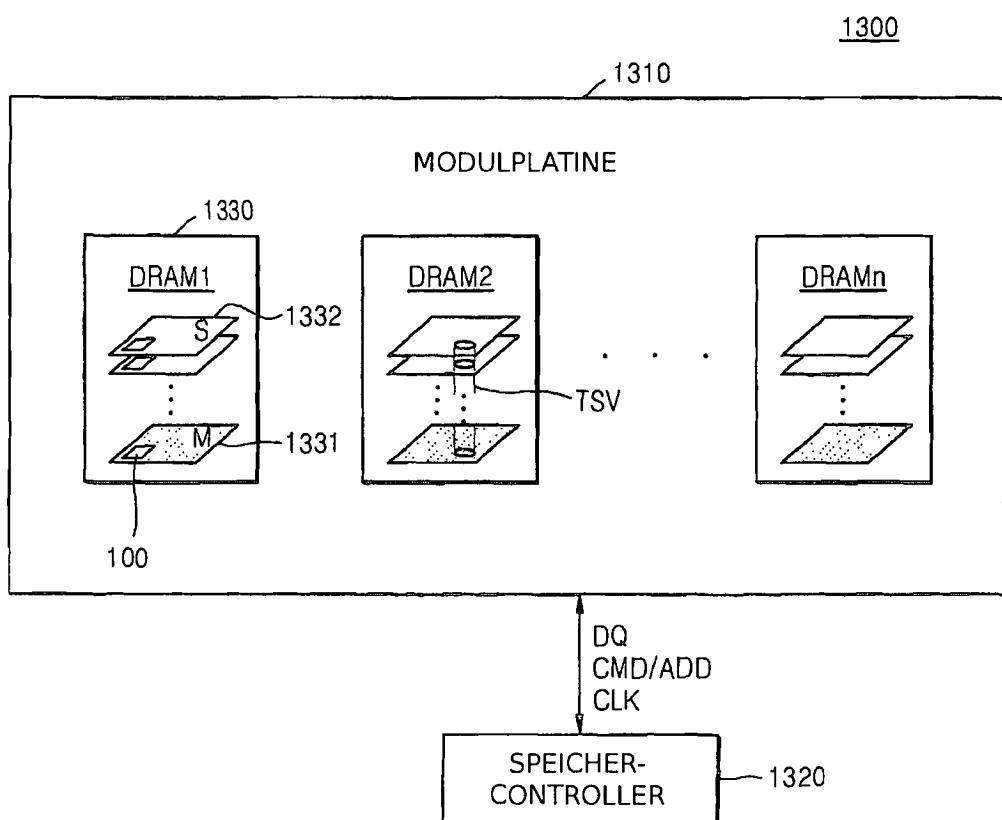

**[0115]** [Fig. 13](#) ist ein Diagramm, das ein Implementierungsbeispiel eines Speichersystems **1300** gemäß einer Ausführungsform zeigt, auf das die Halbleiter-speichervorrichtung nach [Fig. 12](#) angewendet wurde.

**[0116]** Mit Bezug auf [Fig. 13](#) kann das Speichersystem **1300** ein Speichermodul **1310** und einen Speichercontroller **1320** umfassen. Das Speichermodul **1310** kann mindestens eine Halbleiter-speichervorrichtung umfassen, die auf einer Modulplatine angebracht ist. Die Halbleiter-speichervorrichtung **1330** kann zum Beispiel als ein DRAM-Chip implementiert sein und die Halbleiter-speichervorrichtung **1330** kann eine Vielzahl von Halbleiterschichten umfassen. Die Halbleiterschichten können einen oder mehrere Master-Chips **1331** und einen oder mehrere Slave-Chips **1332** umfassen. Eine Signalweitergabe zwischen den Halbleiterschichten kann durch eine Substratdurchkontaktierung, wie bei beispielsweise einer Siliziumdurchkontaktierung (TSV) durchgeführt werden.

**[0117]** Während eine Struktur, in der die Signalweitergabe zwischen den Halbleiterschichten durch eine TSV ausgeführt wird, in der gegenwärtigen Ausführungsform beschrieben worden ist, kann eine solche Signalweitergabe auch auf eine Struktur angewendet werden, in der die Halbleiterschichten durch wire-bonding, interposing oder ein wire-formed tape abgeschieden sind.

**[0118]** Die Signalweitergabe zwischen den Halbleiterschichten kann auch durch optische Eingabe/Ausgabe(IO)-Verbindung durchgeführt werden. Zum Beispiel können die Halbleiterschichten untereinander durch Verwenden einer Verbindung strahlungsbasierter Art, die Radiowellen (RF) oder Ultraschallwellen verwendet, einer Verbindung induktiv gekoppelnder Art, die magnetische Induktion verwendet, oder durch eine Verbindung nicht-strahlungsbasierter Art, die Magnetfeldresonanz verwendet, verbunden sein.

**[0119]** Die strahlungsbasierte Art gibt ein Signal drahtlos unter Verwendung einer Antenne, wie beispielsweise einer Monopolantenne oder einer planaren invertierten F-Antenne (PIFA), weiter. Die Strahlung tritt als ein elektrisches Feld oder als ein magnetisches Feld in Erscheinung, die mit der Zeit wechseln, einander gegenseitig beeinflussen, und eine Antenne, die, wenn irgendeine, die gleiche Frequenz aufweist, kann ein Signal auf geeignete Weise für die Polarisierungscharakteristika einfallender Wellen empfangen.

**[0120]** Die induktiv gekoppelte Art erzeugt durch mehrmaliges Winden einer Spule ein starkes magnetisches Feld, und eine Spule, die auf einer ähnlichen Frequenz resoniert, ist nah an dem starken magnetischen Feld, wodurch sie die Kopplung erzeugt.

**[0121]** Die nicht-strahlungsbasierte Art verwendet evanescente Wellenkopplung, die elektromagnetische Wellen durch ein nahes elektromagnetisches Feld zwischen zwei Medien bewegt, die bei der gleichen Frequenz resonieren.

**[0122]** Der Master-Chip **1331** und der Slave-Chip **1332** können Referenzspannungsgenerator gemäß verschiedenen offenbarten Ausführungsformen umfassen. Der Referenzspannungsgenerator kann einen Clamp-Regler und einen Pegelverstärker, wie in [Fig. 1](#) gezeigt, umfassen. Der Clamp-Regler wird mit der externen Versorgungsspannung betrieben und empfängt eine erste Referenzspannung, um eine Clamp-Spannung zu erzeugen. In einer Ausführungsform kann der Referenzspannungsgenerator die Clamp-Spannung von ungefähr 1,08 V, die höher ist als die erste Referenzspannung, sogar erzeugen, wenn die erste Referenzspannung, da die externe Versorgungsspannung auf 1,2 V oder weniger abgesenkt ist, mit 0,75 V erzeugt wird. Der Clamp-Spannungspegel kann auf einen minimalen Spannungspegel eingestellt werden, der in einer erfolgreichen Zellwiederherstellungsoperation resultiert, wenn Daten in die Speicherzelle MC, die mit der Bitleitung BL des DRAM verbunden ist, geschrieben werden. Der Pegelverstärker wird mit der zweiten Versorgungsspannung, die höher ist als die externe Versorgungsspannung betrieben, und erzeugt unter Verwendung der Clamp-Spannung von zum Beispiel ungefähr 1,08 V die zweite Referenzspannung von zum Beispiel ungefähr 1,2 V. Der Referenzspannungsgenerator kann gemäß einer der Ausführungsformen der Referenzspannungsgenerator, die mit Bezugnahme auf [Fig. 3](#) bis [Fig. 6](#) beschrieben sind, implementiert sein. Die zweite Referenzspannung kann ein Referenzspannungspegel zum Erzeugen der internen Versorgungsspannung, die den Leseverstärker ansteuert, aufweisen. Die interne Versorgungsspannung hat einen Zielspannungspegel, der in einer erfolgreichen Zellwiederherstellungsoperation resultiert, wenn Daten in die Speicherzelle, die mit der Bitleitung ver-

bunden ist, geschrieben werden. Die interne Versorgungsspannung kann die Auffrischungszeit der Speicherzelle MC unabhängig vom Pegel der externen Versorgungsspannung sichern.

**[0123]** Das Speichermodul **1310** kann mit dem Speichercontroller **1320** durch ein Bussystem kommunizieren. Durch den System-Bus können Daten DQ, Kommando(CMD)/Adresse (ADD), ein Uhrensignal CLK etc. zwischen dem Speichermodul **1310** und dem Speichercontroller **1320** gesendet und empfangen werden.

**[0124]** [Fig. 14](#) ist ein Blockdiagramm eines Datenverarbeitungssystems **1440**, welches daran angebracht ein Speichersystem, gemäß einer beispielhaften Ausführungsform aufweist.

**[0125]** Mit Bezug auf [Fig. 14](#) kann eine Halbleiter-speichervorrichtung gemäß einer Ausführungsform als ein RAM **1420** auf dem Datenverarbeitungssystem **1400**, beispielsweise einer mobilen Vorrichtung oder einem Desktopcomputer, angebracht sein. Die Halbleiter-speichervorrichtung, die als der RAM **1420** angebracht ist, kann mit jeder der zuvor genannten Ausführungsformen übereinstimmen. Zum Beispiel kann der RAM **1420** eine Halbleiter-speichervorrichtung gemäß den vorangegangenen Ausführungsformen sein oder er kann ein Speichermodul sein. Der RAM **1420** kann ein Konzept aufweisen, das die Halbleiter-speichervorrichtung und den Speichercontroller umfasst.

**[0126]** Das Datenverarbeitungssystem **1440** gemäß einer beispielhaften Ausführungsform umfasst eine Hauptprozessor (CPU) **1410**, den RAM **1420**, eine Benutzerschnittstelle **1430** und einen nicht-flüchtigen Speicher **1440**, die elektrisch mit einem Bus **1450** verbunden sind. Der nicht-flüchtige Speicher **1440** kann eine Hochkapazitätsspeichervorrichtung, beispielsweise eine Solid-State-Festplatte (SSD) oder eine Festplatte (HDD) sein.