(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5967955号

(P5967955)

(45) 発行日 平成28年8月10日(2016.8.10)

(24) 登録日 平成28年7月15日(2016.7.15)

(51) Int.Cl.

H04N 5/347 (2011.01)

F 1

H 0 4 N

5/335

4 7 O

請求項の数 14 (全 20 頁)

(21) 出願番号 特願2012-18413 (P2012-18413)

(22) 出願日 平成24年1月31日 (2012.1.31)

(65) 公開番号 特開2013-157889 (P2013-157889A)

(43) 公開日 平成25年8月15日 (2013.8.15)

審査請求日 平成27年1月8日 (2015.1.8)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 順木 達也

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 大下内 和樹

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 鈴木 肇

最終頁に続く

(54) 【発明の名称】光電変換装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に設けられた複数の画素と、

各々が、前記行列の列に対応して設けられた複数の信号処理部と、

信号線と、

を有する光電変換装置であって、

前記複数の信号処理部の各々は、

対応する前記列の画素に基づく信号を保持する第1の容量と第2の容量と、

前記第1の容量と前記信号線とを電気的に接続するスイッチと、

前記第2の容量と電気的に接続された容量調整部を有し、

一の前記信号処理部が有する前記第1の容量および別の一の前記信号処理部が有する第2の容量を互いに並列に電気的に接続可能な接続部と、を備え、

前記容量調整部は、一方の主電極が前記第2の容量と電気的に接続され、他方の主電極が電源または前記一方の主電極に電気的に接続されたMOSトランジスタを有することを特徴とする光電変換装置。

## 【請求項 2】

前記スイッチはMOSトランジスタであって、当該MOSトランジスタは、前記容量調整部が有する前記MOSトランジスタと等しいサイズであることを特徴とする請求項1に記載の光電変換装置。

## 【請求項 3】

10

20

前記容量調整部が有する容量値は、前記スイッチに付随する容量値と等しいことを特徴とする請求項 1 または 2 に記載の光電変換装置。

【請求項 4】

前記第 1 の容量と前記第 2 の容量とは、互いに等しい容量値を有することを特徴とする請求項 1 から 3 のいずれかに記載の光電変換装置。

【請求項 5】

前記信号処理部は、前記画素に基づく信号を増幅する増幅器をさらに有することを特徴とする請求項 1 から 4 のいずれかに記載の光電変換装置。

【請求項 6】

前記増幅器は、増幅率が可変であることを特徴とする請求項 5 に記載の光電変換装置。 10

【請求項 7】

前記信号処理部は、前記画素に基づく信号からノイズを低減するノイズ低減部をさらに有することを特徴とする請求項 1 から 6 のいずれかに記載の光電変換装置。

【請求項 8】

前記信号処理部は、

前記画素に基づく信号を保持する第 3 の容量と、

前記第 3 の容量が保持した信号を前記第 1 または第 2 の容量に伝達するバッファ部と、をさらに有することを特徴とする請求項 1 から 7 のいずれかに記載の光電変換装置。

【請求項 9】

前記第 3 の容量の容量値は前記第 1 の容量の容量値よりも小さいことを特徴とする請求項 8 に記載の光電変換装置。 20

【請求項 10】

前記複数の列の各々は複数の前記画素を含み、

一の前記画素に基づく信号を、前記第 1 の容量から前記信号線に伝達する動作と、

別の前記画素に基づく信号を、前記第 3 の容量に保持させる動作と、の少なくとも一部を並行して行う

ことを特徴とする請求項 8 または 9 に記載の光電変換装置。

【請求項 11】

前記接続部により、異なる列の複数の前記画素に基づく信号を加算する第 1 の動作モードと、 30

前記接続部により、異なる列の複数の前記画素に基づく信号を加算しない第 2 の動作モードと、で動作すること

を特徴とする請求項 1 から 10 のいずれかに記載の光電変換装置。

【請求項 12】

前記第 1 の動作モードにおいて、前記信号処理部は、対応する前記列の複数の前記画素に基づく画素信号をさらに加算することを特徴とする請求項 11 に記載の光電変換装置。

【請求項 13】

行列状に設けられた複数の画素と、

各々が、前記行列の列に対応して設けられた複数の信号処理部と、

信号線と、

を有する光電変換装置であって、

前記複数の信号処理部の各々は、

対応する前記列の画素に基づく信号を保持する第 1 の容量と第 2 の容量と、

前記第 1 の容量と前記信号線とを電気的に接続するスイッチと、

前記第 2 の容量と電気的に接続された MOS トランジスタと、

一の前記信号処理部が有する前記第 1 の容量および別の一の前記信号処理部が有する第 2 の容量を互いに並列に電気的に接続可能な接続部と、を備え、

前記 MOS トランジスタのソース端子およびドレイン端子が短絡されていること、を特徴とする光電変換装置。

【請求項 14】

50

請求項 1 から 1 3 のいずれかに記載の光電変換装置と、

前記複数の画素に像を形成する光学系と、

前記光電変換装置から出力された信号を処理して画像データを生成する映像信号処理部

と、

をさらに備えたこと

を特徴とする撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は光電変換装置に関し、特に、信号を加算する機能を備える光電変換装置および 10

撮像システムに関する。

【背景技術】

【0002】

光電変換装置は、デジタルスチルカメラやデジタルカムコーダのような撮像システムに

用いられる。光電変換装置に対しては様々な要求があり、その中には出力レートの向上が

ある。

高出力レートを実現するために、光電変換装置内で複数の画素に基づく信号を加算する

ことで、光電変換装置から出力される信号の数を減らす技術が知られている。信号を加算

することによって、解像度の低下による画質の低下を抑制しながら、高出力レートを得る

ことができる。 20

特許文献 1 には、行列状に配列された画素に対して、行に沿った方向ならびに列に沿った

方向に信号を加算する撮像装置が記載されている。特許文献 1 には、水平方向、すなわ

ち行に沿った方向に重み付け加算を行うことが記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2010-68123 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献 1 に記載された構成では、画素の各列に対して設けられた 2 つ

の保持容量間で、接続されているスイッチの個数が異なるため、2 つの保持容量間の容量

値に差が生じる可能性がある。その結果、各保持容量で保持する電荷量に差が生じ、生成

される画像の画質が劣化する可能性がある。

本発明は、上記画質の劣化を低減することを目的とする。

【課題を解決するための手段】

【0005】

本発明の一つの側面である光電変換装置は、複数の列に設けられた複数の画素と、各々

が、前記列に対応して設けられた複数の信号処理部と、信号線と、を有する光電変換装置

であって、前記信号処理部は、対応する前記列の画素に基づく信号を保持する第 1 の容量

と第 2 の容量と、前記第 1 の容量と前記信号線との間に設けられたスイッチと、前記第 2

の容量と電気的に接続された容量調整部を有し、一の前記信号処理部が有する前記第 1 の

容量および別の一の前記信号処理部が有する第 2 の容量を接続可能な接続部と、を備え、

前記容量調整部は、一方の主電極が前記第 2 の容量と電気的に接続され、他方の主電極が

電源または前記一方の主電極に電気的に接続された MOS テランジスタを有すること、を

特徴とする。 40

【発明の効果】

【0006】

本発明によれば、信号加算時における画質の劣化を低減することができる。

【図面の簡単な説明】

10

20

30

40

50

## 【0007】

- 【図1】実施例に係る光電変換装置の構成例を示す図

- 【図2】実施例1に係る信号処理部の構成例を示す図

- 【図3】実施例1に係る全画素読み出しモードの動作例を示す図

- 【図4】水平方向の加算の概念を示す図

- 【図5】実施例1に係る重み付け加算モードの動作例を示す図

- 【図6】実施例1に係る信号処理部の別の構成例を示す図

- 【図7】実施例1に係る信号処理部の構成例を示す図

- 【図8】実施例2に係る全画素読み出しモードの動作例を示す図

- 【図9】実施例2に係る重み付け加算モードの動作例を示す図

- 【図10】実施例3に係る信号処理部の構成例を示す図

- 【図11】実施例3に係る全画素読み出しモードの動作例を示す図

- 【図12】実施例3に係る重み付け加算モードの動作例を示す図

- 【図13】実施例に係る撮像システムの構成例を示す図

## 【発明を実施するための形態】

## 【0008】

一般に、信号の平均化と信号の加算とは同義に扱うことができる。以下の実施形態においても、平均化と加算とを総称して加算として説明する。

## 【0009】

## (実施例1)

本発明に係る第1の実施形態では、第1の動作モードである全画素読み出しモードに加え、第2の動作モードである水平方向の重み付け加算モードで動作する光電変換装置を例にとって説明する。水平方向とは、行列状に配列された画素アレイにおいて、行に沿った方向のことである。

## 【0010】

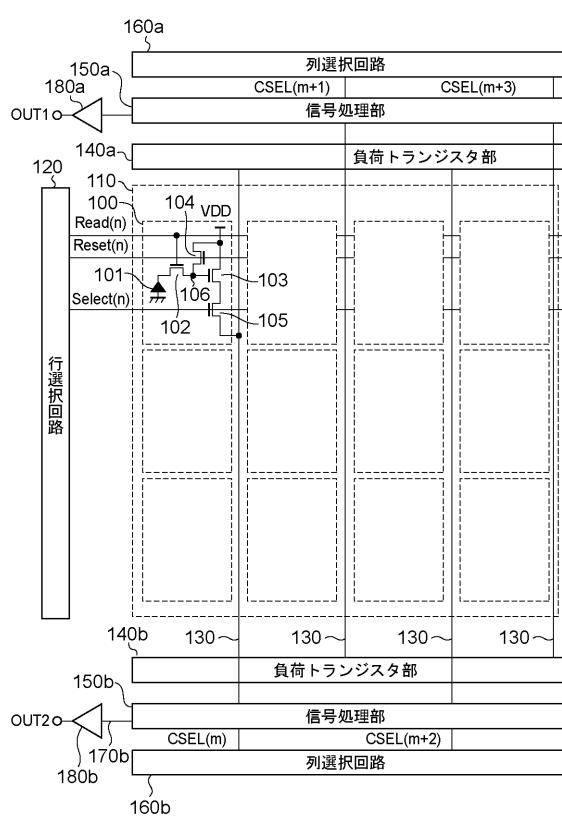

まず、図1を参照しながら本実施例にかかる光電変換装置の構成例を説明する。画素アレイ110には画素100が行列状に配列される。ここでは3行×4列分の画素アレイを示している。制御部である行選択回路120は、信号Read、Reset、およびSelectを画素アレイに供給することで画素100の動作を制御する。画素100から出力されて信号が第1の垂直信号線130に伝達される。第1の垂直信号線130に出力された信号は、読み出し部である信号処理部150aおよび150bで処理される。信号処理部150a、150bで処理された信号は、水平信号線170a、170bを介して、対応する出力アンプ180a、180bに伝達され、出力端子OUT1、OUT2から出力される。信号処理部150a、150bは、それぞれ画素の列に対応して回路を備える。列線選択回路160a、160bは、信号処理部150a、150bに含まれる回路のうちの列を選択するための信号を出力する。負荷トランジスタ部140a、140b、信号処理部150a、150b、ならびに列選択回路160a、160bは、画素アレイ110を挿むように設けられている。画素アレイの左から奇数番目の列(以下、奇数列)の画素からの信号は信号処理部150bを経て出力端子OUT2から出力され、画素アレイの左から偶数番目の列(以下、偶数列)の画素からの信号は信号処理部110aを経て出力端子OUT1から出力される。単板式のカラー光電変換装置を考えると、ペイヤ配列においては、同色のフィルタが1画素おきに設けられているので、ある行に着目すると、各出力端子OUT1とOUT2の各々に着目すると、同一の色の画素に基づく信号のみが出力される。行選択回路120および列選択回路160は、ともに制御部と呼ぶ。また、例えば信号処理部150a、150bのように複数のものを指す場合、信号処理部150として表記するものとする。

## 【0011】

次に、画素100の構成を説明する。画素配列110に含まれる各画素100はフォトダイオード101、転送トランジスタ102、リセットトランジスタ104、FD(Floating Diffusion)部106、増幅トランジスタ103、および選択ト

10

20

30

40

50

ランジスタ 105 を含む。光電変換部であるフォトダイオード 101 は、入射する光量に応じて電荷を生成および蓄積する。転送部である転送トランジスタ 102 は、フォトダイオード 101 と FD 部 106 との間の導通または非導通を切り替える。画素出力部である増幅トランジスタ 103 のゲート電極は FD 部 106 と接続される。リセット部であるリセットトランジスタ 104 は、電源 VDD と増幅トランジスタ 103 のゲート端子との導通、または非導通を切り替える。転送トランジスタ 102 とリセットトランジスタ 104 が同時に導通しているときには、フォトダイオード 101 が電源 VDD によってリセットされる。増幅トランジスタ 103 は画素選択部である選択トランジスタ 105 が導通している期間には、負荷トランジスタ部 140 に含まれる定電流源とともに、ソースフォロワ回路を形成する。これにより、第 1 の信号線である第 1 の垂直出力線 130 には、その時の増幅トランジスタ 103 のゲート電位、言い換えると FD 部 106 の電位、に応じた出力が第 1 垂直信号線に現れる。転送トランジスタ 102 を制御するための信号 a Read 10 、リセットトランジスタ 104 を制御するための信号 Reset 、選択トランジスタ 105 を制御するために信号 Select は同一の行に含まれる画素に対して行選択回路 120 から共通に与えられる。

#### 【0012】

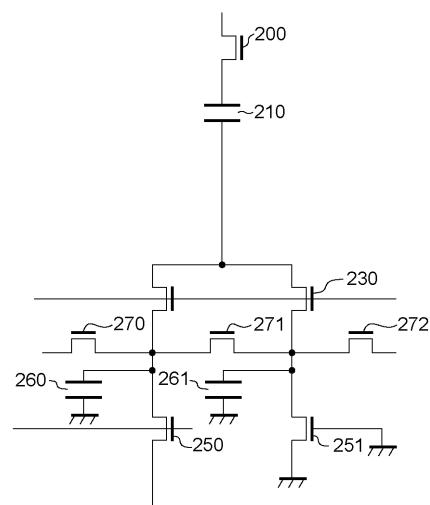

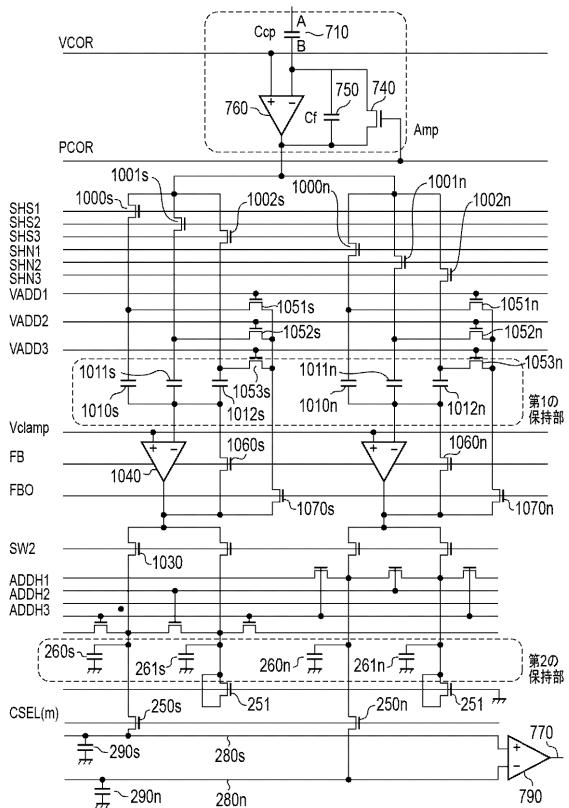

図 2 は、読み出し部である信号処理部 150a、b をより具体的に示した構成例である。ここでは画素の m 列目、m + 5 列目までに対応する部分を抜き出している。画素アレイ 110 を挟んで 150a、150b が配置されているが、接続される画素の列が異なるのみで、構成は信号処理部 150a と同一なので説明を省略する。画素の各列に対してサンプルホールドスイッチ 200 、サンプリング容量 260 - 265 、クランプ容量 210 、クランプスイッチ 240 、信号書き込みスイッチ 230 、加算制御スイッチ 270 - 276 、および列選択スイッチ 250 、およびダミースイッチ 251 を含む。第 1 の垂直信号線 130 はサンプルホールドスイッチ 200 とクランプ容量 210 とを介して第 2 の垂直信号線 220 と接続されている。第 2 の垂直信号線 220 には、サンプリング容量 260 - 265 がそれぞれスイッチ 230 を介して接続されている。サンプリング容量 260 - 265 にはさらに加算制御スイッチ 270 - 276 が接続される。また、サンプリング容量 260 、262 、264 は列選択スイッチ 250 を介してそれぞれ水平信号線 280 へと接続される。水平信号線容量 290 は水平信号線 280 がもつ容量である。水平信号線容量 290 は、水平信号線 280 の配線に付随する寄生容量および、スイッチ 250 が接続されることにより生じる MOS トランジスタの接合容量を含む。一方、サンプリング容量 261 、263 、265 にはダミースイッチ 251 が接続されている。ダミースイッチ 251 を設けることで、サンプリング容量 260 - 265 に接続するスイッチの数をそろえて、サンプリング容量 260 - 265 から見える、容量成分の差を低減している。また、ダミースイッチ 251 のソース - ドレイン間はショートされている。ダミースイッチ 251 は、列選択スイッチ 250 とは違い、水平信号線 280 に接続しないことで、水平信号線容量 290 を増加させず、後述の回路ゲインの低下を抑制している。ここで、サンプリング容量 260 、262 、264 を第 1 の容量、サンプリング容量 261 、263 、265 を第 2 の容量とする。また、スイッチ 272 、274 のように、別の列の第 1 の容量と第 2 の容量とを接続するスイッチを接続部と呼ぶ。 20 30 40

#### 【0013】

次に図 1 および 2 に示した構成の光電変換装置において信号を読み出す動作を記載する。

#### 【0014】

(全画素読み出しモード)

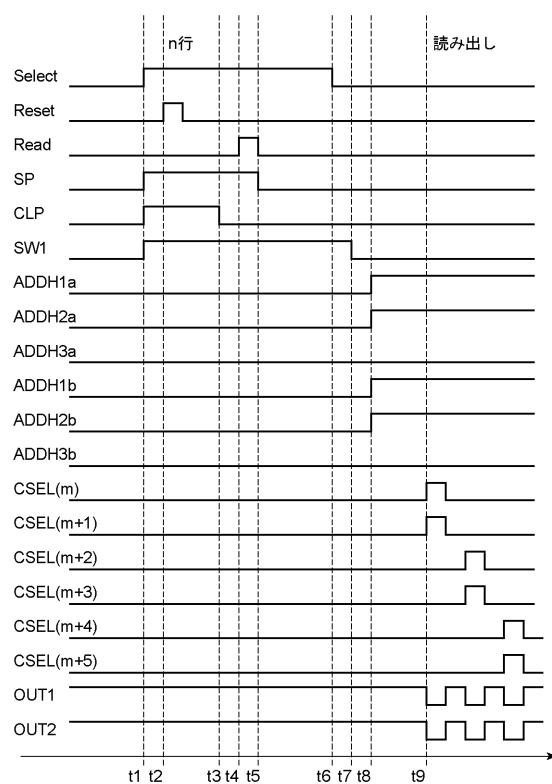

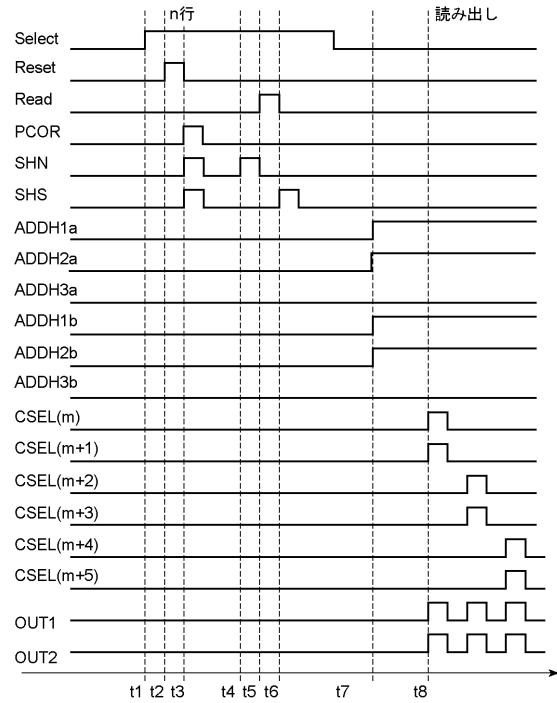

まず、加算動作を行わない動作モードについて図 3 を参照しながら説明する。ここでは全画素読み出しモードと称するが、画素アレイの全ての画素を読み出さなければならないわけではなく、画素間での加算処理を行わないことを意味するものとする。

#### 【0015】

時刻 t1 に、信号 Select (n) がハイレベルになる。これによって n 行目の画素

に含まれる選択トランジスタ 105 がオンしてソースフォロワ動作を行うので、増幅トランジスタ 103 のゲート電極の電位、すなわち FD106 の電位に対応したレベルが第 1 の垂直信号線 130 に現れる。すなわち、時刻  $t_1$  に、 $n$  行目の画素が選択された状態が開始する。同じく時刻  $t_1$  には、信号 SP および CLP がハイレベルになるので、クランプ容量 210 には第 1 の垂直信号線に現れたレベルと電圧と CPDC との電位差が与えられた状態となる。

【0016】

時刻  $t_2$  から信号 Reset( $n$ ) がパルス状にハイレベルになると、FD106 の電位が電源電圧 VDD に応じてリセットされる。これにより第 1 に垂直信号線 130 およびクランプ容量 210 の端子 A には FD 部 106 をリセットしたことに対応するレベルが現れる。 10

【0017】

時刻  $t_3$  に信号 CLP がローレベルになると、クランプスイッチ 240 が非導通状態になるので、第 2 の垂直信号線 220 が電気的に浮遊状態となる。これにより、クランプ容量 210 には、FD 部 106 をリセットしたことに対応するレベルと電圧 CPDC の電位差が保持される。

【0018】

時刻  $t_4$  に信号 a Read( $n$ ) がハイレベルになると、フォトダイオード 101 に蓄積された電荷が FD 部 106 へと転送される。転送された電荷量に応じて FD 部 106 の電位が変化し、これに対応したレベルが第 1 の垂直信号線 130 に現れる。クランプ容量 210 には、FD 部 106 をリセットしたことに対応するレベルと電圧 CPDC との電位差が保持されたままである。したがって、第 2 の垂直信号線 220 の電位は、FD 部 106 をリセットしたことに対応するレベルと、フォトダイオード 101 から FD 部 106 へと電荷を転送したことに対応するレベルとの差分  $V_{in}$  に容量で決まるゲインのかかった分だけ変動する。クランプ容量 210 の容量値を Ccp とすると、第 2 の垂直信号線 220 に生じる電圧変化  $V$  は、 20

$$V = (C_{cp} \cdot 2 \cdot C_{sp}) \times V_{in} \quad \dots (1)$$

となる。

【0019】

FD 部 106 をリセットしたことに対応するレベルには、リセットトランジスタ 104 をスイッチングしたことによるノイズ成分や、画素を構成するトランジスタに固有のノイズ成分を含む。また、フォトダイオード 101 から FD 部 106 に電荷を転送したことによるレベルにも、このノイズ成分が重畠されているので、クランプ容量 210 を用いて上述の動作を行うことでノイズを低減することができる。 30

【0020】

時刻  $t_5$  に信号 SP がローレベルになるとサンプルホールドスイッチ 200 が非導通になり、クランプ容量 210 と第 1 の垂直信号線 130 とは非導通状態になる。これによって  $V$  がサンプリング容量 260 - 265 に保持される。

【0021】

時刻  $t_6$  に信号 Select( $n$ ) がローレベルになり、 $n$  行目の画素 100 に含まれる増幅トランジスタ 103 第 1 の垂直信号線 130 が非導通状態となることで、ソースフォロワ動作が終了する。つまり、 $n$  行目の画素が選択された状態が終了する。 40

【0022】

時刻  $t_8$  に、ADDH1a、ADDH2a、および ADDH1b がハイレベルになる。このとき、図 2 の (a)、(b) より、各列に設けたサンプリング容量つまり、サンプリング容量 260 と 261、サンプリング容量 262 と 263、およびサンプリング容量 264 と 265 がそれぞれ並列で接続された状態で読み出される。

【0023】

時刻  $t_9$  から信号 CSEL( $m$ )、CSEL( $m+1$ )、 $\dots$ 、CSEL( $m+5$ ) が順次供給されると、各列のサンプリング容量 260 - 265 に保持された信号が水平信 50

号線 280 に出力される。サンプリング容量 260 - 265 に保持された信号を水平信号線 280 に出力するときには、容量の比で決まるゲインがかかる。水平線容量 290 の容量値を C<sub>com</sub>、出力アンプ 180 のゲインを G<sub>amp</sub> とすると、出力端子 OUT に現れる出力 V<sub>out</sub> は、

$$V_{out} = V \times \{ C_{sp} / (C_{sp} + C_{com}) \} \times G_{amp} \quad \dots (2)$$

となる。

【0024】

ダミースイッチを設けることで、サンプリング容量 260 - 265 の容量値が同一とみなせるため、上述の通りサンプリング容量の容量値をすべて C<sub>sp</sub> とした。 10

【0025】

期間「n + 1 行」、「n + 2 行」以降も同様の動作が繰り返される。

【0026】

(重み付け加算モード)

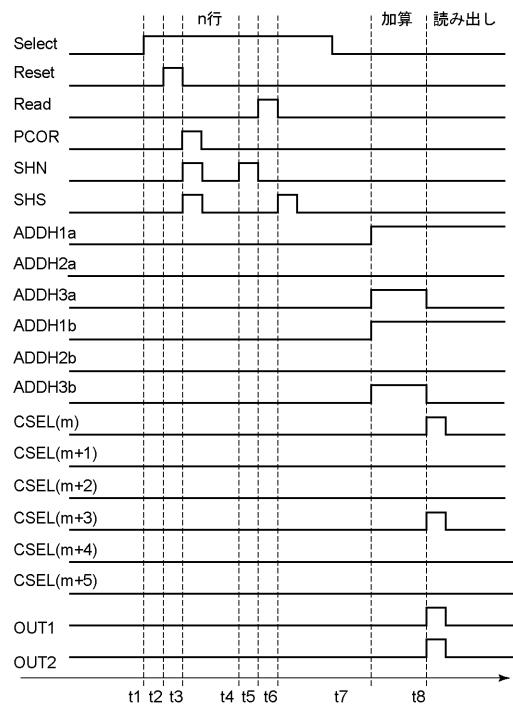

次に、水平方向に重み付けをして加算をする動作モードについて説明する。

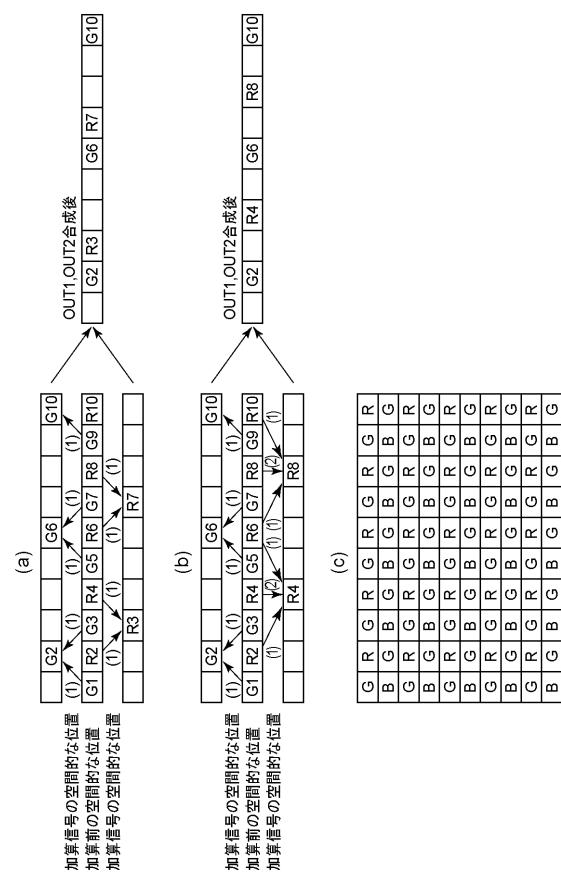

【0027】

重み付け加算動作の説明に先立ち、重み付けをしない加算動作を説明する。図 4 (c) は、カラー光電変換装置において一般的に用いられる、ペイヤ配列のカラーフィルタの配列を示している。R、G、B はそれぞれ赤、緑、青の色の光を透過させるフィルタである。このうち、n 行目の配列を抜き出したものが図 4 (a) である。添え字は図の左側から数えた画素の位置を示し、( ) で囲った数字は加算時の比率を示す。一般に、カラーフィルタを備えた光電変換装置において、行に沿った方向の加算を行う場合、同色の画素のうち隣接する画素からの信号を加算する。したがって、図 4 (a) において G<sub>1</sub> と G<sub>3</sub>、R<sub>2</sub> と R<sub>4</sub>、G<sub>5</sub> と G<sub>7</sub>、R<sub>6</sub> と R<sub>8</sub>、… のような組み合わせで加算される。 20

【0028】

仮に、2つの画素の信号を 1 : 1 の比率で加算すると、G<sub>1</sub> と G<sub>3</sub> を加算した後の信号の空間的な重心の位置は G<sub>1</sub> と G<sub>3</sub> の中間である G<sub>2</sub> で示す位置となる。同様に、R<sub>2</sub> と R<sub>4</sub> は R<sub>3</sub> に、G<sub>5</sub> と G<sub>7</sub> は G<sub>6</sub> に、R<sub>6</sub> と R<sub>8</sub> は R<sub>7</sub> に、それぞれ加算後の信号の空間的な重心位置が現れる。したがって、光電変換装置の外部の映像信号処理回路等によって合成した画像の n 行目の信号は、図 4 (a) の右側に示すような配置となる。つまり、加算後の G と R の空間的な位置は等ピッチにはならず、G と R とが近寄った偏心配置となる。このような色重心の偏心は、空間周波数の高い被写体を撮影した際に偽信号の原因となりうる。 30

【0029】

このような偏心を改善するための手法が重み付け加算である。図 4 (b) を用いて重み付け加算の概念を説明する。重み付け加算においては、隣り合って設けられた 3 個の R 画素を 1 : 2 : 1 の比率で加算する。すなわち、R<sub>2</sub>、R<sub>4</sub>、R<sub>6</sub> の画素であれば、1 : 2 : 1 の比率で加算する。これにより、加算後の R 画素の空間的な重心位置は R<sub>4</sub> で示す位置になる。同様にして、R<sub>6</sub>、R<sub>8</sub>、R<sub>10</sub> の画素を 1 : 2 : 1 の比率で加算する。一方、G 画素については従来と同様に 1 : 1 の比率で加算する。したがって、出力端子 OUT の後段に設けられた映像信号処理回路によって得られる n 行目の信号は、図 4 (b) の右側に示すような配置になり、G 画素と R 画素とが互いに等ピッチに配列される。これにより、重み付けを行わない加算動作の場合に生じる偽信号が発生しにくくなるという利点がある。 40

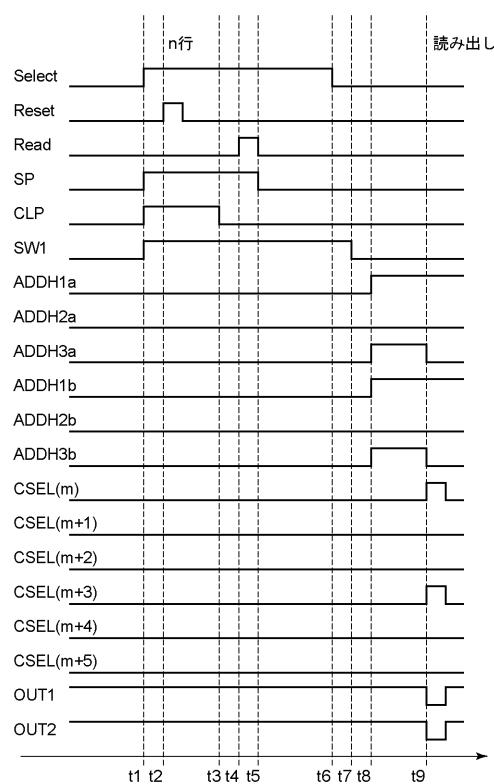

【0030】

図 5 は、図 1 および 2 に示した光電変換装置における、重み付け加算モードの動作タイミングの例を示した図である。ここでは、図 3 で示した全画素読み出しモードにおける動作と異なる点を中心に説明する。全画素読み出しモードでは各列の備えたサンプリング容量のうち、260 - 261、262 - 263、および 264 - 265 を 1 組の容量として扱い、1 画素からの信号を保持していた。これに対して、重み付け加算モードでは、サン 50

プリング容量を二つに分割して利用する点で異なっている。図2をもとに、信号処理部150a、150bの動作をそれぞれ説明する。図5に示したタイミング図において、信号ADDH2、ADDH3のタイミングが、全画素読み出しモードとは異なる。

#### 【0031】

まず、信号処理部150aにおいては、隣接する2列の加算平均信号を出力する。時刻t8にADDH1、ADDH3がハイレベルとなり、加算スイッチ271、272、273、275、276が導通状態になる。サンプリング容量260、261、262、263が並列に接続されるため、信号が加算される。

#### 【0032】

その後、時刻t9にADDH3はローレベルになり、サンプリング容量260、261、262、263で保持された信号の平均値が保持される。つまり、(m)列と(m+2)列は1:1の割合で加算される。その後、時刻t10においてCSEL(m)がハイレベルになると、式(2)で示した回路ゲインにより、水平信号線280へと伝達される。

#### 【0033】

次に信号処理部150bの動作を説明する。時刻t8でADDHb1、ADDHb3がハイレベルとなり、加算スイッチ270、272、273、274、276が導通状態になる。サンプリング容量261、262、263、264が並列に接続されるため、信号が加算される。

#### 【0034】

その後、時刻t9にADDH3はローレベルになり、サンプリング容量261、262、263、264で保持された信号の平均値が保持される。つまり、m+1列、(m+3)列、および(m+5)列の信号が1:2:1の割合で加算される。本例ではダミースイッチ251を設けることにより、サンプリング容量261、262、263、264の容量値が略同一になるよう調整をしているため、上述の1:2:1の割合での平均が精度よく実現できる。例えば、ダミースイッチ251がない場合には、スイッチの分寄生容量にそれが生じるため、スイッチ250の接合容量をCpとした場合、上述の加算において加算されるサンプリング容量の比は(C+Cp):(2xC+Cp):Cとなり、重み付けのバランスが1:2:1からくずれ、得られる画像の画質が低下する可能性がある。特に、素子の微細化などの理由からサンプリング容量260-265の値を大きく設定できない場合には、スイッチの接合容量を含めた寄生容量の影響が無視できなくなる。

#### 【0035】

その後、時刻t10においてCSEL(m+2)がハイレベルになると、式(2)で示した回路ゲインにより、水平信号線280へと伝達される。以後、同様の動作により順次読み出される。

#### 【0036】

以上の動作により、G画素とR画素と加算後の重心が互いに等ピッチに配列され、色重心のずれによる偽信号が発生しにくくなる。

#### 【0037】

上述の列選択スイッチ250とダミースイッチ251とは、ともにMOSトランジスタで構成することができる。このとき、両者のサイズを等しくすることで、第1および第2の容量に付随する容量値を一致させやすくなる。

#### 【0038】

なお、本実施例においては各列のサンプリング容量260-265の容量値の差を抑制する手段として、ダミースイッチを設けたが、ダミースイッチである必要はない。例えば、サンプリング262と263で容量値を(サンプリング容量262の容量値) < (サンプリング容量263の容量値)とすることで、読み出しスイッチ250の接合容量に相当する差分を抑制することもできる。すなわち、2つのサンプリング容量の容量値の差を低減するための容量調整部を設けることにより、重み付け加算を精度よく行うことができ、得られる画像から偽信号を低減することができる。容量調整部は、容量素子であってもよく、これ以降の実施例についても同様である。

10

20

30

40

50

## 【0039】

また、本実施例では水平信号容量290を増加させないために、ダミースイッチのソース端子とドレイン端子という主電極間をショートさせたが、例えば図6に示すよう1列分の等価回路の通り、ソースを固定電位に接続するなど、水平信号容量290を増加させない構成になっていればよい。

## 【0040】

## (実施例2)

第1の実施例においては、画素に起因するノイズ成分を、信号処理部に含まれるクランプ容量を用いて低減するものを例示した。本発明に係る第2の実施例では画素に起因するノイズ成分を低減することに加えて、信号を増幅することができる構成を説明する。本実施例においても、第1の動作モードである全画素読み出しモードに加えて、第2の動作モードである重みつけ加算モードと、で動作できる光電変換装置を例にとって説明する。

10

## 【0041】

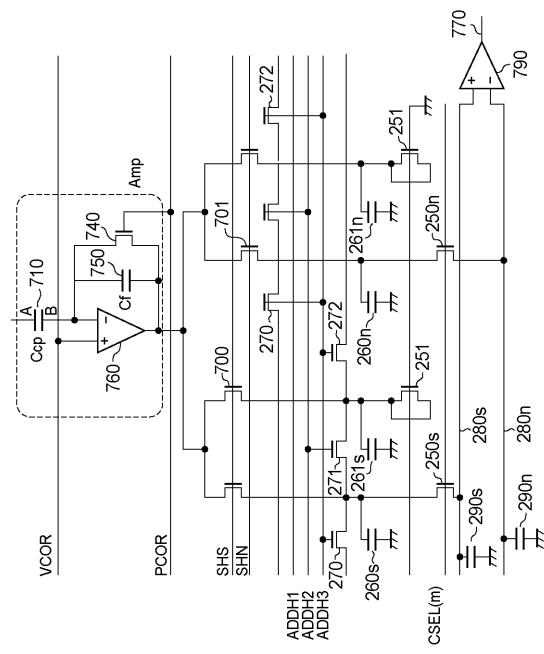

図7は、本実施例に係る信号処理部のうち1列分の回路を抜き出したものである。列増幅部Ampは、クランプ容量710、演算増幅部760、短絡スイッチ740およびフィードバック容量750を含む。クランプ容量710の一方の端子Aは第1の垂直信号線130に接続されており、他方の端子Bは演算増幅部760の反転入力端子に接続されるとともに、フィードバック容量780の一方の端子、および短絡スイッチ740の一方と接続されている。フィードバック容量750の他方の端子は、短絡スイッチ740の他方の電極および演算増幅器760の出力端子と接続される。演算増幅器760の非反転入力端子には基準電圧VCRが供給される。また、短絡スイッチは信号PCRによって制御される。信号PCRは、例えば不図示のタイミング制御回路部から供給される。列増幅部Ampのフィードバック容量を複数設けて、その接続を切り替えることで列増幅部Ampの増幅率を可変とすることができます。また、後述するが、クランプ容量710は、ノイズ低減部としても作用する。

20

## 【0042】

演算増幅器760の出力端子、すなわち列増幅部Ampの出力端子は、スイッチ700、701を介してそれぞれサンプリング容量260s、261sおよびサンプリング容量260n、261nが接続されている。サンプリング容量にはさらにそれぞれ、加算制御スイッチ270s、270s、272sおよび270n、271n、272nが接続されており、列選択スイッチ250を介してそれぞれ水平信号線280s、nに接続される。水平信号線280s、280nは容量値Ccomを持つ。水平信号線容量は第1の水平信号線が持つ容量を模式的に表している。水平信号線280sは、出力部で差動増幅器790の非反転転端子、水平信号線280nは差動増幅器790反転入力端子に接続される。

30

## 【0043】

サンプリング容量260s、261sは、それぞれ実施例1で説明した第1と第2の容量に対応する。同様に、サンプリング容量260n、261nは、それぞれ実施例1で説明した第1と第2の容量に対応する。これらのサンプリング容量は、スイッチ272を介して他の列のサンプリング容量のうち、第2または第1の容量に接続される。

## 【0044】

40

図1における信号処理部150aと150bの両者が実質的に同じ構成であるため、両者を説明する図面として、図7がある。図7においては、信号ADDH1、ADDH2、ADDH3と示している。以下で説明するタイミング図では、信号処理部150aであればADDH1a、ADDH2a、ADDH3aが与えられ、信号処理部150bであればADDH1b、ADDH2b、ADDH3bが与えられるものとする。これは、本実施例以降の実施例についても同様である。

## 【0045】

## (全画素読み出しモード)

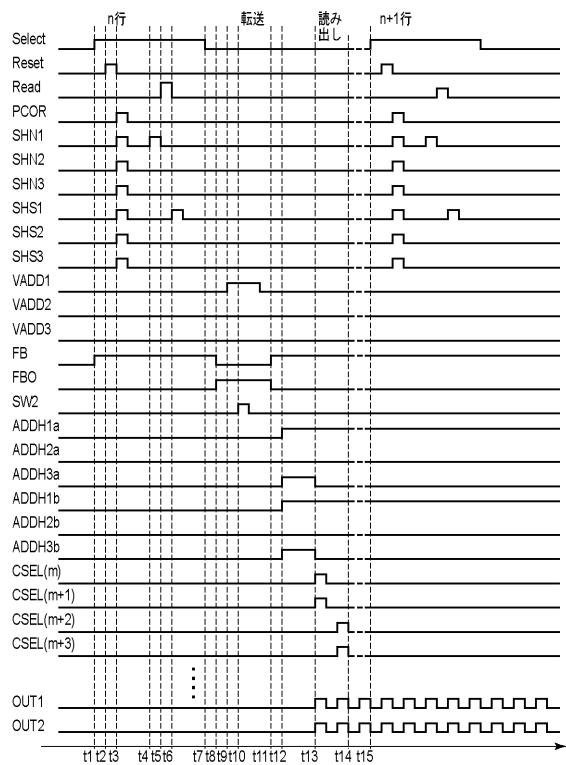

次に図8を参照しながら全画素読み出しモードの動作を説明する。なお、第1の垂直信号線130に接続される画素領域は、図1に示したものと同様であるとする。

50

## 【0046】

時刻  $t_1$  に信号  $S S e l e c t (n)$  がハイレベルになると、 $n$  行目の画素に含まれる選択トランジスタが導通状態となり、増幅トランジスタがソースフォロワ動作を行うので、増幅トランジスタのゲート電極の電位、すなわち  $F D$  部 106 の電位に対応したレベルが第 1 の垂直信号線に現れる。

## 【0047】

時刻  $t_2$  から信号  $R E S E T (n)$  がパルス状にハイレベルになると、 $F D$  部 106 の電位が電源電圧  $V D D$  に応じてリセットされる。これによって第 1 の垂直信号線およびクランプ容量の端子 A には、 $F D$  部 106 をリセットしたことに対応するレベルが現れる。時刻  $t_3$  から信号  $P C 0 R$  がパルス状にハイレベルになると、短絡スイッチ 740 によって、演算増幅器 760 の反転入力端子と出力端子とが短絡される。このとき、演算増幅器 760 の反転入力端子は、演算増幅器 760 の仮想接地により  $V C 0 R$  の電位になる。つまり、フィードバック容量 750 の両端が  $V C 0 R$  にリセットされ、クランプ容量 710 の端子 B も  $V C 0 R$  になる。

10

## 【0048】

時刻  $t_3$  には信号  $S H S$  および  $S H N$  もハイレベルとなるので、このときの演算増幅器の出力によってサンプリング容量がリセットされる。そして、信号  $P C 0 R$  がローレベルになるとクランプ容量の端子 B は電気的浮遊状態となるので、クランプ容量には、 $F D$  部 106 をリセットしたことに対応するレベルと電圧  $V C 0 R$  との電圧差が保持される。

20

## 【0049】

時刻  $t_4$  から信号  $S H N$  がパルス状にハイレベルになると、このときの列増幅部  $A m p$  の出力がサンプリング容量  $260n$ 、 $261n$  に保持される。サンプリング容量  $260n$ 、 $261n$  に保持される信号には、列増幅部  $A m p$  に起因するオフセット成分が含まれる。

## 【0050】

時刻  $t_5$  から信号  $R E A D (n)$  がパルス状にハイレベルになると、フォトダイオード 101 に蓄積された電荷が  $F D$  部 106 へと転送される。転送された電荷量に応じて  $F D$  部 106 の電位が変化し、これに対応したレベルが第 1 の垂直信号線 130 に現れる。クランプ容量には、 $F D$  部 106 をリセットしたことに対応するレベルと電圧  $P C 0 R$  との電位差が保持されたままであるので、クランプ容量の端子 B の電位は、 $F D$  部 106 をリセットしたことに対応したレベルと、フォトダイオード 101 から  $F D$  部 106 へと電荷を転送したことに対応するレベルとの差分  $V_{in}$  だけ変化する。第 1 の実施形態と異なるのは、 $V_{in}$  に対してクランプ容量とフィードバック容量  $C_f$  の容量値の比で決まるゲインがかかることがある。つまり、クランプ容量の容量値を  $C_0$ 、フィードバック容量  $C_f$  の容量値を  $C_f$  とすると、列信号部  $A m p$  の出力  $A m p O U T$  は

30

$$A m p O U T = (C_0 / C_f) \times V_{in} \quad \dots (3)$$

となる。 $F D$  をリセットしたことに対応するレベルには、リセットトランジスタ 104 をスイッチングしたことによるノイズ成分や、画素を構成するトランジスタに固有のノイズ成分を含む。したがって、クランプ容量を用いて上述の動作を行うことで画素に起因するノイズ成分を低減することができる。さらに、本実施形態によれば電圧変化  $V_{in}$  を  $C_0 / C_f$  のゲインで増幅することができる。

40

## 【0051】

時刻  $t_6$  から信号  $S H S$  がハイレベルになり、その後ローレベルになると式 (3) で表される電圧をサンプリング容量に保持する。サンプリング容量に保持される信号には、列信号部  $A m p$  の出力オフセットが含まれる。

## 【0052】

時刻  $t_7$  に信号  $S S e l e c t (n)$  がローレベルとなり、 $n$  行目の画素 100 に含まれる増幅トランジスタ 103 と第 1 の垂直信号線 130 とが非導通状態となることで、ソースフォロワ動作が終了する。言い換えると、 $n$  行目の画素が選択された状態が終了する。

50

## 【0053】

時刻  $t_7$  に加算制御スイッチがハイレベルとなり、各列のサンプリング容量が接続される。時刻  $t_8$  から信号  $CSEL(m)$ 、 $CSEL(m+1)$  が順次供給されると、サンプリング容量に保持された信号が水平信号線に出力される。サンプリング容量に保持される信号を水平信号線に出力するには、容量の比で決まるゲインがかかる。水平信号線の容量値を  $CCom$  とすると、水平信号線に現れる電圧  $V_{s1}$  は

$$V_{s1} = \{ Csp / (Csp + CCom) \} \times (C0 / Cf) \times V_{in} \quad \dots (4)$$

となる。同様に、サンプリングに保持された信号を水平信号線に出力されるとともに容量の比できるゲインがかかる。水平信号線の容量値を  $CCom$  とすると、水平信号線に現れる電圧  $V_{n1}$  は、10

$$V_{n1} = \{ Csp / (Csp + CCom) \} \times (C0 / Cf) \times V_{COR} \quad \dots (5)$$

となる。差動増幅器に入力される  $V_{s1}$  と  $V_{n1}$  の差分が出力端子  $OUT$  から出力される。  $V_{s1}$  と  $V_{n1}$  の両者には列増幅部  $AMP$  の出力オフセットが含まれるので、出力端子  $OUT$  からは列増幅部  $AMP$  の出力オフセットが低減された信号として出力される。

## 【0054】

(重み付け加算モード)

次に重みつけ加算モードについて説明する。図9に重みつけ加算モードの駆動パターンを示す。サンプリング容量への信号書き込みの動作は全画素読みモードと同様のため、省略する。ここでは、図8に示した全画素読み出しモードと異なる点を中心に説明する。全画素読み出しモードでは各列のサンプリング容量を二つを一つ容量として扱っていた。これに対して、重み付け加算モードでは、サンプリング容量をそれぞれ分割して利用する点で異なる。実施例1と同様に、全画素読みモードとの違いは加算平均期間の信号制御にある。サンプリング容量  $260s$ 、 $261s$  より構成される信号経路、およびサンプリング容量  $260n$ 、 $261n$  より構成される信号経路それぞれにおいて、実施例1の図5で示した動作と同様に加算平均動作、および信号出力を行う。20

## 【0055】

以上の本発明の構成によれば、読み出し回路でゲインをかけて出力することが可能になり、より  $S/N$  比を向上させつつ、精度よく重み付け加算を実施することができる。30

## 【0056】

本実施例においても、ダミースイッチ  $251$  を設けることにより、サンプリング容量  $260s$ 、 $261s$ 、 $260n$ 、 $261n$  の容量値が略同一になるよう調整をしている。尚、本実施例においても、サンプリング  $262$  と  $263$  で容量値を（サンプリング容量  $262$  の容量値） $<$ （サンプリング容量  $263$  の容量値）とすることで、読み出しへスイッチ  $250$  の接合容量に相当する差分を抑制することもできる。すなわち、2つのサンプリング容量の容量値の差を低減するための容量調整部を設けることにより、重み付け加算を精度よく行うことができ、得られる画像から偽信号を低減することができる。

## 【0057】

また、本実施例では水平信号容量  $290$  を増加させないために、ダミースイッチのソース - ドレインをショートさせたが、例えば図6に示すよう1列分の等価回路の通り、ソースを固定電位に接続するなど、水平信号容量  $290$  を増加させない構成になっていればよい。

## 【0058】

(第3実施例)

次に、本発明に係る第3実施例を説明する。第2の実施例と大きく異なるのは、信号処理部の構成である。本実施例に係る信号処理部は、第1及び第2の容量に加えて、第3の容量を有する。そして、第1の垂直信号線から供給された信号を前記第3の容量に信号を保持させる第1の工程と、第1の容量が保持した信号を信号線に出力する第2の工程が少なくとも一部を時間的に並行して行うことを特徴とする。本実施例によれば、垂直加算動4050

作および、水平加算平均動作が可能となる。

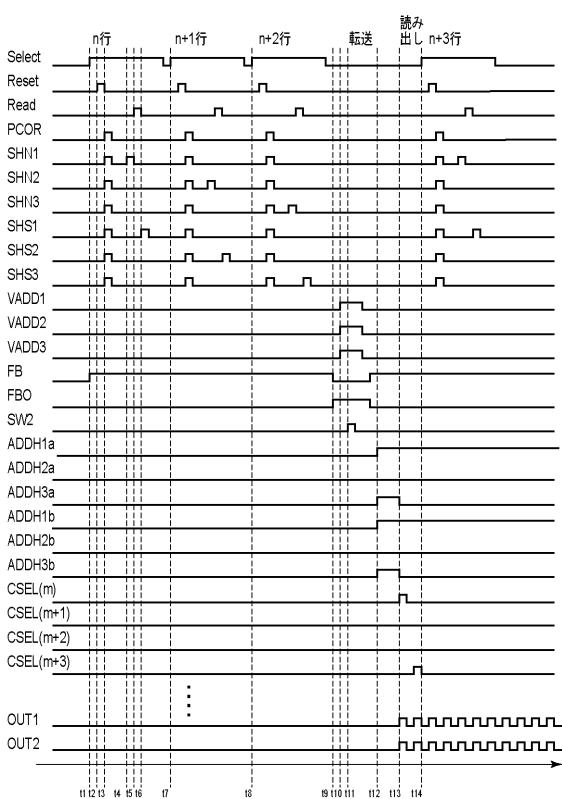

【0059】

図10に本実施例における信号処理部の1列分の構成を示す。実施例2と異なる点は第1の保持部である第3の容量1010s、1011s、1012s、および1010n、1011n、1012nはそれぞれ互いに並列に設けられている。第3の保持容量と第1および第2の容量との間にはバッファ部である差動増幅器1040を備えている。

【0060】

第3の容量1010s、1011s、1012s、および1010n、1011n、1012nの組はそれぞれ、一方の端子が互いに短絡されるとともに差動増幅器1040の反転入力端子に接続される。第3の容量の他方の端子は、それぞれスイッチ1051s、1052s、1053sおよび1051n、1052n、1053nを介して、共通のノード1060s、1060nに接続されている。さらに、1070s、1070nを介して、差動増幅器1040の出力端子に接続されている。

【0061】

サンプリング容量260s、261sは、それぞれ実施例1で説明した第1と第2の容量に対応する。同様に、サンプリング容量260n、261nは、それぞれ実施例1で説明した第1と第2の容量に対応する。これらのサンプリング容量は、スイッチ272を介して他の列のサンプリング容量のうち、第2または第1の容量に接続される。

【0062】

前述の式(2)に示したように、第1および第2の容量は、信号線260に伝達される信号に対するゲインを低減させないために、小さくすることが困難であるが、第3の容量はこの限りではない。したがって、第3の容量の容量値を、第1の容量の容量値よりも小さくすることができる。

【0063】

(全画素読み出しモード)

図11に、全画素読み出しモード時の動作を説明するためのタイミング図を示す。第1の垂直信号線130と接続される画素領域は、図1に示したものと同様であるとする。

【0064】

時刻t1に信号SSelect(n)がハイレベルになると、n行目の画素に含まれる選択トランジスタが導通状態となり、ソースフォロワ動作を行うので、増幅トランジスタのゲート電極の電位すなわちFD部106の電位に対応したレベルが第1の垂直信号線に現れる。

【0065】

時刻t2から信号RESET(n)がパルス状にハイレベルになると、FD部106の電位が電源電圧VDDに応じてリセットされる。これによって第1の垂直信号線およびクランプ容量の端子Aには、FD部106をリセットしたことに対応するレベルが現れる。

【0066】

時刻t3から信号PCRがパルス上にハイレベルになると、短絡スイッチ740によって、演算増幅器760の反転入力端子と出力端子とが短絡される。このとき、演算増幅器760の反転入力端子は、演算増幅器760の仮想接地によりVC0Rの電位になる。つまり、フィードバック容量750の両端がVC0Rにリセットされ、クランプ容量710の端子BもVC0Rになる。時刻t3には信号SHS1、SHS2、SHS3およびSHN1、SHN2、SHN3もハイレベルとなるので、このときの演算増幅器の出力によってサンプリング容量はリセットされる。そして、信号PCRがローレベルになるとクランプ容量の端子Bは電気的浮遊状態となるので、クランプ容量には、FD部106をリセットしたことに対応するレベルと電圧VC0Rとの電圧差が保持される。

【0067】

時刻t4から信号SHN1がパルス状にハイレベルになると、このときの列増幅部AmPの出力が第1の保持容量1010n、1011n、1012nに保持される。第1の保持容量1010n、1011n、1012nに保持される信号には、列増幅部AmPの出

10

20

30

40

50

力オフセットが含まれる。時刻  $t_5$  から信号 R E A D ( n ) がパルス状にハイレベルになると、フォトダイオード 101 に蓄積された電荷が FD 部 106 へと転送される。転送された電荷量に応じて FD 部 106 の電位が変化し、これに対応したレベルが第 1 の垂直信号線 130 に現れる。クランプ容量には、FD 部 106 をリセットしたことに対応するレベルと電圧 P C 0 R との電位差が保持されたままであるので、クランプ容量の端子 B の電位は、FD 部 106 をリセットしたことに対応したレベルと、フォトダイオード 101 から FD 部 106 へと電荷を転送したことに対応するレベルとの差分  $V_{in}$  だけ変化する。実施例 2 で説明したとおり、式 (3) で表すことができる。

## 【0068】

10

時刻  $t_6$  から信号 S H S 1 がハイレベルになり、その後ローレベルになると式 (3) で表される電圧を第 1 の保持容量 1010s に保持する。第 1 の保持容量 1010s に保持される信号には、列信号部 Amp の出力オフセットが含まれる。

## 【0069】

時刻  $t_7$  に信号 S S e l e c t ( n ) がローレベルとなり、n 行目の画素 100 に含まれる増幅トランジスタ 103 と第 1 の垂直信号線 130 とが非導通状態となることで、ソースフォロワ動作が終了する。

## 【0070】

20

一方、時刻  $t_1$  において信号 F B がハイレベルになり、スイッチ 1060s、1060n が導通状態になる。これにより、差動増幅器 1040 の反転入力端子と接続された第 1 の保持容量の電極の電位は V C 1 A m p は差動増幅器 1040 の出力オフセットが重畠されたレベルとなる。

## 【0071】

時刻  $t_8$  において信号 F B がローレベルになり、信号 F B O がハイレベルになる。その後時刻  $t_9$  にて信号 V A D D 1 が、時刻  $t_{10}$  にて信号 S W 2 がハイレベルになる、差動増幅器 1040 の出力端子と第 2 の保持容量が電気的に接続された状態となる。この動作によって、差動増幅器 1040 の出力オフセットが除去された信号が差動増幅器 1040 の出力端子に現れる。時刻  $t_{12}$  以降は実施例 2 と同様に、第 2 の保持容量から水平信号線へ信号が読み出される。

## 【0072】

30

一方で、時刻  $t_{15}$  からは「 $n + 1$ 」行目の読み出しが開始する。時刻  $t_1$  から時刻  $t_7$  で示した「 $n$  行」を行うことにより、「 $n$  行」目の信号を第 2 の保持容量から水平信号線へ読みだす動作の一部を、「 $n + 1$  行」目の信号を第 1 の保持容量に保持する動作が並行して行われる。

## 【0073】

本実施例によれば、画素からの信号を第 1 の保持容量に保持させる第 1 の工程、および第 2 の保持容量に保持された信号を水平出力線に出力する第 2 の工程の少なくとも一部が重複して行われることで、信号出力ない期間が時刻  $t_8$  から時刻  $t_{13}$  までとなり、画素信号の読み出し速度を向上させることができる。

## 【0074】

40

(重み付け加算モード)

次に図 12 のタイミング図を参照しながら、垂直 3 行加算モード、および重み付け加算モードについて説明する。

## 【0075】

時刻  $t_1$  に信号 S e l e c t がハイレベルになると、n 行目の画素に含まれる選択トランジスタが導通状態となり、増幅トランジスタがソースフォロワ動作を行うので、増幅トランジスタのゲート電極の電位すなわち FD 部 106 の電位に対応したレベルが第 1 の垂直信号線に現れる。

## 【0076】

時刻  $t_2$  から信号 R E S E T がパルス状にハイレベルになると、FD 部 106 の電位が

50

電源電圧 V D D に応じてリセットされる。これによって第 1 の垂直信号線およびクランプ容量の端子 A には、F D 部 1 0 6 をリセットしたことに対応するレベルが現れる。

#### 【 0 0 7 7 】

時刻  $t_3$  から信号 P C 0 R がパルス上にハイレベルになると、短絡スイッチ 7 4 0 によって、演算増幅器 7 6 0 の反転入力端子と出力端子とが短絡される。このとき、演算増幅器 7 6 0 の反転入力端子は、演算増幅器 7 6 0 の仮想接地により V C 0 R の電位になる。つまり、フィードバック容量 7 5 0 の両端が V C 0 R にリセットされ、クランプ容量 7 1 0 の端子 B も V C 0 R になる。時刻  $t_3$  には信号 S H S 1 、 S H S 2 、 S H S 3 および S H N 1 、 S H N 2 、 S H N 3 もハイレベルとなるので、このときの演算増幅器の出力によってサンプリング容量はリセットされる。そして、信号 P C 0 R がローレベルになるとクランプ容量の端子 B は電気的浮遊状態となるので、クランプ容量には、F D 1 0 6 をリセットしたことに対応するレベルと電圧 V C 0 R との電圧差が保持される。

#### 【 0 0 7 8 】

時刻  $t_4$  から信号 S H N 1 がパルス状にハイレベルになると、全画素読み出しモードで記載の通り、このときの列増幅部 A m p の出力が第 1 の保持容量 1 0 1 0 n に保持される。時刻  $t_5$  から信号 R E A D ( n ) がパルス状にハイレベルになると、フォトダイオード 1 0 1 に蓄積された電荷が F D 1 0 6 へと転送される。転送された電荷量に応じて F D 1 0 6 の電位が変化し、これに対応したレベルが第 1 の垂直信号線 1 3 0 に現れる。クランプ容量には、F D 1 0 6 をリセットしたことに対応するレベルと電圧 P C 0 R との電位差が保持されたままであるので、クランプ容量の端子 B の電位は、F D 1 0 6 をリセットしたことに対応したレベルと、フォトダイオード 1 0 1 から F D 1 0 6 へと電荷を転送したことに対応するレベルとの差分  $V_{in}$  だけ変化する。実施例 2 で述べたとおり、列増幅部の出力は式 ( 3 ) で表される。

#### 【 0 0 7 9 】

時刻  $t_6$  から信号 S H S 1 がハイレベルになり、その後ローレベルになると式 ( 3 ) で表される電圧をサンプリング容量 1 0 1 0 s に保持する。

#### 【 0 0 8 0 】

時刻  $t_7$  に S S e l e c t がパルス状にハイレベルになり、上述の動作を繰り返すことにより、サンプリング容量 1 0 1 1 n 、 1 0 1 1 s にはそれぞれ、n + 1 行目の画素のリセット信号および光信号が保持される。

#### 【 0 0 8 1 】

時刻  $t_8$  からは同様に n + 2 行目のリセット信号および、光信号が第 1 の保持容量 1 0 1 2 n 、 1 0 1 2 s に保持される。

#### 【 0 0 8 2 】

時刻  $t_9$  において、信号 F B がローレベルになり、信号 F B 0 がハイレベルになる。

#### 【 0 0 8 3 】

その後、時刻  $t_{10}$  にて信号 V A D D 1 、 V A D D 2 、 V A D D 3 がハイレベルになると第 1 の保持容量の電極が電気的に保持されるので、第 1 の保持容量 1 0 1 0 s 、 1 0 1 1 s 、 1 0 1 2 s および、 1 0 1 0 n 、 1 0 1 1 n 、 1 0 1 2 n で保持されている 3 行分の信号がそれぞれ平均化される。また時刻  $t_{11}$  にて、 S W 2 がハイレベルになることで、第 2 の保持容量、 2 6 0 s 、 2 6 1 s にはそれぞれ第 1 の保持容量 1 0 1 0 s 、 1 0 1 1 s 、 1 0 1 2 s の平均化された信号が、 2 6 0 n 、 2 6 1 n にはそれぞれ第 1 の保持容量 1 0 1 0 n 、 1 0 1 1 n 、 1 0 1 2 n の平均化された信号が保持される。

#### 【 0 0 8 4 】

また、時刻  $t_{12}$  では水平方向の画素信号の加算平均、時刻  $t_{13}$  からは水平出力線への信号の読み出しをそれぞれ実施例 1 で述べたものと同様の動作で実施する。一方、全画読み出しモードと同様に、時刻  $t_{14}$  では画素からの信号を第一の保持容量に保持させる第 1 の工程、および第 2 の保持容量に保持された信号を水平出力線に出力する第 2 の工程の少なくとも一部を時間的に並行して実施している。

#### 【 0 0 8 5 】

10

20

30

40

50

本実施例においても、ダミースイッチ 251 を設けることにより、サンプリング容量 260s、261s、260n、261n の容量値が略同一になるよう調整をしている。尚、本実施例においても、サンプリング 262 と 263 で容量値を（サンプリング容量 262 の容量値）<（サンプリング容量 263 の容量値）として、読み出しへスイッチ 250 の接合容量に相当する差分を抑制することもできる。すなわち、2つのサンプリング容量の容量値の差を低減するための容量調整部を設けることにより、重み付け加算を精度よく行うことができ、得られる画像から偽信号を低減することができる。

#### 【0086】

また、本実施例では水平信号容量 290 を増加させないために、ダミースイッチのソース - ドレインをショートさせたが、例えば図 6 に示すよう 1 列分の等価回路の通り、ソースを固定電位に接続するなど、水平信号容量 290 を増加させない構成になっていればよい。

10

#### 【0087】

本実施例によれば、垂直方向の平均化を第 1 の保持容量で行っており、ジャギーを抑制することができる。画素からの信号を第 1 の保持容量に保持させる第一の工程および、第 2 の保持容量に保持された信号を水平出力線に出力する第 3 の工程の少なくとも一部を並行して行う。これにより、同一列の複数の画素からの信号を加算しつつ信号を高速に読み出すことができるので、ジャギーを抑制しつつフレームレートを向上させることが可能となる。

#### 【0088】

20

##### （実施例 4）

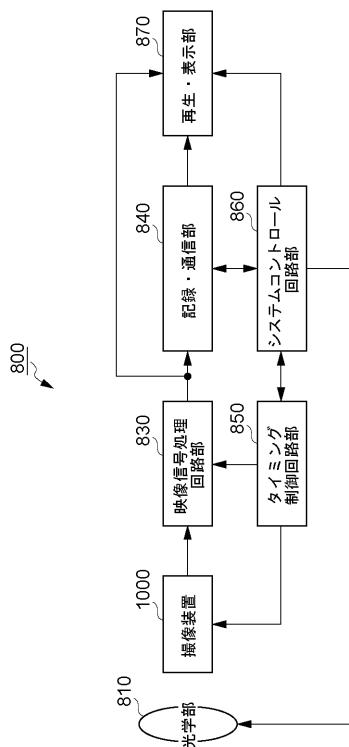

次に、本実施形態に係る撮像システムの概略を、図 13 を用いて説明する。

#### 【0089】

撮像システム 800 は、例えば、光学部 810、撮像装置 1000、映像信号処理回路部 830、記録・通信部 840、タイミング制御回路部 850、システムコントロール回路部 860、および再生・表示部 870 を含む。撮像装置 1000 は、先述の各実施例で説明した光電変換装置が用いられる。ここでは、図 1 に示したタイミングジェネレータ 106 が、撮像装置ではなく、タイミング制御回路部 850 に含まれる場合を例示している。

#### 【0090】

30

レンズなどの光学系である光学部は 810、被写体からの光を撮像装置 1000 の、複数の画素が 2 次元状に配列された画素アレイに結像させ、被写体の像を形成する。撮像装置 1000 は、タイミング制御回路部 850 からの信号に基づくタイミングで、画素部に結像された光に応じた信号を出力する。

#### 【0091】

撮像装置 1000 から出力された信号は、映像信号処理部である映像信号処理回路部 830 に入力され、映像信号処理回路部 830 が、プログラムなどによって定められた方法に従って、入力された電気信号に対して A/D 変換などの処理を行う。映像信号処理回路部での処理によって得られた信号は画像データとして記録・通信部 840 に送られる。記録・通信部 840 は、画像を形成するための信号を再生・表示部 870 に送り、再生・表示部 870 に動画や静止画像が再生・表示させる。記録通信部は、また、映像信号処理回路部 830 からの信号を受けて、システムコントロール回路部 860 とも通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

40

#### 【0092】

システムコントロール回路部 860 は、撮像システムの動作を統括的に制御するものであり、光学部 810、タイミング制御回路部 850、記録・通信部 840、および再生・表示部 870 の駆動を制御する。また、システムコントロール回路部 860 は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラムなどが記録される。また、システムコントロール回路部 860 は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内で供給する。具体的な例

50

としては、読み出す行やリセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらしなどである。

【0093】

タイミング制御回路部850は、制御部であるシステムコントロール回路部860による制御に基づいて撮像装置1000および映像信号処理回路部830の駆動タイミングを制御する。

【0094】

映像信号処理回路部830は、先述の各実施例で説明した補正係数を保持し、撮像装置1000から出力された信号に対して補正処理を行う。

【0095】

以上で説明した各実施例は、本発明を説明するための例示的なものであって、本発明の技術的思想を逸脱しない範囲で様々に変更あるいは組み合わせることが可能である。

10

【符号の説明】

【0096】

110 画素領域

150a、150b 信号処理部

251 ダミースイッチ

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開2010-068123(JP,A)

特開平06-268920(JP,A)

特開2005-333462(JP,A)

特開2005-277709(JP,A)

特開2006-211630(JP,A)

特開2009-182383(JP,A)

特開2009-141631(JP,A)

特開2008-092014(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378