(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2004-7001792   | (65) 공개번호   | 10-2004-0023718 |

| (22) 출원일자   | 2004년02월05일       | (43) 공개일자   | 2004년03월18일     |

| 심사청구일자      | 2004년02월05일       |             |                 |

| 번역문 제출일자    | 2004년02월05일       |             |                 |

| (86) 국제출원번호 | PCT/DE2002/002759 | (87) 국제공개번호 | WO 2003/017374  |

| 국제출원일자      | 2002년07월26일       | 국제공개일자      | 2003년02월27일     |

(30) 우선권주장 10138585.4 2001년08월06일 독일(DE)

(73) 특허권자 인피네온 테크놀로지스 아계

독일, 뮌헨 데-81669, 세인트-마틴-슈트라쎄 53

빌리요셉

독일85521리에메르링프리드리히-프로벨-스트라세62

(74) 대리인 김창세

장성구

김원준

심사관 : 김성회

전체 청구항 수 : 총 8 항

#### (54) 메모리 셀 및 그 프로그래밍 방법

(57) 요약

본 발명은 메모리 셀에 관한 것으로 소스 영역, 드레인 영역, 소스-단 제어 게이트, 드레인-단 제어 게이트, 소스-단 제어 게이트와 드레인-단 제어 게이트 사이에 위치하는 삽입 게이트, 소스-단 제어 게이트에 위치하는 소스-단 기억 소자, 그리고 드레인-단 제어 게이트에 위치하는 드레인-단 기억 소자를 포함한다. 메모리 셀을 프로그래밍 하기 위해서 삽입 게이트에는 낮은 전압을 인가하고 제어 게이트에는 높은 전압을 인가한다.

## 대표도

### 특허청구의 범위

#### 청구항 1.

기판과,

상기 기판 내에 형성된 소스 영역과,

상기 기판 내에 형성된 드레인 영역과,

상기 소스 영역과 상기 드레인 영역 사이에 있으며 가변적 전기 도전성을 갖는 채널 영역과,

상기 소스 영역과 인접한 상기 채널 영역의 소스-단 에지 섹션 위쪽으로 적어도 부분적으로 연장되어 상기 소스-단 에지 섹션의 전기 도전성을 변화시키는 소스-단 제어 게이트와,

상기 드레인 영역과 인접한 상기 채널 영역의 드레인-단 에지 섹션 위쪽으로 적어도 부분적으로 연장되어 상기 드레인-단 에지 섹션의 전기 도전성을 변화시키는 드레인-단 제어 게이트와,

상기 소스-단 제어 게이트와 상기 드레인-단 제어 게이트 사이에 위치하며, 상기 소스-단 제어 게이트 및 상기 드레인-단 제어 게이트와 전기적으로 분리되어 있고, 상기 채널 영역의 중심부 위쪽으로 연장되고, 상기 중심부의 전기 도전성을 변화시키는 삽입 게이트 - 상기 중심부는 상기 채널 영역의 상기 소스-단 에지 섹션과 상기 드레인-단 에지 섹션 사이에서 연장됨 - 와,

적어도 상기 소스-단 에지 섹션과 상기 소스-단 제어 게이트 사이에서 연장되는 소스-단 기억 소자와,

적어도 상기 드레인-단 에지 섹션과 상기 드레인-단 제어 게이트 사이에서 연장되는 드레인-단 기억 소자와,

한편으로는 상기 기판, 다른 한편으로는 상기 소스-단 제어 게이트, 상기 드레인-단 제어 게이트, 그리고 상기 삽입 게이트 사이에서 연장되는 적어도 하나의 게이트 산화물 층을 포함하는 게이트 산화물 구조체를 포함하되,

상기 소스-단 제어 게이트와 상기 드레인-단 제어 게이트는 서로 전기적으로 접속되어 있는

메모리 셀.

## 청구항 2.

제 1 항에 있어서,

상기 기억 소자는 실리콘 질화물을 포함하는 메모리 셀.

## 청구항 3.

제 1 항에 있어서,

상기 기억 소자는 실리콘 이산화물을 포함하는 메모리 셀.

## 청구항 4.

제 1 항에 있어서,

상기 기억 소자는 제 1 실리콘 이산화물 층, 상기 제 1 실리콘 이산화물 층 위에 형성된 실리콘 질화물 층, 상기 실리콘 질화물 층 상에 형성된 제 2 실리콘 이산화물 층으로 이루어진 ONO 층의 일부분(an integrated part)인 메모리 셀.

## 청구항 5.

제 4 항에 있어서,

상기 게이트 산화물 층은 상기 제 1 실리콘 이산화물 층과 일체로 형성되는 메모리 셀.

## 청구항 6.

제 1 항에 있어서,

상기 채널 영역은 n형 채널을 포함하는 메모리 셀.

## 청구항 7.

제 1 항에 있어서,

상기 채널 영역은 p형 채널을 포함하는 메모리 셀.

## 청구항 8.

제 1 항 내지 제 7 항 중 어느 하나의 항에 따른 메모리 셀을 프로그래밍하는 방법에 있어서,

소정 소스 전압 값을 갖는 소스 전압이 상기 소스 영역에 인가되고, 소정 드레인 전압 값을 갖는 드레인 전압이 상기 드레인 영역에 인가되되, 상기 소스 전압 값과 상기 드레인 전압 값이 다르며,

소정 삽입 게이트 전압 값을 갖는 삽입 게이트 전압이 상기 삽입 게이트에 인가되고,

소정 소스-제어-게이트 전압 값을 갖는 소스-제어-게이트 전압이 상기 소스-단 제어 게이트에 인가되고, 소정 드레인-제어-게이트 전압 값을 갖는 드레인-제어-게이트 전압이 상기 드레인-단 제어 게이트에 인가되고,

상기 소스-제어-게이트 전압 값을 갖는 드레인-제어-게이트 전압과 동일하며, 상기 삽입 게이트 전압 값 보다 더 큰 절대값을 갖는

프로그래밍 방법.

## 청구항 9.

삭제

## 청구항 10.

삭제

명세서

### 기술분야

본 발명은 메모리 셀에 관한 것이다.

### 배경기술

메모리 어레이를 구비한 컴퓨터는 메인 프레임 컴퓨터, 퍼스널 컴퓨터를 포함하여 매우 다양한 용도로 사용되고 있으며 세탁기, 주방기구, 자동차, 전화기, 자동 응답기 또는 기타 용도로도 사용되고 있다. 여기에서, 컴퓨터는 가장 넓은 의미로 전자적 제어 장치 그리고/또는 계산 장치로 이해해야 한다.

컴퓨터의 메모리 장치는 컴퓨터를 동작시키는 데 필요한, 예를 들어 파라미터와 같은 데이터나 컴퓨터가 동작하는 동안 컴퓨터에 의해 생성된 계산 결과를 영구적으로 또는 일시적으로 저장하는 데 이용된다.

메모리 장치는 적어도 하나의 메모리 셀, 일반적으로는 다수의 메모리 셀을 갖는 메모리를 포함한다. 각각의 메모리 셀은 메모리 셀의 메모리 내용을 설정하기 위하여 다량의 전기적 전하가 저장될 수 있는 기억 소자를 포함한다.

메모리 셀에는 휘발성 메모리 셀과 비휘발성 메모리 셀이 있다. 휘발성 메모리 셀에서는 기억 소자에 저장된 메모리 내용이 일반적으로 기억 소자에 약 일초 동안만 남아 있다. 따라서, 메모리 내용은 주기적으로 갱신되어야 한다. 비휘발성 메모리 셀에서는 기억 소자에 저장된 메모리 내용이 메모리 소자에 수 년 단위의 저장 시간 동안 지속적으로 남아 있다.

MOSFET(metal oxide semiconductor field effect transistor) 기반의 비휘발성 메모리 셀은 소스 영역, 드레인 영역, 소스 영역과 드레인 영역 사이에 배열된 채널 영역, 채널 영역을 제어하기 위해 배열된 게이트 전극(제어 게이트), 그리고 게이트 전극(제어 게이트)과 채널 영역 사이에 배열된 게이트 산화물 층을 포함하는 모스펫을 기반으로 한다.

MOSFET 기반의 비휘발성 메모리 셀에서 게이트 전극은 제어 게이트로 사용된다. 메모리 셀의 메모리 내용을 저장하기 위한 기억 소자는 채널 영역 위쪽의 제어 게이트와 게이트 산화물 층 사이에 제공된다. 기억 소자는 채널 영역과 제어 게이트 모두에 대해서 전압 차(a potential barrier)를 갖는다. 절대값에 있어서 충분히 높고 적절한 전압이 제어 게이트에 인가되면, 그 결과로 채널 영역으로부터 기억 소자로 전기적 전하 캐리어가 충전될 수 있거나 기억 소자로부터 채널 영역으로 방전될 수 있다. 그 결과, 메모리 셀의 메모리 내용은 프로그램되거나 삭제된다.

비휘발성 메모리의 한 예가 EEPROM(electrically erasable programmable read only memory)이다. EEPROM에서 프로그램된 메모리 내용은 전기적 전압을 인가함으로써 지워질 수 있다.

MOSFET 기반의 비휘발성 메모리 셀은 설계하기에 따라 플로우팅 게이트 메모리 셀과 MIOS(metal insulator oxide semiconductor) 메모리 셀이 있다.

플로우팅 게이트 메모리 셀에서는 기억 소자가 금속적으로 도전성 있는 플로우팅 게이트에 의해 형성된다.

MIOS 메모리 셀에서는 기억 소자가 (적어도) 하나의 절연 물질로 이루어진 절연체 기억 소자로부터 형성된다. 기억 소자의 메모리 내용은 절연체 기억 소자에 트래핑된(trapped) 다양한 전기적 전하 캐리어의 전하에 의해 형성된다.

MOSFET 기반의 메모리 셀을 프로그램하기 위해서는 MOSFET의 채널 영역에 전류를 유지하는 것이 필요하다.

메모리 셀을 효율적으로 이용하고 동작시키기 위해서 메모리 셀이 프로그램될 때 전력의 소비를 줄이는 노력이 행해진다.

선행문헌 [1]은 플로우팅 게이트 메모리 셀을 개시하고 있다. 선행문헌 [1]의 메모리 셀은 소스 영역, 드레인 영역, 채널 영역, 플로우팅 게이트를 갖는 기억 소자 어레이, 기억소자 어레이 위에 배치된 제어 게이트, 기억 소자 어레이 옆에 제공되는 소스-단 측면 선택 게이트를 포함한다. 선행문헌 [1]의 메모리 셀을 프로그램하기 위해서는, 선택 게이트에 비교적 낮은 전압을 인가하여 채널 영역에 전류의 적은 전기적 흐름을 만든다. 제어 게이트에는 전기적 전하 캐리어를 플로우팅 게이트에 충전시킬 만큼 충분히 높은 전기적 전압을 인가한다. 선행 문헌 [1]의 메모리 셀에서는 선택 게이트에 인가된 전기적 전압이 플로우팅 게이트를 충전시키기에 필요한 전압보다 상당히 낮을 수 있다. 그 결과로, 선택 게이트가 없는 플로우팅 게이트 메모리 셀 보다 낮은 전류를 이용하여 프로그램할 수 있다. 반면에 선택 게이트를 위한 전압은 전기적 전하 캐리어가 소스 영역으로부터 채널 영역에 전달되어 연속적인 도전성 채널이 소스 영역과 드레인 영역 사이에 형성되도록 반드시 충분히 크게 선택해야 한다.

이와 달리, 메모리 셀 또는 메모리 셀 어레이의 효율을 높이기 위해서 가능한 가장 높은 집적도를 달성하기 위하여, 즉 단위 면적 또는 단위 부피당 개별적인 메모리 내용 아이템을 가능한 많이 수용하기 위하여 여러가지 시도가 행해진다.

일반적으로 각각의 개별 메모리 셀의 구조의 크기를 줄이는 것은 이러한 목적을 위한 것이다.

선행문헌 [2]에는 제 1 ONO 저장 층과 소스 영역 위쪽에 위치하는 제 1 게이트 영역 섹션, 제 2 ONO 저장 층과 드레인 영역 위쪽에 위치하는 제 2 게이트 영역 섹션, 그리고 채널 영역과 게이트 절연 층 위쪽에 위치하는 제 3 게이트 영역 섹션이 제공되며, 제 1, 제 2, 그리고 제 3 게이트 영역 섹션은 서로 전기적으로 접속되어 있는 비휘발성 반도체 메모리가 기재되어 있다.

뿐만 아니라, 선행문헌 [3](출원일: 2000년 7월 28일, 공개일: 2002년 2월 14일)은 하나는 소스 영역과 인접하고 다른 하나는 드레인 영역과 인접하는 2개의 ONO 저장 층을 갖는 메모리 셀을 제안한다. 채널 영역의 도전성은 채널 영역 위에 배열된 게이트 영역과 접속 라인으로 게이트 영역과 접속된 2개의 측면 게이트 소자에 의해서 제어되며, 게이트 절연층이 채널 영역과 게이트 영역 사이에 위치한다.

본 발명은 전류의 측면에서 경제적이고, 효율적이며 신뢰성이 높은 메모리 셀을 제공하고자 한다.

### 발명의 상세한 설명

상기 문제점은 독립 특허 청구항에 따른 특징을 갖는 메모리 셀에 의해 해결된다.

기판과, 기판 내에 형성된 소스 영역과, 기판 내에 형성된 드레인 영역과, 소스 영역과 드레인 영역 사이에 있으며 가변적 전기 도전성을 갖는 채널 영역과, 소스 영역과 인접한 채널 영역의 소스-단 에지 섹션 위쪽으로 적어도 부분적으로 연장되며 소스-단 에지 섹션의 전기 도전성을 변화시키는 소스-단 제어 게이트와, 드레인 영역과 인접한 채널 영역의 드레인-단 에지 섹션 위쪽으로 적어도 부분적으로 연장되며 드레인-단 에지 섹션의 전기 도전성을 변화시키는 드레인-단 제어 게이트와, 소스-단 제어 게이트와 드레인-단 제어 게이트 사이에 위치하며, 채널 영역의 중심부 위쪽으로 연장되고 중심부의 전기 도전성을 변화시키는 삽입 게이트 - 중심부는 채널 영역의 소스-단 에지 섹션과 드레인-단 에지 섹션 사이에서 연장됨 - 와, 적어도 소스-단 에지 섹션과 소스-단 제어 게이트 사이에서 연장되는 소스-단 기억 소자와, 적어도 드레인-단 에지 섹션과 드레인-단 제어 게이트 사이에서 연장되는 드레인-단 기억 소자와, 한편으로는 기판, 다른 한편으로는 소스-단 제어 게이트, 드레인-단 제어 게이트, 그리고 삽입 게이트 사이에서 연장되는 적어도 하나의 게이트 산화물 층을 포함하는 게이트 산화물 구조체를 포함하는 메모리 셀이 제공된다.

이에 따라, 개별적인 메모리 내용을 저장하는 것이 가능하며, 따라서 일 비트의 데이터를 각각 소스-단 기억 소자와 드레인-단 기억 소자에 저장하는 것이 가능하다. 이러한 방법으로 메모리 셀의 저장 용량이 단지 하나의 기억 소자를 갖는 메모리 셀의 저장 용량과 비교하여 2배가 된다.

또한 메모리 셀은 전류의 측면에서 경제적인 방법으로 신뢰성 있게 프로그램될 수 있다.

메모리 셀은 다음의 방법에 따라 프로그램된다.

소정 소스 전압 값을 갖는 (전기적) 소스 전압을 소스 영역에 인가한다. 소정 드레인 전압 값을 갖는 (전기적) 드레인 전압을 드레인 영역에 인가한다. 여기서 소스 전압 값과 드레인 전압 값은 서로 다르다. 소스 영역과 드레인 영역 사이에는 소스 전압 값과 드레인 전압 값 사이의 차이 만큼에 해당하는 소스 드레인 전압이 있다.

소정 삽입 게이트 전압 값을 갖는 전기적 삽입 게이트 전압을 삽입 게이트에 인가한다. 소정 소스-제어-게이트 전압 값을 갖는 전기적 소스-제어-게이트 전압을 소스-단 제어 게이트에 인가한다. 소정 드레인-제어-게이트 전압 값을 갖는 전기적 드레인-제어-게이트 전압을 드레인-단 제어 게이트에 인가한다. 여기서, 소스-제어-게이트 전압 값과 드레인-제어-게이트 전압 값은 절대값에 있어서 삽입 게이트 전압 값보다 각각 크다.

여기서 소스-제어-게이트 전압 값과 드레인-제어-게이트 전압 값은 같을 수도 있다.

드레인-단 기억 소자를 프로그램하기 위해서는 적절한 전기적 전압을 소스 영역과 드레인 영역 사이에 인가한다. 소스-단 제어 게이트에 의해 전기적 전하 캐리어가 소스 영역으로부터 소스-단 제어 게이트의 아래쪽에 있는 채널 영역의 소스-단 에지 셕션으로 충전된다. 이를 위하여, 절대값이 비교적 높은 전기적 전압을 소스-단 제어 게이트에 인가하는데, 이 경우 소스-단 기억 소자로의 전하 캐리어의 터널 작용은 아직 발생하지 않는다. 이어서, 절대값이 비교적 낮은 전기적 전압을 삽입 게이트에 인가한다. 따라서, 적은 수의 전기적 전하 캐리어만이 채널 영역의 중심부를 지나므로 매우 낮은 전기적 전류가 채널 영역의 중심부에 흐른다. 전기적 전하 캐리어를 드레인-단 기억 소자에 충전시킬 만큼 충분히 높은 전기적 전압을 드레인-단 제어 게이트에 인가한다. 결과적으로, 채널 영역의 중심부에서는 낮은 전기적 전류로 인하여 적은 양의 전력이 소모된다 (전력 = 전류 x 전압).

메모리 셀 내에서는 소스-단 제어 게이트로 인하여, 소스 영역과 드레인 영역 사이의 채널 영역에서 전기적 전류의 흐름이 방해받지 않도록 하면서 동시에 채널 영역 중심부의 전기적 전류를 특히 작게 선택할 수 있다. 따라서 메모리 셀을 전류의 측면에서 특히 경제적인 방법으로 프로그램할 수 있다.

소스-단 기억 소자를 프로그램하기 위해서는 소스 영역과 드레인 영역 사이에 적절한 전기적 소스 드레인 전압을 인가하는데, 이 소스-드레인 전압은 드레인-단 기억 소자를 프로그래밍하기 위한 소스 드레인 전압과 반대의 극성을 가지지만 절대값에 있어서는 같은 크기일 수 있다. 소스 드레인 전압은 절대값에 있어서 동일할 수도 있지만, 드레인-단 기억 소자를 프로그래밍하기 위한 전압과 동일하도록 다른 전압을 선택할 수도 있다.

소스-단 기억 소자를 프로그래밍할 때 특히 적은 전력이 삽입 게이트에 의해 소모된다.

기억 소자는 실리콘 질화물을 포함할 수 있다.

이와 달리, 또는 이에 덧붙여, 기억 소자는 실리콘 이산화물 또는 다른 적당한 절연 물질을 포함할 수 있다.

기억 소자는 제 1 실리콘 이산화물 층, 제 1 실리콘 이산화물 층 위에 형성된 실리콘 질화물 층, 그리고 실리콘 질화물 층 위에 형성된 제 2 실리콘 이산화물 층으로 이루어진 ONO 층의 일부분(an integrated part)일 수 있다.

게이트 산화물 층과 제 1 실리콘 이산화물 층은 별개의 층으로 형성될 수 있다. 이와 달리, 게이트 산화물 층은 제 1 실리콘 이산화물 층과 일체로 형성될 수도 있다.

소스-단 제어 게이트와 드레인-단 제어 게이트에 대한 컨택트가 개별적으로 형성될 수 있다. 이는 소스-단 제어 게이트와 드레인-단 제어 게이트에 다른 전기적 전압이 인가되어야 할 경우 유리하다.

소스-단 제어 게이트와 드레인-단 제어 게이트는 서로 전기적으로 접속되는 것이 바람직하다. 이 경우, 소스-단 제어 게이트와 드레인-단 제어 게이트에 각각의 전압을 인가하는 데는 전체적으로 하나의 전압원만이 필요하다. 게다가 이런 방법으로 특히 간단하고 효율적으로 메모리 셀을 프로그래밍할 수 있다. 예를 들어, 드레인-단 기억 소자를 먼저 프로그래밍할 수 있고, 이후 소스 드레인 전압의 극성을 반전시킬 수 있으며, 그 뒤에는 이미 기술한 바와 같이 소스-단 기억 소자를 다른 변경 사항 없이 프로그래밍할 수 있다. 이와 달리, 소스-단 기억 소자를 먼저 프로그래밍한 후 드레인-단 기억 소자를 프로그래밍할 수 있다.

채널 영역은 n-형 채널을 포함할 수 있다. 이와 달리, 채널 영역은 p-형 채널을 포함할 수도 있다.

EEPROM으로 구현되는 본 발명에 따른 메모리 어레이는 전술한 방법으로 만들어진 적어도 하나의 메모리 셀을 포함한다.

### 실시예

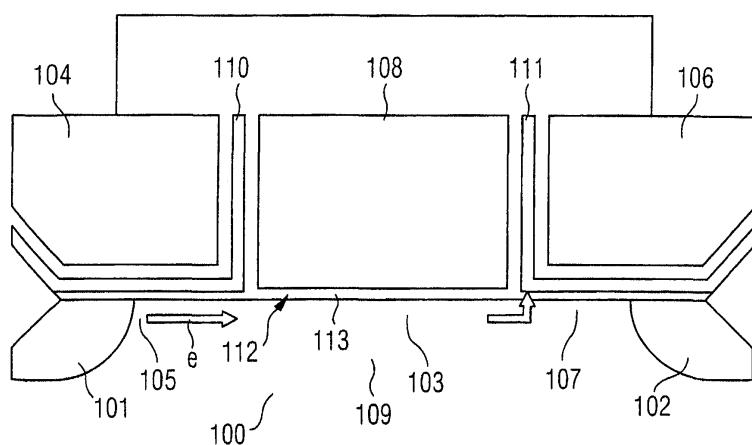

도 1은 본 발명의 제 1 실시예에 따라 드레인-단 기억 소자가 프로그래밍되는 메모리 셀을 도시하고 있다.

도 1의 메모리 셀은 기판(100), 기판(100) 내에 형성된 n<sup>+</sup> 형으로 도핑된 소스 영역(101), 기판(100) 내에 형성된 n<sup>+</sup> 형으로 도핑된 드레인 영역(102), 그리고 소스 영역(101)과 드레인 영역(102) 사이에 있으며 가변적 전기 도전성을 갖는 n형 채널 영역(103)을 포함한다.

또한 메모리 셀은 소스 영역(101)과 인접한 채널 영역(103)의 소스-단 에지 섹션(105) 위쪽으로 적어도 부분적으로 연장되며 소스-단 에지 섹션(105)의 전기 도전성을 변화시키는 소스-단 제어 게이트(104)를 포함한다.

또한 메모리 셀은 드레인 영역(102)과 인접한 채널 영역(103)의 드레인-단 에지 섹션(107) 위쪽으로 적어도 부분적으로 연장되며 드레인-단 에지 섹션(107)의 전기 도전성을 변화시키는 드레인-단 제어 게이트(106)를 포함한다.

채널 영역(103)의 중심부(109) 위쪽으로 연장되며 중심부(109)의 전기 도전성을 변화시키도록 되어 있는 삽입 게이트(108)가 소스-단 제어 게이트(104)와 드레인-단 제어 게이트(106) 사이에 위치한다. 여기서 중심부(109)는 채널 영역(103)의 소스-단 에지 섹션(105)과 드레인-단 에지 섹션(107) 사이에서 연장된다.

그리고 메모리 셀은 한편으로는 소스-단 제어 게이트(104), 다른 한편으로는 삽입 게이트(108), 소스-단 에지 섹션(105), 그리고 소스 영역(101) 사이로 연장되는 실리콘 질화물로 구성된 소스-단 기억 소자(110)를 포함한다.

또한, 메모리 셀은 한편으로는 드레인-단 제어 게이트(106), 다른 한편으로는 삽입 게이트(108), 드레인-단 에지 섹션(107), 그리고 드레인 영역(102) 사이로 연장되는 실리콘 질화물로 구성된 드레인-단 기억 소자(111)를 포함한다.

메모리 셀은 또한 실리콘 이산화물로 구성된 게이트 산화물 구조체(112)를 포함한다. 게이트 산화물 구조체(112)는 한편으로는 기판(100), 다른 한편으로는 소스-단 제어 게이트(104), 드레인-단 제어 게이트(106), 그리고 삽입 게이트(108) 사이로 연장되는 게이트 산화물 층(113)을 포함한다. 실리콘 이산화물로 구성된 층이 소스-단 제어 게이트(104)와 소스-단 기억 소자(110) 사이, 소스-단 기억 소자(110)와 삽입 게이트(108) 사이, 삽입 게이트(108)와 드레인-단 기억 소자(111) 사이, 그리고 드레인-단 기억 소자(111)와 드레인-단 제어 게이트(106) 사이에 각각 제공되며, 실리콘 이산화물로 구성된 이 층은 게이트 산화물 구조체(112)의 일부분을 형성하며, 게이트 산화물 층(113)과 일체를 이루며 형성된다.

드레인-단 기억 소자(106)를 프로그래밍하는 프로세스가 후술된다.

0 V의 전기적 전압을 소스 영역(101)에 인가한다. 5 V의 전기적 전압을 드레인 영역에 인가한다. 공통의 전압원으로 10 V의 전기적 전압을 소스-단 제어 게이트(104)와 드레인-단 제어 게이트(105)에 인가한다. 1.5 V의 전기적 전압을 삽입 게이트(108)에 인가한다. 그 결과 전기적 전하 캐리어(전자)가 소스 영역(101)으로부터 채널 영역(103)의 소스-단 에지 섹션(105)으로 주입된다. 삽입 게이트(108)에 상대적으로 낮은 전압이 걸려 있으므로 채널 영역(103)의 중심부(109)에는 낮은 전류만이 흐른다. 드레인-단 제어 게이트(106)에 높은 전압이 걸려 있으므로 전기적 전하 캐리어(전자)는 드레인-단 기억 소자(111)에 충전되어 그곳에 트래핑되게 된다.

본 발명의 다른 실시예에 따른 메모리 셀은  $p^+$  형으로 도핑된 소스 영역,  $p^+$  형으로 도핑된 드레인 영역, 그리고 소스 영역과 드레인 영역 사이에서 가변적 전기 도전성을 갖는  $p$  형 채널 영역을 포함한다.

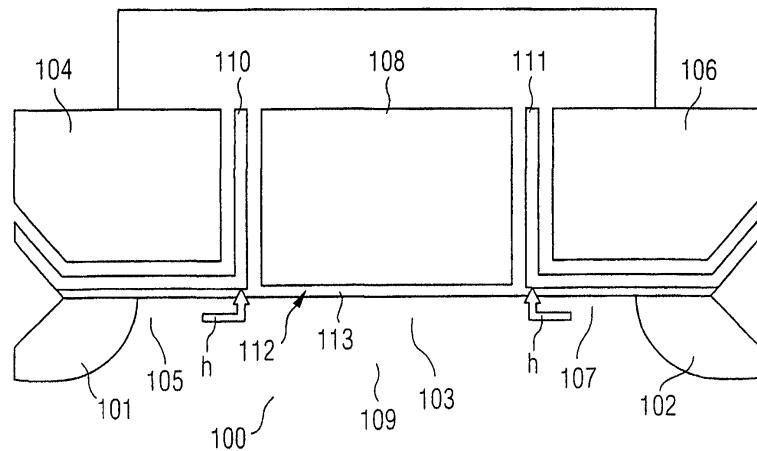

도 2는 소스-단 기억 소자(110)의 메모리 내용과 드레인-단 기억 소자(111)의 메모리 내용이 지워지는 도 1의 메모리 셀을 도시하고 있다.

5 V의 동일한 양의 전기적 전압을 소스 영역(101)과 드레인 영역(102)에 인가한다. -5 V의 동일한 음의 전기적 전압을 소스-단 제어 게이트(104)와 드레인-단 제어 게이트(106)에 인가한다. 0 V의 전기적 전압을 삽입 게이트(108)에 인가한다. 그 결과로, 정공(hole)이 채널 영역(103)으로부터 소스-단 기억 소자(110)로 충전된다. 이 정공은 소스-단 기억 소자(110)에 트래핑되어 있던 음의 전기적 전하 캐리어와 재결합한다. 그 결과로, 소스-단 기억 소자(110)에 불잡혀 있던 음의 전하 캐리어의 음의 전기적 전하는 상보되고, 따라서 소스-단 기억 소자(110)에 있던 메모리 내용이 지워지게 된다. 이와 유사한 방식으로, 정공이 채널 영역(103)으로부터 드레인-단 기억 소자(111)로 충전된다. 그 결과로 드레인-단 기억 소자(111)에 트래핑되어 있던 전기적 전하 캐리어의 음의 전기적 전하가 상보되고, 따라서 드레인-단 기억 소자(111)에 저장되어 있던 메모리 내용이 지워지게 된다. 기억 소자(110, 111)의 방전을 돋기 위하여 이전과는 달리 음의 전기적 전압을 삽입 게이트(108)에 인가할 수도 있다.

소스-단 기억 소자(110)에 저장된 메모리 내용(비트)을 읽어 내기 위해서는 1.2 V의 전기적 전압을 소스 영역(101, 0 V)과 드레인 영역(102, 1.2 V) 사이에 인가할 수 있다. 이후, 약 2 V의 전압을 소스-단 제어 게이트(104), 드레인-단 제어 게이트(106), 그리고 삽입 게이트(108)에 각각 인가한다. 드레인-단 기억 소자(111)에 저장된 메모리 내용(비트)을 읽어 내기 위해서는 -1.2 V의 전기적 전압을 소스 영역(101, 1.2 V)과 드레인 영역(102, 0 V) 사이에 인가한다. 소스-단 제어 게이트(104), 드레인-단 제어 게이트(106), 그리고 삽입 게이트(108)에 걸린 전압은 역시 2 V이며, 즉, 소스 드레인 전압의 극성만이 바뀐다.

다음의 표 1은 메모리 셀의 다른 소자에 인가되는 일반적인 전기적 전압을 표시하고 있는데, 이 전기적 전압은 메모리 셀의 프로그래밍, 소거 또는 판독을 위해 주어진 조합에 있어서 적절한 것이다.

[표 1]

|                    | 프로그래밍<br>드레인<br>111 | 프로그래밍<br>소스<br>110 | 소거   | 판독<br>소스<br>110 | 판독<br>드레인<br>111 |

|--------------------|---------------------|--------------------|------|-----------------|------------------|

| 드레인<br>102         | +5 V                | 0 V                | +5 V | +1, 2 V         | 0 V              |

| 제어 게이트<br>104, 106 | +10 V               | +10 V              | -5 V | +2 V            | +2 V             |

| 삽입 게이트<br>108      | +1, 5 V             | +1, 5 V            | 0 V  | +2 V            | +2 V             |

| 소스<br>101          | 0 V                 | +5 V               | +5 V | 0 V             | +1, 2 V          |

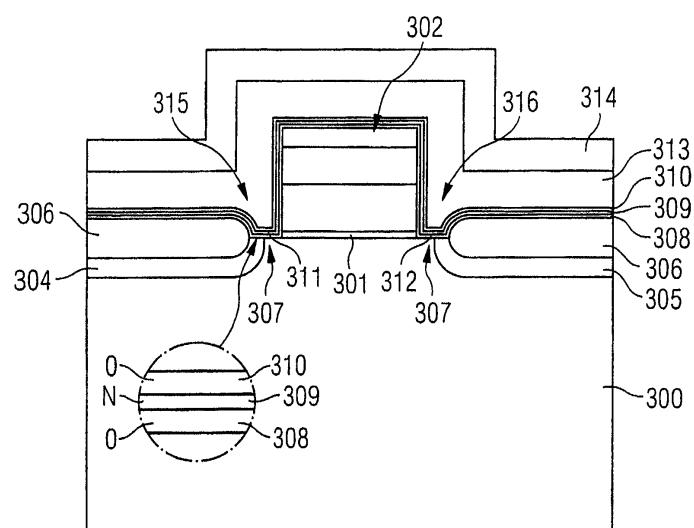

본 발명에 따른 메모리 셀을 제작하는 방법은 도 3a 내지 도 3f를 참조하여 아래 설명될 것이다.

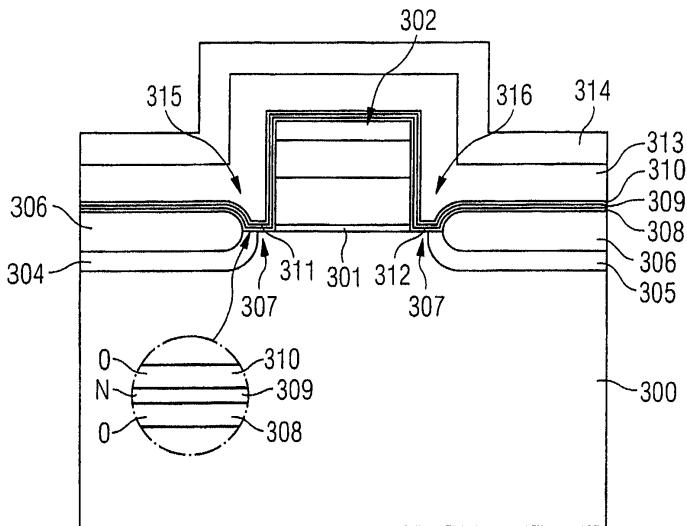

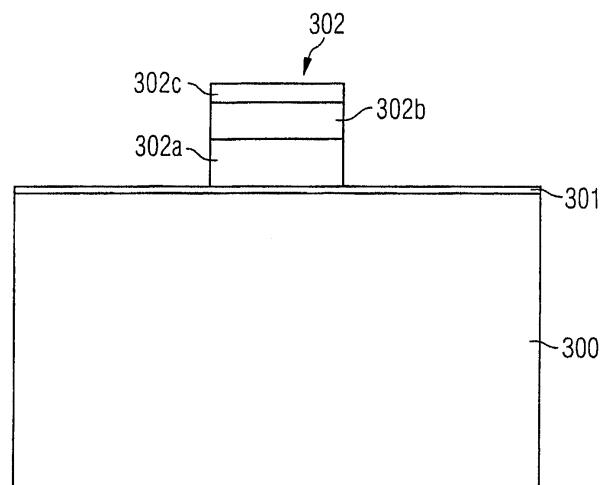

도 3a는 본 발명의 제 2 실시예에 따른 메모리 셀의 제작 과정 중 제 1 제작 상태의 단면을 도시하고 있다.

$p$  형 기판(300)이 메모리 셀을 위한 시작 재료로서 사용된다. 10 nm 두께의 게이트 산화물 층(301)을 기판(300) 위에 형성한다. 폴리실리콘(302a), 텅스텐 실리사이드(302b), TEOS(tetra-ethyl-ortho-silicate, 302c)의 연속적인 순서의 층을 갖는 삽입 게이트 층을 게이트 산화물 층(301) 위에 형성한다. 삽입 게이트 층은 포토리소그래피에 의해 패터닝하고(삽입 게이트 층의 포토리소그래피와 곧이은 에칭), 포토리소그래피 레지스트를 제거하여 삽입 게이트(302)를 형성함으로써 도 3a에 도시된 구조를 형성한다.

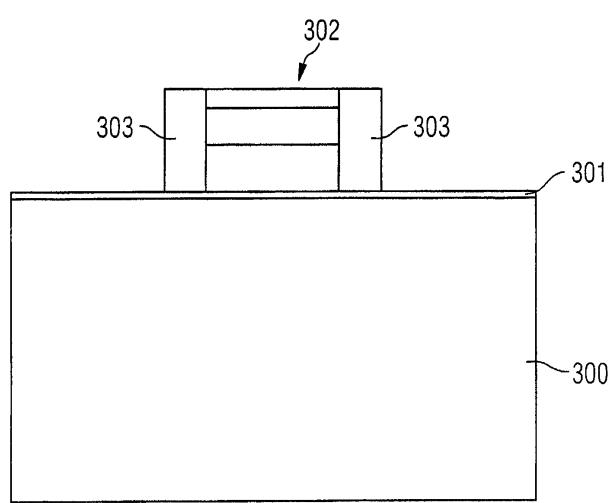

그 다음, 도 3b에 도시된 바와 같이, 실리콘 질화물 층을 도 3a에 도시된 구조 위에 증착한다.

실리콘 질화물 층을 백 에칭하여 질화물 스페이서(303)를 삽입 게이트(302)의 측면에 남김으로써 도 3b에 도시된 구조를 형성한다.

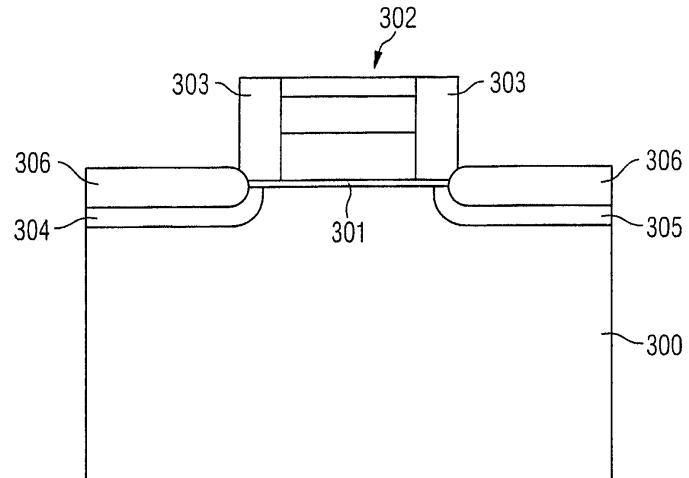

도 3b에 도시된 구조 위에 비소 이온 주입 단계를 수행하여 도 3c에 도시된 바와 같이 소스 영역(304)과 드레인 영역(305)을 형성한다. 채널 영역은 소스 영역(304)과 드레인 영역(305) 사이에 위치한다. 각각의 경우, 산화 공정에 의해 두꺼운 산화물(306)로 구성된 층은 소스 영역(304)과 드레인 영역(305) 위에 형성하여 도 3c에 도시된 구조를 형성한다.

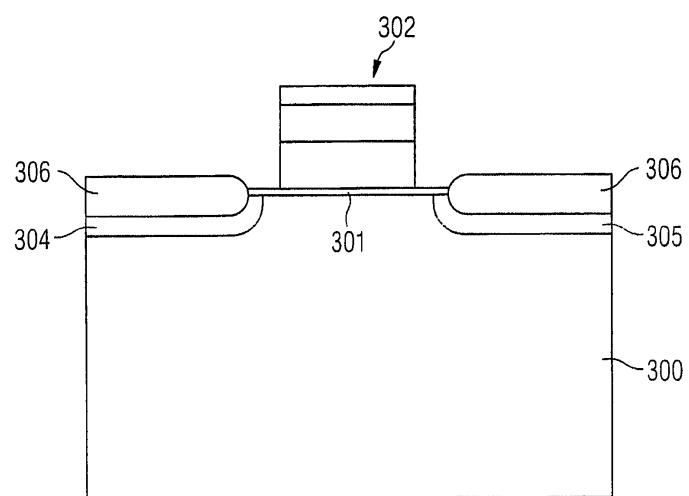

이후 습식 에칭에 의해 질화물 스페이서(303)를 제거한다. 이 습식 에칭 공정에서는 실리콘 이산화물 층이 에칭 정지막으로 작용하므로 게이트 산화물 층(301)은 에칭되지 않고 도 3d에 도시된 구조가 형성된다.

도 3e에 도시된 바와 같이, 도 3d에 도시된 구조에서 시작하여 게이트 산화물 층(301)을 삽입 게이트(302) 옆의 영역(307)에서 제거하는 (두꺼운 산화물(306)도 얇아지는) 실리콘 이산화물 에칭 단계를 먼저 수행한다. 이후, 실리콘 이산화물로 구성된 하부 산화물 층(308)을 미완성된 구조의 표면 위에 형성한다. 실리콘 질화물로 구성된 기억 소자 층(309)을 하부 산화물 층(308) 위에 형성한다. 실리콘 이산화물로 구성된 상부 산화물 층(310)을 기억 소자 층(309) 위에 형성한다. 하부 산화물 층(308), 기억 소자 층(309), 그리고 상부 산화물 층(310)이 삽입 게이트(302) 옆의 영역(307) 각각에 ONO 층(ONO = Oxide-Nitride-Oxide)을 형성하여, 소스-단 기억 소자(311)와 드레인-단 기억 소자(312)를 형성한다. 소스-단 기억 소자(311)와 드레인-단 기억 소자(312)는 각각 실리콘 질화물로 구성된 기억 소자 층(309)으로부터 형성되어 한쪽은 하부 산화물 층(308)에, 다른 한쪽은 상부 산화물 층(310)에 접해 있다.

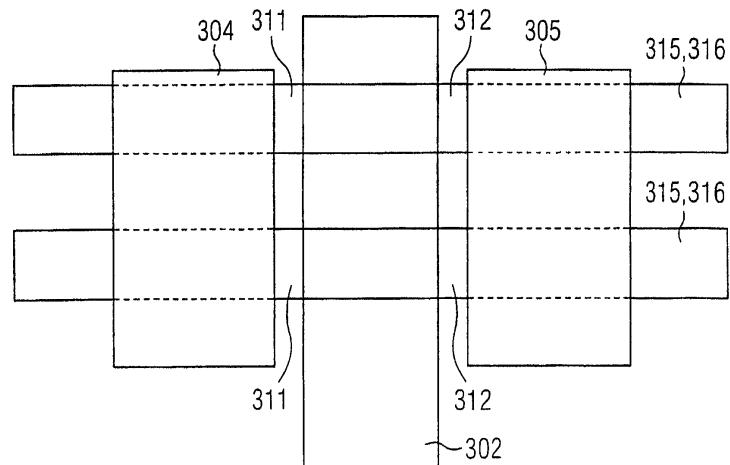

인시츄 도핑(in situ doping) 폴리실리콘 층(313)을 상부 산화물 층(310) 위에 형성한다. 텅스텐 실리사이드 층(314)을 폴리실리콘 층(313) 위에 형성한다. 폴리실리콘 층(313)과 텅스텐 실리사이드 층(314)을 포토리소그래피로 패터닝하고 (층(313, 314)의 포토리소그래피와 곧이은 에칭), 이후 포토리소그래피 레지스트를 제거한다. 이러한 방식으로 소스-단 제어 게이트(315)와 드레인-단 제어 게이트(316)를 폴리실리콘 층(316)과 텅스텐 층(314)으로부터 형성한다. 소스-단 제어 게이트(315)와 드레인-단 제어 게이트(316)는 서로 전기적으로 접속된다.

도 3e는 완성된 메모리 셀의 단면을 도시하고 있다.

도 3f는 보다 명확하게 하기 위하여 본 발명에 따라 도 3e에 도시된 것과 같은 메모리 셀 2 개를 서로 이웃하게 배치한 것을 도시하고 있다.

본 발명에 따른 메모리 셀의 다른 실시예에 있어서, 기판(100, 300)은 n형 기판이다. 이 경우, 채널 영역은 p형 채널을 포함한다. 본 상세한 설명은 다음의 문서를 인용한다.

선행문헌 [1] K. Naruke, S. Yamada, E. Obi, S. Taguchi and M. Wada, "A new flash-erase EEPROM cell with a sidewall select-gate on its source side", Tech. Digest, 1989, IEDM. pp. 25.7.1-25.7.4

선행문헌 [2] US 6,335,554 B1

선행문헌 [3] DE 10036911 A1

도면 부호 목록

도 1

100 기판

101 소스 영역

102 드레인 영역

103 채널 영역

104 소스-단 제어 게이트

105 채널 영역(103)의 소스-단 에지 셙션

106 드레인-단 제어 게이트

107 채널 영역(103)의 드레인-단 에지 셙션

108 삽입 게이트

109 채널 영역(103)의 중심부

110 소스-단 기억 소자

111 드레인-단 기억 소자

112 게이트 산화물 구조체

113 게이트 산화물 층

도 3

300 기판

301 게이트 산화물 층

302 삽입 게이트:

302a 폴리실리콘

302b 텅스텐

302c TEOS

303 질화물 스페이서

304 소스 영역

305 드레인 영역

306 두꺼운 산화물

307 삽입 게이트의 옆 영역

308 하부 산화물 층

309 기억 소자 층

310 상부 산화물 층

311 소스-단 기억 소자

312 드레인-단 기억 소자

313 폴리실리콘 층

314 텅스텐 층

315 소스-단 제어 게이트

316 드레인-단 제어 게이트

### 도면의 간단한 설명

본 발명의 예시적인 실시예는 도면에서 설명되며 이후 더 자세히 설명될 것이다.

도 1은 본 발명의 제 1 실시예에 따라 드레인-단 기억 소자가 프로그래밍되는 메모리 셀을 도시한 것이고,

도 2는 소스-단 기억 소자의 메모리 내용과 드레인-단 기억 소자의 메모리 내용이 지워지는 도 1의 메모리 셀을 도시한 것이고,

도 3a는 본 발명의 제 2 실시예에 따른 메모리 셀의 제작 과정 중 제 1 제작 상태의 단면을 도시한 것이고,

도 3b는 본 발명의 제 2 실시예에 따른 메모리 셀의 제작 과정 중 제 2 제작 상태의 단면을 도시한 것이고,

도 3c는 본 발명의 제 2 실시예에 따른 메모리 셀의 제작 과정 중 제 3 제작 상태의 단면을 도시한 것이고,

도 3d는 본 발명의 제 2 실시예에 따른 메모리 셀의 제작 과정 중 제 4 제작 상태의 단면을 도시한 것이고,

도 3e는 본 발명의 제 2 실시예에 따른 메모리 셀의 최종 제작 상태의 단면을 도시한 것이고,

도 3f는 도 3e에 도시된 것과 같은 본 발명에 따른 2 개의 메모리 셀을 도시한 것이다.

### 도면

도면1

도면2

도면3a

도면3b

도면3c

도면3d

도면3e

도면3f