(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5815661号 (P5815661)

(45) 発行日 平成27年11月17日(2015.11.17)

(24) 登録日 平成27年10月2日(2015.10.2)

(51) Int.Cl. F I GO5B 19/18 (2006.01)

GO5B 19/18 (2006.01) GO5B 19/18 X GO5B 19/414 (2006.01) GO5B 19/414 R

**GO5B 19/042 (2006.01)** GO5B 19/042

請求項の数 1 (全 12 頁)

(21) 出願番号 特願2013-267165 (P2013-267165) (22) 出願日 平成25年12月25日 (2013.12.25)

(65) 公開番号 特開2015-125459 (P2015-125459A)

(43) 公開日 平成27年7月6日 (2015.7.6) 審査請求日 平成27年1月21日 (2015.1.21)

早期審査対象出願

||(73)特許権者 390008235

ファナック株式会社

山梨県南都留郡忍野村忍草字古馬場358

〇番地

||(74)代理人 110001151

あいわ特許業務法人

(72) 発明者 宮▲崎▼ 義人

山梨県南都留郡忍野村忍草字古馬場358

O番地 ファナック株式会社内

||(72)発明者 安藤 博篤

山梨県南都留郡忍野村忍草字古馬場358

〇番地 ファナック株式会社内

審査官 佐藤 彰洋

最終頁に続く

(54) 【発明の名称】複数のCPUと通信するIOユニットを用いた安全通信システム

## (57)【特許請求の範囲】

### 【請求項1】

数値制御装置と、通信コントローラを有する一つ以上のIOユニットが接続され、通信データを該数値制御装置と該IOユニットの該通信コントローラ間で送受する通信システムにおいて、

前記通信コントローラは、

自身のIDを設定する複数のID設定手段と、

前記数値制御装置から受信した通信データに含まれるIDと前記複数のID設定手段に 設定されたIDと比較する比較手段と、

前記複数のID設定手段に対応した前記通信データが複数の外部入出力信号のどれに対応するかを設定するための複数個の外部入出力信号割り当て対応設定手段と、

を備え、

前記比較手段による比較の結果、前記数値制御装置から受信した通信データに含まれる IDが前記複数のID設定手段に設定されたIDのいずれかと一致した場合に、前記通信 コントローラが前記数値制御装置に前記通信データを返信することを特徴とする通信システム。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、数値制御装置とIOユニット間で通信するシステムに関する。

#### 【背景技術】

### [0002]

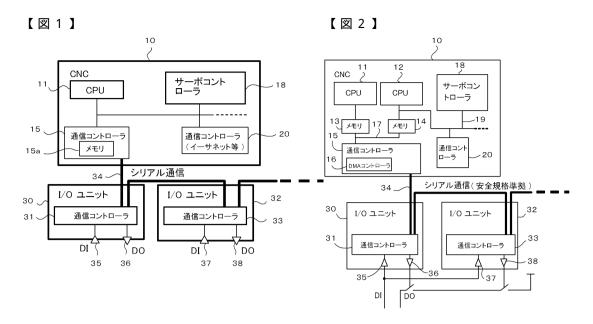

数値制御装置(CNC)10と工作機械(図示せず)との間では、DI/DO信号(入力信号/出力信号)の入出力を行うために、外部信号入出力用ユニット(IOユニット)を複数台接続する構成がとられており、通常、数値制御装置(CNC)10とIOユニット30,32間では、DI/DO信号の転送が行われている(図1参照)。

#### [0003]

IOユニット30,32の通信コントローラ31,33は、数値制御装置10との通信において、受信した通信データのヘッダに含まれるIDが自身の設定レジスタに設定されたIDと一致することをもって、受信したデータが自身宛のデータであることを認識し、数値制御装置10にデータを返信している(特許文献1)。またIOユニット30,32から返信されたDI/DO信号を、数値制御装置10の内部で動作するシーケンスプログラムで実際に使用する際には、数値制御装置10の内部のアドレスにDI/DO信号を割り付ける必要がある。このDI/DO信号の中には、非常停止信号やドアスイッチなど危険回避などに必要な安全信号が含まれている。

#### [0004]

ところで、電気電子安全関連システムや機械類制御システムには、安全規格としてIEC61508やISO13849-1などが存在する。前述の安全信号については、これらの規格に沿って処理及び転送されることが望ましい。規格に準じた処理及び転送方法として、特許文献2がある。

#### [00005]

特許文献2では、CPU11とCPU12に対して対応するIOユニット30、IOユニット32が存在し、CPU11とIOユニット30の組と、CPU12とIOユニット32の組が互いに独立して安全信号の処理と転送を行うことで、高い安全性を確保している(図2参照)。また、信号の転送はPROFIsafeに準じており、通信データにはカウント値やCRCなどが付与されている。先述のようにCPU11とIOユニット30の組と、CPU12とIOユニット32の組が互いに独立しているので、これらの付与される値もさきほどの2組に対応して2組あり、それぞれが互いに独立している。

### [0006]

この時、安全の確保においては、付与されるデータが互いに独立して無関係の値であることも重要になってくる。例えばCPU11のデータを誤ってIOユニット32が処理しようとしても、付与されているカウンタ値が異なるためエラーとなる。このような仕組み上、CPU11とIOユニット30、CPU12とIOユニット32の組み合わせを入れ替えることはできない。すなわちCPU11のアドレスにIOユニット32のDI/DO信号を割り付けたり、CPU12のアドレスにIOユニット30のDI/DO信号を割り付けたり、あるいはIOユニット30をCPU11とCPU12の両方のアドレスに割り付けたりすることはできない。これは、先述のように通信データに付与されるカウンタ値やCRCがCPUとIOユニットの組み合わせに対応しており、入れ替え不可能であることによる。

【先行技術文献】

## 40

50

10

20

30

## 【特許文献】

#### [0007]

【特許文献1】特許第4185142号公報

【特許文献2】特開2013-235300号公報

#### 【発明の概要】

【発明が解決しようとする課題】

#### [00008]

ところで、近年、工作機械はますます多様化しており、多数のヴァリエーションを持つ機械を設計することも少なくない。ヴァリエーションの1つ1つにおいては、構成次第で必要となるDI/DO信号の点数が異なってくる。いずれの構成においても、接続される

IOユニットの個数は最小となるように設計されることが、コストの観点からは重要である。

### [0009]

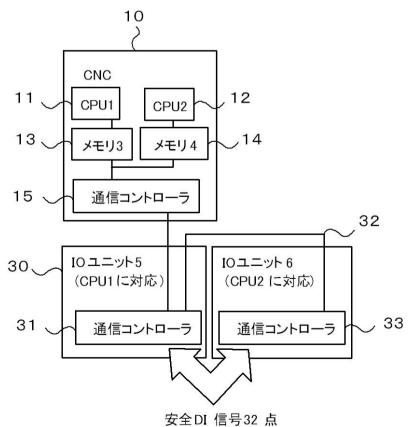

ところが、DI/DO信号に安全信号が含まれている場合に、特許文献2の方法を用いて構成すると、前述のようにCPUとIOユニットの組み合わせが入れ替え不可能なために、必要以上にIOユニットを接続しなければならない場合がある。例えば、まず安全DI信号の総点数が32点(ビット)の機械を、一つあたり32点のDI信号を持つIOユニットで構成する場合を考える。2つのCPU11,12を備え、安全DI信号が32点であるので、32点のDI信号を持つIOユニット30,32の2つで構成することができる(図3参照)。

[0010]

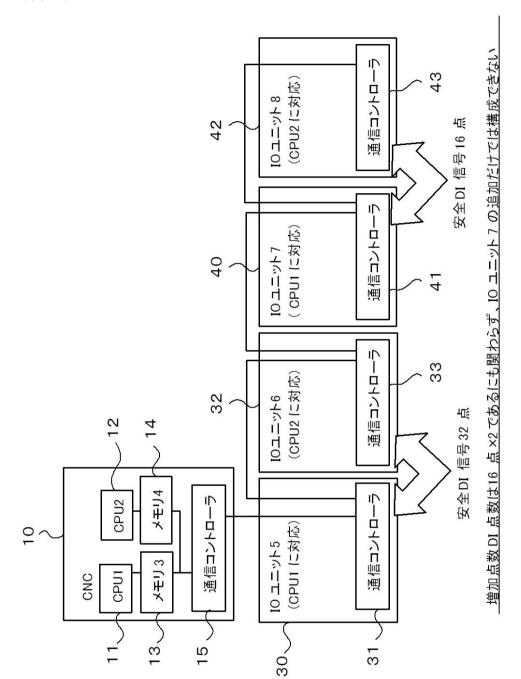

ところが、次に同じ機械のヴァリエーションとして、安全DI信号の総点数が48点の機械を設計する場合、図3のシステムに対して増加した安全DI信号は16点であるから、16点×2=32点のDI信号があればよく、32点のIOユニットを一つ追加すれば総点数を賄うことができるはずである。しかし、実際には安全DI信号の処理に関して、前述の通り2つのCPU11、12に対して2つのIOユニットの組み合わせが必要になるため、IOユニット40,42を2つ更に接続する必要がある(図4参照)。

[0011]

このように、安全DI/DO信号を構成する場合、特許文献2の方法では、CPUとIOユニットの割付に関する制約から、必要以上に多くのIOユニットを接続しなければならない場合がある、という問題があった。

[0012]

そこで本発明の目的は、上記従来技術の問題を解決するために、複数のCPUと通信するIOユニットを用いた安全通信システムを提供することである。

【課題を解決するための手段】

[0013]

本願の請求項1に係る発明は、数値制御装置と、通信コントローラを有する一つ以上の I Oユニットが接続され、通信データを該数値制御装置と該 I Oユニットの該通信コントローラ間で送受する通信システムにおいて、前記通信コントローラは、自身の I D を設定する複数の I D 設定手段と、前記数値制御装置から受信した通信データに含まれる I D と前記複数の I D 設定手段に設定された I D と比較する比較手段と、前記複数の I D 設定手段に対応した前記通信データが複数の外部入出力信号のどれに対応するかを設定するための複数個の外部入出力信号割り当て対応設定手段と、を備え、前記比較手段による比較の結果、前記数値制御装置から受信した通信データに含まれる I D が前記複数の I D 設定手段に設定された I D のいずれかと一致した場合に、前記通信コントローラが前記数値制御装置に前記通信データを返信することを特徴とする通信システムである。

【発明の効果】

[0014]

本発明により、複数のCPUと通信するIOユニットを用いた安全通信システムを提供できる。

【図面の簡単な説明】

[0015]

【図1】数値制御装置とIOユニット間で、DI/DO信号の転送が行われていることを示す図である。

【図2】CPU11とIOユニット30の組と、CPU12とIOユニット32の組が互いに独立して安全信号の処理と転送を行うことを示す図である。

【図3】安全DI信号の総点数が32点(ビット)の機械を、一つあたり32点のDI信号を持つIOユニットで構成する場合を示す図である。

【図4】図3に対して更に2つのIOユニットを接続しなければならないことを示す図である。

10

20

30

40

10

20

30

40

50

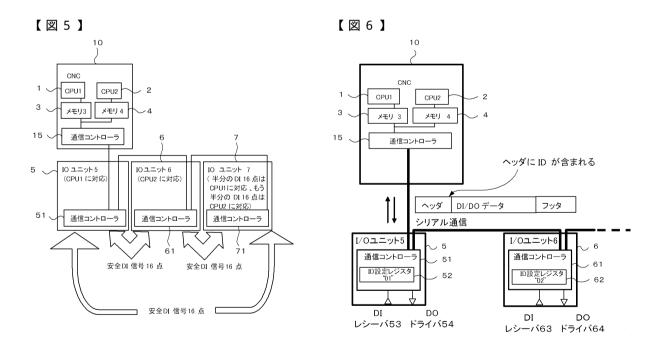

【図5】IOユニットの通信コントローラについて、自身のIDを設定するレジスタを2つ内蔵する本発明の構成を示す図である。

【図 6 】数値制御装置とIOユニット間の通信を示す図である。数値制御装置側の通信コントローラはマスタ、IOユニット側の通信コントローラはスレーブとして動作し、両者はマスタスレープ方式で一対一通信を行うことを示す図である。

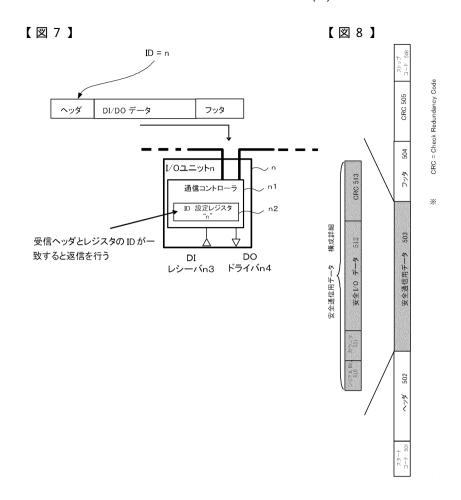

【図7】受信ヘッダとレジスタのIDが一致すると返信を行うことを示す図である。

【図8】安全通信用データの構成を示す図である。

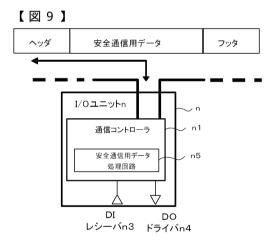

【図9】通信コントローラが内部に安全通信用データを処理するための安全通信用データ 処理回路を備えていることを示す図である。

【図10】マスタ(数値制御装置)とスレーブの間で安全データの送受信を行うことを示す図である。

【図11】複数のCPUと通信するIOユニットを示す図である。

【図12】数値制御装置の複数のCPUと通信するIOユニットを備えた安全通信システムの構成を示す図である。

【発明を実施するための形態】

#### [0016]

以下、本発明の実施形態を図面と共に説明する。

図5はIOユニットの通信コントローラについて、自身のIDを設定するレジスタを2つ内蔵する本発明の構成を示す図である。工作機械を制御する数値制御装置10には、工作機械の本体に取り付けられるIOユニット5,6,7がデージーチェーン式に接続されている。数値制御装置10との通信において、スレーブ(IOユニット7)が自身宛のデータを認識するためのIDを設定するレジスタが通信コントローラに2つ内蔵されている。IOユニット7の半分のDI信号16点(ビット)は数値制御装置10のCPU1に対応し、もう半分のDI信号16点(ビット)はCPU2に対応する。

#### [0017]

IOユニット7のDIのうち半分の16点をCPU1のアドレスに割付け、もう半分の16点をCPU2のアドレスに割り付ける。安全DI信号は、一つの信号を2つのCPU1、CPU2にそれぞれ割りつけて処理する必要がある。いいかえると、一つのIOユニットのDIレシーバ入力に対して、ペアとなる別のIOユニットのDIレシーバ入力が存在する。

#### [0018]

よって、IOユニット 5、IOユニット 6、IOユニット 7 のDIも 2 つのDIレシーバ入力がペアになるように組み合わせる。すると、IOユニット 5 の半分のDIの1 6 点とIOユニット 6 の半分のDIの1 6 点を一つのペア、IOユニット 6 の残り半分のDIの1 6 点とIOユニット 7 の半分のDIの1 6 点をもう一つのペア、IOユニット 7 の残りの半分のDIの1 6 点を最後のペアとして組み合わせることで、DIの4 8 点のすべてがCPU1とCPU 2 のアドレスに割り付けられて入力されることになる。

### [0019]

I O ユニット 7 の通信コントローラ 7 1 は、自身が受信した通信データのヘッダに含まれる I D が自身の 2 つの I D 設定レジスタのいずれかに一致することをもって、数値制御装置 1 0 にデータを返信する。また、予め設定された自身のレジスタに従って、 2 つの C P U 1 , 2 に対応して安全信号の処理を行う。

## [0020]

上述したように、IOユニット7の1つの通信コントローラ71に対してCPU1、CPU2のどちらともが安全通信用データの交換を行って、それぞれのCPU1,2に対応したDI/DOを入出力することができる。一つのIOユニット7のDI/DO信号に対して、CPU1及びCPU2の両方のアドレスを割りつけることができるので、従来技術のようなCPUとIOユニットの組み合わせの制約に縛られることなく、必要最小限のIOユニット接続数で必要な安全DI/DO信号点数を構成できる。

10

20

30

40

50

#### [0021]

図6は数値制御装置とIOユニット間の通信を説明する図である。数値制御装置と一つまたは複数のIOユニットが接続される構成において、数値制御装置10は、通信コントローラ15と2つの独立したCPU1及びCPU2を備え、IOユニット5,6は通信コントローラ51,61と、通信により転送されたDI/DOを外部(機械側)に入出力するためのドライバ54,64とレシーバ53,63を備えている。IOユニット5,6の通信コントローラ51,61は、内部に自身のIDを表すID設定レジスタ52,62を備えている。数値制御装置側10の通信コントローラ15はマスタ、IOユニット5,6側の通信コントローラ51,61はスレーブとして動作し、両者はマスタスレーブ方式で一対一通信を行う。

[0022]

図7は受信ヘッダとレジスタのIDが一致すると返信を行うことを説明する図である。数値制御装置に接続されたIOユニットのうちn番目のIOユニットnの通信コントローラn1は、数値制御装置10との通信において、受信した通信データのヘッダに含まれるIDが自身の設定レジスタ(ID設定レジスタn2)に設定されたID(=n)と一致することをもって、受信したデータが自身宛のデータであることを認識し、数値制御装置10にデータを返信する。

[0023]

図9は通信コントローラが内部に安全通信用データを処理するための回路を備えていることを示す図である。IOユニットnの通信コントローラn1は内部に安全通信用データ(図8参照)を処理するための回路を備えており、自身が送受信する安全通信用データに含まれるシリアルNo.(シリアルナンバー)、カウンタ、CRC(Cyclic Redundancy Code)を処理している。

[0024]

図8に示されるように、安全通信用データの先頭には、各スレーブに予め設定されたシリアルNo.が付与される。СРU1、СРU2及びスレーブ(IOユニット)(図9参照)に内蔵された通信コントローラ n 1 の安全通信用データ処理回路 n 5 は、それぞれ自身が受信したシリアルNo.についてチェックを行う。不正が検出された場合、エラーないしアラームが発生し、受信データは破棄される。

[0025]

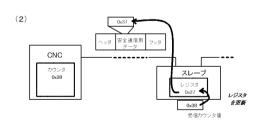

図10はマスタとスレーブの間で安全通信用データの送受信を行うことを示す図である。安全通信用データに含まれるカウンタ(図8参照)は、マスタである数値制御装置10からスレーブであるIOユニットへのデータ送信時に付与される(図10の(1)参照)。一方スレーブ(IOユニット)側は、マスタ側である数値制御装置10から安全通信用データを受信すると、含まれているカウンタ値をマスタ側である数値制御装置へ返信に元々内部レジスタに保存されていたカウンタ値をマスタ側である数値制御装置へ返信を受信の図10の(2)参照)。マスタ側である数値制御装置10はスレーブから返信を受信ると、自身が発行したカウンタ値と受信した安全通信用データに含まれるカウンタの差分をチェックする(図10の(3)を参照)。通信終了後、マスタ側である数値制御装置は次回の通信時に、発行するカウンタ値を+1して、同様の動作を繰り返す。このカウンタ値の発行は、CPU1及びCPU2が独立に行う。CPU1とCPU2は、カウンタの初期値が異なるため、CPU1とCPU2が同じカウンタ値を複数回にわたって連続で発行することはない。

[0026]

マスタ側である数値制御装置10が発行したカウンタ値とマスタ側である数値制御装置10がスレープ側であるIOユニットから受信したカウンタ値の差分は、通信が正常であれば常に1になるが、何らかの要因で通信が失敗した場合には、差分値は2以上となる。この差分値が予め設定された許容値を上回った場合、これを看過できないアラームとして数値制御装置が検出する。また、スレーブが受信したカウンタ値と、スレーブの内部に保存されたカウンタ値についても、正常に通信が行われていれば、差分値は1同様にとなる

が、何らかの要因で通信が失敗した場合には、差分値は2以上になる。この差分値が予め設定された許容値を上回った場合、これも同様に看過できないアラームとして検出する。さらに、この差分値が0の場合、CPU1もしくはCPU2が発行するカウンタ値を更新していないことになる。差分値の更新が予め設定された許容回数を上回って未更新の場合、これも看過できないアラームとして検出する。

### [0027]

図8に示されるように安全通信用データの末尾には、CRC513が付与されており、これはシリアルNo.、カウンタ、安全I/Oデータを保護している。CPU1、CPU2、及びスレーブに内蔵された安全処理用データ処理回路(図9のn5を参照)は、データの受信時にこのCRCをチェックする。不正が検出された場合、エラーないしアラームが発生し、受信データは破棄される。

[0028]

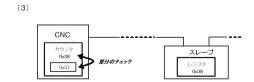

図11は複数のCPUと通信するIOユニットを示す図である。従来技術では、前述のID設定レジスタと安全通信用データ処理回路(図9参照)は1つの通信コントローラにつき1つずつ含まれていたが、本発明の実施形態ではこれを内部に2つ備えているIOユニットを備えている。IOユニット7の通信コントローラ71は、自身が受信した通信データのヘッダに含まれるIDが自身の2つのID設定レジスタ72a及びID設定レジスタ72bのどちらかに一致することをもって、受信したデータが自身宛のデータであることを認識する。

[0029]

また通信コントローラ71は、2つのID1、ID2に対応した安全通信用データ処理回路77a,77bを持っており、受信したIDに従って対応する安全通信用データ処理回路77bが動作し、安全通信用データを処理する。さらに通信コントローラ71は、それぞれのIDで受信したデータが、どのドライバとレシーバに割り当てられるか設定するための外部入出力信号割り当て対応レジスタを持っており、予め設定された外部入出力信号割り当て対応レジスタレジスタに従って、送受信するDI/DOを外部入出力ドライバ/レシーバに割り当てる。

[0030]

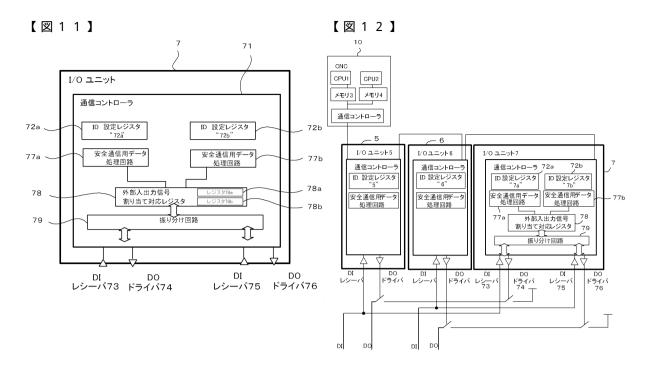

図12は数値制御装置の複数のCPUと通信するIOユニットを用いた安全通信システムを説明する図である。通信コントローラは、CPU1との通信においては、ID1を用いて安全データ用通信を行い、予め設定された外部入出力信号割り当て対応レジスタに従ってドライバ / レシーバを通してDI / DOを入出力する。また、CPU2との通信においては、ID2を用いて安全データ用通信を行い、予め設定された外部入出力信号割り当て対応レジスタに従ってドライバ / レシーバを通してDI / DOを入出力する。

【符号の説明】

[0031]

- 1 C P U

- 2 C P U

- 3 メモリ

- 4 メモリ

- 5 IOユニット

- 5 1 通信コントローラ

- 52 ID設定レジスタ

- 53 レシーバ

- 54 ドライバ

- 6 IOユニット

- 6 1 通信コントローラ

- 62 ID設定レジスタ

- 63 レシーバ

20

10

30

40

## 64 ドライバ

- 7 IOユニット

- 7 1 通信コントローラ

- 72a,72b ID設定レジスタ

- 73 レシーバ

- 7 4 ドライバ

- 75 レシーバ

- 76 ドライバ

- 77a,77b 安全通信用データ処理回路

- 78 外部入出力信号割り当て対応レジスタ

- 79 振り分け回路

- 1 0 数値制御装置

- 1 1 CPU

- 1 2 C P U

- 13 メモリ

- 1 4 メモリ

- 15 通信コントローラ

- 15a メモリ

- 1 6 DMAコントローラ

- 17 専用バス

- 1 8 サーボコントローラ

- 19 バス

- 2 0 通信コントローラ

- 3 0 IOユニット

- 3 1 通信コントローラ

- 3 2 IOユニット

- 3 3 通信コントローラ

- 3 4 通信路

- 3 5 レシーバ

- 3 6 ドライバ

- 37 レシーバ

- 3 8 ドライバ

- 4 0 IOユニット

- 4 1 通信コントローラ

- 4 2 IOユニット

- 4 3 通信コントローラ

10

20

30

【図10】

## 【図3】

【図4】

## フロントページの続き

## (56)参考文献 特許第4185142(JP,B2)

特開2013-058140(JP,A)

特開平11-143680(JP,A)

特開2011-165038(JP,A)

特開2012-226712(JP,A)

特開2006-215763(JP,A)

特開2008-191989(JP,A)

米国特許出願公開第2015/0066979(US,A1)

米国特許第4200936(US,A)

## (58)調査した分野(Int.CI., DB名)

G05B 19/18-19/416

G05B 19/42-19/46

G05B 19/04-19/05