(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7581209号

(P7581209)

(45)発行日 令和6年11月12日(2024.11.12)

(24)登録日 令和6年11月1日(2024.11.1)

|                         |                       |

|-------------------------|-----------------------|

| (51)国際特許分類              | F I                   |

| H 01 L 27/088 (2006.01) | H 01 L 27/088 3 3 1 E |

| G 06 F 9/38 (2018.01)   | G 06 F 9/38 3 7 0 C   |

| G 06 F 12/00 (2006.01)  | G 06 F 12/00 5 6 0 F  |

| G 06 F 15/78 (2006.01)  | G 06 F 15/78 5 5 0    |

| G 11 C 5/02 (2006.01)   | G 11 C 5/02 1 0 0     |

請求項の数 3 (全64頁) 最終頁に続く

|                   |                             |          |                       |

|-------------------|-----------------------------|----------|-----------------------|

| (21)出願番号          | 特願2021-538510(P2021-538510) | (73)特許権者 | 000153878             |

| (86)(22)出願日       | 令和2年7月27日(2020.7.27)        |          | 株式会社半導体エネルギー研究所       |

| (86)国際出願番号        | PCT/IB2020/057051           |          | 神奈川県厚木市長谷3 9 8 番地     |

| (87)国際公開番号        | WO2021/024083               | (72)発明者  | 上妻 宗広                 |

| (87)国際公開日         | 令和3年2月11日(2021.2.11)        |          | 神奈川県厚木市長谷3 9 8 番地 株式会 |

| 審査請求日             | 令和5年7月25日(2023.7.25)        | (72)発明者  | 社半導体エネルギー研究所内         |

| (31)優先権主張番号       | 特願2019-146209(P2019-146209) |          | 石津 貴彦                 |

| (32)優先日           | 令和1年8月8日(2019.8.8)          |          | 神奈川県厚木市長谷3 9 8 番地 株式会 |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     | (72)発明者  | 社半導体エネルギー研究所内         |

|                   |                             |          | 青木 健                  |

| (31)優先権主張番号       | 特願2019-157623(P2019-157623) |          | 神奈川県厚木市長谷3 9 8 番地 株式会 |

| (32)優先日           | 令和1年8月30日(2019.8.30)        | (72)発明者  | 社半導体エネルギー研究所内         |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     |          | 藤田 雅史                 |

| (31)優先権主張番号       | 特願2019-216244(P2019-216244) |          | 神奈川県厚木市長谷3 9 8 番地 株式会 |

|                   | 最終頁に続く                      |          | 社半導体エネルギー研究所内         |

|                   |                             |          | 最終頁に続く                |

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

C P U と、

アクセラレータと、を有し、

前記アクセラレータは、第1メモリ回路と、駆動回路と、演算回路と、を有し、

前記第1メモリ回路は、第1トランジスタを有し、

前記第1トランジスタは、チャネル形成領域に金属酸化物を有する半導体層を有し、

前記駆動回路は、書き込み回路と、読み出し回路と、を有し、

前記書き込み回路は、切替信号、書き込み制御信号、およびデータ信号に応じて、前記第1メモリ回路に書き込むデータを2値または3値の電圧値に切り替えて出力する機能を有し、

前記読み出し回路は、第1参照電圧および第2参照電圧に応じて、前記第1メモリ回路に保持された電圧レベルに応じた2値または3値のデータを切り替えて読み出す機能を有し、

前記駆動回路および前記演算回路は、第2トランジスタを有し、

前記第2トランジスタは、チャネル形成領域にシリコンを有する半導体層を有し、

前記第1トランジスタと、前記第2トランジスタと、は積層して設けられる、半導体装置。

## 【請求項2】

請求項1において、

前記 C P U は、バックアップ回路が設けられたフリップフロップを有する C P U コアを有し、

前記バックアップ回路は、前記 C P U が非動作時において、前記フリップフロップに保持されたデータを電源電圧の供給が停止した状態で保持する機能を有する、半導体装置。

【請求項 3】

請求項 1 または請求項 2 において、

前記演算回路は、積和演算を行う回路である、半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

10

本明細書は、半導体装置等について説明する。

【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する本発明の一態様の技術分野としては、半導体装置、撮像装置、表示装置、発光装置、蓄電装置、記憶装置、表示システム、電子機器、照明装置、入力装置、入出力装置、それらの駆動方法、又はそれらの製造方法、を一例として挙げることができる。

【背景技術】

【0003】

20

C P U ( C e n t r a l P r o c e s s i n g U n i t ) 等を含む半導体装置を有する電子機器が普及している。このような電子機器では、大量のデータを高速に処理するため、半導体装置の性能向上に関する技術開発が活発である。高性能化を実現する技術としては、例えば、G P U ( G r a p h i c s P r o c e s s i n g U n i t ) 等のアクセラレータと C P U とを密結合させた、所謂 S o C ( S y s t e m o n C h i p ) 化がある。S o C 化によって高性能化した半導体装置では、発熱、及び消費電力の増加が問題となってくる。

【0004】

A I ( A r t i f i c i a l I n t e l l i g e n c e ) 技術では、計算量とパラメータ数が膨大になるため、演算量が増大する。演算量の増大は、発熱、および消費電力を増加させる要因となるため、演算量を低減するためのアーキテクチャが盛んに提案されている。代表的なアーキテクチャとして、B i n a r y N e u r a l N e t w o r k ( B N N ) 、およびT e r n a r y N e u r a l N e t w o r k ( T N N ) があり、回路規模縮小、および低消費電力化に対して特に有効となる（例えば特許文献 1 を参照）。例えば、B N N では、もともと 32 ビット、もしくは 16 ビット精度で表現されたデータを、「+1」または「-1」の 2 値に圧縮することで、計算量とパラメータ数を大幅に削減できる。例えば、T N N では、もともと 32 ビット、もしくは 16 ビット精度で表現されたデータを、「+1」、「0」または「-1」の 3 値に圧縮することで、計算量とパラメータ数を大幅に削減できる。B N N およびT N N は、回路規模縮小や低消費電力化に有効なため、組み込みチップのように限られたハードウェア資源において低消費電力が求められるアプリケーションと相性が良いと考えられている。

30

【先行技術文献】

40

【特許文献】

【0005】

【文献】国際公開第 2019 / 078924 号

【発明の概要】

【発明が解決しようとする課題】

【0006】

T N N の演算には 3 値のデータを用いる。3 値のデータを S R A M ( S t a t i c R A M ) に記憶する場合、メモリセル内のトランジスタ数が増えてしまう。そのため、半導体装置の小型化が難しくなるといった虞がある。また、半導体装置が有するアクセラレータでは、メモリが記憶するデータを 2 値または 3 値のデータで切り替える場合がある。こ

50

の場合、データに応じたメモリセルを用意する構成では、メモリセル内のトランジスタ数が増えてしまう。そのため、半導体装置の小型化が難しくなるといった虞がある。また半導体装置の消費電力は、C P Uにおけるデータ転送回数が支配的である。そのため、半導体装置の低消費電力または発熱を抑制するためには、データ転送回数の増加を抑制することが重要となる。

#### 【0007】

本発明の一態様は、半導体装置を小型化することを課題の一とする。または、本発明の一態様は、半導体装置を低消費電力化することを課題の一とする。または、本発明の一態様は、半導体装置の発熱を抑制することを課題の一とする。または、本発明の一態様は、C P Uとメモリとして機能する半導体装置との間のデータ転送回数を削減することを課題の一とする。または、新規な構成の半導体装置を提供することを課題の一とする。

10

#### 【0008】

なお、本発明の一態様は、必ずしも上記の課題の全てを解決する必要はなく、少なくとも一の課題を解決できるものであればよい。また、上記の課題の記載は、他の課題の存在を妨げるものではない。これら以外の課題は、明細書、特許請求の範囲、図面などの記載から、自ずと明らかとなるものであり、明細書、特許請求の範囲、図面などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

#### 【0009】

本発明の一態様は、C P Uと、アクセラレータと、を有し、アクセラレータは、第1メモリ回路と、演算回路と、を有し、第1メモリ回路は、第1トランジスタを有し、第1トランジスタは、チャネル形成領域に金属酸化物を有する半導体層を有し、演算回路は、第2トランジスタを有し、第2トランジスタは、チャネル形成領域にシリコンを有する半導体層を有し、第1トランジスタと、第2トランジスタと、は積層して設けられる、半導体装置である。

20

#### 【0010】

本発明の一態様は、C P Uと、アクセラレータと、を有し、アクセラレータは、第1メモリ回路と、駆動回路と、演算回路と、を有し、第1メモリ回路は、第1トランジスタを有し、第1トランジスタは、チャネル形成領域に金属酸化物を有する半導体層を有し、駆動回路は、書き込み回路と、読み出し回路と、を有し、書き込み回路は、切替信号、書き込み制御信号、およびデータ信号に応じて、第1メモリ回路に書き込むデータを2値または3値の電圧値に切り替えて出力する機能を有し、読み出し回路は、第1参照電圧および第2参照電圧に応じて、第1メモリ回路に保持された電圧レベルに応じた2値または3値のデータを切り替えて読み出す機能を有し、駆動回路および演算回路は、第2トランジスタを有し、第2トランジスタは、チャネル形成領域にシリコンを有する半導体層を有し、第1トランジスタと、第2トランジスタと、は積層して設けられる、半導体装置である。

30

#### 【0011】

本発明の一態様は、C P Uと、アクセラレータと、を有し、アクセラレータは、第1メモリ回路と、演算回路と、を有し、第1メモリ回路は、第1トランジスタを有し、第1トランジスタは、チャネル形成領域に金属酸化物を有する半導体層を有し、演算回路は、第2トランジスタを有し、第2トランジスタは、チャネル形成領域にシリコンを有する半導体層を有し、C P Uは、バックアップ回路が設けられたフリップフロップを有するC P Uコアを有し、バックアップ回路は、第3トランジスタを有し、第3トランジスタは、チャネル形成領域に金属酸化物を有する半導体層を有し、第1トランジスタと、第2トランジスタと、は積層して設けられる、半導体装置である。

40

#### 【0012】

本発明の一態様は、C P Uと、アクセラレータと、を有し、アクセラレータは、第1メモリ回路と、駆動回路と、演算回路と、を有し、第1メモリ回路は、第1トランジスタを有し、第1トランジスタは、チャネル形成領域に金属酸化物を有する半導体層を有し、駆動回路は、書き込み回路と、読み出し回路と、を有し、書き込み回路は、切替信号、書き

50

込み制御信号、およびデータ信号に応じて、第1メモリ回路に書き込むデータを2値または3値の電圧値に切り替えて出力する機能を有し、読み出し回路は、第1参照電圧および第2参照電圧に応じて、第1メモリ回路に保持された電圧レベルに応じた2値または3値のデータを切り替えて読み出す機能を有し、演算回路は、第2トランジスタを有し、第2トランジスタは、チャネル形成領域にシリコンを有する半導体層を有し、CPUは、バックアップ回路が設けられたフリップフロップを有するCPUコアを有し、バックアップ回路は、第3トランジスタを有し、第3トランジスタは、チャネル形成領域に金属酸化物を有する半導体層を有し、第1トランジスタと、第2トランジスタとは積層して設けられる、半導体装置である。

【0013】

10

本発明の一態様において、バックアップ回路は、CPUが非動作時において、フリップフロップに保持されたデータを電源電圧の供給が停止した状態で保持する機能を有する、半導体装置が好ましい。

【0014】

本発明の一態様において、演算回路は、積和演算を行う回路である、半導体装置が好ましい。

【0015】

本発明の一態様において、金属酸化物は、Inと、Gaと、Znと、を含む、半導体装置が好ましい。

【0016】

20

本発明の一態様において、第1トランジスタは、読み出ビット線に電気的に接続され、読み出ビット線は、第2トランジスタが設けられた基板表面に概略垂直に設けられた配線を介して演算回路に電気的に接続される、半導体装置が好ましい。

【0017】

なおその他の本発明の一態様については、以下で述べる実施の形態における説明、および図面に記載されている。

【発明の効果】

【0018】

30

本発明の一態様は、半導体装置を小型化することができる。または、本発明の一態様は、半導体装置を低消費電力化することができる。または、本発明の一態様は、半導体装置の発熱を抑制することができる。または、本発明の一態様は、CPUとメモリとして機能する半導体装置との間のデータ転送回数を削減することができる。または、新規な構成の半導体装置を提供することができる。

【0019】

複数の効果の記載は、他の効果の存在を妨げるものではない。また、本発明の一形態は、必ずしも、例示した効果の全てを有する必要はない。また、本発明の一形態について、上記以外の課題、効果、および新規な特徴については、本明細書の記載および図面から自ずと明らかになるものである。

【図面の簡単な説明】

【0020】

40

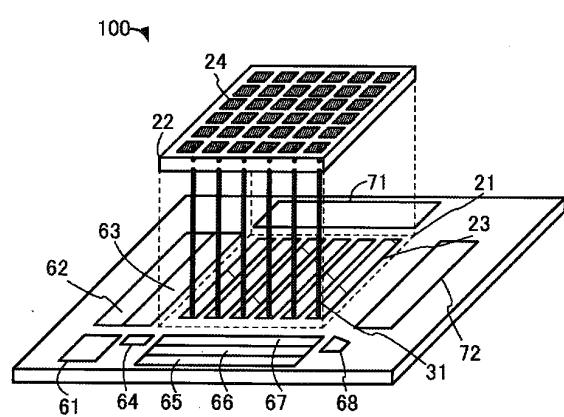

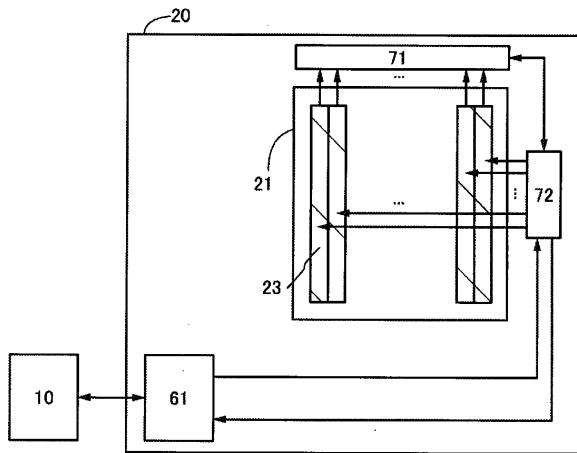

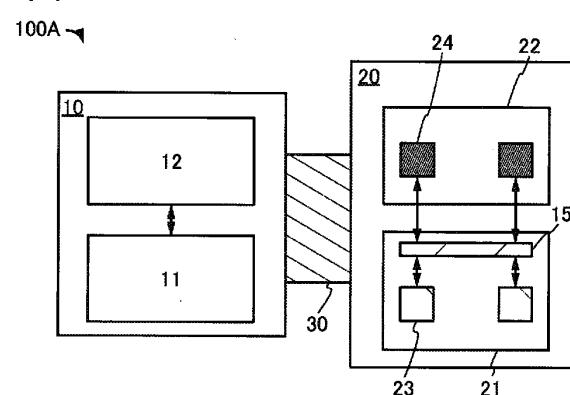

図1Aおよび図1Bは、半導体装置の構成例を説明する図である。

図2Aおよび図2Bは、半導体装置の構成例を説明する図である。

図3Aおよび図3Bは、半導体装置の構成例を説明する図である。

図4は、半導体装置の構成例を説明する図である。

図5Aおよび図5Bは、半導体装置の構成例を説明する図である。

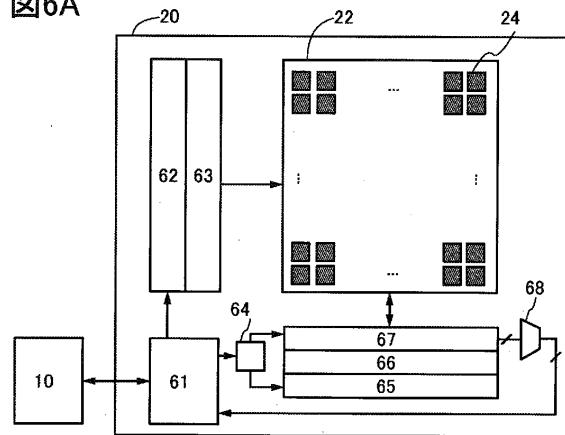

図6Aおよび図6Bは、半導体装置の構成例を説明する図である。

図7Aおよび図7Bは、半導体装置の構成例を説明する図である。

図8Aおよび図8Bは、半導体装置の構成例を説明する図である。

図9は、半導体装置の構成例を説明する図である。

図10A、図10Bおよび図10Cは、半導体装置の処理性能と消費電力との関係を説明

50

する図である。

図11Aおよび図11Bは、半導体装置の構成例を説明する図である。

図12Aおよび図12Bは、半導体装置の構成例を説明する図である。

図13は、半導体装置の構成例を説明する図である。

図14Aおよび図14Bは、半導体装置の構成例を説明する図である。

図15Aおよび図15Bは、半導体装置の構成例を説明する図である。

図16は、半導体装置の構成例を説明する図である。

図17は、半導体装置の構成例を説明する図である。

図18Aおよび図18Bは、半導体装置の構成例を説明する図である。

図19Aおよび図19Bは、半導体装置の構成例を説明する図である。

図20Aおよび図20Bは、半導体装置の構成例を説明する図である。

図21は、半導体装置の構成例を説明する図である。

図22Aおよび図22Bは、半導体装置の構成例を説明する図である。

図23は、半導体装置の構成例を説明する図である。

図24は、半導体装置の構成例を説明する図である。

図25Aおよび図25Bは、半導体装置の構成例を説明する図である。

図26Aおよび図26Bは、半導体装置の構成例を説明する図である。

図27Aおよび図27Bは、半導体装置の構成例を説明する図である。

図28Aおよび図28Bは、半導体装置の構成例を説明する図である。

図29は、半導体装置の構成例を説明する図である。

図30は、CPUの構成例を説明する図である。

図31Aおよび図31Bは、CPUの構成例を説明する図である。

図32は、CPUの構成例を説明する図である。

図33は、集積回路の構成例を説明する図である。

図34Aおよび図34Bは、集積回路の構成例を説明する図である。

図35Aおよび図35Bは、集積回路の適用例を説明する図である。

図36Aおよび図36Bは、集積回路の適用例を説明する図である。

図37A、図37Bおよび図37Cは、集積回路の適用例を説明する図である。

図38は、集積回路の適用例を説明する図である。

図39Aは、半導体装置の外観写真である。図39Bは、半導体装置の断面TEM写真である。

図40は、半導体装置のシステム構成を説明するブロック図である。

図41Aは、メモリセルの回路図である。図41Bは、メモリセルの動作例を示すタイミングチャートである。図41Cは、演算器の構成を示すブロック図である。

図42Aおよび図42Bは、半導体装置の構成を説明するブロック図である。

図43Aおよび図43Bは、半導体装置の動作期間中に生じる消費電力の推移を説明する概念図である。

図44Aおよび図44Bは、情報保持回路の回路図である。

図45Aは、シミュレーション実行後の動作波形を示す図である。図45Bは、シミュレーションで想定したニューラルネットワークモデルを示す図である。

#### 【発明を実施するための形態】

##### 【0021】

以下に、本発明の実施の形態を説明する。ただし、本発明の一形態は、以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明の一形態は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

##### 【0022】

なお本明細書等において、「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものである。従って、構成要素の数を限定するものではない。また、構成要素の順序を限定するものではない。また例えば、本明細書等の実施の形態の

10

20

30

40

50

一において「第1」に言及された構成要素が、他の実施の形態、あるいは特許請求の範囲において「第2」に言及された構成要素とすることもありうる。また例えば、本明細書等の実施の形態の一において「第1」に言及された構成要素を、他の実施の形態、あるいは特許請求の範囲において省略することもありうる。

【0023】

図面において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。

【0024】

本明細書において、例えば、電源電位VDDを、電位VDD、VDD等と省略して記載する場合がある。これは、他の構成要素（例えば、信号、電圧、回路、素子、電極、配線等）についても同様である。

10

【0025】

また、複数の要素に同じ符号を用いる場合、特に、それらを区別する必要があるときには、符号に“\_1”、“\_2”、“[n]”、“[m, n]”等の識別用の符号を付記して記載する場合がある。例えば、2番目の配線GLを配線GL[2]と記載する。

【0026】

（実施の形態1）

本発明の一態様である半導体装置の構成、および動作等について説明する。

20

【0027】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能し得る装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。表示装置（液晶表示装置、発光表示装置など）、投影装置、照明装置、電気光学装置、蓄電装置、記憶装置、半導体回路、撮像装置、電子機器などは、半導体装置を有すると言える場合がある。

【0028】

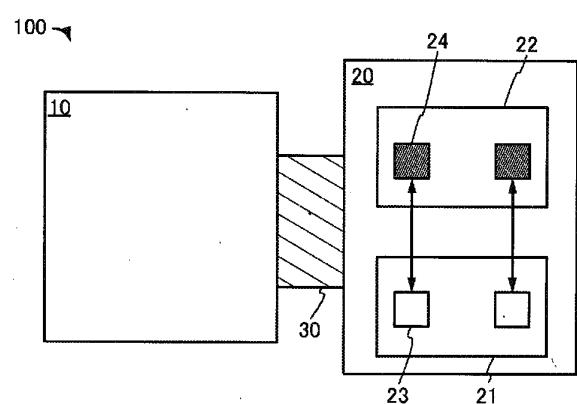

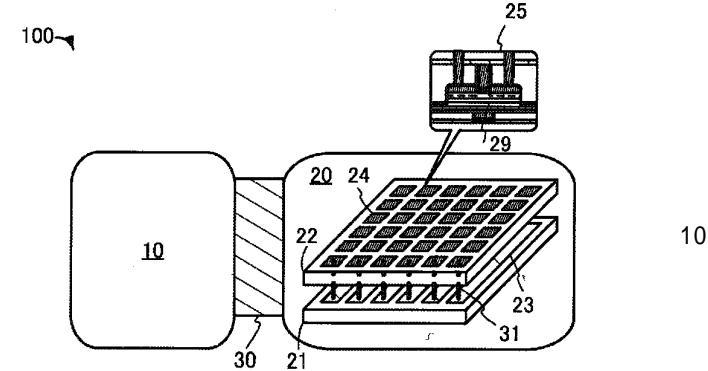

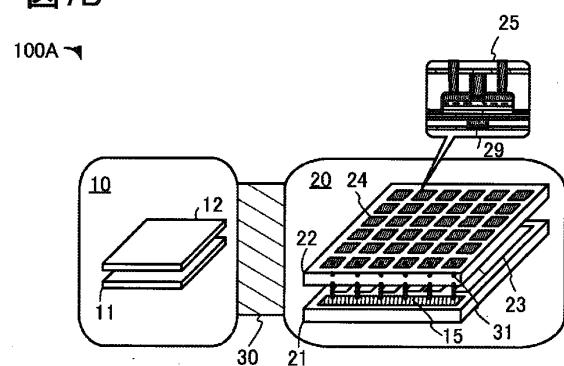

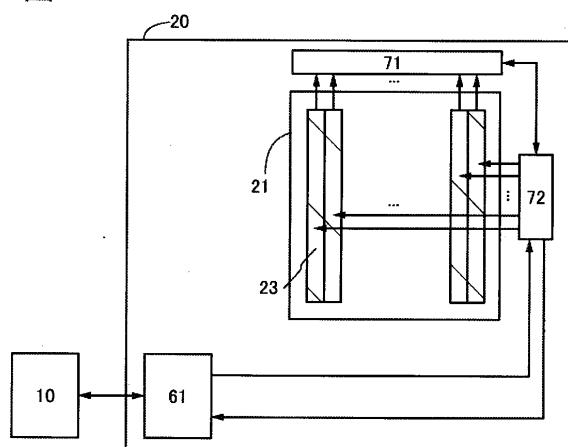

図1Aおよび図1Bは、本発明の一態様である半導体装置100を説明するための図である。半導体装置100は、CPU10、アクセラレータ20およびバス30を有する。アクセラレータ20は、演算処理部21およびメモリ部22を有する。演算処理部21は、演算回路23を有する。メモリ部22は、メモリ回路24を有する。メモリ部22は、デバイスマモリ、共有メモリという場合がある。メモリ回路24は、チャネル形成領域を有する半導体層29を有するトランジスタ25を有する。演算回路23とメモリ回路24とは、配線31を介して電気的に接続される。

30

【0029】

CPU10は、オペレーティングシステムの実行、データの制御、各種演算やプログラムの実行など、汎用の処理を行う機能を有する。CPU10は、1つまたは複数のCPUコアを有する。CPUコアはそれぞれ、電源電圧の供給が停止してもデータを保持できるデータ保持回路を有する。電源電圧の供給は、電源ドメイン（パワードメイン）からのパワースイッチ等による電気的な切り離しによって制御することができる。なお電源電圧は、駆動電圧という場合がある。データ保持回路として、例えば、酸化物半導体（oxide semiconductor）をチャネル形成領域に有するトランジスタ（OSトランジスタ）を有するメモリが好適である。なお酸化物半導体は、金属酸化物ともいう。OSトランジスタを有するデータ保持回路を備えたCPUコアの構成については、実施の形態5で説明する。

40

【0030】

アクセラレータ20は、ホストプログラムから呼び出されたプログラム（カーネル、またはカーネルプログラムとも呼ばれる。）を実行する機能を有する。アクセラレータ20は、例えば、グラフィック処理における行列演算の並列処理、ニューラルネットワークの積和演算の並列処理、科学技術計算における浮動小数点演算の並列処理などを行うことができる。

50

## 【0031】

メモリ部22は、アクセラレータ20が処理するデータを記憶する機能を有する。具体的には、ニューラルネットワークの積和演算の並列処理に用いる重みデータ等、演算処理部21に入力するあるいは出力されるデータを記憶することができる。

## 【0032】

メモリ回路24は、演算処理部21が有する演算回路23と配線31を介して電気的に接続され、2値または3値のデジタル値を保持する機能を有する。メモリ回路24において、トランジスタ25が有する半導体層29は、酸化物半導体である。つまり、トランジスタ25は、OSトランジスタである。メモリ回路24は、OSトランジスタを有するメモリ（以下、OSメモリともいう。）が好適である。

10

## 【0033】

金属酸化物のバンドギャップは2.5eV以上あるため、OSトランジスタは極小のオフ電流をもつ。一例として、ソースとドレイン間の電圧が3.5V、室温（25℃）下において、チャネル幅1μm当たりのオフ電流を $1 \times 10^{-20} \text{ A}$ 未満、 $1 \times 10^{-22} \text{ A}$ 未満、あるいは $1 \times 10^{-24} \text{ A}$ 未満とすることができます。すなわち、ドレイン電流のオン/オフ電流比を20桁以上150桁以下とすることができます。そのため、OSメモリは、OSトランジスタを介して保持ノードからリークする電荷量が極めて少ない。従って、OSメモリは不揮発性メモリ回路として機能できるため、アクセラレータのパワーゲーティングが可能となる。

## 【0034】

高密度で集積化された半導体装置は、回路の駆動による熱が発生する場合がある。この発熱により、トランジスタの温度が上がることで、当該トランジスタの特性が変化して、電界効果移動度の変化や動作周波数の低下などが起こることがある。OSトランジスタは、Siトランジスタよりも熱耐性が高いため、温度変化による電界効果移動度の変化が起こりにくく、また動作周波数の低下も起こりにくい。さらに、OSトランジスタは、温度が高くなっても、ドレイン電流がゲート-ソース間電圧に対して指数関数的に増大する特性を維持しやすい。そのため、OSトランジスタを用いることにより、高い温度環境下での安定した動作を行うことができる。

20

## 【0035】

OSトランジスタに適用される金属酸化物は、Zn酸化物、Zn-Sn酸化物、Ga-Sn酸化物、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物（Mは、Ti、Ga、Y、Zr、La、Ce、Nd、SnまたはHf）などがある。特にMとしてGaを用いる金属酸化物をOSトランジスタに採用する場合、元素の比率を調整することで電界効果移動度等の電気特性に優れたトランジスタとすることができます。また、インジウムおよび亜鉛を含む酸化物に、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンゲステン、マグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

30

## 【0036】

OSトランジスタの信頼性、電気特性の向上のため、半導体層に適用される金属酸化物は、CAAC-OS、CAC-OS、nc-OSなどの結晶部を有する金属酸化物であることが好ましい。CAAC-OSとは、c-axis-aligned crystal line oxide semiconductorの略称である。CAC-OSとは、cloud-aligned Composite oxide semiconductorの略称である。nc-OSとは、nanocrystalline oxide semiconductorの略称である。

40

## 【0037】

CAAC-OSは、c軸配向性を有し、かつa-b面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域との間で格子配列の

50

向きが変化している箇所を指す。

【0038】

CAC-OSは、キャリアとなる電子（または正孔）を流す機能と、キャリアとなる電子を流さない機能とを有する。電子を流す機能と、電子を流さない機能とを分離させることで、双方の機能を最大限に高めることができる。つまり、CAC-OSをOSトランジスタのチャネル形成領域に用いることで、高いオン電流と、極めて低いオフ電流との双方を実現できる。

【0039】

金属酸化物は、バンドギャップが大きく、電子が励起されにくくこと、ホールの有効質量が大きいことなどから、OSトランジスタは、一般的なSiトランジスタと比較して、アバランシェ崩壊等が生じにくく場合がある。従って、例えばアバランシェ崩壊に起因するホットキャリア劣化等を抑制できる。ホットキャリア劣化を抑制できることで、高いドレイン電圧でOSトランジスタを駆動することができる。

10

【0040】

OSトランジスタは、電子を多数キャリアとする蓄積型トランジスタである。そのため、pn接合を有する反転型トランジスタ（代表的には、Siトランジスタ）と比較して短チャネル効果の一つであるDIBL（Drain-Induced Barrier Lowering）の影響が小さい。つまり、OSトランジスタは、Siトランジスタよりも短チャネル効果に対する高い耐性を有する。

【0041】

OSトランジスタは、短チャネル効果に対する耐性が高いために、OSトランジスタの信頼性を劣化させずに、チャネル長を縮小できるので、OSトランジスタを用いることで回路の集積度を高めることができる。チャネル長が微細化するのに伴いドレイン電界が強まるが、上掲したように、OSトランジスタはSiトランジスタよりもアバランシェ崩壊が起きにくい。

20

【0042】

また、OSトランジスタは、短チャネル効果に対する耐性が高いために、Siトランジスタよりもゲート絶縁膜を厚くすることが可能となる。例えば、チャネル長及びチャネル幅が50nm以下の微細なトランジスタにおいても、10nm程度の厚いゲート絶縁膜を設けることが可能な場合がある。ゲート絶縁膜を厚くすることで、寄生容量を低減することができるため、回路の動作速度を向上できる。またゲート絶縁膜を厚くすることで、ゲート絶縁膜を介したリーク電流が低減されるため、静的消費電流の低減につながる。

30

【0043】

以上より、アクセラレータ20は、OSメモリであるメモリ回路24を有することで電源電圧の供給が停止してもデータを保持できる。そのため、アクセラレータ20のパワーゲーティングが可能となり、消費電力の大幅な低減を図ることができる。

【0044】

OSトランジスタで構成されるメモリ回路24は、Si CMOSで構成することができる演算回路23と積層して設けることができる。そのため、回路面積の増加を招くことなく、配置することができる。メモリ回路24と演算回路23とは、演算回路23が設けられる基板表面に対して概略垂直な方向に延在して設けられる配線31を介して電気的に接続される。なお「概略垂直」とは、85度以上95度以下の角度で配置されている状態をいう。

40

【0045】

メモリ回路24は、NOSRAMの回路構成とすることができます。「NOSRAM（登録商標）」とは、「Nonvolatile Oxide Semiconductor RAM」の略称である。NOSRAMは、メモリセルが2トランジスタ型（2T）、又は3トランジスタ型（3T）ゲインセルであり、アクセストランジスタがOSトランジスタであるメモリのことをいう。OSトランジスタはオフ状態でソースとドレインとの間を流れる電流、つまりリーク電流が極めて小さい。NOSRAMは、リーク電流が極めて小さ

50

い特性を用いてデータに応じた電荷をメモリ回路内に保持することで、不揮発性メモリとして用いることができる。特にN O S R A Mは保持しているデータを破壊することなく読み出しすること（非破壊読み出し）が可能なため、データ読み出し動作のみを大量に繰り返す、ニューラルネットワークの積和演算の並列処理に適している。

#### 【 0 0 4 6 】

演算処理部21は、デジタル値を用いた演算処理を行う機能を有する。デジタル値はノイズの影響を受けにくい。そのためアクセラレータ20は、高い精度の演算結果が要求される演算処理を行うのに適している。なお演算処理部21は、Si CMOS、すなわちシリコンをチャネル形成領域に有するトランジスタ（Siトランジスタ）で構成されること好ましい。当該構成とすることでOSトランジスタと積層して設けることができる。

10

#### 【 0 0 4 7 】

演算回路23は、メモリ部22のメモリ回路24のそれぞれに保持されたデジタル値のデータを用いて、整数演算、単精度浮動小数点演算、倍精度浮動小数点演算などの処理のいずれか一を行う機能を有する。演算回路23は、積和演算といった同じ処理を繰り返し実行する機能を有する。

#### 【 0 0 4 8 】

なお演算回路23は、メモリ回路24の読み出ビット線毎、つまり一列（Column）毎に1つの演算回路23を設ける構成とする（Column-Parallel Calculation）。当該構成とすることで、メモリ回路24の1行分（最大で全ビット線）のデータを並列で演算処理することができる。CPU10を用いた積和演算に比べて、CPUとメモリ間のデータバスサイズ（32ビット、など）に制限されないことから、Column-Parallel Calculationでは、演算の並列度を大幅に上げることができるために、AI技術であるディープニューラルネットワークの学習（深層学習）、浮動小数点演算を行う科学技術計算などの膨大な演算処理に係る演算効率の向上を図ることができる。加えてメモリ回路24から出力されるデータの演算を完了させて読み出すことができるため、メモリアクセス（CPUとメモリ間のデータ転送やCPUでの演算）で生じる電力を削減することができ、発熱および消費電力の増加を抑制することができる。さらに、演算回路23とメモリ回路24の物理的な距離を近づけること、例えば積層によって配線距離が短くできることで、信号線に生じる寄生容量を削減できるため、低消費電力化が可能である。

20

#### 【 0 0 4 9 】

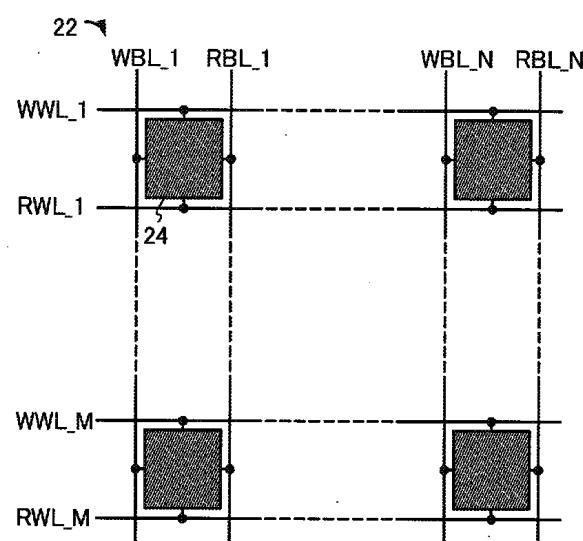

バス30は、CPU10とアクセラレータ20とを電気的に接続する。つまりCPU10とアクセラレータ20とは、バス30を介してデータ伝送を行うことができる。

#### 【 0 0 5 0 】

本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置を小型化することができる。または、本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置を低消費電力化することができる。または、本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置において、発熱を抑制することができる。または、本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置において、CPUとメモリとして機能する半導体装置との間のデータ転送回数を削減することができる。換言すれば計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置は非ノイマン型アーキテクチャを有し、処理速度の増加に伴って消費電力が大きくなるノイマン型アーキテクチャと比較して、極めて少ない消費電力で並列処理を行うことができる。

40

#### 【 0 0 5 1 】

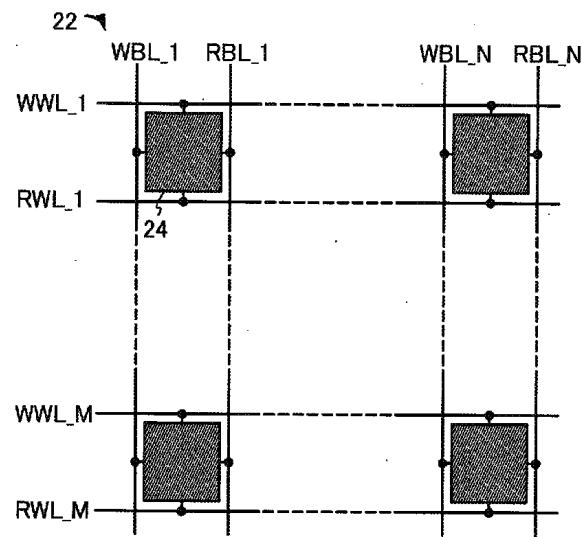

図2Aは、本発明の半導体装置100が有するメモリ部22に適用可能な回路構成例について説明する図である。図2Aでは、M行N列（M、Nは2以上の自然数）行列方向に並べて配置された書込用ワード線W WL\_1乃至W WL\_M、読み出用ワード線R WL\_1乃至R WL\_M、書込用ビット線W BL\_1乃至W BL\_N、および読み出用ビット線R BL

50

—1乃至RBL\_Nを図示している。また各ワード線およびビット線に接続されたメモリ回路24を図示している。

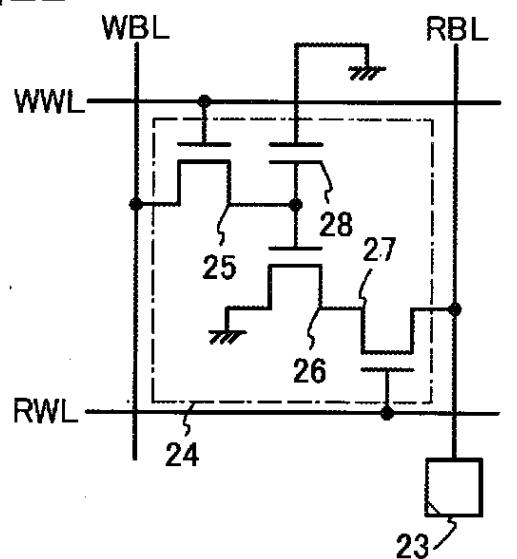

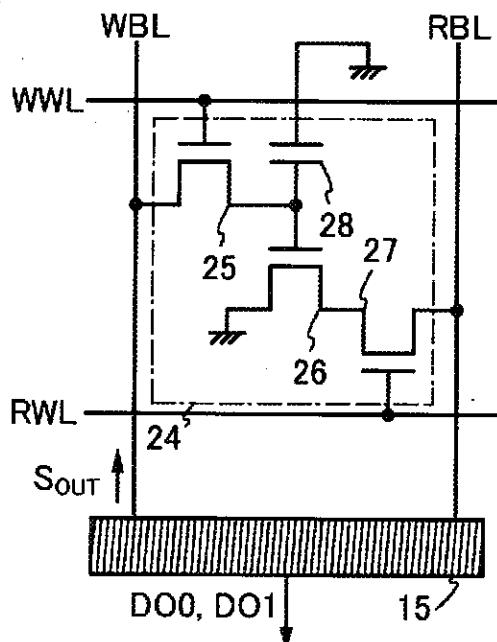

【0052】

図2Bは、メモリ回路24に適用可能な回路構成例について説明する図である。メモリ回路24は、トランジスタ25、トランジスタ26、トランジスタ27、容量素子28(キャパシタともいう)を有する。

【0053】

トランジスタ25のソースまたはドレインの一方は、書込用ビット線WBLに接続される。トランジスタ25のゲートは、書込用ワード線WWLに接続される。トランジスタ25のソースまたはドレインの他方は、容量素子28の一方の電極およびトランジスタ26のゲートに接続される。トランジスタ26のソースまたはドレインの一方および容量素子28の他方の電極は、固定電位たとえばグラウンド電位を与える配線に接続される。トランジスタ26のソースまたはドレインの他方は、トランジスタ27のソースまたはドレインの一方に接続される。トランジスタ27のゲートは、読出用ワード線RWLに接続される。トランジスタ27のソースまたはドレインの他方は、読出用ビット線RBLに接続される。読出用ビット線RBLは、上述したように、演算回路23が設けられる基板表面に對して概略垂直な方向に延在して設けられる配線31等を介して、演算回路23に接続される。

10

【0054】

図2Bに示すメモリ回路24の回路構成は、3トランジスタ型(3T)ゲインセルのNOSRAMに相当する。トランジスタ25乃至トランジスタ27は、OSトランジスタである。OSトランジスタはオフ状態でソースとドレインとの間を流れる電流、つまりリーク電流が極めて小さい。NOSRAMは、リーク電流が極めて小さい特性を用いてデータに応じた電荷をメモリ回路内に保持することで、不揮発性メモリとして用いることができる。

20

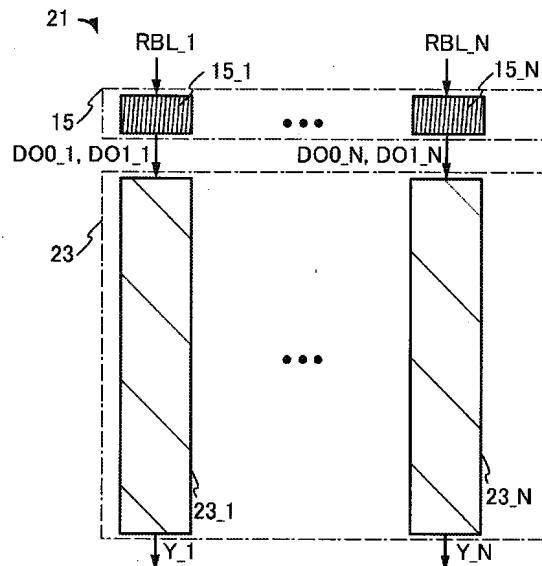

【0055】

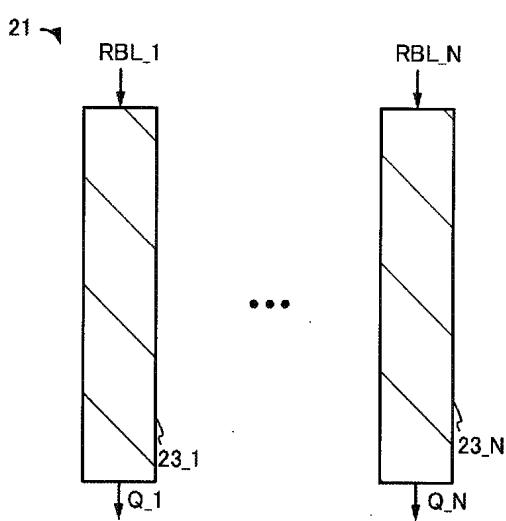

図3Aは、本発明の半導体装置100が有する演算処理部21に適用可能な回路構成例について説明する図である。演算処理部21は、N個の演算回路23\_1乃至演算回路23\_Nを有する。N個の演算回路23\_1乃至演算回路23\_Nはそれぞれ、N本の読出用ビット線RBL\_1乃至読出用ビット線RBL\_Nのいずれか一の信号が入力され、出力信号Q\_1乃至Q\_Nを出力する。読出用ビット線RBL\_1乃至読出用ビット線RBL\_Nの信号は、センスアンプ等で増幅して読み出す構成としてもよい。出力信号Q\_1乃至Q\_Nは、メモリ回路24に保持したデータを用いて積和演算を行うことで得られるデータに相当する。

30

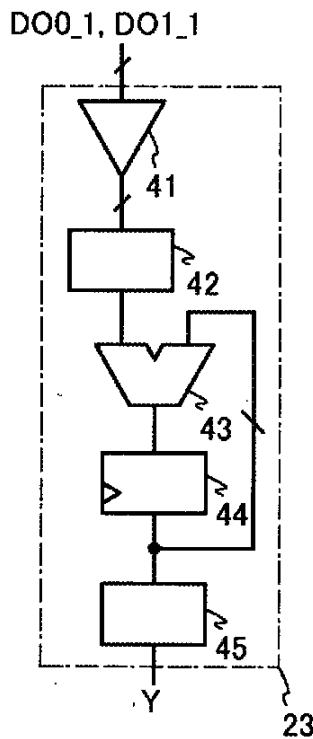

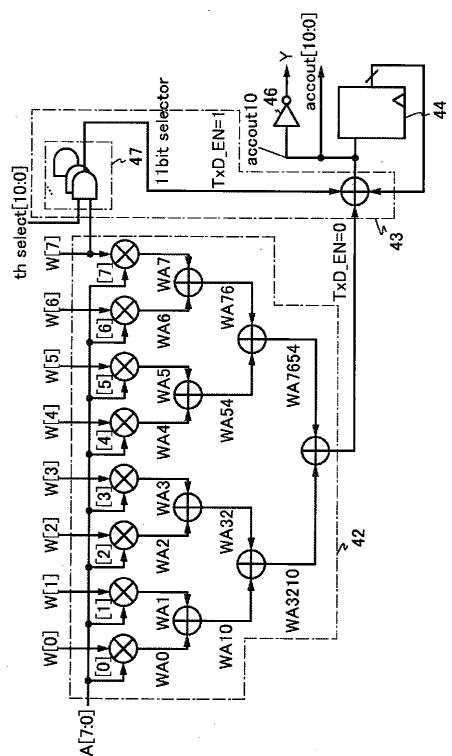

【0056】

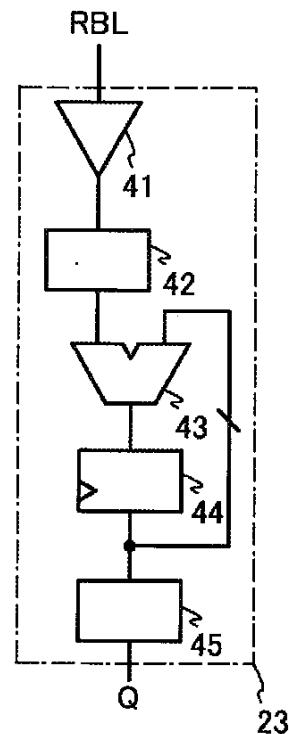

図3Bは、演算回路23\_1乃至演算回路23\_Nに適用可能な演算回路23の回路構成例を説明する図である。図4は、Binary Neural Network(BNN)のアーキテクチャに基づく演算処理を実行するための回路である。演算回路23は、読出用ビット線RBLの信号が与えられる読出回路41と、ビット積和演算器42と、アキュムレータ43、ラッチ回路44、および出力信号Qを出力する符号化回路45を有する。

40

【0057】

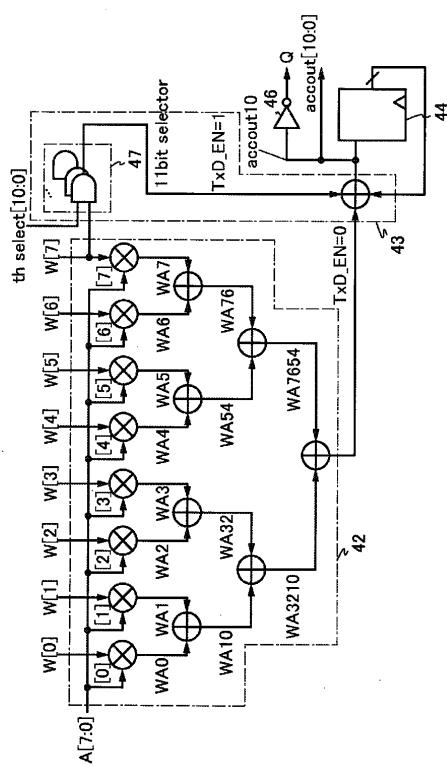

図3Bで図示した演算回路23の構成について、より詳細を示す構成例を図4に図示する。図4では、8ビットの信号(W[0]乃至W[7]、A[0]乃至A[7])の積和演算を行い、1ビットの出力信号Q、11ビットの出力信号(accumout[10:0])を出力する構成を一例として図示している。図3Bでは、メモリアクセスは1クロックで1行を選択するため、M個(=1ビット×M行)の積とその和をMクロックで実行する。図4の演算回路では、同じM個の積とその和を8並列×1ビット×M/8行で実行できるため、M/8クロックを要する。したがって、図4の構成は並列に積和演算を実行することで演算時間を短縮できるため、演算効率を向上できる。

【0058】

50

図4において、ビット積和演算器42は、8ビットの信号( $W[0]$ 乃至 $W[7]$ 、 $A[0]$ 乃至 $A[7]$ )が入力される積算器および当該積算器で得られた値が入力される加算器を有する。図4に示すように、8並列で演算される1ビットの信号の積をWA0乃至WA7、さらにその和をWA10、WA32、WA54、WA76、さらにその和をWA3210、WA7654として図示している。

#### 【0059】

図4において、加算器として機能するアキュムレータ43は、ビット積和演算器42の信号とラッチ回路44の出力信号との和をラッチ回路44に出力する。なおアキュムレータ43は、制御信号 $T \times D\_EN$ に応じて加算器に入力する信号が切り替えられる。制御信号 $T \times D\_EN$ が0( $T \times D\_EN = 0$ )でビット積和演算器42の信号とラッチ回路44の出力信号との和をラッチ回路44に出力する。制御信号 $T \times D\_EN$ が1( $T \times D\_EN = 1$ )でロジック回路47の信号(11bit selector)とラッチ回路44の出力信号との和をラッチ回路44に出力する。

10

#### 【0060】

図4において、AND回路で構成されるロジック回路47は、信号 $A[0]$ 乃至 $A[7]$ と信号 $W[0]$ 乃至 $W[7]$ の積和演算が完了した後、バッチノーマライゼーションのためのデータを足し合わせる。具体的には切替信号( $th\_select[10:0]$ )で切り替えながら、信号 $W[7]$ を足し合わせる。なお、バッチノーマライゼーションのためのデータは、例えば信号 $W[7]$ 以外の信号 $W[0]$ 乃至 $W[6]$ からも同時に読み出して選択する構成としてもよい。バッチノーマライゼーションは、ニューラルネットワークにおける各層の出力データの分布が一定に収まるように調整するための動作である。例えば、ニューラルネットワークにおける演算によく利用される画像データは、学習に用いるデータの分布がばらつきやすいため、予測データ(入力データ)の分布と異なることがある。バッチノーマライゼーションは、ニューラルネットワークの中間層への入力データの分布を平均0、分散1のガウス分布に正規化することで、ニューラルネットワークにおける学習の精度を高めることができる。Binary Neural Network(BNN)では活性化によって各層の出力結果が2値化されるため、しきい値に対してデータ分布の偏りを抑制することで、適切に活性化、つまり情報を分別できるようになる。

20

#### 【0061】

ラッチ回路44は、アキュムレータ43の出力信号( $account[10:0]$ )を保持する。バッチノーマライゼーションによって次のニューラルネットワークにおける層(NN層)に渡す2値データはラッチ回路44が保持する積和演算結果の最上位ビットとなる。出力信号( $account[10:0]$ )において、最上位のビットの信号( $account10$ )は、2の補数で演算されたラッチデータの符号を表し、そのプラスデータを1、マイナスデータを0として次のNN層に渡すため、符号化回路として機能するインバタ回路46で反転され、出力信号Qとして出力される。Qは中間層の出力であるため、アクセラレータ20内のバッファメモリ(入力バッファとも言う)に一時的に保持された後、次層の演算に使用される。

30

#### 【0062】

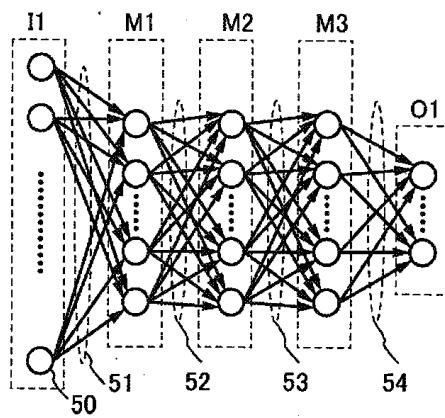

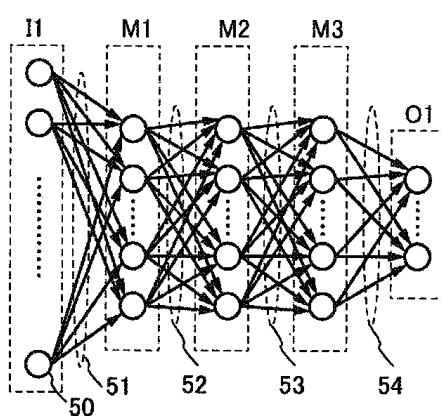

図5Aには、Binary Neural Network(BNN)のアーキテクチャに基づく、階層型のニューラルネットワークを図示する。図5Aでは、ニューロン50、入力層1層(I1)、中間層3層(M1乃至M3)、出力層1層(O1)の全結合型のニューラルネットワークを図示している。入力層I1におけるニューロン数を786、中間層M1乃至M3におけるニューロン数を256、出力層O1におけるニューロン数を10とすると、各層(層51、層52、層53および層54)の結合数は( $784 \times 256$ ) + ( $256 \times 256$ ) + ( $256 \times 256$ ) + ( $256 \times 10$ )で計334336個となる。つまり、ニューラルネットワーク計算に必要な重みパラメータが合計330Kビット程度であるため、小規模システムでも十分実装可能なメモリ容量とすることができます。

40

#### 【0063】

次に、図5Aに図示するニューラルネットワークの演算ができる、半導体装置100の

50

詳細なブロック図について図 5 B に示す。

【 0 0 6 4 】

図 5 B では、図 1 A および図 1 B で説明した、演算処理部 2 1、演算回路 2 3、メモリ部 2 2、メモリ回路 2 4、および配線 3 1 の他、図 1 A および図 1 B で図示する各構成を駆動するための周辺回路の構成例について図示している。

【 0 0 6 5 】

図 5 B では、コントローラ 6 1、ロウデコーダ 6 2、ワード線ドライバ 6 3、カラムデコーダ 6 4、書き込みドライバ 6 5、プリチャージ回路 6 6、センスアンプ 6 7、セレクタ 6 8、入力バッファ 7 1 および演算制御回路 7 2 を図示している。

【 0 0 6 6 】

図 6 A は、図 5 B に図示する各構成について、メモリ部 2 2 を制御するブロックを抜き出した図である。図 6 A では、コントローラ 6 1、ロウデコーダ 6 2、ワード線ドライバ 6 3、カラムデコーダ 6 4、書き込みドライバ 6 5、プリチャージ回路 6 6、センスアンプ 6 7、セレクタ 6 8 を抜き出して図示している。

【 0 0 6 7 】

コントローラ 6 1 は、外部からの入力信号を処理して、ロウデコーダ 6 2 およびカラムデコーダ 6 4 の制御信号を生成する。外部からの入力信号は、書き込みイネーブル信号や読み出しイネーブル信号などのメモリ部 2 2 を制御するための制御信号である。またコントローラ 6 1 は、C P U 1 0 との間でバスを介してメモリ部 2 2 に書き込まれるデータあるいはメモリ部 2 2 から読み出されるデータの入出力が行われる。

【 0 0 6 8 】

ロウデコーダ 6 2 は、ワード線ドライバ 6 3 を駆動するための信号を生成する。ワード線ドライバ 6 3 は、書き用ワード線 W W L および読み出用ワード線 R W L に与える信号を生成する。カラムデコーダ 6 4 は、センスアンプ 6 7 および書き込みドライバ 6 5 を駆動するための信号を生成する。センスアンプ 6 7 は、読み出用ビット線 R B L の電位を増幅する。書き込みドライバは、読み出用ビット線 R B L および書き用ビット線 W B L を制御するための信号を生成する。プリチャージ回路 6 6 は、読み出用ビット線 R B L などをプリチャージする機能を有する。メモリ部 2 2 のメモリ回路 2 4 から読み出される信号は、演算回路 2 3 に入力される他、セレクタ 6 8 を介して出力することができる。セレクタ 6 8 は、バス幅に応じた分のデータを順次読み出し、コントローラ 6 1 を介して必要なデータを C P U 1 0 等に出力することができる。

【 0 0 6 9 】

図 6 B は、図 5 B に図示する各構成について、演算処理部 2 1 を制御するブロックを抜き出した図である。

【 0 0 7 0 】

コントローラ 6 1 は、外部からの入力信号を処理して、演算制御回路 7 2 の制御信号を生成する。またコントローラ 6 1 は、演算処理部 2 1 が有する演算回路 2 3 を制御するための各種信号を生成する。またコントローラ 6 1 は、入力バッファ 7 1 を介して、演算結果に関するデータを入出力する。入力バッファ 7 1 を利用することで、C P U のデータバス幅以上のビット数の並列計算が可能となる。また膨大な数の重みパラメータを C P U 1 0 との間で転送する回数を削減できるため、低消費電力化を図ることができる。

【 0 0 7 1 】

本発明の一態様は、計算量とパラメータ数が膨大な A I 技術などのアクセラレータとして機能する半導体装置を小型化することができる。または、本発明の一態様は、計算量とパラメータ数が膨大な A I 技術などのアクセラレータとして機能する半導体装置を低消費電力化することができる。または、本発明の一態様は、計算量とパラメータ数が膨大な A I 技術などのアクセラレータとして機能する半導体装置において、発熱を抑制することができる。または、本発明の一態様は、計算量とパラメータ数が膨大な A I 技術などのアクセラレータとして機能する半導体装置において、C P U とメモリとして機能する半導体装置との間のデータ転送回数を削減することができる。換言すれば計算量とパラメータ数が

10

20

30

40

50

膨大な A I 技術などのアクセラレータとして機能する半導体装置は非ノイマン型アーキテクチャを有し、処理速度の増加に伴って消費電力が大きくなるノイマン型アーキテクチャと比較して、極めて少ない消費電力で並列処理を行うことができる。

【 0 0 7 2 】

( 実施の形態 2 )

本発明の一態様である半導体装置の構成、および動作等について説明する。なお本実施の形態において、上記実施の形態と同じ符号が付される構成についての繰り返しの説明を省略する場合がある。

【 0 0 7 3 】

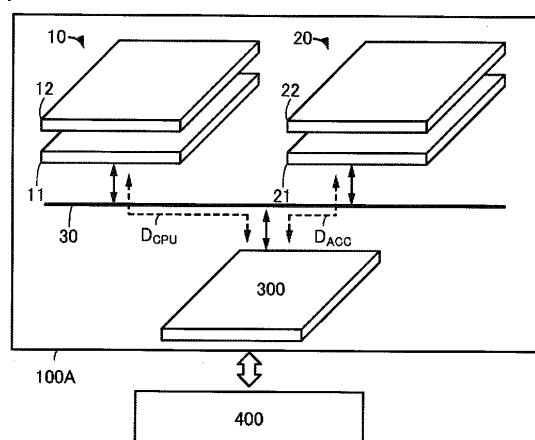

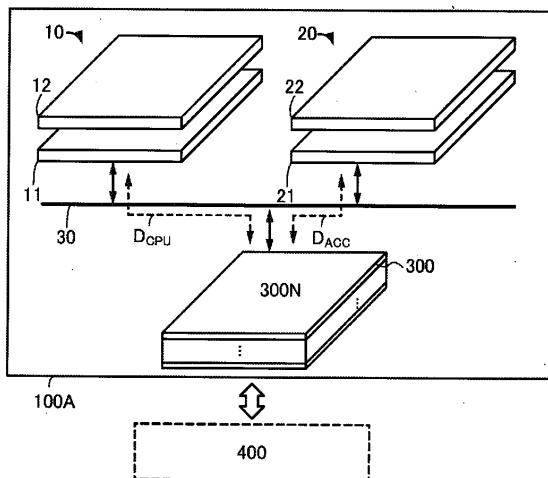

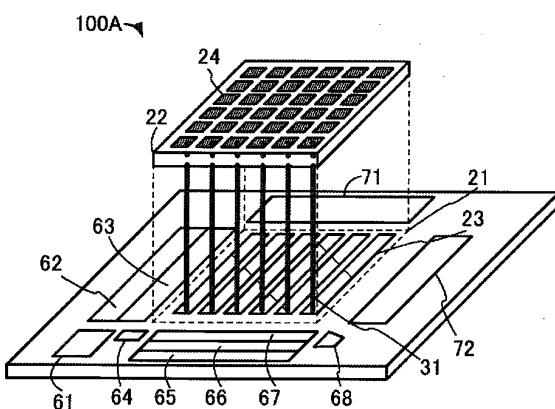

図 7 A および図 7 B は、本発明の一態様である半導体装置 1 0 0 A を説明するための図である。図 7 A および図 7 B における半導体装置 1 0 0 A では、一例として、C P U 1 0 、アクセラレータ 2 0 およびバス 3 0 を図示している。C P U 1 0 は、C P U コア 1 1 およびバックアップ回路 1 2 を有する。アクセラレータ 2 0 は、演算処理部 2 1 およびメモリ部 2 2 を有する。演算処理部 2 1 は、駆動回路 1 5 および演算回路 2 3 を有する。駆動回路 1 5 は、メモリ部 2 2 を駆動するための回路である。メモリ部 2 2 は、メモリ回路 2 4 を有する。メモリ部 2 2 は、デバイスマモリ、共有メモリという場合がある。メモリ回路 2 4 は、チャネル形成領域を有する半導体層 2 9 を有するトランジスタ 2 5 を有する。駆動回路 1 5 とメモリ回路 2 4 とは、配線 3 1 を介して電気的に接続される。

10

【 0 0 7 4 】

メモリ回路 2 4 は、演算処理部 2 1 が有する演算回路 2 3 と配線 3 1 および駆動回路 1 5 を介して電気的に接続される。メモリ回路 2 4 は、2 値または 3 値のデータをアナログの電圧値として保持する機能を有する。当該構成とすることで、B i n a r y N e u r a l N e t w o r k ( B N N ) 、およびT e r n a r y N e u r a l N e t w o r k ( T N N ) といったアーキテクチャに基づく演算処理を演算処理部 2 1 で効率的に行うことができる。

20

【 0 0 7 5 】

駆動回路 1 5 は、メモリ部 2 2 にデータを書き込むための書き込み回路およびメモリ部 2 2 からデータを読み出すための読み出し回路を有する。書き込み回路は、2 値または 3 値のデータ信号の書き込みを切り替える切替信号、書き込み制御信号、およびデータ信号等の各種信号に応じて、メモリ部 2 2 にあるメモリ回路 2 4 に書き込むデータを 2 値または 3 値の電圧値に切り替えて出力する機能を有する。書き込み回路は、複数の信号が入力されるロジック回路で構成される。読み出し回路は、複数の参照電圧を用いて、メモリ部 2 2 にあるメモリ回路 2 4 に保持された電圧値を 2 値または 3 値のデータ信号に切り替えて読み出す機能を有する。読み出し回路は、センスアンプの機能を有する。

30

【 0 0 7 6 】

O S トランジスタで構成されるメモリ回路 2 4 と駆動回路 1 5 とは、駆動回路 1 5 および演算回路 2 3 が設けられる基板表面に対して概略垂直な方向に延在して設けられる配線 3 1 を介して電気的に接続される。なお「概略垂直」とは、85 度以上 95 度以下の角度で配置されている状態をいう。なおメモリ回路 2 4 に接続されるビット線が書き込みビット線と読み出しビット線の場合、別々の配線を介して接続されることが好ましい。例えば書き込みビット線は、駆動回路 1 5 および演算回路 2 3 が設けられる基板表面に概略垂直に設けられた配線（第 1 配線）を介して書き込み回路に接続される。また例えば読み出しビット線は、駆動回路 1 5 および演算回路 2 3 が設けられる基板表面に概略垂直に設けられた配線（第 2 配線）を介して読み出し回路に接続される。

40

【 0 0 7 7 】

次いで図 8 A では、図 7 A および図 7 B で説明した半導体装置 1 0 0 A の構成に加え、バス 3 0 に接続された O S メモリ 3 0 0 の他、D R A M などで構成されるメインメモリ 4 0 0 を図示している。また図 8 A では、O S メモリ 3 0 0 と C P U 1 0 との間のデータをデータ D C P U として図示している。また図 8 A では、O S メモリ 3 0 0 とアクセラレータ 2 0 との間のデータをデータ D A C C として図示している。

50

## 【0078】

上述したように本発明の一態様の構成では、アクセラレータ20において、2値または3値のアナログの電圧値をデータとして保持しつづけることができるとともに、演算回路で演算して得られる演算結果をCPU10に出力する構成とすることができる。そのため、演算処理のためのOSメモリ300からのデータDACCを削減することができる。またCPU10の演算処理量を削減することができるため、OSメモリ300とCPU10との間のデータDCPUも削減することができる。つまり本発明の一態様の構成では、バス30を介したアクセス数の低減、転送するデータ量の削減を図ることができる。

## 【0079】

なおCPU10におけるバックアップ回路12およびアクセラレータ20におけるメモリ部22は、Si CMOSで構成することができるCPUコア11および演算処理部21と積層して設けることができる。そのため、回路面積の増加を招くことなく、配置することができる。

10

## 【0080】

またOSメモリ300に適用可能な記憶回路としては、DOSRAMあるいはNOSRAMが好ましい。DOSRAM(登録商標)とは、「Dynamic Oxide Semiconductor Random Access Memory(RAM)」の略称であり、1T(トランジスタ)1C(容量)型のメモリセルを有するRAMを指す。DOSRAMは、NOSRAMと同様に、OSトランジスタのオフ電流が低いことを利用したメモリである。

20

## 【0081】

DOSRAMは、OSトランジスタを用いて形成されたDRAMであり、DOSRAMは、外部から送られてくる情報を一時的に格納するメモリである。DOSRAMは、OSトランジスタを含むメモリセルと、Siトランジスタ(チャネル形成領域にシリコンを有するトランジスタ)を含む読み出し回路部を有する。上記メモリセルと読み出し回路部は、積層された異なる層に設けることができるため、DOSRAMは、全体の回路面積を小さくすることができる。また、DOSRAMは、メモリセルアレイを細かく分けて、効率的に配置することができる。

## 【0082】

なおOSメモリ300において図8Bに図示するようにOSメモリ300は、OSトランジスタを有する層を積層して形成し、DOSRAMを高集積化したOSメモリ300Nとしてすることで、単位面積あたりの記憶容量を大きくすることができる。この場合、半導体装置100Aと別に設けるメインメモリ400を省略することも可能である。

30

## 【0083】

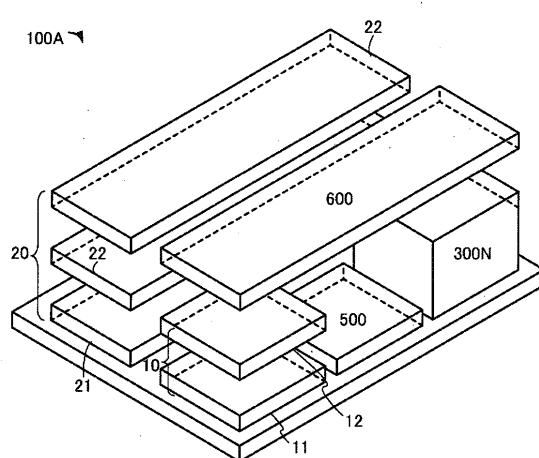

OSメモリ300Nを含め、半導体装置100Aが有するCPU10およびアクセラレータ20が有する回路の一部をOSトランジスタで構成することで、各回路を一体化した1つの集積回路とすることができる。図9には、CPU10、アクセラレータ20およびOSメモリ300Nを密結合させたSOCとして機能する半導体装置100Aの模式図について図示する。

## 【0084】

図9に図示するように、CPU10において、CPUコア11の上層にあるOSトランジスタを有する層にバックアップ回路12を設ける構成とすることができる。また図9に図示するように、アクセラレータ20において、演算処理部21の上層にあるOSトランジスタを有する層にメモリ部22を設けることができる。また図9に図示するように、メモリ部22と同様に積層されたOSメモリ300Nを配置することができる。その他、Siトランジスタを有するコントロール回路500、OSトランジスタを有するロジック回路600等を設ける構成とすることができる。なおロジック回路600は、OSトランジスタで代替可能な、切り替えスイッチなどの簡易なロジック回路等が好ましい。

40

## 【0085】

図9に図示するように、CPU10、アクセラレータ20およびメモリ300N等の各

50

回路を密結合させたS o Cの場合、発熱の問題があるが、O Sトランジスタは熱による電気特性の変動量がS iトランジスタと比べて小さいため、好適である。また、図9に図示するように三次元方向において回路を集積化することによって、シリコン貫通電極（T h r o u g h S i l i c o n V i a : T S V）などを用いた積層構造などと比較して寄生容量を小さくすることができる。各配線の充放電に要する消費電力を削減することができる。そのため、演算処理効率の向上を図ることができる。

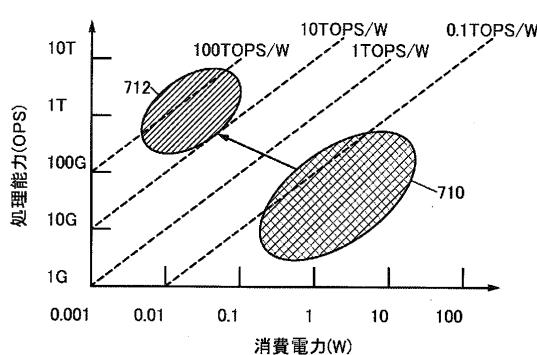

#### 【0086】

図10Aは、処理性能（O P S : O p e r a t i o n s P e r S e c o n d）と、消費電力（W）との関係を説明する図である。なお、図10Aにおいて、縦軸が処理能力を、横軸が消費電力を、それぞれ表している。また、図10A中には、演算効率の指標として、0.1TOPS/W（Tera Operations Per Second/W）、1TOPS/W、10TOPS/W、及び100TOPS/Wを、破線にてそれぞれ明示してある。

#### 【0087】

また、図10Aにおいて、領域710が従来の汎用A Iアクセラレータ（ノイマン型）が含まれる領域を、領域712が本発明の一態様の半導体装置が含まれる領域を、それぞれ示している。なお、領域710には、例えば、C P U（C e n t r a l P r o c e s s i n g U n i t）、G P U（G r a p h i c s P r o c e s s i n g U n i t）、F P G A（F i e l d - P r o g r a m m a b l e G a t e A r r a y）などが含まれる。

#### 【0088】

図10Aに示すように、本発明の一態様の半導体装置を適用することで、従来の汎用A Iアクセラレータ（ノイマン型）よりも、2桁程度の消費電力を低減することができ、且つ処理性能を大幅（例えば1000倍以上）に向上させることができる。なお、本発明の一態様の半導体装置を適用することで、100TOPS/W以上の演算効率が期待できる。

#### 【0089】

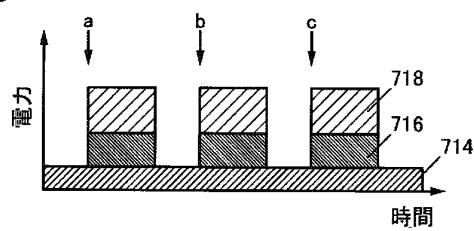

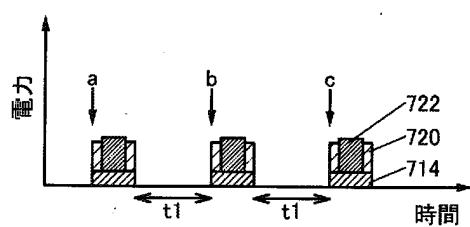

ここで、従来構成と、本発明の一態様の半導体装置を適用する構成との具体例について、図10B、及び図10Cを用いて説明する。図10Bが、画像認識における従来構成の半導体装置の消費電力のイメージ図を表し、図10Cが、画像認識における本発明の一態様の構成を用いる半導体装置の消費電力のイメージ図を表している。

#### 【0090】

なお、図10B、及び図10Cにおいて、縦軸が電力を、横軸が時間を、それぞれ表している。また、図10Bにおいて、電力714がリーク電力を、電力716がC P U電力を、電力718がメモリ電力を、それぞれ示している。また、図10Cにおいて、電力714がリーク電力を、電力720がC P U電力を、電力722がアクセラレータ電力を、それぞれ示している。なお、電力722には、演算回路、及びメモリ回路に用いられる電力も含まれる。

#### 【0091】

また、図10B、及び図10Cにおいて、矢印a、矢印b、及び矢印cは、それぞれ画像認識における信号を表している。なお、矢印a、矢印b、及び矢印cの信号が入力された際に、半導体装置にて、画像認識などの演算処理が開始されると仮定する。

#### 【0092】

図10Bに示すように、従来構成の半導体装置の場合、時間に対して一定のリーク電力（電力714）が生じている。一方で、図10Cに示すように、本発明の一態様の半導体装置を適用する構成の場合、C P U電力（電力720）、及びアクセラレータ電力（電力722）を使用している間はリーク電力（電力714）が生じているが、C P U電力（電力720）、及びアクセラレータ電力（電力722）を使用していない期間は、リーク電力（電力714）が発生しないノーマリーオフ駆動（図10C中に示す期間t1）とすることができる。これにより、消費電力を大幅に低減することが可能となる。すなわち、極低消費電力な半導体装置を提供することができる。

10

20

30

40

50

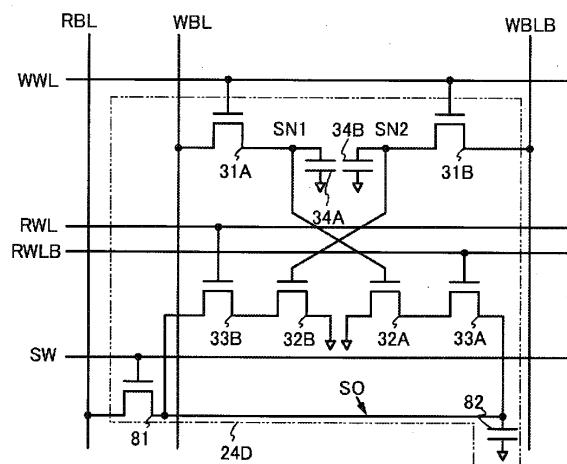

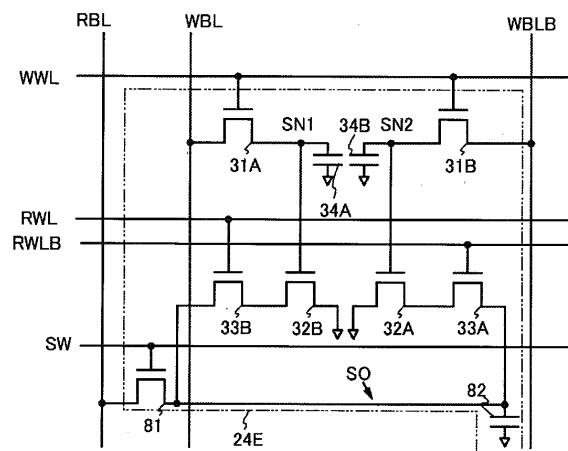

## 【0093】

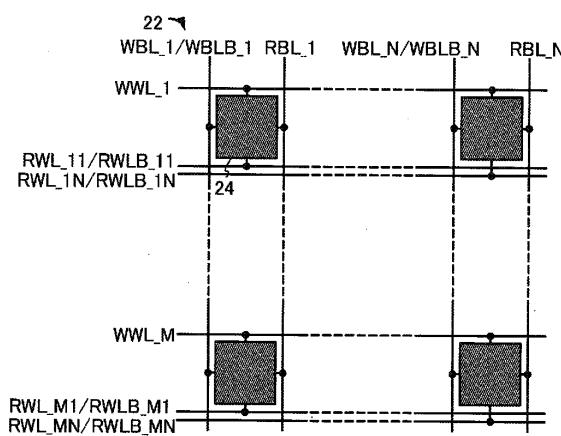

図11Aは、本発明の半導体装置100Aが有するメモリ部22に適用可能な回路構成例について説明する図である。図11Aでは、M行N列（M、Nは2以上の自然数）行列方向に並べて配置された書き込み用ワード線WWL\_1乃至WWL\_M、読み出し用ワード線RWL\_1乃至RWL\_M、書き込み用ビット線WBL\_1乃至WBL\_N、および読み出し用ビット線RBL\_1乃至RBL\_Nを図示している。また各ワード線およびビット線に接続されたメモリ回路24を図示している。

## 【0094】

図11Bは、メモリ回路24に適用可能な回路構成例について説明する図である。メモリ回路24は、トランジスタ25、トランジスタ26、トランジスタ27、容量素子28（キャパシタともいう）を有する。

10

## 【0095】

トランジスタ25のソースまたはドレインの一方は、書き込み用ビット線WBLに接続される。トランジスタ25のゲートは、書き込み用ワード線WWLに接続される。トランジスタ25のソースまたはドレインの他方は、容量素子28の一方の電極およびトランジスタ26のゲートに接続される。トランジスタ26のソースまたはドレインの一方および容量素子28の他方の電極は、固定電位たとえばグラウンド電位を与える配線に接続される。トランジスタ26のソースまたはドレインの他方は、トランジスタ27のソースまたはドレインの一方に接続される。トランジスタ27のゲートは、読み出し用ワード線RWLに接続される。トランジスタ27のソースまたはドレインの他方は、読み出し用ビット線RBLに接続される。書き込み用ビット線WBLおよび読み出し用ビット線RBLは、上述したように、演算回路23が設けられる基板表面に対して概略垂直な方向に延在して設けられる配線等を介して、駆動回路15に接続される。駆動回路15は、2値または3値のアナログの電圧値であるデータ信号SOUTを出力する。また駆動回路15は、メモリ回路24から読み出されるデータに応じた読み出し用ビット線RBLの電圧が与えられ、当該電圧に応じたデータ信号DO0、DO1を出力する。

20

## 【0096】

図11Bに示すメモリ回路24の回路構成は、3トランジスタ型（3T）ゲインセルのNOSRAMに相当する。トランジスタ25乃至トランジスタ27は、OSトランジスタである。OSトランジスタはオフ状態でソースとドレインとの間を流れる電流、つまりリーケ電流が極めて小さい。NOSRAMは、リーケ電流が極めて小さい特性を用いてデータに応じた電荷をメモリ回路内に保持することで、不揮発性メモリとして用いることができる。なお各トランジスタは、バックゲートを有する構成としてもよい。バックゲートを有することで、トランジスタ特性の向上を図ることができる。

30

## 【0097】

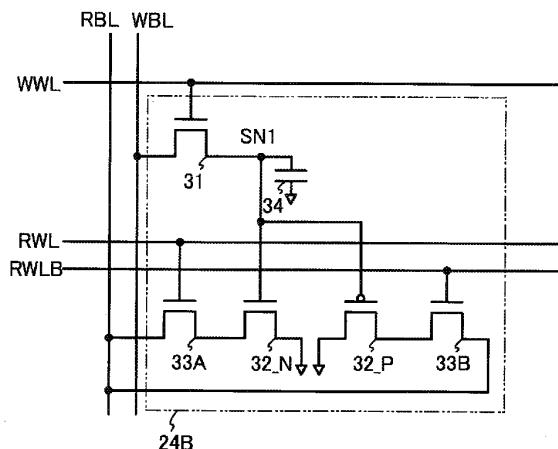

図12Aは、本発明の半導体装置100Aが有する演算処理部21に適用可能な回路構成例について説明する図である。演算処理部21は、駆動回路15および演算回路23を有する。駆動回路15は、N個の駆動回路15\_1乃至駆動回路15\_Nを有する。演算回路23は、N個の演算回路23\_1乃至演算回路23\_Nを有する。N個の駆動回路15\_1乃至駆動回路15\_Nはそれぞれ、N本の読み出し用ビット線RBL\_1乃至読み出し用ビット線RBL\_Nのいずれか一の信号が入力され、データ信号DO0\_1乃至DO0\_Nおよび/またはデータ信号DO1\_1乃至DO1\_Nを出力する。データ信号DO0\_1乃至DO0\_Nおよび/またはデータ信号DO1\_1乃至DO1\_Nは、演算回路23\_1乃至演算回路23\_Nに入力され、出力信号Y\_1乃至Y\_Nを得る。出力信号Y\_1乃至Y\_Nは、メモリ回路24に保持したデータを用いて積和演算を行うことで得られるデータに相当する。

40

## 【0098】

図12Bは、演算回路23\_1乃至演算回路23\_Nに適用可能な演算回路23の回路構成例を説明する図である。図13は、Binary Neural Network (BNN) またはTernary Neural Network (TNN) のアーキテクチャ

50

に基づく演算処理を実行するための回路である。演算回路 23 は、データ信号 D00 および / またはデータ信号 D01 が入力される読出回路 41 と、ビット積和演算器 42 と、アキュムレータ 43、ラッチ回路 44、および出力信号 Y を出力する符号化回路 45 を有する。

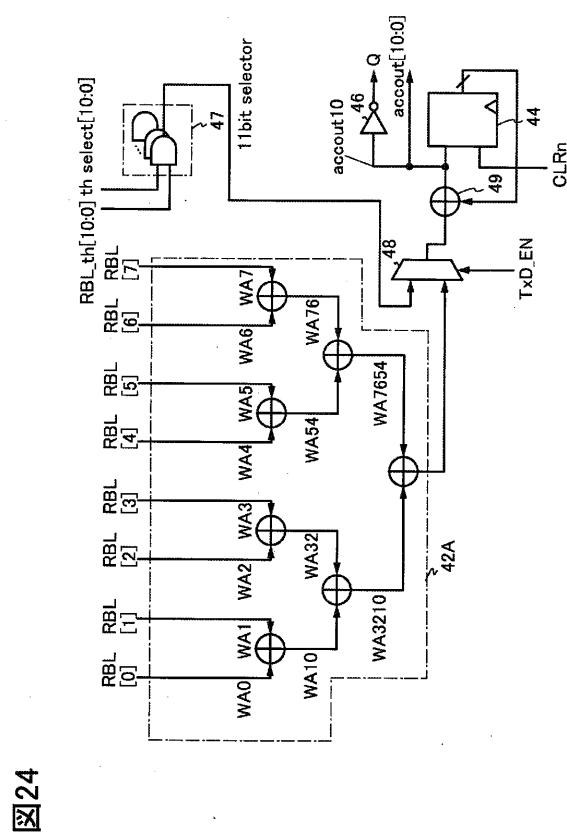

#### 【0099】

図 12B で図示した演算回路 23 の構成について、より詳細を示す構成例を図 13 に図示する。図 13 では、8 ビットの信号 (W[0] 乃至 W[7]、A[0] 乃至 A[7]) の積和演算を行い、出力信号 Y、11 ビットの出力信号 (account[10:0]) を出力する構成を一例として図示している。図 12B では、メモリアクセスは 1 クロックで 1 行を選択するため、M 個 (= 1 ビット × M 行) の積とその和を M クロックで実行する。図 13 の演算回路では、同じ M 個の積とその和を 8 並列 × 1 ビット × M / 8 行で実行できるため、M / 8 クロックを要する。したがって、図 13 の構成は並列に積和演算を実行することで演算時間を短縮できるため、演算効率を向上できる。

10

#### 【0100】

図 13 において、ビット積和演算器 42 は、8 ビットの信号 (W[0] 乃至 W[7]、A[0] 乃至 A[7]) が入力される積算器および当該積算器で得られた値が入力される加算器を有する。図 13 に示すように、8 並列で演算される 1 ビットの信号の積を WA0 乃至 WA7、さらにその和を WA10、WA32、WA54、WA76、さらにその和を WA3210、WA7654 として図示している。

20

#### 【0101】

図 13 において、加算器として機能するアキュムレータ 43 は、ビット積和演算器 42 の信号とラッチ回路 44 の出力信号との和をラッチ回路 44 に出力する。なおアキュムレータ 43 は、制御信号 TXD\_EN に応じて加算器に入力する信号が切り替えられる。制御信号 TXD\_EN が 0 (TXD\_EN = 0) でビット積和演算器 42 の信号とラッチ回路 44 の出力信号との和をラッチ回路 44 に出力する。制御信号 TXD\_EN が 1 (TXD\_EN = 1) でロジック回路 47 の信号 (11bit selector) とラッチ回路 44 の出力信号との和をラッチ回路 44 に出力する。

20

#### 【0102】

図 13 において、AND 回路で構成されるロジック回路 47 は、信号 A[0] 乃至 A[7] と信号 W[0] 乃至 W[7] の積和演算が完了した後、バッチノーマライゼーションのためのデータ、具体的には切替信号 (th select[10:0]) で切り替えながら、信号 W[7] を足し合わせる。なお、バッチノーマライゼーションのためのデータは、例えば信号 W[7] 以外の信号 W[0] 乃至 W[6] からも同時に読み出して選択する構成としてもよい。バッチノーマライゼーションは、ニューラルネットワークにおける各層の出力データの分布が一定に収まるように調整するための動作である。例えば、ニューラルネットワークにおける演算によく利用される画像データは、学習に用いるデータの分布がばらつきやすいため、予測データ (入力データ) の分布と異なることがある。バッチノーマライゼーションは、ニューラルネットワークの中間層への入力データの分布を平均 0、分散 1 のガウス分布に正規化することで、ニューラルネットワークにおける学習の精度を高めることができる。Binary Neural Network (BNN) では活性化によって各層の出力結果が 2 値化されるため、しきい値に対してデータ分布の偏りを抑制することで、適切に活性化、つまり情報を分別できるようになる。

30

#### 【0103】

ラッチ回路 44 は、アキュムレータ 43 の出力信号 (account[10:0]) を保持する。バッチノーマライゼーションによって次のニューラルネットワークにおける層 (NN 層) に渡す 2 値データはラッチ回路 44 が保持する積和演算結果の最上位ビットとなる。出力信号 (account[10:0]) において、最上位のビットの信号 (account10) は、2 の補数で演算されたラッチデータの符号を表し、そのプラスデータを 1、マイナスデータを 0 として次の NN 層に渡すため、符号化回路として機能するインバタ回路 46 で反転され、出力信号 Y として出力される。Y は中間層の出力であるため、ア

40

50

クセラレータ 20 内のバッファメモリ（入力バッファとも言う）に一時的に保持された後、次層の演算に使用される。

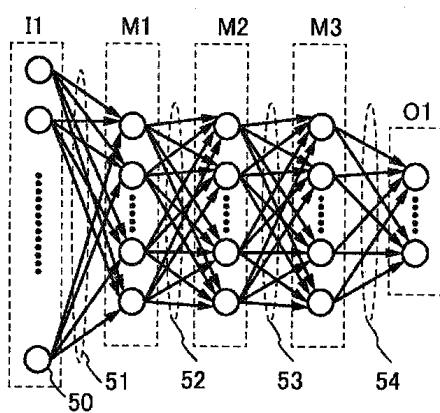

【0104】

図 14A には、Binary Neural Network (BNN) または Ternary Neural Network (TNN) のアーキテクチャに基づく、階層型のニューラルネットワークを図示する。図 14A では、ニューロン 50、入力層 1 層 (I1)、中間層 3 層 (M1 乃至 M3)、出力層 1 層 (O1) の全結合型のニューラルネットワークを図示している。入力層 I1 におけるニューロン数を 786、中間層 M1 乃至 M3 におけるニューロン数を 256、出力層 O1 におけるニューロン数を 10 とすると、例えば Binary Neural Network (BNN) では、各層（層 51、層 52、層 53 および層 54）の結合数は  $(784 \times 256) + (256 \times 256) + (256 \times 256) + (256 \times 10)$  で計 334336 個となる。つまり、ニューラルネットワーク計算に必要な重みパラメータが合計 330K ビット程度であるため、小規模システムでも十分実装可能なメモリ容量とすることができます。

【0105】

次に、図 14A に図示するニューラルネットワークの演算ができる、半導体装置 100A の詳細なブロック図について図 14B に示す。

【0106】

図 14B では、図 7A および図 7B で説明した、演算処理部 21、演算回路 23、メモリ部 22、メモリ回路 24、および配線 31 の他、図 7A および図 7B で図示する各構成を駆動するための周辺回路の構成例について図示している。

【0107】

図 14B では、コントローラ 61、ロウデコーダ 62、ワード線ドライバ 63、カラムデコーダ 64、書き込みドライバ 65、プリチャージ回路 66、センスアンプ 67、セレクタ 68、入力バッファ 71 および演算制御回路 72 を図示している。

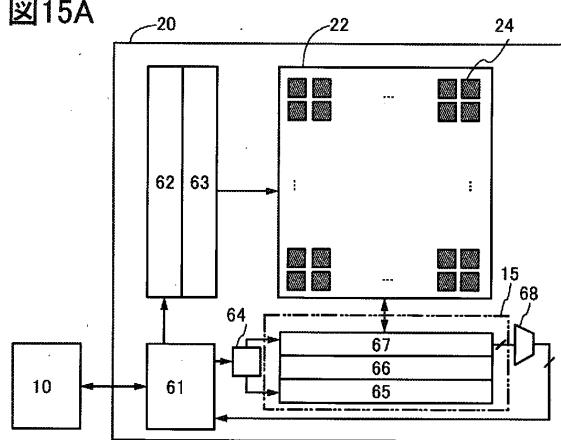

【0108】

図 15A は、図 14B に図示する各構成について、メモリ部 22 を制御するブロックを抜き出した図である。図 15A では、コントローラ 61、ロウデコーダ 62、ワード線ドライバ 63、カラムデコーダ 64、書き込みドライバ 65、プリチャージ回路 66、センスアンプ 67、セレクタ 68 を抜き出して図示している。図 7A および図 7B で図示する駆動回路 15 は、書き込みドライバ 65、プリチャージ回路 66、およびセンスアンプ 67 のブロックに相当する。なお駆動回路 15 には、ワード線ドライバ 63 およびカラムデコーダ 64 を含めてよい。

【0109】

コントローラ 61 は、外部からの入力信号を処理して、ロウデコーダ 62 およびカラムデコーダ 64 の制御信号を生成する。外部からの入力信号は、書き込みイネーブル信号や読み出しイネーブル信号などのメモリ部 22 を制御するための制御信号である。またコントローラ 61 は、CPU 10 との間でバスを介してメモリ部 22 に書き込まれるデータあるいはメモリ部 22 から読み出されるデータの入出力が行われる。

【0110】

ロウデコーダ 62 は、ワード線ドライバ 63 を駆動するための信号を生成する。ワード線ドライバ 63 は、書き込み用ワード線 WWL および読み出し用ワード線 RWL に与える信号を生成する。カラムデコーダ 64 は、センスアンプ 67 および書き込みドライバ 65 を駆動するための信号を生成する。プリチャージ回路 66 は、読み出し用ビット線 RBL などをプリチャージする機能を有する。メモリ部 22 のメモリ回路 24 から読み出される信号は、演算回路 23 に入力される他、セレクタ 68 を介して出力することができる。セレクタ 68 は、バス幅に応じた分のデータを順次読み出しし、コントローラ 61 を介して必要なデータを CPU 10 等に出力することができる。

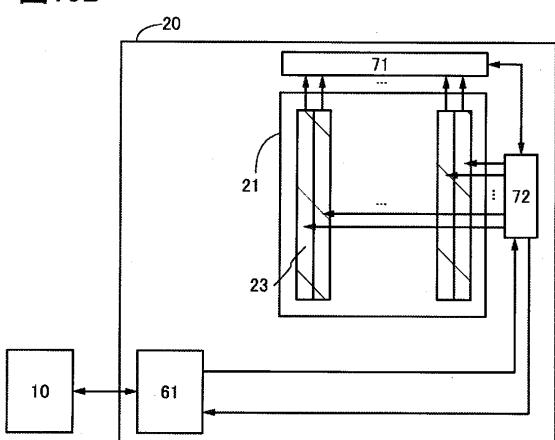

【0111】

図 15B は、図 14B に図示する各構成について、演算処理部 21 を制御するブロック

10

20

30

40

50

を抜き出した図である。

【0112】

コントローラ61は、外部からの入力信号を処理して、演算制御回路72の制御信号を生成する。またコントローラ61は、演算処理部21が有する演算回路23を制御するための各種信号を生成する。またコントローラ61は、入力バッファ71を介して、演算結果に関するデータを入出力する。このバッファメモリを利用してことで、CPUのデータバス幅以上のビット数の並列計算が可能となる。また膨大な数の重みパラメータをCPU10との間で転送する回数を削減できるため、低消費電力化を図ることができる。

【0113】

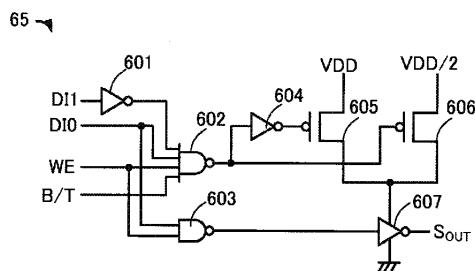

図16では、2値または3値のアナログの電圧値に変換されたデータ信号をメモリ回路に書き込むための、書き込みドライバ65の構成例について説明する。書き込みドライバ65は、インバータ回路601、NAND回路602、NAND回路603、インバータ回路604、トランジスタ605、トランジスタ606、およびインバータ回路607を有する。書き込みドライバ65を構成するトランジスタは、Siトランジスタである。トランジスタ605およびトランジスタ606は、図16に図示するようにpチャネル型トランジスタが好ましい。

10

【0114】

トランジスタ605およびトランジスタ606のソースまたはドレインの一方には、図16に図示するように、電位VDD(>GND)または電位VDD/2(>GND)が与えられる。またインバータ回路601には、入力データであるデータ信号DI1が与えられる。NAND回路602には、インバータ回路601の出力信号の他、データ信号DI0、データの書き込みを制御するための書き込み制御信号WEおよび2値または3値のデータ信号の書き込みを切り替えるための切替信号B/Tが入力される。NAND回路603には、データ信号DI0および書き込み制御信号WEが入力される。インバータ回路607は、2値または3値のデータに応じた電圧値に相当するデータ信号SOUTを出力する。

20

【0115】

図16に図示する各信号の真理値表は、表1のようになる。

【0116】

【表1】

30

| WE | B/T | DI1 | DI0 | SOUT  |

|----|-----|-----|-----|-------|

| 1  | 0   | 1   | 1   | X     |

|    |     | 0   | 1   | VDD   |

|    |     | 0   | 0   | GND   |

|    | 1   | 1   | 1   | VDD   |

|    |     | 0   | 1   | VDD/2 |

|    |     | 0   | 0   | GND   |

40

【0117】

つまり2値のデータをメモリ回路に書き込む場合、データ信号SOUTはデータ信号DI0に応じて、電圧VDDまたは電圧GNDに切り替えられる。3値のデータをメモリ回路に書き込む場合、データ信号SOUTはデータ信号DI0およびDI1に応じて、電圧VDD、電圧VDD/2または電圧GNDの3値に切り替えられる。切り替えられた電圧は、書き込みビット線WBLを介して、メモリ回路に書き込むことができる。

50

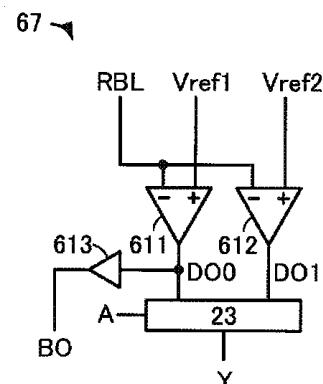

## 【0118】

図17では、2値または3値のアナログの電圧値に応じたデータ信号を演算回路23に出力するセンスアンプ67を含む構成例について説明する。図17では、入力信号に相当する読み出しビット線RBLの電位から出力データであるデータ信号D00、D01を生成する、比較回路611および比較回路612が、センスアンプ67として機能する。比較回路611には、読み出しビット線RBLの電位の電位および参照電圧Vref1が与えられる。比較回路612には、読み出しビット線RBLの電位の電位および参照電圧Vref2が与えられる。参照電圧Vref2は、参照電圧Vref1より大きく、VDDより小さい。参照電圧Vref1は、GNDより大きく、VDD/2より小さい。

## 【0119】

二値のデータの場合、バッファ回路613を介して出力される2値の出力データであるデータ信号D00およびデータ信号BOが得られる。データ信号D00は、データ信号BOと同じ論理値である。データ信号D00と、データ信号BOとの各信号の真理値表は、表2のようになる。

## 【0120】

## 【表2】

| D00 |   | BO |   |

|-----|---|----|---|

| 0   | 0 | 0  | 0 |

| 1   | 1 | 1  | 1 |

10

20

## 【0121】

3値の出力データの場合、演算回路23を介して出力されるデータ信号Yが得られる。データ信号D00、データ信号D01と、データ信号Yとの各信号の真理値表は、表3のようになる。

30

## 【0122】

## 【表3】

| D01 | D00 | W  | A  | Y=A*X |

|-----|-----|----|----|-------|

| 1   | 1   | 0  | -1 | 0     |

| 0   | 1   | +1 | -1 | -1    |

| 0   | 0   | -1 | -1 | +1    |

| 1   | 1   | 0  | +1 | 0     |

| 0   | 1   | +1 | +1 | +1    |

| 0   | 0   | -1 | +1 | -1    |

40

## 【0123】

データ信号Yは、重みデータAとデータ信号D00、D01(X)とが、積和演算され

50

ることで積和信号  $Y$  ( $= A * X$ ) を生成する。

【0124】

以上説明したように、本発明の一態様は、アクセラレータとCPUを備えた半導体装置において、小型化された半導体装置を提供することができる。または、本発明の一態様は、アクセラレータとCPUを備えた半導体装置において、低消費電力化された半導体装置を提供することができる。または、本発明の一態様は、アクセラレータとCPUを備えた半導体装置において、発熱が抑制された半導体装置を提供することができる。または、本発明の一態様は、CPUにおけるデータ転送回数が削減された半導体装置を提供することができる。または、新規な構成の半導体装置を提供することができる。換言すれば、本発明の一態様の半導体装置は、非ノイマン型アーキテクチャを有し、処理速度の増加に伴って消費電力が大きくなるノイマン型アーキテクチャと比較して、極めて少ない消費電力で並列処理を行うことができる。

10

【0125】

(実施の形態3)

本発明の一態様である半導体装置の構成、および動作等について説明する。なお本実施の形態において、上記実施の形態と同じ符号が付される構成についての繰り返しの説明を省略する場合がある。

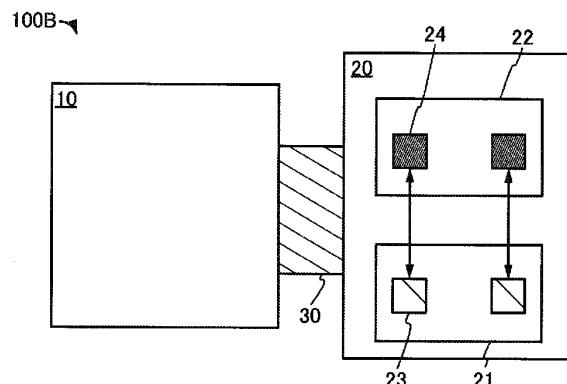

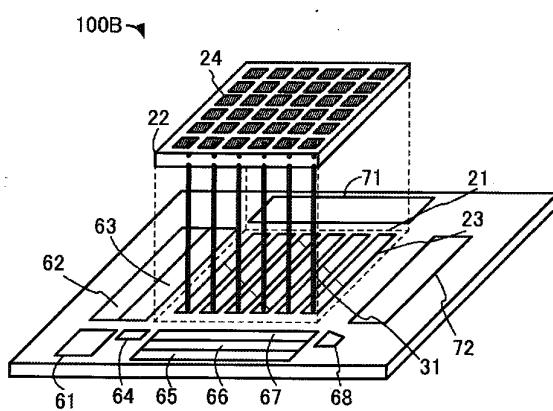

【0126】

図18Aおよび図18Bは、本発明の一態様である半導体装置100Bを説明するための図である。半導体装置100Bは、CPU10、アクセラレータ20およびバス30を有する。アクセラレータ20は、演算処理部21およびメモリ部22を有する。演算処理部21は、演算回路23を有する。メモリ部22は、メモリ回路24を有する。メモリ部22は、デバイスマモリ、共有メモリという場合がある。メモリ回路24は、チャネル形成領域を有する半導体層29を有するトランジスタ25を有する。演算回路23とメモリ回路24とは、配線31を介して電気的に接続される。

20

【0127】

メモリ部22は、アクセラレータ20が処理するデータを記憶および生成する機能を有する。具体的には、ニューラルネットワークの積和演算の並列処理に用いる重みデータ(第1データ信号ともいう)を記憶する機能を有する。またメモリ部22は、入力データ(第2データ信号ともいう)との乗算の結果に応じた出力データ(第3データ信号)を生成する機能を有する。メモリ部は、生成された出力データを演算処理部21に入力する機能を有する。

30

【0128】

メモリ回路24は、演算処理部21が有する演算回路23と配線31を介して電気的に接続され、2値で表される重みデータ、つまり1ビットのデジタル信号を保持する機能を有する。またメモリ回路は、重みデータと、入力データと、の乗算結果に相当する排他的論理和によって得られる信号を生成する機能を有する。なおメモリ回路24において、トランジスタ25が有する半導体層29は、酸化物半導体である。つまり、トランジスタ25は、OSトランジスタである。メモリ回路24は、OSトランジスタを有するメモリ(以下、OSメモリともいう。)が好適である。

40

【0129】

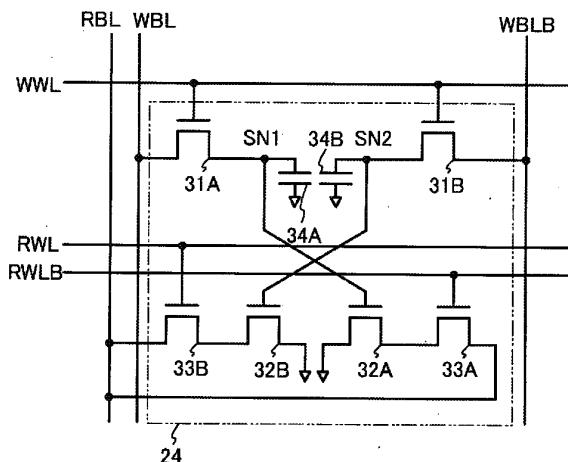

図19Aは、本発明の半導体装置100Bが有するメモリ部22に適用可能な回路構成例について説明する図である。図19Aでは、M行N列(M、Nは2以上の自然数)行列方向に並べて配置された書込用ワード線WWL\_1乃至WWL\_M、読出用ワード線RWL\_1\_1乃至RWL\_MN、読出用反転ワード線RWLB\_1\_1乃至RWLB\_MN、書込用ビット線WBL\_1乃至WBL\_N、書込用反転ビット線WBLB\_1乃至WBLB\_N、および読出用ビット線RBL\_1乃至RBL\_Nを図示している。また各ワード線およびビット線に接続された複数のメモリ回路24を図示している。

【0130】

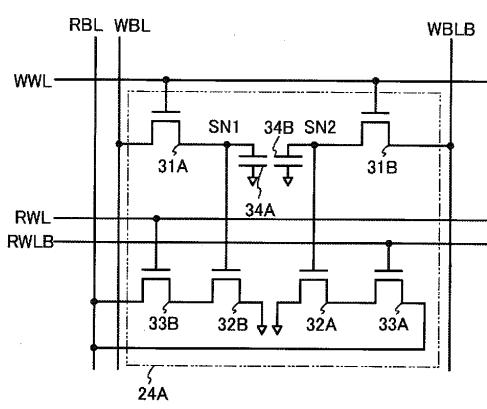

図19Bは、メモリ回路24に適用可能な回路構成例について説明する図である。メモ

50

リ回路24は、トランジスタ31A、31B、トランジスタ32A、32B、トランジスタ33A、33B、容量素子34A、34B（キャパシタともいう）の各素子を有する。各素子は、図19Bに図示するように、書込用ワード線RWL、読出用ワード線RWL、読出用反転ワード線RWLB、書込用ピット線WBL、書込用反転ピット線WBLB、および読出用ピット線RBLの各配線に接続される。

#### 【0131】

容量素子34A、34Bの一方の電極、およびトランジスタ32A、32Bのソースまたはドレインの一方は、固定電位たとえばグラウンド電位を与える配線に接続される。読出用ピット線RBLは、上述したように、演算回路23が設けられる基板表面に対して概略垂直な方向に延在して設けられる配線31等を介して、演算回路23に接続される。

10

#### 【0132】

図19Bに示すメモリ回路24の回路構成は、トランジスタ31A、トランジスタ32A、およびトランジスタ33A並びにトランジスタ31B、トランジスタ32B、およびトランジスタ33Bで、3トランジスタ型（3T）ゲインセルのNOSRAMを構成する。トランジスタ31A、31B、トランジスタ32A、32B、トランジスタ33A、33Bは、OSトランジスタである。OSトランジスタはオフ状態でソースとドレインとの間を流れる電流、つまりリーク電流が極めて小さい。NOSRAMは、リーク電流が極めて小さい特性を用いてデータに応じた電荷をメモリ回路内に保持することで、不揮発性メモリとして用いることができる。図19Bで言えば、トランジスタ31A、31Bをオフにすることで、ノードSN1、SN2に与えられた電荷を保持することができる。なお各トランジスタは、バックゲート電極を有する構成としてもよい。

20

#### 【0133】

図19Bのメモリ回路24の真理値表は、表4のようになる。表3においてHレベルおよびLレベルの電圧は、論理「1」、「0」で表している。「RWL」、「RWLB」は、入力データとして与えられる読出用ワード線RWL、読出用反転ワード線RWLBの電圧に応じた論理に相当する。「SN1」、「SN2」は、重みデータとして書込用ピット線WBL、書込用反転ピット線WBLBからノードSN1、SN2に与えられる電圧に応じた論理に相当する。「RBL」は、出力データとして生成される読出用ピット線RBLの電圧に応じた論理に相当する。

30

#### 【0134】

#### 【表4】

| RWL | RWLB | SN1 | SN2 | RBL |

|-----|------|-----|-----|-----|

| 1   | 0    | 1   | 0   | 1   |

| 1   | 0    | 0   | 1   | 0   |

| 0   | 1    | 1   | 0   | 0   |

| 0   | 1    | 0   | 1   | 1   |

40

#### 【0135】

図19Bの回路構成において、表4で示す真理値表のデータを得ることができる。そのため、例えば、表5に示す読出用ワード線RWL（入力データA）と、ノードSN2（重みデータW）と、の排他的論理和に基づく出力信号（出力データY = W × A）を得ることができる。なお表5に図示するように、論理「1」、「0」は、Binary Neural Network (BNN)に用いる「+1」または「-1」の2値で表されるデータである。

#### 【0136】

50

【表 5】

| RWL (A) | SN1 (W) | RBL (Y=W × A) |

|---------|---------|---------------|

| -1 (0)  | -1 (0)  | +1 (1)        |

| -1 (0)  | +1 (1)  | -1 (0)        |

| +1 (1)  | -1 (0)  | -1 (0)        |

| +1 (1)  | +1 (1)  | +1 (1)        |

10

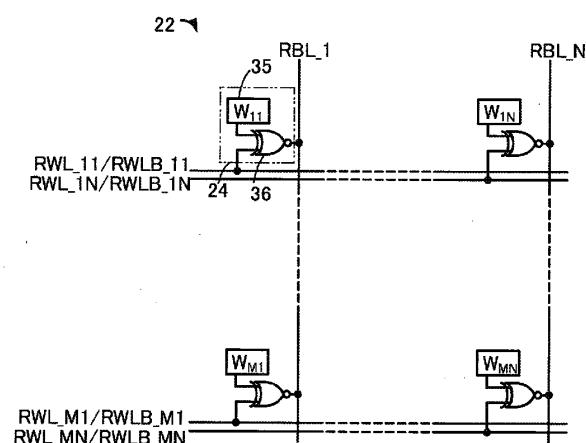

【0137】

読出用ビット線 RBL にデータを読み出す場合の動作について、図 20A を用いて説明する。まずスタンバイ期間 T01 で読出用ワード線 RWL、読出用反転ワード線 RWLB を H レベル、読出用ビット線 RBL を中間電位とする。次いで、プリチャージ期間 T02 で読出用ワード線 RWL、読出用反転ワード線 RWLB を H レベルとし、読出用ビット線 RBL を H レベルとして電気的に浮遊状態（フローティング）とする。次いで、読み出し期間 T03 で読出用ワード線 RWL、読出用反転ワード線 RWLB を入力データに応じた論理「1」、「0」とすることで、読出用ビット線 RBL の論理が「1」または「0」に変化することで出力データを生成することができる。

20

【0138】

重みデータの保持、および入力データとの排他的論理和に基づく信号を生成可能なメモリ部 22 は、図 20B に図示するような構成とすることができます。つまり複数のメモリ回路 24 において、重みデータである  $W_{11}$  乃至  $W_{MN}$  を記憶部 35 に保持させ、読出用ワード線  $RWL_{11}$  乃至  $RWL_{MN}$ 、読出用反転ワード線  $RWLB_{11}$  乃至  $RWLB_{MN}$  を介して入力データを排他的論理和部 36 (EXOR) に与えることで、重みデータと入力データとの排他的論理和に基づく出力データを読出用ビット線  $RBL_{11}$  乃至  $RBL_{MN}$  に入力することができます。

30

【0139】

なお図 19B のメモリ回路 24 は、図 21 の回路構成に変形することができる。図 21 のメモリ回路 24A は、ノード SN1、SN2 の接続先であるトランジスタ 32A、32B のゲートの接続を変更した構成に相当する。図 21 の回路構成において、表 6 で示す真理値表のデータを得ることができる。

【0140】

【表 6】

| RWL | RWLB | SN1 | SN2 | RBL |

|-----|------|-----|-----|-----|

| 1   | 0    | 1   | 0   | 0   |

| 1   | 0    | 0   | 1   | 1   |

| 0   | 1    | 1   | 0   | 1   |

| 0   | 1    | 0   | 1   | 0   |

40

【0141】

同様に図 22A のメモリ回路 24B は、ノード SN1 の接続先であるトランジスタを同

50

じ極性のトランジスタから、pチャネル型とnチャネル型を組み合わせたトランジスタ32\_P、32\_Nに変更した構成に相当する。トランジスタ32\_P、32\_Nは、Siトランジスタ等を用いることができる。当該構成とすることで、図19BにおけるノードSN2に接続されるトランジスタおよび配線を省略することができる。図22Aの回路構成において、表7で示す真理値表のデータを得ることができる。

【0142】

【表7】

| RWL | RWLB | SN1 | RBL |

|-----|------|-----|-----|

| 1   | 0    | 1   | 0   |

| 1   | 0    | 0   | 1   |

| 0   | 1    | 1   | 1   |

| 0   | 1    | 0   | 0   |

10

【0143】

同様に図22Bのメモリ回路24Cは、図19BのノードSN1、SN2の接続先である同じ極性のトランジスタから、異なる極性のトランジスタ32\_P、32\_Nに変更し、さらにトランジスタ37、38、および容量素子39を追加した構成に相当する。当該構成とすることで、ノードSN2に接続されるトランジスタおよび配線を省略することができる。図22Bの回路構成の真理値表は、表7と同様である。

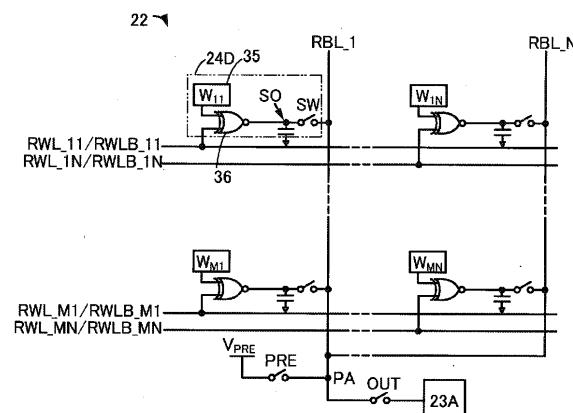

【0144】

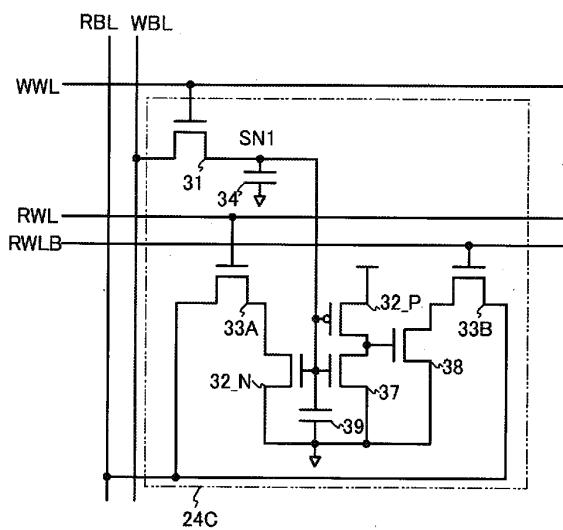

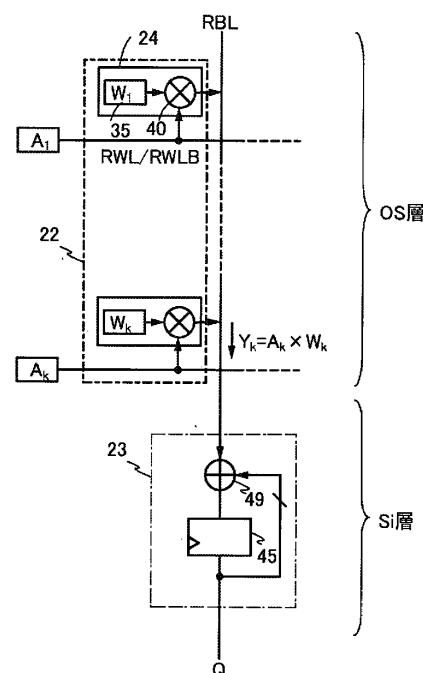

図23は、本発明の半導体装置100Bにおける、複数のメモリ回路24を有するメモリ部22と、演算回路23と、を説明する模式図である。上述したようにメモリ部22におけるメモリ回路24はそれぞれ、記憶部35と乗算部40とを備える。重みデータW<sub>1</sub>乃至W<sub>k</sub>（kは2以上の自然数）は記憶部35に保持され、読出用ワード線RWL、読出用反転ワード線RWLBを介して入力される入力データA<sub>1</sub>乃至A<sub>k</sub>と乗算に応じた1ビットのデジタル信号である出力信号（Y<sub>k</sub> = A<sub>k</sub> × W<sub>k</sub>）が演算回路23に与えられる。メモリ部22の各トランジスタは、OSトランジスタとすることで、演算回路23と積層して設けることができるため好ましい。

30

【0145】

また図23に示す演算回路23は、アキュムレータ49と符号化回路45を備える。演算回路23は、乗算された出力信号を足し合わせることで、積和演算された信号Qを生成することができる。

【0146】

図23で図示した演算回路23の構成について、より詳細を示す構成例を図24に図示する。図24では、8ビットの信号（WA[0]乃至WA[7]）の加算を行い、1ビットの出力信号Q、11ビットの出力信号（account[10:0]）を出力する構成を一例として図示している。図24の構成例では、積和演算と、バッチノーマライゼーションのための和の演算と、を切り替えて行う構成を図示している。図24では、メモリアクセスは1クロックで1行を選択するため、M個（=1ビット×M行）の積とその和をMクロックで実行する。図24の演算回路では、同じM個の積とその和を8並列×1ビット×M/8行で実行できるため、M/8クロックを要する。したがって、図24の構成は並列に積和演算を実行することで演算時間を短縮できるため、演算効率を向上できる。

40

【0147】

50

図24において、ビット加算器42Aは、8ビットの信号(WA[0]乃至WA[7])が入力される加算器を有する。図24に示すように、1ビットの信号の和をWA10、WA32、WA54、WA76、さらにその和をWA3210、WA7654として図示している。

#### 【0148】

図24において、加算器として機能するアキュムレータ49は、ビット加算器42Aの信号とラッチ回路44の出力信号との和をラッチ回路44に出力する。なお図24において、アキュムレータ49に入力される信号は、制御信号TxD\_ENに応じて切り替えられるセレクタ48を備える。制御信号TxD\_ENが0(TxD\_EN=0)でビット加算器42Aの信号とラッチ回路44の出力信号との和をラッチ回路44に出力する。制御信号TxD\_ENが1(TxD\_EN=1)でロジック回路47の信号(11bit selector)とラッチ回路44の出力信号との和をラッチ回路44に出力する。セレクタ48によって、積和演算と、バッチノーマライゼーションのための和の演算と、を切り替えて行うことができる。

10

#### 【0149】

図24において、AND回路で構成されるロジック回路47は、信号WA0乃至WA7の積和演算が完了した後、バッチノーマライゼーションのためのデータ、具体的には切替信号(th\_select[10:0])で切り替えながら信号RBL\_th[10:0]を足し合わせる。なお、信号RBL\_th[10:0]は、メモリ回路24に保持される重みデータに相当する。バッチノーマライゼーションは、ニューラルネットワークにおける各層の出力データの分布が一定に収まるように調整するための動作である。例えば、ニューラルネットワークにおける演算によく利用される画像データは、学習に用いるデータの分布がばらつきやすいため、予測データ(入力データ)の分布と異なることがある。バッチノーマライゼーションは、ニューラルネットワークの中間層への入力データの分布を平均0、分散1のガウス分布に正規化することで、ニューラルネットワークにおける学習の精度を高めることができる。Binary Neural Network(BNN)では活性化によって各層の出力結果が2値化されるため、しきい値に対してデータ分布の偏りを抑制することで、適切に活性化、つまり情報を分別できるようになる。

20

#### 【0150】

ラッチ回路44は、アキュムレータ49の出力信号(account[10:0])を保持する。ラッチ回路44は、信号CLRnでリセットされる。バッチノーマライゼーションによって次のニューラルネットワークにおける層(NN層)に渡す2値データはラッチ回路44が保持する積和演算結果の最上位ビットとなる。出力信号(account[10:0])において、最上位のビットの信号(account10)は、2の補数で演算されたラッチデータの符号を表し、そのプラスデータを1、マイナスデータを0として次のNN層に渡すため、符号化回路として機能するインバータ回路46で反転され、出力信号Qとして出力される。Qは中間層の出力であるため、アクセラレータ20内のバッファメモリ(入力バッファとも言う)に一時的に保持された後、次層の演算に使用される。

30

#### 【0151】

図25Aには、Binary Neural Network(BNN)のアーキテクチャに基づく、階層型のニューラルネットワークを図示する。図25Aでは、ニューロン50、入力層1層(I1)、中間層3層(M1乃至M3)、出力層1層(O1)の全結合型のニューラルネットワークを図示している。入力層I1におけるニューロン数を786、中間層M1乃至M3におけるニューロン数を256、出力層O1におけるニューロン数を10とすると、各層(層51、層52、層53および層54)の結合数は( $784 \times 256$ ) + ( $256 \times 256$ ) + ( $256 \times 256$ ) + ( $256 \times 10$ )で計334336個となる。つまり、ニューラルネットワーク計算に必要な重みパラメータが合計330Kビット程度であるため、小規模システムでも十分実装可能なメモリ容量とすることができます。

40

#### 【0152】

次に、図25Aに図示するニューラルネットワークの演算ができる、半導体装置100

50

Bの詳細なブロック図について図25Bに示す。

【0153】

図25Bでは、図18Aおよび図18Bで説明した、演算処理部21、演算回路23、メモリ部22、メモリ回路24、および配線31の他、図18Aおよび図18Bで図示する各構成を駆動するための周辺回路の構成例について図示している。

【0154】

図25Bでは、コントローラ61、ロウデコーダ62、ワード線ドライバ63、カラムデコーダ64、書き込みドライバ65、プリチャージ回路66、センスアンプ67、セレクタ68、入力バッファ71および演算制御回路72を図示している。

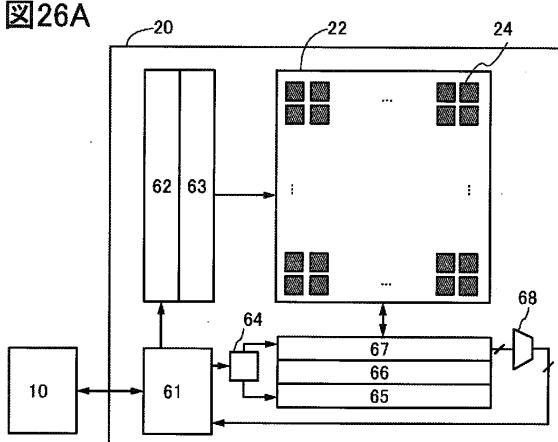

【0155】

図26Aは、図25Bに図示する各構成について、メモリ部22を制御するブロックを抜き出した図である。図26Aでは、コントローラ61、ロウデコーダ62、ワード線ドライバ63、カラムデコーダ64、書き込みドライバ65、プリチャージ回路66、センスアンプ67、セレクタ68を抜き出して図示している。

【0156】

コントローラ61は、外部からの入力信号を処理して、ロウデコーダ62およびカラムデコーダ64の制御信号を生成する。外部からの入力信号は、書き込みイネーブル信号や読み出しイネーブル信号などのメモリ部22を制御するための制御信号である。またコントローラ61は、CPU10との間でバスを介してメモリ部22に書き込まれるデータあるいはメモリ部22から読み出されるデータの入出力が行われる。

【0157】

ロウデコーダ62は、ワード線ドライバ63を駆動するための信号を生成する。ワード線ドライバ63は、書き用ワード線WWLおよび読み用ワード線RWLに与える信号を生成する。カラムデコーダ64は、センスアンプ67および書き込みドライバ65を駆動するための信号を生成する。センスアンプ67は、読み用ビット線RBLの電位を増幅する。書き込みドライバは、読み用ビット線RBLおよび書き用ビット線WBLを制御するための信号を生成する。プリチャージ回路66は、読み用ビット線RBLなどをプリチャージする機能を有する。メモリ部22のメモリ回路24から読み出される信号は、演算回路23に入力される他、セレクタ68を介して出力することができる。セレクタ68は、バス幅に応じた分のデータを順次読み出し、コントローラ61を介して必要なデータをCPU10等に出力することができる。

【0158】

図26Bは、図25Bに図示する各構成について、演算処理部21を制御するブロックを抜き出した図である。

【0159】

コントローラ61は、外部からの入力信号を処理して、演算制御回路72の制御信号を生成する。またコントローラ61は、演算処理部21が有する演算回路23を制御するための各種信号を生成する。またコントローラ61は、入力バッファ71を介して、演算結果に関するデータを入出力する。このバッファメモリを利用してすることで、CPUのデータバス幅以上のビット数の並列計算が可能となる。また膨大な数の重みパラメータをCPU10との間で転送する回数を削減できるため、低消費電力化を図ることができる。

【0160】

また上述したメモリ回路24は、トランジスタ等の構成を追加した回路構成に変形することができる。例えばメモリ回路24に適用可能な図27Aのメモリ回路24Dは、図19Bで図示した構成に加えて、トランジスタ81および容量素子82を追加した構成に相当する。また図27Aでは、ノードS0を図示している。なお図27Aに図示する回路構成は、図21に対応する変形例として、図27Bのメモリ回路24Eの構成とすることもできる。

【0161】

トランジスタ81は、OSトランジスタであることが好ましい。トランジスタ81をO

10

20

30

40

50

Sトランジスタとすることで、リーク電流が極めて小さい特性を用いて容量素子82、すなわちノードSOに出力データに応じた電荷を保持させることができる。ノードSOに保持された出力データは、トランジスタ81のゲートに接続された制御信号SWに応じて、読み出しひット線RBLに出力させることができる。

#### 【0162】

図28Aは、図27Aの構成のメモリ回路24Dをメモリ部22に適用した際の動作を説明するための模式図である。図28Aに示すメモリ回路24Dでは、図20Bで説明した記憶部35および排他的論理部36に加えて、図27Aで示したノードSO、およびスイッチとして機能するトランジスタを制御する制御信号SWを図示している。1行目のメモリ回路24Dには、読み出用ワード線RWL\_11乃至RWL\_1Nのいずれか一、読み出用反転ワード線RWL\_B\_11乃至RWL\_B\_1Nのいずれか一が接続されている。M行目のメモリ回路24Dには、読み出用ワード線RWL\_M1乃至RWL\_MNのいずれか一、読み出用反転ワード線RWL\_B\_M1乃至RWL\_B\_MNのいずれか一が接続されている。また図28Aでは、読み出しひット線RBL\_1乃至RBL\_Nをプリチャージするためのプリチャージ電圧が与えられる配線に接続されたスイッチを制御する制御信号PRE、読み出しひット線RBL\_1乃至RBL\_NのノードPA、読み出しひット線RBL\_1乃至RBL\_Nと演算回路23Aとの間のスイッチを制御する制御信号OUTを図示している。

#### 【0163】

各行のノードSOに保持される電荷を制御信号SWで一斉に読み出しひット線RBL\_1乃至RBL\_Nにチャージシェアリングさせることで、読み出しひット線RBL\_1乃至RBL\_Nは各行のメモリ回路24Dの出力データの和に応じた電位とすることができます。つまり読み出しひット線RBL\_1乃至RBL\_Nは、メモリ回路24Dにおける乗算に応じた電荷の加算に応じたアナログ電圧とすることができます。そのため演算回路23Aでは、図23で説明した加算器の代わりにアナログデジタル変換回路を用いることができる。

#### 【0164】

読み出用ヒット線RBLにデータを読み出す場合の動作について、図28Bを用いて説明する。なお各スイッチは、Hレベルでオン、Lレベルでオフであるとして説明する。

#### 【0165】

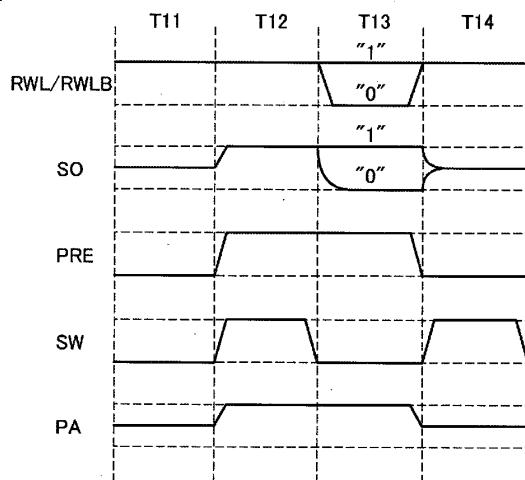

まずスタンバイ期間T11で読み出用ワード線RWL、読み出用反転ワード線RWLBをHレベル、制御信号SWおよび制御信号PREをLレベル、ノードSOおよびノードPAを中間電位とする。次いで、プリチャージ期間T12で読み出用ワード線RWL、読み出用反転ワード線RWLBをHレベルとし、制御信号SWおよび制御信号PREをHレベル、ノードSOおよびノードPAをHレベルとして電気的に浮遊状態(フローティング)とする。次いで、乗算を行う期間T13で読み出用ワード線RWL、読み出用反転ワード線RWLBを入力データに応じた論理「1」、「0」とすることで、ノードSOの論理が「1」または「0」に変化する。期間T13では、制御信号SWをLレベル、制御信号PREおよびノードPAをHレベルとする。次いで、加算を行う期間T14で読み出用ワード線RWL、読み出用反転ワード線RWLBをHレベル、制御信号PREをLレベルとして、制御信号SWをHレベルとする。ノードSOとノードPAがチャージシェアリングされ、ノードPAの電位は、乗算して得られた複数のメモリ回路におけるノードSOの電荷が加算されていられるアナログ電位とすることができます。当該アナログ電位は、制御信号OUTによって、演算回路23Aに読み出すことができる。

#### 【0166】

本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置を小型化することができる。または、本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置を低消費電力化することができる。または、本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置において、発熱を抑制することができる。または、本発明の一態様は、計算量とパラメータ数が膨大なAI技術などのアクセラレータとして機能する半導体装置において、消費電力を削減することができる。

10

20

30

40

50

セラレータとして機能する半導体装置において、C P Uとメモリとして機能する半導体装置との間のデータ転送回数を削減することができる。換言すれば計算量とパラメータ数が膨大なA I技術などのアクセラレータとして機能する半導体装置は非ノイマン型アーキテクチャを有し、処理速度の増加に伴って消費電力が大きくなるノイマン型アーキテクチャと比較して、極めて少ない消費電力で並列処理を行うことができる。

【0167】

(実施の形態4)

本実施の形態では、上記実施の形態で説明したC P U10で実行するプログラムの演算の一部をアクセラレータ20で実行する場合の、動作の一例を説明する。

【0168】

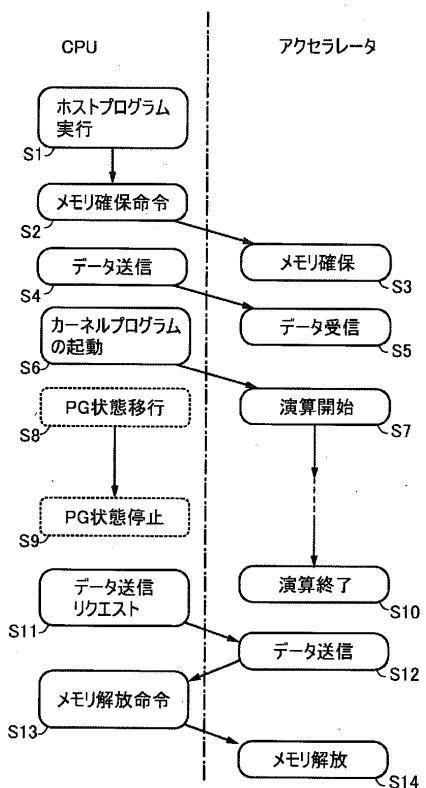

図29は、C P Uで実行するプログラムの演算の一部をアクセラレータで実行する場合の、動作の一例を説明する図である。

【0169】

C P Uにて、ホストプログラムが実行される(ステップS1)。

【0170】

C P Uは、アクセラレータを用いて演算を行う際に必要とされるデータ用領域を、メモリ部に確保するとの命令を確認した場合(ステップS2)、該データ用領域を、メモリ部に確保する(ステップS3)。

【0171】

次に、C P Uは、メインメモリから上記メモリ部へ入力データを送信する(ステップS4)。上記メモリ部は該入力データを受信し、該入力データを、ステップS2で確保された領域に格納する(ステップS5)。

【0172】

C P Uは、カーネルプログラムを起動するとの命令を確認した場合(ステップS6)、アクセラレータは、カーネルプログラムの実行を開始する(ステップS7)。

【0173】

アクセラレータがカーネルプログラムの実行を開始した直後、C P Uを、演算を行う状態からP G状態へと切り替えてよい(ステップS8)。その場合、アクセラレータがカーネルプログラムの実行を終了する直前に、C P Uは、P G状態から演算を行う状態へ切り替えられる(ステップS9)。ステップS8からステップS9までの期間、C P UをP G状態にすることで、半導体装置全体として消費電力および発熱を抑制することができる。

【0174】

アクセラレータがカーネルプログラムの実行を終了すると、出力データが上記メモリ部に格納される(ステップS10)。

【0175】

カーネルプログラムの実行が終了した後、C P Uは、メモリ部に格納された出力データをメインメモリへ送信するとの命令を確認した場合(ステップS11)、上記の出力データが上記メインメモリへ送信され、上記メインメモリに格納される(ステップS12)。

【0176】

C P Uは、メモリ部上に確保されたデータ用領域を解放するとの指示を確認した場合(ステップS13)、上記メモリ部上に確保された領域が解放される(ステップS14)。

【0177】

以上のステップS1からステップS14までの動作を繰り返すことにより、C P Uおよびアクセラレータの消費電力および発熱を抑制しつつ、C P Uで実行するプログラムの演算の一部をアクセラレータで実行することができる。

【0178】

本実施の形態は、他の実施の形態の記載と適宜組み合わせることができる。

【0179】

(実施の形態5)

本実施の形態では、パワーゲーティングが可能なC P Uコアを有するC P Uの一例につ

10

20

30

40

50

いて説明する。

【0180】

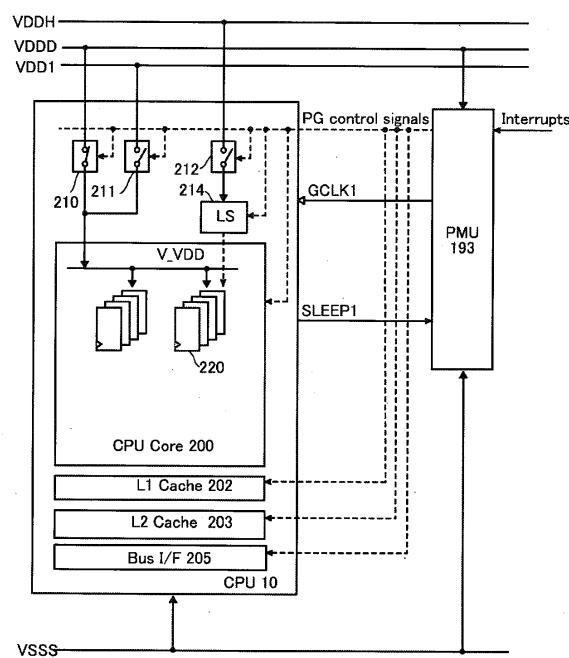

図30に、CPU10の構成例を示す。CPU10は、CPUコア(CPU Core)200、L1(レベル1)キャッシュメモリ装置(L1 Cache)202、L2キャッシュメモリ装置(L2 Cache)203、バスインターフェース部(Bus I/F)205、パワースイッチ210～212、レベルシフタ(LS)214を有する。CPUコア200はフリップフロップ220を有する。

【0181】

バスインターフェース部205によって、CPUコア200、L1キャッシュメモリ装置202、L2キャッシュメモリ装置203が相互に接続される。

10

【0182】

外部から入力される割り込み信号(Interrupts)、CPU10が発行する信号SLEEP1等の信号に応じて、PMU193はクロック信号GCLK1、各種のPG(パワーゲーティング)制御信号(PG control signals)の生成を行う。クロック信号GCLK1、PG制御信号はCPU10に入力される。PG制御信号は、パワースイッチ210～212、フリップフロップ220を制御する。

【0183】

パワースイッチ210、211は、仮想電源線V\_VDD(以下、V\_VDD線と呼ぶ)への電圧VDDD、VDD1の供給をそれぞれ制御する。パワースイッチ212は、レベルシフタ(LS)214への電圧VDDHの供給を制御する。CPU10およびPMU193には、パワースイッチを介さずに電圧VSSSが入力される。PMU193には、パワースイッチを介さずに電圧VDDDが入力される。

20

【0184】

電圧VDDD、VDD1はCMOS回路用の駆動電圧である。電圧VDD1は電圧VDよりも低く、スリープ状態での駆動電圧である。電圧VDDHはOSトランジスタ用の駆動電圧であり、電圧VDDDよりも高い。

【0185】

L1キャッシュメモリ装置202、L2キャッシュメモリ装置203、バスインターフェース部205それぞれは、少なくとも1つパワーゲーティング可能なパワードメインを有する。パワーゲーティング可能なパワードメインには、1または複数のパワースイッチが設けられている。これらのパワースイッチは、PG制御信号によって制御される。

30

【0186】

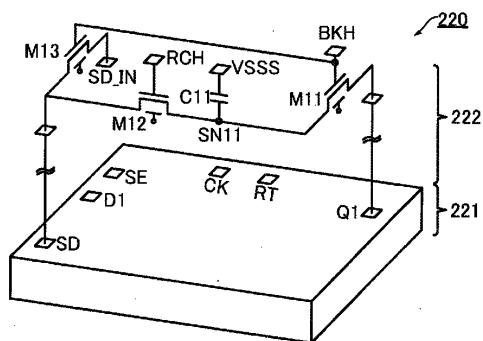

フリップフロップ220は、レジスタに用いられる。フリップフロップ220には、バックアップ回路が設けられている。以下、フリップフロップ220について説明する。

【0187】

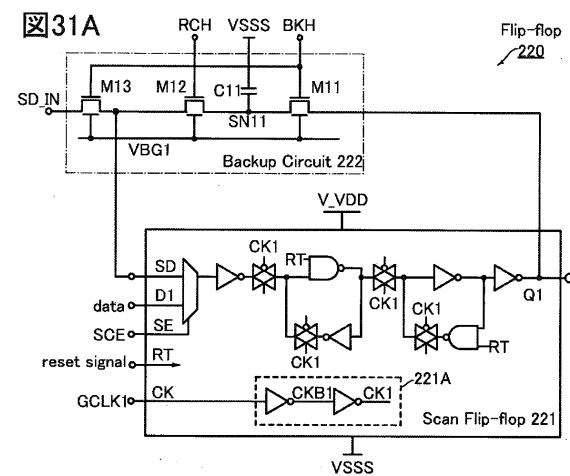

図31にフリップフロップ220(Flip-flop)の回路構成例を示す。フリップフロップ220はスキャンフリップフロップ(Scan Flip-flop)221、バックアップ回路(Backup Circuit)222を有する。

【0188】

スキャンフリップフロップ221は、ノードD1、Q1、SD、SE、RT、CK、クロックバッファ回路221Aを有する。

40

【0189】

ノードD1はデータ(data)入力ノードであり、ノードQ1はデータ出力ノードであり、ノードSDはスキャンテスト用データの入力ノードである。ノードSEは信号SC-Eの入力ノードである。ノードCKはクロック信号GCLK1の入力ノードである。クロック信号GCLK1はクロックバッファ回路221Aに入力される。スキャンフリップフロップ221のアナログスイッチは、クロックバッファ回路221AのノードCK1、CKB1に接続される。ノードRTはリセット信号(reset signal)の入力ノードである。

【0190】

50

信号 S C E は、スキャンイネーブル信号であり、PMU193 で生成される。PMU193 は信号 BK、RC (図示せず) を生成する。レベルシフタ214 は信号 BK、RC をレベルシフトし、信号 BKH、RCH を生成する。信号 BK、RC はバックアップ信号、リカバリ信号である。

#### 【0191】

スキャンフリップフロップ221 の回路構成は、図31 に限定されない。標準的な回路ライブラリに用意されているフリップフロップを適用することができる。

#### 【0192】

バックアップ回路222 は、ノード SD\_IN、SN11、トランジスタM11～M13、容量素子C11 を有する。

10

#### 【0193】

ノード SD\_IN は、スキャンテストデータの入力ノードであり、スキャンフリップフロップ221 のノード Q1 に接続される。ノード SN11 は、バックアップ回路222 の保持ノードである。容量素子C11 はノード SN11 の電圧を保持するための保持容量である。

#### 【0194】

トランジスタM11 はノード Q1 とノード SN11 間の導通状態を制御する。トランジスタM12 はノード SN11 とノード SD 間の導通状態を制御する。トランジスタM13 はノード SD\_IN とノード SD 間の導通状態を制御する。トランジスタM11、M13 のオンオフは信号 BKH で制御され、トランジスタM12 のオンオフは信号 RCH で制御される。

20

#### 【0195】

トランジスタM11～M13 は、上述したメモリ回路24 が有するトランジスタ25 乃至27 と同様に、OSトランジスタである。トランジスタM11～M13 はバックゲートを有する構成を図示している。トランジスタM11～M13 のバックゲートは、電圧VBG1 を供給する電源線に接続されている。

#### 【0196】

少なくともトランジスタM11、M12 がOSトランジスタであることが好ましい。オフ電流が極めて小さいというOSトランジスタの特長によって、ノード SN11 の電圧の低下を抑えることができること、データの保持に電力を殆んど消費しないことから、バックアップ回路222 は不揮発性の特性をもつ。容量素子C11 の充放電によってデータを書き換えるため、バックアップ回路222 は原理的には書き換え回数に制約はなく、低エネルギーで、データの書き込みおよび読み出しが可能である。

30

#### 【0197】

バックアップ回路222 の全てのトランジスタはOSトランジスタであることが非常に好ましい。図31B に示すように、シリコンCMOS回路で構成されるスキャンフリップフロップ221 上にバックアップ回路222 を積層することができる。

#### 【0198】

バックアップ回路222 は、スキャンフリップフロップ221 と比較して素子数が非常に少ないので、バックアップ回路222 を積層するためにスキャンフリップフロップ221 の回路構成およびレイアウトの変更が必要ない。つまり、バックアップ回路222 は、汎用性が非常に高いバックアップ回路である。また、スキャンフリップフロップ221 が形成されている領域内にバックアップ回路222 を設けることができるので、バックアップ回路222 を組み込んでも、フリップフロップ220 の面積オーバーヘッドはゼロにすることが可能である。よって、バックアップ回路222 をフリップフロップ220 に設けることで、CPUコア200 のパワーゲーティングが可能となる。パワーゲーティングに必要なエネルギーが少ないため、CPUコア200 を高効率にパワーゲーティングすることが可能である。

40

#### 【0199】

バックアップ回路222 を設けることによって、トランジスタM11 による寄生容量が

50

ノードQ1に付加されることになるが、ノードQ1に接続される論理回路による寄生容量と比較して小さいので、スキャンフリップフロップ221の動作に影響はない。つまり、バックアップ回路222を設けても、フリップフロップ220の性能は実質的に低下しない。

#### 【0200】

CPUコア200の低消費電力状態として、例えば、クロックゲーティング状態、パワーゲーティング状態、休止状態を設定することができる。PMU193は、割り込み信号、信号SLEEP1等に基づき、CPUコア200の低消費電力モードを選択する。例えば、通常動作状態からクロックゲーティング状態に移行する場合、PMU193はクロック信号GCLK1の生成を停止する。

10

#### 【0201】

例えば、通常動作状態から休止状態に移行する場合は、PMU193は、電圧および/または周波数スケーリングを行う。例えば、電圧スケーリングを行う場合、PMU193は、電圧VDD1をCPUコア200に入力するため、パワースイッチ210をオフにし、パワースイッチ211をオンにする。電圧VDD1は、スキャンフリップフロップ221のデータを消失させない電圧である。周波数スケーリングを行う場合、PMU193はクロック信号GCLK1の周波数を低下させる。

#### 【0202】

CPUコア200を通常動作状態からパワーゲーティング状態に移行する場合には、スキャンフリップフロップ221のデータをバックアップ回路222にバックアップする動作が行われる。CPUコア200をパワーゲーティング状態から通常動作状態に復帰する際には、バックアップ回路222のデータをスキャンフリップフロップ221に書き戻すリカバリ動作が行われる。

20

#### 【0203】

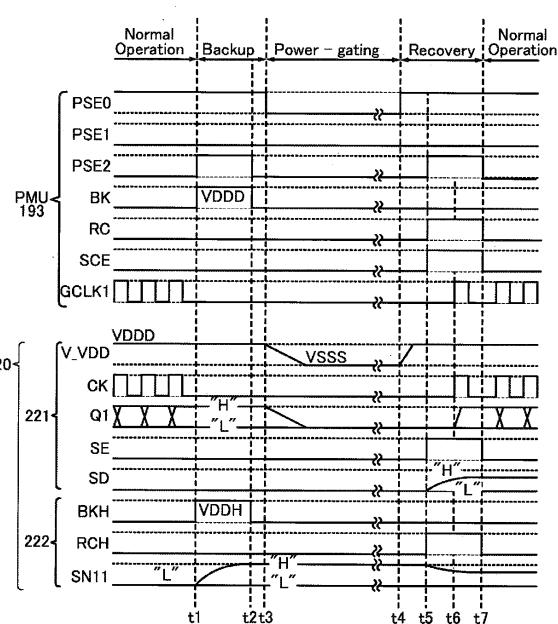

図32に、CPUコア200のパワーゲーティングシーケンスの一例を示す。なお、図32において、t1~t7は時刻を表している。信号PSE0~PSE2は、パワースイッチ210~212の制御信号であり、PMU193で生成される。信号PSE0が“H”/“L”的とき、パワースイッチ210はオン/オフである。信号PSE1、PSE2についても同様である。

#### 【0204】

30

時刻t1以前は、通常動作状態(Normal Operation)である。パワースイッチ210はオンであり、CPUコア200には電圧VDDDが入力される。スキャンフリップフロップ221は通常動作を行う。このとき、レベルシフタ214は動作させる必要がないため、パワースイッチ212はオフであり、信号SCE、BK、RCは“L”である。ノードSEが“L”であるため、スキャンフリップフロップ221はノードD1のデータを記憶する。なお、図32の例では、時刻t1において、バックアップ回路222のノードSN11は“L”である。

#### 【0205】

バックアップ(Backup)時の動作を説明する。時刻t1で、PMU193はクロック信号GCLK1を停止し、信号PSE2、BKを“H”にする。レベルシフタ214はアクティブになり、“H”的信号BKHをバックアップ回路222に出力する。

40

#### 【0206】

バックアップ回路222のトランジスタM11がオンになり、スキャンフリップフロップ221のノードQ1のデータがバックアップ回路222のノードSN11に書き込まれる。スキャンフリップフロップ221のノードQ1が“L”であれば、ノードSN11は“L”的ままであり、ノードQ1が“H”であれば、ノードSN11は“H”になる。

#### 【0207】

PMU193は、時刻t2で信号PSE2、BKを“L”にし、時刻t3で信号PSE0を“L”にする。時刻t3で、CPUコア200の状態はパワーゲーティング状態に移行する。なお、信号BKを立ち下げるタイミングで信号PSE0を立ち下げてもよい。

50

## 【0208】

パワーゲーティング (Power-gating) 時の動作を説明する。信号 PSE0 が “L” になることで、V\_VDD 線の電圧が低下するため、ノード Q1 のデータは失われる。ノード SN11 は、時刻 t3 でのノード Q1 のデータを保持し続ける。

## 【0209】

リカバリ (Recovery) 時の動作を説明する。時刻 t4 で、PMU193 が信号 PSE0 を “H” にすることで、パワーゲーティング状態からリカバリ状態に移行する。V\_VDD 線の充電が開始され、V\_VDD 線の電圧が VDDD になった状態 (時刻 t5) で、PMU193 は信号 PSE2、RC、SCE を “H” にする。

## 【0210】

トランジスタ M12 はオンになり、容量素子 C11 の電荷がノード SN11 とノード SD とに分配される。ノード SN11 が “H” であれば、ノード SD の電圧は上昇する。ノード SE は “H” であるので、スキャンフリップフロップ 221 の入力側ラッチ回路にノード SD のデータが書き込まれる。時刻 t6 でノード CK にクロック信号 GCLK1 が入力されると、入力側ラッチ回路のデータがノード Q1 に書き込まれる。つまり、ノード SN11 のデータがノード Q1 に書き込まれたことになる。

## 【0211】

時刻 t7 で、PMU193 は信号 PSE2、SCE、RC を “L” にし、リカバリ動作が終了する。

## 【0212】

OS トランジスタを用いたバックアップ回路 222 は、動的および静的低消費電力双方が小さいため、ノーマリオフ・コンピューティングに非常に好適である。フリップフロップ 220 を搭載しても、CPUコア 200 の性能低下、動的電力の増加をほとんど発生させないようにできる。

## 【0213】

なお、CPUコア 200 は複数のパワーゲーティング可能なパワードメインを有してもよい。複数のパワードメインには、電圧の入力を制御するための 1 または複数のパワースイッチが設けられる。また、CPUコア 200 は、1 または複数のパワーゲーティングが行われないパワードメインを有していてもよい。例えば、パワーゲーティングが行われないパワードメインに、フリップフロップ 220、パワースイッチ 210 ~ 212 の制御を行うためのパワーゲーティング制御回路を設けてもよい。

## 【0214】

なお、フリップフロップ 220 の適用は CPU10 に限定されない。演算装置において、パワーゲーティング可能なパワードメインに設けられるレジスタに、フリップフロップ 220 を適用できる。

## 【0215】

本実施の形態は、他の実施の形態の記載と適宜組み合わせることができる。

## 【0216】

## (実施の形態 6)

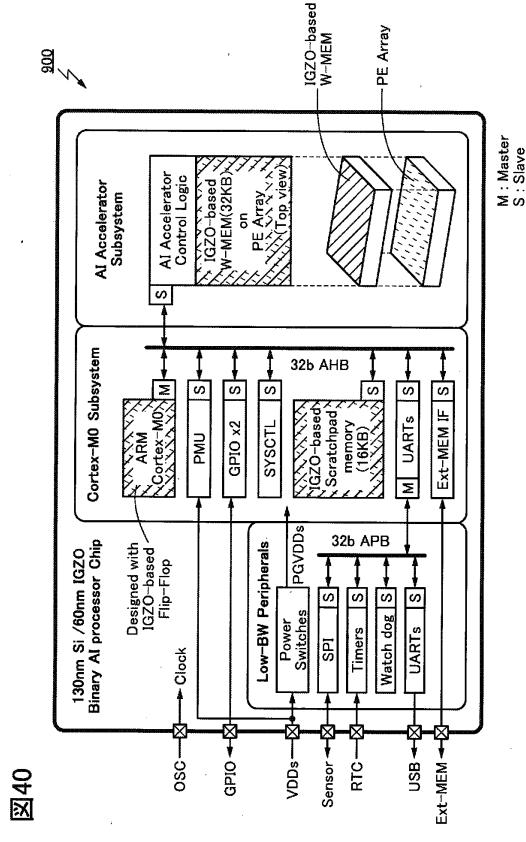

本実施の形態では、上記実施の形態で説明した半導体装置 100 の構成を含む集積回路の構成について図 33 および図 34 を参照しながら説明する。

## 【0217】

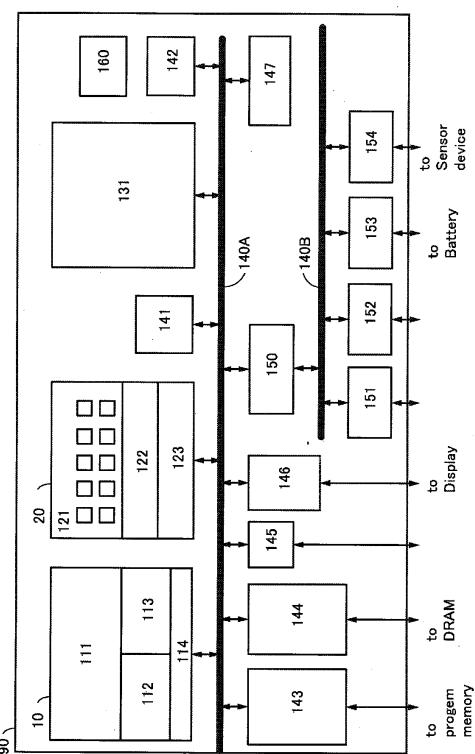

図 33 は、半導体装置 100 の構成を含む集積回路の構成例を説明するためのブロック図の一例である。

## 【0218】

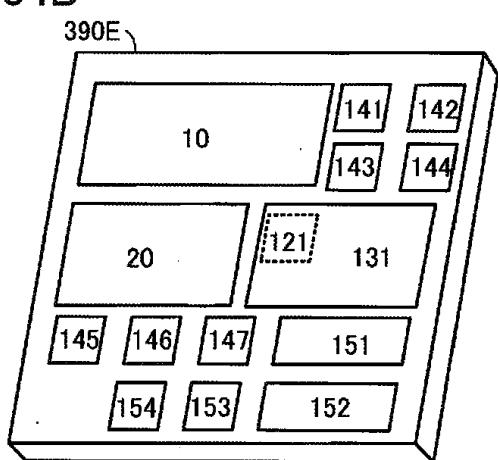

図 33 に図示する集積回路 390 は、CPU10、アクセラレータ 20、オンチップメモリ 131、DMAC (Direct Memory Access Controller) 141、電源回路 160、パワーマネジメントユニット (PMU) 142、セキュリティ回路 147、メモリコントローラ 143、DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access

10

20

30

40

50

Memory)コントローラ144、USB(Universal Serial Bus)インターフェース回路145、ディスプレイインターフェース回路146、ブリッジ回路150、割り込み制御回路151、インターフェース回路152、バッテリー制御回路153、およびADC(Analog-to-digital converter)/DAC(Digital-to-analog converter)インターフェース回路154を有する。

#### 【0219】

CPU10は、一例として、CPUコア111、命令キャッシュ112、データキャッシュ113、およびバスインターフェース回路114を有する。アクセラレータ20は、メモリ回路121、演算回路122、および制御回路123を有する。

10

#### 【0220】

CPUコア111は、複数のCPUコアを有する。命令キャッシュ112は、CPUコア111で実行する命令を一時的に記憶する回路構成とすればよい。データキャッシュ113は、CPUコア111で処理するデータまたは処理によって得られたデータを一時的に記憶する回路構成とすればよい。バスインターフェース回路114は、CPU10と、半導体装置内の他の回路とを接続するためのバスとデータやアドレス等の信号を送受信することができる回路構成であればよい。

#### 【0221】

メモリ回路121は、実施の形態1で説明したメモリ回路24に相当する。メモリ回路121は、アクセラレータ20で処理するデータを記憶する回路構成とすればよい。演算回路122は、実施の形態1で説明した演算回路23に相当する。演算回路122は、メモリ回路121に保持したデータの演算処理を行う回路構成とすればよい。制御回路123は、図5Bで図示したように、アクセラレータ20内の各回路を制御するための回路構成とすればよい。

20

#### 【0222】

高速バス140Aは、CPU10、アクセラレータ20、オンチップメモリ131、DMAC141、パワーマネジメントユニット142、セキュリティ回路147、メモリコントローラ143、DDR SDRAMコントローラ144、USBインターフェース回路145、およびディスプレイインターフェース回路146の間の各種信号を高速で送受信するためのバスである。一例としては、AMBA(Advanced Microcontroller Bus Architecture)-AHB(Advanced High-performance Bus)をバスとして用いることができる。

30

#### 【0223】

オンチップメモリ131は、集積回路390が有する回路、例えばCPU10またはアクセラレータ20に入出力するデータまたはプログラムを記憶するための回路構成を有する。

#### 【0224】

DMAC141は、ダイレクトメモリアクセスコントローラである。DMAC141を有することで、CPU10以外の周辺機器は、CPU10を介さずにオンチップメモリ131にアクセスすることができる。

40

#### 【0225】

パワーマネジメントユニット142は、集積回路390が有するCPUコア等の回路のパワーゲーティングを制御するための回路構成を有する。

#### 【0226】

セキュリティ回路147は、集積回路390と外部の回路との間で暗号化して信号を送受信するなど、信号の秘匿性を高めるための回路構成を有する。

#### 【0227】

メモリコントローラ143は、集積回路390の外部にあるプログラムメモリからCPU10またはアクセラレータ20で実行するためのプログラムを書き込みまたは読み出しを行うための回路構成を有する。

50

**【0228】**

DDR SDRAMコントローラ144は、集積回路390の外部にあるDRAM等のメインメモリとの間でデータを書き込みまたは読み出しを行うための回路構成を有する。

**【0229】**

USBインターフェース回路145は、集積回路390の外部にある回路とUSB端子を介してデータの送受信を行うための回路構成を有する。

**【0230】**

ディスプレイインターフェース回路146は、集積回路390の外部にあるディスプレイデバイスとデータの送受信を行うための回路構成を有する。

**【0231】**

電源回路160は、集積回路390内で用いる電圧を生成するための回路である。例えば、OSトランジスタのバックゲートに与える、電気的特性を安定化するための負電圧を生成する回路である。

**【0232】**

低速バス140Bは、割り込み制御回路151、インターフェース回路152、バッテリーコントローラ153、およびADC/DACインターフェース回路154の間の各種信号を低速で送受信するためのバスである。一例としては、AMBA-APP(Advanced Peripheral Bus)をバスとして用いることができる。高速バス140Aと低速バス140Bとの間の各種信号の送受信は、ブリッジ回路150を介して行う。

**【0233】**

割り込み制御回路151は、周辺機器から受け取る要求に対して、割り込み処理を行うための回路構成を有する。

**【0234】**

インターフェース回路152は、UART(Universal Asynchronous Receiver/Transmitter)や、I2C(Inter-Integrated Circuit)、SPI(Serial Peripheral Interface)などのインターフェースを機能させるための回路構成を有する。

**【0235】**

バッテリーコントローラ153は、集積回路390の外部にあるバッテリーの充放電に関するデータを送受信するための回路構成を有する。

**【0236】**

ADC/DACインターフェース回路154は、集積回路390の外部にあるMEMS(Micro Electro Mechanical Systems)デバイス等のアナログ信号を出力するデバイスとの間でデータを送受信するための回路構成を有する。

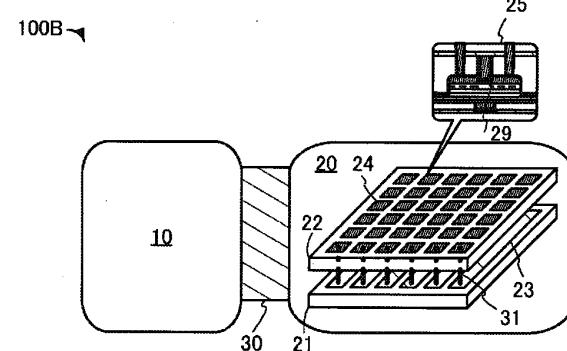

**【0237】**

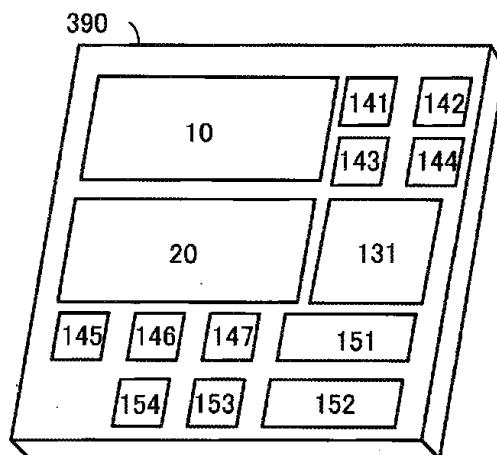

図34A、図34Bは、SoC化した際の回路ブロックの配置の一例を示す図である。図34Aに図示する集積回路390のように図33のブロック図で図示した各構成は、チップ上で領域を区切って配置することができる。

**【0238】**

なお図33で説明したオンチップメモリ131は、OSトランジスタで構成される記憶回路、例えばNOSRAM等で構成することができる。つまりオンチップメモリ131とメモリ回路121とは、同じ回路構成を有する。そのため、SoC化した際、図34Bに図示する集積回路390Eのようにオンチップメモリ131とメモリ回路121とを一体化して同じ領域内に配置することも可能である。

**【0239】**

以上説明した本発明の一態様により、新規な半導体装置および電子機器を提供することができる。又は、本発明の一態様により、消費電力の小さい半導体装置および電子機器を提供することができる。又は、本発明の一態様により、発熱の抑制が可能な半導体装置および電子機器を提供することができる。

**【0240】**

10

20

30

40

50

本実施の形態は、他の実施の形態の記載と適宜組み合わせることができる。

【0241】

(実施の形態7)

本実施の形態では、上記実施の形態で説明した集積回路390を適用することが可能な電子機器、移動体、演算システムについて、図35乃至図38を参照しながら説明する。

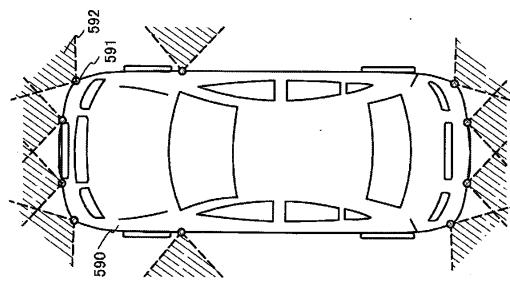

【0242】

図35Aは、移動体の一例として自動車の外観図を図示している。図35Bは、自動車内でのデータのやり取りを簡略化した図である。自動車590は、複数のカメラ591等を有する。また、自動車590は、赤外線レーダー、ミリ波レーダー、レーザーレーダーなど各種センサ(図示せず)などを備える。

10

【0243】

自動車590において、カメラ591等に上記集積回路390を用いることができる。自動車590は、カメラ591が複数の撮像方向592で得られた複数の画像を上記実施の形態で説明した集積回路390で処理し、バス593等を介してホストコントローラ594等により複数の画像をまとめて解析することで、ガードレールや歩行者の有無など、周囲の交通状況を判断し、自動運転を行うことができる。また、道路案内、危険予測などを行うシステムに用いることができる。

【0244】

集積回路390では、得られた画像データをニューラルネットワークなどの演算処理を行うことで、例えば、画像の高解像度化、画像ノイズの低減、顔認識(防犯目的など)、物体認識(自動運転の目的など)、画像圧縮、画像補正(広ダイナミックレンジ化)、レンズレスイメージセンサの画像復元、位置決め、文字認識、反射映り込み低減などの処理を行うことができる。

20

【0245】

なお、上述では、移動体の一例として自動車について説明しているが、移動体は自動車に限定されない。例えば、移動体としては、電車、モノレール、船、飛行体(ヘリコプター、無人航空機(ドローン)、飛行機、ロケット)なども挙げることができ、これらの移動体に本発明の一態様の半導体装置を適用して、人工知能を利用したシステムを付与することができる。

【0246】

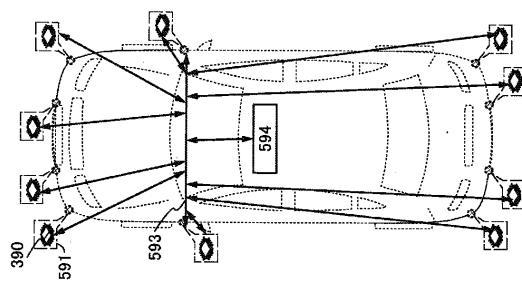

30

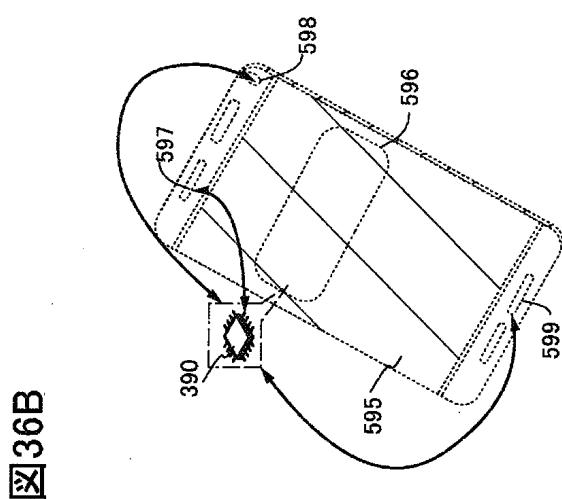

図36Aは、携帯型電子機器の一例を示す外観図である。図36Bは、携帯型電子機器内でのデータのやり取りを簡略化した図である。携帯型電子機器595は、プリント配線基板596、スピーカー597、カメラ598、マイクロフォン599等を有する。

【0247】

携帯型電子機器595において、プリント配線基板596に上記集積回路390を設けることができる。携帯型電子機器595は、スピーカー597、カメラ598、マイクロフォン599等で得られる複数のデータを上記実施の形態で説明した集積回路390を用いて処理・解析することで、ユーザの利便性を向上させることができる。また、音声案内、画像検索などを行うシステムに用いることができる。

【0248】

40

集積回路390では、得られた画像データをニューラルネットワークなどの演算処理を行うことで、例えば、画像の高解像度化、画像ノイズの低減、顔認識(防犯目的など)、物体認識(自動運転の目的など)、画像圧縮、画像補正(広ダイナミックレンジ化)、レンズレスイメージセンサの画像復元、位置決め、文字認識、反射映り込み低減などの処理を行うことができる。

【0249】

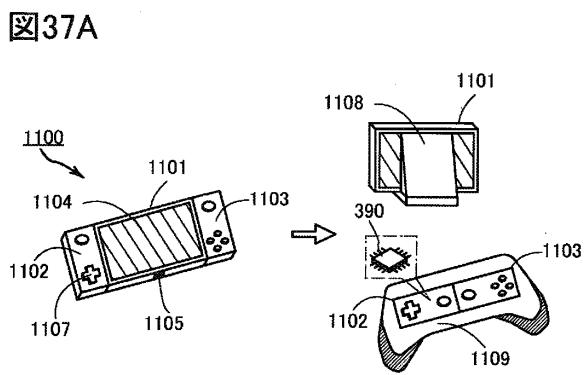

図37Aに示す携帯型ゲーム機1100は、筐体1101、筐体1102、筐体1103、表示部1104、接続部1105、操作キー1107等を有する。筐体1101、筐体1102および筐体1103は、取り外しが可能である。筐体1101に設けられている接続部1105を筐体1108に取り付けることで、表示部1104に出力される

50

映像を、別の映像機器に出力することができる。他方、筐体 1102 および筐体 1103 を筐体 1109 に取り付けることで、筐体 1102 および筐体 1103 を一体化し、操作部として機能させる。筐体 1102 および筐体 1103 の基板に設けられているチップなどに先の実施の形態に示す集積回路 390 を組み込むことができる。

【0250】

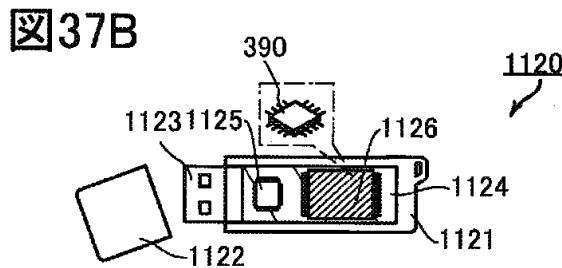

図 37B は USB 接続タイプのスティック型の電子機器 1120 である。電子機器 1120 は、筐体 1121、キャップ 1122、USB コネクタ 1123 および基板 1124 を有する。基板 1124 は、筐体 1121 に収納されている。例えば、基板 1124 には、メモリチップ 1125、コントローラチップ 1126 が取り付けられている。基板 1124 のコントローラチップ 1126 などに先の実施の形態に示す集積回路 390 を組み込むことができる。

10

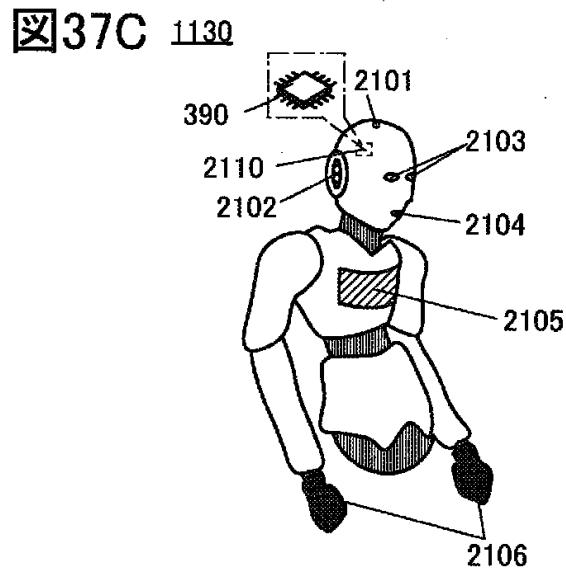

【0251】

図 37C は人型のロボット 1130 である。ロボット 1130 は、センサ 2101 乃至 2106、および制御回路 2110 を有する。例えば、制御回路 2110 には、先の実施の形態に示す集積回路 390 を組み込むことができる。

【0252】

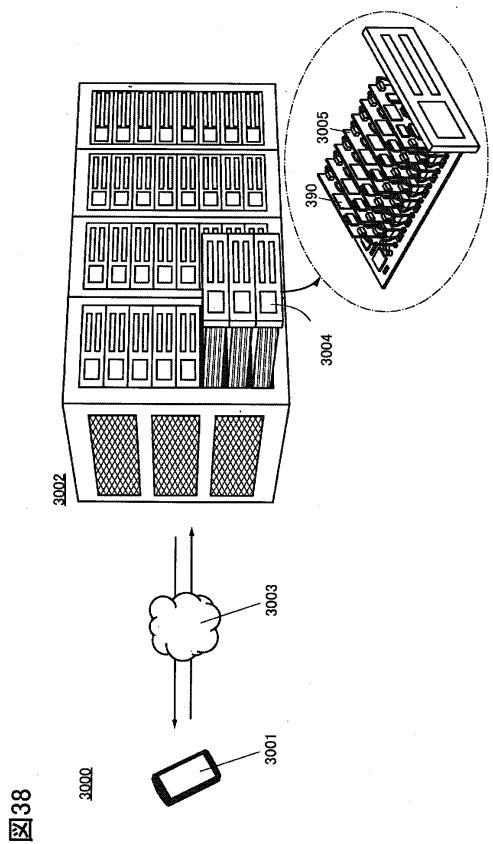

上記実施の形態で説明した集積回路 390 は、電子機器に内蔵する代わりに、電子機器と通信を行うサーバーに用いることもできる。この場合、電子機器とサーバーによって演算システムが構成される。図 38 に、システム 3000 の構成例を示す。

20

【0253】

システム 3000 は、電子機器 3001 と、サーバー 3002 によって構成される。電子機器 3001 とサーバー 3002 間の通信は、インターネット回線 3003 を介して行うことができる。

【0254】

サーバー 3002 には、複数のラック 3004 を有する。複数のラックには、複数の基板 3005 が設けられ、当該基板 3005 上に上記実施の形態で説明した集積回路 390 を搭載することができる。これにより、サーバー 3002 にニューラルネットワークが構成される。そして、サーバー 3002 は、電子機器 3001 からインターネット回線 3003 を介して入力されたデータを用いて、ニューラルネットワークの演算を行うことができる。サーバー 3002 による演算の結果は必要に応じて、インターネット回線 3003 を介して電子機器 3001 に送信することができる。これにより、電子機器 3001 における演算の負担を低減することができる。

30

【0255】

本実施の形態は、他の実施の形態の記載と適宜組み合わせることができる。

【0256】

(本明細書等の記載に関する付記)

以上の実施の形態、および実施の形態における各構成の説明について、以下に付記する。

【0257】

各実施の形態に示す構成は、他の実施の形態あるいは実施例に示す構成と適宜組み合わせて、本発明の一態様とすることができます。また、1つの実施の形態の中に、複数の構成例が示される場合は、構成例を適宜組み合わせることが可能である。

40

【0258】

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）、および／または、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、または置き換えなどを行うことが出来る。

【0259】

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、または明細書に記載される文章を用いて述べる内容のことである。

【0260】

50

なお、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）、および／または、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）に対して、組み合わせることにより、さらに多くの図を構成させることが出来る。

#### 【0261】

また本明細書等において、ブロック図では、構成要素を機能毎に分類し、互いに独立したブロックとして示している。しかしながら実際の回路等においては、構成要素を機能毎に切り分けることが難しく、一つの回路に複数の機能が係わる場合や、複数の回路にわたって一つの機能が関わる場合があり得る。そのため、ブロック図のブロックは、明細書で説明した構成要素に限定されず、状況に応じて適切に言い換えることができる。

10

#### 【0262】

また、図面において、大きさ、層の厚さ、または領域は、説明の便宜上任意の大きさに示したものである。よって、必ずしもそのスケールに限定されない。なお図面は明確性を期すために模式的に示したものであり、図面に示す形状または値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、または、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

#### 【0263】

また、図面等において図示する構成要素の位置関係は、相対的である。従って、図面を参照して構成要素を説明する場合、位置関係を示す「上に」、「下に」等の語句は便宜的に用いられる場合がある。構成要素の位置関係は、本明細書の記載内容に限定されず、状況に応じて適切に言い換えることができる。

20

#### 【0264】

本明細書等において、トランジスタの接続関係を説明する際、「ソースまたはドレインの一方」（または第1電極、または第1端子）、「ソースまたはドレインの他方」（または第2電極、または第2端子）という表記を用いる。これは、トランジスタのソースとドレインは、トランジスタの構造または動作条件等によって変わるためである。なおトランジスタのソースとドレインの呼称については、ソース（ドレイン）端子や、ソース（ドレイン）電極等、状況に応じて適切に言い換えることができる。

#### 【0265】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

30

#### 【0266】

また、本明細書等において、電圧と電位は、適宣言い換えることができる。電圧は、基準となる電位からの電位差のことであり、例えば基準となる電位をグラウンド電圧（接地電圧）とすると、電圧を電位に言い換えることができる。グラウンド電位は必ずしも0Vを意味するとは限らない。なお電位は相対的なものであり、基準となる電位によっては、配線等に与える電位を変化させる場合がある。

#### 【0267】

また本明細書等において、ノードは、回路構成やデバイス構造等に応じて、端子、配線、電極、導電層、導電体、不純物領域等と言い換えることが可能である。また、端子、配線等をノードと言い換えることが可能である。

40

#### 【0268】

本明細書等において、AとBとが接続されている、とは、AとBとが電気的に接続されているものをいう。ここで、AとBとが電気的に接続されているとは、AとBとの間で対象物（スイッチ、トランジスタ素子、またはダイオード等の素子、あるいは当該素子および配線を含む回路等を指す）が存在する場合にAとBとの電気信号の伝達が可能である接続をいう。なおAとBとが電気的に接続されている場合には、AとBとが直接接続されている場合を含む。ここで、AとBとが直接接続されているとは、上記対象物を介すこと

50

なく、AとBとの間で配線（または電極）等を介してAとBとの電気信号の伝達が可能である接続をいう。換言すれば、直接接続とは、等価回路で表した際に同じ回路図として見なせる接続をいう。

【0269】

本明細書等において、スイッチとは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有するものをいう。または、スイッチとは、電流を流す経路を選択して切り替える機能を有するものをいう。

【0270】

本明細書等において、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲートとが重なる領域、またはチャネルが形成される領域における、ソースとドレインとの間の距離をいう。

10

【0271】

本明細書等において、チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。

【0272】

なお本明細書等において、「膜」、「層」などの語句は、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

20

【実施例】

【0273】

本発明の一態様に係る半導体装置の一例として、チャネルが形成される半導体層にIn-Ga-Zn酸化物を用いたトランジスタ（「IGZO-FET」ともいう。）とSiトランジスタ（「Si-FET」ともいう。）を用いたBinary AI Processorを作製した。本実施例では、作製したBinary AI Processorの構成、および動作のシミュレーション結果について説明する。作製したBinary AI Processorは、後述するNooffコンピューティング可能な半導体装置である。

【0274】

30

近年、IoT（Internet of Things）およびAIなどの技術が注目されている。IoT分野で使用される機器（IoT機器）では、消費電力の低減が求められる一方で、AI処理時は演算性能の高さが求められる。

【0275】

消費電力の低減を目的として、待機状態の回路への電源供給を遮断するパワーゲーティング（PG）技術が知られている。また、IoT機器などの低消費電力化を実現する技術として、PG技術にメモリを組み合わせたNormally-off（Nooff）コンピューティングが提案されている。

【0276】

40

Nooffコンピューティングでは、システム全体としては動作しているが、一時的に動作不要となる回路に対して当該回路のデータをメモリに退避させた後に、当該回路への電源供給を遮断する動作が行われる。Nooffコンピューティングに用いるメモリとして、ReRAM（抵抗変化型メモリ）、MRAM（磁気メモリ）、PCM（相変化メモリ）などの不揮発性メモリが検討されている。

【0277】

OSメモリは、ReRAM、MRAM、およびPCMよりもデータ書き込み時のエネルギー消費が少ないため、Nooffコンピューティングに用いるメモリとして好適である。なお、OSトランジスタは、ReRAM、MRAM、およびPCMなどに用いることも可能である。

【0278】

50

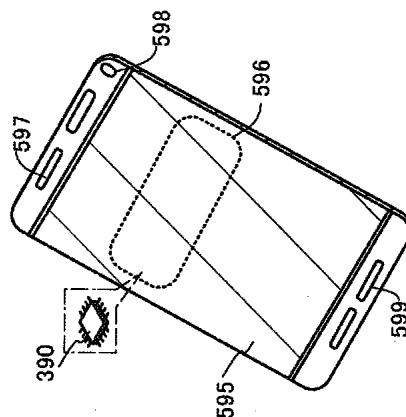

作製した Binary AI Processor Chip (以下、「BAP900」ともいう。) は、130 nm Si CMOSプロセスで形成された演算器 (PE: Processing Element) とPE上に60 nm IGZOプロセスで形成されたOSメモリを含む。

#### 【0279】

また、BAP900は、IGZO-FETを用いたOSメモリをAI Acceleratorの重みパラメータを格納するメモリ (W-MEM) として使用し、当該メモリの読み出し線を演算器と直結した構成を有する。

#### 【0280】

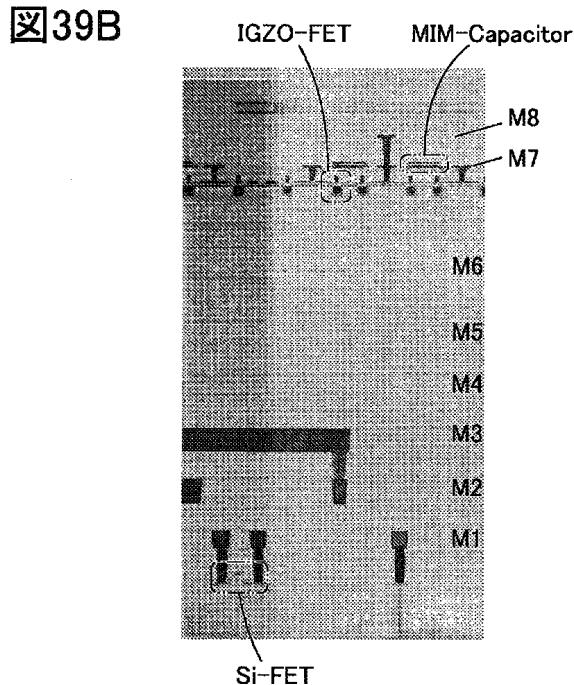

図39Aに作製したBAP900の外観写真を示す。図39Bに、BAP900の一部を拡大した断面TEM写真を示す。BAP900は、層M1乃至層M8を有する。なお、層M1乃至層M8は、配線または電極などの導電体を含む層である。図39Bより、Si-FETの上方に、IGZO-FETおよびMIM (Metal-Insulator-Metal) 構造の容量 (MIM-Capacitor) が設けられていることがわかる。表8にBAP900の主な仕様を示す。

#### 【0281】

#### 【表8】

|                   |               |                                          |

|-------------------|---------------|------------------------------------------|

| Technology        |               | 130 nm Si CMOS,<br>60 nm IGZO-FET (BEOL) |

| Supply voltage    |               | 1.2 V, 3.3 V                             |

| CPU               |               | ARM Cortex-M0                            |

| AI Accelerator    | Weight memory | 32 KB                                    |

| Subsystem         | # of PE       | 128                                      |

| Scratchpad memory |               | 16 KB                                    |

#### 【0282】

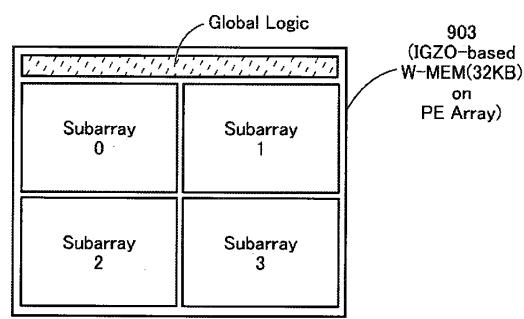

BAP900は、回路部901乃至回路部905を有する。回路部901は、32 bitのARM Cortex-M0 CPUと、その周辺回路 (Peripherals) と、を含む。回路部902は、AI Accelerator Control Logicを含む。回路部903は、PEアレイ上に設けられた、IGZOプロセスで形成された32 KBのW-MEMを含む (IGZO-based W-MEM (32 KB) on PE Array)。回路部904は、16 KBのScratchpad memoryを含む。回路部905は、Power Switchesを含む。

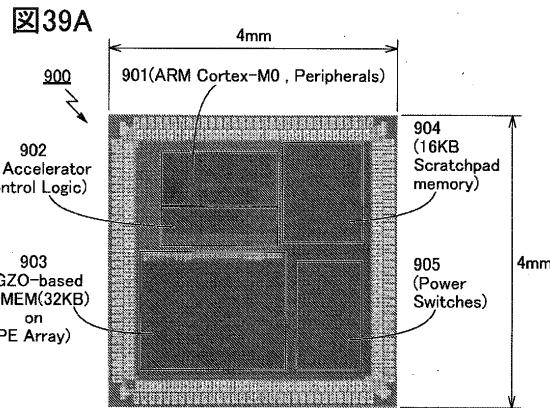

#### 【0283】

図40は、BAP900の詳細なシステム構成を説明するブロック図である。BAP900は、Cortex-M0サブシステム (Cortex-M0 Subsystem)、AI Acceleratorサブシステム (AI Accelerator Subsystem)、およびCortex-M0サブシステムよりも動作周波数が低い周辺回路 (Low-BW (Band Width) Peripherals) を含む。

#### 【0284】

Cortex-M0サブシステムは、32 bitのARM Cortex-M0 CPU、電源管理ユニット (PMU: Power Management Unit)、2つのGPIO (General purpose input/output)、SYSCTL、記憶容量16 KByteの組み込みIGZOスクラッチメモリ、UARTs (Universal Asynchronous Receiver/Transmitter)、および外部メモリインターフェイス (Ext-MEM IF) を含む。それぞれは、32ビットのAHBバスライン (32 b AHB) を介して接続される。

10

20

30

40

50

## 【0285】

AI Acceleratorサブシステムは、AI Accelerator制御回路(AI Accelerator Control Logic)、PEアレイ(PE Array)、およびPEアレイ上に設けられた記憶容量32KbyteのW-MEMを含む。PEアレイは、128個のPEを含む。

## 【0286】

Low-BW Peripheralsは、パワースイッチ(Power Switches)、SPI(Serial Peripheral Interface)、タイマー(Timers)、Watch dog、およびUARTsを含む。パワースイッチ、SPI、タイマー、Watch dog、およびUARTsは、32ビットのAPBバスライン(32b APB)を介して接続される。パワースイッチは、Cortex-M0サブシステムへの電力供給を制御する機能を有する。

10

## 【0287】

また、BAP900は、OSCノード、GPIOノード、VDDsノード、Sensorノード、RTCノード、USBノード、およびExt-MEMノードを有する。これらのノードを介して信号の入出力などが行われる。例えば、OSCノードを介して外部からクロック信号(Clock)が入力される。なお、図40に記す「M」はMasterを示し、「S」はSlaveを示している。

## 【0288】

電源ドメインは、VDDsノードを介して外部から常時供給される電源VDDsと、PG可能な電源PGVDDsの2つがある。PMUは、動作モードに応じて電力供給を制御する機能を有する。待機モードで動作する場合、PMUはPG可能な回路に対してPGを行うことで消費電力を削減する。AI処理(積和演算処理)を行う際にAI Acceleratorサブシステムを用いることで、CPUによる演算よりも高速かつ高効率にAI処理を行うことができる。

20

## 【0289】

BAP900はPGが可能なため、AI処理を行わない期間は、システム全体として消費電力を低減できる。一方で、Sensorノードからの信号入力が発生すると、元のシステム状態を瞬間に復元し、すぐにAI処理を実行できる。

## 【0290】

30

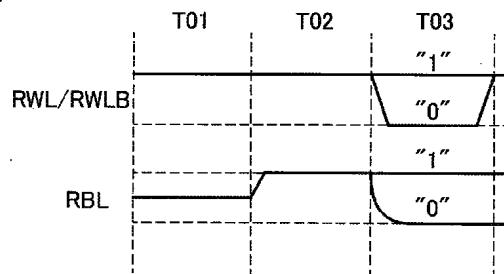

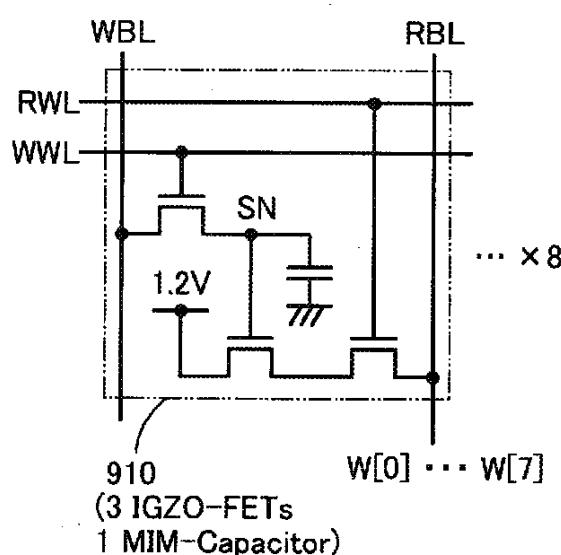

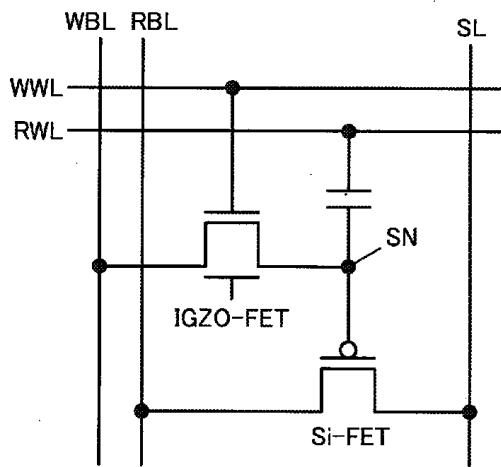

図41Aに、W-MEMに含まれるメモリセル910の回路図を示す。メモリセル910は、3つのIGZO-FETと1つの容量を含むメモリセルである。当該容量はMIM(Metal-Insulator-Metal)構造の容量である。メモリセル910の電源電圧は3.3Vである。メモリセル910はノードSNに電荷を保持するメモリのため、電源遮断時にもデータが消失しない。

## 【0291】

1つのメモリセル910で、1ビットの重み情報Wを保持する。重み情報Wは、配線WBLを介してノードSNに書き込まれる。ノードSNに書き込まれた重み情報Wは、配線RBLを介して読み出される。8つのメモリセルを用いることで、重み情報W[0]から重み情報W[7]で構成される8ビットの重み情報W(「W[7:0]」ともいう。)を保持することができる。

40

## 【0292】

図41Bは、図41Aに示したメモリセルの動作例を示すタイミングチャートである。図41Bは、書き込みモード(Write)、待機モード(Sleep)、および読み出しモード(Read)における、配線WBL、配線WWL、配線RBL、および配線RWLの電位変化を示している。配線WBLには1.7Vまたは0Vが供給される。配線WWLには3.3Vまたは0Vが供給される。配線RBLには1.0Vまたは0Vが供給される。配線RWLには1.2Vまたは0Vが供給される。また、図41Bでは、ノードSNにdata0を供給する場合の電位変化と、data1を供給する場合の電位変化を示している。

50

## 【0293】

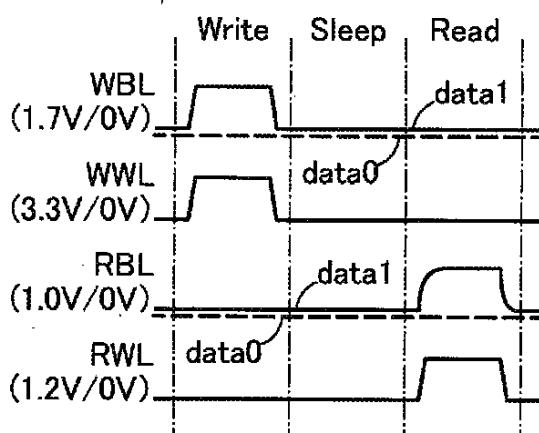

図41Cは、P E 9 2 0の構成を示すブロック図である。P E 9 2 0は、電源電圧1.2VのSiロジックセルで作製した。P E 9 2 0は、センスアンプ921(SA)、乗算回路922(M u l t i p l i e r)と加算回路923(Adder tree)を含むbinary積和演算器924(M A C)、アキュムレータ925(A c c u m u l a t o r)を含む。アキュムレータ925は、バッチ正規化用の1ビット(1b)しきい値加算器と11ビットのレジスタ(11bit register)を含む。

## 【0294】

1つのP E 9 2 0には8本の配線R B Lが並列に接続され、8ビットの重み情報W[7:0]が入力される。入力された重み情報W[7:0]は、センスアンプ(SA)で増幅された後に積和演算処理に使用されるか、積和演算処理に使用されず直接読み出される。どちらが行われるかは、P r o c e s s i n g / R e a d s e l e c t o r信号で決定される。積和演算処理に使用される場合は、重みW[7:0]は乗算回路で信号A[7:0]と乗算され、積信号M[7:0]に変換される。直接読み出す場合、信号r e a d o u t[7:0]として出力される。

10

## 【0295】

積信号M[7:0]はAdder tree回路で加算され、積和信号M Aに変換される。M A C / B N s e l e c t o r信号によって、積和信号M Aおよびしきい値信号T Hのどちらをアキュムレータに入力するかが決定される。アキュムレータは、11ビットの信号m a c o u t[10:0]を出力する機能と、インバータ回路を介してサインビット(S i g n b i t)信号を出力する機能と、を有する。

20

## 【0296】

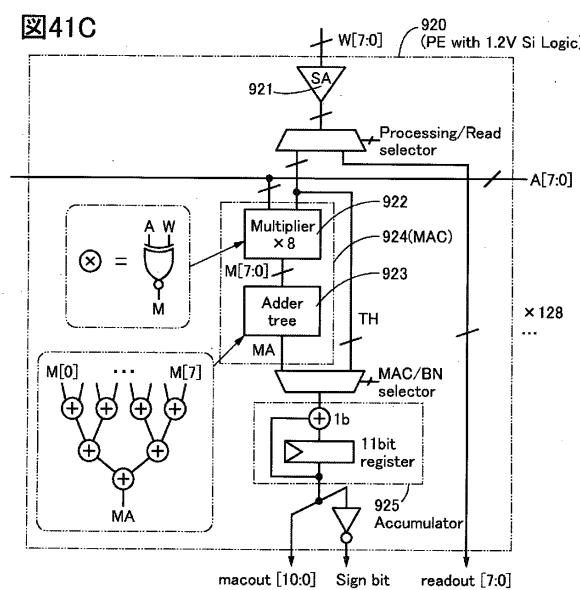

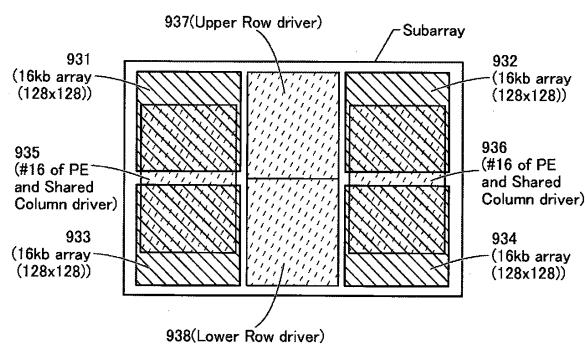

図42Aは、回路部903(I G Z O - b a s e d W - M E M(32KB) on P E A r r a y)の構成を示すブロック図である。回路部903は、1つのG l o b a l L o g i c回路と4つのS u b a r r a y回路(S u b a r r a y 0乃至S u b a r r a y 3)を含む。

## 【0297】

図42Bは、1つのS u b a r r a y回路の構成を示すブロック図である。1つのS u b a r r a y回路は、回路部931乃至回路部938を含む。回路部931乃至回路部934は、それぞれが $128 \times 128$ 個のメモリセル910を含む記憶容量16kビットのメモリセルアレイ(16k b a r r a y( $128 \times 128$ ))として機能する。1つのメモリセルアレイは、128本の配線R B L(読み出しひき線)を含む。また、1本の配線R B Lには128個のメモリセルが接続されている。

30

## 【0298】

回路部935および回路部936は、それぞれが、16個のP E 9 2 0および列ドライバを有する(# 1 6 o f P E a n d S h a r e d C o l u m n d r i v e r)。回路部935が有する列ドライバは、回路部931および回路部933を駆動する。回路部936が有する列ドライバは、回路部932および回路部934を駆動する。回路部937は、回路部931および回路部932を駆動する行ドライバ(U p p e r R o w d r i v e r)を含む。回路部938は、回路部933および回路部934を駆動する行ドライバ(L o w e r R o w d r i v e r)を含む。

40

## 【0299】

よって、回路部903全体では、P Eアレイに1024本の配線R B Lが並列に接続される。1024本の配線R B Lから読み出された情報は並列演算される。また、行ドライバをメモリセルアレイと重ねて設けることで、情報の読み出しときエネルギーとチップ面積を削減できる。

## 【0300】

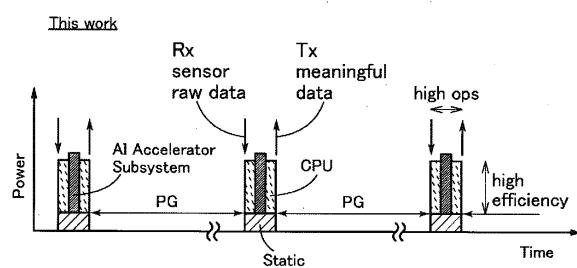

図43Aに、作製したB A P 9 0 0の動作期間中に生じる消費電力の推移とP G期間の概念図を示す( T h i s w o r k)。比較例として、図43Bに従来動作(P Gを行わない)の動作期間中に生じる消費電力推移の概念図を示す( C o n v e n t i o n a l

50

）。図43A、図43Bとともに、縦軸は消費電力（Power）を示し、横軸は経過時間（Time）を示している。

#### 【0301】

従来動作では、電源供給が停止すると重み情報やニューラルネットワーク構造などの情報が消えるため、再起起動時にこれらの情報をROMなどから読み出して、RAMに書き込む必要があった（ROM/RAM access）。よって、演算処理時間の短縮が難しかった。また、演算処理時間に比例して、メモリアクセス時の消費電力およびCPUの消費電力のみでなく、静的消費電力（Static）も増加する。

#### 【0302】

今回作製したBAP900は、センサノードからBAP900の起動信号Rx（sensor raw data）が入力されると起動し、CPUからAI Acceleratorサブシステムへ生データが転送される。生データはAI Acceleratorサブシステムで演算処理され、演算結果が信号Tx（meaningful data）として出力される。その後、PGが行われる。AI Acceleratorサブシステムでは並列処理が行われるため、従来例よりも演算処理時間が短く（high ops）、消費電力も小さい。よって効率の良い演算処理が実現できる（high efficiency）。

10

#### 【0303】

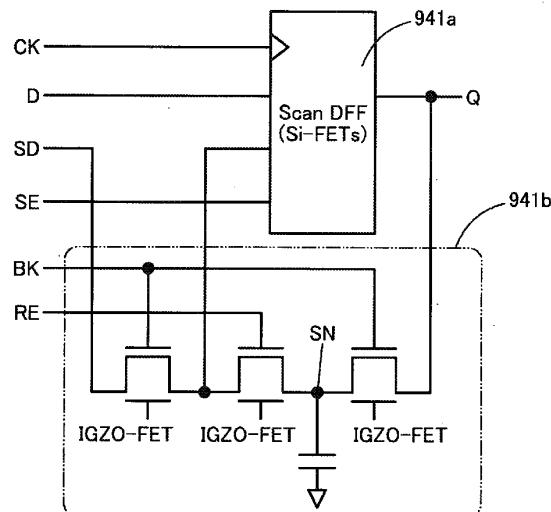

また、今回作製したBAP900では、PG開始直前に、重み情報などの復帰時に必要な情報が保持される。このような情報の保持にはOSメモリを用いることが好ましい。図44Aおよび図44Bに、BAP900に用いた情報保持回路の一例を示す。

20

#### 【0304】

図44Aに示す情報保持回路941は、Siプロセス（Si-FET）で作製したスキャンDフリップフロップ941a（Scan DFF）に、IGZO-FET含むOSメモリ941bを組み合わせた構成を有する。

#### 【0305】

スキャンDフリップフロップ941aは、端子CK、端子D、端子SE、および端子Qと電気的に接続される。また、スキャンDフリップフロップ941aは、IGZO-FETを介して端子Qと電気的に接続される。OSメモリ941bは端子BK、端子RE、および端子Qと電気的に接続される。

30

#### 【0306】

図44Bに示す情報保持回路942は、Si-FET、IGZO-FET、および容量で構成された、1Tr1C型のスクラッチメモリセル（IGZO-based Scratchpad memory cell）である。情報保持回路942は、配線WWL、配線RWL、配線WBL、配線RBL、および配線SLと電気的に接続される。

#### 【0307】

情報保持回路941および情報保持回路942とともに、復帰時に必要な情報をノードSNに保持することができる。

#### 【0308】

回路シミュレーションソフトウェアを用いて、BAP900の動作を検証した。回路シミュレーションソフトウェアとして、SILVACO社SmartSpiceを使用した。

40

#### 【0309】

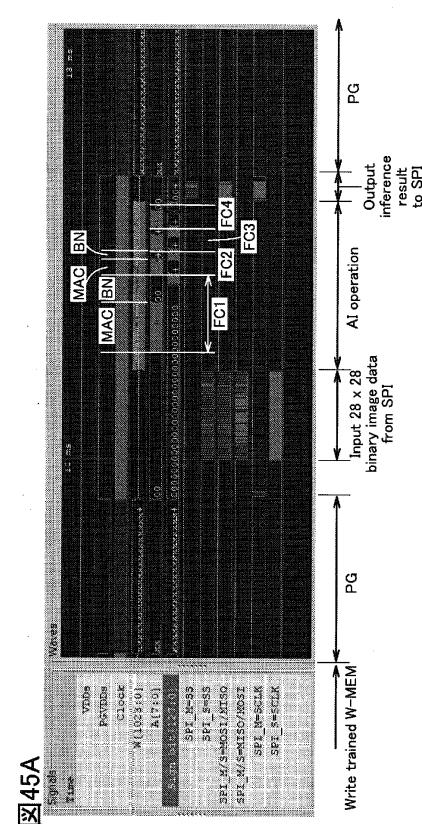

シミュレーションでは、以下の動作を検証した。はじめに、W-MEMに学習済の重みデータを格納し（Write trained W-MEM）、次に、電源供給を停止した（PG）。続いて、電源供給を再開し、SPIを介して解像度が28×28の2値イメージデータを入力して（Input 28 × 28 binary image data from SPI）、推論動作を行なった（AI operation）。その後、推論結果をSPIに出力し（Output inference result to SPI）、再び電源供給を停止した。

#### 【0310】

50

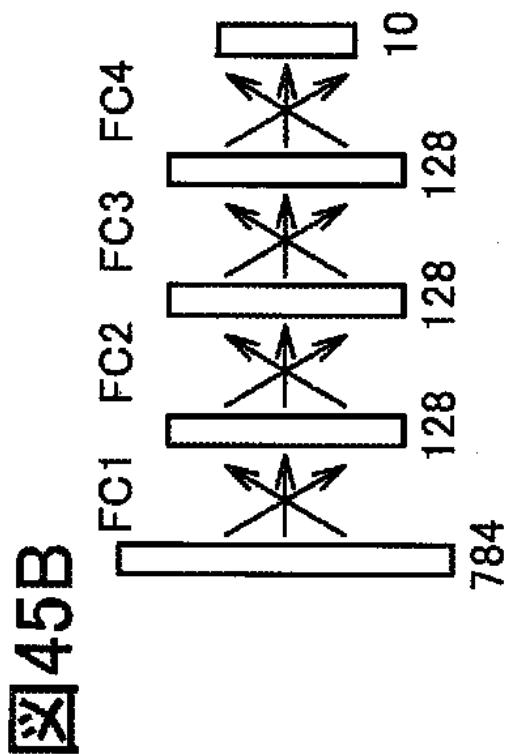

図45Aに、シミュレーション実行後の動作波形の一例を示す。図45Bに、当該シミュレーションで想定した全結合型のニューラルネットワークモデルを示す。シミュレーションで想定したニューラルネットワークモデルでは、784個のニューロンを有する入力層と、10個のニューロンを有する出力層の間に、128個のニューロンを有する隠れ層を3層設定した。なお、図45Aおよび図45Bでは、入力層と1つめの隠れ層の全結合をFC1、1つめの隠れ層と2つめの隠れ層の全結合をFC2、2つめの隠れ層と3つめの隠れ層の全結合をFC3、3つめの隠れ層と出力層の全結合をFC4と示している。シミュレーションによって、前述した動作が問題なく行われることが確認できた。

## 【0311】

シミュレーションから見積もられた演算効率、消費エネルギーなどを表9に示す。

10

## 【0312】

## 【表9】

|                                                        |                |

|--------------------------------------------------------|----------------|

| Memory Read energy : W-MEM cell                        | 1.4pJ/bit      |

| Computation energy : 1PE                               | 2.46pJ         |

| Energy efficiency<br>(w/ AI Accelerator control Logic) | 0.54TOPS/W     |

| Performance                                            | 0.82GOPS       |

| W-MEM retention time                                   | > 1 hour @85°C |

20

## 【0313】

シミュレーションによって、AI Acceleratorサブシステムを使用したBAP900の演算性能が0.82GOPSであることがわかった。本実施例では記載しないが、別途シミュレーションを行ったAI Acceleratorサブシステムを使用しない場合のBAP900の演算性能と比較したところ、約215倍の演算性能が得られていた。また、演算効率は0.54TOPS/Wであることがわかった。

## 【0314】

IGZO-FETは、極低消費電力、高速復帰が要求されるイベントドリブンシステムと相性がよく、IoT機器や末端機器でのAIアプリケーションに好適に用いることができる。

30

## 【符号の説明】

## 【0315】

10 : CPU、20 : アクセラレータ、21 : 演算処理部、22 : メモリ部、23 : 演算回路、24 : メモリ回路、29 : 半導体層、30 : バス、31 : 配線、100 : 半導体装置

40

50

【図面】

【図 1 A】

図1A

【図 1 B】

図1B

【図 2 A】

図2A

【図 2 B】

図2B

【図 3 A】

図3A

【図 3 B】

図3B

【図 4】

【図 5 A】

図5A

図4

【図 5 B】

図5B

【図 6 A】

図6A

【図 6 B】

図6B

【図 7 A】

図7A

10

20

30

40

50

【図 7 B】

図7B

【図 8 A】

図8A

10

【図 8 B】

図8B

【図 9】

図9

20

30

40

50

【図10A】

図10A

【図10B】

図10B

10

【図10C】

図10C

【図11A】

図11A

20

30

40

50

【図 11B】

図11B

【図 12A】

図12A

10

20

【図 12B】

図12B

【図 13】

【図14A】

図14A

【図14B】

図14B

10

【図15A】

図15A

【図15B】

図15B

20

30

40

50

【図16】

図16

【図17】

図17

10

20

【図18A】

図18A

【図18B】

図18B

30

40

50

【図 19 A】

図19A

【図 19 B】

図19B

【図 20 A】

図20A

【図 20 B】

図20B

【図 2 1】

図21

【図 2 2 A】

図22A

10

【図 2 2 B】

図22B

【図 2 3】

図23

20

30

40

50

【図 24】

図24

【図 25 A】

図25A

10

20

【図 25 B】

図25B

【図 26 A】

図26A

30

40

50

【図 2 6 B】

図26B

【図 2 7 A】

図27A

10

【図 2 7 B】

図27B

20

【図 2 8 A】

図28A

30

40

50

【図 28B】

図28B

【図 29】

図29

10

20

30

40

【図 30】

図30

【図 31A】

図31A

Flip-flop

220

40

50

【図31B】

図31B

### 【図32】

图32

### 【図33】

1

【図34A】

义 34A

33

【図34B】

図34B

【図35A】

図35A

10

【図35B】

図35B

【図36A】

図36A

20

30

40

50

【図36B】

図36B

【図37A】

10

【図37B】

図37B

【図37C】

20

30

40

50

【図38】

【図39B】

【図39A】

【図40】

【図 4 1 A】

図41A

【図 4 1 B】

図41B

10

20

【図 4 1 C】

図41C

【図 4 2 A】

図42A

30

40

50

【図 4 2 B】

図42B