(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5431188号

(P5431188)

(45) 発行日 平成26年3月5日(2014.3.5)

(24) 登録日 平成25年12月13日(2013.12.13)

(51) Int.Cl.

G06F 11/28 (2006.01)

F 1

G 06 F 11/28

L

請求項の数 1 (全 9 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2010-15711 (P2010-15711)    |

| (22) 出願日     | 平成22年1月27日 (2010.1.27)        |

| (65) 公開番号    | 特開2010-174891 (P2010-174891A) |

| (43) 公開日     | 平成22年8月12日 (2010.8.12)        |

| 審査請求日        | 平成24年2月7日 (2012.2.7)          |

| (31) 優先権主張番号 | 10 2009 006 517.2             |

| (32) 優先日     | 平成21年1月28日 (2009.1.28)        |

| (33) 優先権主張国  | ドイツ(DE)                       |

(73) 特許権者 506012213

ディスペース デジタル シグナル プロ

セッシング アンド コントロール エン

ジニアリング ゲゼルシャフト ミット

ベシュレンクテル ハフツィング

d s p a c e   d i g i t a l   s i g

n a l   p r o c e s s i n g   a n d   c

o n t r o l   e n g i n e e r i n g

G m b H

ドイツ連邦共和国 パデルボルン ラーテ

ナウシュトラーゼ 26

R a t h e n a u s t r . 2 6 , D - 3 3

1 0 2 P a d e r b o r n , G e r m

a n y

最終頁に続く

(54) 【発明の名称】制御装置を調整ユニットにより調整する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

制御装置 (ECU) を調整ユニット (IN) により調整する方法であって、前記制御装置 (ECU) は、少なくとも 1 つのマイクロコントローラ (PC) と、複数のメモリセルを有する少なくとも 1 つの第 1 のメモリ (SP1) と、少なくとも 1 つのデバッグインターフェース (TRDE) と、を含んでおり、

前記マイクロコントローラ (PC) と前記デバッグインターフェース (TRDE) はデータ線 (20) により前記第 1 のメモリ (SP1) と接続されており、

該デバッグインターフェース (TRDE) がメモリ内容を監視する機能を有するものである形式の方法において、

第 1 の値 (V1X) が、第 1 の時点 (t1) に、前記制御装置 (ECU) によって前記第 1 のメモリ (SP1) の第 1 のメモリセルに書き込まれ、

前記第 1 の時点 (t1) に前記第 1 の値 (V1X) が書き込まれたという情報は、前記デバッグインターフェース (TRDE) により前記調整ユニット (IN) に通知され、

処理ルーチン (R1U) のトリガ時点を、前記第 1 の時点 (t1) に前記デバッグインターフェース (TRDE) から前記調整ユニット (IN) へ送られた情報を用いて、前記調整ユニット (IN) により求め、

前記第 1 のメモリ (SP1) の第 1 のメモリセルが前記制御装置 (ECU) によって第 3 の時点 (t3) において読み出される前に、前記調整ユニット (IN) が前記処理ルーチン (R1U) を用いて第 2 の時点 (t2) に第 2 の値 (V1Y) を、前記デバッグイン

10

20

タフェース(ＴＲＤＥ)を介して前記第1のメモリ(ＳＰ1)の第1のメモリセルに上書きするようとする、

ことを特徴とする制御装置(ＥＣＵ)を調整ユニット(ＩＮ)により調整する方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、請求項1の上位概念に従った制御装置の調整方法と、請求項12の上位概念に従った調整ユニットに関する。

【背景技術】

【0002】

制御装置は多くの技術分野で多数使用されている。特に重要な適用分野はなかでも自動車のエンジン制御と飛行機のエンジン制御である。

10

【0003】

制御装置の調整方法は特許文献1から公知である。この方法では、調整装置が制御装置デバッグインターフェースと調整装置内に形成されたメモリ領域とを用いて制御装置のデータを調整装置の前記メモリ領域に反映させ、さらに制御装置デバッグインターフェースを使用してデータを制御装置のメモリにも反映させる。1つの実施形態では、データは調整装置内で整合ユニットにより受信され、時間的な順序づけのためにタイムスタンプを付与される。さらに、整合ユニットは内部トリガ信号と外部トリガ信号のための端子を有しており、調整装置内の相応するサブユニットの活動化、および、例えばバイパスルーチンの開始は、これらの端子によって可能になる。

20

【0004】

特許文献2からは、制御装置を監視する方法が公知である。この方法では、制御装置を監視するために調整装置はマイクロコントローラと、少なくとも1つのメモリと、少なくとも1つのデバッグインターフェースを有している。このデバッグインターフェースはいわゆるトレース機能を有しており、監視すべきアドレスをモニタリングすることができる。

【0005】

上記の方法から明らかなように、制御装置機能の調整は時間コストがかかり、いわゆる外部バイパス法によって実行されることが多い。その場合、制御装置のプログラムの中で固定的に設定された制御装置のサービス呼び出しによるプログラムの処理の際に、外部へ伝達されるトリガパルスにより外部調整装置において割り込み処理がトリガされる。割り込み処理の際、さらに計算に必要な値が調整装置に送られる。調整装置での計算の後、変更された値が制御装置に送り返される。サービス呼び出しが制御装置のプログラムコードに固定的に対応付けられているため、サービス呼び出しポイントを後で変更することは非常にコストがかかり、制御装置メーカごとに後で莫大なコストをかけて実施するしかない。というのも、既にある制御装置プログラムを新たに移し換えなければならないからである。さらに、サービス呼び出しポイントによって必要なメモリの量が増え、制御装置プログラムの処理速度に不利な影響が出てしまう。

30

【先行技術文献】

【特許文献】

40

【0006】

【特許文献1】DE 10 2004 027 033 A1

【特許文献2】DE 10 2006 062 555 A1

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の課題は制御装置を有利に調整することのできる方法を提供することである。本発明のもう1つの課題はこの方法を実施するための調整ユニットを提供することである。

【課題を解決するための手段】

【0008】

50

第1の課題は、制御装置を調整ユニットにより調整する方法であって、前記制御装置は少なくとも1つのマイクロコントローラ、複数のメモリセルを有する少なくとも1つのメモリ、および少なくとも1つのデバッグインターフェースを含んでおり、該デバッグインターフェースがメモリ内容を監視する機能を有するものである形式の方法において、第1の値が前記制御装置によって第1のメモリの第1のメモリセルに書き込まれる第1の時点を前記デバッグインターフェースにより検知し、処理ルーチンのトリガ時点を前記第1の時点に前記デバッグインターフェースから前記調整ユニットへ送られた情報を用いて前記調整ユニットにより求め、前記第1のメモリの第1のメモリセルが前記制御装置によって第3の時点において読み出される前に、前記調整ユニットが前記処理ルーチンを用いて第2の時点に第2の値を前記デバッグインターフェースを介して前記第1のメモリの第1のメモリセルに書き込むようにすることにより解決される。10

#### 【0009】

第2の課題は、制御装置を調整する調整ユニットであって、前記制御装置は少なくとも1つのマイクロコントローラ、複数のメモリセルを有する少なくとも1つのメモリ、および少なくとも1つのデバッグインターフェースを含んでおり、該デバッグインターフェースがメモリ内容を監視する機能を有するものである形式の調整ユニットにおいて、前記デバッグインターフェースは第1のメモリの第1のメモリセルへの書き込みの第1の時点を検知し、関連する第1の値を前記調整ユニットに送るよう構成されており、前記調整ユニットは送られてきた前記時点に基づいて処理ルーチンを実行させ、該処理ルーチンにより第2の値を求め、前記第1のメモリの第1のメモリセルが前記制御装置によって読み出される前に、上記構成のデバッグインターフェースにより前記第2の値を第2の時点に前記第1のメモリの第1のメモリセルに書き込むよう構成されているものとすることにより解決される。20

#### 【図面の簡単な説明】

#### 【0010】

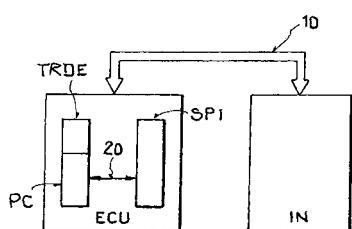

【図1】制御装置に接続された調整ユニットを概略的に示す。

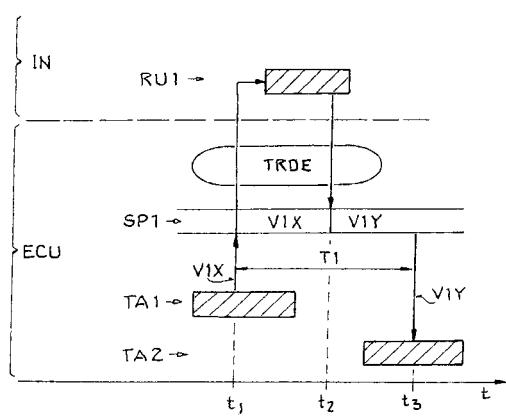

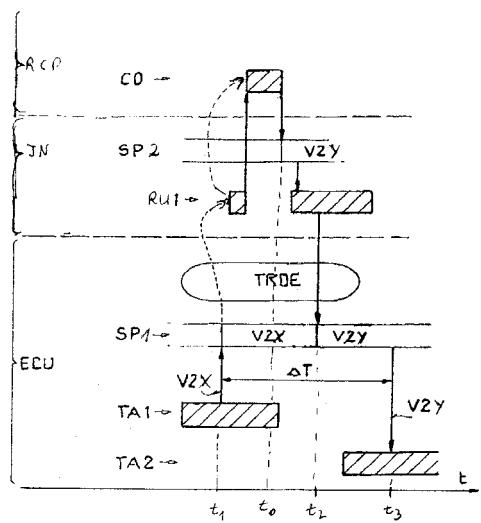

【図2】図1の調整ユニットによる制御装置内でのデータ変化の時間シーケンスを概略的に示す。

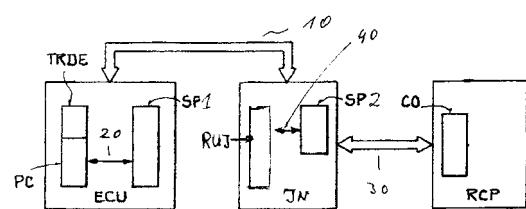

【図3】制御装置に接続された調整ユニットと調整ユニットに接続された遠隔制御ユニットを概略的に示す。

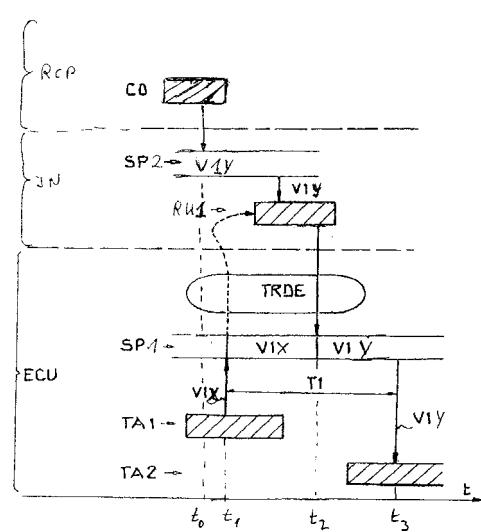

【図4】第1の値が読み出される前の遠隔制御装置による第2の値の準備と、データ変化の時間シーケンスを概略的に示す。30

【図5】調整ユニットによるデータ変化の時間シーケンスを概略的に示す。

#### 【発明を実施するための形態】

#### 【0011】

制御装置を調整ユニットにより調整する方法であり、制御装置は少なくとも1つのマイクロコントローラ、多数のメモリセルを有する少なくとも1つのメモリ、および少なくとも1つのデバッグインターフェースを含んでおり、デバッグインターフェースはメモリ内容を監視する機能を有しており、制御装置が第1の値を第1のメモリの第1のメモリセルに書き込む第1の時点がデバッグインターフェースにより検知され、処理ルーチンのトリガ時点が第1の時点にデバッグインターフェースから調整ユニットへ送られた情報を用いて調整ユニットにより求められ、第1のメモリの第1のメモリセルが第3の時点に制御装置によって読み出される前に、調整ユニットが処理ルーチンを用いて第2の時点に第2の値をデバッグインターフェースを介して第1のメモリの第1のメモリセルに書き込む。40

#### 【0012】

本発明の第2の側面によれば、制御装置を調整するよう構成された調整ユニットが提供される。ここで、制御装置は少なくとも1つのマイクロコントローラ、多数のメモリセルを有する少なくとも1つのメモリ、および少なくとも1つのデバッグインターフェースを有している。さらに、デバッグインターフェースはメモリ内容を監視する監視機能を有し、第1のメモリの第1のメモリセルへの第1の書き込み時点を検知し、相応する第1の値を調整ユニットに送るよう構成されており、調整ユニットは、送られてきた時点に基づいて処理50

ルーチンを開始させ、処理ルーチンを用いて第2の値を求め、第1のメモリセルが制御装置によって読み出される前に、上記構成のデバッグインターフェースを用いて第2の値を第2の時点において第1のメモリの第1のメモリセルに書き込むように構成されている。

#### 【0013】

この方法の利点は、制御装置のメモリセルへの値の書き込みがサービス呼び出しとは無関係に任意のプログラムポイントおよび任意の時点において調整ユニットによって検知され、その後この値がその時その時のメモリセルにおいて変更されうることにある。このため、本発明による方法は非常に融通性に富んでおり、とりわけ制御装置プログラムのソースコードを一々知らなくても、様々なメーカーの多くの制御装置に適用できる。さらに、制御装置プログラムを適合させる必要もない。制御装置向けのプログラムでは、サービス呼び出しは相応するプログラム断片と必ずしも結び付けられていなくてもよいため、プログラム処理とメモリ消費の不利な調整が回避される。10

#### 【0014】

この方法の別の実施形態では、第2の時点がそのつど第3の時点より前にあるか、ないしは、あったかが調整ユニットにより検査ないし監視され、検査結果に応じて所定の値が出力される。このため、調整の成功、すなわち、メモリセルの適時の上書きを検知し、ユーザに通知することが可能である。有利には、上述の監視および出力は調整ユニットに実装されているサービスプログラムによって実行される。20

#### 【0015】

別の有利な実施形態では、制御装置による第1のメモリの第1のメモリセルに第1の値を書き込みと第1のメモリの第1のメモリセルの読み出しへに要する時間が求められる。別の実施形態によれば、特定のメモリセルへの書き込み／読み出しがアクセスの持続時間が制御装置のプログラムコードの分析によって求められる。このために、例えばマイクロコントローラのトラッキングにより、制御装置で実行されるプログラムコードが分析される。有利には、プログラムコードの分析は制御装置を使用せずに外部機器で、とりわけPCで実行される。関連する時点は、有利にはその時その時の命令セット、いわゆる「命令コード」、の逐次評価によって行われる。個々の書き込み／読み出しがアクセスの間の最小持続時間はプロセッサのタイプと使用されるクロック周波数とに基づいて決まる各命令の典型的な実行時間から抽出される。この実施形態の利点は、制御装置プログラムの実行とは関係なく、例えば車両内に取り付けた状態で生じるような実際の条件の下で、それもフォアグラウンドで、持続時間を求めることができることにある。これとともに、発生するすべての書き込み／読み出しがアクセスの持続時間が調べられ、調整ユニットの実行時間がその時その時の値を調整ユニットから該当するメモリセルに上書きするのにどの程度十分であるかが検査されるので、上書きエラーによる誤動作の危険性が低減される。制御装置が組み込まれていない場合には、検査は仮想的なテスト環境ないしシミュレータを用いても可能である。つまり、制御装置のインターフェースに実際の条件と同等のデータが供給される。30

#### 【0016】

別の実施形態によれば、制御装置が必要とする持続時間は調整ユニットがデバッグインターフェースの監視機能を用いて求める。別の実施形態では、時点は準「オンライン」で、つまり、制御装置の稼働中に求められ、それ以降は、制御装置の動作中でも、調整ユニットによって第1のメモリのどのメモリセルに第2の値が書き込まれるかがリアルタイムで決定される。40

#### 【0017】

別の実施形態によれば、制御装置内で発生する書き込み／読み出しがアクセスの時間間隔の大きさに基づいて、調整ユニットがサービスプログラムを用いて制御装置の調整可能なメモリセルを出力する。これにより、ユーザは狙い撃ちで特定のメモリセルを、つまり、調整に適したメモリセルを、有利にはフォアグラウンドで決定する手段を得ることができる。

#### 【0018】

好みの実施形態では、第2の値は第4の時点に第2のメモリの第1のメモリセルに書50

き込まれ、調整ユニットが処理ルーチンを用いて第2のメモリの第1のメモリセルから読み出す。出願人の行った試験では、第2のメモリは多数のメモリセルを有していることが有利であり、制御装置にも調整ユニットにも配置しうることが示された。さらに、特に好ましい実施形態では、第2のメモリの第1のメモリセルは遠隔制御装置によって書き込まれる。第1のメモリに第2の値が書き込まれてからでなければ、第1のメモリの第1のメモリセルが第3の時点に制御装置によって読み出されないように、第4の時点が第2の時点に先行していることが好ましい。これにより、第2の値は、調整ルーチンによって第1のメモリの第1のメモリセルに書き込まれる時点より前に、調整ルーチンで使用可能となる。

## 【0019】

10

出願人が行った試験では、特に時間が決定的重要性をもつ制御装置内の処理タスクの場合、第1の時点よりも時間的に前にある第4の時点に、第2の値を第2のメモリの第1のメモリセルに用意するのが好ましいことが示された。これにより、命令を処理する際の遅延が回避される。というのも、第2の値は、第1のメモリの第1のメモリセルに初めて書き込まれる前にすでに、後に続く第1の値の上書きの用意ができているからである。

## 【0020】

1つの代替実施形態によれば、第2の値は遠隔制御装置によって、つまり、いわゆるRCP装置によって第2のメモリの第1のメモリセルに書き込まれる。とりわけ、調整ユニットの複雑さを低く抑えるべき場合には、コストのかかる計算や入力を非常に計算能力の高い遠隔制御装置によって行うと有利である。この場合、第2のメモリは調整ユニット内にも遠隔制御装置内にも形成してよい。第1の代替実施形態では、第2のメモリは好ましくは先覚制御装置によって書き込まれる。

20

## 【0021】

以下では、概略的な図面を参照しながら、本発明による方法を実施例に基づいて説明する。図中、同じ機能には同じ参照記号が付してある。

## 【実施例】

## 【0022】

図1によれば、調整ユニットINはデータ線10により制御装置ECUと接続されている。さらに、制御装置ECUは監視機能(トレース機能)を有するデバッグインターフェースTRDEを備えたマイクロコントローラPCを有している。マイクロコントローラPCとデバッグインターフェースTRDEはデータ線20によりメモリSP1と接続されている。なお、デバッグインターフェースは有利にはマイクロコントローラの一体部分として実施されている。上記メモリは有利にはマイクロコントローラの構成部分として実現されている。調整ユニットINの内部には、一般に、様々なサービスプログラムと、とりわけ処理ルーチンが実現されている(図示なし)。

30

## 【0023】

図2には、調整ユニットINと図1の制御装置ECUのデバッグインターフェースTRDEとの協働によるメモリセルの調整の詳細な時間シーケンスが示されている。このために、図示されたステップの時間シーケンスが時間軸t上にプロットされている。制御装置ECUの内部では、制御装置プログラムによって第1のタスクTA1が実行され、第1のタスクTA1の処理中、第1の時点 $t_1$ に第1の値V1XがメモリSP1の第1のメモリセルに書き込まれる。第1の時点 $t_1$ における第1の値V1Xの書き込みは第1の値V1XとともにデバッグインターフェースTRDEによって調整ユニットINに通知される。調整ユニットINでは、通知された情報がトリガ時点を決定し、このトリガ時点に基づいて処理ルーチンRU1が開始され、処理される。調整ユニットINは、第2のタスクTA2の処理中に制御装置ECUによって第1のメモリセルが第3の時点 $t_3$ に読み出される前に、処理ルーチンRU1とデバッグインターフェースTRDEを用いて第2の時点 $t_2$ に第2の値V1Yを第1のメモリSP1のメモリセルに書き込む。

40

## 【0024】

図3では、図1から知られている調整ユニットINに加えて、遠隔制御装置RCPが形

50

成されている。以下では、図1に関連して説明した実施形態との相違点のみを挙げる。遠隔制御装置RCPはデータ接続30によって調整ユニットINと接続されている。調整ユニットINでは、処理ルーチンRU1がボックスで示されている。処理ルーチンRU1は複数のメモリセルを有する第2のメモリSP2と線路40によって接続されている。さらに、遠隔制御装置RCPが同様にボックスとして形成された制御ルーチンCOを有している。

#### 【0025】

第2の値V1Yは制御ルーチンCOと調整ユニットINとによって第2のメモリSP2の第1のメモリに書き込まれる。第2の値V1Yは続いて処理ルーチンRU1によって線路40を介して第2のメモリSP2から消去され、データ線10を介して第1のメモリSP1に格納される。10

#### 【0026】

図4には、メモリ領域へのアクセスの考えられる時間シーケンスの第1の実施形態が示されている。以下では、図2および図3に関連して説明した実施形態との相違点のみを説明する。遠隔制御装置RCPの内部では、制御ルーチンCOにより第4の時点t0において第2の値V1Yが第2のメモリSP2に格納される。この場合、第4の時点t0は第1の時点に先行している。このシーケンスの利点は、第1のメモリSP1に対する第2の値V1Yの書込み／読み出しが非常に高速な場合でも、第1のメモリへの書込みアクセスがデバッグインターフェースTRDEによって検知される時点t1よりも前に、第2の値V1Yを第1のメモリSP1に書き込む準備ができるという点にある。それゆえ、制御装置が処理すべきタスクTA1およびTA2を処理する際に遅延が生じない。20

#### 【0027】

図5には、メモリ領域へのアクセスの考えられる時間シーケンスの別の実施形態が示されている。以下では、図4に関連して説明した実施形態との相違点のみを挙げる。遠隔制御装置RCPの内部では、制御ルーチンCOにより第4の時点t0において第2の値V1Yが第2のメモリSP2に格納される。この場合、第4の時点t0は第1の時点t1よりも後であるが、時点t2よりは前である。この実施形態の利点は、第2の値V1Yが第1の値V1Xに依存している場合に、有利には遠隔制御ユニットRCPで計算を行えるよう、第1の値V1Xが遠隔制御ユニットRCPの処理ルーチンRU1により供給されるという点にある。とりわけ、遠隔制御装置RCPが調整ユニットINおよび／または制御装置ECUよりも遙かに高い計算能力を持っていれば、遠隔制御装置RCPは複雑なアルゴリズムも処理することができ、調整ユニットINでまたは制御装置ECUによって計算した場合よりも速く第2の値V1Yを計算する。処理ルーチンRU1の実行は、処理ルーチンRU1による制御ルーチンCOのトリガと第2の値V1Yの供給との間の時間に中断されるか、または遅くとも第2の値V1Yが第1のメモリSP1に格納される時点t2まで状態BYで進行する。30

#### 【符号の説明】

#### 【0028】

10 データ線

20 データ線

30 データ接続

40 線路

CO 制御ルーチン

ECU 制御装置

IN 調整ユニット

PC マイクロコントローラ

RCP 遠隔制御装置

RU1 処理ルーチン

SP1 第1のメモリ

SP2 第2のメモリ

40

50

T 1 第1のメモリセルの書き込みと読み出しに必要な時間

TA 1 第1のタスク

TA 2 第2のタスク

TRDE デバッグインターフェース

V1X 第1の値

V1Y 第2の値

【図1】

【図3】

【図2】

【図4】

【図5】

---

フロントページの続き

(74)代理人 100061815

弁理士 矢野 敏雄

(74)代理人 100099483

弁理士 久野 孜也

(74)代理人 100112793

弁理士 高橋 佳大

(74)代理人 100128679

弁理士 星 公弘

(74)代理人 100135633

弁理士 二宮 浩康

(74)代理人 100114890

弁理士 アインゼル・フェリックス=ラインハルト

(74)復代理人 100165940

弁理士 大谷 令子

(72)発明者 マルク ドレスラー

ドイツ連邦共和国 ホルン バーンホフシュトラーセ 27

(72)発明者 トルステン フーフナーゲル

ドイツ連邦共和国 ザルツコッテン マリエンシュトラーセ 44

(72)発明者 パスティアン ケラース

ドイツ連邦共和国 パーダーボルン ローベルト - コッホ - シュトラーセ 164

(72)発明者 ダニエル ホフマン

ドイツ連邦共和国 パーダーボルン ローベルト - コッホ - シュトラーセ 4ア-

審査官 相崎 裕恒

(56)参考文献 特開平11-119989(JP,A)

特開平06-284161(JP,A)

特開平08-185335(JP,A)

特開平10-214201(JP,A)

特開2000-227862(JP,A)

特開2008-152544(JP,A)

特開2007-004793(JP,A)

(58)調査した分野(Int.Cl., DB名)

F 02 D 41/00 - 45/00

G 06 F 11/22 - 11/34