(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년10월27일

(11) 등록번호 10-1670148

(24) 등록일자 2016년10월21일

- (51) 국제특허분류(Int. Cl.)

*H01L 29/24* (2006.01) *C01G 30/00* (2006.01)

*G02F 1/1365* (2006.01) *G02F 1/1368* (2006.01)

*H01L 21/336* (2006.01) *H01L 21/368* (2006.01)

*H01L 29/786* (2006.01) *H01L 29/861* (2006.01)

*H01L 29/868* (2006.01) *H01L 51/50* (2006.01)

*H05B 33/02* (2006.01)

- (21) 출원번호 10-2014-7017429

- (22) 출원일자(국제) 2012년11월28일

심사청구일자 2014년06월25일

- (85) 번역문제출일자 2014년06월25일

- (65) 공개번호 10-2014-0095106

- (43) 공개일자 2014년07월31일

- (86) 국제출원번호 PCT/JP2012/081429

- (87) 국제공개번호 WO 2013/081169

국제공개일자 2013년06월06일

- (30) 우선권주장

JP-P-2011-261845 2011년11월30일 일본(JP)

JP-P-2012-058668 2012년03월15일 일본(JP)

- (56) 선행기술조사문헌

US20110253997 A1\*

US07521716 B2\*

- \*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 11 항

심사관 : 김종호

(54) 발명의 명칭 **p** 형 산화물, **p** 형 산화물 제조용 조성물, **p** 형 산화물의 제조 방법, 반도체 소자, 표시 소자, 영상 표시 장치, 및 시스템

**(57) 요 약**

본 발명에서는, 산화물을 포함하고 무정형인 **p** 형 산화물로서, 산화물은 Cu, 및 p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M을 포함하고, 여기서 평형 상태는 최외각의 **p** 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 있는 상태인 것인 **p** 형 산화물이 제공된다.

**대 표 도** - 도14

(72) 발명자

**나카무라 유키**

일본 143-8555 도쿄도 오다꾸 나가마고메 1-3-6 가

부시키가이샤 리코 나이

**다카다 미키코**

일본 143-8555 도쿄도 오다꾸 나가마고메 1-3-6 가

부시키가이샤 리코 나이

**마츠모토 신지**

일본 143-8555 도쿄도 오다꾸 나가마고메 1-3-6 가

부시키가이샤 리코 나이

---

**소네 유지**

일본 143-8555 도쿄도 오다꾸 나가마고메 1-3-6 가

부시키가이샤 리코 나이

**사오토메 료이치**

일본 143-8555 도쿄도 오다꾸 나가마고메 1-3-6 가

부시키가이샤 리코 나이

## 명세서

### 청구범위

#### 청구항 1

산화물을 포함하고, 0가(zero-valent) 구리 금속 또는 0가 구리 합금을 포함하지 않는, 무정형 p형 산화물 화합물(oxide compound)로서,

산화물은

Cu, 및

p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M으로서, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M

으로 이루어지는 것인 p형 산화물 화합물.

#### 청구항 2

제1항에 있어서, 원소 M은 Sb, 또는 Sn, 또는 이들 둘 다를 포함하는 것인 p형 산화물 화합물.

#### 청구항 3

Cu, 및

p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M으로서, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M

으로 이루어지는 산화물을 포함하는 무정형 p형 산화물 화합물의 제조에 사용되는 p형 산화물 화합물 제조용 조성물로서,

용매,

Cu 함유 화합물, 및

원소 M 함유 화합물로서, 원소 M은 p 블록 원소로부터 선택되고, 이온으로 존재할 때 평형 상태로 존재할 수 있으며, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M 함유 화합물

을 포함하는 p형 산화물 화합물 제조용 조성물.

#### 청구항 4

Cu, 및

p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M으로서, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M

으로 이루어지는 산화물을 포함하는 무정형 p형 산화물 화합물을 제조하는 방법으로서,

조성물을 지지체 상에 도포하는 단계, 및

상기 도포 후 열처리를 수행하는 단계

를 포함하고, 여기서 조성물은

용매,

Cu 함유 화합물, 및

원소 M 함유 화합물로서, 원소 M은 p 블록 원소로부터 선택되고, 이온으로 존재할 때 평형 상태로 존재할 수 있으며, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M 함유 화합물

을 포함하는 것인 방법.

#### 청구항 5

활성층을 포함하는 반도체 소자로서,

활성층은 제1항 또는 제2항에 따른 p형 산화물 화합물을 포함하는 것인 반도체 소자.

#### 청구항 6

제5항에 있어서, 상기 반도체 소자는 다이오드이고, 여기서 다이오드는

제1 전극,

제2 전극, 및

제1 전극과 제2 전극 사이에 형성된 활성층

을 포함하는 것인 반도체 소자.

#### 청구항 7

제5항에 있어서, 상기 반도체 소자는 전계 효과 트랜지스터이고, 여기서 전계 효과 트랜지스터는

게이트 전압을 인가하도록 구성된 게이트 전극,

둘 다 전류를 추출하도록 구성된 소스 전극 및 드레인 전극,

소스 전극과 드레인 전극 사이에 형성된 활성층, 및

게이트 전극과 활성층 사이에 형성된 게이트 절연층

을 포함하는 것인 반도체 소자.

#### 청구항 8

광 출력이 구동 신호에 상응하여 제어되는 광 제어 소자, 및

제5항에 따른 반도체 소자를 포함하고 광 제어 소자를 구동하도록 구성된 구동 회로

를 포함하는 표시 소자.

#### 청구항 9

제8항에 있어서, 광 제어 소자는 유기 전계발광 소자, 전기변색(electrochromic) 소자, 액정 소자, 전기영동 소자 또는 전기습윤(electrowetting) 소자를 포함하는 것인 표시 소자.

#### 청구항 10

영상 데이터에 상응하는 영상을 표시하는 영상 표시 장치로서,

매트릭스 중에 정렬되어 있는, 각각 제8항에 따른 복수의 표시 소자,

각각의 표시 소자 내의 각각의 전계 효과 트랜지스터에 게이트 전압 및 신호 전압을 별도로 인가하도록 구성된 복수의 라인, 및

영상 데이터에 상응하는, 라인을 통하여 각각의 전계 효과 트랜지스터의 게이트 전압 및 신호 전압을 개별적으로 제어하도록 구성된 표시 제어 장치

를 포함하는 영상 표시 장치.

## 청구항 11

제10항에 따른 영상 표시 장치, 및

표시될 영상 정보를 기반으로 하는 영상 데이터를 형성하고 영상 데이터를 영상 표시 장치에 출력하도록 구성된 영상 데이터 형성 장치

를 포함하는 시스템.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 p형 산화물, 이의 제조용의 조성물, 이의 제조 방법, 반도체 소자, 표시 소자, 영상 표시 장치, 및 시스템에 관한 것이다.

### 배경 기술

[0002]

무정형 상태에서 a-Si 이상의 이동도를 나타내는 InGaZnO<sub>4</sub>(a-IGZO) 박막 트랜지스터(thin film transistor; TFT)의 발표 아래로, 전 세계에서 실용화를 위한 산화물 반도체의 연구 개발이 정력적으로 행해졌다. 그러나, 이들 산화물 반도체 재료 대부분은 전자를 캐리어로 사용하는 n형 산화물 반도체이다.

[0003]

n형 산화물 반도체에 비견되는 p형 산화물 반도체가 실제 이용될 수 있다면, 이들 p형 산화물 반도체 및 n형 산화물 반도체는 조합되어 p-n 접합을 형성함으로써 다이오드, 광 센서, 태양 전지, LED, 또는 바이폴라 트랜지스터(bipolar transistor)를 실현시킨다. 산화물 반도체는 광대역 갭(wide-band gap)을 갖도록 설계될 수 있기 때문에, 이들 소자를 투명하게 하는 것이 또한 가능하다.

[0004]

더 나아가, 활성 매트릭스형(active-matrix) 디스플레이는 도 7에 도시된 바와 같이 2T1C 회로를 기본 구동 회로로 이용한다. 이러한 디스플레이에서, 구동 트랜지스터(전계 효과 트랜지스터(20))가 n형일 경우, 구동 회로는 소위 소스 팔로우어 회로(source follower circuit)이다. 따라서, 유기 EL 소자의 특성의 에이징(aging)(특히, 전압 증가)으로 인하여 구동 트랜지스터의 동작점이 상이한 게이트 전압의 동작점으로 이동함으로써 디스플레이의 반감 수명이 단축된다. 이러한 이유 때문에, 고 이동도의 a-IGZO TFT를 백플레인(backplane)으로 이용한 활성 매트릭스형 유기 EL 디스플레이(AM-OLED)는 아직 실현되지 않았으며, p형 저온 폴리실리콘 박막 트랜지스터(low temperature polysilicon thin film transistor; LTPS-TFT)가 배타적으로 이용되어 왔다. 따라서, 고성능의 p형 산화물 반도체가 필요하다.

[0005]

1950년대 이래로, 1가 구리 산화물인 Cu<sub>2</sub>O의 결정이 p형 전도성을 나타낸다는 것이 공지되었다 (예를 들어, NPL 1 참조). 이 결정은 O-Cu-O의 아령 구조를 기본으로 가지며, Cu의 3d-궤도와 산소의 2p-궤도의 혼성 궤도가 가전자대(valence band) 정상을 구성한다. 정공(hole)은 산소의 화학량론적 과량에 의해 가전자대 내에 도입됨으로써 p형 전도성을 나타내게 된다.

[0006]

기본 유닛(unit)으로서 아령 구조를 갖는 결정의 예는 CuMO<sub>2</sub>(M=Al, Ga, In)로 표시되는 델라포사이트(delafossite) 결정 및 SrCu<sub>2</sub>O<sub>2</sub> 결정을 포함한다. 이들 산화물이 p형 전기 전도성을 나타내기 위해서는 상기 산화물은 높은 결정성을 가질 필요가 있으며, p형 전도성이 보고된 유일한 결정으로는 CuAlO<sub>2</sub>, CuInO<sub>2</sub>, 및 SrCu<sub>2</sub>O<sub>2</sub>가 있다(예를 들어, NPL 2 내지 NPL 4 참조).

[0007]

p형 전도성을 나타내는 것이 어려운 이유들 중 하나는 Cu의 원자가와 산소 함량의 제어가 어렵기 때문이다. 고도 결정성 Cu<sup>+</sup>를 함유하는 산화물의 단일상 막을 형성하려고 시도할 때, 대부분의 경우에 생성된 막은 CuO, SrCuO<sub>2</sub>, 및 SrCu<sub>2</sub>O<sub>3</sub>과 같이 Cu<sup>2+</sup>를 함유하는 결정상이 혼합된 막이다. 이와 같은 막에서는 탁월한 p형 전기 전도성이 획득될 수 없으며, 이의 특성을 제어하는 것이 어렵다. 따라서, 이들 p형 산화물 재료가 반도체 소자의 활성층으로서 사용될 경우, 캐리어 밀도 및 캐리어 이동도와 같은 특성이 최적화될 수 없다.

[0008]

상기 이외에, 1가 Cu 또는 Ag를 함유하는 델라포사이트 산화물이 개시된다(예를 들어, PTL 1 참조). 그러나, 개시된 기술에서, 500°C 이상의 고온의 열처리가 필요하며, 따라서 이것은 실제 사용에 적합하지 않다.

- [0009] 더 나아가, 결정성  $\text{SrCu}_2\text{O}_2$ 의 p형 전기 전도성 박막이 개시된다(예를 들어, PTL 2 참조). 개시된 기술에서, 박막 형성 온도는 비교적 낮으며, 즉,  $300^\circ\text{C}$ 이지만, 충분한 전기 전도도가 획득되지 않았으며, 획득된 최상의 전도도는  $4.8 \times 10^{-2} \text{ Scm}^{-1}$ 이다. 더 나아가, 이의 제어가 또한 불충분하다.

- [0010] 상기에 기술된 바와 같이, 이러한 개시된 기술은 p형 산화물 재료가 실용적인 방법에 의해 제조될 수 없으며 적절하게 제어되고 충분한 전기 전도성을 갖는 p형 산화물이 제공될 수 없다는 문제를 갖는다.

- [0011] 더 나아가, 활성층으로서 1가 Cu 또는 Ag를 함유하는 델라포사이트 결정의 p형 산화물 재료를 사용한 TFG가 개시되어 있다(예를 들어, PTL 3 참조).

- [0012] 그러나, 이 문헌에는 충분한 정보, 예컨대 상기 활성층의 재료의 특성, 이의 형성 방법 및 트랜지스터의 특성이 개시되어 있지 않다.

- [0013] 또한, 활성층으로서  $\text{Cu}_2\text{O}$  결정을 사용한 TFT가 개시되어 있다(예를 들어, NPL 5 및 NPL 6 참조). 그러나, 이들 기술에 따르면, 활성층의 특성이 충분히 제어될 수 없으며, 따라서 TFT의 전계 효과 이동도 및 온오프 비(on-off ratio)가 실제 사용에 적합한 수준에 도달하지 않았다.

- [0014] 상기에 기술된 바와 같이, 이들 개시된 기술은 p형 산화물 재료의 특성, 예컨대 캐리어 밀도를 제어하는 것이 어렵고, 소자에 사용하기에 적합한 특성이 획득될 수 없다는 문제를 갖는다.

- [0015] 지금까지, 실제 사용에서 효과적인 p형 산화물은 아직 발견되지 못하였다.

- [0016] 따라서, n형 산화물의 특성에 비견되는 특성을 갖는 p형 산화물이 현재 필요하다.

## 선행기술문헌

### 특허문헌

- [0017] (특허문헌 0001) PTL 1: 일본 공개 특허 공보(JP-A) 제11-278834호

(특허문헌 0002) PTL 2: 일본 공개 특허 공보 제2000-150861호

(특허문헌 0003) PTL 3: 일본 공개 특허 공보 제2005-183984호

### 비특허문헌

- [0018] (비특허문헌 0001) NPL 1: J. Bloem, Discussion of some optical and electrical properties of  $\text{Cu}_2\text{O}$ , Philips Research Reports, VOL 13, 1958, pp. 167- 193

(비특허문헌 0002) NPL 2: H. Kawazoe and 5 others, P-type electrical conduction in transparent thin films of  $\text{CuAlO}_2$ , Nature, VOL. 389, 1997, pp. 939-942

(비특허문헌 0003) NPL 3: H. Yanagi and 4 others, Bipolarity in electrical conduction of transparent oxide semiconductor  $\text{CuInO}_2$  with delafossite structure, Applied Physics Letters, VOL. 78, 2001, pp. 1583-1585

(비특허문헌 0004) NPL 4: A. Kudo and 3 others,  $\text{SrCu}_2\text{O}_2$ : A p-type conductive oxide with wide band gap, Applied Physics Letters, VOL. 73, 1998, pp. 220-222

(비특허문헌 0005) NPL 5: E. Fortunato and 8 others, Thin-film transistors based on p-type  $\text{Cu}_2\text{O}$  thin films produced at room temperature, Applied Physics Letters, VOL. 96, 2010, pp. 192102

(비특허문헌 0006) NPL 6: K. Matsuzaki and 5 others, Epitaxial growth of high mobility  $\text{Cu}_2\text{O}$  thin films and application to p-channel thin film transistor, Applied Physics Letters, VOL. 93, 2008, pp. 202107

## 발명의 내용

## 해결하려는 과제

[0019]

본 발명은 종래 기술의 전술한 다양한 문제를 제공하여 하기 목적을 달성하는 것을 목표로 한다. 구체적으로, 본 발명의 목적은 탁월한 특성, 즉, 충분한 전기 전도성을 갖고, 비교적 저온인 실용적인 조건 하에서 제조될 수 있고, 제형비의 조정에 의해 전기 전도성을 제어할 수 있는 신규한 p형 산화물을 제공하는 것이다.

## 과제의 해결 수단

[0020]

전술한 문제를 해결하는 수단은 하기와 같다:

[0021]

산화물을 포함하고 무정형인 p형 산화물로서, 산화물은

[0022]

Cu, 및

[0023]

p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M으로서, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M

[0024]

을 포함하는 것인 p형 산화물.

## 발명의 효과

[0025]

본 발명은 본 기술 분야의 다양한 문제를 해결할 수 있으며, 탁월한 특성, 즉, 충분한 전기 전도성을 갖고, 비교적 저온인 실용적인 조건 하에서 제조될 수 있고, 제형비의 조정에 의해 전기 전도성을 제어할 수 있는 신규한 p형 산화물을 제공할 수 있다.

## 도면의 간단한 설명

[0026]

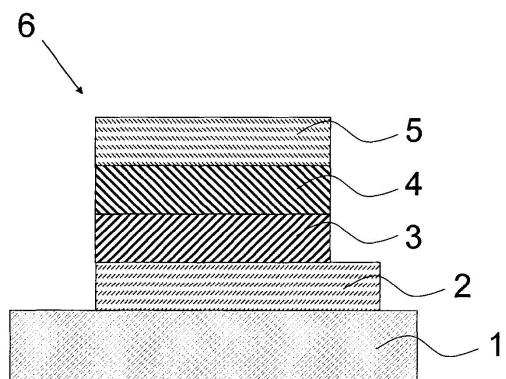

도 1은 다이오드의 일례를 도시하는 개략적 구조도이다.

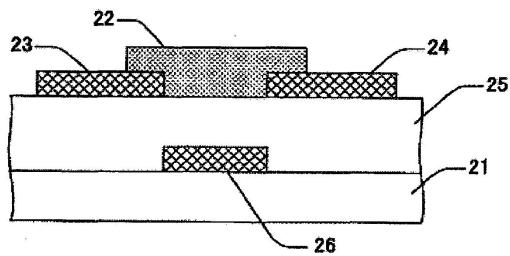

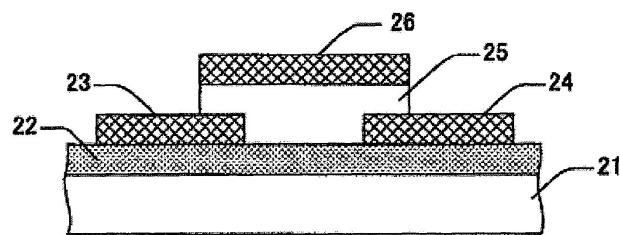

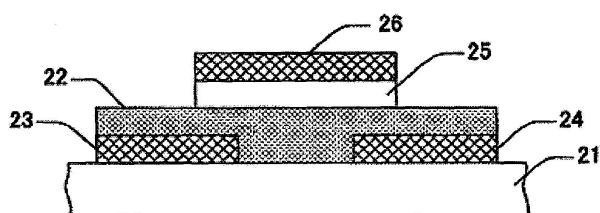

도 2는 상부 콘택, 하부 게이트형 전계 효과 트랜지스터의 일례를 도시하는 개략적 구조도이다.

도 3은 하부 콘택, 하부 게이트형 전계 효과 트랜지스터의 일례를 도시하는 개략적 구조도이다.

도 4는 상부 콘택, 상부 게이트형 전계 효과 트랜지스터의 일례를 도시하는 개략적 구조도이다.

도 5는 하부 콘택, 상부 게이트형 전계 효과 트랜지스터의 일례를 도시하는 개략적 구조도이다.

도 6은 영상 표시 장치의 일례를 설명하는 다이어그램(diagram)이다.

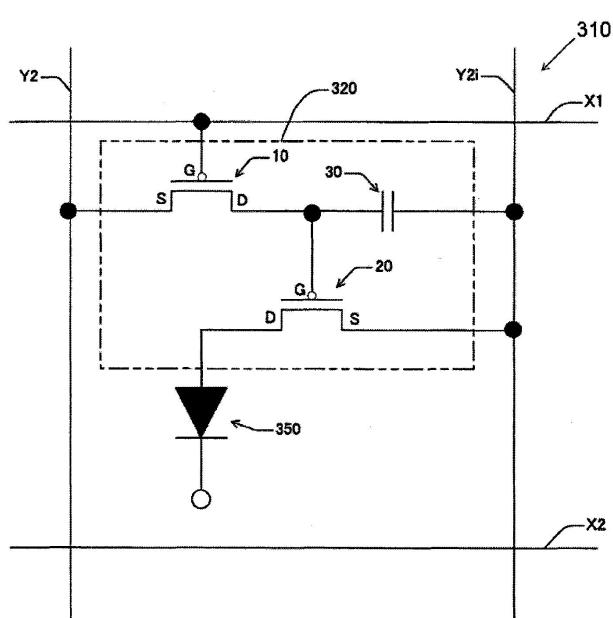

도 7은 본 발명의 표시 소자의 일례를 설명하는 다이어그램이다.

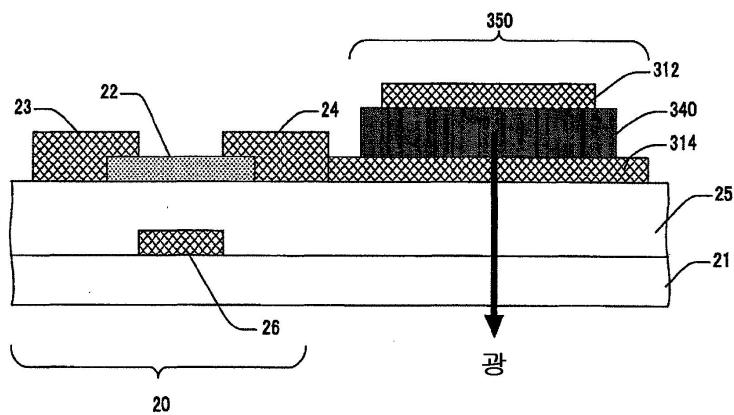

도 8은 표시 소자에 있어서 유기 EL 소자와 전계 효과 트랜지스터 사이의 물리적 관계의 일례를 도시하는 개략적 구조도이다.

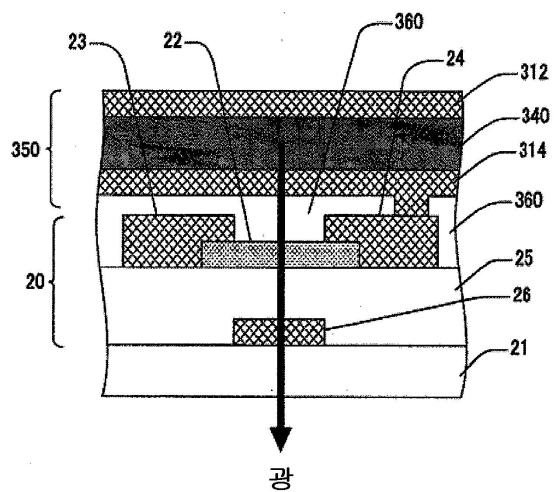

도 9는 표시 소자에 있어서 유기 EL 소자와 전계 효과 트랜지스터 사이의 물리적 관계의 또 다른 예를 도시하는 개략적 구조도이다.

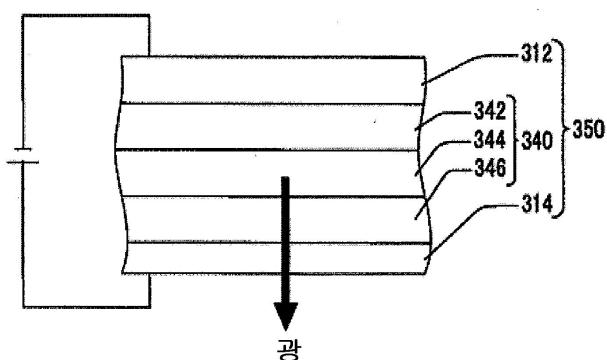

도 10은 유기 EL 소자의 일례를 도시하는 개략적 구조도이다.

도 11은 표시 제어 장치의 일례를 설명하는 다이어그램이다.

도 12는 액정 디스플레이의 일례를 설명하는 다이어그램이다.

도 13은 도 12의 표시 소자를 설명하는 다이어그램이다.

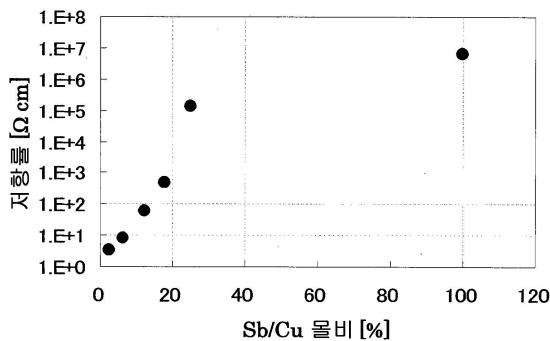

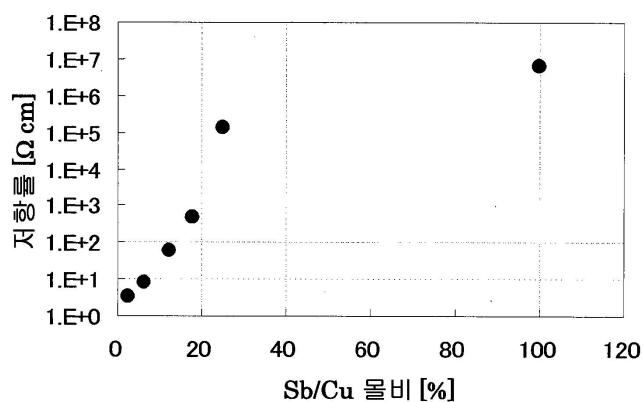

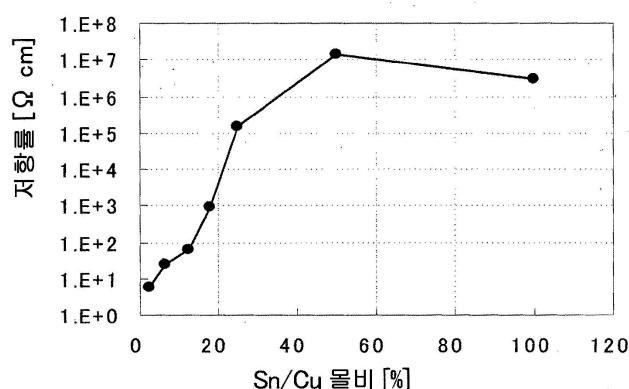

도 14는 실시예 1 내지 실시예 6의 p형 산화물의 체적 저항률을 도시하는 다이어그램이다.

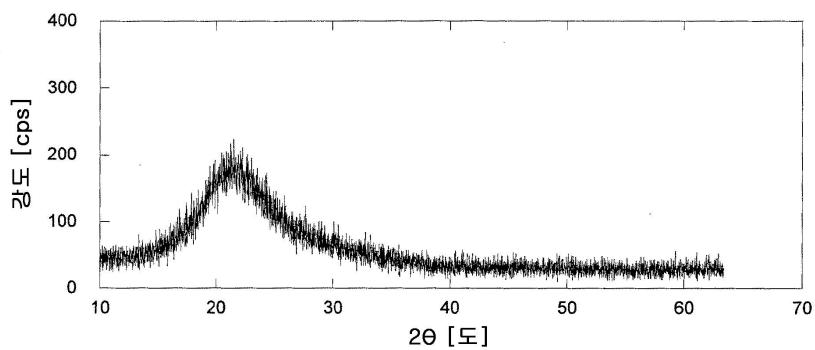

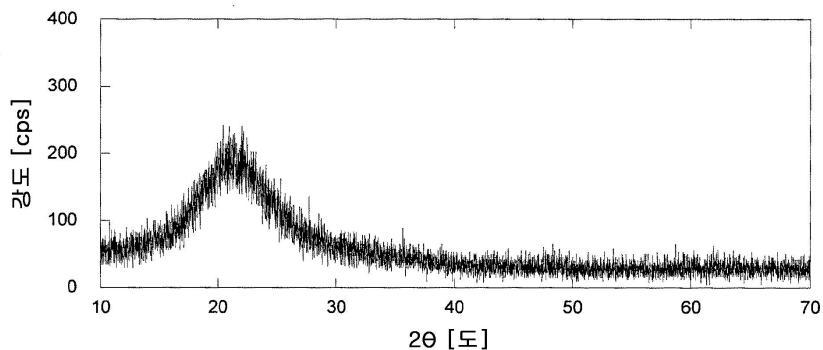

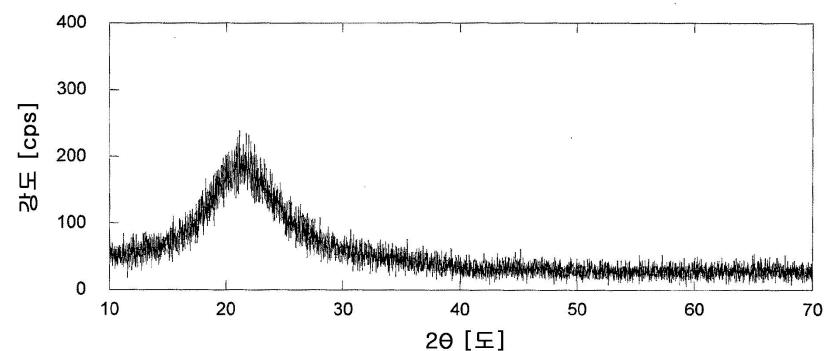

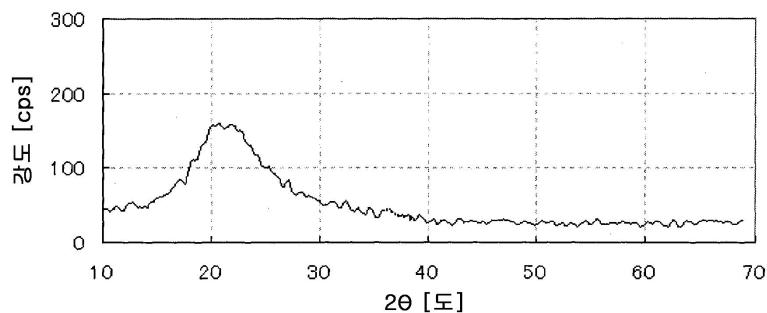

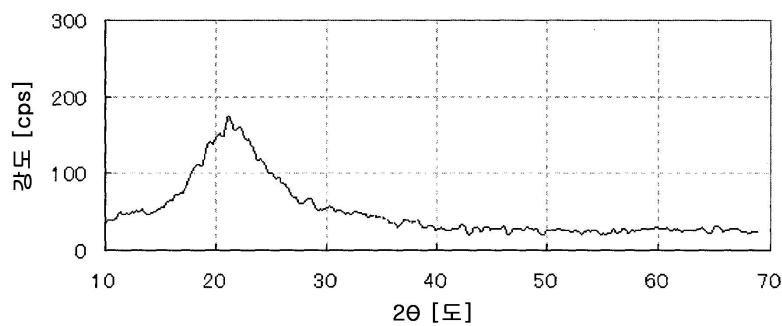

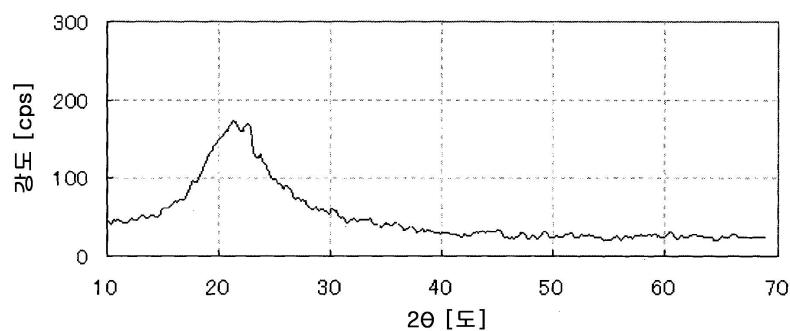

도 15는 실시예 1의 p형 산화물의 X선 회절 측정 결과를 도시한다.

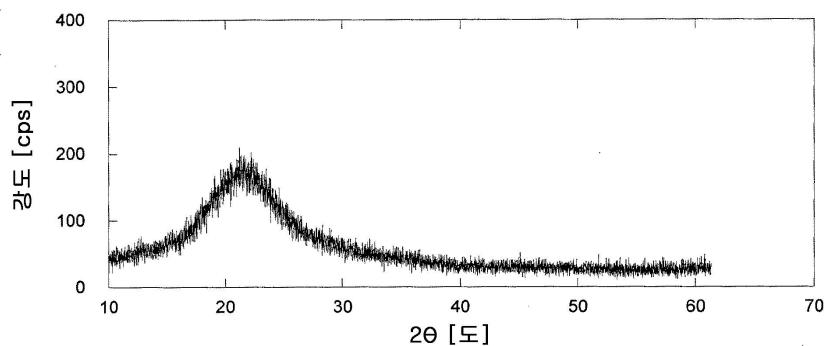

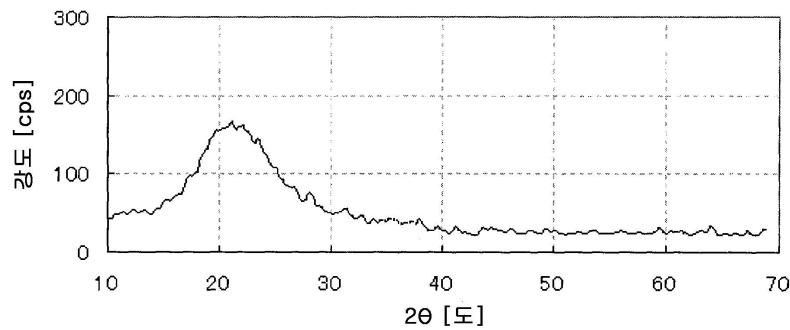

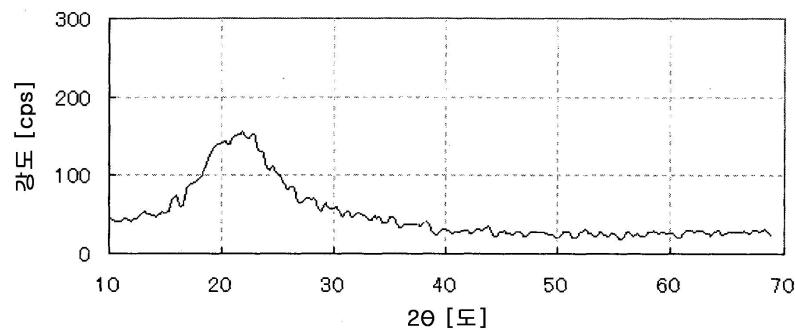

도 16은 실시예 2의 p형 산화물의 X선 회절 측정 결과를 도시한다.

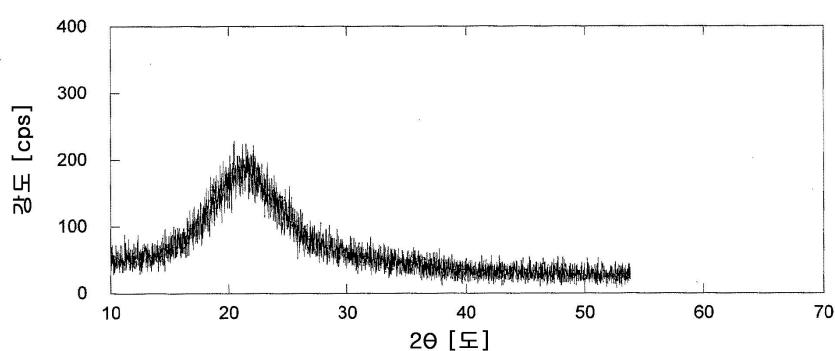

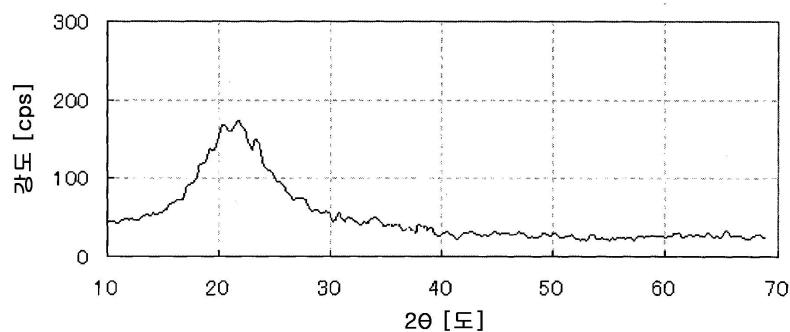

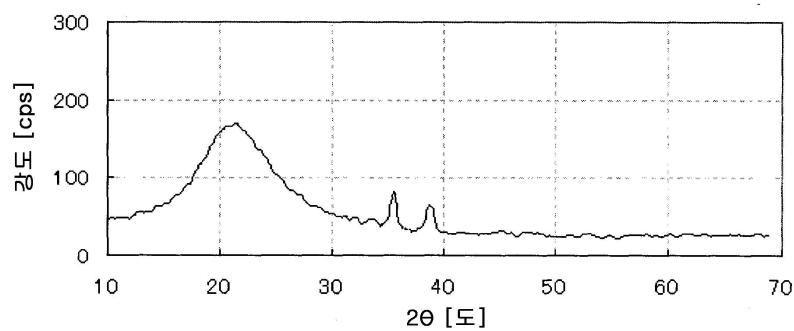

도 17은 실시예 3의 p형 산화물의 X선 회절 측정 결과를 도시한다.

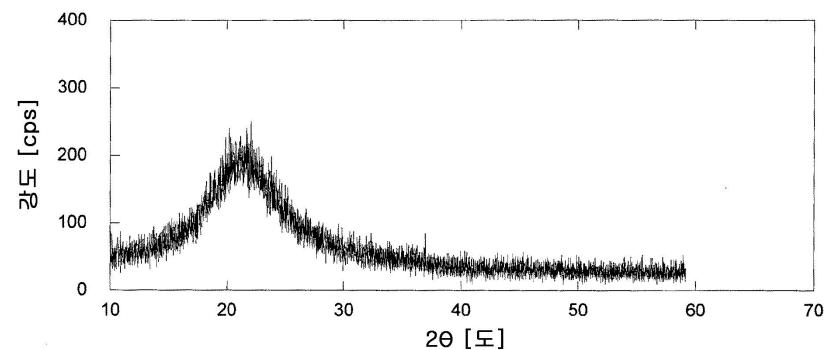

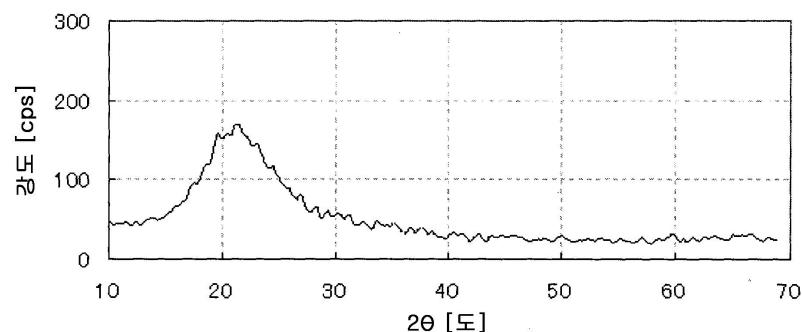

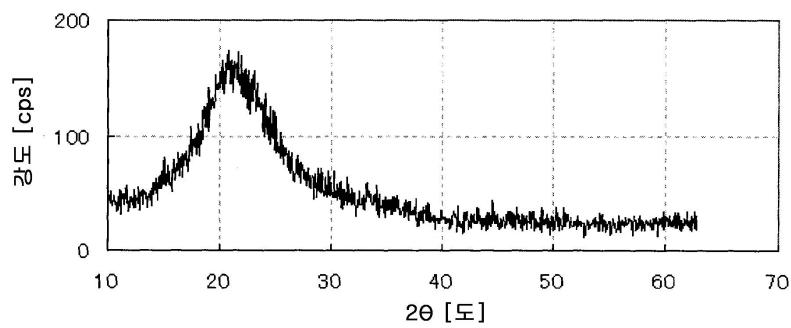

도 18은 실시예 4의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 19는 실시예 5의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 20은 실시예 6의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 21은 비교예 1의 Cu-Sb 산화물의 X선 회절 측정 결과를 도시한다.

도 22는 비교예 2의 Cu-Sb 산화물의 X선 회절 측정 결과를 도시한다.

도 23은 실시예 7의 p형 산화물의 X선 회절 측정 결과를 도시한다.

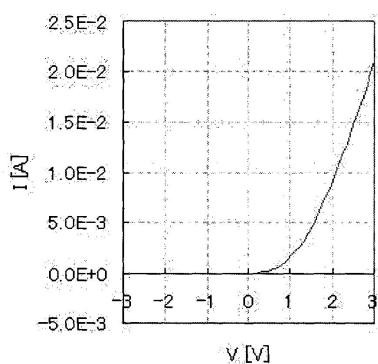

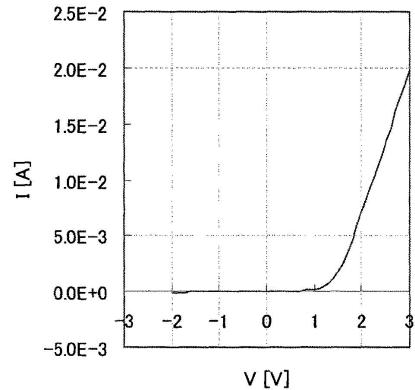

도 24는 실시예 8에서 제조된 다이오드의 전류-전압(I-V) 특성을 도시하는 다이어그램이다.

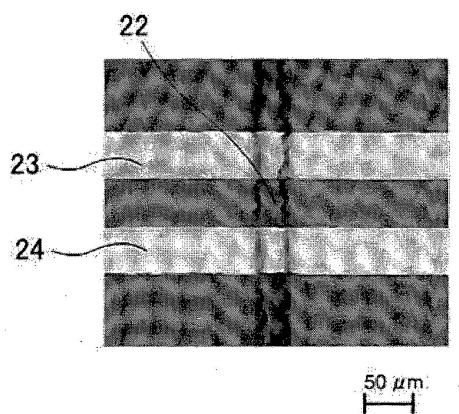

도 25는 실시예 10에서 제조된 전계 효과 트랜지스터의 채널의 현미경 사진이다.

도 26은 실시예 11 내지 실시예 17의 p형 산화물의 체적 저항률을 도시하는 다이어그램이다.

도 27은 실시예 11의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 28은 실시예 12의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 29는 실시예 13의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 30은 실시예 14의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 31은 실시예 15의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 32는 실시예 16의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 33은 실시예 17의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 34는 비교예 3의 Cu-Sb 산화물의 X선 회절 측정 결과를 도시한다.

도 35는 실시예 18의 p형 산화물의 X선 회절 측정 결과를 도시한다.

도 36은 실시예 19에서 제조된 다이오드의 전류-전압(I-V) 특성을 도시하는 다이어그램이다.

도 37은 실시예 21에서 제조된 전계 효과 트랜지스터의 채널의 현미경 사진이다.

### 발명을 실시하기 위한 구체적인 내용

[0027]

#### 실시형태의 설명

[0028]

(p형 산화물, p형 산화물 제조용 조성물, 및 p형 산화물의 제조 방법)

[0029]

<p형 산화물>

[0030]

본 발명의 p형 산화물은 산화물로 본질적으로 이루어지고 무정형인 p형 산화물로서, 산화물은 Cu, 및 p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M으로서, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M 을 포함한다.

[0031]

하기의 설명에서, p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M으로서, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M은 단지 "원소 M"으로 지칭될 수 있다.

[0032]

p형 산화물은 무정형이며, 정공을 캐리어로서 사용하는 p형 전기 전도성을 나타낸다.

[0033]

Cu의 3d-궤도와 O의 2p-궤도의 혼성 궤도로 이루어진 가전자대를 이용하는 1가 구리(또는 은) 산화물에 있어서, 전자 궤도의 이방성이 강하며, 따라서 통상적으로 구리 산화물은 p형을 나타내도록 결정일 필요가 있는 것으로 여겨진다. 이는 중금속의 등방성 s-궤도로 이루어진 전도대를 이용하는 n형 산화물 반도체와는 완전히 다르다. 그러나, 본 발명자는 무정형 상태의 특정한 Cu 산화물이 p형 전도성을 나타낸다는 것을 밝혀냈다.

[0034]

p형 산화물은 무정형이기 때문에, Cu 함유 산화물과 원소 M 함유 산화물의 비는 연속적으로 조정될 수 있다. 상기 산화물의 전기 전도성은 전술한 비에 의해 제어될 수 있으며, 그 결과, 의도된 목적에 적합한 특성의 p형 산화물이 수득될 수 있다.

- [0035] 1가 구리를 함유하는 종래의 결정성 p형 산화물 중 산소의 함량 및 Cu의 원자가의 제어는 어려우며, 따라서 종래의 p형 산화물을 이용한 단일상 막을 형성하는 것은 어렵다. 더 나아가, 의도치 않게 생성된  $Cu^{2+}$ 를 함유하는 상의 존재는 p형 전기 전도성을 방해한다.

- [0036] 본 발명의 p형 산화물은 본질적으로 Cu, 및 원소 M을 함유하는 산화물로 이루어진다. 원소 M은 이온으로서 제시될 때, 최외각의 p 궤도의 모든 전자가 상실된 상태(이 상태는  $M^{x+}$ 로 표시됨) 및 2개의 전자가 방출되고 최외각의 s-궤도 및 p-궤도의 모든 전자가 상실된 상태(이 상태는 원자가가 2만큼 증가함에 의해  $M^{(x+2)+}$ 로 제시됨) 둘 모두가 존재하는 평형 상태일 수 있는 원소이다. 본 발명의 p형 산화물은 본질적으로 Cu 및 원소 M을 함유하는 산화물로 이루어지며,  $M^{x+}$ 가  $M^{(x+2)+}$ 로 변환될 경우 방출되는 전자는  $Cu^{2+}$  내에 포함되어  $Cu^{+}$ 가 되게 한다. 상기 상태의 이러한 변화의 결과로서, Cu는  $Cu^{2+}$ 보다  $Cu^{+}$ 로서 안정하게 존재할 수 있다.

- [0037] 예를 들어, 원소 M의 일례로는 Sn이 있다. Sn은, 최외각의 2개의 5p 전자가 상실된  $Sn^{2+}$ 의 상태로부터, 2개의 5s 전자 및 2개의 5p 전자가 상실된  $Sn^{4+}$ 의 상태로의 전이 동안 2개의 전자를 방출하여서, Cu가  $Cu^{2+}$ 보다  $Cu^{+}$ 로서 안정하게 존재하게 됨에 따라 p형 산화물에 있어서 p형 전기 전도 특성을 향상시키는 효과를 갖는다.

- [0038] 더 나아가, 원소 M의 또 다른 예로는 Sb가 있다. Sb는, 최외각의 3개의 5p 전자가 상실된  $Sb^{3+}$ 의 상태로부터, 2개의 5s 전자 및 3개의 5p 전자가 상실된  $Sb^{5+}$ 의 상태로의 전이 동안 2개의 전자를 방출하여서, Cu가  $Cu^{2+}$ 보다  $Cu^{+}$ 로서 안정하게 존재하게 됨에 따라 p형 산화물에 있어서 p형 전기 전도 특성을 향상시키는 효과를 갖는다.

- [0039] 더 나아가, Cu를 함유하는 종래의 p형 산화물이 결정성이라는 것과 비교해 보면, 본 발명의 p형 산화물은 무정형이고, 따라서 본 발명의 p형 산화물은, 결정성의 변동으로 인한 이의 특성의 변동을 일으키지 않으면서 균일한 막을 형성할 수 있다는 이점을 갖는다.

- [0040] p형 산화물은 본질적으로 Cu를 함유하는 산화물 및 원소 M을 함유하는 산화물로 이루어진 무정형 산화물이지만, p형 산화물은 반도체 특성에 거의 영향을 주지 않는 미량의 결정성 입자를 함유할 수 있음에 유의한다. 미량의 결정을 함유하는 이러한 p형 산화물은 본 발명의 p형 산화물의 범주 내에 포함된다. 여기서, "미량"은, 예를 들어, 결정 입자의 퍼콜레이션(percolation)이 일어나지 않는 양을 의미하며, 약 15 부피% 이하를 의미한다.

- [0041] p형 산화물의 전기적 특성은 Cu 함유 산화물과 원소 M 함유 산화물의 비에 따른다. p형 산화물은 다양한 반도체 소자에 이용될 수 있지만, 일반적으로, 반도체 소자의 유형 또는 특성에 따라 그 소자 중의 반도체에 요구되는 특성(저항률)은 달라진다. 따라서, 조성(예를 들어, 막 중의 Cu와 원소 M의 몰비의 값)은 의도된 목적에 따라 적절하게 선택될 수 있다.

- [0042] 원소 M은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 p 블록 원소로부터 선택된 원소, 및 이온으로서 존재할 때 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 평형 상태를 취할 수 있는 원소이다. 원소 M의 예는 Sn, Sb, Te, Tl 및 Pb를 포함한다.

- [0043] p형 산화물의 형상은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 막, 및 벌크(입자)를 포함한다.

- [0044] 본 p형 산화물은, pn 접합 다이오드, PIN 광다이오드, 전계 효과 트랜지스터, 발광 소자, 및 광전 변환 소자와 같은 반도체 소자의 p형 활성층으로서 효과적이다.

- [0045] p형 산화물의 제조 방법은 바람직하게는 본 발명의 p형 산화물의 제조 방법이며, 이는 본 발명의 p형 산화물을 제조하기 위한 하기에 기술된 조성물을 이용한다.

- [0046] p형 산화물의 다른 제조 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 스퍼터링(sputtering), 펄스 레이저 증착(pulsed laser deposition; PLD), CVD, 및 ALD를 포함한다.

- [0047] <p형 산화물 제조용 조성물>

- [0048] 본 발명의 p형 산화물 제조용 조성물은 적어도 용매, Cu 함유 화합물, 및 원소 M을 함유하는 화합물(이하, "원소 M 함유 화합물"로 지칭될 수 있음)로서, 원소 M은 p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있으며, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M을 함유하는 화합물을 함유할 수 있다. 본 발명의 p형 산화물

제조용 조성물은 필요할 경우 다른 성분을 추가로 함유할 수 있다.

[0049] p형 산화물 제조용 조성물은 본 발명의 p형 산화물의 제조에 사용되는 조성물이다.

[0050] -용매-

[0051] 용매는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 툴루엔, 자일렌, 2-에틸헥산산, 아세틸 아세톤, 에틸렌 글리콜, 및 2-메톡시 에탄올을 포함한다.

[0052] 더 나아가, 바람직한 특성(예를 들어, 점탄성 및 유전율)을 p형 산화물 제조용 조성물에 부여하기 위하여, 용매, 예컨대 디에틸렌 글리콜 및 디메틸 포름아미드가 사용될 수 있다.

[0053] 이들은 독립적으로, 또는 조합으로 사용될 수 있다.

[0054] p형 산화물 제조용 조성물 중 용매의 양은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

[0055] -Cu 함유 화합물-

[0056] p형 산화물 중 Cu의 원자는 1가이지만, Cu 함유 화합물 중 Cu의 원자는 1가로 한정되지 않는다. Cu 함유 화합물은 의도된 목적에 따라 적절하게 선택될 수 있으며, 이의 예는 유기 구리 카르복실레이트, 유기 구리 착물, 및 무기 구리염을 포함한다. 유기 구리 카르복실레이트의 예는 네오데칸산구리(II)를 포함한다. 유기 구리 착물의 예는 구리(II) 프탈로시아닌, 및 구리(I) 페닐아세틸리드를 포함한다. 무기 구리염의 예는 질산구리(II), 및 아세트산구리(I)를 포함한다.

[0057] 이들 중, p형 산화물 제조용 조성물이 비극성 용매를 이용하여 제조되는 경우에는, 용해성의 관점에서 유기 구리 카르복실레이트가 바람직하며, 네오데칸산구리(II)가 더 바람직하다. 더 나아가, p형 산화물 제조용 조성물이 극성 용매를 이용하여 제조되는 경우, 용해성의 관점에서 무기 구리염이 바람직하며, 질산구리(II)가 더 바람직하다.

[0058] p형 산화물 제조용 조성물 중 Cu 함유 화합물의 양은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

[0059] -원소 M 함유 화합물-

[0060] 원소 M 함유 화합물은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 Sb 함유 화합물 및 Sn 함유 화합물을 포함한다.

[0061] 더 나아가, 원소 M 함유 화합물의 예는 원소 M을 함유하는 유기금속 착물, 원소 M을 함유하는 유기 카르복실산염, 원소 M을 함유하는 금속 알콕시드, 및 원소 M을 함유하는 무기 염을 포함한다.

[0062] --Sb 함유 화합물--

[0063] Sb 함유 화합물은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 Sb를 함유하는 유기 금속 착물, Sb를 함유하는 유기 카르복실산염, Sb를 함유하는 금속 알콕시드, 및 Sb를 함유하는 무기염을 포함한다. Sb를 함유하는 무기염의 예는 염화안티몬을 포함한다.

[0064] 이들 중, p형 산화물 제조용 조성물이 비극성 용매를 이용하여 제조되는 경우, 용해성의 관점에서 트리페닐안티몬이 바람직하다. p형 산화물 제조용 조성물이 극성 용매를 이용하여 제조되는 경우, 용해성의 관점에서 Sb를 함유하는 무기염이 바람직하며, 염화안티몬이 더 바람직하다.

[0065] p형 산화물 제조용 조성물 중 Sb 함유 화합물의 양은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

[0066] --Sn 함유 화합물--

[0067] Sn 함유 화합물은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 Sn을 함유하는 유기 금속 착물, Sn을 함유하는 유기 카르복실산염, Sn을 함유하는 금속 알콕시드, 및 Sn을 함유하는 무기염을 포함한다. Sn을 함유하는 유기 카르복실산염의 예는 주석 2-에틸 헥사노에이트를 포함한다. Sn을 갖는 무기염의 예는 염화주석을 포함한다.

[0068] 이들 중, p형 산화물 제조용 조성물이 비극성 용매를 이용하여 제조되는 경우, 용해성의 관점에서 Sn을 함유하는 유기 카르복실산염이 바람직하며, 주석-2-에틸 헥사노에이트가 더 바람직하다. 더 나아가, p형 산화물 제조

용 조성물이 극성 용매를 이용하여 제조되는 경우, 용해성의 관점에서 Sn을 함유하는 무기염이 바람직하며, 염화주석이 더 바람직하다.

[0069] p형 산화물 제조용 조성물 중 Sn 함유 화합물의 양은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

[0070] 본 발명의 p형 산화물 제조용 조성물은 p형 전기 전도성이 탁월한 p형 산화물의 제조에 사용되는 원료 용액으로 적합하다. p형 산화물 중 Cu의 원자는 1가이지만, p형 산화물 제조용 조성물에 함유되는 Cu 함유 화합물 중 Cu의 원자는 1가로 한정되지 않는다. Cu 함유 화합물 중 Cu의 원자는 바람직하게는 2가이다. 구체적으로, Cu 함유 화합물 중 Cu의 원자가 2개인 경우, 1개의 Cu 원자에 대하여 1개의 산소가 존재하지만, p형 전기 전도성이 기여하는, Cu 및 산소로 형성된 Cu 산화물의 상에서, Cu는 1가이며, 따라서 2개의 Cu 원자에 대하여 1개의 산소 원자가 존재한다. 즉, p형 산화물 제조 과정에서, p형 산화물 제조용 조성물은 Cu와 O 사이의 관계에 있어서 산소 과잉 상태로 존재한다. p형 산화물 제조를 위한 이러한 조성물의 사용에 의해, 생성된 p형 산화물 중 산소 함량은 증가하며, 산소 결핍으로 인한 캐리어 보상이 억제된다. 따라서, 정공 농도를 증가시킴으로써 p형 전기 전도성이 탁월한 p형 산화물을 수득한다.

[0071] 더 나아가, 금속 원소 조성물과 용매의 블렌딩비는 넓은 범위에서 제어될 수 있기 때문에, 본 발명의 p형 산화물 제조용 조성물은 p형 산화물의 하기에 기술된 제조 방법 또는 의도된 용도에 따라 적절하게 조정될 수 있다.

[0072] <p형 산화물의 제조 방법>

[0073] 본 발명의 p형 산화물의 제조 방법은 적어도 코팅 단계 및 열처리 단계를 포함하며, 필요할 경우 다른 단계를 추가로 포함할 수 있다.

[0074] -코팅 단계-

[0075] 코팅 단계는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 조성물을 지지체 상에 도포하는 것을 포함한다.

[0076] 조성물은 본 발명의 p형 산화물 제조용 조성물이다.

[0077] 지지체는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 유리 기판을 포함한다.

[0078] 코팅 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 코팅 방법에 대해서는, 종래의 방법, 예컨대 스판 코팅, 잉크젯 인쇄, 슬릿 코팅, 노즐 인쇄, 그라비어(gravure) 인쇄 및 미세 접촉 인쇄가 이용될 수 있다. 이들 중, 큰 면적 및 균일한 두께를 갖는 막의 간단한 제조가 의도되는 경우, 스판 코팅이 바람직하다.

[0079] 더 나아가, 적절한 인쇄 방법(예를 들어, 잉크젯 인쇄 및 미세 접촉 인쇄) 및 인쇄 조건을 이용함으로써, 조성물은 소정 형상으로 인쇄될 수 있으며, 따라서 더욱 이후의 단계에서 패터닝(patterning)을 수행할 필요가 없다.

[0080] -열처리 단계-

[0081] 열처리 단계는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 열처리 단계는 코팅 단계 후 열처리를 수행하고, p형 산화물 제조용 조성물 중 용매의 건조, Cu 함유 화합물의 분해, 원소 M 함유 화합물(예를 들어, Sb 함유 화합물, 및 Sn 함유 화합물)의 분해, 및 p형 산화물의 생성이 가능한 단계이다.

[0082] 상기 열처리 단계의 과정에서, 용매의 건조(이하, "건조 공정"으로 지칭됨), 및 Cu 함유 화합물의 분해, 원소 M 함유 화합물(예를 들어, Sb 함유 화합물, 및 Sn 함유 화합물)의 분해 및 p형 산화물의 생성(이하, "분해 및 생성 공정"으로 총칭됨)은 바람직하게는 상이한 온도에서 수행된다. 구체적으로, 용매의 건조 후, 온도를 상승시켜서 Cu 함유 화합물의 분해, 원소 M 함유 화합물(예를 들어, Sb 함유 화합물, 및 Sn 함유 화합물)의 분해 및 p형 산화물의 생성을 수행하는 것이 바람직하다.

[0083] 건조 공정의 온도는 어떠한 제한도 없이, 함유되는 용매에 따라 적절하게 선택되며, 예를 들어, 이것은 80°C 내지 180°C의 범위이다. 건조에 있어서, 건조에 사용되는 온도를 저하시키기 위하여 진공 오븐을 사용하는 것이 또한 효과적이다.

[0084] 건조 공정의 지속 시간은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 예를 들어, 이것은 10분 내지 1시간이다.

- [0085] 분해 및 생성 공정의 온도는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 예를 들어, 이것은 200°C 내지 400°C의 범위이다.

- [0086] 분해 및 생성 공정의 지속 시간은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 예를 들어, 이것은 1시간 내지 5시간이다.

- [0087] 열처리 단계에서, 전술한 공정은 동시에 수행될 수 있거나, 복수의 단계로 분할될 수 있다.

- [0088] 열처리 단계를 실시하는 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 지지체를 가열하는 방법을 포함한다.

- [0089] 열처리 단계가 실시되는 분위기는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 산소 분위기이다. 산소 분위기에서의 열처리의 수행에 의해, 분해 생성물은 상기 시스템으로부터 신속하게 배출될 수 있으며, 생성된 p형 산화물에서의 산소 결함이 감소될 수 있다.

- [0090] 건조 공정 후 조성물에 파장이 400 nm 이하인 UV 광을 적용하는 것이 열처리 단계에서 효과적이며, 그 이유는 분해 및 생성 공정의 반응이 가속화되기 때문이다. p형 산화물은 파장이 400 nm 이하인 UV 광을 적용함으로써 효율적으로 생성될 수 있으며, 그 이유는 UV광의 적용시에 조성물에 함유된 유기 재료의 화학 결합에서 결합 절단이 일어나서 유기 재료가 분해되기 때문이다.

- [0091] 파장이 400 nm 이하인 UV광은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 엑시머 램프(excimer lamp)로부터 방출되는, 파장이 222 nm인 UV광을 포함한다.

- [0092] 더 나아가, UV광의 적용 대신에 또는 UV광의 적용과 조합하여 오존을 적용하는 것이 또한 바람직하다. 건조 공정 후 조성물에 오존을 적용함으로써, 산화물의 생성이 가속화된다.

- [0093] 본 발명의 p형 산화물의 제조 방법은 진공 공정과 비교하여 대량으로 그리고 저비용으로, 용이하게 p형 산화물을 제조할 수 있으며, 그 이유는 p형 산화물이 코팅 공정에 의해 제조되기 때문이다.

- [0094] 더 나아가, 본 발명의 p형 산화물의 제조 방법은 p형 전기 전도성이 탁월한 p형 산화물을 제조할 수 있다. 본 발명의 p형 산화물의 제조 방법에서 2가 Cu를 함유하는 Cu 함유 화합물이 전술한 방법에 사용되는 p형 산화물 제조용 조성물에서 사용되는 것이 바람직하다. 이 경우, p형 산화물 제조용 조성물 중 Cu의 원자는 2가이고, 1개의 Cu 원자에 대하여 1개의 산소 원자가 존재하지만, Cu는 본 조성물을 이용하여 형성된 그리고 p형 전기 전도성에 기여하는 p형 산화물의 상에서 1가이며, 2개의 Cu 원자에 대하여 1개의 산소 원자가 존재한다. 즉, p형 산화물의 제조 과정에서, p형 산화물 제조용 조성물은 Cu와 O 사이의 관계에서 산소 과잉 상태로 존재한다. p형 산화물 제조를 위해 이러한 조성물을 사용함으로써, 제조된 p형 산화물 중 산소 함량은 증가하며, 산소 결핍에 의해 야기되는 전자의 생성은 억제된다. 따라서, 정공 농도가 증가하고 따라서 p형 전기 전도성이 탁월한 p형 산화물이 수득된다.

- [0095] (반도체 소자)

- [0096] 본 발명의 반도체 소자는 적어도 활성층을 포함하며, 필요할 경우 다른 부재를 추가로 포함할 수 있다.

- [0097] <활성층>

- [0098] 활성층은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 본 발명의 p형 산화물을 포함한다.

- [0099] 이전에 기술된 바와 같이, 본 발명의 p형 산화물은 조성의 조정의 결과로서 의도된 목적에 따른 특성을 획득하며, 따라서 본 발명의 p형 산화물은 반도체 소자의 활성층에서 적합하게 사용된다. 구체적으로, 특성이 활성층에 대하여 최적화된 p형 산화물을 첨가함으로써, 반도체 소자의 특성이 개선될 수 있다.

- [0100] 활성층의 구조, 형상 및 크기는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

- [0101] 반도체 소자의 예는 다이오드, 전계 효과 트랜지스터, 발광 소자, 및 광전 변환 소자를 포함한다.

- [0102] <다이오드>

- [0103] 다이오드는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 제1 전극, 제2 전극, 및 제1 전극과 제2 전극 사이에 형성된 활성층을 포함하는 다이오드를 포함한다. 이러한 다이오드의 예는 pn 접합 다이오드, 및 PIN 광다이오드를 포함한다.

- [0104] n형 산화물 반도체에 대해서는, 가시광에 대한 투과율이 높은 많은 재료가 공지되었다. 본 발명의 p형 산화물도 광대역 캡을 갖는 가시광을 투과시키기 때문에, 투명 다이오드가 이를 재료를 사용하여 제조될 수 있다.

- [0105] -pn 접합 다이오드-

- [0106] pn 접합 다이오드는 적어도 활성층을 포함하며, 필요할 경우, 다른 부재, 예컨대 애노드(anode) 및 캐소드(cathode)를 추가로 포함할 수 있다.

- [0107] --활성층--

- [0108] 활성층은 적어도 p형 반도체층 및 n형 반도체층을 포함하며, 필요할 경우 다른 부재를 추가로 포함할 수 있다.

- [0109] p형 반도체층 및 n형 반도체층은 서로와 접촉한 상태로 있다.

- [0110] ---p형 반도체층---

- [0111] p형 반도체층은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 상기 층은 본 발명의 p형 산화물을 포함한다.

- [0112] p형 산화물의 조성 또는 형성 조건은 활성층으로서 기능하는 데 요구되는 캐리어 밀도 및 캐리어 이동도를 획득하도록 선택되는 것이 바람직하다.

- [0113] p형 반도체층의 평균 두께는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 50 nm 내지 2,000 nm이다.

- [0114] ---n형 반도체층---

- [0115] n형 반도체층의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 n형 투명 산화물 반도체이다.

- [0116] n형 투명 산화물 반도체는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 ZnO, 및 IGZO(In-Ga-Zn-O)를 포함한다.

- [0117] n형 투명 산화물 반도체의 경우에, 활성층은 투명하게 만들어질 수 있으며, 그 이유는 본 발명의 p형 산화물이 광대역 캡을 갖는 가시광을 투과시키기 때문이다.

- [0118] n형 반도체층의 형성 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 진공 공정 및 인쇄를 포함한다. 진공 공정의 예는 스퍼터링, 펄스 레이저 증착(PLD), CVD, 및 ALD를 포함한다. 인쇄의 예는 딥 코팅(dip coating), 잉크젯 인쇄 및 나노 임프린팅(nano imprinting)을 포함한다.

- [0119] n형 반도체층의 평균 두께는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 50 nm 내지 2,000 nm이다.

- [0120] p형 반도체층 및 n형 반도체층 둘 모두가 결정성 재료일 경우에, 이를 층이 적층된 경우 격자의 미스매칭으로 인하여 탁월한 결정성이 획득될 수 없다. 그 결과, 탁월한 특성의 반도체 소자가 제조될 수 없다. 이러한 문제를 회피하기 위하여, 격자가 매칭되는 재료를 선택하는 것이 필요하다. 따라서, 사용 가능한 재료는 한정된다.

- [0121] 반면에, p형 반도체층에 본 발명의 p형 산화물을 사용함으로써, 심지어 n형 반도체층이 결정성인 경우에도, 전술한 문제를 야기하지 않고서 바람직한 pn 접합 계면이 형성될 수 있다. 즉, 본 발명의 p형 산화물의 사용은 다이오드에 있어서 n형 반도체용으로 사용 가능한 재료의 선택을 넓힐 수 있으며, 이외에도 탁월한 소자 특성을 달성하는 것이 가능하다.

- [0122] --애노드(Anode)--

- [0123] 애노드는 p형 반도체층과 접촉 상태로 있다.

- [0124] 애노드의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 금속, 예컨대 Mo, Al, Au, Ag, 및 Cu, 이들의 합금, 투명 전기 전도성 산화물, 및 유기 도체를 포함한다. 투명 전기 전도성 산화물의 예는 산화인듐주석(ITO), 및 안티몬 도핑된 주석 산화물(ATO)을 포함한다. 유기 도체의 예는 폴리에틸렌 디옥시티오펜(PEDOT), 및 폴리아닐린(PANI)을 포함한다.

- [0125] 애노드의 형상, 크기 및 구조는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

- [0126] 애노드는 p형 반도체층과 접촉하도록 배치된다. 이러한 배치 중, 옴 콘택(ohmic contact)이 형성되는 것이 바람직하다.

- [0127] 애노드의 형성 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 (i) 스퍼터링 또는 딥 코팅에 의한 막의 형성, 이어서 포토리소그래피(photolithography)에 의해 패터닝하는 방법, 및 (ii) 인쇄 공정, 예컨대 잉크젯 인쇄, 나노임프린트 및 그라비어에 의해 소정 형상을 갖는 막을 직접적으로 형성하는 방법을 포함한다.

- [0128] --캐소드(Cathode)--

- [0129] 캐소드의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 애노드의 설명에 열거된 재료를 포함한다.

- [0130] 캐소드의 형상, 크기 및 구조는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

- [0131] 캐소드는 n형 반도체층과 접촉하도록 배치된다. 이러한 배치 중, 옴 콘택이 형성되는 것이 바람직하다.

- [0132] 캐소드의 형성 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 애노드의 설명에서 형성 방법으로 기술된 방법을 포함한다.

- [0133] --pn 접합 다이오드의 제조 방법--

- [0134] 도 1에 도시된 pn 접합 다이오드의 제조 방법의 일례를 설명한다.

- [0135] 처음에, 캐소드(2)를 기판(1) 상에 형성시킨다.

- [0136] 기판의 형상, 구조 및 크기는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

- [0137] 기판의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 유리 기판 및 플라스틱 기판을 포함한다.

- [0138] 유리 기판은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 비알칼리 유리 및 실리카 유리를 포함한다.

- [0139] 플라스틱 기판은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 폴리카르보네이트(PC), 폴리이미드(PI), 폴리에틸렌 테레프탈레이트(PET), 및 폴리에틸렌 나프탈레이트(PEN)를 포함한다.

- [0140] 전처리, 예컨대 산소 플라즈마, UV 오존 및 UV 방사선 세척을 기판 상에서 수행하여 이의 표면을 세정하고 또 다른 층과의 부착성을 향상시키는 것이 바람직함에 유의한다.

- [0141] 다음, n형 반도체층(3)을 캐소드(2) 상에 형성시킨다.

- [0142] 후속적으로, p형 반도체층(4)을 n형 반도체층(3) 상에 형성시킨다.

- [0143] 그 후, 애노드(5)를 p형 반도체층(4) 상에 형성시킨다.

- [0144] 상기에 기술된 방식으로 pn 접합 다이오드(6)이 제조된다.

- [0145] <전계 효과 트랜지스터>

- [0146] 전계 효과 트랜지스터는 적어도 게이트 전극, 소스 전극, 드레인 전극, 활성층 및 게이트 절연층을 포함하며, 필요할 경우 다른 부재를 추가로 포함할 수 있다.

- [0147] -게이트 전극-

- [0148] 게이트 전극은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 게이트 전압 인가용 전극이다.

- [0149] 게이트 전극의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 금속, 예컨대 Mo, Al, Au, Ag, 및 Cu, 이들의 합금, 투명 전기 전도성 산화물, 및 유기 도체를 포함한다. 투명 전기 전도성 산화물의 예는 산화주석인듐(ITO), 및 안티몬 도핑된 주석 산화물(ATO)을 포함한다. 유기 도체의 예는 폴리에틸렌 디옥시티오펜(PEDOT), 및 폴리아닐린(PANI)을 포함한다.

- [0150] 게이트 전극의 형성 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 (i) 스퍼터링 또는 딥 코팅에 의한 막의 형성, 이어서 포토리소그래피에 의해 패터닝하는 방법, 및 (ii) 인쇄 공정, 예컨

대 잉크젯 인쇄, 나노임프린트 및 그라비어에 의해 소정 형상을 갖는 막을 직접적으로 형성하는 방법을 포함한다.

[0151] 게이트 전극의 평균 두께는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 20 nm 내지 1  $\mu\text{m}$ , 더 바람직하게는 50 nm 내지 300 nm이다.

[0152] -소스 전극 및 드레인 전극-

[0153] 소스 전극 및 드레인 전극은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이들은 전계 효과 트랜지스터로부터 전류를 추출하도록 구성된 전극이다.

[0154] 소스 전극 및 드레인 전극 각각의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 게이트 전극의 설명에 기술된 재료를 포함한다.

[0155] 활성층과 소스 전극 사이의, 또는 활성층과 드레인 전극 사이의 콘택 저항이 크면 트랜지스터 특성이 열화된다. 이러한 열화를 회피하기 위하여, 낮은 콘택 저항을 달성하는 재료가 소스 전극 및 드레인 전극으로서 선택되는 것이 바람직하다. 구체적으로, 활성층에 함유되는 본 발명의 p형 산화물의 것보다 일함수가 더 큰 재료를 선택하는 것이 바람직하다.

[0156] 소스 전극 및 드레인 전극 각각의 형성 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 게이트 전극에 대한 설명에서 형성 방법으로 기술된 방법을 포함한다.

[0157] 소스 전극 및 드레인 전극 각각의 평균 두께는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 20 nm 내지 1  $\mu\text{m}$ , 더 바람직하게는 50 nm 내지 300 nm이다.

[0158] -활성층-

[0159] 활성층은 본 발명의 p형 산화물을 함유한다.

[0160] 활성층은 소스 전극과 드레인 전극 사이에 형성된다. 여기서, 전술한 "사이"라는 것은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 활성층이 소스 전극 및 드레인 전극과 함께 전계 효과 트랜지스터로서의 기능을 할 수 있는 위치이다.

[0161] p형 산화물의 조성 또는 형성 조건은 활성층으로서의 기능에 요구되는 캐리어 밀도 및 캐리어 이동도를 획득하도록 선택되는 것이 바람직하다.

[0162] 활성층의 평균 두께는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 5 nm 내지 1  $\mu\text{m}$ , 더 바람직하게는 10 nm 내지 300 nm이다.

[0163] -게이트 절연층-

[0164] 게이트 절연층은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 게이트 전극과 활성층 사이에 형성된 절연층이다.

[0165] 게이트 절연층의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 널리 제조된 종래의 재료, 예컨대  $\text{SiO}_2$ , 및  $\text{SiN}_x$ ; 고 유전율 재료, 예컨대  $\text{La}_2\text{O}_3$ , 및  $\text{HfO}_2$ ; 및 유기 재료, 예컨대 폴리이미드(PI) 및 플루오로수지를 포함한다.

[0166] 게이트 절연층의 형성 방법은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 진공 막 형성법, 예컨대 스펀팅, 화학 기상 증착(CVD), 및 원자층 증착(ALD); 및 인쇄법, 예컨대 스펀 코팅, 다이 코팅, 잉크젯 인쇄를 포함한다.

[0167] 게이트 절연층의 평균 두께는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되지만, 이것은 바람직하게는 50 nm 내지 3  $\mu\text{m}$ , 더 바람직하게는 100 nm 내지 1  $\mu\text{m}$ 이다.

[0168] 전계 효과 트랜지스터의 구조는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 상부 콘택, 하부 게이트(도 2); 하부 콘택, 하부 게이트(도 3); 상부 콘택, 상부 게이트(도 4); 및 하부 콘택, 상부 게이트(도 5)를 포함한다.

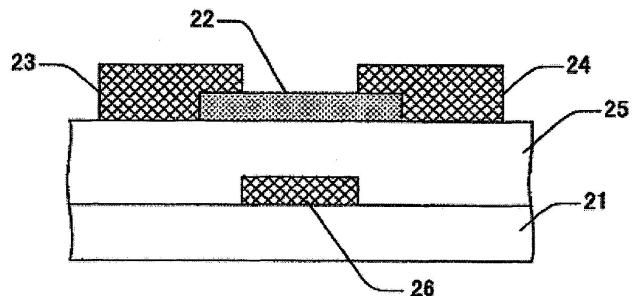

[0169] 도 2 내지 도 5에서, 21은 기판(지지체)이고, 22는 활성층이며, 23은 소스 전극이고, 24는 드레인 전극이며, 25는 게이트 절연층이고, 26은 게이트 전극임에 유의한다.

- [0170] 전계 효과 트랜지스터는 하기에 기술된 표시 소자용으로 적합하게 사용되지만, 이의 사용은 표시 소자로 한정되지 않는다. 예를 들어, 전계 효과 트랜지스터는 IC 카드, 또는 ID 태그에 사용될 수 있다.

- [0171] 전계 효과 트랜지스터는 이의 활성층에 있어서 본 발명의 p형 산화물을 사용하기 때문에, 바람직한 특성의 활성층은 그 조성의 조정에 의해 실현되며, 따라서 이의 트랜지스터 특성은 탁월하다. 더 나아가, 활성층은 무정형이며 따라서 균일성이 높다. 따라서, 트랜지스터들 사이에서의 특성의 분산이 감소될 수 있다.

- [0172] -전계 효과 트랜지스터의 제조 방법-

- [0173] 전계 효과 트랜지스터의 제조 방법의 일례를 설명한다.

- [0174] 먼저, 게이트 전극을 기판 상에 형성시킨다.

- [0175] 기판의 형상, 구조 및 크기는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

- [0176] 기판의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 유리 기판 및 플라스틱 기판을 포함한다.

- [0177] 유리 기판은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 비알칼리 유리 및 실리카 유리를 포함한다.

- [0178] 플라스틱 기판은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 폴리카르보네이트(PC), 폴리이미드(PI), 폴리에틸렌 테레프탈레이트(PET), 및 폴리에틸렌 나프탈레이트(PEN)를 포함한다.

- [0179] 기판은 바람직하게는 전처리, 예컨대 산소 플라즈마, UV 오존 및 UV 방사선 세척에 처해진다.

- [0180] 후속적으로, 게이트 절연층을 게이트 전극 상에 형성시킨다.

- [0181] 그 후, 본 p형 산화물을 함유하는 활성층을 채널 영역에서 게이트 절연층 상에 형성시킨다.

- [0182] 후속적으로, 소스 전극 및 드레인 전극을 게이트 절연층 상에 형성시켜서 소스 전극과 드레인 전극이 서로로부터 분리되게 하며, 이때 활성층은 이들 사이에 존재한다.

- [0183] 상기에 기술된 방식으로, 전계 효과 트랜지스터가 제조된다. 이 제조 방법에 따르면, 예를 들어, 도 2에 도시된 바와 같이, 상부 콘택, 하부 게이트 전계 효과 트랜지스터가 제조된다.

- [0184] 본 발명의 반도체 소자는 이의 활성층 내에 본 발명의 p형 산화물을 함유한다. 본 p형 산화물은 이의 조성의 조정에 의해 의도된 목적에 적합한 특성(전기 전도성)을 달성할 수 있다. 따라서, 특성이 활성층으로서 최적화된 p형 산화물의 사용에 의해, 반도체 소자의 특성이 개선될 수 있다.

- [0185] 본 발명의 반도체 소자로서의 전계 효과 트랜지스터는 특성이 탁월한 TFT를 제공할 수 있다. 활성층이 무정형이기 때문에 높은 균일성이 달성되며, 따라서 트랜지스터들 사이에서의 특성의 분산이 감소될 수 있다.

- [0186] (표시 소자)

- [0187] 본 발명의 표시 소자는 적어도 광 제어 소자, 및 광 제어 소자를 구동하도록 구성된 구동 회로를 포함하며, 필요할 경우 다른 부재를 추가로 포함할 수 있다.

- [0188] <광 제어 소자>

- [0189] 광 제어 소자는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 구동 신호에 따라 광 출력을 제어하는 소자이다. 광 제어 소자의 예는 유기 발광(EL) 소자, 전기변색(electrochromic; EC) 소자, 액정 소자, 전기영동 소자, 및 전기습윤(electrowetting) 소자를 포함한다.

- [0190] <구동 회로>

- [0191] 구동 회로는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 본 발명의 반도체 소자를 갖는다.

- [0192] <다른 부재>

- [0193] 다른 부재는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

- [0194] 본 발명의 표시 소자는 반도체 소자(예를 들어, 전계 효과 트랜지스터)를 포함하며, 따라서 소자들 사이에서의 분산이 적다. 더 나아가, 표시 소자가 에이징되는 경우에도, 구동 트랜지스터가 일정 게이트 전압에 의해 작동

되어서 소자의 사용 수명이 길어질 수 있다.

[0195] (영상 표시 장치)

본 발명의 영상 표시 장치는 적어도 복수의 표시 소자, 배선(복수의 라인), 및 표시 제어 장치를 포함하며, 필요할 경우 다른 부재를 추가로 포함할 수 있다.

[0197] <표시 소자>

표시 소자는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이는 매트릭스 중에 정렬되어 있는 본 발명의 표시 소자이다.

[0199] <배선>

배선은 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 게이트 전압 및 영상 데이터 신호를 표시 소자에 있어서의 각각의 전계 효과 트랜지스터에 개별적으로 인가하는 것이 가능하다.

[0201] <표시 제어 장치>

표시 제어 장치는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 단, 이것은 영상 데이터에 따라 배선을 통하여 각각의 전계 효과 트랜지스터의 신호 전압 및 게이트 전압을 개별적으로 제어하는 것이 가능하다.

[0203] <다른 부재>

[0204] 전술한 다른 부재는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택된다.

[0205] 본 발명의 영상 표시 장치는 본 발명의 표시 소자를 포함하며, 따라서, 영상 표시 장치는 긴 사용 수명에 의해 안정하게 작동될 수 있다.

[0206] 본 발명의 영상 표시 장치는 이동 정보 장치(예를 들어, 이동 전화, 이동식 음악 재생기, 이동식 비디오 재생기, 전자책, 개인 휴대 정보 단말기(personal digital assistant; PDA)에서 또는 영상 장치(예를 들어, 스털 카메라(still camera) 및 비디오 카메라)에서 표시 유닛으로서 사용될 수 있다. 더 나아가, 영상 표시 장치는 수송 시스템, 예컨대 차, 항공기, 기차 및 선박에서 다양한 정보를 위한 표시 유닛으로서 사용될 수 있다. 또한, 영상 표시 장치는 측정 장치, 분석 장치, 의료 장치 또는 광고 매체에서 다양한 정보를 표시하기 위한 표시 유닛으로서 사용될 수 있다.

[0207] (시스템)

[0208] 본 발명의 시스템은 적어도 본 발명의 영상 표시 장치 및 영상 데이터 형성 장치를 포함한다.

[0209] 영상 데이터 형성 장치는 표시될 영상 정보를 기반으로 하는 영상 데이터를 형성하고 상기 영상 데이터를 영상 표시 장치로 출력하도록 구성된다.

[0210] 본 발명의 시스템에는 본 발명의 영상 표시 장치가 구비되어 있으며, 따라서 본 시스템은 높은 정확도로 영상 정보를 표시할 수 있다.

[0211] 다음, 본 발명의 영상 표시 장치를 설명한다.

[0212] 본 발명의 영상 표시 장치는 예를 들어, 일본 공개 특허 공보 제 2010-074148호의 단락 [0059] 내지 [0060], 및 도 2 및 도 3에 기술된 구성을 적용할 수 있다.

[0213] 본 발명의 실시형태의 일례를 다이어그램을 참조하여 설명한다.

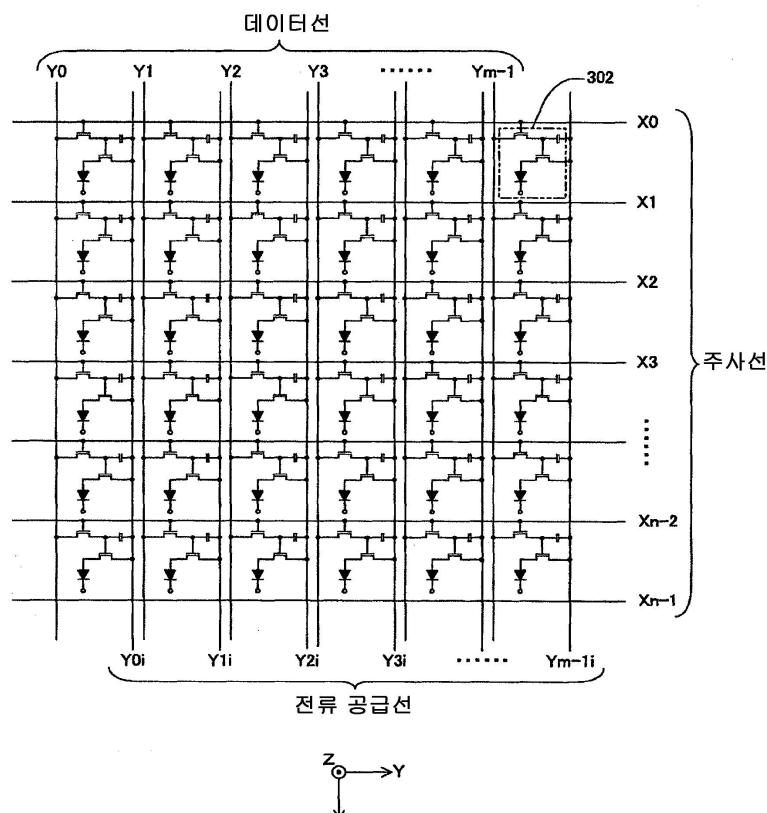

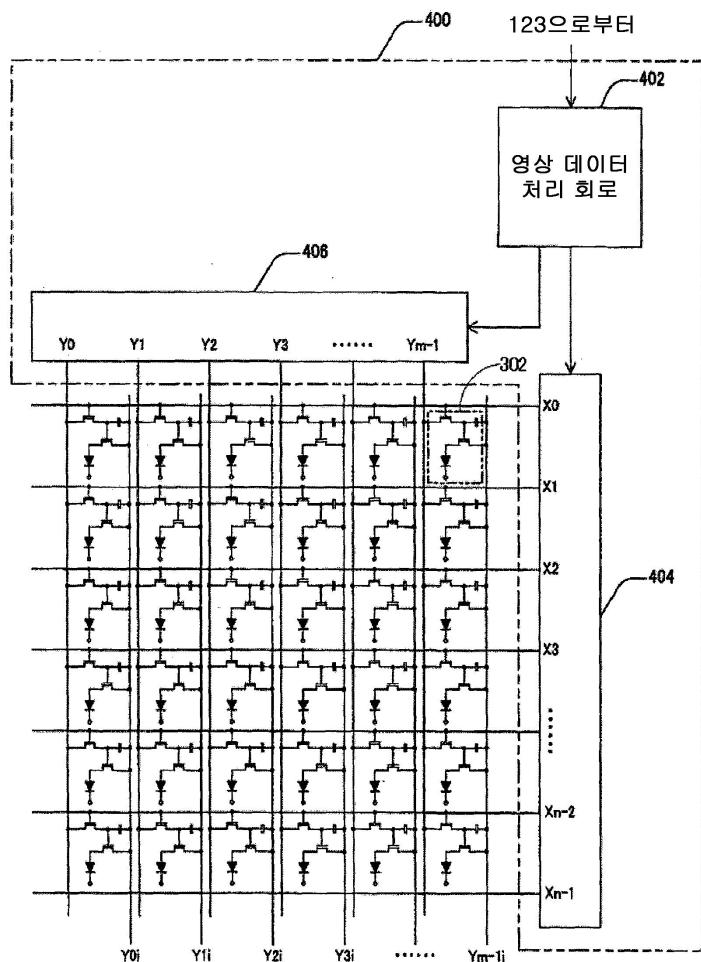

[0214] 도 6은 표시 소자가 배치된 디스플레이를 도시하는 다이어그램이다. 도 6에 도시된 바와 같이, 디스플레이의 X축 방향을 따라서 일정한 간격으로 배치된 "n"개의 주사선(X0, X1, X2, X3, ..., Xn-2, Xn-1), Y 축 방향을 따라서 일정한 간격으로 배치된 "m"개의 데이터선(Y0, Y1, Y2, Y3, ..., Ym-1), 및 Y축 방향을 따라서 일정한 간격으로 배치된 "m"개의 전류 공급선(Y0i, Y1i, Y2i, Y3i, ..., Ym-1i)을 포함한다. 도 7, 도 11, 도 12 및 도 13에서, 동일한 참조 부호(예를 들어, X1, Y1)는 상기와 동일한 것을 나타낸다는 것에 유의한다.

[0215] 기술된 바와 같이, 표시 소자(302)는 주사선 및 데이터선으로 특정된다.

[0216] 도 7은 본 발명의 표시 소자의 일례를 도시하는 개략적 구조도이다.

- [0217] 일례로서 도 7에 도시된 바와 같이, 표시 소자는 유기 EL(발광) 소자(350), 및 유기 EL 소자(350)을 발광시키기 위한 구동 회로(320)를 포함한다. 즉, 디스플레이(310)는 소위 활성 매트릭스식 유기 EL 디스플레이이다. 더 나아가, 디스플레이(310)는 32인치 컬러 디스플레이이다. 디스플레이의 크기는 전술한 크기로 한정되지 않음에 유의한다.

- [0218] 도 7의 구동 회로(320)를 설명한다.

- [0219] 구동 회로(320)는 2개의 전계 효과 트랜지스터(10, 20) 및 커패시터(capacitor; 30)를 포함한다.

- [0220] 전계 효과 트랜지스터(10)는 스위칭 소자로서의 기능을 한다. 전계 효과 트랜지스터(10)의 게이트 전극 G는 특정한 주사선과 접속되며, 전계 효과 트랜지스터(10)의 소스 전극 S는 특정한 데이터선과 접속된다. 더 나아가, 전계 효과 트랜지스터(10)의 드레인 전극 D는 커패시터(30)의 단자들 중 하나와 접속된다.

- [0221] 전계 효과 트랜지스터(20)는 유기 EL 소자(350)에 전류를 공급한다. 전계 효과 트랜지스터(20)의 게이트 전극 G는 전계 효과 트랜지스터(10)의 드레인 전극 D와 접속된다. 더 나아가, 전계 효과 트랜지스터(20)의 드레인 전극 D는 유기 EL 소자(350)의 애노드와 접속되며, 전계 효과 트랜지스터(20)의 소스 전극 S는 특정한 전류 공급 선과 접속된다.

- [0222] 커패시터(30)는 전계 효과 트랜지스터(10)의 상태, 즉, 데이터를 저장하도록 구성된다. 커패시터(30)의 다른 단자는 특정한 전류 공급선과 접속된다.

- [0223] 전계 효과 트랜지스터(10)가 "온(on)" 상태일 경우, 영상 데이터는 신호선 Y2를 통하여 커패시터(30)에 저장된다. 심지어 전계 효과 트랜지스터(10)를 "오프(off)" 상태로 한 후에도, 유기 EL 소자(350)는 영상 데이터에 상응하여 전계 효과 트랜지스터(20)의 "온" 상태를 유지함으로써 구동될 수 있다.

- [0224] 도 8은 표시 소자의 유기 EL 소자(350)와 구동 회로로서의 전계 효과 트랜지스터(20) 사이의 위치 관계의 일례를 도시한다. 여기서, 유기 EL 소자(350)는 전계 효과 트랜지스터(20) 옆에 있도록 배치된다. 전계 효과 트랜지스터 및 커패시터(도시되지 않음)는 동일한 기판 상에 형성됨에 유의한다.

- [0225] 도 8에 도시되어 있는 것은 아니지만, 보호막이 활성층(22)의 상부 상에 제공되는 것이 또한 바람직하다. 보호막의 재료에 대해서는,  $\text{SiO}_2$ ,  $\text{SiNx}$ ,  $\text{Al}_2\text{O}_3$ , 또는 플루오로중합체가 적합하게 사용된다.

- [0226] 더 나아가, 예를 들어 도 9에 도시된 바와 같이, 유기 EL 소자(350)는 전계 효과 트랜지스터(20) 상에 배치될 수 있다. 이 경우, 투명성이 게이트 전극(26)에 요구되며, 따라서 투명 전기 전도성 산화물, 예컨대 ITO,  $\text{In}_2\text{O}_3$ ,  $\text{SnO}_2$ ,  $\text{ZnO}$ , Ga 도핑된  $\text{ZnO}$ , Al 도핑된  $\text{ZnO}$ , 및 Sb 도핑된  $\text{SnO}_2$ 가 게이트 전극(26)용으로 사용된다. 참조 부호 "360"은 층간 절연막(평탄화 막)을 나타냄에 유의한다. 절연막에 대해서는, 예를 들어, 폴리이미드 또는 아크릴 수지가 사용될 수 있다.

- [0227] 도 8 및 도 9에서, 전계 효과 트랜지스터(20)는 기판(21), 활성층(22), 소스 전극(23), 드레인 전극(24), 게이트 절연층(25), 및 게이트 전극(26)을 포함한다. 유기 EL 소자(350)는 캐소드(312), 애노드(314), 및 유기 EL 박막층(340)을 포함한다.

- [0228] 도 10은 유기 EL 소자의 일례를 도시하는 개략적 구조도이다.

- [0229] 도 10에서, 유기 EL 소자(350)는 캐소드(312), 애노드(314), 및 유기 EL 박막층(340)을 포함한다.

- [0230] 캐소드(312)의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 알루미늄(Al), 마그네슘(Mg)-은(Ag) 합금, 알루미늄(Al)-리튬(Li) 합금, 및 ITO(산화인듐주석)를 포함한다. 충분한 두께를 갖는 마그네슘(Mg)-은(Ag) 합금은 고 반사율의 전극으로서의 기능을 하며, 이의 매우 얇은 막(약 20 nm 미만)은 투명 전극으로서의 기능을 한다. 상기 다이어그램에서, 광은 애노드쪽으로부터 나오지만, 광은 캐소드를 투명하게 만들도록써 또는 투명 전극을 캐소드로서 사용함으로써 캐소드쪽으로부터 나올 수 있다.

- [0231] 애노드(314)의 재료는 어떠한 제한도 없이, 의도된 목적에 따라 적절하게 선택되며, 이의 예는 ITO(산화인듐주석), IZO(산화인듐아연), 및 은(Ag)-네오디뮴(Nd) 합금을 포함한다. 은 합금이 애노드용으로 사용될 경우, 애노드는 고 반사율의 전극이며, 이는 광이 캐소드쪽으로부터 나오는 경우에 적합함에 유의한다.

- [0232] 유기 EL 박막층(340)은 전자 수송층(342), 발광층(344), 및 정공 수송층(346)을 포함한다. 전자 수송층(342)은 캐소드(312)에 접속되며, 정공 수송층(346)은 애노드(314)에 접속된다. 애노드(314)와 캐소드(312) 사이에서의

특정한 전압의 인가시에, 발광층(344)은 광을 방출한다.

- [0233] 여기서, 전자 수송층(342) 및 발광층(344)은 공동으로 1개의 층을 형성할 수 있다. 더 나아가, 전자 주입층이 전자 수송층(342)과 캐소드(312) 사이에 제공될 수 있다. 또한, 정공 주입층이 정공 수송층(346)과 애노드(314) 사이에 제공될 수 있다.

- [0234] 더 나아가, 광이 기판쪽(도 10에서 하부쪽)으로부터 나오는 "하부 방출"의 실시형태가 상기에 설명되어 있지만, 유기 EL 소자는 광이 기판쪽(도 10에서 하부쪽)의 반대쪽으로부터 나오는 "상부 방출"을 이용할 수 있다.

- [0235] 도 11은 본 발명의 영상 표시 장치의 또 다른 예를 도시하는 개략적 구조도이다.

- [0236] 도 11에서, 영상 표시 장치는 표시 소자(302), 배선(주사선, 데이터선, 전류 공급선) 및 표시 제어 장치(400)를 포함한다.

- [0237] 표시 제어 장치(400)는 영상 데이터 처리 회로(402), 주사선 구동 회로(404), 및 데이터선 구동 회로(406)를 포함한다.

- [0238] 영상 데이터 처리 회로(402)는 영상 출력 회로의 출력 신호를 기반으로 하여 디스플레이 상에서의 복수의 표시 소자(302)의 회도를 결정한다.

- [0239] 주사선 구동 회로(404)는 영상 데이터 처리 회로(402)로부터의 지시에 응답하여 ("n"개의) 주사선 각각에 전압을 인가한다.

- [0240] 데이터선 구동 회로(406)는 영상 데이터 처리 회로(402)로부터의 지시에 응답하여 ("m"개의) 데이터선 각각에 전압을 인가한다.

- [0241] 더 나아가, 상기 실시형태는 광 제어 소자가 유기 EL 소자인 경우를 설명하지만, 광 제어 소자는 유기 EL 소자로 한정되지 않는다. 예를 들어, 광 제어 소자는 전기변색 소자일 수 있다. 이러한 경우에, 디스플레이는 전기변색 디스플레이이다.

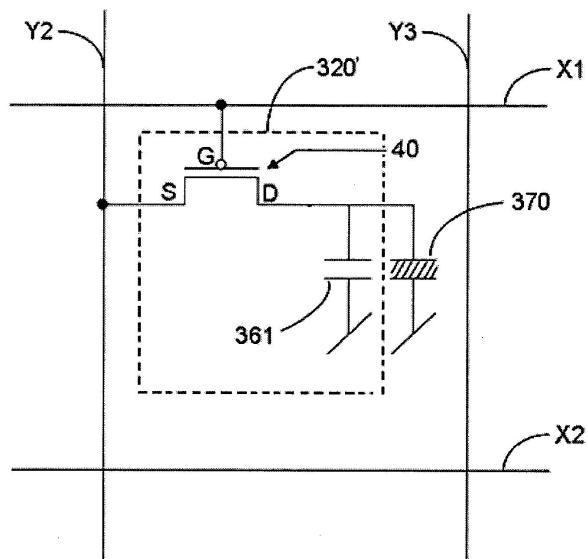

- [0242] 또한, 광 제어 소자는 액정 소자일 수 있다. 이 경우에, 디스플레이는 액정 디스플레이이며, 표시 소자(302')용 전류 공급선은 요구되지 않는데, 이는 도 12에 도시된 바와 같다. 더욱이, 도 13에 도시된 바와 같이, 구동 회로(320')는 전계 효과 트랜지스터(10, 20)의 것과 동일한 구조를 갖는 1개의 전계 효과 트랜지스터(40)로 구성될 수 있다. 전계 효과 트랜지스터(40)에서, 게이트 전극 G는 특정한 주사선과 접속되며, 소스 전극 S는 특정한 데이터선과 접속된다. 더 나아가, 드레인 전극 D는 커페시터(361) 및 액정 소자(370)의 화소 전극과 접속된다.

- [0243] 더 나아가, 광 제어 소자는 전기영동 소자, 무기 EL 소자 또는 전기습윤 소자 중 임의의 것일 수 있다.

- [0244] 본 발명의 시스템이 텔레비전 장치인 실시형태가 상기에 설명되었지만, 본 시스템은 텔레비전 장치로 한정되지 않는다. 본 시스템은, 이것이 영상 및 정보를 표시하는 장치로서 영상 표시 장치를 갖기만 한다면, 임의의 시스템으로서 적용될 수 있다. 예를 들어, 본 시스템은 컴퓨터(개인용 컴퓨터를 포함함) 및 영상 표시 장치가 접속된 컴퓨터 시스템일 수 있다.

- [0245] 본 발명의 시스템은 본 발명의 영상 표시 장치를 포함하며, 따라서 본 시스템은 긴 사용 수명과 함께 안정하게 작동된다.

- [0246] **[실시예]**

- [0247] 본 발명의 실시예를 이하에 설명하지만, 이를 실시예는 어떠한 방식으로든지 본 발명의 범주를 한정하는 것으로 해석되어서는 안된다.

- [0248] (실시예 1 내지 실시예 6)

- [0249] <Cu-Sb 산화물 (무정형) 막의 제조>

- [0250] 각각이 표 1에 나타낸 제형 및 Sb/Cu 몰비를 갖는 Cu-Sb 산화물용 잉크들(p형 산화물 제조용 조성물들)을 제조하였다. 구체적으로, 네오데칸산구리(8.28 질량%) 틀루엔 용액 및 트리페닐 안티몬(5.83 질량%) 틀루엔 용액을 표 1에 나타낸 제형에 따라 블렌딩하여, 생성된 잉크 중 Sb 몰에 대한 생성된 잉크 중 Cu 몰의 비(Sb/Cu 몰비)가 각각 2.5%, 6.3%, 12.5%, 18%, 25%, 및 100%가 되게 함으로써 Cu-Sb 산화물용의 6가지의 상이한 잉크들(p형 산화물 제조용 조성물들)을 제조하였다. 0.5 mL의 틀루엔을 표 1에 나타낸 제형에 첨가하였음에 유의한다.

- [0251] 다음, Cu-Sb 산화물용 잉크를 스펀 코팅에 의해 유리 기판 상에 도포하였다. 120°C에서 1시간 동안 잉크를 건조

시킨 후, 산소 기류 중에서 엑시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 Cu-Sb 산화물 막(p형 산화물 막)을 형성하였다.

표 1

| [0252] | Sb/Cu 몰비 [%] | 네오데칸산구리(8.28 질량%) 톨루엔 용액 [mL] | 트리페닐 안티몬(5.83 질량%) 톨루엔 용액 [mL] | 막 두께 [nm] | 체적 저항률 [Ωcm] |

|--------|--------------|-------------------------------|--------------------------------|-----------|--------------|

| 실시예 1  | 2.5          | 0.153                         | 0.01                           | 39.4      | 3.39E+00     |

| 실시예 2  | 6.3          | 0.153                         | 0.025                          | 42        | 8.00E+00     |

| 실시예 3  | 12.5         | 0.153                         | 0.05                           | 41        | 5.72E+01     |

| 실시예 4  | 18           | 0.153                         | 0.07                           | 42.1      | 4.87E+02     |

| 실시예 5  | 25           | 0.153                         | 0.1                            | 37.2      | 1.27E+05     |

| 실시예 6  | 100          | 0.153                         | 0.4                            | 73.1      | 6.58E+06     |

[0253] 표 1에서, E는 "10의 지수"를 나타냄에 유의한다. 예를 들어, "1.0E + 01"은 "10"을 나타내며, "1.0E + 02"는 "100"을 나타낸다. 표 2, 도 14 및 도 24에 나타낸 E는 동일한 것을 나타낸다.

[0254] (비교예 1)

[0255] <Cu-Sb 산화물(결정)의 제조>

[0256] 실시예 1에서와 동일한 방식으로 제조한 Cu-Sb 산화물 막(Sb/Cu 몰비: 2.5%)을 주위 분위기에서 500°C에서 1시간 동안 가열하였다.

[0257] (비교예 2)

[0258] <Cu-Sb 산화물(결정)의 제조>

[0259] 실시예 1에서와 동일한 방식으로 제조한 Cu-Sb 산화물 막(Sb/Cu 몰비: 2.5%)을 질소 분위기에서 500°C에서 1시간 동안 가열하였다.

표 2

| [0260] | Sb/Cu 몰비 [%] | 가열 처리 조건             | 막 두께 [nm] | 체적 저항률 [Ωcm] |

|--------|--------------|----------------------|-----------|--------------|

| 비교예 1  | 2.5          | 대기 중에서 500°C, 1시간    | 43.2      | 5.43E+10     |

| 비교예 2  | 2.5          | 질소 가스 중에서 500°C, 1시간 | 42.2      | 3.10E+01     |

[0261] 실시예 1 내지 실시예 6 및 비교예 1 내지 비교예 2에서 수득한 산화물 막 각각은 두께(막 두께)를 측정하고 체적 저항률을 측정하였다. 또한, 상기 산화물 막 각각을 X선 회절 분석하였다.

[0262] <두께>

[0263] 산화물 막의 두께는 반사 분광 막 두께 계측기(meter)(FE-3000, 오츠카 일렉트로닉스 컴퍼니, 리미티드(Otsuka Electronics Co., Ltd.)에 의해 제조)로 측정할 경우, 파장이 약 300 nm 내지 약 700 nm인 반사 스펙트럼을 측정 및 분석하여 결정하였다. 그 결과가 표 1 및 표 2에 제시되어 있다.

[0264] <체적 저항률>

[0265] 실시예 1 내지 실시예 6 및 비교예 1 내지 비교예 2에서 제조한 산화물 막 각각에 Au를 금속 마스크를 통하여 기상 증착에 의해 증착시킴으로써 한 쌍의 선 형상의 전극을 형성하였다. 상기 전극들 사이의 전류-전압(I-V) 특성을 측정함으로써 체적 저항률을 결정하였다. 그 결과가 표 1 및 표 2에 제시되어 있다. 더 나아가, 표 1에 제시된 Sb/Cu 몰비와 (체적) 저항률 사이의 관계가 도 14에 도시되어 있다.

[0266] 표 1 및 도 14에 제시된 바와 같이, 모든 실시예에서 전기 전도성이 확인되었다. 더 나아가, Sb/Cu 몰비가 증가함에 따라 체적 저항률이 증가하는 경향이 있었으며, 체적 저항률은 약 20 Ωcm로부터 약 107 Ωcm까지 변화하였다.

[0267] <X선 회절>

- [0268] 엑스퍼트프로(X'PertPro)(필립스(Philips)사제)에 의해 실시예 1 내지 실시예 6 및 비교예 1 내지 비교예 2의 산화물 막에서 X선 회절 분석을 수행하였다.

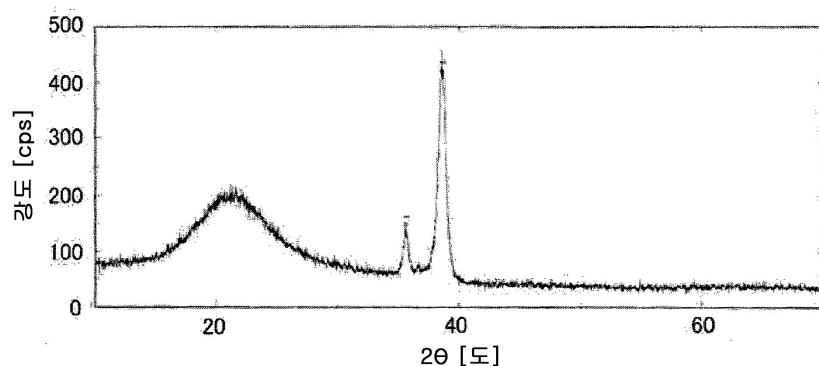

- [0269] 실시예 1의 p형 산화물의 X선 회절 측정 결과가 도 15에 도시되어 있다. 실시예 2의 p형 산화물의 X선 회절 측정 결과가 도 16에 도시되어 있다. 실시예 3의 p형 산화물의 X선 회절 측정 결과가 도 17에 도시되어 있다. 실시예 4의 p형 산화물의 X선 회절 측정 결과가 도 18에 도시되어 있다. 실시예 5의 p형 산화물의 X선 회절 측정 결과가 도 19에 도시되어 있다. 실시예 6의 p형 산화물의 X선 회절 측정 결과가 도 20에 도시되어 있다. 비교예 1의 p형 산화물의 X선 회절 측정 결과가 도 21에 도시되어 있다. 비교예 2의 p형 산화물의 X선 회절 측정 결과가 도 22에 도시되어 있다.

- [0270] 회절 피크는 실시예 1 내지 실시예 6의 모든 6가지의 샘플에서 발견되지 않았으며, 따라서 이들 Cu-Sb 산화물 막 각각은 무정형의 상태로 있음이 확인되었다.

- [0271] 비교예 1의 샘플에서 수행한 X선 회절 측정 결과로부터 몇몇 회절 피크가 발견되었으며, 이의 각( $2\theta$ )으로부터 CuO 결정이 비교예 1의 산화물에 존재함이 밝혀졌다. 산소가 가열 처리 동안 상기 막 내에 들어감으로써 CuO가 생성되었다고 여겨진다.

- [0272] 비교예 2의 샘플에서 수행한 X선 회절 측정 결과는 Cu<sub>2</sub>O 결정 및 금속 Cu에 상응하는 각에서 회절 피크가 있음을 나타내며, 따라서 가열 처리 동안 일어난 환원에 의해 금속 Cu가 생성됨이 밝혀졌다.

- [0273] 본 발명의 p형 산화물 막을 다양한 반도체 소자에서 사용할 수 있지만, 반도체 소자 중 반도체에 요구되는 특성(저항률)은 일반적으로 반도체 소자의 유형 및 특성에 따라 달라진다. 따라서, Sb/Cu 몰비의 값은 의도된 목적에 따라 적절하게 선택할 수 있다.

- [0274] 비교예 1의 샘플의 Au 전극들 사이에서 측정한 전류-전압(I-V) 특성은 선형 관계를 나타내지 않았으며, 샘플은 저항률이 높았고, 즉, 체적 저항률이  $10^{10} \Omega\text{cm}$  이상이었다. Cu가 2가인 다양한 CuO 결정이 상기 막에 함유되었기 때문에 충분한 전기 전도성이 수득되지 않았던 것으로 여겨진다.

- [0275] 비교예 2의 샘플은 실시예 1의 샘플의 것과 유사한 낮은 저항률을 달성하였다. 그러나, X선 회절 측정 결과를 참조하면, 이의 전기 전도성이 금속 Cu가 부분적으로 기여하는 것으로 보였다. 따라서, 탁월한 p형 전기 전도성을 획득하는 목적은 비교예 2의 막에 의해서는 달성되지 않았다.

- [0276] 구체적으로, 결정성 Cu-Sb 산화물은 p형 전기 전도성을 제어할 수 없었다.

- [0277] (실시예 7)

- [0278] <Cu-Sb 산화물 막(무정형)의 제조>

- [0279] 10 mL의 에틸렌 글리콜 중에, 2.42 g(10 mmol에 상응함)의 질산구리 3수화물을 용해시켜 구리 원료 용액을 제조하였다. 더 나아가, 2.29 g(10 mmol에 상응함)의 염화안티몬을 10 mL의 프로필렌 글리콜에 용해시킴으로써 안티몬 원료 용액을 제조하였다.

- [0280] 구리 원료 용액(5 mL) 및 안티몬 원료 용액(0.9 mL)을 혼합하고 교반시킴으로써 Cu-Sb 산화물용 잉크(p형 산화물 제조용 조성물)를 제조하였다. 잉크 중 Sb 몰에 대한 잉크 중 Cu 몰의 비(Sb/Cu 몰비)는 18%였다.

- [0281] 다음, 유리 기판을 스플 코팅에 의해 Cu-Sb 산화물용 잉크로 코팅하였다. 120°C에서 1시간 동안 잉크를 건조시킨 후, 산소 기류 중에서 엑시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 Cu-Sb 산화물 막(p형 산화물 막)을 형성하였다. 수득한 막 중 Sb/Cu 몰비는 18%였으며, 실시예 4의 것과 동일한 조성을 갖는 막이 형성되었다.

- [0282] 상기 막의 막 두께 및 체적 저항률을 실시예 1에서와 동일한 방식으로 측정하였다. 그 결과, 막 두께는 89 nm였으며, 체적 저항률은  $6.28 \times 10^2 \Omega\text{cm}$ 였다. 상기 막의 체적 저항률은 실시예 4의 p형 막의 체적 저항률( $4.87 \times 10^2 \Omega\text{cm}$ )과 유사함이 확인되었다. 따라서, 심지어 상이한 유형의 Cu 함유 화합물, Sb 함유 화합물 및 용매를 잉크의 제형화 동안 사용할 경우에도, Cu와 Sb의 몰비가 동일하기만 하다면 실질적으로 유사한 전기 전도성 특성을 갖는 p형 산화물 막이 수득될 수 있음이 확인되었다.

- [0283] 실시예 7에서 수득한 막에서 수행한 X선 회절 측정 결과가 도 23에 제시되어 있다. 도 23에 제시된 바와 같이, 실시예 7에서 수득한 막도 무정형 상태로 있음이 확인되었다.

- [0284] (실시예 8)

- [0285] <pn 접합 다이오드의 제조>

- [0286] -기판의 제조-

- [0287] 기판에 대해서는, 비알칼리 유리 기판(판 두께: 0.7 mm)을 사용하였다. 중성 세제, 순수(pure water) 및 이소프로필 알코올을 사용하여 초음파 세정함으로써 유리 기판을 세척하였다. 기판의 건조 후, 기판은 90°C에서 10분 동안 UV-오존 처리를 추가로 수행하였다.

- [0288] -캐소드의 형성-

- [0289] 유리 기판에서, 금속 마스크를 통하여 기상 증착에 의해 100 nm의 두께로 Al을 증착시킴으로써 캐소드를 형성하였다.

- [0290] -n형 반도체층의 형성-

- [0291] 캐소드에서, 금속 마스크를 통하여 무선 주파수 스퍼터링에 의해 Mg-In 산화물 막을 형성시켰다. 표적으로서,  $In_2MgO_4$ 의 조성을 갖는 다결정성 소결체(크기(직경: 4 인치)를 사용하였다. 스퍼터링 챔버 내의 최종 압력을  $2 \times 10^{-5}$  Pa로 설정하였다. 스퍼터링 동안의 아르곤 가스 및 산소 가스의 유량을 제어하여 1.0 Pa의 총 압력 및  $6.0 \times 10^{-2}$  Pa의 산소 분압을 달성하였다. 기판의 온도는 스퍼터링 동안 특별히 제어하지 않았다. 전력 및 스퍼터링의 지속 시간을 각각 150 W 및 15분으로 조정함으로써 두께가 160 nm인 Mg-In 산화물 막을 형성하였다.

- [0292] -p형 반도체층의 형성-

- [0293] n형 반도체층에서 Cu-Sb 산화물 막(Sb/Cu 몰비: 12.5%)을 실시예 3에서와 동일한 방식으로 형성하였다. Cu-Sb 산화물 막의 두께는 48.5 nm였다.

- [0294] -애노드의 형성-

- [0295] p형 반도체층 상에 Au를 금속 마스크를 통하여 기상 증착에 의해 100 nm의 두께로 증착시킴으로써 애노드를 형성하였다.

- [0296] 상기에 기술한 공정에 의해 pn 접합 다이오드를 수득하였다.

- [0297] <평가>

- [0298] 실시예 8에서 수득한 다이오드의 전류-전압(I-V) 특성을 측정하였다. 그 결과가 도 24에 제시되어 있다. 상기 결과로부터, 전형적인 정류성이 수득됨이 밝혀졌다. 구체적으로, 상기 결과는 본 발명의 p형 산화물을 활성층으로서 사용함으로써 pn 접합 다이오드가 실현될 수 있음을 나타냈다.

- [0299] (실시예 9)

- [0300] <전계 효과 트랜지스터의 제조>

- [0301] -기판(게이트 전극, 게이트 절연층)의 제조-

- [0302] 기판에 대해서는, 열산화된 막(두께: 200 nm)을 포함하는 Si 기판을 사용하였다. 중성 세제, 순수 및 이소프로필 알코올을 사용하여 초음파 세정함으로써 Si 기판을 세척하였다. 기판의 건조 후, 상기 기판에서 90°C에서 10분 동안 UV-오존 처리를 추가로 수행하였다. 열산화된 막은 게이트 절연층이며, Si 기판은 게이트 전극임에 유의한다.

- [0303] -활성층의 형성-

- [0304] 실시예 1에서 제조한 Cu-Sb 산화물 막(Sb/Cu 몰비: 2.5%)용 잉크를 스판 코팅에 의해 상기 기판 상에 적용하였다. 120°C에서 1시간 동안 잉크를 건조시킨 후, 산소 기류 중에서 엑시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 평균 두께가 45 nm인 Cu-Sb 산화물 막(Sb/Cu 몰비: 2.5%)을 형성하였다.

- [0305] 그 후, 포토레지스트를 그 위에 적용하고, 코팅된 포토레지스트를 예비베이킹하고, 노광 장비에 의해 노광시키고, 현상함으로써, 형성시킬 활성층과 동일한 패턴을 갖는 레지스트 패턴을 형성하였다. 더 나아가, 레지스트 패턴이 형성되지 않은 영역 내의 Cu-Sb 산화물 막을 습식 에칭에 의해 제거하고, 이어서 레지스트 패턴을 제거

함으로써 활성층을 형성하였다.

[0306] -소스 전극 및 드레인 전극의 형성-

[0307] 금속 마스크를 통하여 기상 증착에 의해 활성층에서 Cr을 1 nm의 두께로 증착시키고 이어서 Au를 100 nm의 두께로 증착시킴으로써 소스 전극 및 드레인 전극을 형성하였다. 이의 채널 길이는 50  $\mu$ m였으며, 이의 채널 폭은 0.4 mm였다.

[0308] 마지막으로, 산소 기류 중에서 300°C에서 1시간 동안 어닐링을 수행함으로써 전계 효과 트랜지스터를 제조하였다.

[0309] <평가>

[0310] 실시예 9에서 제조한 전계 효과 트랜지스터의 전달 특성( $V_{ds} = -20$  V)을 측정하였으며, 이의 결과는 보통은 오프인 타입의 탁월한 p형 특성을 나타냈다.

[0311] (실시예 10)

[0312] <전계 효과 트랜지스터의 제조>

[0313] -기판(게이트 전극, 게이트 절연층)의 제조-

[0314] 기판에 대해서는, 열산화된 막(두께: 200 nm)을 포함하는 Si 기판을 사용하였다. 중성 세제, 순수 및 이소프로필 알코올을 사용하여 초음파 세정함으로써 Si 기판을 세척하였다. 기판의 건조 후, 상기 기판에서 90°C에서 10분 동안 UV-오존 처리를 추가로 수행하였다. 열산화된 막은 게이트 절연층이며, Si 기판은 게이트 전극임에 유의한다.

[0315] -소스 전극 및 드레인 전극의 형성-

[0316] 열산화된 막을 포함하는 Si 기판에서 헥사메틸디실라잔(HMDS)을 스펀 코팅, 이어서 건조 공정에 의해 적용함으로써 기판의 표면에 소수화 처리를 제공하였다. 그 후, 리프트오프(lift-off)용의 하층 레지스트를 스펀 코팅 및 건조 공정에 의해 형성하였다. 하층 레지스트 상에, 감광성 포토레지스트를 스펀 코팅 및 건조 공정에 의해 형성시켰다. 포토마스크를 통한 노광을 통하여 레지스트를 패터닝하고 현상한 후, 전극 재료인 Pt의 막을 DC 스퍼터링에 의해 형성시켰다. 표적으로서, Pt(크기(직경): 4 인치)를 사용하였다. 스퍼터링 챔버 내의 최종 압력을  $1 \times 10^{-3}$  Pa로 설정하였다. 스퍼터링 동안 아르곤 기류를 공급하였으며, 압력을 0.35 Pa로 설정하였다. 기판의 온도는 스퍼터링 동안 특별히 제어하지 않았다. 전력 및 스퍼터링의 지속 시간을 각각 DC 200 W 및 6분 15초로 조정함으로써 두께가 50 nm인 Pt 막을 형성하였다.

[0317] 그 후, Pt 막을 형성한 기판을 N-메틸피롤리돈에 침지시켜 원하지 않는 부분의 Pt를 레지스트와 함께 제거함으로써 의도한 형상의 Pt 소스 전극 및 Pt 드레인 전극을 수득하였다.

[0318] -잉크젯 인쇄용 반도체 잉크의 제조-

[0319] 10 mL의 에틸렌 글리콜 중에, 2.42 g(10 mmol에 상응함)의 질산구리 3수화물을 용해시킴으로써 구리 원료 용액을 제조하였다. 더 나아가, 2.29 g(10 mmol에 상응함)의 염화안티몬을 10 mL의 에틸렌 글리콜에 용해시킴으로써 안티몬 원료 용액을 제조하였다.

[0320] 에틸렌 글리콜(2.25 mL), 에틸렌 글리콜 모노부틸 에테르(4.5 mL), 상기 구리 원료 용액(2 mL), 및 상기 안티몬 원료 용액(0.25 mL)을 혼합하고 교반시킴으로써 잉크젯 인쇄용 반도체 잉크(Cu-Sb 반도체 잉크)를 제조하였다. 잉크 중 Cu 몰과 잉크 중 Sb 몰의 비(Sb/Cu 몰비)는 12.5%였다.

[0321] -활성층의 형성-

[0322] Cu-Sb 반도체 잉크(Sb/Cu 몰비: 12.5%)를 잉크젯 장비에 의해 소스-드레인 전극을 형성시킨 의도된 기판 영역 상에 적용하였다. 120°C에서 1시간 동안 잉크를 건조시킨 후, 엑시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 두께가 52 nm인 Cu-Sb 산화물 막(Sb/Cu 몰비: 12.5%)을 형성하였다.

[0323] 마지막으로, 어닐링을 300°C에서 1시간 동안 수행함으로써 전계 효과 트랜지스터를 제조하였다.

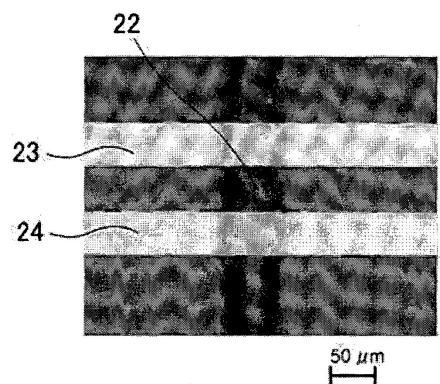

[0324] 전계 효과 트랜지스터의 채널 영역의 현미경 사진을 도 25에 나타낸다. 소스 전극(23)과 드레인 전극(24) 사이

의 공간이 채널 길이이며, 이는 50  $\mu\text{m}$ 였다. 채널 폭은 종방향 라인의 형상으로 적용된 활성층(22)의 폭에 의해 규정하였으며, 상기 사진의 전계 효과 트랜지스터에서 채널 폭은 37  $\mu\text{m}$ 였다.

[0325] <평가>

[0326] 실시예 10에서 제조한 전계 효과 트랜지스터의 전달 특성( $V_{ds} = -20$  V)을 측정하였으며, 이의 결과는 보통은 오프인 타입의 탁월한 p형 특성을 나타냈다. 스핀 코팅에 의해 Cu-Sb 산화물 막(Sb/Cu 몰비: 2.5%)을 형성시키고 이어서 습식 에칭에 의해 의도된 형상을 갖도록 막을 가공한 실시예 9와 비교하여, 실시예 10에서는 잉크젯 인쇄에 의해 단지 의도된 영역 내에 Cu-Sb 산화물 막(Sb/Cu 몰비: 12.5%)을 형성시켰기 때문에 실시예 10에서는 이후의 단계에서 패터닝 없이 더욱 간단한 방법에 의해 전계 효과 트랜지스터를 제조하였다.

[0327] (실시예 11 내지 실시예 17)

[0328] <Cu-Sn 산화물 (무정형) 막의 제조>

[0329] 각각이 표 3에 나타낸 제형 및 Sn/Cu 몰비를 갖는 Cu-Sn 산화물용 잉크들(p형 산화물 제조용 조성물들)을 제조하였다. 구체적으로, 네오데칸산구리(8.28 질량%) 톨루엔 용액 및 주석 2-에틸 헥사노에이트(27.83 질량%) 톨루엔 용액을 표 3에 나타낸 제형에 따라 블렌딩하여, 생성된 잉크 중 Sn 몰에 대한 생성된 잉크 중 Cu 몰의 비(Sn/Cu 몰비)가 각각 2.5%, 6.3%, 12.5%, 18%, 25%, 50% 및 100%가 되게 함으로써 Cu-Sn 산화물용의 7가지의 상이한 잉크들(p형 산화물 제조용 조성물들)을 제조하였다. 0.5 mL의 톨루엔을 표 3에 나타낸 제형에 첨가하였음에 유의한다.

[0330] 다음, Cu-Sn 산화물용 잉크를 스핀 코팅에 의해 유리 기판 상에 도포하였다. 120°C에서 1시간 동안 잉크를 건조시킨 후, 산소 기류 중에서 액시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 Cu-Sn 산화물 막(p형 산화물 막)을 형성하였다.

표 3

| [0331] | Sn/Cu 몰비 [%] | 네오데칸산구리(8.28 질량%) 톨루엔 용액 [mL] | 주석 2-에틸 헥사노에이트(27.83 질량%) 톨루엔 용액 [mL] | 막 두께 [nm] | 체적 저항률 [ $\Omega\text{cm}$ ] |

|--------|--------------|-------------------------------|---------------------------------------|-----------|------------------------------|

| 실시예 11 | 2.5          | 0.153                         | 0.0017                                | 47.2      | 5.61E+00                     |

| 실시예 12 | 6.3          | 0.153                         | 0.0043                                | 49.6      | 2.51E+01                     |

| 실시예 13 | 12.5         | 0.153                         | 0.0085                                | 46.2      | 6.53E+01                     |

| 실시예 14 | 18           | 0.153                         | 0.012                                 | 48.6      | 9.53E+02                     |

| 실시예 15 | 25           | 0.153                         | 0.017                                 | 42.6      | 1.52E+05                     |

| 실시예 16 | 50           | 0.153                         | 0.034                                 | 55.1      | 1.44E+07                     |

| 실시예 17 | 100          | 0.153                         | 0.068                                 | 114.7     | 3.06E+06                     |

[0332] 표 3에서, E는 "10의 지수"를 나타냄에 유의한다. 예를 들어, "1.0E + 01"은 "10"을 나타내며, "1.0E + 02"는 "100"을 나타낸다. 표 4, 도 16 및 도 36에 나타낸 E는 동일한 것을 나타낸다.

[0333] (비)교예 3)

[0334] <Cu-Sn 산화물(결정)의 제조>

[0335] 실시예 11에서와 동일한 방식으로 제조한 Cu-Sn 산화물 막(Sn/Cu 몰비: 2.5%)을 주위 분위기에서 300°C에서 1시간 동안 가열하였다.

표 4

| [0336] | Sn/Cu 몰비 [%] | 가열 처리 조건          | 막 두께 [nm] | 체적 저항률 [ $\Omega\text{cm}$ ] |

|--------|--------------|-------------------|-----------|------------------------------|

| 비교예 3  | 2.5          | 대기 중에서 300°C, 1시간 | 45.0      | 2.10E+13                     |

[0337] 실시예 11 내지 실시예 17 및 비교예 3에서 수득한 산화물 막 각각을 실시예 1에서와 동일한 방식으로 두께(막 두께)를 측정하고 체적 저항률을 측정하였다. 또한, 상기 산화물 막 각각을 X선 회절 분석하였다.

- [0338] 막 두께 및 체적 저항률의 결과가 표 3 및 표 4에 제시되어 있다.

- [0339] 표 3에 나타낸 Sn/Cu 몰비와 (체적) 저항률 사이의 관계가 도 26에 제시되어 있다.

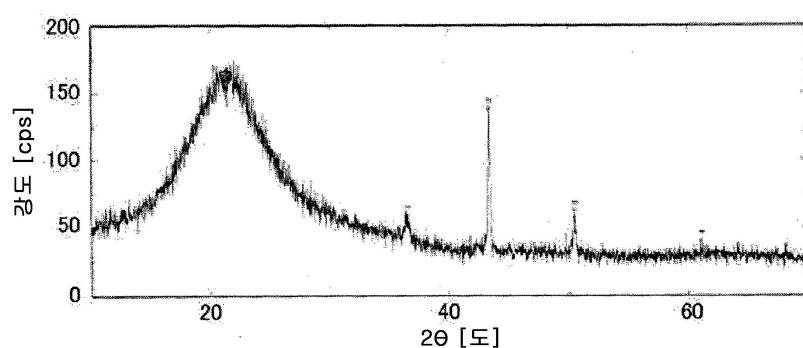

- [0340] 실시예 11의 p형 산화물의 X선 회절 측정 결과가 도 27에 도시되어 있다. 실시예 12의 p형 산화물의 X선 회절 측정 결과가 도 28에 도시되어 있다. 실시예 13의 p형 산화물의 X선 회절 측정 결과가 도 29에 도시되어 있다. 실시예 14의 p형 산화물의 X선 회절 측정 결과가 도 30에 도시되어 있다. 실시예 15의 p형 산화물의 X선 회절 측정 결과가 도 31에 도시되어 있다. 실시예 16의 p형 산화물의 X선 회절 측정 결과가 도 32에 도시되어 있다. 실시예 17의 p형 산화물의 X선 회절 측정 결과가 도 33에 도시되어 있다. 비교예 3의 p형 산화물의 X선 회절 측정 결과가 도 34에 도시되어 있다.

- [0341] 회절 피크는 실시예 11 내지 실시예 17의 모든 7가지의 샘플에서 발견되지 않았으며, 따라서 이를 Cu-Sn 산화물 막 각각은 무정형의 상태로 있음이 확인되었다.

- [0342] 비교예 3의 샘플에서 수행한 X선 회절 측정 결과로부터 몇몇 회절 피크가 발견되었으며, 이의 각( $2\theta$ )으로부터 CuO 결정이 비교예 3의 산화물에 존재함이 밝혀졌다. 산소가 가열 처리 동안 상기 막 내에 들어감으로써 CuO가 생성되었다고 여겨진다.

- [0343] 본 발명의 p형 산화물 막을 다양한 반도체 소자에서 사용할 수 있지만, 반도체 소자 중 반도체에 요구되는 특성 (저항률)은 일반적으로 반도체 소자의 유형 및 특성에 따라 달라진다. 따라서, Sn/Cu 몰비의 값은 의도된 목적에 따라 적절하게 선택할 수 있다.

- [0344] 비교예 3의 샘플의 Au 전극들 사이에서 측정한 전류-전압(I-V) 특성은 선형 관계를 나타내지 않았으며, 샘플은 저항률이 높았고, 즉, 체적 저항률이  $10^{13} \Omega\text{cm}$  이상이었다. Cu가 2가인 다량의 CuO 결정이 상기 막에 함유되었기 때문에 충분한 전기 전도성이 수득되지 않았던 것으로 여겨진다.

- [0345] 구체적으로, 결정성 Cu-Sn 산화물은 p형 전기 전도성을 제어할 수 없었다.

- [0346] (실시예 18)

- [0347] <Cu-Sn 산화물 막(무정형)의 제조>

- [0348] 10 mL의 에틸렌 글리콜 중에, 2.42 g(10 mmol에 상응함)의 질산구리 3수화물을 용해시킴으로써 구리 원료 용액을 제조하였다. 더 나아가, 1.9 g(10 mmol에 상응함)의 염화주석을 10 mL의 프로필렌 글리콜에 용해시킴으로써 주석 원료 용액을 제조하였다.

- [0349] 구리 원료 용액(5 mL) 및 주석 원료 용액(0.9 mL)을 혼합하고 교반시킴으로써 Cu-Sn 산화물용 잉크를 제조하였다. 잉크 중 Cu 몰과 잉크 중 Sn 몰의 비(Sn/Cu 몰비)는 18%였다.

- [0350] 다음, 유리 기판을 스핀 코팅에 의해 Cu-Sn 산화물용 잉크로 코팅하였다. 120°C에서 1시간 동안 잉크를 건조시킨 후, 산소 기류 중에서 엑시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 Cu-Sn 산화물 막(p형 산화물 막)을 형성하였다. 수득한 막 중 Sn/Cu 몰비는 18%였으며, 실시예 14의 것과 동일한 조성을 갖는 막이 형성되었다.

- [0351] 상기 막의 막 두께 및 체적 저항률을 실시예 11에서와 동일한 방식으로 측정하였다. 그 결과, 막 두께는 98 nm였으며, 체적 저항률은  $1.12 \times 10^3 \Omega\text{cm}$ 였다. 상기 막의 체적 저항률은 실시예 14의 p형 막의 체적 저항률( $9.53 \times 10^2 \Omega\text{cm}$ )과 유사함이 확인되었다. 따라서, 심지어 상이한 유형의 Cu 함유 화합물, Sn 함유 화합물 및 용매를 잉크의 제형화 동안 사용할 경우에도, Cu와 Sn의 몰비가 동일하기만 하다면 실질적으로 유사한 전기 전도성 특성을 갖는 p형 산화물 막이 수득될 수 있음이 확인되었다.

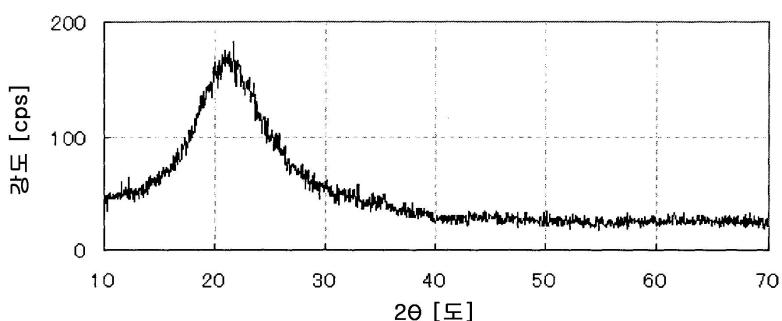

- [0352] 실시예 18에서 수득한 막에서 수행한 X선 회절 측정 결과가 도 35에 제시되어 있다. 도 35에 제시된 바와 같이, 실시예 18에서 수득한 막이 또한 무정형 상태로 있음이 확인되었다.

- [0353] (실시예 19)

- [0354] <pn 접합 다이오드의 제조>

- [0355] -기판의 제조-

- [0356] 기판에 대해서는, 비알칼리 유리 기판(판 두께: 0.7 mm)을 사용하였다. 중성 세제, 순수 및 이소프로필 알코올

을 사용하여 초음파 세정함으로써 유리 기판을 세척하였다. 기판의 건조 후, 기판은 90°C에서 10분 동안 UV-오존 처리를 추가로 수행하였다.

[0357] -캐소드의 형성-

유리 기판에서, 금속 마스크를 통하여 기상 증착에 의해 100 nm의 두께로 Al을 증착시킴으로써 캐소드를 형성하였다.

[0359] -n형 반도체층의 형성-

캐소드 상에, 금속 마스크를 통하여 무선 주파수 스퍼터링에 의해 Mg-In 산화물 막을 형성시켰다. 표적으로서,  $In_2MgO_4$ 의 조성을 갖는 다결정성 소결체(크기(직경: 4 인치)를 사용하였다. 스퍼터링 챔버 내의 최종 압력을  $2 \times 10^{-5}$  Pa로 설정하였다. 스퍼터링 동안의 아르곤 가스 및 산소 가스의 유량을 제어하여 1.0 Pa의 총 압력 및  $6.0 \times 10^{-2}$  Pa의 산소 분압을 달성하였다. 기판의 온도는 스퍼터링 동안 특별히 제어하지 않았다. 전력 및 스퍼터링의 지속 시간을 각각 150 W 및 15분으로 조정함으로써 두께가 160 nm인 Mg-In 산화물 막을 형성하였다.

[0361] -p형 반도체층의 형성-

n형 반도체층 상에 Cu-Sn 산화물 막(Sn/Cu 몰비: 12.5%)을 실시예 13에서와 동일한 방식으로 형성하였다. Cu-Sn 산화물 막의 두께는 45.5 nm였다.

[0363] -애노드의 형성-

p형 반도체층 상에 Au를 금속 마스크를 통하여 기상 증착에 의해 100 nm의 두께로 증착시킴으로써 애노드를 형성하였다.

[0365] 상기에 기술한 공정에 의해 pn 접합 다이오드를 수득하였다.

[0366] <평가>

[0367] 실시예 19에서 수득한 다이오드의 전류-전압(I-V) 특성을 측정하였다. 그 결과가 도 36에 제시되어 있다. 상기 결과로부터, 전형적인 정류성이 수득됨이 밝혀졌다. 구체적으로, 상기 결과는 본 발명의 p형 산화물을 활성층으로서 사용함으로써 pn 접합 다이오드가 실현될 수 있음을 나타냈다.

[0368] (실시예 20)

[0369] <전계 효과 트랜지스터의 제조>

[0370] -기판(게이트 전극, 게이트 절연층)의 제조-

[0371] 기판에 대해서는, 열산화된 막(두께: 200 nm)을 포함하는 Si 기판을 사용하였다. 중성 세제, 순수 및 이소프로필 알코올을 사용하여 초음파 세정함으로써 Si 기판을 세척하였다. 기판의 건조 후, 상기 기판에서 90°C에서 10분 동안 UV-오존 처리를 추가로 수행하였다. 열산화된 막은 게이트 절연층이며, Si 기판은 게이트 전극임에 유의한다.

[0372] -활성층의 형성-

[0373] 실시예 11에서 제조한 Cu-Sn 산화물 막(Sn/Cu 몰비: 2.5%)용 잉크를 스판 코팅에 의해 상기 기판 상에 적용하였다. 120°C에서 1시간 동안 잉크를 건조시킨 후, 산소 기류 중에서 엑시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 평균 두께가 49 nm인 Cu-Sn 산화물 막(Sn/Cu 몰비: 2.5%)을 형성하였다.

[0374] 그 후, 포토레지스트를 그 위에 적용하고, 코팅된 포토레지스트를 예비베이킹하고, 노광 장비에 의해 노광시키고, 현상함으로써, 형성시킬 활성층과 동일한 패턴을 갖는 레지스트 패턴을 형성하였다. 더 나아가, 레지스트 패턴이 형성되지 않은 영역 내의 Cu-Sn 산화물 막을 습식 에칭에 의해 제거하고, 이어서 레지스트 패턴을 제거함으로써 활성층을 형성하였다.

[0375] -소스 전극 및 드레인 전극의 형성-

[0376] 금속 마스크를 통하여 기상 증착에 의해 활성층 상에 Cr을 1 nm의 두께로 증착시키고 이어서 Au를 100 nm의 두께로 증착시킴으로써 소스 전극 및 드레인 전극을 형성하였다. 이의 채널 길이는 50  $\mu\text{m}$ 였으며, 이의 채널 폭은

0.4 mm였다.

[0377] <평가>

[0378] 실시예 20에서 제조한 전계 효과 트랜지스터의 전달 특성( $V_{ds} = -20$  V)을 측정하였으며, 이의 결과는 보통은 오프인 타입의 탁월한 p형 특성을 나타냈다.

[0379] (실시예 21)

[0380] <전계 효과 트랜지스터의 제조>

[0381] -기판(게이트 전극, 게이트 절연층)의 제조-

[0382] 기판에 대해서는, 열산화된 막(두께: 200 nm)을 포함하는 Si 기판을 사용하였다. 중성 세제, 순수 및 이소프로필 알코올을 사용하여 초음파 세정함으로써 Si 기판을 세척하였다. 기판의 건조 후, 상기 기판에서 90°C에서 10분 동안 UV-오존 처리를 추가로 수행하였다. 열산화된 막은 게이트 절연층이며, Si 기판은 게이트 전극임에 유의한다.

[0383] -소스 전극 및 드레인 전극의 형성-

[0384] 열산화된 막을 포함하는 Si 기판 상에 헥사메틸디실라잔(HMDS)을 스판 코팅, 이어서 건조 공정에 의해 적용함으로써 기판의 표면에 소수화 처리를 제공하였다. 그 후, 리프트오프용의 하층 레지스트를 스판 코팅 및 건조 공정에 의해 형성하였다. 하층 레지스트 상에, 감광성 포토레지스트를 스판 코팅 및 건조 공정에 의해 형성시켰다. 포토마스크를 통한 노광을 통하여 레지스트를 패터닝하고 현상한 후, 전극 재료인 Pt의 막을 DC 스퍼터링에 의해 형성시켰다. 표적으로서, Pt(크기(직경): 4 인치)를 사용하였다. 스퍼터링 챔버 내의 최종 압력을  $1 \times 10^{-3}$  Pa로 설정하였다. 스퍼터링 동안 아르곤 기류를 공급하였으며, 압력을 0.35 Pa로 설정하였다. 기판의 온도는 스퍼터링 동안 특별히 제어하지 않았다. 전력 및 스퍼터링의 지속 시간을 각각 DC 200 W 및 6분 15초로 조정함으로써 두께가 50 nm인 Pt 막을 형성하였다.

[0385] 그 후, Pt 막을 형성한 기판을 N-메틸페롤리돈에 침지시켜 원하지 않는 부분의 Pt를 레지스트와 함께 제거함으로써 의도한 형상의 Pt 소스 전극 및 Pt 드레인 전극을 수득하였다.

[0386] -잉크젯 인쇄용 반도체 잉크의 제조-

[0387] 10 mL의 에틸렌 글리콜 중에, 2.42 g(10 mmol에 상응함)의 질산구리 3수화물을 용해시킴으로써 구리 원료 용액을 제조하였다. 더 나아가, 1.90 g(10 mmol에 상응함)의 염화주석을 10 mL의 에틸렌 글리콜에 용해시킴으로써 주석 원료 용액을 제조하였다.

[0388] 에틸렌 글리콜(2.25 mL), 에틸렌 글리콜 모노부틸 에테르(4.5 mL), 상기 구리 원료 용액(2 mL), 및 상기 주석 원료 용액(0.25 mL)을 혼합하고 교반시킴으로써 잉크젯 인쇄용 반도체 잉크(Cu-Sn 반도체 잉크)를 제조하였다. 잉크 중 Cu 몰과 잉크 중 Sn 몰의 비(Sn/Cu 몰비)는 12.5%였다.

[0389] -활성층의 형성-

[0390] Cu-Sn 반도체 잉크(Sn/Cu 몰비: 12.5%)를 잉크젯 장비에 의해 소스-드레인 전극을 형성한 의도된 기판 영역 상에 적용하였다. 120°C에서 1시간 동안 잉크를 건조시킨 후, 엑시머 램프(파장: 222 nm)로부터 방출되는 광을 적용하면서 잉크를 250°C에서 3시간 동안 베이킹함으로써 두께가 48 nm인 Cu-Sn 산화물 막(Sn/Cu 몰비: 12.5%)을 형성하였다.

[0391] 마지막으로, 어닐링을 300°C에서 1시간 동안 수행함으로써 전계 효과 트랜지스터를 제조하였다.

[0392] 전계 효과 트랜지스터의 채널 영역의 현미경 사진을 도 37에 나타낸다. 소스 전극(23)과 드레인 전극(24) 사이의 공간이 채널 길이이며, 이는 50  $\mu$ m였다. 채널 폭은 종방향 라인의 형상으로 적용된 활성층(22)의 폭에 의해 규정하였으며, 상기 사진의 전계 효과 트랜지스터에서 채널 폭은 54  $\mu$ m였다.

[0393] <평가>

[0394] 실시예 21에서 제조한 전계 효과 트랜지스터의 전달 특성( $V_{ds} = -20$  V)을 측정하였으며, 이의 결과는 보통은 오프인 타입의 탁월한 p형 특성을 나타냈다. 스판 코팅에 의해 Cu-Sn 산화물 막(Sn/Cu 몰비: 2.5%)을 형성시키고 이어서 습식 에칭에 의해 의도된 형상을 갖도록 막을 가공한 실시예 20과 비교하여, 실시예 21에서는 잉크젯 인

쇄에 의해 단지 의도된 영역 내에 Cu-Sn 산화물 막(Sn/Cu 몰비: 12.5%)을 형성시켰기 때문에 실시예 21에서는 이후의 단계에서 패터닝 없이 더욱 간단한 방법에 의해 전계 효과 트랜지스터를 제조하였다.

[0395] 본 발명의 실시형태는 예를 들어 하기와 같다:

[0396] <1>

[0397] 산화물을 포함하고 무정형인 p형 산화물로서,

[0398] 산화물은

[0399] Cu, 및

[0400] p 블록 원소로부터 선택되고, 이온으로서 존재할 때 평형 상태로 존재할 수 있는 원소 M으로서, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M

[0401] 을 포함하는 것인 p형 산화물.

[0402] <2>

[0403] <1>에 있어서, 원소 M은 Sb, 또는 Sn, 또는 이들 둘 다를 포함하는 것인 p형 산화물.

[0404] <3>

[0405] <1> 또는 <2>에 따른 p형 산화물의 제조에 사용되는 p형 산화물 제조용 조성물로서,

[0406] 용매,

[0407] Cu 함유 화합물, 및

[0408] 원소 M 함유 화합물로서, 원소 M은 p 블록 원소로부터 선택되고, 이온으로 존재할 때 평형 상태로 존재할 수 있으며, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M 함유 화합물

[0409] 을 포함하는 p형 산화물 제조용 조성물.

[0410] <4>

[0411] <1> 또는 <2>에 따른 p형 산화물을 제조하는 방법으로서,

[0412] 조성물을 지지체 상에 도포하는 단계, 및

[0413] 상기 도포 후 열처리를 수행하는 단계

[0414] 를 포함하고, 여기서 조성물은

[0415] 용매,

[0416] Cu 함유 화합물, 및

[0417] 원소 M 함유 화합물로서, 원소 M은 p 블록 원소로부터 선택되고, 이온으로 존재할 때 평형 상태로 존재할 수 있으며, 평형 상태는 최외각의 p 궤도의 모든 전자가 상실된 상태와 최외각의 모든 전자가 상실된 상태 둘 모두가 존재하는 상태인 것인 원소 M 함유 화합물

[0418] 을 포함하는 것인 방법.

[0419] <5>

[0420] 활성층을 포함하는 반도체 소자로서,

[0421] 활성층은 <1> 또는 <2>에 따른 p형 산화물을 포함하는 것인 반도체 소자.

[0422] <6>

[0423] <5>에 있어서, 상기 반도체 소자는 다이오드이고, 여기서 다이오드는

[0424] 제1 전극,

- [0425] 제2 전극, 및

- [0426] 제1 전극과 제2 전극 사이에 형성된 활성층

- [0427] 을 포함하는 것인 반도체 소자.

- [0428] <7>

- [0429] <5>에 있어서, 상기 반도체 소자는 전계 효과 트랜지스터이고, 여기서 전계 효과 트랜지스터는

- [0430] 게이트 전압을 인가하도록 구성된 게이트 전극,

- [0431] 둘 다 전류를 추출하도록 구성된 소스 전극 및 드레인 전극,

- [0432] 소스 전극과 드레인 전극 사이에 형성된 활성층, 및

- [0433] 게이트 전극과 활성층 사이에 형성된 게이트 절연층

- [0434] 을 포함하는 것인 반도체 소자.

- [0435] <8>

- [0436] 광 출력이 구동 신호에 상응하여 제어되는 광 제어 소자, 및

- [0437] <5>에 따른 반도체 소자를 포함하고 광 제어 소자를 구동하도록 구성된 구동 회로

- [0438] 를 포함하는 표시 소자.

- [0439] <9>

- [0440] <8>에 있어서, 광 제어 소자는 유기 전계발광 소자, 전기변색 소자, 액정 소자, 전기영동 소자 또는 전기습윤 소자를 포함하는 것인 표시 소자.

- [0441] <10>

- [0442] 영상 데이터에 상응하는 영상을 표시하는 영상 표시 장치로서,

- [0443] 매트릭스 중에 정렬되어 있는, 각각 <8>에 따른 복수의 표시 소자,

- [0444] 각각의 표시 소자 내의 각각의 전계 효과 트랜지스터에 게이트 전압 및 신호 전압을 별도로 인가하도록 구성된 복수의 라인, 및

- [0445] 영상 데이터에 상응하는, 라인을 통하여 각각의 전계 효과 트랜지스터의 게이트 전압 및 신호 전압을 개별적으로 제어하도록 구성된 표시 제어 장치

- [0446] 를 포함하는 영상 표시 장치.

- [0447] <11>

- [0448] <10>에 따른 영상 표시 장치, 및

- [0449] 표시될 영상 정보를 기반으로 하는 영상 데이터를 형성하고 영상 데이터를 영상 표시 장치에 출력하도록 구성된 영상 데이터 형성 장치

- [0450] 를 포함하는 시스템.

### 부호의 설명

- [0451] 2: 캐소드

- 3: n형 반도체층

- 4: p형 반도체층

- 5: 애노드

- 6: pn 접합 다이오드

10: 전계 효과 트랜지스터

20: 전계 효과 트랜지스터

22: 활성층

23: 소스 전극

24: 드레인 전극

25: 게이트 절연층

26: 게이트 전극

40: 전계 효과 트랜지스터

302, 302': 표시 소자

310: 디스플레이

320, 320': 구동 회로

370: 액정 소자

400: 표시 제어 장치

**도면****도면1****도면2**

도면3

도면4

도면5

## 도면6

## 도면7

도면8

도면9

도면10

## 도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

도면28

도면29

도면30

도면31

도면32

도면33

도면34

도면35

도면36

도면37