(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

22 March 2007 (22.03.2007)

PCT

(10) International Publication Number

WO 2007/031704 A1(51) International Patent Classification:

G09G 3/32 (2006.01)

(74) Agent: TURNBULL, Alexander; Cambridge Display Technology Limited, c/o IP Department, Building 2020, Cambourne Business Park, Cambridgeshire CB23 6DW (GB).

(21) International Application Number:

PCT/GB2006/003171

(22) International Filing Date: 25 August 2006 (25.08.2006)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

0518541.8 12 September 2005 (12.09.2005) GB

(71) Applicant (for all designated States except US): CAMBRIDGE DISPLAY TECHNOLOGY LIMITED [GB/GB]; c/o IP Department, Building 2020, Cambourne Business Park, Cambridgeshire CB23 6DW (GB).

(72) Inventors; and

(75) Inventors/Applicants (for US only): ROUTLEY, Paul [GB/GB]; 17 Haddows Close, Longstanton, Cambridge Cambridgeshire CB4 5DJ (GB). SMITH, Euan [GB/GB]; c/o IP Department, Cambridge Display Technology Ltd, Building 2020, Cambourne Business Park, Cambourne Cambridgeshire CB23 6DW (GB).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Published:

— with international search report

[Continued on next page]

(54) Title: ACTIVE MATRIX DISPLAY DRIVE CONTROL SYSTEMS

WO 2007/031704 A1

(57) Abstract: This invention relates to methods, apparatus, and computer program code for driving an active matrix display, in particular an organic light emitting diode (OLED) display, with reduced power consumption. A method of reducing the power consumption of an active matrix electroluminescent display, the method comprising: controlling a power supply voltage to the display; and monitoring a power supply current to the display; and wherein said controlling further comprises progressively reducing said power supply voltage until said power supply current reduces by greater than a threshold.

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

Active Matrix Display Drive Control Systems

This invention relates to methods, apparatus, and computer program code for driving an active matrix display, in particular an organic light emitting diode (OLED) display, with reduced power consumption.

Displays fabricated using OLEDs provide a number of advantages over LCD and other flat panel technologies. They are bright, colourful, fast-switching (compared to LCDs), provide a wide viewing angle and are easy and cheap to fabricate on a variety of substrates. Organic (which here includes organometallic) LEDs may be fabricated using materials including polymers, small molecules and dendrimers, in a range of colours which depend upon the materials employed. Examples of polymer-based organic LEDs are described in WO 90/13148, WO 95/06400 and WO 99/48160; examples of dendrimer-based materials are described in WO 99/21935 and WO 02/067343; and examples of so called small molecule based devices are described in US 4,539,507.

A typical OLED device comprises two layers of organic material, one of which is a layer of light emitting material such as a light emitting polymer (LEP), oligomer or a light emitting low molecular weight material, and the other of which is a layer of a hole transporting material such as a polythiophene derivative or a polyaniline derivative.

Organic LEDs may be deposited on a substrate in a matrix of pixels to form a single or multi-colour pixellated display. A multicoloured display may be constructed using groups of red, green, and blue emitting pixels. So-called active matrix (AM) displays have a memory element, typically a storage capacitor and a transistor, associated with each pixel whilst passive matrix displays have no such memory element and instead are repetitively scanned to give the impression of a steady image. Examples of polymer and small-molecule active matrix display drivers can be found in WO 99/42983 and EP 0,717,446A respectively.

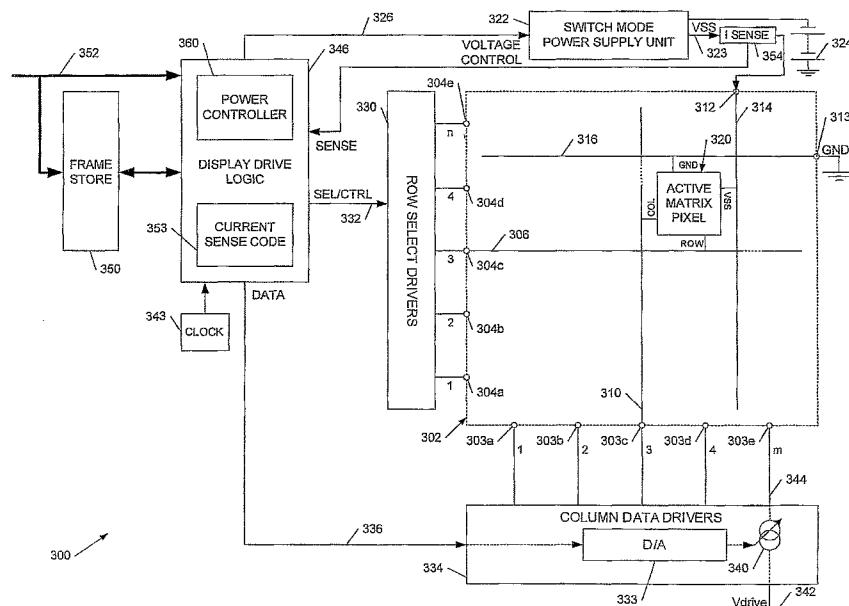

Figure 1a shows such an example OLED active matrix pixel circuit 150. A circuit 150 is provided for each pixel of the display and ground 152,  $V_{ss}$  154, row select 124 and column data 126 busbars are provided interconnecting the pixels. Thus each pixel has a power and ground connection and each row of pixels has a common row select line 124 and each column of pixels has a common data line 126.

Each pixel has an organic LED 152 connected in series with a driver transistor 158 between ground and power lines 152 and 154. A gate connection 159 of driver transistor 158 is coupled to a storage capacitor 120 and a control transistor 122 couples gate 159 to column data line 126 under control of row select line 124. Transistor 122 is a thin film field effect transistor (FET) switch which connects column data line 126 to gate 159 and capacitor 120 when row select line 124 is activated. Thus when switch 122 is on a voltage on column data line 126 can be stored on a capacitor 120. This voltage is retained on the capacitor for at least the frame refresh period because of the relatively high impedances of the gate connection to driver transistor 158 and of switch transistor 122 in its “off” state.

Driver transistor 158 is typically an FET transistor and passes a (drain-source) current which is dependent upon the transistor’s gate voltage less a threshold voltage. Thus the voltage at gate node 159 controls the current through OLED 152 and hence the brightness of the OLED.

The voltage-controlled circuit of Figure 1 suffers from a number of drawbacks, and some ways to address these are described in the applicant’s WO03/038790.

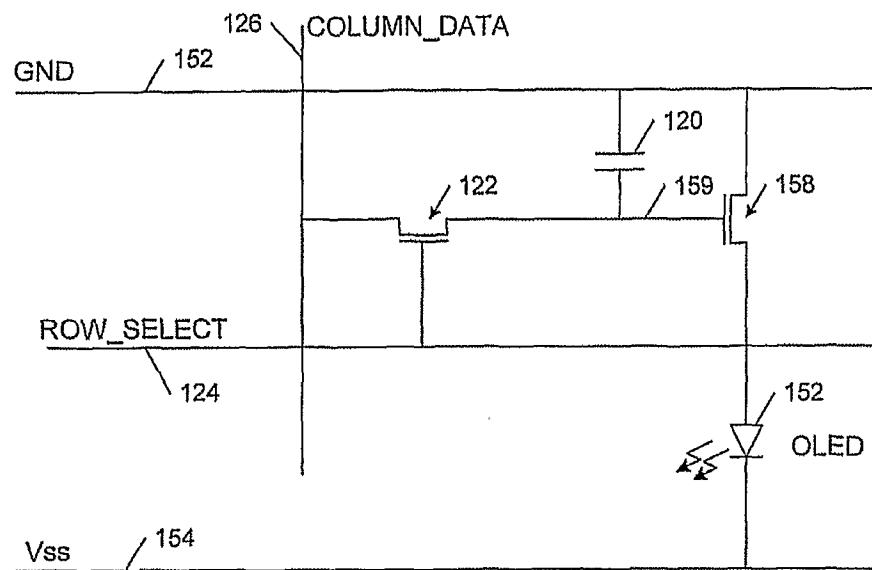

Figure 1b, taken from WO03/038790, shows an example of a current-controlled pixel driver circuit 160 which addresses these problems. In this circuit the current through an OLED 152 is set by setting a drain source current for OLED driver transistor 158 using a reference current sink 162 and memorising the driver transistor gate voltage required for this drain-source current. Thus the brightness of OLED 152 is determined by the current,  $I_{col}$ , flowing into reference current sink 162, which is preferably adjustable and set as desired for the pixel being addressed. In addition, a further switching transistor

164 is connected between drive transistor 158 and OLED 152. In general one current sink 162 is provided for each column data line.

It can be seen from these examples that an active matrix pixel circuit generally incorporates a thin film (driver) transistor (TFT) in series with an electroluminescent display element.

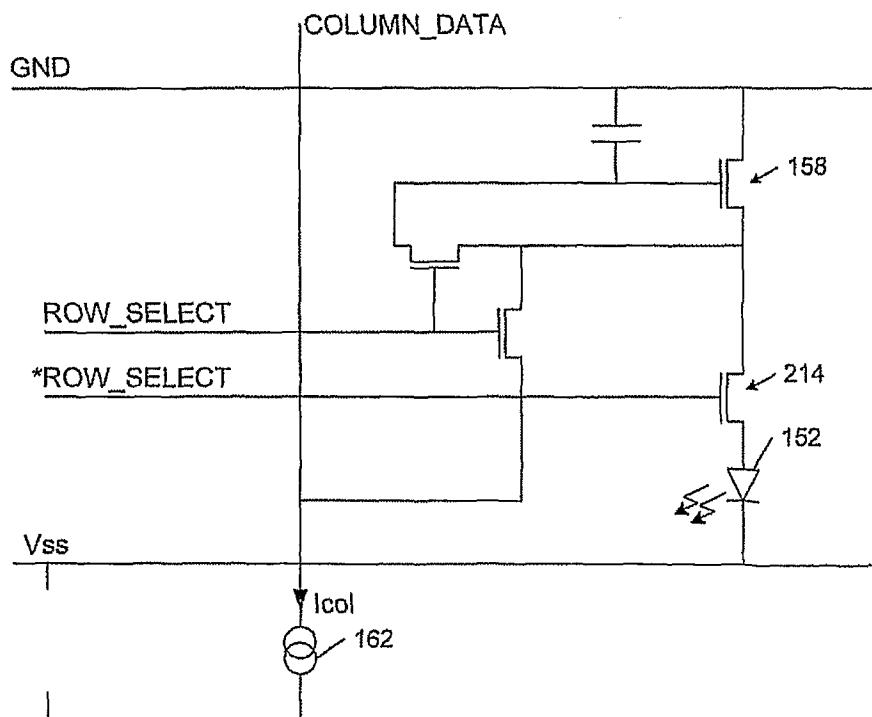

Referring now to Figure 2a, this shows drain characteristics 200 for a FET TFT driver transistor of an active matrix pixel circuit. A set of curves 202, 204, 206, 208 is shown each illustrating the variation of drain current of the FET with drain-source voltage for a particular gate-source voltage. After an initial non-linear portion the curves become substantially flat, and the FET operates in the so-called saturation region. With increasing gate-source voltage the saturation drain current increases; below a threshold gate-source voltage  $V_T$  the drain current is substantially 0. Typical values of  $V_T$  are between 1V and 6V. Broadly speaking the FET acts as a voltage controlled current limiter.

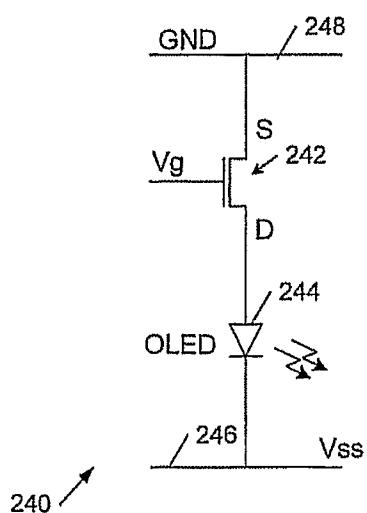

Figure 2b shows a drive portion 240 of a typical active matrix pixel circuit. A PMOS driver FET 242 is connected in series with an organic light emitting diode 244 between a ground line 248 and a negative power line  $V_{ss}$  246.

It will be appreciated from the circuit of Figure 2b that, for a given OLED drive current, the greater  $V_{ss}$  the greater the excess (waste) power dissipation in driver transistor 242. It is therefore preferable to reduce  $V_{ss}$  as much as possible to reduce this excess dissipated power. However it can be appreciated from graph 220 that there is a limit, as indicated by dashed line 230, below which  $V_{ss}$  may not be reduced, this limit being determined by the maximum available  $V_{gs}$  and the required OLED drive voltage.

In an active matrix driver multiple factors contribute to increasing the supply voltage of an AM OLED display above that which is necessary at a given time. In principle a supply voltage might only need to be ~0.5V above that required to drive the highest voltage OLED (~4V for polymer, ~7V for small molecule and phosphorescent systems). However in practice the supply needs to be sufficient to hold the drive TFT in

saturation, and possess enough overhead to cope with increases in OLED threshold voltage with time which can result in supply voltages as high as 14V for small molecule. This extra voltage is dropped entirely over the drive TFT increasing (doubling in the example given) the power consumption and stressing the TFT both with the enhanced field drop and heating. We have previously described, in WO03/107313, some techniques for addressing these difficulties.

According to the present invention there is therefore provided a method of reducing the power consumption of an active matrix electroluminescent display, the method comprising: controlling a power supply voltage to the display; and monitoring a power supply current to the display; and wherein said controlling further comprises progressively reducing said power supply voltage until said power supply current reduces by greater than a threshold.

In embodiments this method provides enhanced efficiency of the display and reduced stress on the drive thin film transistor. This also helps to reduce threshold voltage drift with time. Thus, broadly speaking embodiments of the method provide reduced power consumption and/or increased display lifetime.

The current threshold may be an absolute current value threshold or a relative threshold such as a percentage (such as 90 percent) of a saturation current determined as, for example, a current value which is substantially constant for small changes in supply voltage. Alternatively the threshold may be defined in terms of a rate of reduction of supply current – that is, for example, a percentage change in supply current with a step reduction in supply voltage. In a further alternative a response curve of an active matrix pixel (drive transistor and electroluminescent display element) may be stored, for example in non-volatile memory, and the threshold determined by a position on such a characteristic curve, which may in turn be determined by the monitored power supply current.

Preferably the monitoring and controlling maintains the active matrix display in an operating region in which a highest driven driver transistor (that is, a driver transistor with a maximum drive) is just within saturation. Preferably the monitoring and

controlling is performed substantially continuously, for example in a computer program controlled feedback loop.

Where the active matrix display is a multi-coloured display with at least two, and preferably three sub-pixels of different colours each of the sub-pixels may be provided with a different respective power supply line so that the power supplies for the different sub-pixels may be controlled substantially independently. This is advantageous because, in general, different colour sub-pixels have different threshold voltages and by driving them from separate power supply lines a separate optimisation may be supplied for each. Additionally or alternatively different spatially separate regions of the display may be provided with their own respective power supply lines for separate respective power supply control along the lines outlined above. This may be advantageous where, for example, different regions of the display are substantially dedicated to different tasks.

In embodiments the method also controls a drive level to one or more pixels of the display. This allows a further reduction in power supply voltage providing the drive level of one or more pixels, which might otherwise be brought out of saturation is increased to compensate.

In a related aspect the invention provides a controller for an active matrix electroluminescent display driver, the display having a plurality of pixels each with an electroluminescent display element and an associated drive transistor, the display having a power supply line for providing power to the driver transistors of said pixels; the driver comprising a pixel data driver to drive said display pixels with data for display, a controllable voltage power supply to provide a power supply to said power supply line, and a current sensor to sense a current in said power supply line; the controller comprising: a current sense input for said current sensor; a voltage control output for said controllable power supply; and a voltage controller to provide a voltage control signal for said voltage control output responsive to a current sense signal from said current sense input.

Preferably the voltage controller is configured to adjust the power supply control signal to progressively reduce the sensed current to a threshold point, and to then adjust the control signal to maintain the sensed current in the region of this threshold point.

Generally the power supply voltage is determined with respect to a ground line of the active matrix display, although it may in principle be determined with respect to some other power supply line. Optionally the driver may include a voltage sensor to sense the power supply voltage and to provide an input to the controller which may be used, for example, to facilitate determination of an operating point of the display. In this case the control output may also be responsive to the sensed power supply voltage.

As mentioned above, the display may have a plurality of power supply lines driving different portions of the display such as different sub-pixels or different spatially separate regions of the display, in which case the controller (or separate controllers) may control the power supply voltage to each separate power supply line. Optionally, as mentioned above, the pixel drive data may be adjusted in coordination with the voltage control signal, in particular to compensate (the hardest or highest driven drive transistors) for a reduction in power supply voltage.

The invention further provides an active matrix electroluminescent display driver incorporating the above described controller in combination with the above described pixel data driver, controllable voltage power supply, and current sensor.

In all of the above aspects of the invention the electroluminescent display device preferably comprises an organic light emitting diode-based display such as a small molecule, polymer and/or dendrimer-based display.

In a further aspect the invention provides an active matrix OLED display as claimed in claim 18 wherein each said pixel comprises at least first and second sub-pixels of different colours, and wherein said two portions comprises said first and second sub-pixels respectively.

The invention further provides a carrier medium carrying processor control code to implement the above described methods and display drivers. This code may comprise

conventional program code, for example source, object or executable code in a conventional programming language (interpreted or compiled) such as C, or assembly code, code for setting up or controlling an ASIC (Application Specific Integrated Circuit) or FPGA (Field Programmable Gate Array), or code for a hardware description language such as Verilog (Trade Mark) or VHDL (Very high speed integrated circuit Hardware Description Language). Such code may be distributed between a plurality of coupled components. The carrier medium may comprise any conventional storage medium such as a disk or programmed memory (for example firmware such as Flash RAM or ROM), or a data carrier such as an optical or electrical signal carrier.

These and other aspects of the of the invention will now be further described, by way of example only, with the reference to the accompanying figures in which:

Figure 1 shows an example of an active matrix OLED pixel circuit;

Figures 2a and 2b show, respectively drain characteristics for a TFT driver transistor of an active matrix pixel circuit, and a drive portion of a generalised active matrix pixel circuit;

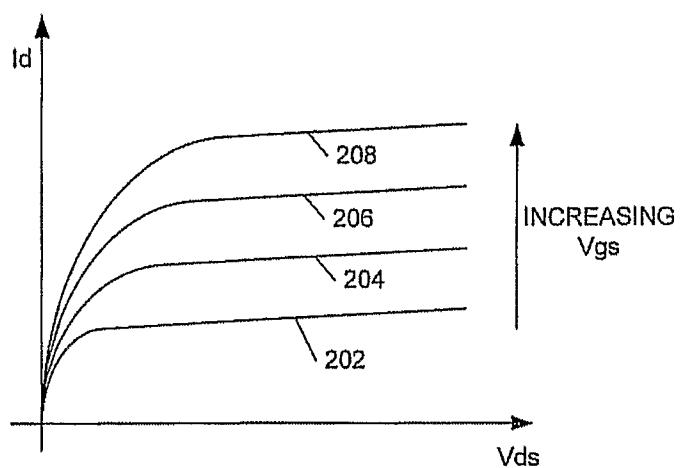

Figure 3 shows an active matrix display driver according to an embodiment of the present invention; and

Figure 4 shows a flow diagram of a power supply voltage control procedure for the driver of figure 3.

Broadly speaking we will describe a technique for reducing power consumption of an active matrix OLED display by means of active monitoring and adjustment of the supply voltage. In outline, test reductions of the supply voltage are made and the current drawn monitored. The voltage at which the current starts to dip significantly is the point at which the highest driven TFT is just within saturation. If the supply voltage is then held at this point then no additional allowance in supply voltage need be made for OLED ageing (and/or temperature effects) and/or possible TFT process/characteristic variations. In embodiments the active supply monitoring

automatically compensates for this over time resulting in lower stresses on the TFTs and a reduced power consumption.

In some preferred embodiments these advantages are enhanced by providing separate monitors and adjustments on red, green and blue sub-pixel power supply lines. This is because the operational voltages of each colour can differ considerably – for example a red sub-pixel may require a drive voltage of 3.6V while a green sub-pixel may require 4.2V and a blue sub-pixel 5.15V in which case a power supply voltage of at least 6.15V (allowing 1V overhead for driver transistor compliance and other losses) might be needed were only a single power supply line used. Alternatively, where two of the sub-pixel colours have a similar IV characteristic (for example the red and green sub-pixels) and only one differs (for example the blue sub-pixel then two rather than three sub-pixel power supplies may be provided). This can simplify electrode line routing on the display glass (substrate), sometimes significantly.

Additionally or alternatively sub-sections of the display may be supplied and monitored separately in applications where peak luminescences and thus drive levels, can vary significantly (and systematically) between different areas of the display, thus enabling further savings to be made.

In addition to the above techniques it can also be possible to drop the supply voltage further and compensate the lower OLED drive currents on some of the drive transistors by increasing the corresponding gate voltages in response. Preferably this is done with knowledge of the (average) electrical characteristics of the drive transistors, so that this information (in effect a graph) can be used to determine an increase in gate voltage needed to compensate a particular supply voltage reduction. Such characteristics may, for example, be stored in non-volatile memory in the driver.

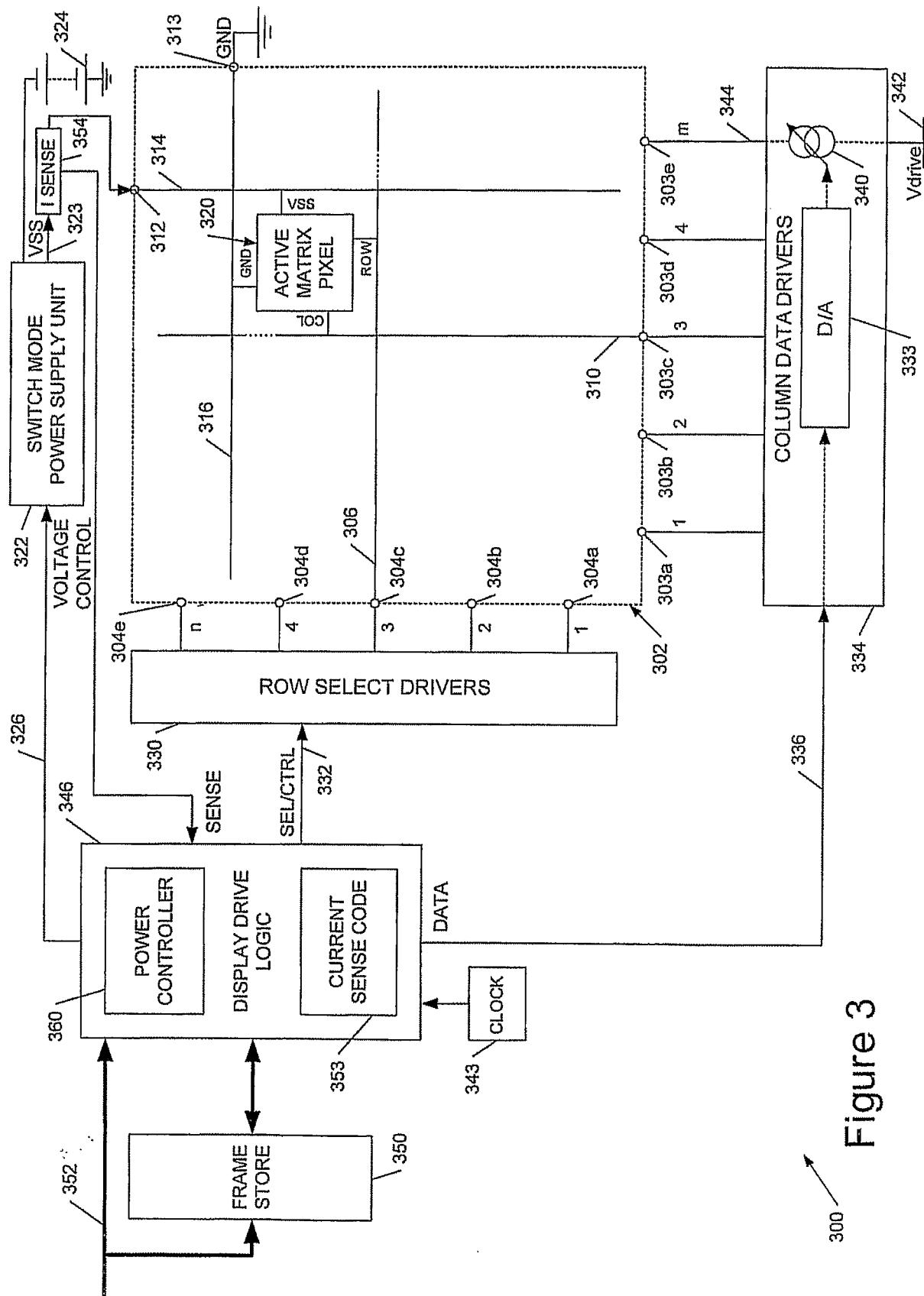

Figure 3 shows a block diagram 300 of a display driver for an active matrix display 302, configured to control  $V_{ss}$  in accordance with the available active matrix pixel drive voltage to increase the power efficiency of the display plus driver combination.

In Figure 3 the active matrix display 302 has a plurality of row electrodes 304a-e and a plurality of column electrodes 308a-e each connecting to internal respective row and column lines 306, 310 of which, for clarity, only two are shown. Power ( $V_{ss}$ ) 312 and ground 318 connections are also provided, again connected to respective internal conducting traces 314 and 316 to provide power to the pixels of the display. For clarity a single pixel 320 is illustrated, connected as shown to  $V_{ss}$ , ground, row, and column lines 314, 316, 306, and 310. It will be recognised that in practice a plurality of such pixels is provided generally, but not necessarily, arranged in a rectangular grid and addressed by row and column electrodes 304, 308. The active matrix pixel 320 may comprise any conventional active matrix pixel driver circuit.

In operation each row of active matrix display 302 is selected in turn by appropriately driving row electrodes 304 and, for each row, the brightness of each pixel in a row is set by driving, preferably simultaneously, column electrodes 308 with brightness data. This brightness data as described above, may comprise either a current or a voltage. Once the brightnesses of the pixels in one row have been set the next row may be selected and the process repeated, the active matrix pixels including a memory element, generally a capacitor, to keep the row illuminated even when not selected. Once data has been written to the entire display, the display only needs to be updated with changes to the brightness of pixels.

Power to the display is provided by a battery 324 and a power supply unit 322 to provide a regulated  $V_{ss}$  output 328. Power supply 322 has a voltage control input 326 to control the voltage on output 328. Preferably power supply 322 is a switch mode power supply with rapid control of the output voltage 328, typically on a microsecond time scale where the power supply operates at a switching frequency 1MHz or greater. Use of a switch mode power supply also facilitates use of a low battery voltage which can be stepped up to the required  $V_{ss}$  level, thus assisting compatibility with, for example low voltage consumer electronic devices.

The row select electrodes 304 are driven by row select drivers 330 in accordance with a control input 332. Likewise the column electrodes 308 are driven by column data drivers 334 in response to a data input 336. In the illustrated embodiment each column

electrode is driven by an adjustable constant current generator 340, in turn controlled by a digital-to-analogue converter 338 coupled to input 336. For clarity only one such constant current generator is shown.

The constant current generator 340 has a current output 344 to source or sink a substantially constant current. The constant current generator 340 is connected to a power supply drive  $V_{drive}$  342, which may be equal and connected to  $V_{ss}$  or which may be greater than (here, more negative than)  $V_{ss}$  to allow active matrix pixel 320 to be driven harder than  $V_{ss}$ . The voltage for  $V_{drive}$  may be provided, for example, by a separate output from power supply unit 322.

The embodiment of the display driver illustrated in Figure 3 shows a current-controlled active matrix display in which a column electrode current is set a pixel brightness. It will be appreciated that a voltage-controlled active matrix display, in which the brightness of a pixel is set by the voltage on a column line, could also be employed by using voltage rather than current drivers for column data drivers 334.

The control input 332 of row select drivers 330 and the data input 336 of column data drivers 334 are both driven by display drive logic circuitry 346 which may, in some embodiments, comprise a microprocessor. The display drive logic 346 is clocked by a clock 348 and, in the illustrated embodiment, has access to a frame store 350. Pixel brightness and/or colour data for display on display 302 is written to display drive logic 346 and/or frame store 350 by means of data bus 352.

The display drive logic has a sense input 356 driven from the output of a current sensing device 354. This may comprise, for example, an analogue-to-digital converter configured to sense the voltage drop across a resistor. This is used to monitor the current drawn by display 302 from output 328 of power supply 322. In embodiments in which a plurality of power supply lines are monitored a plurality of converters or a multiplexed converter may be employed. Optionally (but not shown in Figure 3) the supply voltage  $V_{ss}$  may also be monitored.

The display drive logic 346 (which may be implemented by a processor under stored program control or in hardware or in a combination of the two) includes a current sense unit 358 and a power controller 360 (in this example both implemented by processor control code stored in non-volatile memory). The current sense unit 358 inputs a current signal on sense input 356 and the power controller 360 outputs a voltage control signal to input 326 of power supply unit 322 to control power supply voltage  $V_{ss}$  in response to the sensed input voltage. Operation of the power controller is described in more detail below with reference to Figure 4.

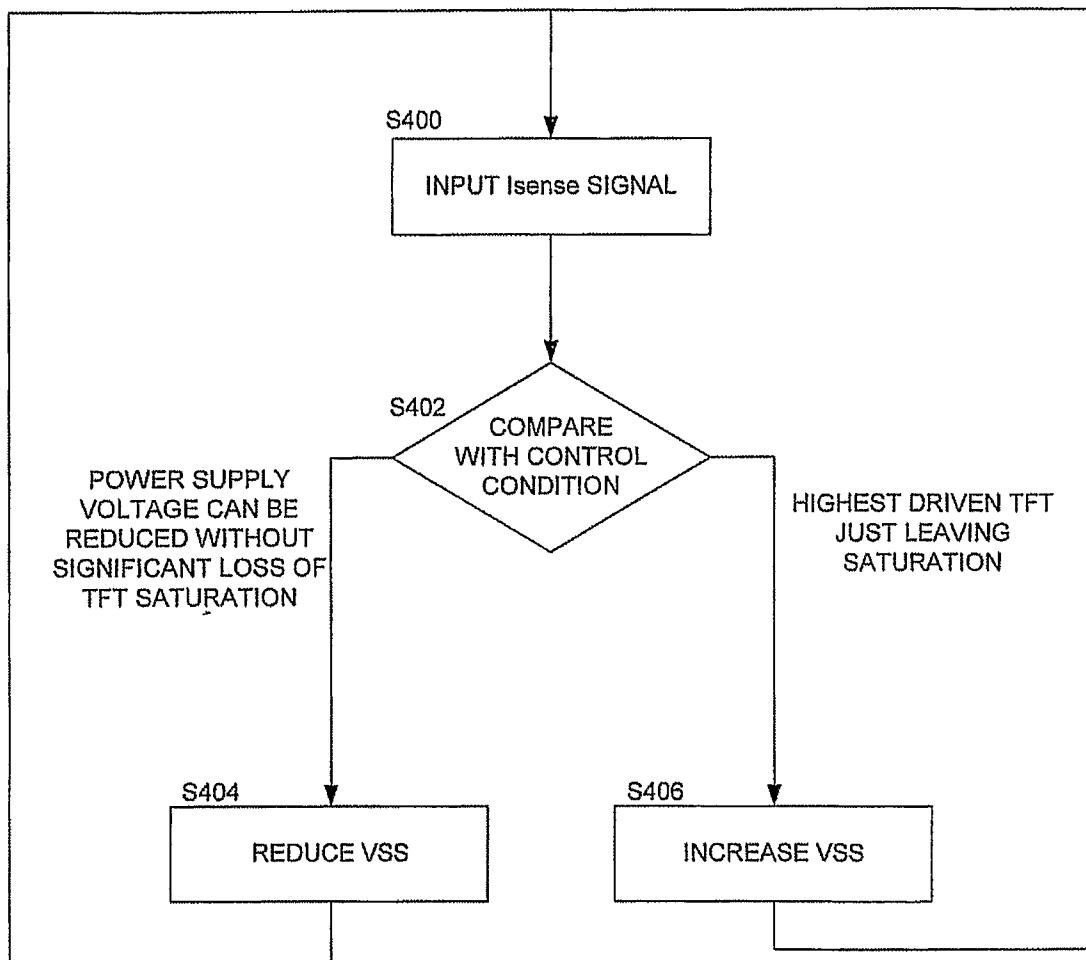

Figure 4 shows a flow diagram of a procedure which may be implemented by power controller 360 in embodiments of a display driver for driving an active matrix display. The general procedure is suitable for both current- and voltage-programmed active matrix displays.

Referring to figure 4, the display controller 346, at step S400, inputs a current sense signal which it then compares (step S402) with a control condition. This control condition comprises a test to determine whether the current has begun to dip significantly and, in one embodiment, may therefore be implemented by determining a change in sensed current since a previous measurement, either in absolute terms or as a percentage, and then comparing this with a threshold such as two percent, five percent, ten percent.

If comparison with the control condition indicates that the power supply voltage can be reduced without significant loss of TFT driver transistor saturation, for example because the change in current is less than a pre-determined threshold, then at step S404  $V_{ss}$  is reduced and the procedure loops back to step S400. If, however, comparison with the control condition indicates that the one or more TFT driver transistors with the highest drive (which should be closest to saturation) are just leaving saturation then, at step S406,  $V_{ss}$  is increased and the procedure again loops back to step S400.

The skilled person will appreciate that a variety of conditions will be employed as the control condition, depending upon the particular application. In embodiments where the active matrix display has two or more separate power supply lines, for example for two

or more separate sub-pixels of the display then separate control loops are shown in figure 4, optionally with different control conditions, may be employed for each separate power supply lines.

No doubt many other effective alternatives will occur to the skilled person. It will be understood that the invention is not limited to the described embodiments and encompasses modifications apparent to those skilled in the art lying within the spirit and scope of the claims appended hereto.

**CLAIMS:**

1. A method of reducing the power consumption of an active matrix electroluminescent display, the method comprising:

- controlling a power supply voltage to the display; and

- monitoring a power supply current to the display; and wherein said controlling further comprises progressively reducing said power supply voltage until said power supply current reduces by greater than a threshold.

2. A method as claimed in claim 1 wherein said active matrix display comprises a plurality of pixels each having a driver transistor; and wherein said monitoring and controlling comprises at least periodically monitoring said power supply current and controlling said power supply voltage to maintain said active matrix display in an operating region in which a highest drive one of said driver transistors is just within saturation.

3. A method as claimed in claim 1 or 2 wherein said active matrix display is a multicolour display, each pixel of the display comprising at least first and second sub-pixels of different colours, first and second sub-pixels having different respective power supply lines, and wherein the method comprises separate said controlling and monitoring of each said sub-pixel power supply line.

4. A method as claimed in claim 1, 2 or 3 wherein said active matrix display has a plurality of spatial sub-divisions, each with a separate respective power supply line, and wherein the method comprises separate said controlling and monitoring of each said spatial sub-division power supply line.

5. A method as claimed in any preceding claim further comprising controlling a drive level to one or more pixels of said display to compensate for said power supply voltage reducing.

6. A carrier carrying the processor control code to implement the method of any preceding claim.

7. An active matrix display driver including the carrier of claim 7.

8. An active matrix display driver for driving an active matrix electroluminescent display, the driver comprising:

- means for controlling a power supply voltage to the display;

- means for monitoring a power supply current to the display; and

- wherein said means for controlling further comprises means for progressively reducing said power supply voltage until said power supply current reduces by greater than a threshold.

9. A controller for an active matrix electroluminescent display driver, the display having a plurality of pixels each with an electroluminescent display element and an associated drive transistor, the display having a power supply line for providing power to the driver transistors of said pixels; the driver comprising a pixel data driver to drive said display pixels with data for display, a controllable voltage power supply to provide a power supply to said power supply line, and a current sensor to sense a current in said power supply line; the controller comprising:

- a current sense input for said current sensor;

- a voltage control output for said controllable power supply; and

- a voltage controller to provide a voltage control signal for said voltage control output responsive to a current sense signal from said current sense input.

10. A controller as claimed in claim 9 wherein said voltage controller is configured to adjust said control signal to progressively reduce said sensed current to a threshold point.

11. A controller as claimed in claim 10 wherein said controller is further configured to adjust said control signal to maintain said sensed current in the vicinity of said threshold point.

12. A controller as claimed in claim 11 wherein said threshold point comprises a point at which a highest drive one of said driver transistors is just within saturation.

13. A controller as claimed in claim 9, 10, 11 or 12 wherein said driver further comprises a voltage sensor to sense a voltage on said power supply line, wherein said controller further comprises a voltage sense input for said voltage sensor; and wherein said voltage control output is responsive to a sensed voltage signal on said voltage sense input.

14. A controller as claimed in any one of claims 9 to 13 wherein said display has a plurality of said power supply lines; wherein said driver is configured to provide a plurality of separately controllable power supplies to said plurality of power supply lines, and to sense current in said plurality of power supply lines; and wherein said controller is configured to separately control a power supply voltage on each of said plurality of power supply lines responsive to a current in the respective line.

15. A controller as claimed in any one of claims 9 to 14 further configured to adjust said pixel drive data in coordination with said voltage control signal.

16. An active matrix electroluminescent display driver including the controller of any one of claims 9 to 15 and said pixel data driver, said controllable voltage power supply, and said current sensor.

17. The method, carrier, controller or display driver as claimed in any preceding claim wherein said active matrix electroluminescent display comprises an OLED display.

18. An active matrix OLED display comprising a plurality of pixels each with an OLED display element and an associated driver transistor, and wherein said display comprises at least two portions with separate power supply lines for providing power to said driver transistor.

19. An active matrix OLED display as claimed in claim 18 wherein each said pixel comprises at least first and second sub-pixels of different colours, and wherein said two portions comprises said first and second sub-pixels respectively.

20. An active matrix OLED display as claimed in claim 18 or 19 wherein said portions include a plurality of spatially separate sub-divisions of said display.

1/4

Figure 1a

(PRIOR ART)

Figure 1b

(PRIOR ART)

2/4

200 ↗

Figure 2a

Figure 2b

3/4

Figure 3

4/4

Figure 4

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/GB2006/003171            |

|                                                      |

|------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. G09G3/32 |

|------------------------------------------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols)<br>G09G |

|---------------------------------------------------------------------------------------------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used) |

|----------------------------------------------------------------------------------------------------------------------------|

|                        |

|------------------------|

| EPO-Internal, WPI Data |

|------------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                    | Relevant to claim No.                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| X         | US 2004/263444 A1 (KIMURA HAJIME [JP])<br>30 December 2004 (2004-12-30)<br><br>paragraphs [0002], [0018], [0048] –<br>[0058], [0069] – [0072], [0086]<br>figures 1,3-7,19<br>-----<br><br>X GB 2 389 951 A (CAMBRIDGE DISPLAY TECH<br>[GB]) 24 December 2003 (2003-12-24)<br>page 1, paragraph 1 – paragraph 3<br>page 13, paragraph 4<br>page 17, paragraph 3 – paragraph 4<br>page 20, paragraph 9<br>page 22, paragraph 1<br>page 26, paragraph 3<br>page 27, paragraph 3<br>figures 2b,7a,8,9<br>-----<br><br>-/- | 1,3,4,<br>6-11,13,<br>14,16-20<br><br>1-4,6-20 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |

|                                                                                                |

|------------------------------------------------------------------------------------------------|

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C. |

|------------------------------------------------------------------------------------------------|

|                                                              |

|--------------------------------------------------------------|

| <input checked="" type="checkbox"/> See patent family annex. |

|--------------------------------------------------------------|

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

|                                                           |

|-----------------------------------------------------------|

| Date of the actual completion of the international search |

|-----------------------------------------------------------|

|                 |

|-----------------|

| 15 January 2007 |

|-----------------|

|                                                    |

|----------------------------------------------------|

| Date of mailing of the international search report |

|----------------------------------------------------|

|            |

|------------|

| 22/01/2007 |

|------------|

|                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL – 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax. (+31-70) 340-3016 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| Authorized officer |

|--------------------|

|                  |

|------------------|

| Ladiray, Olivier |

|------------------|

## INTERNATIONAL SEARCH REPORT

International application No

PCT/GB2006/003171

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                 | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 2003/122813 A1 (ISHIZUKI SHINICHI [JP]<br>ET AL) 3 July 2003 (2003-07-03)<br>paragraphs [0102], [0103]<br>figures 9,10<br>----- | 4,20                  |

| A         | EP 1 450 345 A (PIONEER TOHOKU CORP [JP])<br>25 August 2004 (2004-08-25)<br>the whole document<br>-----                            | 1-20                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                                                   |  |

|---------------------------------------------------|--|

| International application No<br>PCT/GB2006/003171 |  |

|---------------------------------------------------|--|

| Patent document cited in search report |    | Publication date |                            | Patent family member(s)                                                     |  | Publication date                                                   |

|----------------------------------------|----|------------------|----------------------------|-----------------------------------------------------------------------------|--|--------------------------------------------------------------------|

| US 2004263444                          | A1 | 30-12-2004       | NONE                       |                                                                             |  |                                                                    |

| GB 2389951                             | A  | 24-12-2003       | AU<br>EP<br>WO<br>JP<br>US | 2003244794 A1<br>1516310 A2<br>03107313 A2<br>2005530200 T<br>2006038758 A1 |  | 31-12-2003<br>23-03-2005<br>24-12-2003<br>06-10-2005<br>23-02-2006 |

| US 2003122813                          | A1 | 03-07-2003       | AU<br>EP<br>WO<br>TW       | 2002356439 A1<br>1459285 A1<br>03058594 A1<br>575859 B                      |  | 24-07-2003<br>22-09-2004<br>17-07-2003<br>11-02-2004               |

| EP 1450345                             | A  | 25-08-2004       | CN<br>JP<br>KR<br>TW<br>US | 1523558 A<br>2004252036 A<br>20040074607 A<br>234757 B<br>2004160395 A1     |  | 25-08-2004<br>09-09-2004<br>25-08-2004<br>21-06-2005<br>19-08-2004 |