(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 696 36 913 T2 2007.11.15**

(12)

## Übersetzung der europäischen Patentschrift

(97) **EP 1 233 457 B1**

(21) Deutsches Aktenzeichen: **696 36 913.3**

(96) Europäisches Aktenzeichen: **02 008 520.5**

(96) Europäischer Anmeldetag: **09.05.1996**

(97) Erstveröffentlichung durch das EPA: **21.08.2002**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **14.02.2007**

(47) Veröffentlichungstag im Patentblatt: **15.11.2007**

(51) Int Cl.<sup>8</sup>: **H01L 29/739 (2006.01)**

**H01L 21/331 (2006.01)**

(30) Unionspriorität:

**18578395 21.07.1995 JP**

(84) Benannte Vertragsstaaten:

**DE, FR, GB**

(73) Patentinhaber:

**Mitsubishi Denki K.K., Tokyo, JP**

(72) Erfinder:

**Takahashi, Hideki, Chiyoda-ku, Tokyo 100, JP**

(74) Vertreter:

**WINTER, BRANDL, FÜRNISS, HÜBNER, RÖSS,

KAISER, POLTE, Partnerschaft, 85354 Freising**

(54) Bezeichnung: **Halbleiteranordnung mit isoliertem Gate und Verfahren zu ihrer Herstellung**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft eine Halbleitervorrichtung bzw. -anordnung mit isoliertem Gate und ein Verfahren zum Herstellen derselben. Genauer betrifft die vorliegende Erfindung einen Anordnungsaufbau, bei welchem ein parasitärer Transistor eines Bipolartransistor mit isoliertem Gate, welcher ein Graben-MOS-Gate aufweist, nicht leicht ein- bzw. durchschaltet, sodass ein sicherer Betriebsbereich (nachstehend "SOA" – safe operating area) groß ist, und betrifft auch ein Verfahren zum Herstellen derselben.

**[0002]** [Fig. 26](#) ist eine Teilschnittansicht einer herkömmlichen Halbleiteranordnung mit isoliertem Gate. Als ein Beispiel wird ein Bipolartransistor mit isoliertem Gate (nachstehend "IGBT"), speziell ein IGBT mit einem Grabengateaufbau beschrieben werden (ein IGBT mit einem Grabengateaufbau wird nachstehend als ein "U-IGBT" bezeichnet werden).

**[0003]** In den vergangenen Jahren sind in Spannungsschwingkreisen, die als Hochfrequenzumsetzer, Allzweck-Umsetzer, AC-Servo, Klimaanlage, etc. dienen, sehr oft IGBTs in verschiedenen Vorrichtungen wie etwa einem intelligenten Leistungsmodul, das eine veränderliche Drehzahl eines Dreiphasenmotors steuert, eingesetzt worden, um den Energieverbrauch, die Größe und das Gewicht von elektrischen Haushaltsgeräten zu verringern. Während eine Schaltcharakteristik, eine Sättigungsspannung und ein SOA bei IGBTs, d.h. Schlüsselvorrichtungen in diesen verschiedenen Geräten, gegeneinander abgewogen werden müssen, werden IGBTs mit einer besseren Schaltcharakteristik, einer niedrigen Sättigungsspannung und einem großen SOA verlangt.

**[0004]** In [Fig. 26](#) bezeichnet **1** eine P<sup>+</sup>-Kollektorschicht, **2** eine N<sup>-</sup>-Schicht, **3** eine P-Basissschicht, **4** N<sup>+</sup>-Emitterregionen, **5** Gräben, **6** Gateisolationsfilme, **7** Gateelektroden, **8** einen Zwischenschichtisolationsfilm, **9** eine N<sup>+</sup>-Pufferschicht, **10** eine Emitterelektrode, **11** eine Kollektorelektrode und **12** Kanalregionen.

**[0005]** Als nächstes wird eine Betriebsweise eines IGBT beschrieben werden.

**[0006]** Wenn über die Emitterelektrode **10** und die Kollektorelektrode **11** eine vorbestimmte Kollektorspannung  $V_{CE}$  angelegt wird und über die Emitterelektrode **10** und die Gateelektroden **7** eine vorbestimmte Gatespannung  $V_{GE}$  angelegt wird, kehren sich, wenn die Gates eingeschaltet werden, die Kanalregionen **12** in den N-Typ um, wodurch Kanäle gebildet werden. Durch diese Kanäle werden Elektronen aus der Emitterelektrode **10** in die N<sup>-</sup>-Schicht **2** injiziert. Injizierte Elektronen legen eine Vorspannung in Durchlassrichtung über die P<sup>+</sup>-Kollektorschicht **1**

und die N<sup>-</sup>-Schicht **2** an, sodass Löcher aus der Kollektorelektrode **11** durch die P<sup>+</sup>-Kollektorschicht **1** und die N<sup>+</sup>-Pufferschicht **9** in die N<sup>-</sup>-Schicht **2** injiziert werden. Die Leitfähigkeit wird demzufolge geändert und der Widerstand der N<sup>-</sup>-Schicht **2** wird in hohem Ausmaß vermindert, sodass sich eine Stromkapazität des IGBT erhöht. Ein Spannungsabfall zwischen Kollektor und Emitter in dem IGBT während diesen Zustands (ON-Zustand) definiert eine ON-Spannung ( $V_{CE(sat)}$ ).

**[0007]** Um den IGBT von einem ON-Zustand in einen OFF-Zustand zu ändern, wird die über die Emitterelektrode **10** und die Gateelektroden **7** angelegte Gatespannung  $V_{GE}$  auf 0 V geändert oder wird über die Emitterelektrode **10** und die Gateelektroden **7** eine umgekehrte Vorspannung angelegt, wodurch die Gates sperren. Im Ergebnis kehren die in den N-Typ umgekehrten Kanalregionen **12** in den P-Typ zurück, sodass eine Injektion von Elektronen aus der Emitterelektrode **10** endet. In der N<sup>-</sup>-Schicht **2** aufgespeicherte Elektronen und Löcher fließen dann in die Kollektorelektrode **11** bzw. die Emitterelektrode **10** oder rekombinieren miteinander so, dass sie sich neutralisieren.

**[0008]** Die ON-Spannung des IGBT wird primär durch einen substanzialen Widerstand der N<sup>-</sup>-Schicht **2** bestimmt, der erforderlich ist, um eine Durchbruchspannung zu halten. Einer der Faktoren, die den Materialwiderstand bestimmen, ist eine Fähigkeit eines den IGBT ausbildenden MOSFET, Elektronen zuzuführen.

**[0009]** Bei einem U-IGBT, bei welchem enge und tiefe Nuten (Gräben) in einer Oberfläche eines Chips ausgebildet sind und MOSFETs in Seitenwänden der Gräben ausgebildet sind, wird die Fähigkeit der MOSFETs, Elektronen zuzuführen, durch weitestmögliches Reduzieren von Abständen zwischen Einheitszellen verbessert.

**[0010]** Im Allgemeinen ist ein Abschalt-Stromwert unter einer angelegten hohen Spannung eine wichtige elektrische Eigenschaft eines IGBT. Es ist daher vorzuziehen, einen höchstmöglichen Abschalt-Stromwert sicherzustellen. Je besser diese elektrische Eigenschaft ist, um so größer wird ein sicherer Betriebsbereich unter umgekehrter Vorspannung (nachstehend "RBSOA" – reverse bias safe operating area).

**[0011]** Wie indessen aus [Fig. 26](#), die den Aufbau des U-IGBT zeigt, klar verstanden werden kann, beinhaltet der U-IGBT einen parasitären Bipolartransistor, der durch die N<sup>+</sup>-Emitterregionen **4**, die P-Basissschicht **3** und die N<sup>-</sup>-Schicht **2** ausgebildet wird.

**[0012]** Wenn der parasitäre Bipolartransistor durchschaltet, kann die Gatespannung  $V_{GE}$  allein einen in

dem U-IGBT fließenden Strom nicht mehr steuern, wodurch der U-IGBT zerstört wird. Daher sind als Maßnahme zur Vergrößerung des RBSOA verschiedene Vorrichtungsstrukturen vorgeschlagen worden, in denen die Zellengröße klein ist, wobei eine Grabengatestruktur verwendet wird, sodass der parasitäre Bipolartransistor nicht leicht durchschaltet.

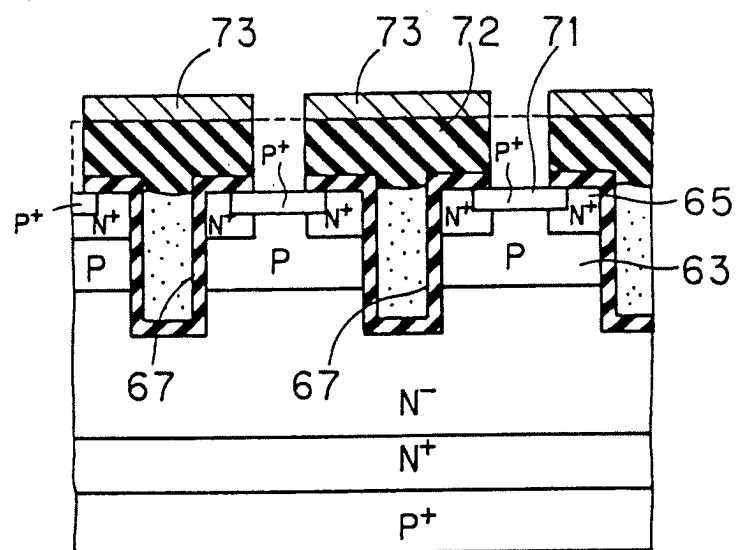

[0013] [Fig. 27](#) ist eine Teilschnittansicht, welche ein Beispiel einer herkömmlichen Halbleiteranordnung mit isoliertem Gate zeigt, die in der japanischen Offenlegungsschrift Nr. 60-253275 beschrieben ist.

[0014] In [Fig. 27](#) ist ein Halbleitersubstrat mit **13**, eine erste Hauptoberfläche des Halbleitersubstrats mit **14**, und P<sup>+</sup>-Regionen mit **15** bezeichnet. Die anderen Bezugszeichen sind den in [Fig. 24](#) verwendeten gleich. Die P<sup>+</sup>-Regionen **15** der N<sup>+</sup>-Emitterregionen **4** sind einfach deshalb angeordnet, um einen besseren Kontakt mit der Emitterelektrode **10** sicherzustellen. Die Störstellenkonzentration der P<sup>+</sup>-Regionen **15** ist niedriger als diejenige der N<sup>+</sup>-Emitterregionen.

[0015] Wenn bei dieser herkömmlichen Halbleiteranordnung mit isoliertem Gate die gleiche Maske als eine Maske zum Ausbilden der N<sup>+</sup>-Emitterregionen **4** und eine Maske zum Ausbilden der V-förmigen Gateelektroden **7** verwendet wird, wird eine Ausrichtung der Masken unnötig und werden Abstände zwischen Zellen reduziert. Nachdem jedoch die Gateelektroden **7** von der ersten Hauptoberfläche **14** des Halbleitersubstrats **13** hervorragen, müssen, um sicherzustellen, dass die N<sup>+</sup>-Emitterregionen **4** die P<sup>+</sup>-Regionen **15** kontaktieren, und gleichzeitig eine Anordnung des Zwischenschichtisolationsfilm **8** über der Emitterelektrode **10** und den Gateelektroden **7** zuzulassen, die N<sup>+</sup>-Emitterregionen **4** groß mit einem zusätzlichen Rand ausgebildet werden, wenn Masken während Ausbildung des Zwischenschichtisolationsfilm **8** ausgerichtet werden. Dies wirkt als ein Hindernis bezüglich eines Aufwand zur Reduzierung der Abstände zwischen den Zellen.

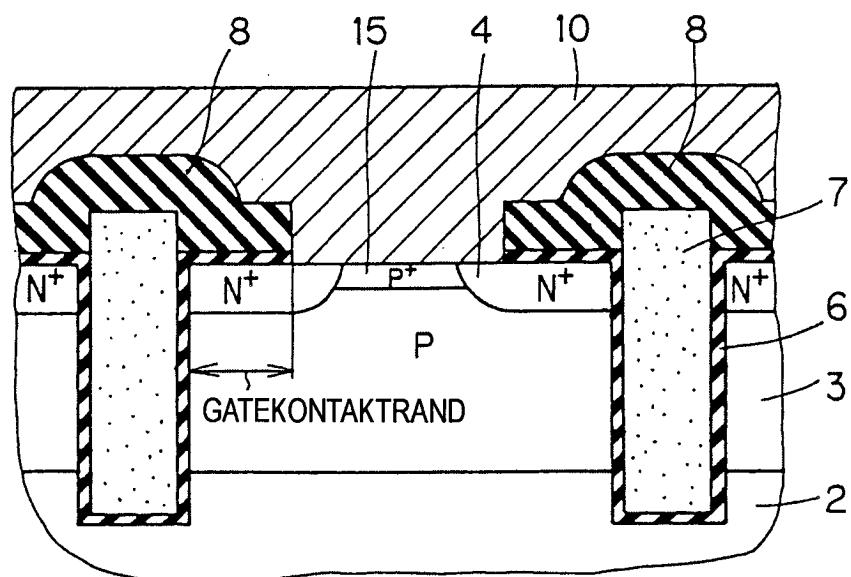

[0016] [Fig. 28](#) ist eine schematische Darstellung, welche einen Kontaktrand bei der herkömmlichen Technik zeigt.

[0017] In [Fig. 28](#) sind die Gateelektroden **7** eher Elektroden vom Grabentyp denn V-förmige Elektroden. [Fig. 28](#) zeigt zusätzliche Bereiche, welche erforderlich sind, damit die N<sup>+</sup>-Emitterregionen **4** mit einer Fehlausrichtung der Masken zureckkommen (d.h., Gate-Kontaktränder).

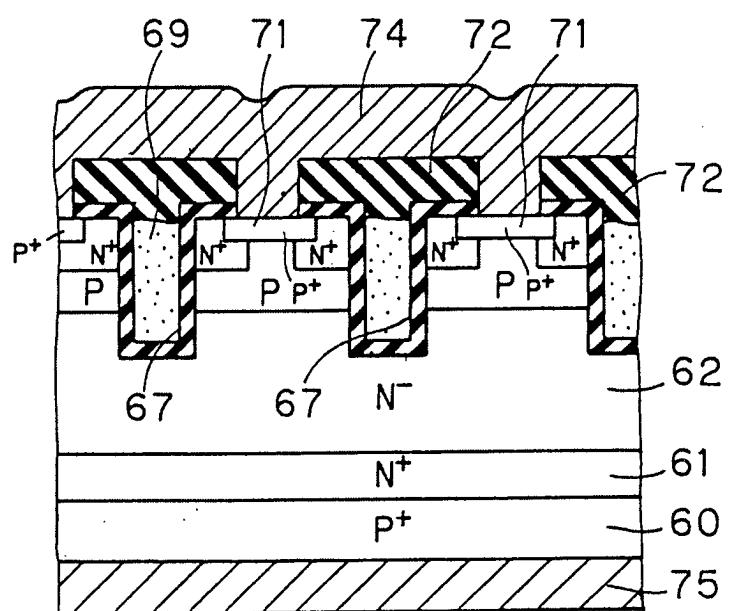

[0018] [Fig. 29](#) ist eine Teilschnittansicht, welche ein Beispiel einer herkömmlichen Halbleiteranordnung mit isoliertem Gate zeigt, die in US-Patent Nr. 5,034,785 beschrieben ist. Die Abstände zwischen Zellen sind in der dargestellten Anordnung kürzer, da

die dargestellte Anordnung keine Gate-Kontaktränder verwendet, die bei der herkömmlichen Technik gemäß [Fig. 28](#) verwendet werden.

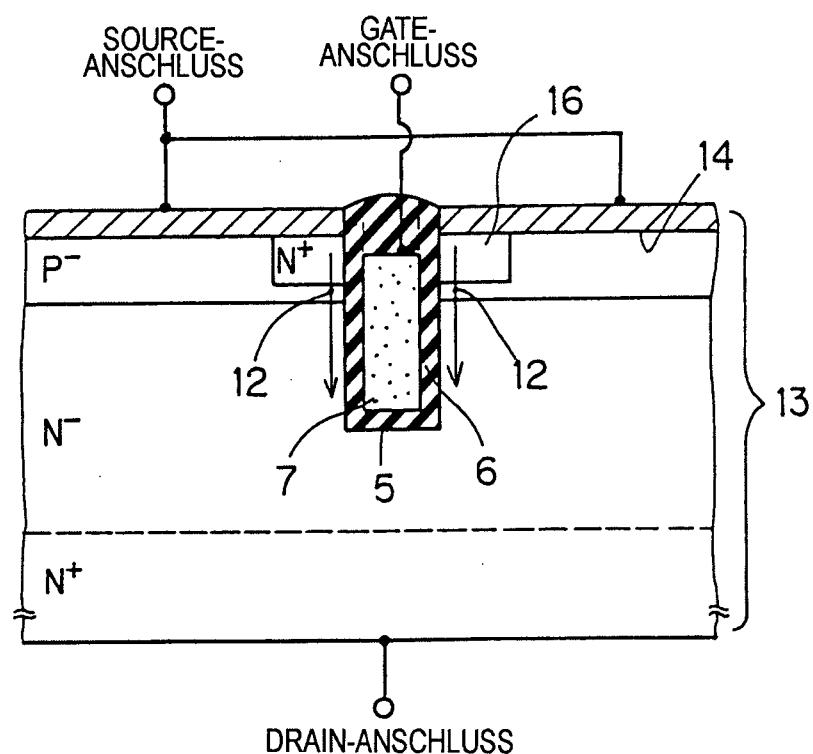

[0019] Die in [Fig. 29](#) gezeigte Anordnung bzw. Vorrichtung ist ein DMOS-Leistungstransistor und enthält ein Gate einer Grabenstruktur. Die Gateelektroden **7** weisen eine Oberfläche auf, die von der Hauptoberfläche **14** des Halbleitersubstrats **13** zurückgesetzt ist. Mit **16** ist eine Sourceelektrode bezeichnet.

[0020] In dem dargestellten Aufbau sind die Oberflächen der Gateelektroden **7** von der Hauptoberfläche **14** des Halbleitersubstrats **13** zurückgesetzt. Dies macht eine Maske zur Ausbildung der Gateelektroden **7** entbehrlich und macht es auch entbehrlich, dass die Sourceelektrode einen Rand zur Ausrichtung der Masken aufweist. Daher ist es möglich, den Grabenabstand bzw. die Grabenteilung zu reduzieren.

[0021] Es ist jedoch erforderlich, die N<sup>+</sup>-Sourceregion **16** so auszubilden, dass sie tiefer als die Oberfläche der Gateelektroden **7** ist. Die N<sup>+</sup>-Sourceregion **16** neigt daher dazu, tiefer zu sein. Nachdem die N<sup>+</sup>-Sourceregion **16** in den meisten Fällen durch Diffusion ausgebildet wird, wird dann, wenn die N<sup>+</sup>-Sourceregion **16** tief diffundiert wird, die N<sup>+</sup>-Sourceregion **16** breit diffundiert. Dies vergrößert die Grabenteilung.

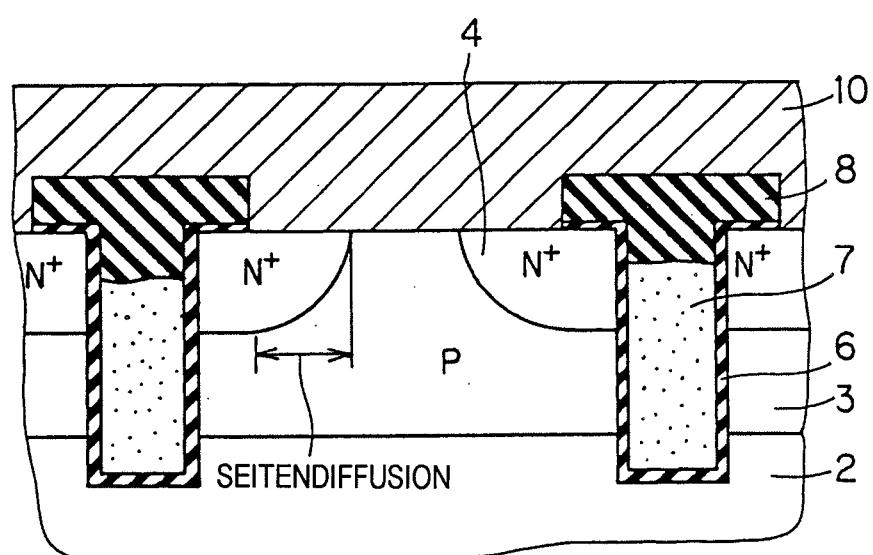

[0022] [Fig. 30](#) ist eine schematische Darstellung, welche eine Seitendiffusion bei der herkömmlichen Struktur zeigt. Die dargestellte Anordnung ist ein IGBT.

[0023] In [Fig. 30](#) sind, um sicherzustellen, dass die Oberflächen der Gateelektroden **7** von den Oberflächen der N<sup>+</sup>-Emitterregionen **4** zurückgesetzt sind, die N<sup>+</sup>-Emitterregionen **4** tiefer ausgebildet und ist daher eine Seitendiffusion der N<sup>+</sup>-Emitterregionen **4** groß. Daher muss, damit eine freiliegende Oberfläche der P-Basissschicht **3** und die Oberflächen der N<sup>+</sup>-Emitterregionen **4** an der Emitterelektrode **10** miteinander kontaktieren, die Grabenteilung groß ausgebildet werden. Dies ermöglicht es dem parasitären Transistor, leicht durchzuschalten.

[0024] Ein anderer Wert, der mit dem SOA eines Elements in Bezug steht, ist der Sättigungsstrom  $I_c(\text{sat})$ .

[0025] Der Wert eines Stroms, der in einem IGBT als Reaktion auf eine bestimmte angelegte Gatespannung fließt, wird als  $I_c(\text{sat})$  ausgedrückt. Falls der Wert  $I_c(\text{sat})$  zu groß ist, schaltet der parasitäre Transistor leicht durch, was wiederum den IGBT zerstört.

**[0026]** Weitere Informationen über den Stand der Technik können in Proceedings of the International Symposium on Power Semiconductor Devices, "600V Trench IGBT in Comparison with Planar IGBT Performance," 31. Mai 1994, Davos, Schweiz, Seiten 411-416 gefunden werden, wo die Entwicklung einer Verarbeitung eines großflächigen Graben-MOS wie auch eines Graben IGBT diskutiert werden, wie in **Fig. 31** beispielhaft dargestellt.

**[0027]** JP-A-1198076 offenbart eine Halbleiteranordnung zur Sicherstellung einer Erhöhung einer Latch-up-Fließgrenze durch Ausbilden eines Grabens, um eine Basis eines ersten Leitfähigkeitstyps auf der Sourceseite eines IGBT einer vertikalen Grabenstruktur zu reduzieren, und Ausbilden einer Sourceelektrode, die sich so weit wie der Grabengrund erstreckt, oder Installieren einer Diffusionsregion des ersten Leitfähigkeitstyps mit hoher Störstellenkonzentration anstelle des Grabens. Bei dieser Halbleiteranordnung ist die sourceseitige Oberfläche eines IGBT einer vertikalen Grabenstruktur abgeflacht und ist die sourceseitige Oberfläche mit Ausnahme der freiliegenden Region einer P<sup>+</sup>-Basisschicht mit einem Resistfilm bedeckt. Durch Verwenden des Resistfilms als eine Maske wird ein zweiter Graben gegraben und wird die Region der Oberflächenseite der P<sup>+</sup>-Basisschicht abrasiert. Der Resistfilm wird beseitigt, und eine Sourceelektrode, die sich so weit wie die Seitenfläche und die Bodenfläche des zweiten Grabens ausdehnt, wird ausgebildet. Eine Drainelektrode wird ausgebildet, und Polysilizium wird in dem zweiten Graben vergraben, um eine Halbleiteranordnung fertigzustellen. Eine P<sup>++</sup>-Diffusionsregion hoher Konzentration, die einen niedrigen Widerstand aufweist, wird anstelle des Grabens installiert, und die Reihenwiderstandskomponente zwischen der P<sup>+</sup>-Basisschicht und der Sourceelektrode wird verkleinert. Hierdurch kann die Latch-up-Fließgrenze verbessert werden.

**[0028]** EP 0 485 059 A2 betrifft eine Halbleiteranordnung mit einer Pin-Diode, welche eine hohe Durchbruchspannung aufweist. Eine p-Emitterschicht **2** ist in einem Oberflächenabschnitt einer N<sup>-</sup>Basisschicht **1** eines hohen Widerstands ausgebildet. P<sup>+</sup>P<sup>+</sup>-Kontaktschichten **2b** und N<sup>+</sup>-Stromblockierschichten **6** sind in einem vorher festgelegten Flächenverhältnis in dem Oberflächenbereich der p-Emitterschicht ausgebildet. Eine Kathodenelektrode **4** ist im Kontakt mit der Kontaktschicht **2b** wie auch der Stromblockierschicht **6** des pn-Sperrschichtdiodenabschnitts ausgebildet. Mit diesem Kathodenaufbau kann die Elektroneninjektion in dem ON-Zustand unterdrückt werden, um die Trägerkonzentration eines Abschnitts der auf der Kathodenseite liegenden n<sup>-</sup>Basisschicht **1** zu reduzieren, und die zu der Zeit einer umgekehrten Erholung verursachte Wirkung eines parasitären Transistors kann durch Vorsehen der Stromblockierschicht **6** unterdrückt

werden.

**[0029]** EP 0 633 611 A1 offenbart einen Bipolartransistor mit isoliertem Gate, der einen Halbleiterkörper bzw. -body mit einer ersten Region eines Leitfähigkeitstyps, einer zweiten Region des entgegengesetzten Leitfähigkeitstyps, einer dritten Region des einen Leitfähigkeitstyps, die von der ersten Region durch die zweite Region getrennt ist, und wenigstens einer Injektorregion zum Injizieren von Ladungsträgern des entgegengesetzten Leitfähigkeitstyps in die erste Region aufweist. Der Leitungskanalbereich, der an das isolierte Gate angrenzt, weist einen ersten und einen zweiten subsidiären Bereich zum Bereitstellen eines jeweiligen ersten und zweiten subsidiären Leitungskanals auf. Der zweite subsidiäre Bereich ist von der dritten Region beabstandet und ist niedriger dotiert als der erste subsidiäre Leitungskanalbereich, um dann, wenn der injizierte Stromtyp entgegengesetzter Leitfähigkeit einen gegebenen Wert erreicht, bewirkt, dass der pn-Übergang zwischen dem zweiten subsidiären Kanal und der zweiten Region eine Vorspannung in Durchlassrichtung annimmt, was bewirkt, dass der durch den zweiten subsidiären Kanal, die zweite Region und die ersten Region ausgebildete Bipolartransistor leitet, um mit der wenigstens einen Injektorregion einen Thyristorvorgang einzuleiten, der nach Entfernen des Leitungskanals verschwindet.

**[0030]** "500-V n-Channel Insulated-Gate Bipolar Transistor with a Trench Gate Structure" von H.-R. Chang und B. Jayant Baliga, IEEE transactions on electron devices 36 (1989) September, Nr. 9-I, New York, USA, beschreibt einen verbesserten IGBT mit einer Grabengatestruktur, der einen niedrigen Spannungsabfall in Durchlassrichtung von 1,2 V bei einer Leitungsstromdichte in Durchlassrichtung von 200 A/cm<sup>2</sup> zeigt. Der Aufbau dieser Anordnung wurde unter Verwendung eines Selbstausrichtungsprozesses hergestellt, der nahe beabstandete vertikale Grabengates mit einer Einheitszelle von 6 µm erlaubt. Dies ermöglicht eine Erhöhung der Kanaldichte um das Fünffache und eine Beseitigung des parasitären JFET-Effekts, wodurch der Spannungsabfall in Durchlassrichtung signifikant reduziert wird.

**[0031]** Demgemäß ist es eine Aufgabe der vorliegenden Erfindung, eine Halbleiteranordnung mit isoliertem Gate zu schaffen, die einen Anordnungsaufbau aufweist, bei welchem ein parasitärer Transistor nicht leicht durchschaltet und daher die SOA verbessert ist, sowie ein Verfahren zur Herstellung einer solchen Anordnung.

**[0032]** Um diese und andere nachstehend genannten Aufgaben zu lösen, stellt die vorliegende Erfindung eine Halbleiteranordnung mit isoliertem Gate bereit, wie sie in dem unabhängigen Anspruch 1 definiert ist, wie auch ein Verfahren zur Herstellung ei-

ner Halbleiteranordnung mit isoliertem Gate, wie sie in Anspruch 4 definiert ist. Bevorzugte Ausführungsformen sind in den abhängigen Ansprüchen definiert.

**[0033]** Die Erfindung, wie sie beansprucht wird, beruht unter anderem auf dem nachstehend beschriebenen technischen Hintergrund.

**[0034]** Eine beispielhafte Halbleiteranordnung mit isoliertem Gate kann aufweisen: eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps, wobei die erste Halbleiterschicht eine erste Hauptoberfläche und eine zweite Hauptoberfläche aufweist; eine zweite Halbleiterschicht eines zweiten Leitfähigkeitstyps, die auf der ersten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist, wobei die zweite Halbleiterschicht eine niedrige Störstellenkonzentration aufweist; eine dritte Halbleiterschicht des ersten Leitfähigkeitstyps, die auf einer Oberfläche der zweiten Halbleiterschicht angeordnet ist; eine vierte Halbleiterschicht des zweiten Leitfähigkeitstyps, die selektiv auf einem Abschnitt einer Oberfläche der dritten Halbleiterschicht angeordnet ist; eine nutförmige Innenwand, die wenigstens eine zählt und die eine Öffnung definiert, die sich in einer Oberfläche der vierten Halbleiterschicht so öffnet, dass sie sich in einer Richtung entlang der Oberfläche der vierten Halbleiterschicht erstreckt, wobei sich die nutförmige Innenwand entlang einer Tiefenrichtung hiervon von der Oberfläche der vierten Halbleiterschicht zu der zweiten Halbleiterschicht erstreckt; eine fünfte Halbleiterschicht des zweiten Leitfähigkeitstyps, die auf den Oberflächen der dritten und der vierten Halbleiterschicht so angeordnet ist, dass sie sich über die dritte und die vierte Halbleiterschicht erstreckt, wobei eine Verbindungs- bzw. Übergangsstelle zwischen der fünften Halbleiterschicht und der vierten Halbleiterschicht einer Oberfläche ausgesetzt ist, wobei eine Bodenfläche der fünften Halbleiterschicht in einer seichteren Lage als eine Bodenfläche der vierten Halbleiterschicht angeordnet ist, wobei die fünfte Halbleiterschicht eine höhere Störstellenkonzentration als die vierte Halbleiterschicht aufweist; einen Isolationsfilm, der die Innenwand und eine Oberfläche der vierten Halbleiterschicht, die sich an die Innenwand anschließt und sich in der Umgebung der Öffnung befindet, bedeckt; eine Steuerelektrode, die auf einer Oberfläche der Innenwand über den Isolationsfilm so angeordnet ist, dass sie eine zurückgesetzte Oberfläche aufweist, die von einer Oberfläche eines die Oberfläche der vierten Halbleiterschicht bedeckenden Abschnitts des Isolationsfilms zurückgesetzt ist; eine erste Hauptelektrode, die auf den Oberflächen der vierten und der fünften Halbleiterschicht angeordnet ist; und eine zweite Hauptelektrode, die auf der zweiten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist.

**[0035]** Die beispielhafte Halbleiteranordnung mit isoliertem Gate kann eine Mehrzahl von nutförmigen

Innenwänden aufweisen, und eine freiliegende Oberfläche der fünften Halbleiterschicht zwischen zwei aneinandergrenzenden der nutförmigen Innenwände kann sich entlang den nutförmigen Innenwänden erstrecken.

**[0036]** Bei der beispielhaften Halbleiteranordnung mit isoliertem Gate des zweiten Gesichtspunkts kann die freiliegende Oberfläche der fünften Halbleiterschicht eine verstreute Konfiguration aufweisen.

**[0037]** Eine andere beispielhafte Halbleiteranordnung mit isoliertem Gate kann aufweisen: eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps, wobei die erste Halbleiterschicht eine erste Hauptoberfläche und eine zweite Hauptoberfläche aufweist; eine zweite Halbleiterschicht eines zweiten Leitfähigkeitstyps, die auf der ersten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist, wobei die zweite Halbleiterschicht eine niedrige Störstellenkonzentration aufweist; eine dritte Halbleiterschicht des ersten Leitfähigkeitstyps, die auf einer Oberfläche der zweiten Halbleiterschicht angeordnet ist; eine vierte Halbleiterschicht des zweiten Leitfähigkeitstyps, die selektiv auf einem Abschnitt einer Oberfläche der dritten Halbleiterschicht angeordnet ist; nutförmige Innenwände mehrfacher Zahl, wobei jede derselben eine Öffnung definiert, die sich in einer Oberfläche der vierten Halbleiterschicht so öffnet, dass sie sich in einer Richtung entlang der Oberfläche der vierten Halbleiterschicht erstreckt, wobei sich die nutförmigen Innenwände entlang einer Tiefenrichtung hiervon von der Oberfläche der vierten Halbleiterschicht zu der zweiten Halbleiterschicht erstrecken; eine fünfte Halbleiterschicht des zweiten Leitfähigkeitstyps, die auf den Oberflächen der dritten und der vierten Halbleiterschicht, die zwischen zwei benachbarten der nutförmigen Innenwände vorliegen, so angeordnet ist, dass sie sich über die dritte und die vierte Halbleiterschicht erstreckt, wobei eine Verbindungs- bzw. Übergangsstelle zwischen der fünften Halbleiterschicht und der vierten Halbleiterschicht einer Oberfläche ausgesetzt ist; wobei die fünfte Halbleiterschicht eine höhere Störstellenkonzentration als die vierte Halbleiterschicht aufweist; einen Isolationsfilm, der die nutförmigen Innenwände, einen Abschnitt einer Oberfläche der vierten Halbleiterschicht, der sich an die nutförmigen Innenwände anschließt und an diese angrenzt, und einen Abschnitt einer Oberfläche der fünften Halbleiterschicht, der an den Abschnitt der Oberfläche der vierten Halbleiterschicht angrenzt, bedeckt; eine Steuerelektrode, die auf Oberflächen der nutförmigen Innenwände über den Isolationsfilm so angeordnet ist, dass sie eine zurückgesetzte Oberfläche aufweist, die von einer Oberfläche eines den Abschnitt der Oberfläche der vierten Halbleiterschicht bedeckenden Abschnitts des Isolationsfilms zurückgesetzt ist; eine erste Hauptelektrode, die auf den Oberflächen der vierten und der fünften Halbleiterschicht angeordnet ist; und eine zweite

Hauptelektrode, die auf der zweiten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist.

**[0038]** Eine weitere beispielhafte Halbleiteranordnung mit isoliertem Gate kann aufweisen: eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps, wobei die erste Halbleiterschicht eine erste Hauptoberfläche und eine zweite Hauptoberfläche aufweist; eine zweite Halbleiterschicht eines zweiten Leitfähigkeitstyps, die auf der ersten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist, wobei die zweite Halbleiterschicht eine niedrige Störstellenkonzentration aufweist; eine dritte Halbleiterschicht des ersten Leitfähigkeitstyps, die auf einer Oberfläche der zweiten Halbleiterschicht angeordnet ist; vierte Halbleiterschichten des zweiten Leitfähigkeitstyps, die in einer Mehrzahl vorliegen und parallel zueinander in der Gestalt von Säulen auf einem Abschnitt einer Oberfläche der dritten Halbleiterschicht angeordnet sind; nutförmige Innenwände mehrfacher Zahl, welche jeweils Öffnungen definieren, die sich in jeweiligen Oberflächen der vierten Halbleiterschichten so öffnen, dass sie sich entlang den Säulen der vierten Halbleiterschichten erstrecken, wobei sich die nutförmigen Innenwände entlang einer Tiefenrichtung hier von den Oberflächen der vierten Halbleiterschichten zu der zweiten Halbleiterschicht erstrecken; eine fünfte Halbleiterschicht des zweiten Leitfähigkeitstyps, die auf den Oberflächen der dritten Halbleiterschicht und der vierten Halbleiterschichten so angeordnet ist, dass sie sich über die dritte und die vierten Halbleiterschichten erstreckt, wobei eine Verbindungs- bzw. Übergangsstelle zwischen der fünften Halbleiterschicht und den vierten Halbleiterschichten einer Oberfläche ausgesetzt ist, wobei eine Bodenfläche der fünften Halbleiterschicht in einer seichteren Position angeordnet ist als die Bodenflächen der vierten Halbleiterschichten, wobei die fünfte Halbleiterschicht eine höhere Störstellenkonzentration als die vierten Halbleiterschichten aufweist; einen Isolationsfilm, der die nutförmigen Innenwände und Oberflächen der vierten Halbleiterschichten, die sich in der Umgebung der Öffnungen befinden und sich an die nutförmigen Innenwände anschließen, bedeckt; eine Steuerelektrode, die auf Oberflächen der nutförmigen Innenwände über den Isolationsfilm so angeordnet ist, dass sie eine zurückgesetzte Oberfläche aufweist, die von einer Oberfläche eines die Oberflächen der vierten Halbleiterschichten bedeckenden Abschnitts des Isolationsfilms zurückgesetzt ist; eine erste Hauptelektrode, die auf den Oberflächen der vierten und der fünften Halbleiterschichten und dem Zwischenschichtisolationsfilm angeordnet ist; und eine zweite Hauptelektrode, die auf der zweiten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist.

**[0039]** Bei der weiteren beispielhaften Halbleiteranordnung mit isoliertem Gate kann die fünfte Halbleiterschicht in einer verstreuten Konfiguration entlang

den vierten Halbleiterschichten angeordnet sein.

**[0040]** Eine noch weitere beispielhafte Halbleiteranordnung mit isoliertem Gate kann aufweisen: eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps, wobei die erste Halbleiterschicht eine erste Hauptoberfläche und eine zweite Hauptoberfläche aufweist; eine zweite Halbleiterschicht eines zweiten Leitfähigkeitstyps, die auf der ersten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist, wobei die zweite Halbleiterschicht eine niedrige Störstellenkonzentration aufweist; eine dritte Halbleiterschicht des ersten Leitfähigkeitstyps, die auf einer Oberfläche der zweiten Halbleiterschicht angeordnet ist; vierte Halbleiterschichten des zweiten Leitfähigkeitstyps, die in einer Mehrzahl vorliegen und parallel zueinander in der Gestalt von Säulen auf einem Abschnitt einer Oberfläche der dritten Halbleiterschicht angeordnet sind; nutförmige Innenwände mehrfacher Zahl, welche jeweils Öffnungen definieren, die sich in jeweiligen Oberflächen der vierten Halbleiterschichten so öffnen, dass sie sich entlang den Säulen der vierten Halbleiterschichten erstrecken, wobei sich die nutförmigen Innenwände entlang einer Tiefenrichtung hier von der Oberfläche der vierten Halbleiterschichten zu der zweiten Halbleiterschicht erstrecken; eine fünfte Halbleiterschicht des zweiten Leitfähigkeitstyps, die in einer verstreuten Konfiguration entlang den vierten Halbleiterschichten und auf den Oberflächen der dritten und der vierten Halbleiterschichten so angeordnet ist, dass sie sich über die dritte und die vierten Halbleiterschichten erstreckt, wobei eine Verbindungs- bzw. Übergangsstelle zwischen der fünften Halbleiterschicht und den vierten Halbleiterschichten einer Oberfläche ausgesetzt ist, wobei die fünfte Halbleiterschicht eine höhere Störstellenkonzentration als die vierten Halbleiterschichten aufweist; einen Isolationsfilm, der die nutförmigen Innenwände, Oberflächen der vierten Halbleiterschichten, die sich an die nutförmigen Innenwände anschließen, an diese angrenzen und entlang diesen liegen, und einen Abschnitt einer Oberfläche der fünften Halbleiterschicht, der sich in der Umgebung der vierten Halbleiterschichten befindet, bedeckt; eine Steuerelektrode, die auf Oberflächen der nutförmigen Innenwände über den Isolationsfilm so angeordnet ist, dass sie eine zurückgesetzte Oberfläche aufweist, die von einer Oberfläche eines die Oberflächen der vierten Halbleiterschichten bedeckenden Abschnitts des Isolationsfilms zurückgesetzt ist; einen Zwischenschichtisolationsfilm, der auf einer Oberfläche der Steuerelektrode angeordnet ist; eine erste Hauptelektrode, die auf den Oberflächen der vierten und der fünften Halbleiterschichten und dem Zwischenschichtisolationsfilm angeordnet ist; und eine zweite Hauptelektrode, die auf der zweiten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist.

**[0041]** Ein erster Gesichtspunkt der vorliegenden Erfindung betrifft eine Halbleiteranordnung mit isolier-

tem Gate, die aufweist: eine erste Halbleiterschicht eines ersten Leitfähigkeitsstyps, wobei die erste Halbleiterschicht eine erste Hauptoberfläche und eine zweite Hauptoberfläche aufweist; eine zweite Halbleiterschicht eines zweiten Leitfähigkeitsstyps, die auf der ersten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist, wobei die zweite Halbleiterschicht eine niedrige Störstellenkonzentration aufweist; eine dritte Halbleiterschicht des ersten Leitfähigkeitsstyps, die auf einer Oberfläche der zweiten Halbleiterschicht angeordnet ist; eine vierte Halbleiterschicht des zweiten Leitfähigkeitsstyps, die auf einer Oberfläche der dritten Halbleiterschicht so angeordnet ist, dass sie eine freiliegende Oberfläche der dritten Halbleiterschicht in einer Konfiguration paralleler, diskontinuierlicher Säulen belässt; wenigstens eine nutförmige Innenwand, welche eine Öffnung definiert, die sich in einer Oberfläche der vierten Halbleiterschicht so öffnet, dass sie sich in einer Richtung entlang der Oberfläche der vierten Halbleiterschicht erstreckt, wobei sich die nutförmige Innenwand entlang einer Tiefenrichtung hiervon von der Oberfläche der vierten Halbleiterschichten zu der zweiten Halbleiterschicht erstreckt; einen Isolationsfilm, der die nutförmige Innenwand, einen Abschnitt der Oberfläche der vierten Halbleiterschicht, der sich in der Umgebung der Öffnung befindet und sich an die Innenwand anschließt, und einen Abschnitt einer Oberfläche der dritten Halbleiterschicht, der an die vierte Halbleiterschicht angrenzt, bedeckt; eine Steuerelektrode, die auf einer Oberfläche der nutförmigen Innenwand über den Isolationsfilm so angeordnet ist, dass sie eine zurückgesetzte Oberfläche aufweist, die von einer Oberfläche eines Abschnitts des Isolationsfilms, der den Abschnitt der Oberfläche der vierten Halbleiterschicht bedeckt, zurückgesetzt ist; einen Zwischenschichtisolationsfilm, der Oberflächen der Steuerelektrode und des Isolationsfilms bedeckt; eine erste Hauptelektrode, die auf den Oberflächen der dritten und der vierten Halbleiterschichten und dem Zwischenschichtisolationsfilm angeordnet ist; und eine zweite Hauptelektrode, die auf der zweiten Hauptoberfläche der ersten Halbleiterschicht angeordnet ist.

**[0042]** Die Halbleiteranordnung mit isoliertem Gate kann eine Mehrzahl von nutförmigen Innenwänden aufweisen, wobei die freiliegende Oberfläche der dritten Halbleiterschicht zwischen und entlang zweier benachbarter der nutförmigen Innenwände angeordnet ist und sich in einer Längsrichtung der zwei benachbarten erstreckt.

**[0043]** Ein Verfahren zum Herstellen einer beispielhaften Halbleiteranordnung mit isoliertem Gate kann aufweisen: einen ersten Schritt eines Ausbildens eines Halbleitersubstrats, welches eine erste Halbleiterschicht eines ersten Leitfähigkeitsstyps und eine zweite, auf einer Oberfläche der ersten Halbleiterschicht angeordnete Halbleiterschicht eines zweiten

Leitfähigkeitsstyps aufweist; einen zweiten Schritt eines Implantierens von Fremdatomen bzw. Störstellen des ersten Leitfähigkeitsstyps in eine ersten Hauptoberfläche des Halbleitersubstrats, die sich auf der Seite der zweiten Halbleiterschicht des Halbleitersubstrats befindet, um hierdurch eine dritten Halbleiterschicht des ersten Leitfähigkeitsstyps auszubilden; einen dritten Schritt eines Stapelns eines Resists auf der ersten Hauptoberfläche, eines selektiven Entfernen des Resists, um ein Resistmuster zu erhalten, eines selektiven Implantierens von Störstellen des zweiten Leitfähigkeitsstyps unter Verwendung des Resistmusters als einer Maske, und eines Diffundierens der Störstellen des zweiten Leitfähigkeitsstyps in einer Oberfläche der dritten Halbleiterschicht, um hierdurch eine vierte Halbleiterschicht des zweiten Leitfähigkeitsstyps mit einer höheren Störstellenkonzentration als die zweite Halbleiterschicht auszubilden; einen vierten Schritt eines Ausbildens eines Abschirmfilms auf der ersten Hauptoberfläche, eines Ausbildens einer Öffnung in dem Abschirmfilms auf einem Abschnitt einer Oberfläche der vierten Halbleiterschicht so, dass sich die Öffnung entlang einer Oberfläche des Abschirmfilms erstreckt, eines selektiven Entfernen eines Halbleiters hinab zu der zweiten Halbleiterschicht unter Verwendung des Abschirmfilms als eine Maske, welche die Öffnung aufweist, um hierdurch eine nutförmige Innenwand, die eine Nut definiert, auszubilden, und hiernach eines Entfernen des Abschirmfilms; einen fünften Schritt eines Ausbildens eines Isolationsfilms auf einer Oberfläche der nutförmigen Innenwand und auf der ersten Hauptoberfläche; einen sechsten Schritt eines Stapelns eines leitfähigen Materials auf dem Isolationsfilm so, dass die Nut aufgefüllt wird; einen siebenten Schritt eines einheitlichen Entfernen des leitfähigen Materials unter Belassen des Isolationsfilms, bis ein Oberfläche des leitfähigen Materials, das in der Nut vergraben ist, von einer Oberfläche eines Abschnitts des Isolationsfilms, der auf der ersten Hauptoberfläche ausgebildet ist, zurückgesetzt ist; einen achten Schritt eines Stapeln eines Resists auf einem Abschnitt des Isolationsfilms, der nach dem siebenten Schritt auf der ersten Hauptoberfläche freiliegt, und der Oberfläche des leitfähigen Materials, eines Ausbildens einer Öffnung hierin in einer Position derart, dass sie einen Bereich, der dem in dem dritten Schritt relativ belassenen Resist entspricht, umgibt und einen Abschnitt der Oberfläche der vierten Halbleiterschicht, der an den Bereich angrenzt, umgibt, eines selektiven Implantierens von Störstellen des ersten Leitfähigkeitsstyps mit einer höheren Störstellenkonzentration als derjenigen der vierten Halbleiterschicht durch den Isolationsfilm unter Verwendung des Resists als einer Maske, welche die Öffnung aufweist, und eines Diffundierens der Störstellen des ersten Leitfähigkeitsstyps seichter als einen Boden der vierten Halbleiterschicht, um hierdurch eine fünfte Halbleiterschicht des ersten Leitfähigkeitsstyps, welche in Verbindung mit der dritten Halbleiterschicht steht, se-

lektiv auszubilden; einen neunten Schritt eines Stapelns eines Isolationsmaterials auf dem Abschnitt des Isolationsfilms, der in dem siebten Schritt freigelegt wird, und auf einer Oberfläche des leitfähigen Materials; einen zehnten Schritt eines Stapelns eines Resists auf einer Oberfläche des Isolationsmaterials, eines Ausbildens einer Öffnung hierin, welche die fünfte Halbleiterschicht und einen Abschnitt der vierten Halbleiterschicht, der an die fünfte Halbleiterschicht angrenzt, umgibt, eines selektiven Entfernens des Isolationsmaterials und des Isolationsfilms unter Verwendung des Resists als einer Maske, welche die Öffnung aufweist, um hierdurch die fünfte und die vierte Halbleiterschicht freizulegen; einen elften Schritt eines Stapelns einer leitfähigen Schicht auf der vierten und der fünften Halbleiterschicht, die nach dem zehnten Schritt freigelegt sind, und auf der Oberfläche des Isolationsmaterials; und einen zwölften Schritt eines Stapelns einer leitfähigen Schicht auf einer zweiten Hauptoberfläche des Halbleitersubstrats, die sich auf einer gegenüberliegenden Seite bezüglich der ersten Hauptoberfläche befindet.

**[0044]** Ein Verfahren zum Herstellen einer anderen beispielhaften Halbleiteranordnung mit isoliertem Gate kann aufweisen: einen ersten Schritt eines Ausbildens eines Halbleitersubstrats, welches eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps und eine zweite, auf einer Oberfläche der ersten Halbleiterschicht angeordnete Halbleiterschicht eines zweiten Leitfähigkeitstyps aufweist; einen zweiten Schritt eines Implantierens von Fremdatomen bzw. Störstellen des ersten Leitfähigkeitstyps in eine ersten Hauptoberfläche des Halbleitersubstrats, die sich auf der Seite der zweiten Halbleiterschicht des Halbleitersubstrats befindet, um hierdurch eine dritten Halbleiterschicht des ersten Leitfähigkeitstyps auszubilden; einen dritten Schritt eines Stapelns eines Resists auf der ersten Hauptoberfläche, eines selektiven Entfernens des Resists, so dass ein Abschnitt des Resists als eine Mehrzahl von Regionen, die parallel zueinander in der Gestalt von Säulen angeordnet sind, so belassen wird, dass ein Resistmuster ausgebildet wird, eines selektiven Implantierens von Störstellen des zweiten Leitfähigkeitstyps unter Verwendung des Resist musters als einer Maske, und eines Diffundierens der Störstellen des zweiten Leitfähigkeitstyps in einer Oberfläche der dritten Halbleiterschicht, um hierdurch vierte Halbleiterschichten des zweiten Leitfähigkeitstyps mit einer höheren Störstellenkonzentration als die zweite Halbleiterschicht selektiv auszubilden; einen vierten Schritt eines Ausbildens eines Abschirmfilms auf der ersten Hauptoberfläche, eines Ausbildens einer Öffnung in dem Abschirmfilm auf einem Abschnitt einer Oberfläche der vierten Halbleiterschichten so, dass sich die Öffnung entlang einer Oberfläche von Säulen der vierten Halbleiterschichten erstreckt, eines selektiven Entfernens eines Halbleiters hinab zu der zweiten Halbleiterschicht unter Verwendung des Abschirmfilms als

eine Maske, welche die Öffnung aufweist, um hierdurch nutförmige Innenwände, die Nuten definieren, auszubilden, und hiernach eines Entfernens des Abschirmfilms; einen fünften Schritt eines Ausbildens eines Isolationsfilms auf Oberflächen der nutförmigen Innenwände und auf der ersten Hauptoberfläche; einen sechsten Schritt eines Stapelns eines leitfähigen Materials auf dem Isolationsfilm so, dass die Nuten aufgefüllt werden; einen siebten Schritt eines einheitlichen Entfernens des leitfähigen Materials unter Belassen des Isolationsfilms, bis ein Oberfläche des leitfähigen Materials, das in den Nuten vergraben ist, von einer Oberfläche eines Abschnitts des Isolationsfilms, der auf der ersten Hauptoberfläche ausgebildet ist, zurückgesetzt ist; einen achten Schritt eines Stapelns eines Resists auf einem Abschnitt des Isolationsfilms, der nach dem siebten Schritt auf der ersten Hauptoberfläche freiliegt, und der Oberfläche des leitfähigen Materials, eines Ausbildens einer Öffnung hierin in einer Position derart, dass sie einen Bereich, der dem in dem dritten Schritt in der Gestalt von Säulen belassenen Resist entspricht, umgibt und Abschnitte der Oberflächen der vierten Halbleiterschichten, die an den Bereich angrenzen, umgibt, eines selektiven Implantierens von Störstellen des ersten Leitfähigkeitstyps mit einer höheren Störstellenkonzentration als derjenigen der vierten Halbleiterschichten durch den Isolationsfilm unter Verwendung des Resists als eine Maske, welche die Öffnung aufweist, und eines Diffundierens der Störstellen des ersten Leitfähigkeitstyps seichter als Böden der vierten Halbleiterschichten, um hierdurch eine fünfte Halbleiterschicht des ersten Leitfähigkeitstyps, welche in Verbindung mit der dritten Halbleiterschicht steht, selektiv auszubilden; einen neunten Schritt eines Stapelns eines Isolationsmaterials auf dem Abschnitt des Isolationsfilms, der nach dem siebten Schritt frei ist, und auf einer Oberfläche des leitfähigen Materials; einen zehnten Schritt eines Stapelns eines Resists auf einer Oberfläche des Isolationsmaterials, eines Ausbildens einer Öffnung hierin, welche die fünfte Halbleiterschicht und Abschnitte der vierten Halbleiterschichten, die an die fünfte Halbleiterschicht angrenzen, umgibt, eines selektiven Entfernens des Isolationsmaterials und des Isolationsfilms unter Verwendung des Resists als einer Maske, welche die Öffnung aufweist, um hierdurch die fünfte und die vierten Halbleiterschichten freizulegen; einen elften Schritt eines Stapelns einer leitfähigen Schicht auf den vierten und der fünften Halbleiterschicht, die nach dem zehnten Schritt frei und auf der Oberfläche des Isolationsmaterials ist; und einen zwölften Schritt eines Stapelns einer leitfähigen Schicht auf einer zweiten Hauptoberfläche des Halbleitersubstrats, die sich auf einer gegenüberliegenden Seite bezüglich der ersten Hauptoberfläche befindet.

**[0045]** Bei dem vorstehend erwähnten Verfahren kann in dem dritten Schritt der Abschnitt des Resists

als eine Mehrzahl von Regionen belassen werden, die in der Gestalt von Säulen verstreut sind und parallel zueinander angeordnet sind, um hierdurch das Resistmuster zu erhalten, und kann in dem zehnten Schritt die Öffnung des Resists so ausgebildet werden, dass sie die fünfte und die vierten Halbleiterschichten mit Ausnahme von Abschnitten der Oberflächen der vierten Halbleiterschichten, die an die Innenwände angrenzen und sich entlang diesen befinden, umgibt.

**[0046]** Ein Verfahren zum Herstellen einer weiteren beispielhaften Halbleiteranordnung mit isoliertem Gate kann aufweisen: einen ersten Schritt eines Ausbildens eines Halbleitersubstrats, welches eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps und eine zweite, auf einer Oberfläche der ersten Halbleiterschicht angeordnete Halbleiterschicht eines zweiten Leitfähigkeitstyps aufweist; einen zweiten Schritt eines Implantierens von Fremdatomen bzw. Störstellen des ersten Leitfähigkeitstyps in eine erste Hauptoberfläche des Halbleitersubstrats, die sich auf der Seite der zweiten Halbleiterschicht des Halbleitersubstrats befindet, um hierdurch eine dritten Halbleiterschicht des ersten Leitfähigkeitstyps auszubilden; einen dritten Schritt eines Stapelns eines Resists auf der ersten Hauptoberfläche, eines selektiven Entfernens des Resists so, dass ein Abschnitt des Resists als eine Mehrzahl von Regionen, die in der Gestalt von Säulen verstreut sind und parallel zueinander angeordnet sind, so belassen wird, dass ein Resistmuster ausgebildet wird, eines selektiven Implantierens von Störstellen des zweiten Leitfähigkeitstyps unter Verwendung des Resistmusters als einer Maske, und eines Diffundierens der Störstellen des zweiten Leitfähigkeitstyps in einer Oberfläche der dritten Halbleiterschicht, um hierdurch vierte Halbleiterschichten des zweiten Leitfähigkeitstyps mit einer höheren Störstellenkonzentration als die zweite Halbleiterschicht auszubilden; einen vierten Schritt eines Ausbildens eines Abschirmfilms auf der ersten Hauptoberfläche, eines Ausbildens einer Öffnung in dem Abschirmfilms auf einem Abschnitt einer Oberfläche der vierten Halbleiterschichten so, dass sich die Öffnung entlang einer Oberfläche von Säulen der vierten Halbleiterschichten erstreckt, eines selektiven Entfernens eines Halbleiters hinab zu der zweiten Halbleiterschicht unter Verwendung des Abschirmfilms als eine Maske, welche die Öffnung aufweist, um hierdurch nutförmige Innenwände, die Nuten definieren, auszubilden, und hiernach eines Entfernens des Abschirmfilms; einen fünften Schritt eines Ausbildens eines Isolationsfilms auf Oberflächen der nutförmigen Innenwände und auf der ersten Hauptoberfläche; einen sechsten Schritt eines Stapelns eines leitfähigen Materials auf dem Isolationsfilm so, dass die Nuten aufgefüllt werden; einen siebenten Schritt eines einheitlichen Entfernens des leitfähigen Materials unter Belassen des Isolationsfilms, bis ein Oberfläche des leitfähigen Materials, das in den Nuten

vergraben ist, von einer Oberfläche eines Abschnitts des Isolationsfilms, der auf der ersten Hauptoberfläche ausgebildet ist, zurückgesetzt ist; einen achten Schritt eines Stapeln eines Resists auf einem Abschnitt des Isolationsfilms, der nach dem siebenten Schritt auf der ersten Hauptoberfläche freiliegt, und der Oberfläche des leitfähigen Materials, eines Ausbildens einer Öffnung hierin in einer Position derart, dass sie einen Bereich, der dem in dem dritten Schritt in der Gestalt von Säulen belassenen Resist entspricht, umgibt und Abschnitte der Oberflächen der vierten Halbleiterschichten, die an den Bereich angrenzen, umgibt, eines selektiven Implantierens von Störstellen des ersten Leitfähigkeitstyps mit einer höheren Störstellenkonzentration als derjenigen der vierten Halbleiterschichten durch den Isolationsfilm unter Verwendung des Resists als eine Maske, welche die Öffnung aufweist, und eines Diffundierens der Störstellen des ersten Leitfähigkeitstyps, um hierdurch eine fünfte Halbleiterschicht des ersten Leitfähigkeitstyps, welche in Verbindung mit der dritten Halbleiterschicht steht, selektiv auszubilden; einen neunten Schritt eines Stapelns eines Isolationsmaterials auf dem Abschnitt des Isolationsfilms, der nach dem siebenten Schritt freigelegt ist, und auf einer Oberfläche des leitfähigen Materials; einen zehnten Schritt eines Stapelns eines Resists auf einer Oberfläche des Isolationsmaterials, eines Ausbildens einer Öffnung hierin, welche die fünfte Halbleiterschicht und die vierten Halbleiterschichten mit Ausnahme der Abschnitte der Oberflächen der vierten Halbleiterschichten, die an die Innenwände angrenzen und sich entlang diesen befinden, und mit Ausnahme eines Abschnitts einer Oberfläche der fünften Halbleiterschicht umgibt, eines selektiven Entfernens des Isolationsmaterials und des Isolationsfilms unter Verwendung des Resists als einer Maske, welche die Öffnung aufweist, um hierdurch die fünfte und die vierten Halbleiterschichten freizulegen; einen elften Schritt eines Stapelns einer leitfähigen Schicht auf den vierten und der fünften Halbleiterschicht, die nach dem zehnten Schritt freigelegt sind, und auf der Oberfläche des Isolationsmaterials; und einen zwölften Schritt eines Stapelns einer leitfähigen Schicht auf einer zweiten Hauptoberfläche des Halbleitersubstrats, die sich auf einer gegenüberliegenden Seite bezüglich der ersten Hauptoberfläche befindet.

**[0047]** Ein zweiter Gesichtspunkt der vorliegenden Erfindung betrifft ein Verfahren zum Herstellen einer Halbleiteranordnung mit isoliertem Gate, welches aufweist: einen ersten Schritt eines Ausbildens eines Halbleitersubstrats, welches eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps und eine zweite, auf einer Oberfläche der ersten Halbleiterschicht angeordnete Halbleiterschicht eines zweiten Leitfähigkeitstyps aufweist; einen zweiten Schritt eines Implantierens von Fremdatomen bzw. Störstellen des ersten Leitfähigkeitstyps in eine ersten Hauptoberfläche des Halbleitersubstrats, die sich auf der Seite der

zweiten Halbleiterschicht des Halbleitersubstrats befindet, um hierdurch eine dritten Halbleiterschicht des ersten Leitfähigkeitstyps auszubilden; einen dritten Schritt eines Stapelns eines Resists auf der ersten Hauptoberfläche, eines selektiven Entfernens des Resists, so, dass ein Abschnitt des Resists als eine Mehrzahl von Regionen, die in der Gestalt von zueinander parallelen, diskontinuierlichen Säulen angeordnet sind, so belassen wird, dass ein Resistmuster ausgebildet wird, eines selektiven Implantierens von Störstellen des zweiten Leitfähigkeitstyps unter Verwendung des Resistmusters als einer Maske, und eines Diffundierens der Störstellen des zweiten Leitfähigkeitstyps in einer Oberfläche der dritten Halbleiterschicht, um einen Abschnitt einer Oberfläche der dritten Halbleiterschicht zu belassen, um hierdurch eine vierte Halbleiterschicht des zweiten Leitfähigkeitstyps mit einer höheren Störstellenkonzentration als die zweite Halbleiterschicht auszubilden; einen vierten Schritt eines Ausbildens eines Abschirmfilms auf der ersten Hauptoberfläche, eines Ausbildens einer Öffnung in dem Abschirmfilms auf einem Abschnitt einer Oberfläche der vierten Halbleiterschicht so, dass sich die Öffnung entlang einer Oberfläche von Säulen der vierten Halbleiterschichten erstreckt, eines selektiven Entfernens eines Halbleiters hinab zu der zweiten Halbleiterschicht unter Verwendung des Abschirmfilms als eine Maske, welche die Öffnung aufweist, um hierdurch nutförmige Innenwände, die Nuten definieren, auszubilden, und hiernach eines Entfernens des Abschirmfilms; einen fünften Schritt eines Ausbildens eines Isolationsfilms auf Oberflächen der nutförmigen Innenwände und auf der ersten Hauptoberfläche; einen sechsten Schritt eines Stapelns eines leitfähigen Materials auf dem Isolationsfilm so, dass die Nuten aufgefüllt werden; einen siebenten Schritt eines einheitlichen Entfernens des leitfähigen Materials unter Belassen des Isolationsfilms, bis eine Oberfläche des leitfähigen Materials, das in den Nuten vergraben ist, von einer Oberfläche eines Abschnitts des Isolationsfilms, der auf der ersten Hauptoberfläche ausgebildet ist, zurückgesetzt ist; einen acht Schritt eines Stapelns eines Zwischenschichtisolationsfilms auf einem Abschnitt des Isolationsfilms, der nach dem siebenten Schritt freiliegt, und der Oberfläche des leitfähigen Materials; einen neunten Schritt eines Stapelns eines Resists auf einer Oberfläche des Zwischenschichtisolationsfilms, eines Ausbildens einer Öffnung hierin, welche die dritte und die vierten Halbleiterschicht mit Ausnahme von Abschnitten von Oberflächen der vierten Halbleiterschichten, die an die Innenwände angrenzen und sich entlang diesen befinden, und mit Ausnahme von Abschnitten der freiliegenden Oberfläche der dritten Halbleiterschicht, die an die Abschnitte der Oberflächen der vierten Halbleiterschichten angrenzen, umgibt, eines selektiven Entfernens des Zwischenschichtisolationsfilms und des Isolationsfilms unter Verwendung des Resists als einer Maske, welche die Öffnung aufweist, um hierdurch die dritte Halbleiter-

schicht und die Abschnitte der vierten Halbleiterschichten, die an die dritte Halbleiterschicht angrenzen, freizulegen; einen zehnten Schritt eines Stapelns einer leitfähigen Schicht auf Oberflächen der dritten und der vierten Halbleiterschichten, die nach dem neunten Schritt freigelegt sind, und auf der Oberfläche des Zwischenschichtisolationsfilms; und einen elften Schritt eines Stapelns einer leitfähigen Schicht auf einer zweiten Hauptoberfläche des Halbleitersubstrats, die sich auf einer gegenüberliegenden bezüglich der ersten Hauptoberfläche befindet.

**[0048]** Bei der beispielhaften Halbleiteranordnung mit isoliertem Gate ist die fünfte Halbleiterschicht auf den Oberflächen der dritten und der vierten Halbleiterschicht so angeordnet, dass sie sich über die dritte und die vierte Halbleiterschicht hinweg erstreckt, eine Verbindungsstelle zwischen der fünften und der vierten Halbleiterschicht einer Oberfläche ausgesetzt ist, und die Bodenfläche der fünften Halbleiterschicht an einer seichteren Position als der Dicke der vierten Halbleiterschicht angeordnet ist. Daher bleibt auch dann, wenn die freiliegende Oberfläche der dritten Halbleiterschicht, die an die vierte Halbleiterschicht angrenzt, klein wird, die Zellengröße klein, ist die ON-Spannung vermindert, schaltet ein parasitärer Transistor nicht leicht durch, und fällt der Wert eines Stroms, der beim Abschalten beendet werden kann, nicht ab, da die erste Haupteletrode über die fünfte Halbleiterschicht einen Kontakt zwischen der dritten und der vierten Halbleiterschicht herstellt. Daher ist der Stromverbrauch der Halbleiteranordnung mit isoliertem Gate niedrig, ist der RBSOA der Halbleiteranordnung mit isoliertem Gate groß, und ist die Zuverlässigkeit der Halbleiteranordnung mit isoliertem Gate hoch.

**[0049]** Falls die Mehrzahl der nutförmigen Innenwände angeordnet ist, die freiliegende Oberfläche der fünften Halbleiterschicht zwischen benachbarten Innenwänden ausgebildet ist und sich die freiliegende Oberfläche entlang den Innenwänden in der Richtung der Längsausdehnung der Innenwände erstreckt, ist es möglich, eine Mehrzahl der Steuerelektroden auszubilden. Ferner stellt die erste Haupteletrode über die fünfte Halbleiterschicht einen Kontakt zwischen der dritten und der vierten Halbleiterschicht auch dann her, wenn benachbarte vierte Halbleiterschichten durch die freiliegende Oberfläche der fünften Halbleiterschicht extrem nahe aneinander liegen.

**[0050]** Bei der Halbleiteranordnung mit isoliertem Gate sind die Grabenabstände klein und ist die Anordnung klein und dicht.

**[0051]** Falls die freiliegende Oberfläche der fünften Halbleiterschicht eine verstreute Konfiguration aufweist, stellt die erste Haupteletrode an dem Verbindungsabschnitt der vierten Halbleiterschicht, der die freiliegenden Oberflächenabschnitte der fünften

Halbleiterschicht, die zwischen benachbarten Innenwänden angeordnet ist, trennt, einen Kontakt zwischen der dritten und der vierten Halbleiterschicht her. Daher sind die Grabenabstände bei der Halbleiteranordnung mit isoliertem Gate klein und ist die Halbleiteranordnung mit isoliertem Gate klein und dicht.

**[0052]** Da bei der anderen beispielhaften Halbleiteranordnung mit isoliertem Gate der Film die Innenwände, die Abschnitte der Oberflächen der vierten Halbleiterschichten, die sich entlang den Innenwänden aneinander angrenzend befinden, und die Abschnitte der Oberflächen der fünften Halbleiterschicht, die an die Abschnitte der vierten Halbleiterschichten angrenzen, bedeckt, stehen die Verbindungsabschnitte der vierten Halbleiterschichten, welche die zwischen benachbarten Innenwänden angeordneten fünften Halbleiterschichten trennen, und die fünften Halbleiterschichten in abwechselndem Kontakt mit der ersten Hauptelektrode, während die vierten Halbleiterschichten, welche durch die fünften Halbleiterschichten und die Innenwände eingefasst sind, die erste Hauptelektrode nicht berühren. Daher dienen diese Abschnitte als ein Widerstand zwischen den vierten Halbleiterschichten, welche die erste Hauptelektrode berühren. Wenn ein großer Strom fließt, induziert der Widerstand einen Spannungsabfall innerhalb der vierten Halbleiterschichten. Daher schaltet ein parasitärer Transistor in der Halbleiteranordnung mit isoliertem Gate nicht leicht durch, ist ein RBSOA der Halbleiteranordnung mit isoliertem Gate groß, ist die Halbleiteranordnung mit isoliertem Gate klein und dicht und ist die Zuverlässigkeit der Halbleiteranordnung mit isoliertem Gate hoch.

**[0053]** Bei der weiteren beispielhaften Halbleiteranordnung mit isoliertem Gate nehmen die vierten Halbleiterschichten die fünfte Halbleiterschicht in der Gestalt von Säulen zwischen sich auf, ist die Mehrzahl der Innenwände entlang dieser säulenartigen Anordnung ausgebildet, ist der Zwischenschichtisolationsfilm auf der Oberfläche der Steuerelektrode ausgebildet und ist die erste Hauptelektrode auf den Oberflächen der vierten und der fünften Halbleiterschichten und dem Zwischenschichtisolationsfilm angeordnet. Daher ist es möglich, eine Mehrzahl der Steuerelektroden auszubilden. Es ist auch möglich, die freiliegende Oberfläche der fünften Halbleiterschicht klein auszubilden. Auch ohne Erzeugen des zusätzlichen Bereichs hinsichtlich des Zwischenschichtisolationsfilms zum Zwecke einer Ausrichtung einer Maske erzeugt die erste Hauptelektrode über die fünfte Halbleiterschicht einen Kontakt zwischen der dritten und den vierten Halbleiterschichten. Dies reduziert Grabenabstände und die Zellengröße. Daher ist die ON-Spannung verringert, schaltet ein parasitärer Transistor nicht leicht durch und fällt der Wert eines Stroms, der beim Abschalten beendet werden kann, nicht ab. So verwendet die Halbleiteranordnung mit

isoliertem Gate eine geringe Verbrauchsleistung, ist ein RBSOA der Halbleiteranordnung mit isoliertem Gate groß, ist die Zuverlässigkeit der Halbleiteranordnung mit isoliertem Gate hoch und ist die Halbleiteranordnung mit isoliertem Gate klein und dicht.

**[0054]** Falls die freiliegende Oberfläche der fünften Halbleiterschicht eine verstreute Konfiguration aufweist, ist der Verbindungsabschnitt der vierten Halbleiterschicht, der freiliegende Oberflächenabschnitte der fünften Halbleiterschicht, die sich zwischen benachbarten Innenwänden befinden, trennt, nicht mit dem Zwischenschichtisolationsfilm überzogen. Dieser Verbindungsabschnitt der vierten Halbleiterschicht ermöglicht der ersten Hauptelektrode, einen Kontakt zwischen der dritten und den vierten Halbleiterschichten zu erzeugen. Daher weist die Halbleiteranordnung mit isoliertem Gate noch kleinere Grabenabstände, eine geringe Größe und eine hohe Dichte auf.

**[0055]** Bei der noch weiteren Halbleiteranordnung mit isoliertem Gate bedeckt von den vierten Halbleiterschichten, die durch die fünfte Halbleiterschicht, welche eine verstreute Konfiguration zwischen benachbarten Innenwänden aufweist, angeordnet sind, der Isolationsfilm diese vierten Halbleiterschichten, die aneinander angrenzend entlang den Wandoberflächen vorliegen, und den Abschnitt der fünften Halbleiterschicht, der sich in der Umgebung dieser vierten Halbleiterschichten befindet. Daher weisen die Verbindungsabschnitte der vierten Halbleiterschichten, welche die fünfte Halbleiterschicht in die verstreute Konfiguration teilen, und die fünfte Halbleiterschicht abwechselnd einen Kontakt mit der ersten Hauptelektrode auf. Nachdem die vierten Halbleiterschichten, die zwischen der fünften Halbleiterschicht und den Innenwänden eingeschlossen sind, keinen Kontakt mit der ersten Hauptelektrode aufweisen, dienen diese Abschnitte als ein Widerstand zwischen den vierten Halbleiterschichten, die die erste Hauptelektrode berühren. Wenn ein großer Strom fließt; induziert der Widerstand einen Spannungsabfall innerhalb der vierten Halbleiterschichten. Daher schaltet ein parasitärer Transistor in der Halbleiteranordnung mit isoliertem Gate nicht leicht durch und ist ein RBSOA der Halbleiteranordnung mit isoliertem Gate groß. Ferner ist die Durchbruchcharakteristik während Kurzschlusses ohne Vergrößerung der Zellengröße verbessert. Die Halbleiteranordnung mit isoliertem Gate ist klein und dicht, und die Zuverlässigkeit der Halbleiteranordnung mit isoliertem Gate ist hoch.

**[0056]** Bei der Halbleiteranordnung mit isoliertem Gate, die gemäß der Definition in dem ersten Gesichtspunkt der vorliegenden Erfindung aufgebaut ist, bedeckt von den vierten Halbleiterschichten, die durch die eine verstreute Konfiguration aufweisende dritte Halbleiterschicht angeordnet sind, der Film die-

se vierten Halbleiterschichten, die aneinander angrenzend entlang den Wandoberflächen vorliegen, und den Abschnitt der dritten Halbleiterschicht, der sich in der Umgebung dieser vierten Halbleiterschichten befindet. Daher stehen die Verbindungsabschnitte der vierten Halbleiterschichten, welche die dritte Halbleiterschicht trennen, und die dritte Halbleiterschicht abwechselnd in Kontakt mit der ersten Hauptelektrode. Nachdem die vierten Halbleiterschichten, welche zwischen der dritten Halbleiterschicht und den Innenwänden eingeschlossen sind, nicht in Kontakt mit der ersten Hauptelektrode stehen, dienen diese Abschnitte als ein Widerstand zwischen den vierten Halbleiterschichten, welche die erste Halbleiterschicht berühren. Wenn ein großer Strom fließt, induziert der Widerstand einen Spannungsabfall innerhalb der vierten Halbleiterschichten. Daher schaltet bei der Halbleiteranordnung mit isoliertem Gate ein parasitärer Transistor nicht leicht durch, ist ein RSBOA der Halbleiteranordnung mit isoliertem Gate groß und ist die Zuverlässigkeit der Halbleiteranordnung mit isoliertem Gate hoch.

**[0057]** Falls die Mehrzahl der nutzförmigen Innenwände angeordnet ist und die dritte Halbleiterschicht in der verstreuten Konfiguration zwischen benachbarten Innenwänden entlang den Innenwänden angeordnet ist, bedeckt der Zwischenschichtisolationsfilm von den durch die dritte Halbleiterschicht angeordneten vierten Halbleiterschichten diese vierten Halbleiterschichten, die sich aneinander angrenzend entlang den Wandoberflächen befinden, und den Abschnitt der dritten Halbleiterschicht, der sich in der Umgebung jener vierten Halbleiterschichten befindet. Daher ist es möglich, eine Mehrzahl der Steuerelektroden auszubilden. Ferner stehen die Verbindungsabschnitte der vierten Halbleiterschichten, welche die dritte Halbleiterschicht trennen, und die dritte Halbleiterschicht abwechselnd in Kontakt mit der ersten Hauptelektrode, während die vierten Halbleiterschichten, die durch die dritte Halbleiterschicht und die Innenwände eingefasst sind, keinen Kontakt mit der ersten Hauptelektrode aufweisen. Daher dienen diese Abschnitte als ein Widerstand zwischen den vierten Halbleiterschichten, welche die erste Hauptelektrode berühren. Auch wenn die freiliegende Oberfläche der dritten Halbleiterschicht klein wird, stellt die erste Hauptelektrode über die fünfte Halbleiterschicht einen Kontakt zwischen der dritten und den vierten Halbleiterschichten her und wird bei den vierten Halbleiterschichten ein Spannungsabfall erzeugt, wenn ein großer Strom fließt. Deshalb schaltet ein parasitärer Transistor in der Halbleiteranordnung mit isoliertem Gate nicht leicht durch, ist ein RSBOA der Halbleiteranordnung mit isoliertem Gate groß, ist die Halbleiteranordnung mit isoliertem Gate klein und dicht und ist die Zuverlässigkeit der Halbleiteranordnung mit isoliertem Gate hoch.

**[0058]** Bei dem Verfahren zur Herstellung einer bei-

spielhaften Halbleiteranordnung mit isoliertem Gate stellt auch dann, wenn die freiliegende Oberfläche der dritten Halbleiterschicht klein wird, die erste Hauptelektrode über die fünfte Halbleiterschicht einen Kontakt zwischen der dritten und den vierten Halbleiterschichten her. Daher ist es möglich, eine Halbleiteranordnung mit isoliertem Gate herzustellen, die eine geringe Verbrauchsleistung verwendet, die einen großen RSBOA aufweist und die hoch zuverlässig ist, und das zu geringen Kosten und ohne komplizierte Herstellungsschritte.

**[0059]** Bei dem Verfahren zur Herstellung einer anderen beispielhaften Halbleiteranordnung mit isoliertem Gate ist es möglich, eine Halbleiteranordnung mit isoliertem Gate herzustellen, bei welcher ein zusätzlicher Bereich bezüglich des Zwischenschichtisolationsfilms zum Zweck einer Maskenausrichtung klein ist, die Zellenabstände klein sind, der Energieverbrauch niedrig ist, ein RSBOA groß ist und die Zuverlässigkeit hoch ist bei geringen Kosten und ohne komplizierte Herstellungsschritte.

**[0060]** Falls der Zwischenschichtisolationsfilm die Verbindungsabschnitte der vierten Halbleiterschichten, welche die freiliegende Oberfläche der fünften Halbleiterschicht, die zwischen benachbarten Innenwänden angeordnet ist, trennen, nicht bedeckt und die Verbindungsabschnitte der vierten Halbleiterschichten und der fünften Halbleiterschicht der ersten Hauptelektrode ermöglichen, einen Kontakt zwischen der dritten und den vierten Halbleiterschichten herzustellen, ist es möglich, eine Halbleiteranordnung mit isoliertem Gate herzustellen, bei der bei geringen Kosten und ohne komplizierte Herstellungs schritte die Zellenabstände klein sind.

**[0061]** Bei dem Verfahren zur Herstellung einer weiteren beispielhaften Halbleiteranordnung mit isoliertem Gate dienen die vierten Halbleiterschichten, die zwischen der fünften Halbleiterschicht und den Innenwänden eingeschlossen sind, als ein Widerstand zwischen den vierten Halbleiterschichten, welche einen Kontakt mit der ersten Hauptelektrode aufweisen. Wenn ein großer Strom fließt, induziert der Widerstand einen Spannungsabfall innerhalb der vierten Halbleiterschichten. Daher ist es möglich, zu geringen Kosten und ohne komplizierte Herstellungs schritte eine kleine, dichte und zuverlässige Halbleiteranordnung mit isoliertem Gate herzustellen, bei welcher ein parasitärer Transistor nicht leicht durchschaltet und ein RSBOA groß ist.

**[0062]** Bei dem Verfahren zur Herstellung einer Halbleiteranordnung mit isoliertem Gate gemäß dem zweiten Gesichtspunkt der vorliegenden Erfindung ist die freiliegende Oberfläche der dritten Halbleiterschicht klein ausgebildet. Die vierten Halbleiterschichten, die zwischen der dritten Halbleiterschicht und den Innenwänden angeordnet sind, dienen als

ein Widerstand zwischen den vierten Halbleiterschichten, die einen Kontakt mit der ersten Hauptelektrode aufweisen. Wenn eine großer Strom fließt, induziert der Widerstand einen Spannungsabfall innerhalb der vierten Halbleiterschichten. Daher ist es möglich, zu geringen Kosten und ohne komplizierte Herstellungsschritte eine kleine, dichte und zuverlässige Halbleiteranordnung mit isoliertem Gate herzustellen, bei welcher ein parasitärer Transistor nicht leicht durchschaltet und ein RBSOA groß ist.

[0063] Nachdem dem vorstehenden Hintergrund der Erfindung Rechnung getragen wurde, wird nun die Erfindung selbst auf der Grundlage der Figuren, welche spezifische Ausführungsformen darstellen, diskutiert werden.

[0064] Die vorgenannten und andere Aufgaben, Merkmale, Gesichtspunkte und Vorteile der vorliegenden Erfindung werden aus den nachstehenden genauen Beschreibung der vorliegenden Erfindung ersichtlicher werden, wenn sie im Zusammenhang mit den begleitenden Zeichnungen genommen wird, in welchen

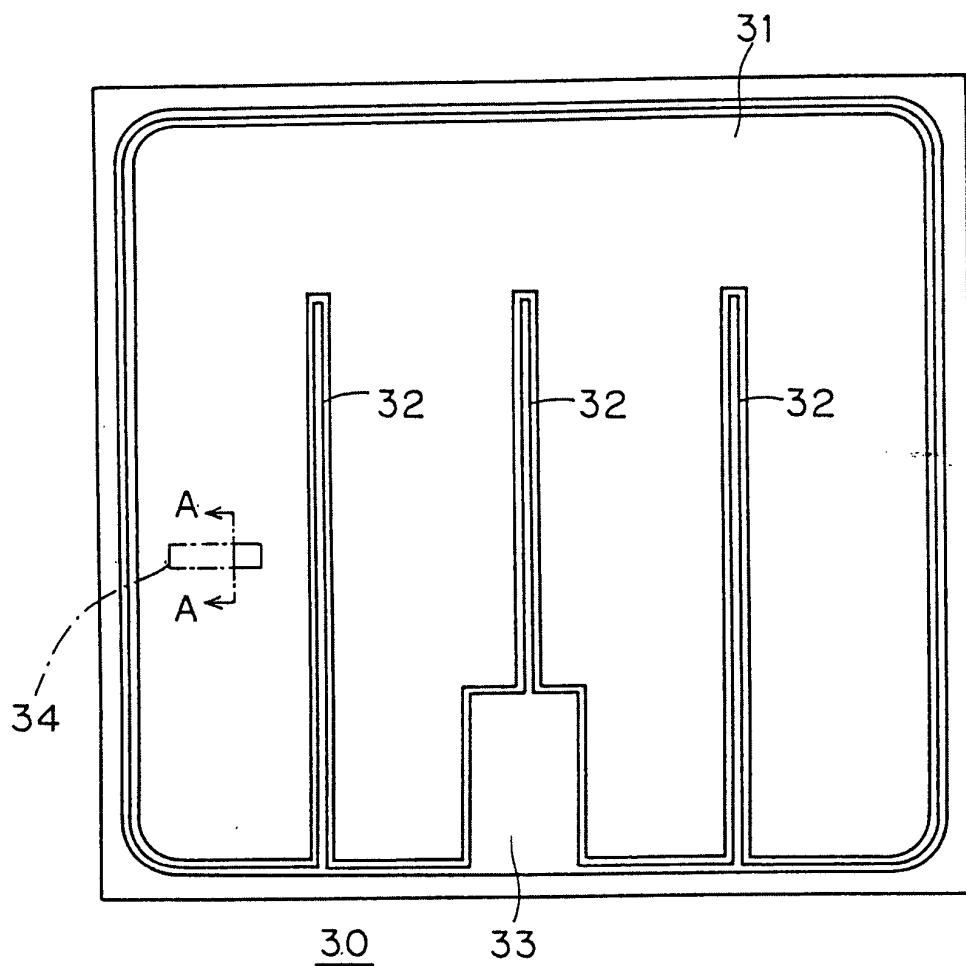

[0065] [Fig. 1](#) eine Draufsicht einer Halbleiteranordnung mit isoliertem Gate gemäß der vorliegenden Erfindung ist;

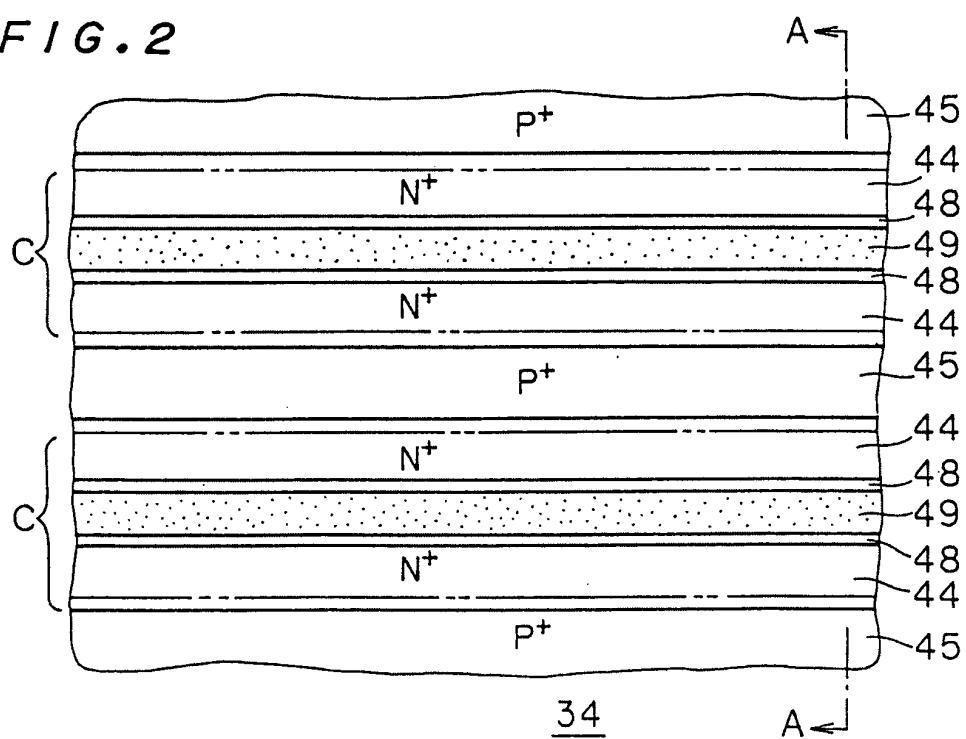

[0066] [Fig. 2](#) eine Teildraufsicht ist, welche einige Zellen einer beispielhaften Halbleiteranordnung mit isoliertem Gate zeigt;

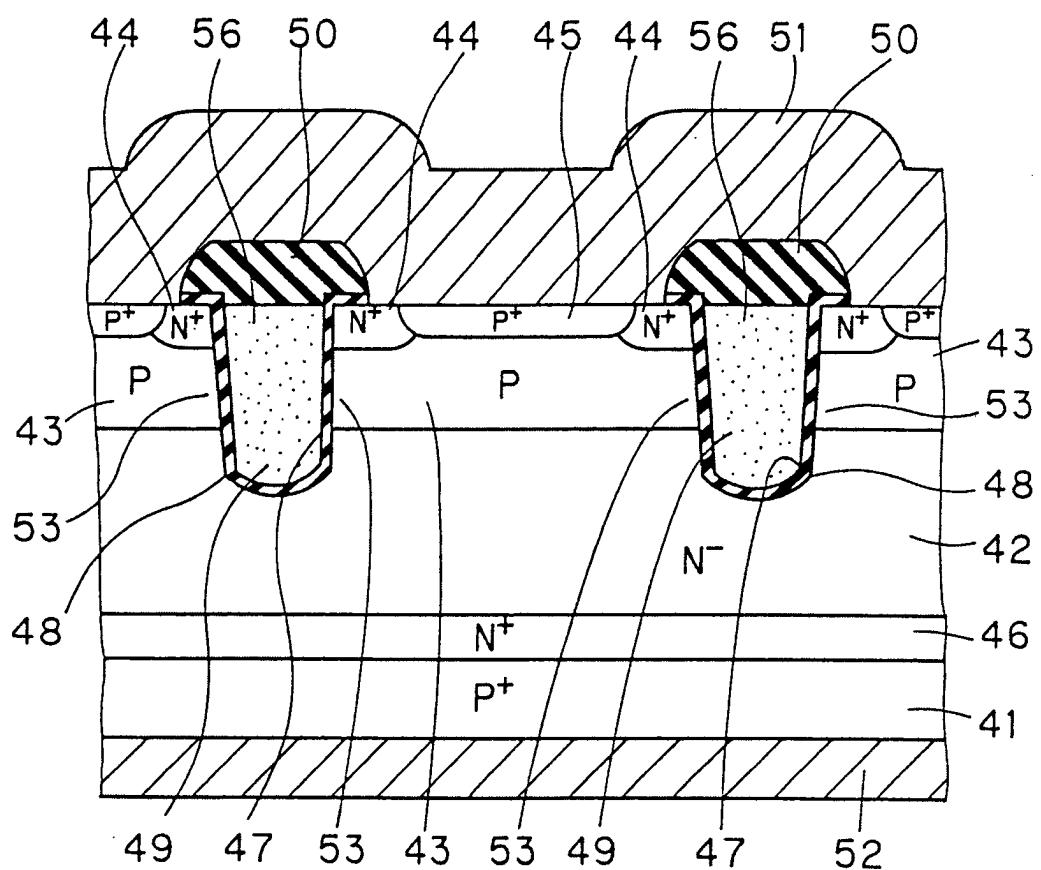

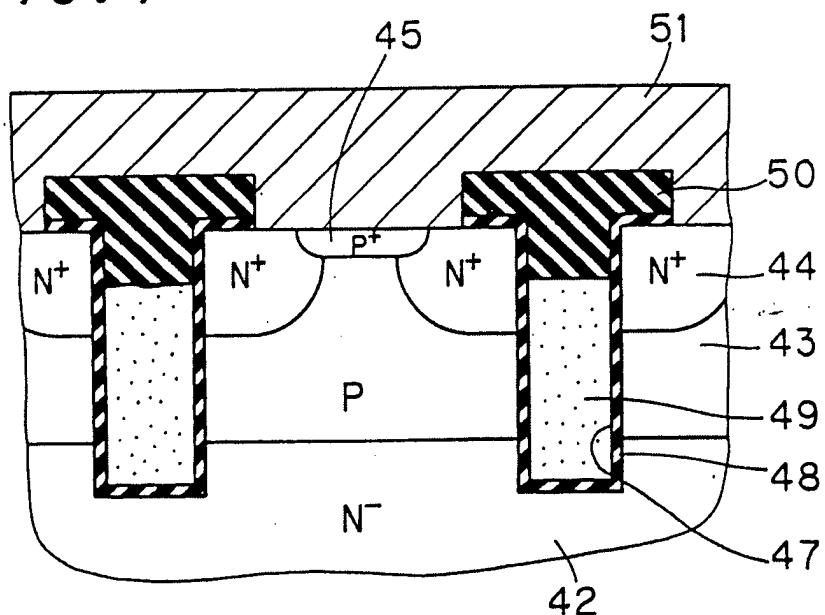

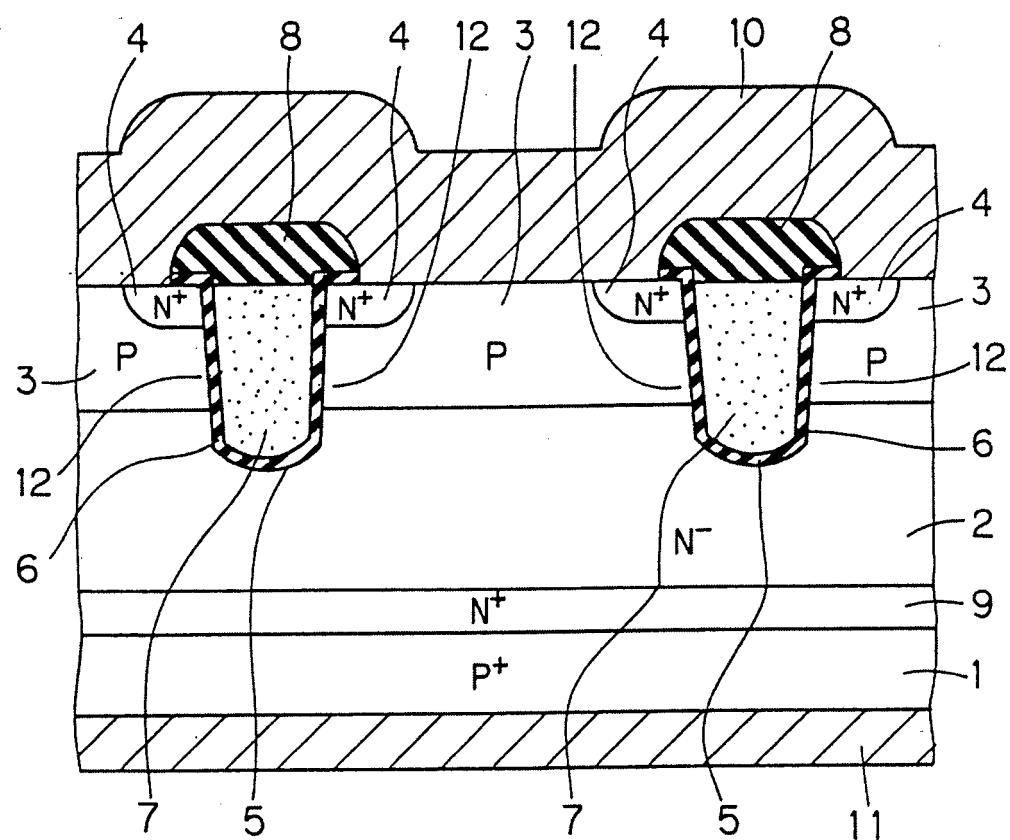

[0067] [Fig. 3](#) eine Teilschnittansicht ist, welche einige Zellen der Halbleiteranordnung mit isoliertem Gate von [Fig. 2](#) entlang Linien A-A genommen zeigt;

[0068] [Fig. 4](#) eine schematische Teilschnittansicht ist, welche die vorliegende Erfindung zeigt;

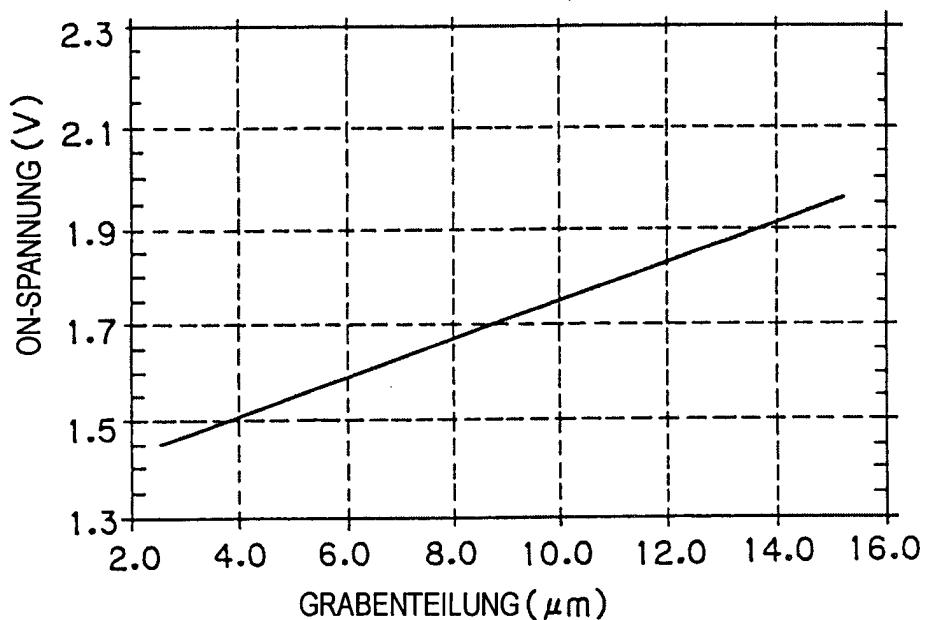

[0069] [Fig. 5](#) ein Graph ist, welcher eine Beziehung zwischen einer Grabenteilung und einer ON-Spannung in einem U-IGBT zeigt;

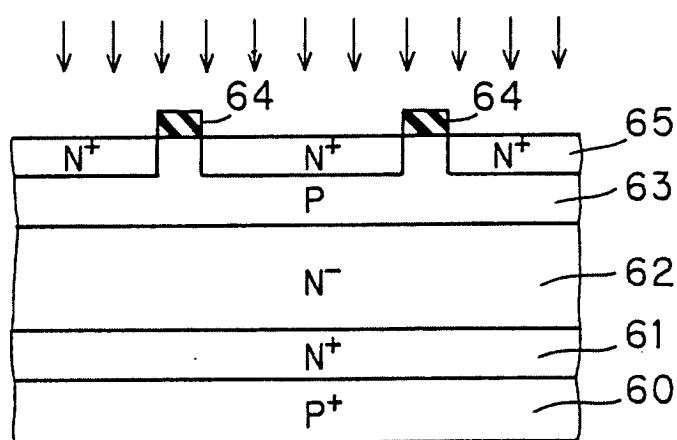

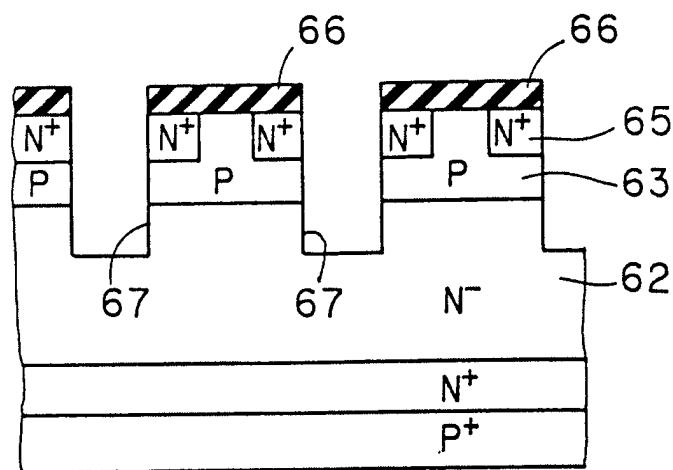

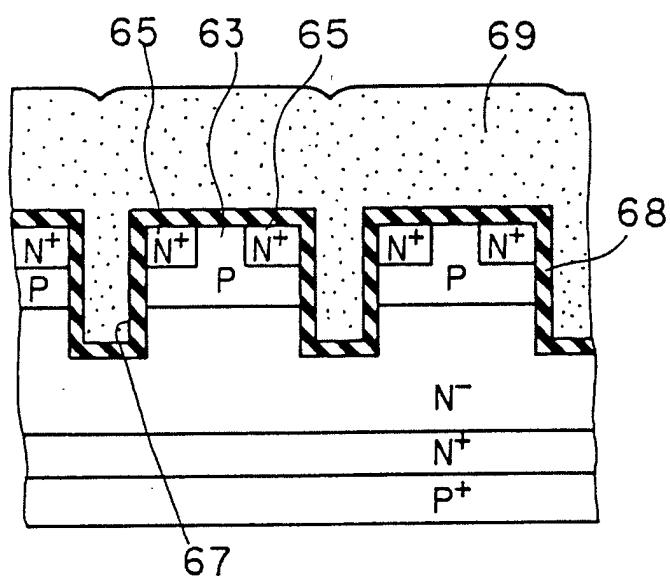

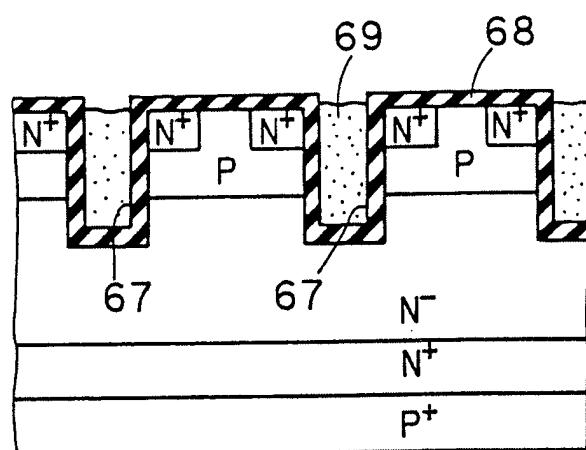

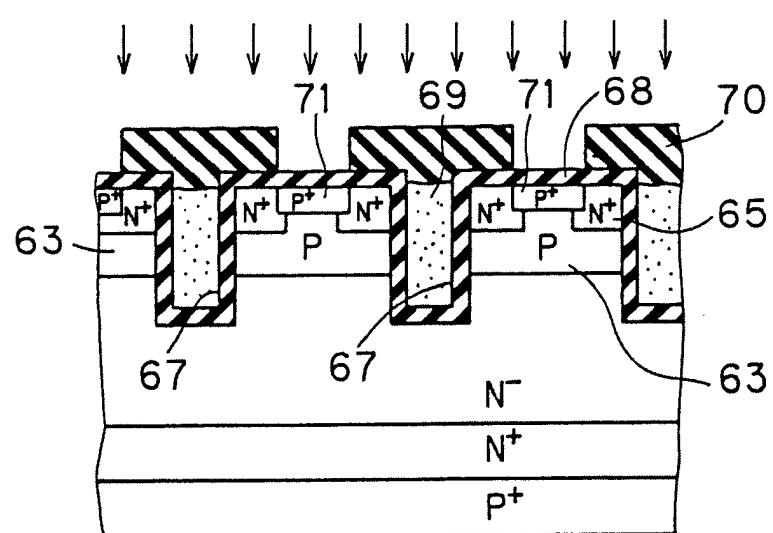

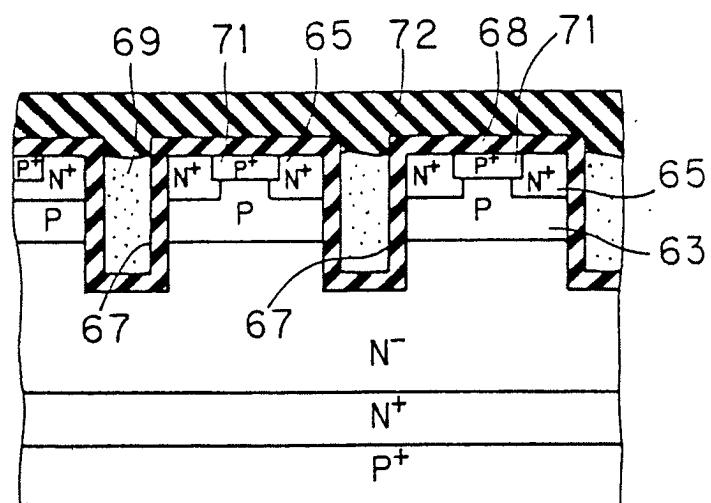

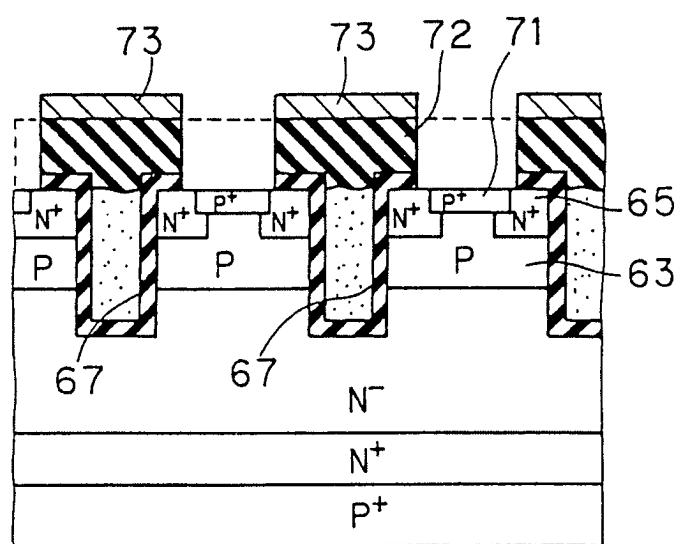

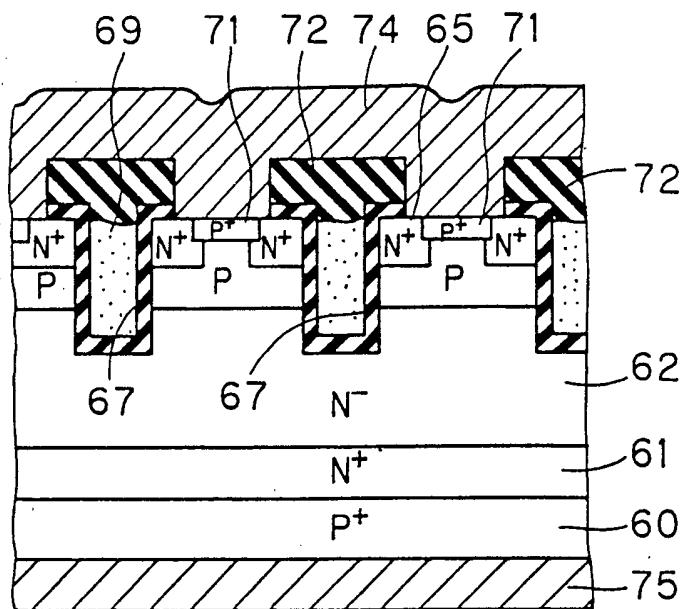

[0070] [Fig. 6](#) bis [Fig. 12](#) Teilschnittansichten eines Elements während Herstellungsschritten der Halbleiteranordnung mit isoliertem Gate gemäß der vorliegenden Erfindung sind;

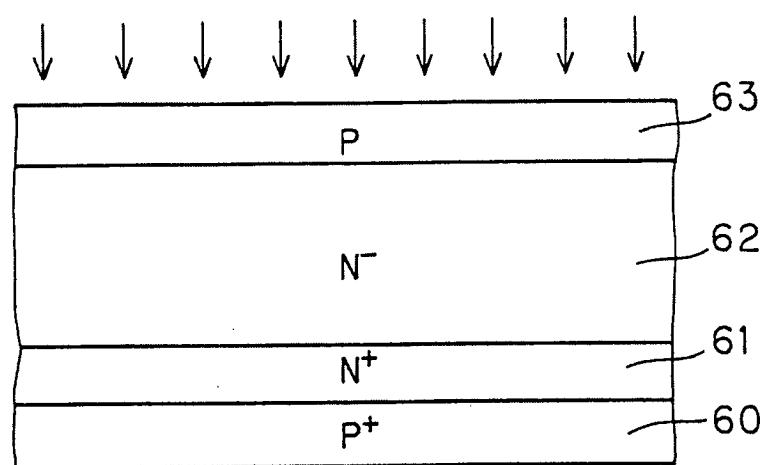

[0071] [Fig. 12](#) bis [Fig. 14](#) Teilschnittansichten eines Elements während Herstellungsschritten einer beispielhaften Halbleiteranordnung mit isoliertem Gate sind;

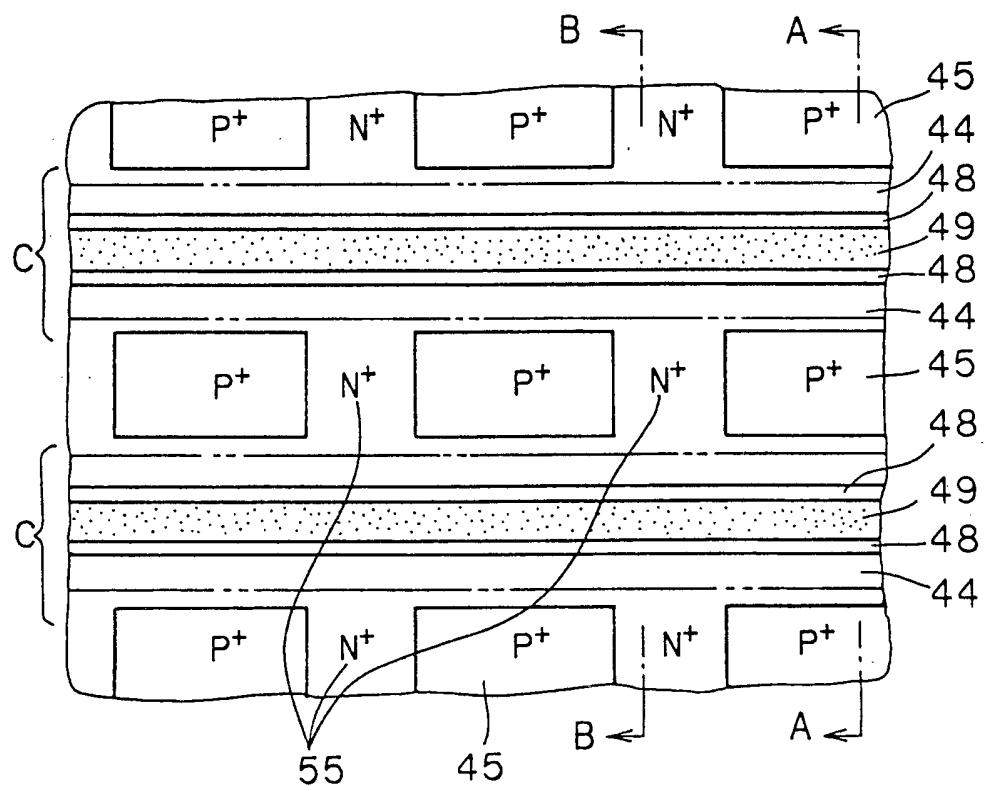

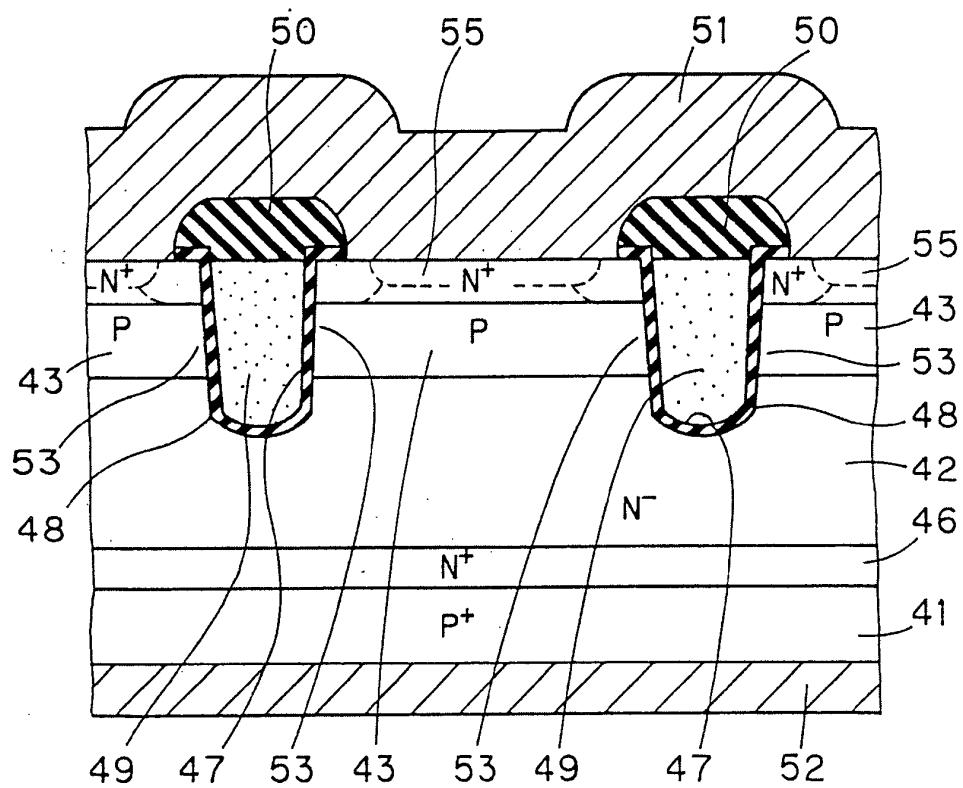

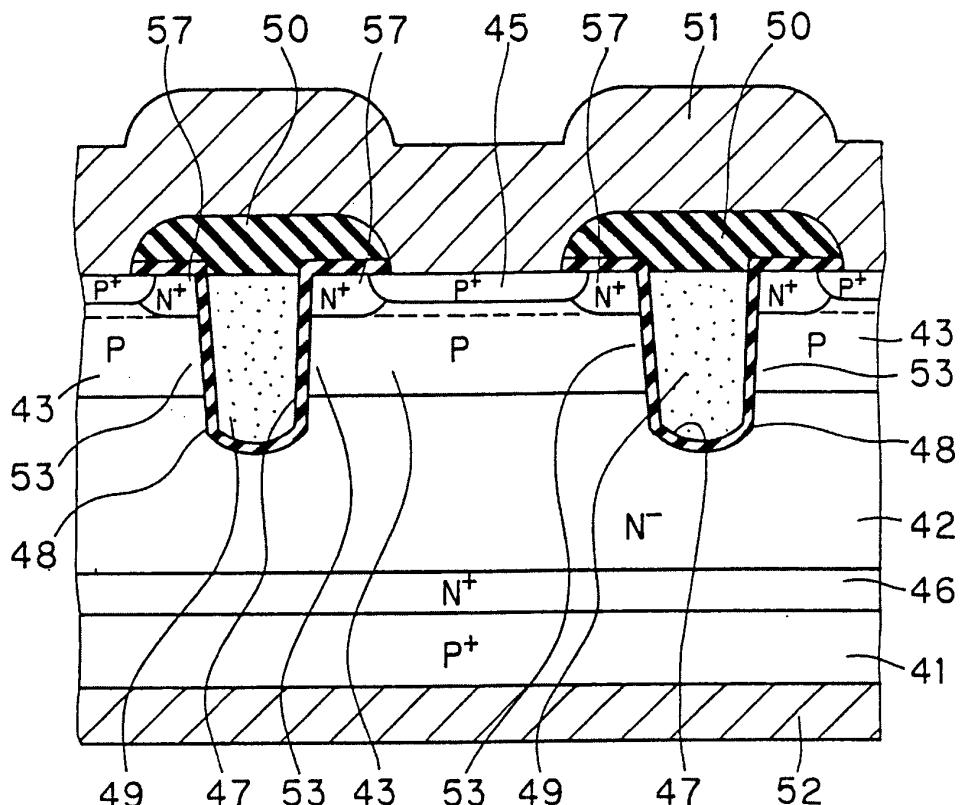

[0072] [Fig. 15](#) eine Teildraufsicht einer anderen beispielhaften Halbleiteranordnung mit isoliertem Gate ist, die nicht unter die vorliegende Erfindung fällt;

[0073] [Fig. 16](#) eine Teilschnittansicht der Halbleiteranordnung mit isoliertem Gate gemäß [Fig. 15](#) ist, ge-

nommen entlang Linien A-A;

[0074] [Fig. 17](#) eine Teilschnittansicht der Halbleiteranordnung mit isoliertem Gate gemäß [Fig. 15](#) ist, genommen entlang Linien B-B;

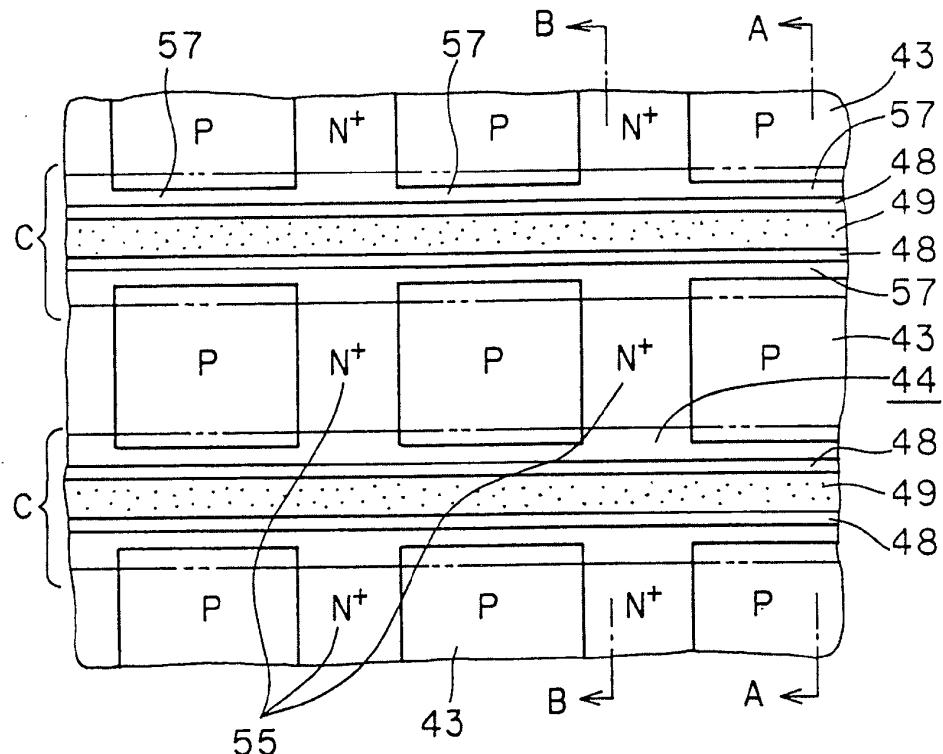

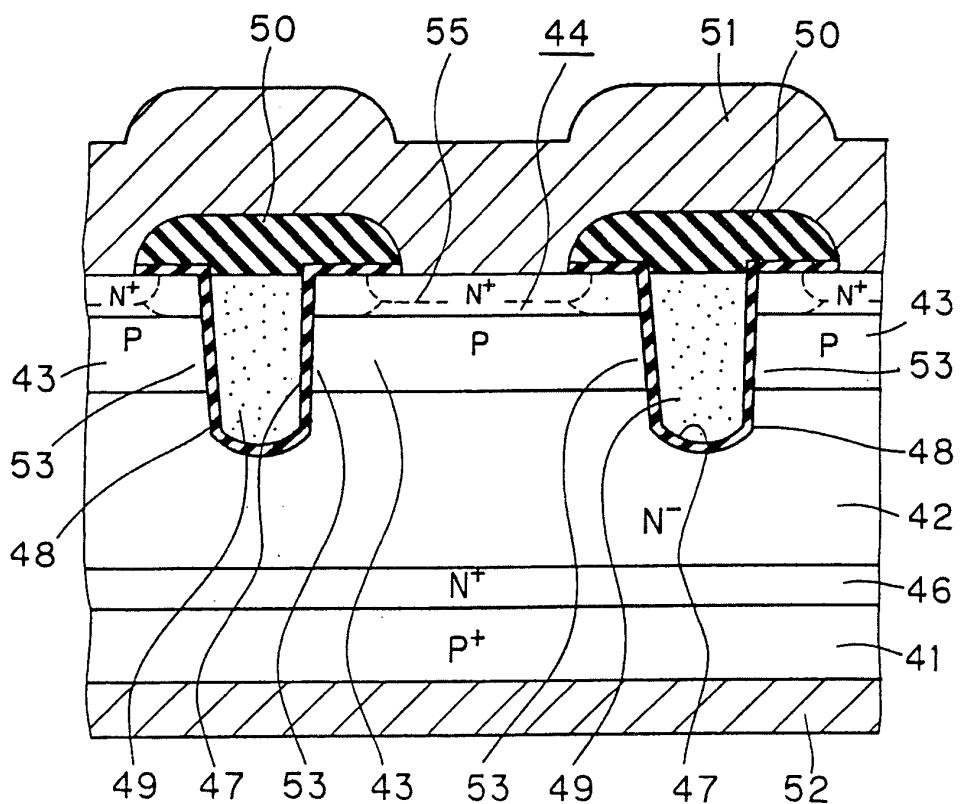

[0075] [Fig. 18](#) eine Teildraufsicht einer Halbleiteranordnung mit isoliertem Gate gemäß dner bevorzugten Ausführungsform der vorliegenden Erfindung ist;

[0076] [Fig. 19](#) eine Teilschnittansicht der Halbleiteranordnung mit isoliertem Gate gemäß [Fig. 18](#) ist, genommen entlang Linien A-A;

[0077] [Fig. 20](#) eine Teilschnittansicht der Halbleiteranordnung mit isoliertem Gate gemäß [Fig. 18](#) ist, genommen entlang Linien B-B;

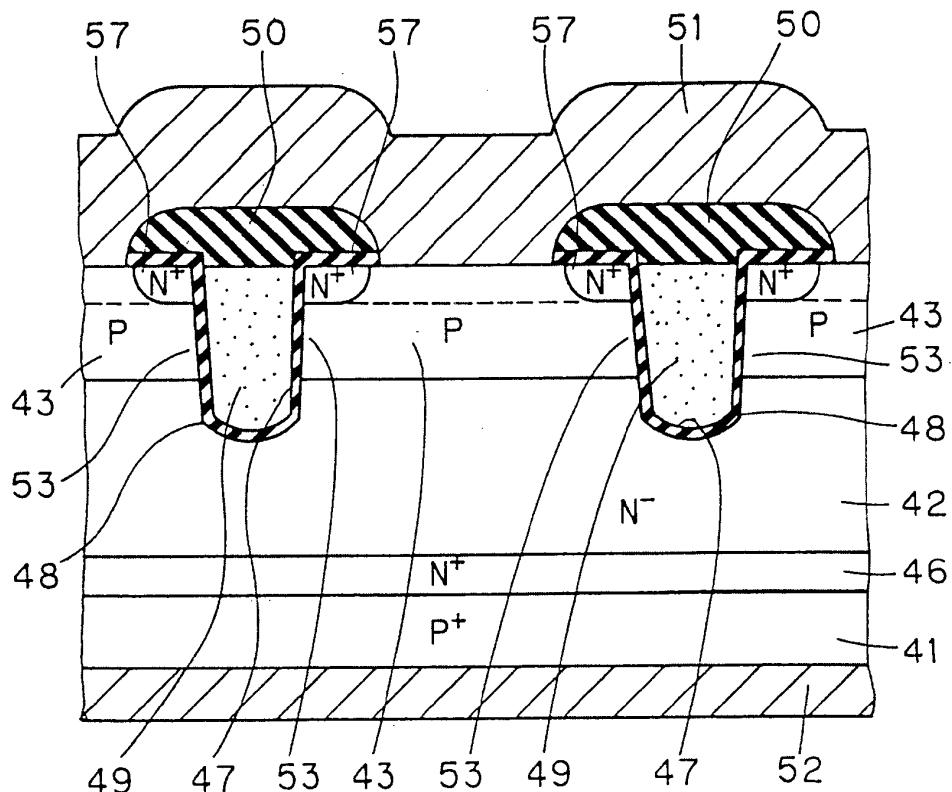

[0078] [Fig. 21](#) eine Teildraufsicht einer weiteren beispielhaften Halbleiteranordnung mit isoliertem Gate ist, die nicht unter die vorliegende Erfindung fällt;

[0079] [Fig. 22](#) eine Teilschnittansicht der Halbleiteranordnung mit isoliertem Gate gemäß [Fig. 21](#) ist, genommen entlang Linien A-A;

[0080] [Fig. 23](#) eine Teilschnittansicht der Halbleiteranordnung mit isoliertem Gate gemäß [Fig. 21](#) ist, genommen entlang Linien B-B;

[0081] [Fig. 24](#) und [Fig. 25](#) Teilschnittansichten eines Elements während weiterer Herstellungsschritte der Halbleiteranordnung mit isoliertem Gate sind;

[0082] [Fig. 26](#) eine Teilschnittansicht einer herkömmlichen Halbleiteranordnung mit isoliertem Gate ist;

[0083] [Fig. 27](#) eine Teilschnittansicht einer anderen herkömmlichen Halbleiteranordnung mit isoliertem Gate ist;

[0084] [Fig. 28](#) eine schematische Darstellung ist, welche einen Kontaktrand in der anderen herkömmlichen Halbleiteranordnung mit isoliertem Gate zeigt;

[0085] [Fig. 29](#) eine Teilschnittansicht einer noch anderen Halbleiteranordnung mit isoliertem Gate ist; und

[0086] [Fig. 30](#) eine schematische Darstellung ist, welche eine Seitendiffusion in der noch anderen herkömmlichen Halbleiteranordnung mit isoliertem Gate zeigt.

[0087] [Fig. 1](#) ist eine Draufsicht einer Halbleiteranordnung mit isoliertem Gate gemäß der vorliegenden Erfindung. Als ein Beispiel einer Halbleiteranordnung mit isoliertem Gate wird nachstehend ein U-IGBT beschrieben werden.

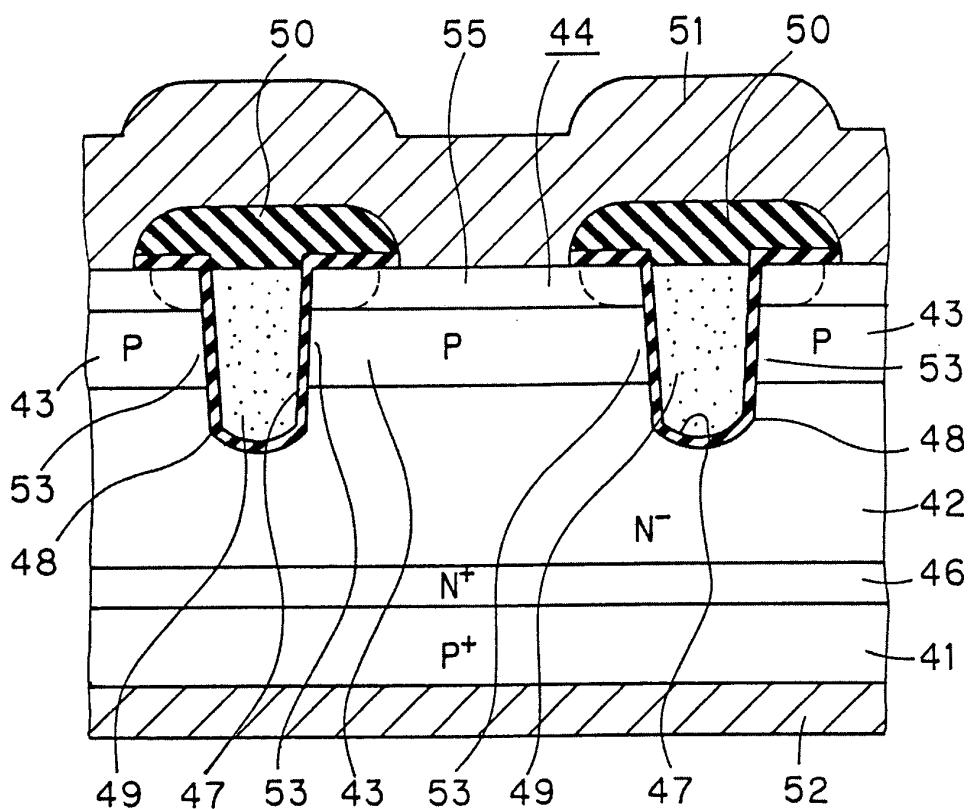

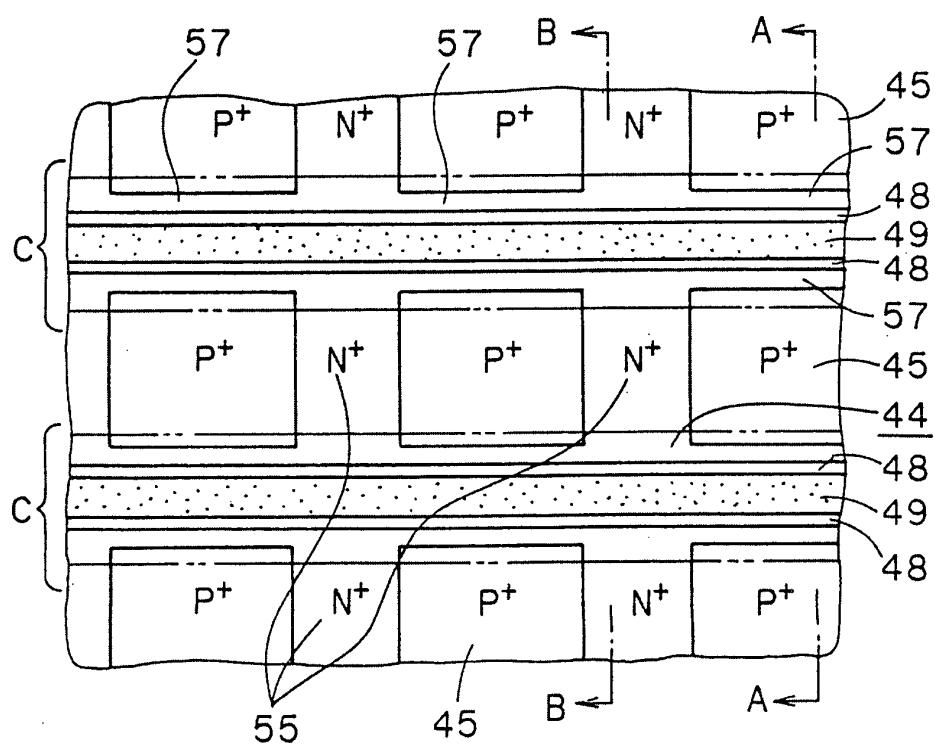

[0088] [Fig. 2](#) ist eine Teildraufsicht, welche einige Zellen des U-IGBT von [Fig. 1](#) zeigt, und [Fig. 3](#) zeigt einige Zellen von [Fig. 2](#) in einer Teilschnittansicht entlang Linien A-A. In [Fig. 2](#) sind die Zellen so gezeigt, wie sie sich darstellen, wenn eine Emitterelektrode **51** und ein Zwischenschichtisolationsfilm **50** entfernt sind.

[0089] In [Fig. 1](#) ist mit **30** ein U-IGBT bezeichnet, ist mit **31** eine Emitterelektrode bezeichnet, die als eine erste Hauptelektrode dient, sind mit **32** gateleistungen bezeichnet, ist mit **33** ein Gateanschlussfleck bezeichnet, und ist mit **34** ein Teil von Zellen bezeichnet.

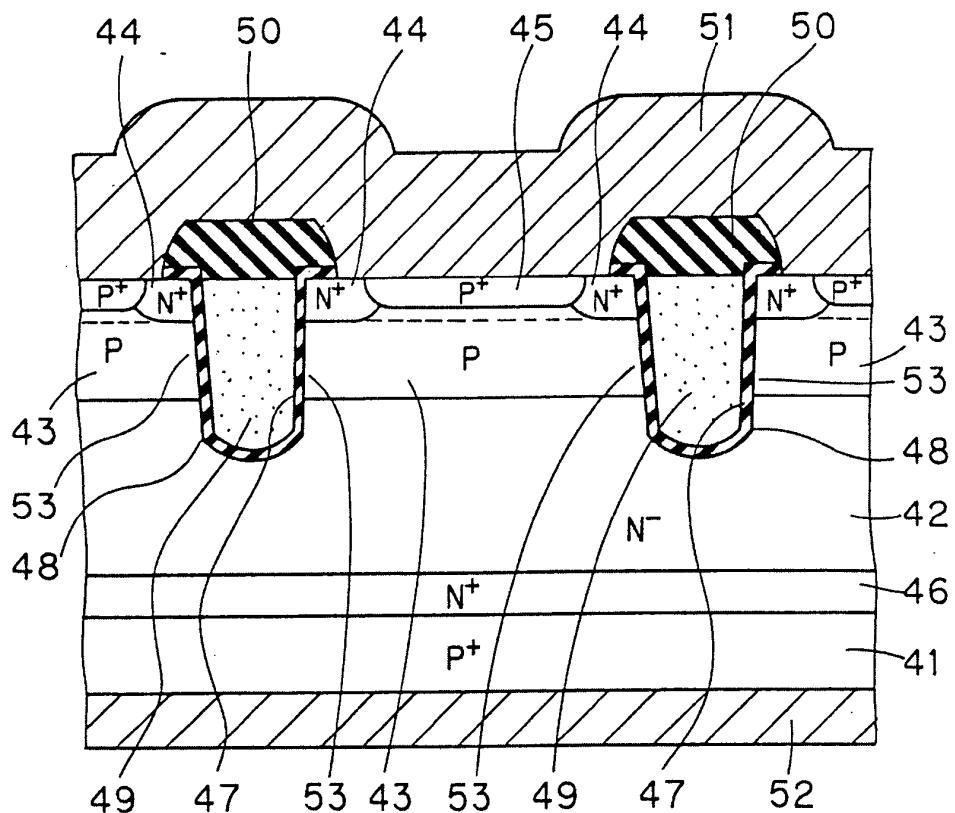

[0090] In [Fig. 2](#) und [Fig. 3](#) sind mit **41** eine P<sup>+</sup>-Kollektorschicht bezeichnet, die als eine erste Halbleiterschicht dient, ist mit **42** eine N<sup>-</sup>-Schicht bezeichnet, die als eine zweite Halbleiterschicht dient, ist mit **43** ein P-Basisschicht bezeichnet, die als eine dritte Halbleiterschicht dient, ist mit **44** eine N<sup>+</sup>-Emitterschicht bezeichnet, die als eine vierte Halbleiterschicht dient, sind mit **45** P<sup>+</sup>-Halbleiterschichten bezeichnet, die als eine fünfte Halbleiterschicht dienen, ist mit **46** eine N<sup>+</sup>-Pufferschicht bezeichnet, sind mit **47** Innenwände bezeichnet, die jeweils in der Gestalt einer Nut ausgebildet sind. Durch die Innenwände **47** sind Gräben definiert. Mit **48** sind Gateisolationsfilme bezeichnet, mit **49** sind Gateelektroden bezeichnet, die jeweils als eine Steuerelektrode dienen, mit **50** ist der Zwischenschichtisolationsfilm bezeichnet, und mit **51** ist die Emitterelektrode bezeichnet, die als die erste Hauptelektrode dient. Die Emitterelektrode **51** ist ein Abschnitt der Emitterelektrode **31** von [Fig. 1](#). Mit **52** ist eine Kollektorelektrode bezeichnet, die als eine zweite Hauptelektrode dient, und mit **53** sind Kanalregionen bezeichnet. Bereiche C, die in [Fig. 2](#) durch Klammern und strichpunktige Linien definiert sind, sind Bereiche, die mit dem Zwischenschichtisolationsfilm **50** bedeckt sind.

[0091] In der vorliegenden Ausführungsform, die später beschrieben werden wird, bezeichnen gleiche bzw. ähnliche Symbole gleiche bzw. ähnliche Strukturen.

[0092] Üblicherweise sind die Gateisolationsfilme **48** thermische Oxidationsfilme aus SiO<sub>2</sub> und sind die Gateelektroden **49** aus Polysilizium hergestellt, das mit Störstellen bzw. Fremdatomen des Leitfähigkeitsstyps N dotiert ist. Der Zwischenschichtisolationsfilm **50** ist aus einem Silikatglas hergestellt, welches Bor und Phosphor aufweist (nachstehend als "BPSG" bezeichnet). Die Emitterelektrode **51**, die Gateleitungen **32** und der Gateanschlussfleck **33** sind aus Si enthaltendem Al (nachstehend als "Al-Si" bezeichnet) hergestellt. Die Kollektorelektrode **52** ist aus einer AlMo-NiAu-Legierung hergestellt.

[0093] Die Gateleitungen **32** sind mit den Gateelek-

troden **49** so verbunden, dass Polysiliziumabschnitte in Wegen von den Gateelektroden **49** zu dem Gateanschlussfleck **33** klein sind, sodass ein elektrischer Widerstand von den Gateelektroden **49** zu dem Gateanschlussfleck **33** reduziert ist und das Element einheitlich über die gesamte Oberfläche des Elements gesteuert wird.

[0094] Bei diesem U-IGBT ist die N<sup>+</sup>-Pufferschicht **46** auf ein Oberfläche der P<sup>+</sup>-Kollektorschicht **41** angeordnet und ist die N<sup>-</sup>-Schicht **42** auf einer Oberfläche der N<sup>+</sup>-Pufferschicht **46** angeordnet. Ferner ist die P-Basisschicht **43** auf der N<sup>-</sup>-Schicht **42** angeordnet. Die N<sup>+</sup>-Emitterschichten **44** sind auf einer Oberfläche der P-Basisschicht **43** mit Abständen derart angeordnet, dass sie Streifen ausbilden. Entlang der Längsausdehnung der Streifen der N<sup>+</sup>-Emitterschichten **44** sind die grabenförmigen Innenwände **47** ausgebildet, die sich von Oberflächen der N<sup>+</sup>-Emitterschichten **44** aus erstrecken und durch die P-Basissschicht **43** hindurch in die N<sup>-</sup>-Schicht **42** eindringen.

[0095] In einer durch die P-Basisschicht **43** und die N<sup>+</sup>-Emitterschichten **44**, die zwischen zwei benachbarten Innenwänden **47** vorliegen, definierten Oberflächen, sind die P<sup>+</sup>-Halbleiterschichten **45** in solcher Weise ausgebildet, dass Bodenflächen der P<sup>+</sup>-Halbleiterschichten **45** einen Kontakt mit der P-Basissschicht **43** aufweisen und die N<sup>+</sup>-Emitterschichten **44** an den beiden Enden teilweise überlappen, und dass Verbindungsstellen zwischen den N<sup>+</sup>-Emitterschichten **44** und den P<sup>+</sup>-Halbleiterschichten **45** einer Oberfläche ausgesetzt sind bzw. an einer Oberfläche freiliegen.

[0096] Die Störstellenkonzentration der P<sup>+</sup>-Halbleiterschichten **45** ist allgemein höher als diejenige der N<sup>+</sup>-Emitterschichten **44**. Falls die Störstellenkonzentration der N<sup>+</sup>-Emitterschichten **44** bei etwa  $1 \times (10^{18} - 10^{19})$  festgelegt ist, ist die Störstellenkonzentration der P<sup>+</sup>-Halbleiterschichten **45** bei etwa  $2 \times (10^{18} - 10^{19})$  festgelegt, also etwa zwei mal höher als die Störstellenkonzentration der N<sup>+</sup>-Emitterschichten **44**.

[0097] Die Gateisolationsfilme **48** sind in den Innenwänden **47** angeordnet. Die Gateisolationsfilme **48** erstrecken sich bis hinauf zu den Oberflächen der N<sup>+</sup>-Emitterschichten **44**, welche an Öffnungen **56** der Innenwände **47** angrenzen. In jedem Graben, der von jeder Innenwand **47** über jeweilige Gateisolationsfilme **48** umgeben ist, sind die jeweiligen Gateelektroden **49** bis hinauf zu den jeweiligen Öffnungen an den Oberfläche der N<sup>+</sup>-Emitterschichten **44** eingefüllt. Oberflächen der Gateelektroden **49** sind niedriger als Oberflächen der Gateisolationsfilme **48**, welche auf den Oberflächen der an die Öffnungen **56** der Innenwände **47** angrenzenden N<sup>+</sup>-Emitterschichten **44** ausgebildet sind.

[0098] In [Fig. 3](#) fliehen die Oberflächen der Gate-

lektroden **49** mit den Oberflächen der N<sup>+</sup>-Emitterschichten **44**. Obgleich die Oberflächen der Gateelektroden **49** weiter von den Oberflächen der N<sup>+</sup>-Emitterschichten **44** zurückgesetzt sein können, um Kanäle auszubilden, müssen die Oberflächen der Gateelektroden **49** in einer seichteren Position als der Boden der N<sup>+</sup>-Emitterschichten **44** angeordnet sein. Die Gateelektroden **49** stehen den Oberflächen der P-Basisschicht **43** über die Gateisolationsfilme **48** gegenüber. Die Oberflächen der P-Basisschicht **43** dienen als die Kanalregionen **53**.

**[0099]** Die Oberflächen der Gateelektroden **49** sind mit dem Zwischenschichtisolationsfilm **50** bedeckt. Über den Zwischenschichtisolationsfilm **50** ist die Emitterelektrode **51** auf einer Oberfläche des Elements angeordnet, in welcher die N<sup>+</sup>-Emitterschichten **44** und die P<sup>+</sup>-Halbleiterschichten **45** ausgebildet sind. Die N<sup>+</sup>-Emitterschichten **44** und die P-Basisschicht **43** stehen mit der Emitterelektrode **51** durch die P<sup>+</sup>-Halbleiterschichten **45** in Verbindung. Die Gateleitungen **32** und der Gateanschlussfleck **33**, die mit den Gateelektroden **49** verbunden sind, sind auf der Oberfläche des Elements angeordnet, während sie von den N<sup>+</sup>-Emitterschichten **44** und den P<sup>+</sup>-Halbleiterschichten **45** isoliert sind. Die Kollektorelektrode **52** ist auf der anderen Oberfläche der P<sup>+</sup>-Kollektorschicht **41** angeordnet.

**[0100]** Falls das Element eine Durchbruchsspannung in der Größenordnung von beispielsweise 2000 V aufweist, beträgt die Dicke von der Oberfläche des Elements aus, d.h., der freiliegenden Oberflächen der P<sup>+</sup>-Halbleiterschichten **45**, oder von den Oberflächen der N<sup>+</sup>-Emitterschichten **44** aus bis zu einer Grenze zwischen der N<sup>-</sup>-Schicht **42** und der N<sup>+</sup>-Pufferschicht **46** etwa 200 µm, die Störstellenkonzentration der N<sup>-</sup>-Schicht **42**  $5 \times 10^{13} \text{ cm}^{-3}$ , die Abstände zwischen den grabenförmigen Innenwände **47**, d.h., die Abstände zwischen den Zellen, etwa 4 µm, und die Tiefe der Innenwände **47**, gemessen von den Oberflächen der P<sup>+</sup>-Halbleiterschichten **45** aus, etwa 8 µm. Die Tiefe einer Verbindungs- bzw. Übergangsstelle zwischen Bodenflächen der N<sup>+</sup>-Emitterschichten **44** und der P-Basisschicht **43** beträgt etwa 1 µm, entweder von den N<sup>+</sup>-Emitterschichten **44** aus oder von den Oberflächen der P<sup>+</sup>-Halbleiterschichten **45** aus. Die Dicke der N<sup>+</sup>-Pufferschicht **46** beträgt etwa 10 µm und die Dicke der P<sup>+</sup>-Kollektorschicht **41** beträgt etwa 300 µm.

**[0101]** Als Nächstes wird eine Betriebsweise beschrieben werden.

**[0102]** Wenn eine vorbestimmte Kollektorspannung  $V_{CE}$  über die Emitterelektrode **51** und die Kollektorelektrode **52** angelegt wird und eine vorbestimmte Gatespannung  $V_{GE}$  über die Emitterelektrode **51** und die Gateelektroden **49** angelegt wird, d.h., wenn die Gates eingeschaltet werden, werden die Kanalregionen