(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6491509号

(P6491509)

(45) 発行日 平成31年3月27日(2019.3.27)

(24) 登録日 平成31年3月8日(2019.3.8)

(51) Int.Cl.

F 1

|        |        |           |        |        |   |

|--------|--------|-----------|--------|--------|---|

| HO 1 L | 27/146 | (2006.01) | HO 1 L | 27/146 | A |

| HO 1 L | 21/322 | (2006.01) | HO 1 L | 21/322 | J |

| HO 1 L | 21/76  | (2006.01) | HO 1 L | 21/76  | L |

| HO 1 L | 21/265 | (2006.01) | HO 1 L | 21/265 | R |

HO 1 L 21/265 HO 1 L 21/265 V

請求項の数 15 (全 13 頁) 最終頁に続く

(21) 出願番号

特願2015-63370(P2015-63370)

(22) 出願日

平成27年3月25日(2015.3.25)

(65) 公開番号

特開2016-184624(P2016-184624A)

(43) 公開日

平成28年10月20日(2016.10.20)

審査請求日

平成30年3月15日(2018.3.15)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板に配された第1の導電型の電荷蓄積領域を含む複数の光電変換素子と、少なくとも互いに隣接する前記電荷蓄積領域の間に配された素子分離領域と、を含む固体撮像装置であって、

前記素子分離領域は、

半導体基板の表面の溝の内側に配された絶縁体分離部と、

前記絶縁体分離部の側面に沿って配された、前記第1の導電型とは逆の第2の導電型の半導体領域と、を含み、

前記電荷蓄積領域と前記絶縁体分離部の側面との間の前記絶縁体分離部の側面の少なくとも一部に沿って、前記半導体領域と前記絶縁体分離部との間にゲッタリング領域が配され、

前記ゲッタリング領域が、炭素およびゲルマニウムのうち少なくとも一方を含有することを特徴とする固体撮像装置。

## 【請求項 2】

前記固体撮像装置は、

前記電荷蓄積領域、フローティングディフュージョン領域、及び、前記電荷蓄積領域と前記フローティングディフュージョン領域との間にチャネルを形成する転送ゲートを含む第1の領域と、

増幅トランジスタを含む第2の領域と、

10

20

前記第1の領域及び前記第2の領域の間に配された、前記素子分離領域を含む第3の領域と、を含み、

前記第1の領域と前記第3の領域の前記絶縁体分離部との間では、前記絶縁体分離部の側面に沿って、前記半導体領域と前記絶縁体分離部との間に、前記ゲッタリング領域が配され、

前記第2の領域と前記第3の領域の前記絶縁体分離部との間では、前記絶縁体分離部の側面に沿って、前記半導体領域が前記絶縁体分離部と接触して配されていることを特徴とする請求項1に記載の固体撮像装置。

**【請求項3】**

前記ゲッタリング領域が、前記第3の領域の前記絶縁体分離部の少なくとも側面の一部に沿って、前記第3の領域の半導体領域と前記第3の領域の前記絶縁体分離部との間、かつ、前記フローティングディフュージョン領域と前記第3の領域の前記絶縁体分離部の側面との間に配されることを特徴とする請求項2に記載の固体撮像装置。

10

**【請求項4】**

前記半導体基板に対する平面視において、前記ゲッタリング領域及び前記半導体領域は、前記第1の領域の周囲を囲み、かつ、前記半導体領域は、前記ゲッタリング領域と前記第1の領域との間に配されることを特徴とする請求項2又は3に記載の固体撮像装置。

**【請求項5】**

前記第2の領域と前記第3の領域の前記絶縁体分離部との間において、前記絶縁体分離部に沿って前記ゲッタリング領域が配されないことを特徴とする請求項2乃至4の何れか1項に記載の固体撮像装置。

20

**【請求項6】**

前記ゲッタリング領域の不純物濃度のピークの位置が、前記半導体基板の表面と、前記半導体領域の不純物濃度のピークの位置と、の間にあることを特徴とする請求項1乃至5の何れか1項に記載の固体撮像装置。

**【請求項7】**

前記半導体基板の表面から同じ深さにおいて、前記ゲッタリング領域の不純物濃度が、前記半導体領域の不純物濃度よりも低いことを特徴とする請求項1乃至5の何れか1項に記載の固体撮像装置。

30

**【請求項8】**

前記ゲッタリング領域の不純物濃度が、炭素およびゲルマニウムのうち少なくとも一方の濃度であり、

前記半導体領域の不純物濃度が、p型の不純物の濃度であることを特徴とする請求項6又は7に記載の固体撮像装置。

**【請求項9】**

前記電荷蓄積領域の下端が、前記ゲッタリング領域の下端よりも深いことを特徴とする請求項1乃至8の何れか1項に記載の固体撮像装置。

**【請求項10】**

前記固体撮像装置は、前記素子分離領域のうち前記半導体領域よりも深い位置に前記第2の導電型の半導体分離部を更に有し、

40

前記半導体分離部の内側に、前記ゲッタリング領域を備えることを特徴とする請求項1乃至9の何れか1項に記載の固体撮像装置。

**【請求項11】**

前記ゲッタリング領域が、炭素を含有することを特徴とする請求項1乃至10の何れか1項に記載の固体撮像装置。

**【請求項12】**

前記ゲッタリング領域が、酸素又は窒素を含有することを特徴とする請求項1乃至11の何れか1項に記載の固体撮像装置。

**【請求項13】**

前記固体撮像装置は、前記第2の導電型のウェル領域を含み、

50

前記電荷蓄積領域と前記ウェル領域とは、前記光電変換素子であるフォトダイオードを構成し、

前記半導体領域の不純物濃度は、前記ウェル領域の不純物濃度よりも高く、

前記半導体領域は、前記ゲッタリング領域と前記電荷蓄積領域との間に配されることを特徴とする請求項 1 乃至 1 2 の何れか 1 項に記載の固体撮像装置。

**【請求項 1 4】**

固体撮像装置の製造方法であって、

半導体基板の表面に溝を形成する工程と、

前記溝の側面に沿って、炭素およびゲルマニウムのうち少なくとも一方のイオン注入により 10

ゲッタリング領域を形成する工程と、

前記溝の側面に沿って、不純物のイオン注入により 半導体領域を形成する工程と、

前記ゲッタリング領域及び前記半導体領域を形成した後に、前記溝を絶縁体で充填する工程と、

前記半導体領域に隣接する光電変換素子を形成する工程と、を有し、

前記ゲッタリング領域が、前記絶縁体と前記半導体領域との間、かつ、前記絶縁体の側面と前記光電変換素子との間に位置することを特徴とする製造方法。

**【請求項 1 5】**

前記半導体領域を前記ゲッタリング領域の後に形成することを特徴とする請求項 1 4 に記載の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、固体撮像装置及びその製造方法に関する。

**【背景技術】**

**【0 0 0 2】**

固体撮像装置の特有の欠点として白点キズが挙げられる。白点キズとは、重金属などの不純物や結晶欠陥が、光電変換素子に存在することによって発生するノイズである。このノイズに対して、半導体基板中に欠陥層を形成し、製造プロセス中の熱処理によって不純物を欠陥層でゲッタリングしノイズを低減させる。近年、光電変換素子近傍の素子分離領域に欠陥層を形成する技術が提案されている。特許文献 1 には、光電変換素子の間の素子分離領域のうち、素子分離領域の上部に配された溝型の素子分離（S T I）の底部よりも深い位置に欠陥層を有する構造が開示されている。 30

**【先行技術文献】**

**【特許文献】**

**【0 0 0 3】**

【特許文献 1】特開 2 0 0 9 - 1 9 4 2 6 9 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0 0 0 4】**

固体撮像装置において、多画素化の実現のため、画素サイズの縮小による微細化プロセスの採用が進んでいる。微細化プロセスにおいて、ドーパントの拡散制御や応力緩和のため低温の熱処理が用いられる。一方、特許文献 1 の構造では、欠陥層が半導体基板の深い領域に形成される。このため、重金属などの不純物が半導体基板の表面近傍に導入された場合、低温の熱処理では、この不純物を深い領域に形成された欠陥層でゲッタリングすることは難しい。 40

**【0 0 0 5】**

本発明は、ゲッタリングの効果向上し、またゲッタリングした不純物に起因する電荷の放出を抑制することによって、ノイズを低減する技術を提供することを目的とする。

**【課題を解決するための手段】**

**【0 0 0 6】**

10

20

30

40

50

上記課題に鑑みて、本発明の実施形態に係る固体撮像装置は、半導体基板に配された第1の導電型の電荷蓄積領域を含む複数の光電変換素子と、少なくとも互いに隣接する電荷蓄積領域の間に配された素子分離領域と、を含む固体撮像装置であって、素子分離領域は、半導体基板の表面の溝の内側に配された絶縁体分離部と、絶縁体分離部の側面に沿って配された、第1の導電型とは逆の第2の導電型の半導体領域と、を含み、電荷蓄積領域と絶縁体分離部の側面との間の絶縁体分離部の側面の少なくとも一部に沿って、半導体領域と絶縁体分離部との間にゲッタリング領域が配され、ゲッタリング領域が、炭素およびガルマニウムのうち少なくとも一方を含有することを特徴とする。

**【発明の効果】**

**【0007】**

上記手段により、ゲッタリングの効果を向上し、またゲッタリングした不純物に起因する電荷の放出を抑制することによって、ノイズを低減する技術が提供される。

10

**【図面の簡単な説明】**

**【0008】**

**【図1】**本発明の実施形態に係る固体撮像装置の平面図。

**【図2】**図1の固体撮像装置の断面図。

**【図3】**図1の固体撮像装置のゲッタリング領域及びチャネルトップ領域の不純物濃度を示す図。

**【図4】**図1の固体撮像装置の変形例を示す断面図。

**【図5】**図1の固体撮像装置の素子分離領域の製造方法を示す工程図。

20

**【図6】**図1の固体撮像装置のゲッタリング領域の製造方法を示す工程図。

**【図7】**図1の固体撮像装置のゲッタリング領域の製造方法の変形例を示す図。

**【発明を実施するための形態】**

**【0009】**

以下、本発明に係る固体撮像装置の具体的な実施形態を、添付図面を参照して説明する。なお、以下の説明及び図面において、複数の図面に渡って共通の構成については共通の符号を付している。そのため、複数の図面を相互に参照して共通する構成を説明し、共通の符号を付した構成については適宜説明を省略する。

**【0010】**

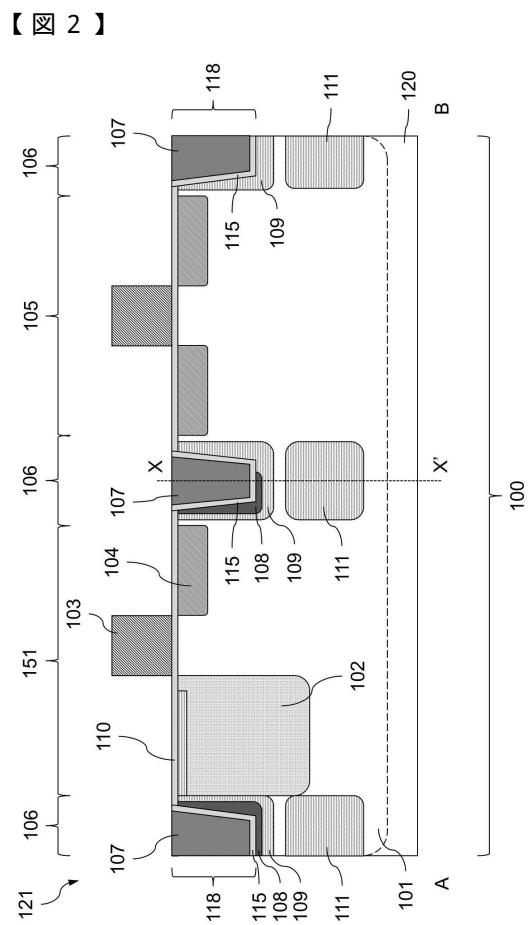

図1は、本実施形態における固体撮像装置121の画素領域の平面図である。図1において、コンタクト、配線層、カラーフィルタ、マイクロレンズ、固体撮像装置121の周辺回路領域などの構成要素は、説明の簡略化のために省略されている。固体撮像装置121の画素領域は、第1の素子領域151及び第2の素子領域152を含む。素子領域は活性領域やアクティブ領域とも呼ばれる。第1の素子領域151は、光電変換素子の電荷蓄積領域102、フローティングディフュージョン領域(FD領域)104及び電荷蓄積領域とFD領域104との間にチャネルを形成する転送ゲート103を含む。電荷蓄積領域102は光電変換素子において信号電荷として扱われる電荷を多数キャリアとする第1の導電型であり、本実施形態ではn型の半導体領域である。また第2の素子領域152は、図1に示す上から順番に、増幅トランジスタ105、選択トランジスタ153、リセットトランジスタ154及びウェルコンタクト155を含む。図1では、2つの第1の素子領域151に対して、1組の第2の素子領域152が設けられた例を示すが、例えば1つの第1の素子領域151に対して、1組の第2の素子領域152が設けられてもよい。また第2の素子領域152の構成は、これに限られるものでなく、例えば増幅トランジスタ105のみが配されていてもよい。

30

**【0011】**

図1において、互いに隣接する第1の素子領域151及び第2の素子領域152の間に、素子分離領域106が配される。素子分離領域はフィールド領域とも呼ばれる。素子分離領域106のうち、第1の素子領域151及び第2の素子領域152の周囲は、第1の導電型とは逆の第2の導電型であるp型の半導体領域であるチャネルトップ領域109で囲まれる。また電荷蓄積領域102及びFD領域104の活性領域を含む第1の素子領

40

50

域 151において、チャネルストップ領域 109が、ゲッタリング領域 108を挟み、第1の素子領域 151の周囲を囲む。

#### 【0012】

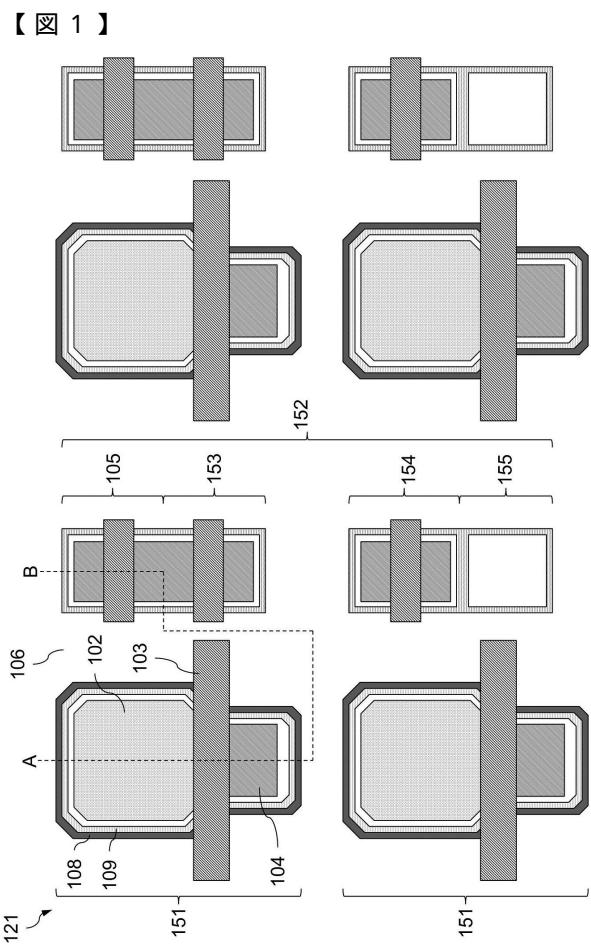

図2に、図1に示す固体撮像装置121のA-B間の断面図を示す。固体撮像装置121の画素領域100は、半導体基板120の内部に形成されたp型のウェル領域101に形成される。本実施形態において、第1の導電型はn型、第2の導電型はp型として説明するが、第1の導電型がp型、第2の導電型がn型であってもよい。

#### 【0013】

図2には、第1の素子領域151及び第2の素子領域152のうち、第2の素子領域152に配された増幅トランジスタ105が示される。n型の電荷蓄積領域102とp型のウェル領域101とは、光電変換素子であるpnフォトダイオードを構成する。電荷蓄積領域102は、固体撮像装置121に入射した光に対してpnフォトダイオードで発生する電子及び正孔のうち、n型の多数キャリアの電子を蓄積する。転送ゲート103は、電荷蓄積領域102とFD領域104との間にチャネルを、転送ゲート103の電位を変更することによって形成し、電荷蓄積領域102に蓄積された電荷をFD領域104に転送する。FD領域104の電位は、電荷蓄積領域102からチャネルを通して電荷が転送されることによって変化する。増幅トランジスタ105は、FD領域104の電位に応じた信号を、列信号線(不図示)に出力する。このようにして、電荷蓄積領域102から固体撮像装置121に入射した光に対応する信号が読み出される。選択トランジスタ153は、信号を出力する画素が選択された際にON動作する。リセットトランジスタ154は、FD領域104の電位をリセットする際にON動作する。ウェルコンタクト155には、ウェル領域101の電位が供給される。

10

20

30

#### 【0014】

画素領域100には、互いに隣接する第1の素子領域151と増幅トランジスタ105との相互を分離する素子分離領域106が配される。素子分離領域106には、溝型の素子分離構造(Shallow Trench Isolation: STI)が設けられる。溝型の素子分離構造は、半導体基板120の表面に設けられた溝の内部に、絶縁体分離部118が配された構造である。絶縁体分離部118は、溝に充填された絶縁体107と、溝の内壁に沿って形成された絶縁膜115とを含む。絶縁膜115は、省略可能である。また素子分離領域106には、絶縁体分離部118を覆うように、p型の半導体領域であるチャネルストップ領域109が配される。

30

#### 【0015】

本実施形態において、素子分離領域106には、ゲッタリング領域108が配される。ゲッタリング領域108は、絶縁体分離部118の側面の少なくとも一部に沿って配される。またゲッタリング領域108は、絶縁体分離部118とチャネルストップ領域109との間に配される。

#### 【0016】

また本実施形態において、ゲッタリング領域108は、電荷蓄積領域102及びFD領域104を含む第1の素子領域151と絶縁体分離部118との間において、絶縁体分離部118の側面に沿って配される。一方で、増幅トランジスタ105を含む第2の素子領域152と絶縁体分離部118との間における絶縁体分離部118の側面では、チャネルストップ領域109と絶縁体分離部118とが接触し、ゲッタリング領域108は配されない。しかしながら、第2の素子領域152と絶縁体分離部118との間の絶縁体分離部118の側面にゲッタリング領域108を設けてよい。また例えば増幅トランジスタ105、選択トランジスタ153、リセットトランジスタ154から適宜選択し、選択されたトランジスタと絶縁体分離部118との間の絶縁体分離部118の側面にゲッタリング領域108を設けてよい。

40

#### 【0017】

本実施形態において、ゲッタリング領域108は、絶縁体分離部118の絶縁体107及び絶縁膜115と、チャネルストップ領域109との間に形成されている。しかしながら

50

ら、チャネルトップ領域 109 よりも内側であれば、例えばゲッタリング領域 108 は、絶縁体分離部 118 の絶縁体 107 及び絶縁膜 115 の内部に渡り形成されていてもよい。また例えばゲッタリング領域 108 は、チャネルトップ領域 109 の内側の絶縁体分離部 118 の底面に形成されてもよい。

#### 【0018】

ここで、本実施形態に効果について説明する。光電変換素子及びその近傍に、例えば固体撮像装置 121 を形成する際のエッチングによるダメージや金属不純物、結晶格子ひずみ、結晶欠陥などが存在する場合がある。これらの影響によって、白点キズが生成される可能性がある。また第 1 の素子領域 151 から読み出される信号のノイズが増加する可能性がある。このノイズに対して、半導体基板 120 中に欠陥を含むゲッタリング領域を形成する。これによって、固体撮像装置 121 の製造プロセスで不純物がウェーハに導入された場合でも、製造プロセス中の熱処理によって、不純物は、光電変換素子の活性領域である電荷蓄積領域 102 から離れたゲッタリング領域中の欠陥に捕獲されて無害化される。しかしながら、固体撮像装置 121 の微細化に伴い、例えば不純物濃度のプロファイルを維持するために、固体撮像装置 121 の製造プロセスに高温の熱処理を用いることができず、低温の熱処理プロセスが用いられる。このとき特許文献 1 に示される半導体基板の深い位置に設けられたゲッタリング領域では、例えば STI 形成のための溝を形成するエッチングプロセスなどによって不純物がシリコン基板表面近傍に導入された場合、ゲッタリングの効果を発揮することは難しい。

#### 【0019】

しかしながら本実施形態において、ゲッタリング領域 108 は、絶縁体分離部 118 の側面に沿って、第 1 の素子領域 151 の光電変換素子の活性領域である電荷蓄積領域 102 と絶縁体分離部 118との間に配される。このため低温の熱履歴のプロセスにおいても、シリコン基板表面近傍に導入される不純物に対して効果的なゲッタリングが可能となる。これによって、白点キズなどのノイズを低減することが可能となる。また、ゲッタリング領域 108 は、チャネルトップ領域 109 と絶縁体分離部 118 との間の、チャネルトップ領域 109 の内部に形成される。このためゲッタリング領域 108 内で重金属などの不純物の準位に起因した電荷の放出が起きた場合であっても、チャネルトップ領域 109 により、電荷蓄積領域 102 とゲッタリング領域 108 との間に電位障壁が形成される。これによって、素子分離領域 106 から光電変換素子を構成する電荷蓄積領域 102 への電子の流入を抑制し、ノイズの発生を抑制することができる。

#### 【0020】

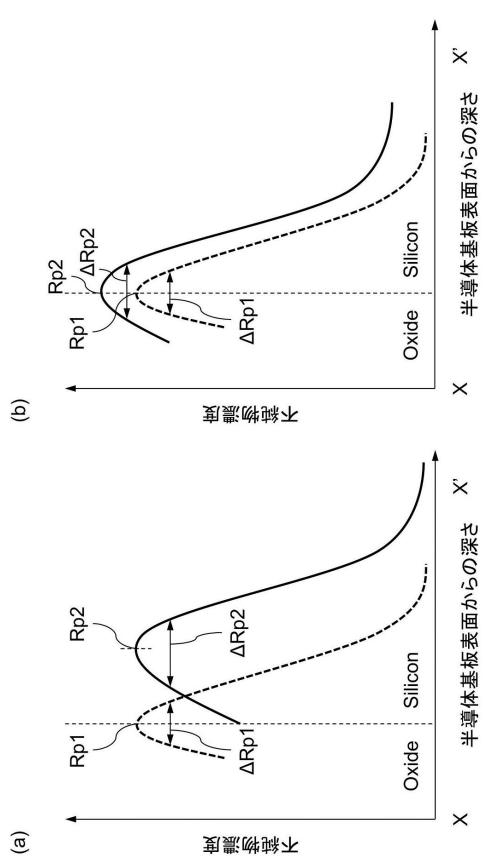

図 3 に、図 2 の X-X' 間におけるゲッタリング領域 108 とチャネルトップ領域 109 との、半導体基板 120 の深さ方向に対する不純物の濃度の関係を示す。図の横軸は基板の表面からの深さ、縦軸は不純物の濃度を示す。本実施形態において、ゲッタリング領域 108 は、不活性元素などの不純物を半導体基板 120 中に注入し、欠陥を生成することによって形成される。ゲッタリング領域 108 の不純物濃度の分布を破線で示し、チャネルトップ領域 109 の p 型の不純物濃度の分布を実線で示す。図 3 において、ゲッタリング領域 108 の不純物濃度のピークの位置を Rp1、またピークからの広がりの標準偏差を Rp1 とする。また同様に、チャネルトップ領域 109 の不純物濃度のピークの位置を Rp2、その広がりの標準偏差を Rp2 とする。

#### 【0021】

本実施形態におけるゲッタリング領域 108 とチャネルトップ領域 109 との不純物濃度の関係を図 3 (a)、(b) に示す。しかしながら不純物濃度の関係は、これらに限られるものでなく、上述したゲッタリングの効果及びゲッタリングした不純物に起因するノイズを低減する効果を有する濃度分布であれば、何れの濃度の関係で形成してもよい。

#### 【0022】

不純物濃度の関係は、図 3 (a) に示すように、ゲッタリング領域 108 の不純物濃度のプロファイルが、チャネルトップ領域 109 の不純物濃度のプロファイルと比較して、浅い位置に形成されていてもよい。このときゲッタリング領域 108 の Rp1 は、チャ

10

20

30

40

50

ネルストップ領域 109 の Rp2 よりも半導体基板 120 の表面から深さ方向に浅い位置、換言すると半導体基板 120 の表面と Rp2 の間に形成される。また Rp1 の広がりの分布も、Rp2 の広がりの分布と比較して、半導体基板 120 の表面に近い浅い位置に分布を有する。また不純物濃度の関係は、図 3 (b) に示すように、Rp1 と Rp2 とが半導体基板 120 の表面から同等の深さに配置され、ゲッタリング領域 108 の不純物濃度のプロファイルがチャネルストップ領域 109 のプロファイルに包含されるように形成されてもよい。このとき、半導体基板 120 の表面から同じ深さにおいて、ゲッタリング領域 108 の不純物濃度は、チャネルストップ領域 109 の不純物濃度よりも低くなる。

## 【0023】

10

図 3 に示す濃度分布のうち、図 3 (a) の濃度分布を有するようにプロファイルを形成した方が、チャネルストップ領域 109 によって、ゲッタリング領域 108 と電荷蓄積領域 102 との間に生じる電位障壁が高くなる。このため、ゲッタリング領域 108 から電荷蓄積領域 102 へのゲッタリングした不純物の準位に起因する電荷の流入が抑制され、ノイズをより効果的に低減することが可能となる。

## 【0024】

また図 2 に示すように、電荷蓄積領域 102 の下端が、ゲッタリング領域 108 の下端よりも半導体基板 120 の表面からの深さの深い位置に配されていてもよい。例えば、電荷蓄積領域 102 の不純物濃度のピークに対して半分の濃度となる位置が、ゲッタリング領域 108 の不純物濃度のピークに対して半分の濃度となる位置よりも深い位置であってよい。固体撮像装置 121 の製造プロセス中に導入される不純物は、半導体基板 120 の表面に付着する可能性が高い。このため、ゲッタリング領域 108 は、電荷蓄積領域 102 のうち半導体基板 120 の表面に近い領域に配されているとよい。

20

## 【0025】

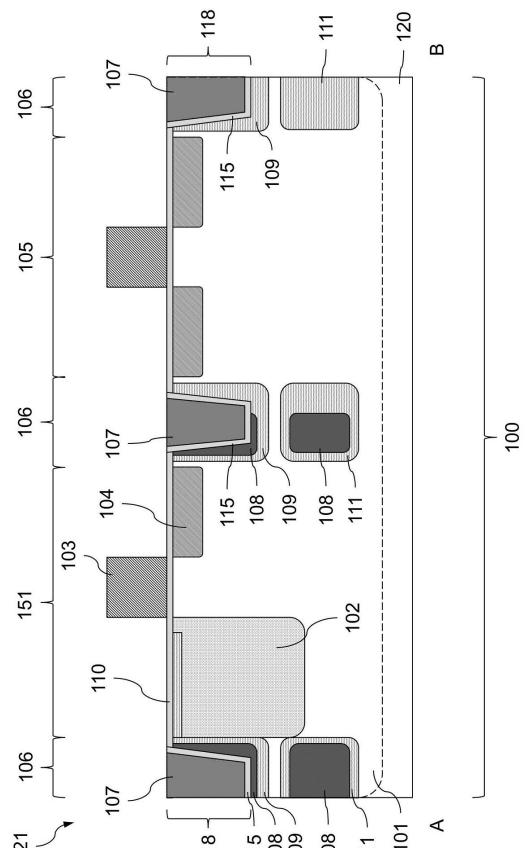

またゲッタリング領域 108 は、素子分離領域 106 のうち絶縁体分離部 118 の周囲だけでなく、より半導体基板 120 の表面から深い位置に形成されてもよい。例えば図 4 に示すように、素子分離領域 106 の絶縁体分離部 118 及びチャネルストップ領域 109 よりも半導体基板 120 の表面から深い位置に、チャネルストップ領域 109 と同様に p 型の半導体領域で、画素間を分離するための半導体分離部 111 を形成する。半導体分離部 111 は、pn 接合、あるいは同一導電型の領域内での不純物濃度の高低によって、ポテンシャル障壁を形成することで、画素間の電荷の混合を抑制するものである。例えば第 1 の素子領域 151 の外縁に接するように配された半導体分離部 111 が、半導体分離部 111 の内側にゲッタリング領域 108 を備えていてもよい。この場合、1 つの第 1 の素子領域 151 に対するゲッタリング領域 108 の占める体積が増加する。また半導体基板 120 の深い領域の不純物だけでなく、深い領域に導入された不純物や欠陥に対しても効果的にゲッタリングすることが可能となり、より白点キズなどのノイズが抑制される。

30

## 【0026】

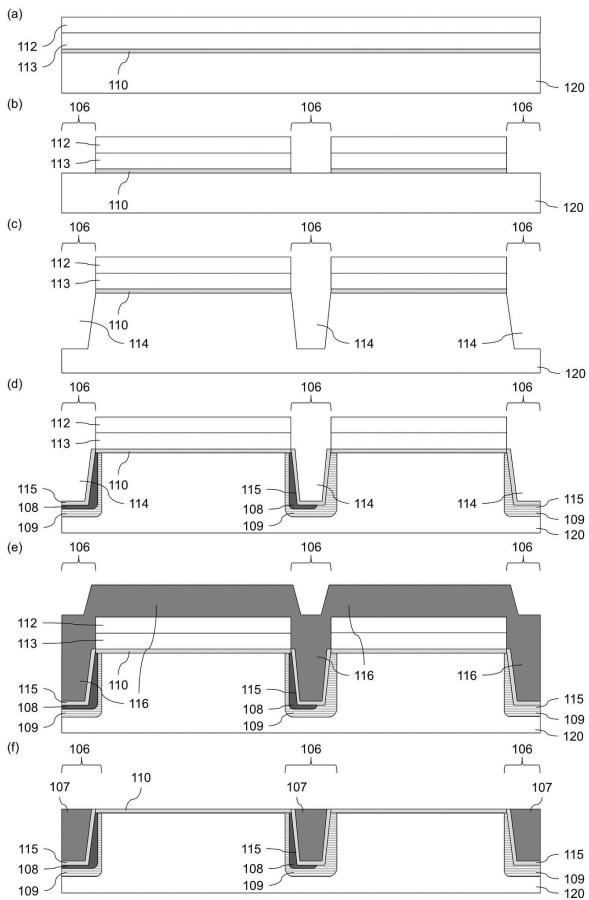

次に、図 5 から図 7 を参照しながら、本実施形態の固体撮像装置 121 の製造方法のうち、素子分離領域 106 を形成する工程について説明する。素子分離領域 106 の形成以外の、固体撮像装置 121 を構成するウェル領域 101 や電荷蓄積領域 102 、FD 領域 104 、各トランジスタなどの形成工程は、既存の手法を用いて形成できる。このため、その詳細な説明を省略する。

40

## 【0027】

本実施形態において半導体基板 120 にシリコン基板を用いる。まず、シリコン基板の表面を酸化し酸化膜（パッド酸化膜）110 を形成する。パッド酸化膜 110 の形成後、例えば CVD 法を用いて、ポリシリコン 112 及びシリコン窒化膜 113 を形成する。このときの状態を図 5 (a) に示す。

## 【0028】

次いで、図 5 (b) に示すように、固体撮像装置 121 の画素領域 100 において、素子分離領域 106 を形成する領域のポリシリコン 112 及びシリコン窒化膜 113 を除去

50

する。具体的には、シリコン窒化膜113の上にレジスト膜を形成し、例えばフォトリソグラフィ工程を用いてレジスト膜をパターニングする。これによって、素子分離領域106を形成する部分に開口を有するレジストパターンが形成される。次いで形成したレジストパターンをマスクとして用い、シリコン窒化膜113、ポリシリコン112及びパッド酸化膜110を例えば異方性のドライエッチング法を用いてエッチングする。これによって、半導体基板120の素子分離領域106となる部分に開口部を有する、シリコン窒化膜113、ポリシリコン112及びパッド酸化膜110で構成されたハードマスクが形成される。ハードマスク形成の後、レジストパターンを除去する。

#### 【0029】

次にシリコン窒化膜113、ポリシリコン112及びパッド酸化膜110で構成されたハードマスクを用いて、ハードマスクの開口部分の半導体基板120をエッチングし、素子分離領域106の絶縁体分離部118を配するための溝114を形成する工程を行う。溝114の半導体基板120の表面からの深さは、例えば50～500nm、具体的に250nm程度である。このときの状態を図5(c)に示す。

#### 【0030】

溝114を形成した後、再びシリコン窒化膜113、ポリシリコン112及びパッド酸化膜110で構成されたハードマスクを用いて、素子分離領域106に、ゲッタリング領域108及びチャネルトップ領域109を形成する。ゲッタリング領域108及びチャネルトップ領域109の形成の前に、溝114の側面及び底面に絶縁膜115を形成する。例えば酸化性ガス雰囲気中での熱酸化法を用い、35nm程成の膜厚の絶縁膜115を形成する。次いで、ゲッタリング領域108を形成する第1の注入工程を行う。第1の注入工程として、例えば原子価4価の第14族元素である炭素を、イオン注入法などを用いて半導体基板120の表面から0.3μm以下程度の深さとなるように、溝114の内壁に沿って注入する。これによって、ゲッタリング領域108を形成する。その後、チャネルトップ領域109を形成する第2の注入工程を行う。第2の注入工程として、例えばp型の不純物であるボロンを、ゲッタリング領域108として炭素を注入した領域よりも深い、例えば半導体基板120の表面から0.4μm程度までの領域に注入する。これによってp型の導電型を有するチャネルトップ領域109を形成する。また溝114の深さに応じて、ゲッタリング領域108、チャネルトップ領域109の形成深さを変更してもよい。ただしゲッタリング領域108は、チャネルトップ領域109の内側の、チャネルトップ領域109と絶縁体分離部118との間に配される。ゲッタリング領域108及びチャネルトップ領域109の形成された状態を図5(d)に示す。

#### 【0031】

絶縁膜115、ゲッタリング領域108及びチャネルトップ領域109を形成する工程において、溝114の側面及び底面に絶縁膜115を形成する前に、ゲッタリング領域108及びチャネルトップ領域109を形成してもよい。この場合、絶縁膜115を形成する際の熱処理を、不純物をゲッタリングするための熱処理として活用することが可能である。

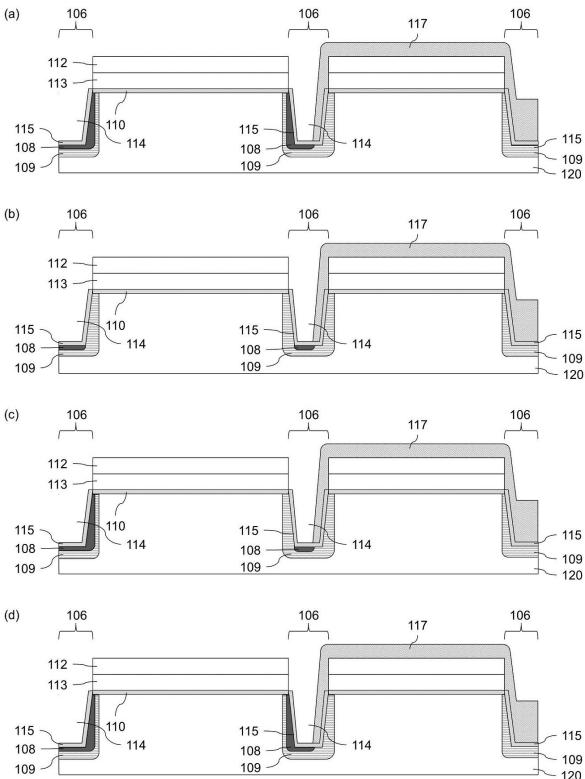

#### 【0032】

ここで、ゲッタリング領域108の形成方法として、図6(a)に示すように溝114の内壁の絶縁膜115越しに、例えば25度程度のチルト角度でイオン注入を行い、一度に溝114の底部及び側壁にゲッタリング領域108を形成してもよい。またこのとき、ゲッタリング領域108を形成しない増幅トランジスタ105の周囲の素子分離領域106は、図6(a)に示すようにレジスト117で保護し、注入が行われないようにしてよい。この場合、増幅トランジスタ105の周囲の素子分離領域106には、ゲッタリング領域108が配されない。これによって、ゲッタリング領域108に捕獲された不純物による増幅トランジスタ105のチャネル電子へのクーロン散乱の影響を軽減でき、移動度の低下を抑制できる。

#### 【0033】

またゲッタリング領域108の注入を、図6(b)に示すように、溝114の内壁の絶

10

20

30

40

50

縁膜 115 越しに、例えば 0 度の小さいチルト角度によってイオン注入を行い、溝 114 の底部のみにゲッタリング領域 108 を形成する。その後、図 6 (c)、(d) に示すように、40 度程度の大きなチルト角度を用いてイオン注入を行い、溝 114 の側壁にゲッタリング領域 108 を形成する。このように、ゲッタリング領域 108 は、必ずしも 1 回の注入で形成する必要はなく、チルト角度を変更し、複数回の注入を用いて形成してもよい。

#### 【0034】

またゲッタリング領域 108 に注入されることによって、ゲッタリング領域 108 が含有する元素は、炭素に限られるものではない。欠陥を生成するための不純物として、例えば炭素、シリコン、ゲルマニウムなどの第 14 族元素のうち少なくとも 1 種類を適宜、選択し注入し、ゲッタリング領域 108 に含有させてもよい。また例えば、酸素や窒素を注入し、半導体基板 120 の材料と化学結合させてもよい。ゲッタリング領域 108 が酸素や窒素を含有し、このとき酸素や窒素を、例えば半導体基板 120 の材料に対する化学量論比よりも少なく注入することによって欠陥を生成させ、ゲッタリング領域 108 として用いてもよい。

#### 【0035】

ゲッタリング領域 108 及びチャネルトップ領域 109 を形成した後、溝 114 を絶縁体で充填する充填工程を行う。図 5 (e) に示すように、半導体基板 120 上に絶縁体 116 を形成する。絶縁体 116 は、例えば高密度プラズマ CVD 法を用いて形成されたシリコン酸化膜でありうる。次いで、パッド酸化膜 110 の上面よりも上側の部分を、例えば CMP 法を用いて除去する。これによって図 5 (f) に示す、絶縁体 107 及び絶縁膜 115 を備える絶縁体分離部 118 と、ゲッタリング領域 108 と、チャネルトップ領域 109 と、を含む素子分離領域 106 が形成される。

#### 【0036】

以上のように、溝 114 の形成時にゲッタリング領域 108 及びチャネルトップ領域 109 を形成することによって、溝 114 に対して自己整合的にゲッタリング領域 108 及びチャネルトップ領域 109 を電荷蓄積領域 102 の近くに設けることが可能となる。ゲッタリング領域 108 が、光電変換素子を構成する電荷蓄積領域 102 の近くに配されることによって、低温の熱処理でも電荷蓄積領域 102 の近傍に存在する不純物のゲッタリング効果を向上することが可能となる。またゲッタリング領域 108 がチャネルトップ領域 109 に覆われることによって、ゲッタリングした不純物の準位に起因するノイズを低減することが可能となる。

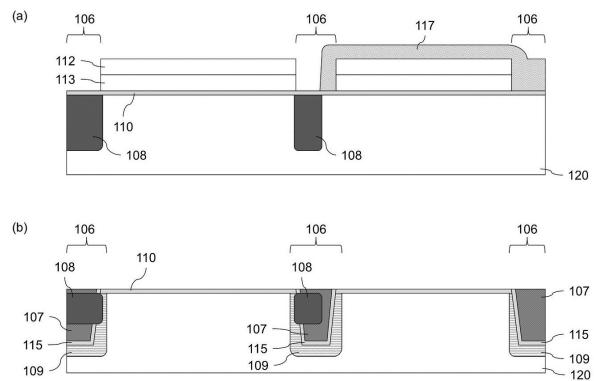

#### 【0037】

素子分離領域 106 の形成方法は、上述した方法に限られるものではない。第 1 の素子領域 151 と対向する素子分離領域 106 の STI の側面に沿って、チャネルトップ領域 109 と絶縁体分離部 118 との間にゲッタリング領域 108 が配される構成であればよい。例えば、図 5 (b) の工程において、パッド酸化膜 110 をエッチングする前に、図 7 (a) に示すように、ポリシリコン 112 及びシリコン窒化膜 113 をハードマスクとして、炭素イオンなどを注入し、ゲッタリング領域 108 を形成してもよい。ゲッタリング領域 108 を形成した後、図 5 (c) 以降に示す工程のうちゲッタリング領域 108 の形成工程以外の工程を行ってもよい。また例えば、図 7 (b) に示されるように、図 5 (d) の工程でゲッタリング領域 108 を形成するための第 1 の注入工程を行わず、絶縁体 116 を平坦化し絶縁体 107 を形成した後にゲッタリング領域 108 を形成してもよい。この場合、ゲッタリング領域 108 を形成する部分以外は、例えばレジストマスクなどを用いて保護し、不純物の注入を行えばよい。このとき、ゲッタリング領域 108 は、図 7 (b) に示すように、絶縁体分離部 118 の絶縁体 107 及び絶縁膜 115 の内部に渡り形成されてもよい。

#### 【符号の説明】

#### 【0038】

102 電荷蓄積領域、106 素子分離領域、108 ゲッタリング領域、109 チ

10

20

30

40

50

ヤネルストップ領域、118 絶縁体分離部、120 半導体基板、121 固体撮像装置

【図3】

【 四 4 】

【図5】

【 四 6 】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

H 01L 21/265

F

(72)発明者 金田 翼

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 柴山 将隆

(56)参考文献 特表2012-507871 (JP, A)

特開2004-193547 (JP, A)

特開2009-194269 (JP, A)

特開2005-294705 (JP, A)

特開2010-182976 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 27/146

H 01L 21/265

H 01L 21/322

H 01L 21/76