(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5822544号

(P5822544)

(45) 発行日 平成27年11月24日(2015.11.24)

(24) 登録日 平成27年10月16日(2015.10.16)

(51) Int.Cl.

F 1

H04N 5/225 (2006.01)

H04N 5/225

F

H04N 5/232 (2006.01)

H04N 5/232

Z

H04N 5/341 (2011.01)

H04N 5/335

4 1 O

請求項の数 5 (全 18 頁)

(21) 出願番号

特願2011-128640 (P2011-128640)

(22) 出願日

平成23年6月8日(2011.6.8)

(65) 公開番号

特開2012-257059 (P2012-257059A)

(43) 公開日

平成24年12月27日(2012.12.27)

審査請求日

平成26年6月9日(2014.6.9)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

第1モードと第2モードとを含む複数のモードで動作可能な撮像装置であって、複数のタイプの画素を含み、同じのタイプの画素には同じ色を透過するカラーフィルタが配されている複数の画素の画素値をデジタルデータとして取得し、2以上のタイプの画素のデジタルデータを含み、各タイプの画素のデジタルデータを2以上含む複数のデジタルデータをI個のMビット・パラレルデータとして並列に出力する撮像部と、

前記I個のMビット・パラレルデータからJ個のMビット・パラレルデータを得る圧縮部と、

前記圧縮部から入力された前記J個のMビット・パラレルデータのビットを入れ替えてL個のPビット・パラレルデータを生成する第1データ変換部と、

前記撮像部から入力された前記I個のMビット・パラレルデータのビットを入れ替えてQ個のPビット・パラレルデータを生成する第2データ変換部と、

前記第1モードにおいて前記第2データ変換部からの前記Pビット・パラレルデータをシリアルデータに変換して複数のポートから出力し、前記第2モードにおいて前記第1データ変換部からの前記Pビット・パラレルデータをシリアルデータに変換して前記複数のポートの一部のポートから出力するPS変換部と、

前記複数のポートから出力されたデジタルデータの伝送形式を変換して信号処理部へ出力する伝送部とを備え、

前記一部のポートはそれぞれ、前記第1モードと前記第2モードとにおいて、同じタイ

10

20

の画素のデジタルデータのみを出力し、

前記伝送部は、前記複数のポートのそれぞれに対して、該ポートから出力されたデジタルデータの传送形式を変換する変換回路を備え、

前記一部のポートは第1ポートと第2ポートとを含み、

前記第1ポートに対する変換回路と前記第2ポートに対する変換回路との間に、前記複数のポートのうち前記第2モードにおいて使用されないポートに対する変換回路が配置され、

前記使用されないポートに対する変換回路は前記第2モードの間にオフとなることを特徴とする撮像装置。

#### 【請求項2】

10

前記圧縮部は、同じタイプの複数の画素のデジタルデータから1つのデジタルデータを得ることによって、前記J個のMビット・パラレルデータを得ることを特徴とする請求項1に記載の撮像装置。

#### 【請求項3】

前記変換回路はLVDS回路を含み、

前記変換回路は、前記複数のポートから出力されたデジタルデータをLVDS信号に変換する

ことを特徴とする請求項1又は2に記載の撮像装置。

#### 【請求項4】

20

前記圧縮部は、複数のデジタルデータの加算、平均化、最大値の取得又は最小値の取得を行うことを特徴とする請求項1乃至3の何れか1項に記載の撮像装置。

#### 【請求項5】

請求項1乃至4の何れか1項に記載の撮像装置と、

前記撮像装置から出力された信号を処理する信号処理部と、

を備えることを特徴とする撮像システム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は撮像装置および撮像システムに関する。

##### 【背景技術】

30

##### 【0002】

従来の撮像装置の1つの課題として消費電力を低減がある。充電式のバッテリーによって駆動される撮像装置ではその消費電力が1回の充電あたりの撮影時間や撮影枚数に影響するためこの課題の重要性が高い。また、別の課題として、固体撮像素子の高画素化や高フレームレート化(高速読み出し化)がある。高速に読み出すために固体撮像素子からの読み出し動作周波数が向上すると消費電力も増加するため、消費電力の低減とフレームレートの向上とは背反する課題である。特許文献1に開示された固体撮像装置では両方の課題に対応すべく、固体撮像素子からの画素値の読み出しを複数のチャンネルに分割して行う。これにより同時に複数画素を読み出すことができるため高速読み出しに対応できる。また動作モードに応じて固体撮像素子からの読み出しチャンネル数を減少させることで消費電力を低減する。

40

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

##### 【特許文献1】特開2008-283331号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

特許文献1に記載の撮像装置では、動作モードに依存して、各チャネルから読み出される画素の色が異なる。例えば特許文献1の図10では、1つの行の画素の読み出しにおい

50

て、チャネル 1 から赤色を表す信号のみが読み出されるモードとチャネル 1 から赤色を表す信号と緑色を表す信号との両方が読み出されるモードとが混在している。このように動作モードによって 1 つのチャネルから出力される画素の色が異なると、撮像装置からの信号を処理する信号処理部の動作を動作モードごとに変える必要が生じ、撮像システムの設計が複雑になる。そこで、本発明の 1 つの側面は、複数の動作モードを有する撮像装置からの信号を処理する信号処理部の設計を容易にするための技術を提供することを目的とする。

#### 【課題を解決するための手段】

##### 【0005】

上記課題に鑑みて、第 1 モードと第 2 モードとを含む複数のモードで動作可能な撮像装置であって、複数のタイプの画素を含み、同じのタイプの画素には同じ色を透過するカラーフィルタが配されている複数の画素の画素値をデジタルデータとして取得し、2 以上のタイプの画素のデジタルデータを含み、各タイプの画素のデジタルデータを 2 以上含む複数のデジタルデータを I 個の M ビット・パラレルデータとして並列に出力する撮像部と、前記 I 個の M ビット・パラレルデータから J 個の M ビット・パラレルデータを得る圧縮部と、前記圧縮部から入力された前記 J 個の M ビット・パラレルデータのビットを入れ替えて L 個の P ビット・パラレルデータを生成する第 1 データ変換部と、前記撮像部から入力された前記 I 個の M ビット・パラレルデータのビットを入れ替えて Q 個の P ビット・パラレルデータを生成する第 2 データ変換部と、前記第 1 モードにおいて前記第 2 データ変換部からの前記 P ビット・パラレルデータをシリアルデータに変換して複数のポートから出力し、前記第 2 モードにおいて前記第 1 データ変換部からの前記 P ビット・パラレルデータをシリアルデータに変換して前記複数のポートの一部のポートから出力する P S 変換部と、前記複数のポートから出力されたデジタルデータの伝送形式を変換して信号処理部へ出力する伝送部とを備え、前記一部のポートはそれぞれ、前記第 1 モードと前記第 2 モードとにおいて、同じタイプの画素のデジタルデータのみを出力し、前記伝送部は、前記複数のポートのそれぞれに対して、該ポートから出力されたデジタルデータの伝送形式を変換する変換回路を備え、前記一部のポートは第 1 ポートと第 2 ポートとを含み、前記第 1 ポートに対する変換回路と前記第 2 ポートに対する変換回路との間に、前記複数のポートのうち前記第 2 モードにおいて使用されないポートに対する変換回路が配置され、前記使用されないポートに対する変換回路は前記第 2 モードの間にオフとなることを特徴とする撮像装置が提供される。10

#### 【発明の効果】

##### 【0006】

上記手段により、複数の動作モードを有する撮像装置からの信号を処理する信号処理部の設計を容易にするための技術が提供される。

#### 【図面の簡単な説明】

##### 【0007】

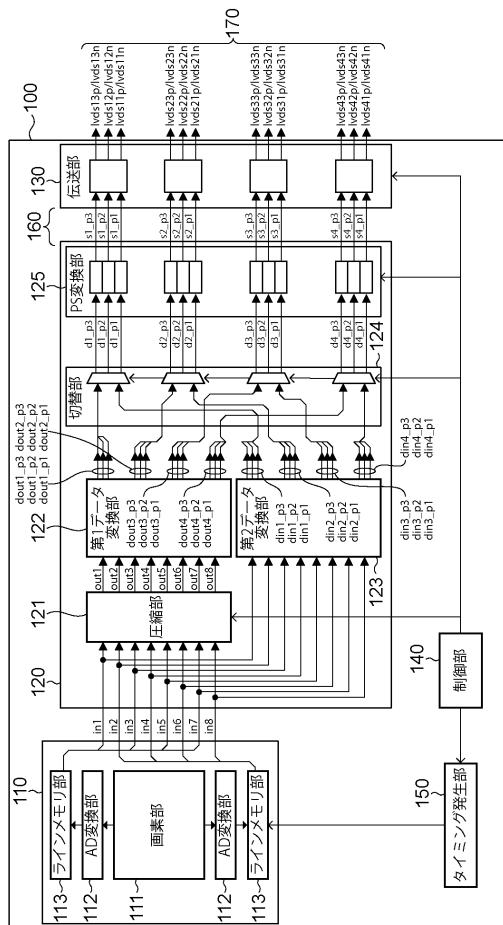

【図 1】本発明の実施形態の固体撮像装置 100 の全体構成例を説明する図。

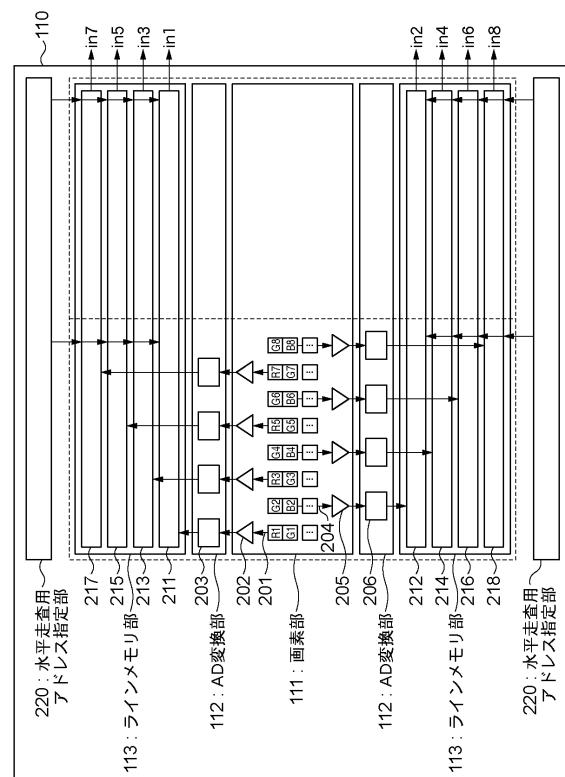

【図 2】本発明の実施形態の撮像部 110 の構成例を説明する図。

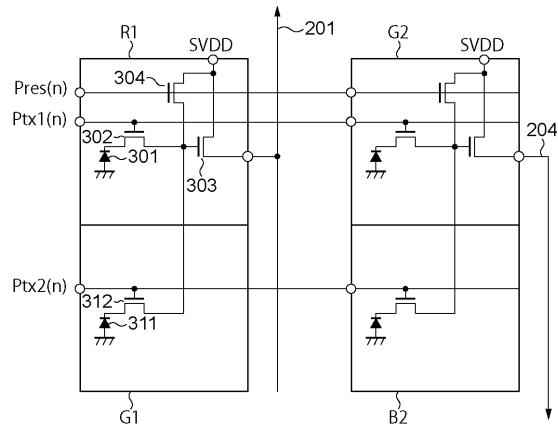

【図 3】本発明の実施形態の画素の回路構成例を説明する図。

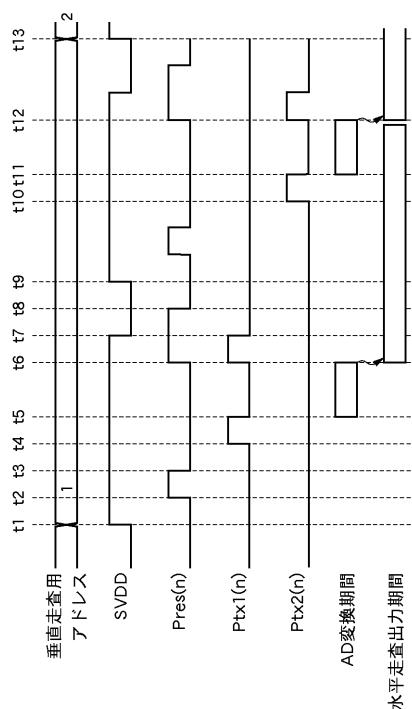

【図 4】本発明の実施形態の撮像部 110 の動作の例を説明する図。

【図 5】本発明の実施形態のラインメモリ部 113 の状態例を説明する図。

【図 6】本発明の実施形態のデータ変換部へ入力されるデジタルデータを説明する図。

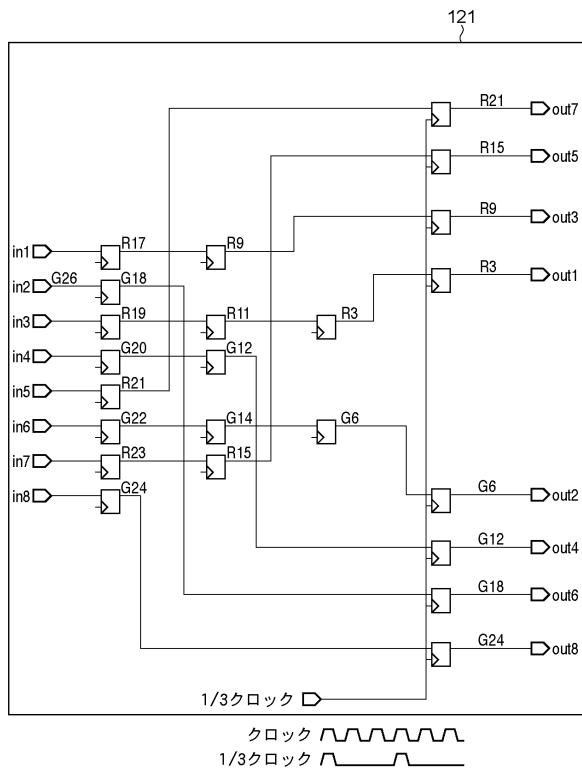

【図 7】本発明の実施形態の圧縮部 121 の構成例を説明する図。

【図 8】本発明の実施形態の圧縮部 121 の入出力レートを説明する図。

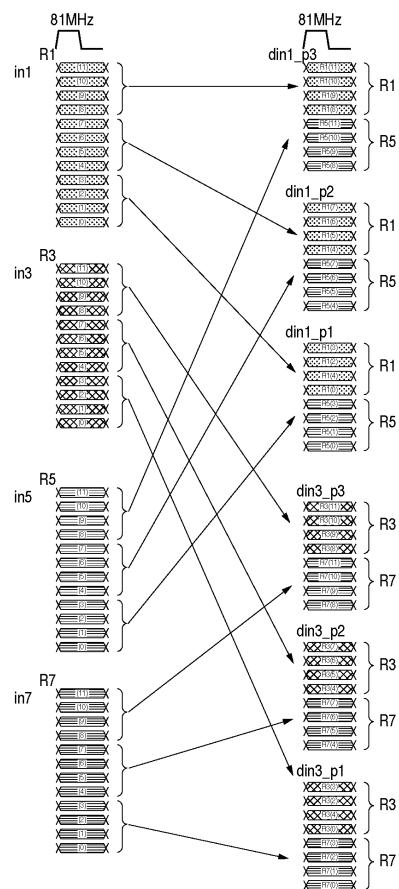

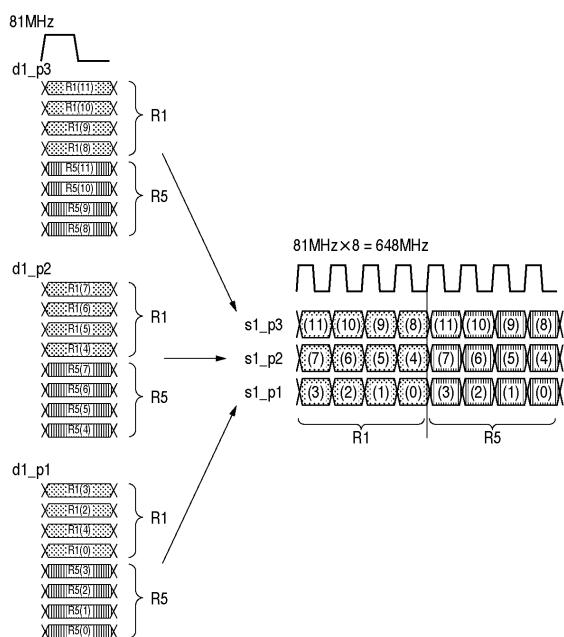

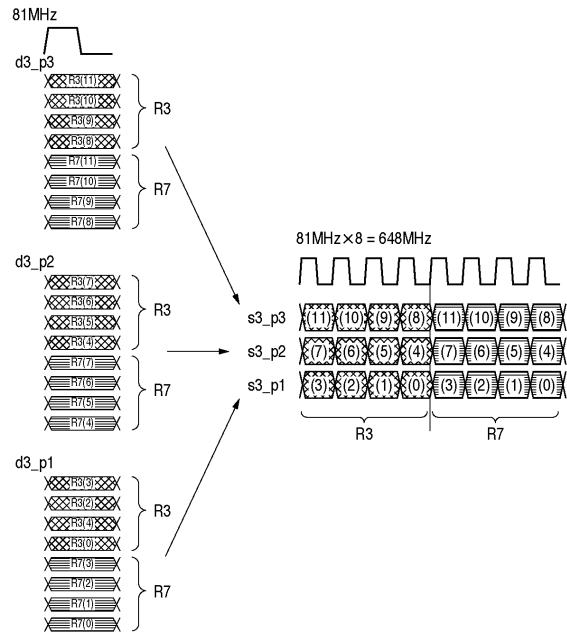

【図 9 A】本発明の実施形態の第 2 データ変換部 123 における処理の一例を説明する図。

。

【図 9 B】本発明の実施形態の第 2 データ変換部 123 における処理の一例を説明する図。

。

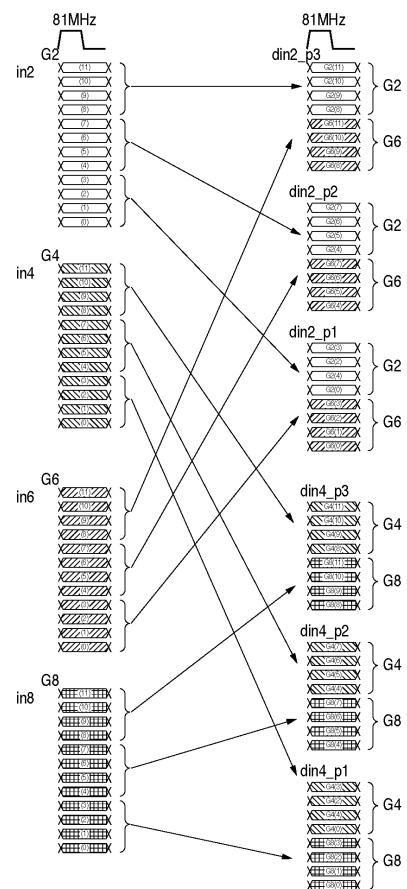

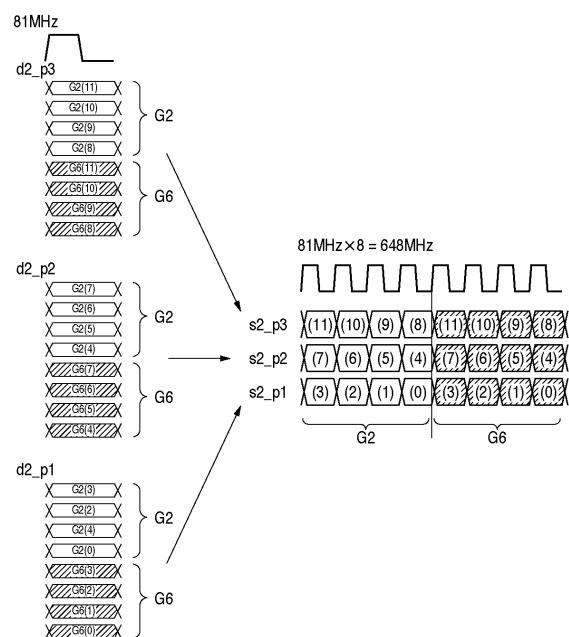

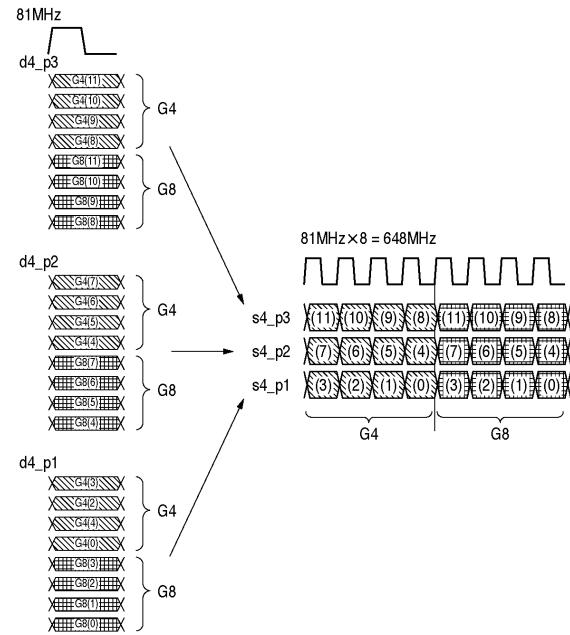

【図 10 A】本発明の実施形態の第 1 データ変換部 122 における処理の一例を説明する40

50

図。

【図10B】本発明の実施形態の第1データ変換部122における処理の一例を説明する図。

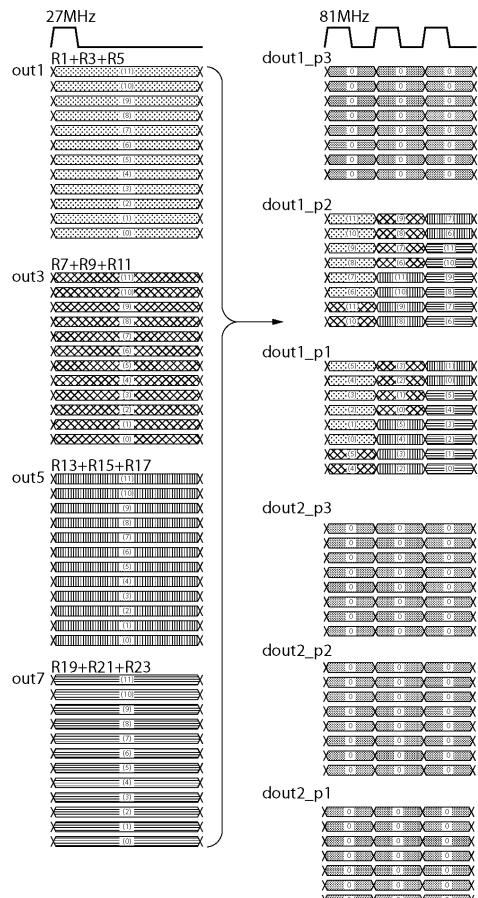

【図11A】本発明の実施形態の通常モードにおけるPS変換部125の動作の一例を説明する図。

【図11B】本発明の実施形態の通常モードにおけるPS変換部125の動作の一例を説明する図。

【図11C】本発明の実施形態の通常モードにおけるPS変換部125の動作の一例を説明する図。

【図11D】本発明の実施形態の通常モードにおけるPS変換部125の動作の一例を説明する図。 10

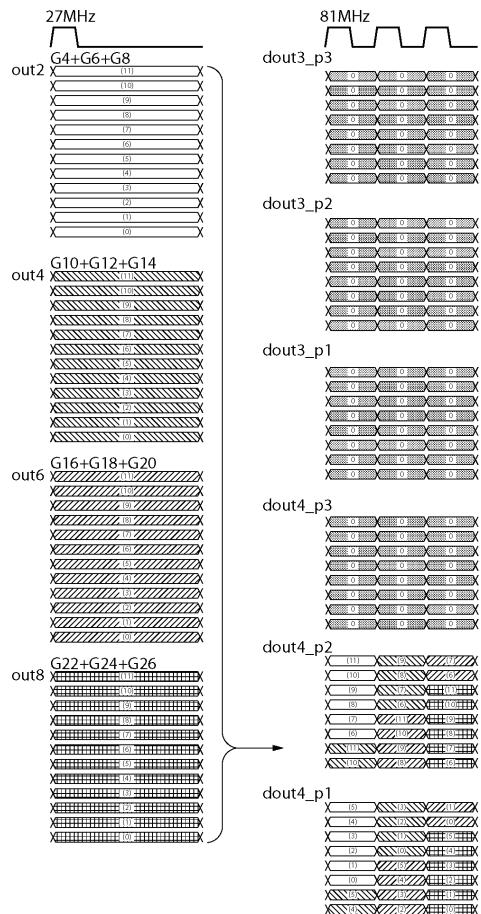

【図12A】本発明の実施形態の圧縮モードにおけるPS変換部125の動作の一例を説明する図。

【図12B】本発明の実施形態の圧縮モードにおけるPS変換部125の動作の一例を説明する図。

【図13】本発明の実施形態の圧縮モードにおける一部のLVDSS回路のオフを説明する図。

【図14】本発明の実施形態の撮像部1400の構成例を説明する図。

【図15】本発明の実施形態の圧縮部121の別の構成例を説明する図。

【図16】本発明の実施形態の圧縮部121の入出力レートを説明する図。 20

【図17】本発明の実施形態の撮像システム2200の構成例を説明する図。

#### 【発明を実施するための形態】

##### 【0008】

添付の図面を参照しつつ、本発明の様々な実施形態を以下に説明する。図1を用いて1つの実施形態に係る固体撮像装置100の全体の構成例を説明する。固体撮像装置100は撮像部110、変換部120、伝送部130、制御部140およびタイミング発生部150を備えうる。撮像部110で得られた各画素の画素値を表すデジタルデータはデータ「in1」～「in8」として変換部120へ出力される。変換部120と伝送部130とは本実施形態では12本の信号線で接続される。変換部120は撮像部110から出力されたデータを変換して12個のデータ「s1\_p1」～「s4\_p1」として伝送部130へ出力する。伝送部130は変換部120から出力されたデータの伝送形式を変換して信号線170へ出力する。タイミング発生部150は撮像部110へ供給されるタイミングを発生する。制御部140は固体撮像装置100全体の動作を制御する。特に、本実施形態の固体撮像装置100は通常モード(第1モード)と圧縮モード(第2モード)との2つのモードで動作可能であり、制御部140は固体撮像装置100が何れのモードで動作するかを制御する。通常モードは撮像部110から出力された画素値を表すデジタルデータをそのまま後続の信号処理部へ出力するモードであり、例えば静止画撮影などの高精細画像撮影時に用いられる。一方、圧縮モードは撮像部110から出力された画素値を表すデジタルデータの複数個を代表する1つのデジタルデータを後続の信号処理部へ出力するモードである。この圧縮モードは例えば動画撮影などの高速駆動が必要な場合に用いられる。 30

##### 【0009】

撮像部110は、画素部111、AD(アナログデジタル)変換部112およびラインメモリ部113を備えうる。画素部111には複数の画素がアレイ状に配列されており、各画素の画素値がアナログデータとして取得される。AD変換部112は画素部111で取得されたアナログデータをそれぞれデジタルデータに変換する。AD変換部112から出力されたデジタルデータはラインメモリ部113に格納され、1クロックあたり8画素分のデジタルデータが変換部120へ出力される。本実施形態では1つのデジタルデータは12ビットで構成される。撮像部110と変換部120とを接続するバスは96ビット(=12ビット×8データ)のバス幅を有しており、撮像部110から変換部120へ伝送されるデジタルデータの各ビットはパラレルに伝送される。 40 50

## 【0010】

変換部120は、圧縮部121、第1データ変換部122、第2データ変換部123、切替部124およびPS(パラレルシリアル)変換部125を備えうる。圧縮部121は撮像部110が出力したデータ「in1」～「in8」(I個のMビット・パラレルデータ)に基づいてデータ「out1」～「out8」(J個のPビット・パラレルデータ)を出力する。一部の実施形態において、圧縮部121は画素値を表すデジタルデータを複数個加算して1つのデジタルデータを生成する。すなわち、圧縮部121は加算部として機能する。この1つのデジタルデータは複数の画素の値を代表する。本実施形態では、それそれが画素値を表す複数個のデジタルデータを単純に加算して1つのデジタルデータを生成しているが、複数個のデジタルデータを処理する方法は加算に限られない。例えば複数個のデジタルデータの平均化を行って平均値を求めてよいし、最大値や最小値を有するデジタルデータを代表値として取得してもよい。すなわち、複数個のデジタルデータから、複数の画素の値を表す1つのデジタルデータを得る処理であればよい。10

## 【0011】

第1データ変換部122は、圧縮部121が出力した8個のデータ「out1」～「out8」のビット幅を変換して12個のデータ「dout1\_p1」～「dout4\_p3」として出力する。本実施形態では、データ「out1」～「out8」はそれぞれ12ビットであり、データ「dout1\_p1」～「dout4\_p3」はそれぞれ8ビットである。第2データ変換部123は、撮像部110が出力した8個のデータ「in1」～「in8」のビット幅を変換して12個のデータ「din1\_p1」～「din4\_p3」として出力する。本実施形態では、データ「in1」～「in8」はそれぞれ12ビットであり、データ「din1\_p1」～「din4\_p3」はそれぞれ8ビットである。20

## 【0012】

切替部124は、制御部140からの指示に従って出力を切り替える。具体的には、固体撮像装置100が圧縮モードで動作する場合に、切替部124は第1データ変換部122からの出力「dout1\_p1」～「dout4\_p3」をデータ「d1\_p1」～「d4\_p3」として出力する。固体撮像装置100が通常モードで動作する場合に、切替部124は第2データ変換部123からの出力「din1\_p1」～「din4\_p3」をデータ「d1\_p1」～「d4\_p3」として出力する。PS変換部125は切替部124が出力するパラレルデータ「d1\_p1」～「d4\_p3」をシリアルデータ「s1\_p1」～「s4\_p3」に変換して出力する。30

## 【0013】

上記において概要を説明した各構成要素について、以下により詳細に説明する。まず、図2を用いて撮像部110の構成をより詳細に説明する。画素部111には光電変換素子を含む画素がアレイ状に配列されており、光電変換素子の上にはカラーフィルタが載せられている。その結果として、画素部111の各画素から、複数の色のうちの何れか1色についての画素値が読み出される。図2では例としてベイヤー配列のカラーフィルタが用いられ、第1行の行に沿った方向に赤(R)、緑(G)のカラーフィルタが繰り返し配置される。そこで、第1行の画素を画面の左側からR1、G2、…と呼ぶ。図2では画素G8までしか示していないが、これ以降も同様に列方向に画素が配置される。第2行の行に沿った方向に緑(G)、青(B)のカラーフィルタが繰り返し配置される。そこで、第2行の画素を画面の左側からG1、B2、…と呼ぶ。第3行以降は第1行、第2行の配列が繰り返される。例えば赤色のカラーフィルタが設けられた画素から得られた信号を、赤の画素値と呼ぶことにする。緑色、青色についても同様である。40

## 【0014】

図2に示される構成例では、画面の左側から奇数列に位置する画素のデータが画素部111の上部に配置されたAD変換部112に出力され、偶数列に位置する画素のデータが画素部111の下部に配置されたAD変換部112に出力される。例えば、画素R1からの信号は垂直信号線201を介して列アンプ202へ出力され、列アンプ202で増幅されてアナログデータとしてAD変換器203へ出力される。AD変換器203は列アンプ202が出力したアナログデータをデジタルデータに変換してラインメモリ211に格納する。同様に、画素G2からの信号は垂直信号線204を介して列アンプ205へ出力さ50

れ、列アンプ 205 で増幅されてアナログデータとして A/D 変換器 206 へ出力される。A/D 変換器 206 は列アンプ 205 が output したアナログデータをデジタルデータに変換してラインメモリ 212 に格納する。以降では、特に断らない限り、列の奇数及び偶数は、図の左側から数えるものとする。

#### 【0015】

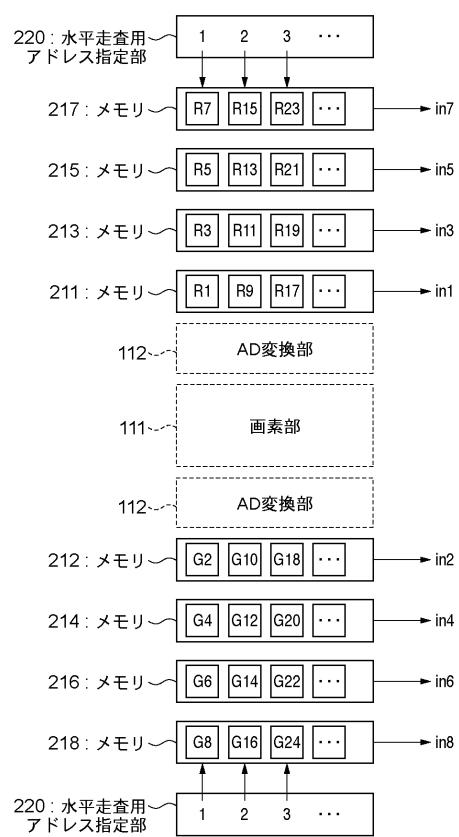

ラインメモリ部 113 は 8 つのラインメモリ 211 ~ 218 を有し、それぞれ第 1 列 ~ 第 8 列の画素の値を表すデジタルデータを記憶する。第 9 列以降の画素の値を表すデジタルデータについても同様に 8 つのラインメモリ 211 ~ 218 の何れかに記憶される。撮像部 110 は水平走査用アドレス指定部 220 をさらに備えうる。水平走査用アドレス指定部 220 は、ラインメモリ部 113 に格納された 1 行分の画素のデジタルデータを 8 個ずつ「in1」~「in8」として 8 個のチャンネルで出力する。10

#### 【0016】

図 3 を用いて画素部 111 に含まれる画素の回路構成の例を説明する。図 3 は画素部 111 の左上の 4 つの画素 R1、G2、G1、B2 に注目した図である。奇数行に含まれる画素を代表して画素 R1 について説明し、偶数行に含まれる画素を代表して画素 G1 について説明する。画素 R1 は入射光量に応じて電荷を生じる光電変換を行う光電変換素子（フォトダイオード）301 を含む。光電変換素子 301 で光電変換された電荷は、転送 MOS ランジスタ 302 を介してフローティングディフュージョン（FD）（図示せず）に保持される。FD に保持された電荷は FD の寄生容量によって電位に変換され、その FD の電位に応じた信号が増幅 MOS ランジスタ 303 によって増幅される。増幅された信号は垂直信号線 201 に現れる。また、画素 R1 は FD の電圧を所定の電圧にリセットするリセット MOS ランジスタ 304 を含む。画素 G1 は光電変換素子 311 を含む。光電変換素子 311 で光電変換された電荷は、転送 MOS ランジスタ 312 を介して増幅 MOS ランジスタ 303 に供給され、増幅 MOS ランジスタ 303 によって増幅される。図 3 では、列方向に隣接する 2 つの画素で増幅 MOS ランジスタ 303 を共有するが、これに限られず、それぞれの画素が増幅 MOS ランジスタを有してもよい。20

#### 【0017】

図 4 に示されるタイミング図を用いて撮像部 110 の動作の一例を説明する。時刻 t1 において垂直走査用アドレス指定部（図 3 に図示せず）によって 1 アドレス目が選択される。1 アドレス目が指定されると、パルスの引数 n が 1 となり、1 行目の画素と 2 行目の画素の値が読み取られる。また、時刻 t1 に図 3 に示された SVDD が、増幅 MOS ランジスタ 303 が増幅器として動作しない基準レベル（例えば接地レベル）から VDD レベルに変更される。時刻 t2 ~ t3 において Pres(1) を Low から High にすることによってリセット MOS ランジスタ 304 を ON し、FD に VDD レベルを書き込む。この 1 アドレス目（1 行目、2 行目）の FD のみを VDD レベルにし、他の行を基準レベルにすることで、1 アドレス目の増幅 MOS ランジスタ 303 からの出力のみが垂直信号線 201、204 に出力される。30

#### 【0018】

時刻 t4 ~ t5 において、1 アドレス目の上の行、つまり 1 行目の転送 MOS ランジスタ 302 のゲートに接続されている Ptx1(1) を ON する。これにより光電変換素子 301 に蓄積された電荷が FD に転送される。また転送された電荷量に応じた信号が増幅 MOS ランジスタ 303 によって電圧値として垂直信号線 13 に読み出され、列アンプ 202 を通じて A/D 変換器 203 へ出力される。時刻 t5 ~ t6 では A/D 変換器 203 において A/D 変換が行なわれる。40

#### 【0019】

時刻 t6 にて、Pres(1)、Ptx1(1) が再度 ON となり、光電変換素子 301 がリセットされる。また A/D 変換後の 1 行目のデジタルデータを、水平走査用アドレス指定部 220 によって順次指定することによって第 1 行のデータを読み出す。この読み出しは、2 行目の A/D 変換が終了する時刻(t12)までに完了すればよい。時刻 t7 ~ t8 では、SVDD を基準レベルにし、Pres(1) を High にすることで光電変換素子50

301に基準レベルを書き込んでいる。これにより1行目からの画素出力を垂直信号線13、14に出力しないようにする。

#### 【0020】

時刻t9にて再度SVDをVDDレベルに変更する。またPress(1)をHighにし、時刻t10～t11にてPt×2(1)をONすることで2行目の画素の値を垂直信号線に出力する。時刻t12にて光電変換素子311をリセットし、基準レベルを書き込んで、2行目の処理を終了する。時刻t13以降では、垂直走査用アドレス指定部にて次の2アドレス目を指定して同様の処理を行う。

#### 【0021】

図5を用いて、1行目の画素の値を表すデジタルデータを記憶したラインメモリ部113の状態を説明する。図5において、参照符号R1は画素そのものを参照するのではなく、画素R1の画素値を表すデジタルデータを参照する。図4のタイミング図を用いて説明したように、時刻t6の時点でラインメモリ部113には1行目の画素の値を表すデジタルデータが記憶されている。前述のように、ラインメモリ部113はラインメモリ211～218を有しており、ラインメモリ211には1列目の画素R1や、9列目の画素R9などを表すデジタルデータが記憶されている。すなわち、ラインメモリ211には、1列目の画素から始めて8列ごとの画素値が記憶されている。その他のラインメモリ212～218についても同様である。前述の通り、各画素値を表すデジタルデータは12ビットで構成される。水平走査用アドレス指定部220は、タイミング発生部150が出力するクロックごとに、各ラインメモリからそれぞれ1個のデジタルデータを出力する。すなわち、1クロックあたり8個のデジタルデータが並列に出力される。例えば、1クロック目ではR1、G2、…、G8を表す8個のデジタルデータが出力される。本実施形態では各ラインメモリから出力されるデジタルデータがパラレルデータである場合を扱うが、シリアルデータであってもよい。また、本実施形態では水平走査用アドレス指定部220は81MHzのレートでデジタルデータを出力する。

#### 【0022】

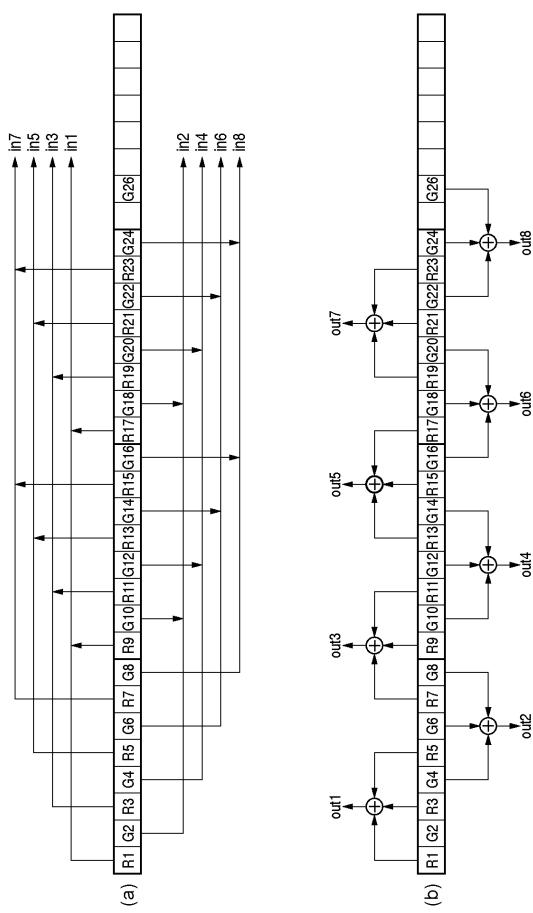

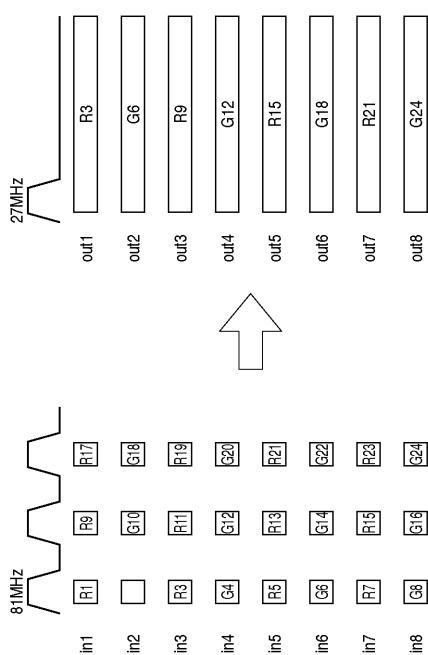

図6を用いて第1データ変換部122および第2データ変換部123へ入力されるデジタルデータについて説明する。図6(a)は第2データ変換部123へ入力されるデジタルデータについて説明する。図1に示すように、第2データ変換部123へは、撮像部110が出力するデジタルデータ「in1」～「in8」がそのまま入力される。例えば、1クロック目にはR1～G8の画素の値がそれぞれデジタルデータ「in1」～「in8」として第2データ変換部123へ入力される。2クロック目にはR9～G16の画素の値がそれぞれデジタルデータ「in1」～「in8」として第2データ変換部123へ入力される。

#### 【0023】

図6(b)は第1データ変換部122へ入力されるデジタルデータについて説明する。図1に示すように、第1データ変換部122へは、圧縮部121が出力するデジタルデータ「out1」～「out8」が入力される。一部の実施形態では、圧縮部121は3個の隣接する同色画素のデジタルデータを加算して1つのデジタルデータを生成する。例えば、圧縮部121は画素R1、R3、R5の3個のデジタル信号を加算して得られたデジタルデータを「out1」として出力する。本実施形態では、加算後の画素の重心を等ピッチとするために、緑色画素について、画素G2のデジタルデータを使用せず、画素G4から3個ずつ加算する。

#### 【0024】

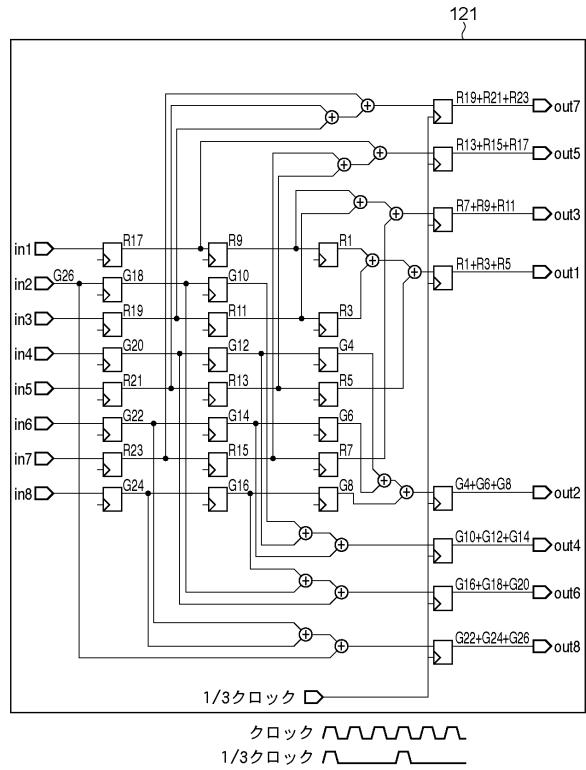

図7を用いて圧縮部121の構成例を説明する。図に示されるように、3クロック分の入力が各Dフリップフロップに記憶される。そして、圧縮部121は、各Dフリップフロップに記憶されたデジタルデータを3個加算して1個のデジタルデータを生成し出力する。

#### 【0025】

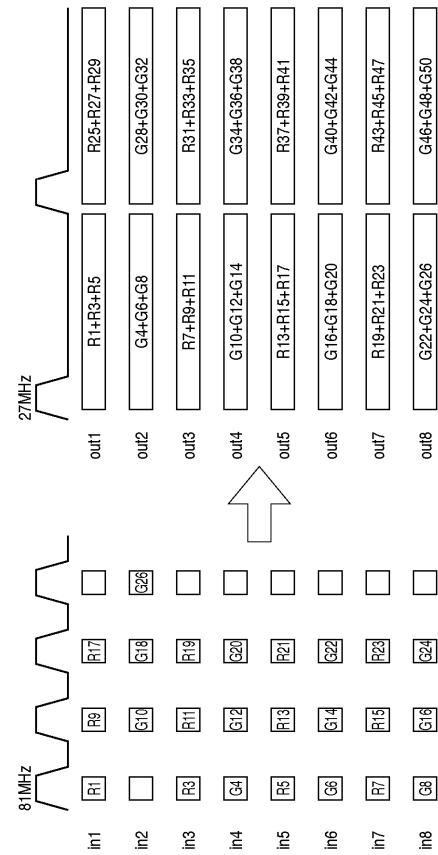

図8を用いて圧縮部121の入出力レートについて説明する。圧縮部121へは1クロックあたり8個のデジタルデータが入力される。圧縮部121では3個のデジタルデータ

10

20

30

40

50

から 1 個のデジタルデータを生成しているため、デジタルデータの個数は 1 / 3 になる。圧縮部 121 から 1 クロックあたり 8 個のデジタルデータを出力するためには、圧縮部 121 からの出力レートを圧縮部 121 への入力レートの 1 / 3 にすればよい。前述の通り、圧縮部 121 への入力レートは 81MHz であるので、圧縮部 121 からの出力レートはその 1 / 3 の 27MHz となる。

#### 【0026】

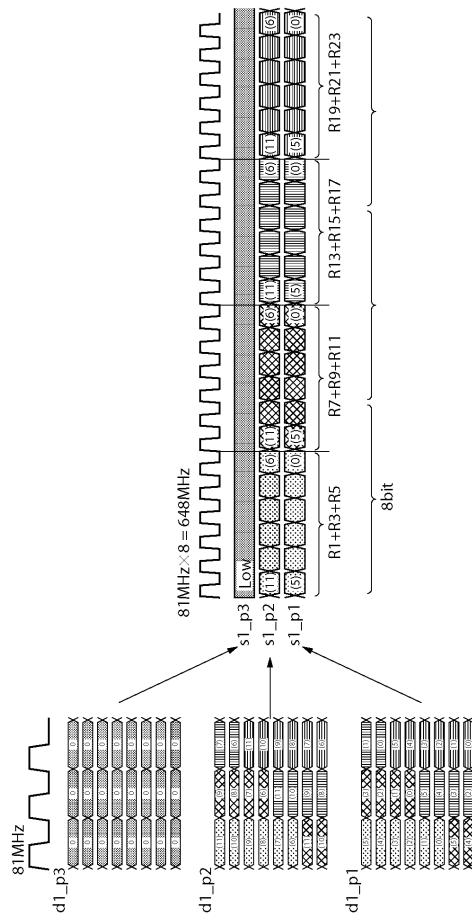

続いて、図 9A、図 9B を用いて第 2 データ変換部 123 における処理の一例を説明する。前述の通り、第 2 データ変換部 123 へは、81MHz のレートで 1 クロックあたり 12 ビット・パラレルデータが 8 個入力される。そこで、第 1 データ変換部 122 は入力データのビット幅を 8 ビットに変換して、81MHz のレートで 1 クロックあたり 8 ビット・パラレルデータを 12 個出力する。図に示される例では、「in1」として入力された画素 R1 を表す 12 ビット・デジタルデータの各ビットは、4 ビットずつ「din1\_p1」～「din1\_p3」の上位ビットに振り分けられる。同様に、「in5」として入力された画素 R5 を表す 12 ビット・デジタルデータが 4 ビットずつ「din1\_p1」～「din1\_p3」の下位ビットに振り分けられる。その結果として、例えば

```

din1_p3[7:0] = {in1[11:8], in5[11:8]},

din1_p2[7:0] = {in1[7:4], in5[7:4]},

din1_p1[7:0] = {in1[3:0], in5[3:0]},

```

のように変換される。ここで、例えば in1[11:8] はデータ「in1」の 11 ビット目から 8 ビット目までのビット列を表す。また、{...} はビット連接を表す。他の 12 ビット・デジタルデータの各ビットも同様に図に示すように振り分けられる。一般に、第 2 データ変換部 123 は I 個の M ビット・パラレルデータのビットを入れ替えて Q 個の P ビット・パラレルデータを生成する。

#### 【0027】

次に、図 10A、図 10B を用いて第 1 データ変換部 122 における処理の一例を説明する。前述の通り、第 1 データ変換部 122 へは、27MHz のレートで 1 クロックあたり 12 ビットのパラレルデータが 8 個入力される。そこで、第 1 データ変換部 122 は入力データのビット幅を 8 ビットに変換する。また、第 1 データ変換部 122 は、出力レートを 3 倍の 81MHz に変換して、第 2 データ変換部 123 の出力レートに一致させる。ビット幅が変換されると、8 個の 12 ビット・パラレルデータは 12 個の 8 ビット・パラレルデータになる。また、出力レートが入力レートの 3 倍であるため、1 クロックあたり 4 個の 8 ビット・パラレルデータを出力する。図に示される例では、「out1」として入力された 3 個の画素 R1、R3、R5 を表す 12 ビット・デジタルデータの各ビットは、6 ビットずつ 1 クロック目に出力される「dout1\_p1」と「dout1\_p2」との上位ビットに振り分けられる。「out2」～「out8」の各ビットも図に示されるように、3 クロックの間に送信される「dout1\_p1」～「dout4\_p3」の何れかのビットに振り分けられる。その結果として、例えば、

```

1 クロック目の dout1_p1[7:0] = {out1[5:0], out3[5:4]}

2 クロック目の dout1_p1[7:0] = {out3[3:0], out5[5:2]}

3 クロック目の dout1_p1[7:0] = {out5[1:0], out7[5:0]}

```

のように変換される。第 1 データ変換部 122 からは 1 クロックあたり 4 個のデジタルデータが出力される。そのため、「dout1\_p3」、「dout2\_p1」～「dout2\_p3」、「dout3\_p1」～「dout3\_p3」、「dout4\_p3」としてデータを出力する必要がない。そこで、第 1 データ変換部 122 はこれらのデータとして L0W (図では「0」と表示) を出力する。一般に、第 1 データ変換部 122 は J 個の M ビット・パラレルデータのビットを入れ替えて L 個の P ビット・パラレルデータを生成する。

#### 【0028】

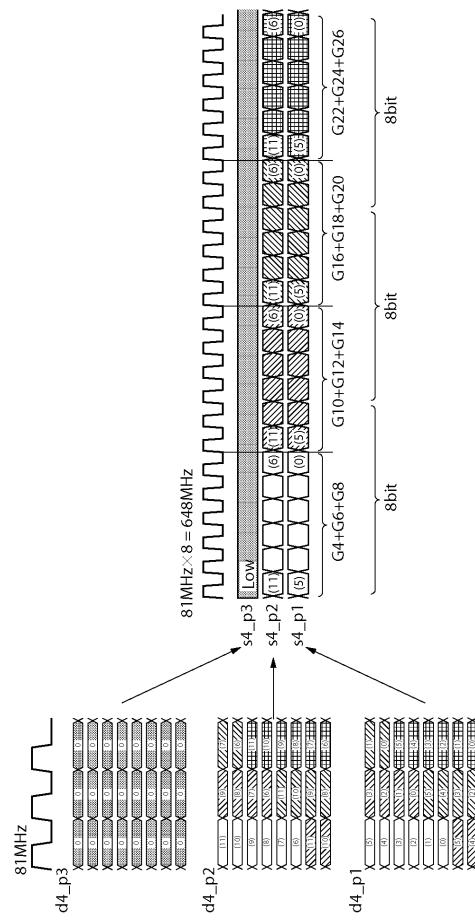

続いて、図 11A～図 11D を用いて、通常モードにおける PS 変換部 125 の動作の一例について説明する。前述の通り、PS 変換部 125 へは 81MHz のレートで 1 クロックあたり 12 個の 8 ビット・パラレルデータが入力される。PS 変換部 125 はこのパ

10

20

30

40

50

ラレルデータをそれぞれシリアルデータに変換して、648MHzで1クロックあたり12個の1ビット・シリアルデータを出力する。例えば、図11Aに示されるように、PS変換部125は、「d1\_p3」として入力されたデジタルデータを最上位ビットから順に「s1\_p3」として各クロックに出力する。その結果として、「s1\_p3」として画素R1を表すデジタルデータの11ビット目から8ビット目までが出力され、続いて画素R5を表すデジタルデータの11ビット目から8ビット目までが出力される。その他の入力データも同様にシリアルデータに変換される。その結果として、例えば図11Aに示すように、1クロック目から4クロック目の「s1\_p1」～「s1\_p3」のデータとして、画素R1を表すデジタルデータが出力される。このように、通常モードにおいて、1行目の画素の読み出しの際に、ポート「s1\_p1」～「s1\_p3」、「s3\_p1」～「s3\_p3」から赤色を表す画素値が出力される。また、ポート「s2\_p1」～「s2\_p3」、「s4\_p1」～「s4\_p3」から緑色を表す画素値が出力される。10

#### 【0029】

次に、図12A、図12Bを用いて、圧縮モードにおけるPS変換部125の動作の一例について説明する。通常モードと圧縮モードとではPS変換部125へ入力されるデータの値が異なるだけで、PS変換部125の動作自体は同じであるため、説明を省略する。20 PS変換部125による変換結果として、例えば図11Aに示すように、1クロック目から6クロック目の「s1\_p1」、「s1\_p2」のデータとして、3個の画素R1、R3、R5を表すデジタルデータが出力される。圧縮モードでは、「d1\_p3」、「d2\_p1」～「d2\_p3」、「d3\_p1」～「d3\_p3」、「d4\_p3」として常にLOWが入力される。そこで、PS変換部125は「s1\_p3」、「s2\_p1」～「s2\_p3」、「s3\_p1」～「s3\_p3」、「s4\_p3」としてLOWを出力する。このように、圧縮モードにおいて、1行目の画素の読み出しの際に、ポート「s1\_p1」、「s1\_p2」から赤色を表す画素値が出力され、ポート「s4\_p1」、「s4\_p2」から緑色を表す画素値が出力される。それ以外のポートはLOWが出力される。すなわち、ポート「s1\_p1」、「s1\_p2」(第1ポート)からは、通常モード(第1モード)と圧縮モード(第2モード)との両方において、赤色を表す画素のデジタルデータ(第1色のデジタルデータ)が出力される。また、ポート「s4\_p1」、「s4\_p2」(第2ポート)からは、通常モードと圧縮モードとの両方において、緑色を表す画素のデジタルデータ(第2色のデジタルデータ)が出力される。これにより、後続の信号処理部はモードによって処理すべき色を切り替える必要が無くなり、入力されたデータの処理が容易になる。30

#### 【0030】

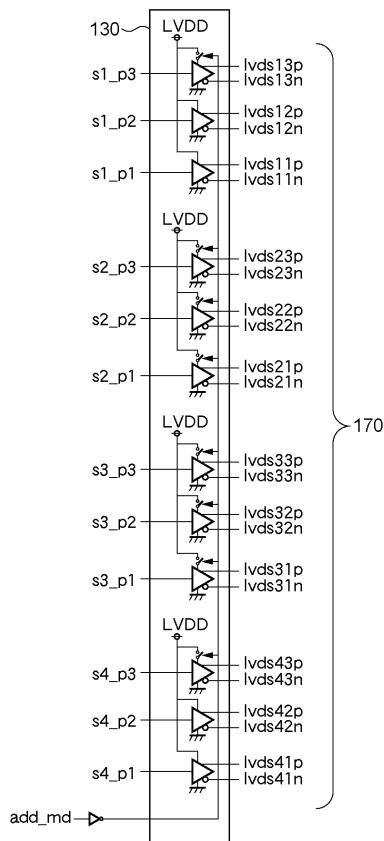

続いて、図13を用いて伝送部130を詳細な構成の一例を説明する。伝送部130は出力ドライバとして機能する12個のLVD<sub>S</sub>(Low voltage differential signaling)回路を有し、それに伝送部130へ入力されるシリアルデータ「s1\_p1」～「s4\_p3」が供給される。各LVD<sub>S</sub>回路は供給されたシリアルデータをLVD<sub>S</sub>信号へ変換して信号線170へ出力する。

#### 【0031】

上述されたように、変換部120から伝送部130へは12本の信号線を介してデータが転送される。通常モードにおいては、この12本の信号線をすべて用いてデータが転送されるが、圧縮モードでは12本の信号線のうち4本を用いてデータが転送される。そこで、圧縮モードでは、add\_md信号をHighにして、データ処理を行わないLVD<sub>S</sub>回路の電源をオフする。40 上述の例では、圧縮モードにおいて8個のLVD<sub>S</sub>回路の電源をオフにできる。その結果、圧縮モードでは通常モードと比較して伝送部130の消費電力を1/3に低減できる。伝送部130は固体撮像装置100の他の構成要素と比較して消費電力が大きいため、伝送部130での消費電力の低減は固体撮像装置100全体の消費電力の低減に大きく寄与する。また、PS変換部125を12本の信号線ごとに動作を停止可能ないように構成してもよい。そして、圧縮モードにおいて使用されない信号線に対応するPS変換動作を停止する。これは例えばPS変換部125で使用しているクロックを止めることによって実現されうる。これにより、圧縮モードでは通常モードと比較してPS変換部125の消費電力も1/3に低減できる。50

**【 0 0 3 2 】**

さらに、図13に示すように、圧縮モードにおいて用いられるLVDS回路の間に、圧縮モードにおいて用いられないLVDS回路を配置するように伝送部130が構成されてもよい。図13の例では、シリアルデータ「s4\_p2」が供給されるLVDS回路とシリアルデータ「s1\_p1」が供給されるLVDS回路との間に、圧縮モードで用いられないLVDS回路が配置されている。このように、圧縮モードで用いられるLVDS回路を分散して配置することにより、LVDS回路で生じる発熱を分散することができる。これにより、伝送部130の一部が過熱することを軽減できる。

**【 0 0 3 3 】**

さらに、上述の数値例のように、通常モードと圧縮モードの両方において伝送部130の各出力線から信号が絶えず出力されるように各種パラメータを設定してもよい。まず、固体撮像装置100で用いられるパラメータを以下のように定義する。

- ・ K : 1クロックあたりに撮像部110から読み出す画素数。

- ・ L : 伝送部130がLVDS信号を出力する信号線170の本数。

- ・ M : AD変換部112の分解能。AD変換部112は画素値をMビットのデジタルデータで表す。

- ・ N : 圧縮率。圧縮部121はN個の画素のデジタルデータを用いて1つのデジタルデータを出力する。

**【 0 0 3 4 】**

このようにパラメータを定義した場合に、伝送部130からビットを隙間無く出力するための条件式は以下のようになる。

条件1 :  $(K \times M) / L$  が自然数である。

条件2 :  $(K \times M) / N$  が自然数である。

**【 0 0 3 5 】**

$K \times M$  は1クロックあたりに変換部120へ入力される総ビット数を表す。そのため、通常モードにおいて伝送部130からビットが隙間無く出力されるためには、この総ビット数が信号線の本数Lで割り切れる必要があり、条件1が得られる。次に、 $(K \times M) / N$  は、圧縮モードにおける1クロックあたりの総ビット数を表す。そのため、圧縮モードにおいて伝送部130からビットが隙間無く出力されるためには、これも自然数となる必要があり、条件2が得られる。ビットが隙間無く出力されることで、通常モード、圧縮モードの両方において、信号線170の本数を最小化できる。圧縮モードにおいて、オフにできるLVDS回路の個数を最大化することができ、圧縮モードにおける伝送部130の消費電力が最小となる。この場合に、圧縮モードにおいてオンにするLVDS回路の個数は、 $L / N$  で与えられる。上述の例では、 $K = 8$ 、 $L = 12$ 、 $M = 12$ 、 $N = 3$  であるため、上述の条件をすべて満たし、4個のLVDS回路をオンにすればよいことがわかる。

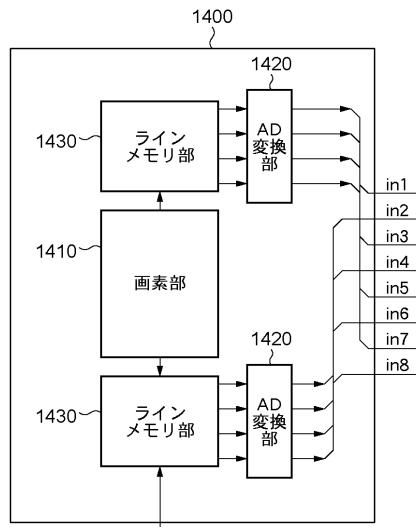

**【 0 0 3 6 】**

続いて、図14を用いて図1の撮像部110の変形例を説明する。本発明の一部の実施形態において、図1の固体撮像装置100は撮像部110の代わりに図14の撮像部1400を備えうる。撮像部1400も撮像部110と同様に、画素部1410、AD変換部1420、およびラインメモリ部1430を備えうる。画素部1410、AD変換部1420、およびラインメモリ部1430のそれぞれの構成は画素部111、AD変換部112、およびラインメモリ部113と同様であるが、撮像部1400ではこれらの配置が撮像部110と異なる。画素部1410からのアナログデータはラインメモリ部1430で一時的に保持される。ラインメモリ部1430に記憶されたアナログデータは1クロックあたり8個ずつAD変換部1420へ出力され、AD変換部1420においてそれぞれデジタルデータへ変換される。これらのデジタルデータが「in1」～「in8」として変換部120へ出力される。

**【 0 0 3 7 】**

続いて、図15を用いて圧縮部121が信号間引きによってデータ量を低減し高速駆動を行う場合の回路構成を説明する。この場合、圧縮部121はそれぞれが画素値を表す3

10

20

30

40

50

個のデジタルデータから1個のデジタルデータを第1データ変換部122へ出力する。図16は圧縮部121が間引き処理を行う場合の入出力レートを示す。間引き処理の場合も図8で説明された加算処理の場合と同様に圧縮部121の出力レートは入力レートの1/3となる。

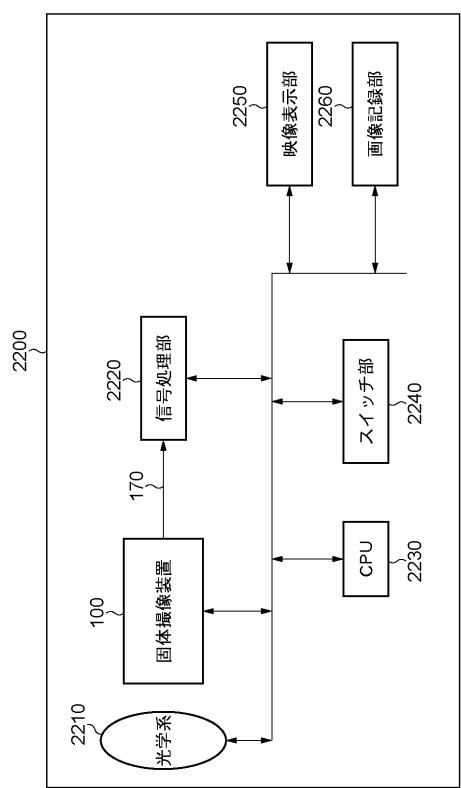

### 【0038】

図17を用いて上述した固体撮像装置100を撮像システム2200に適用した実施形態を説明する。撮像システム2200は例えばカメラであり、第1実施形態で説明された固体撮像装置100を備える。撮像システム2200は光学系2210、信号処理部2220、CPU2230、スイッチ部2240、映像表示部2250および画像記録部2260をさらに備えうる。光学系2210より入射した光に応じて、固体撮像装置100は前述のようにLVDs信号を信号線170へ出力する。出力されたLVDs信号は、さらに映像表示部2250、画像記録部2260に出力できるように信号処理部2220にて画像補正が行なわれる。信号処理後の画像信号は例えば映像表示部2250に表示され、画像記録部2260に記録される。またスイッチ部2240の操作によって動作モードが切り替えられると、その情報はCPU2230に入力され、CPU2230にて光学系2210、固体撮像装置100、信号処理部2220、映像表示部2250および画像記録部2260の制御が変更される。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図10A】

【図10B】

【図11A】

【図11B】

【図 1 1 C】

【図 1 1 D】

【図 1 2 A】

【図 1 2 B】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(72)発明者 林 英俊

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 竹中 真太郎

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 山崎 竜彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 山口 祐一郎

(56)参考文献 特開2008-283331(JP,A)

特開2010-283671(JP,A)

特開2008-40272(JP,A)

特開平9-46480(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/222-5/257

5/30-5/378

9/04-9/11