(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년03월06일

(11) 등록번호 10-1119371

(24) 등록일자 2012년02월15일

(51) 국제특허분류(Int. Cl.)

*G11C 16/34* (2006.01) *G11C 16/14* (2006.01)

*G11C 16/24* (2006.01) *G11C 16/06* (2006.01)

(21) 출원번호 10-2010-0039897

(22) 출원일자 2010년04월29일

심사청구일자 2010년04월29일

(65) 공개번호 10-2011-0120470

(43) 공개일자 2011년11월04일

(56) 선행기술조사문헌

JP09180475 A

KR1020100006666 A

KR1020050064033 A

KR1020010055299 A

전체 청구항 수 : 총 13 항

심사관 : 이진익

(54) 발명의 명칭 반도체 메모리 장치 및 이의 동작 방법

**(57) 요 약**

반도체 메모리 장치 및 이의 동작 방법은 메모리 셀의 문턱전압을 션싱하기 위한 조건을 동작 종류에 따라 다르게 설정함으로써, 프로그램 동작과 소거 동작의 반복 실시에 의해 메모리 장치의 물리적/전기적 특성이 저하되는 것을 최소화하고, 동작의 신뢰성을 향상시킬 수 있다.

**대 표 도** - 도1a

## 특허청구의 범위

### 청구항 1

비트라인과 연결된 메모리 스트링;

소거 동작 또는 프로그램 동작 후 상기 메모리 스트링에 포함된 메모리 셀의 문턱전압 레벨에 따라 상기 메모리 셀에 저장된 데이터를 검증하기 위한 페이지 버퍼; 및

상기 메모리 셀의 데이터를 검증하기 위해 상기 비트라인으로부터 상기 페이지 버퍼로 공급되는 센싱 전류의 레벨을, 상기 프로그램 동작 또는 상기 소거 동작에 의해 변경된 상기 메모리 셀의 상기 문턱전압 레벨에 따라 조절하기 위한 센싱 제어 회로를 포함하는 반도체 메모리 장치.

### 청구항 2

제 1 항에 있어서,

상기 센싱 제어 회로는 상기 메모리 셀의 상기 문턱전압 레벨에 비례하여 상기 센싱 전류의 레벨을 조절하는 반도체 메모리 장치.

### 청구항 3

제 1 항에 있어서,

상기 센싱 제어 회로는 상기 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 상기 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 상기 센싱 전류의 레벨을 높게 설정하는 반도체 메모리 장치.

### 청구항 4

제 3 항에 있어서,

상기 메모리 셀의 문턱전압 레벨이 상기 소거 동작에 의해 낮아진 경우, 상기 센싱 제어 회로가 상기 센싱 전류의 레벨을 제1 레벨로 설정하고,

상기 메모리 셀의 문턱전압 레벨이 상기 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 상기 센싱 제어 회로가 상기 센싱 전류의 레벨을 상기 제1 레벨보다 높은 제2 레벨로 설정하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 상기 센싱 제어 회로가 상기 센싱 전류의 레벨을 상기 제2 레벨보다 높은 제3 레벨로 설정하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 상기 센싱 제어 회로가 상기 센싱 전류의 레벨을 상기 제3 레벨보다 높은 제4 레벨로 설정하는 반도체 메모리 장치.

### 청구항 5

제 1 항에 있어서, 상기 센싱 제어 회로는,

상기 비트라인을 프리차지할 때 제1 전압을 출력하고, 상기 비트라인으로부터 상기 센싱 전류를 상기 페이지 버퍼로 공급할 때 상기 제1 전압보다 낮은 제2 전압을 출력하도록 구성된 센싱 전압 생성부; 및

상기 제1 전압 또는 상기 제2 전압에 응답하여 상기 비트라인과 상기 페이지 버퍼의 연결 저항을 조절하는 센싱 회로를 포함하는 반도체 메모리 장치.

**청구항 6**

제 5 항에 있어서,

상기 센싱 전압 발생 회로는 상기 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 상기 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 상기 제2 전압의 레벨을 더 높게 출력하는 반도체 메모리 장치.

**청구항 7**

제 6 항에 있어서,

상기 메모리 셀의 문턱전압 레벨이 상기 소거 동작에 의해 낮아진 경우, 상기 센싱 전압 발생 회로가 제1 센싱 레벨의 상기 제2 전압을 출력하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 상기 센싱 전압 발생 회로가 상기 제1 센싱 레벨보다 높은 제2 센싱 레벨의 상기 제2 전압을 출력하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 상기 센싱 전압 발생 회로가 상기 제2 센싱 레벨보다 높은 제3 센싱 레벨의 상기 제2 전압을 출력하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 상기 센싱 전압 발생 회로가 상기 제3 센싱 레벨보다 높은 제4 센싱 레벨의 상기 제2 전압을 출력하는 반도체 메모리 장치.

**청구항 8**

제 5 항에 있어서,

상기 센싱 전압 발생 회로는 상기 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 상기 제1 전압의 레벨을 더 높게 출력하는 반도체 메모리 장치.

**청구항 9**

제 8 항에 있어서,

상기 메모리 셀의 문턱전압 레벨이 상기 소거 동작에 의해 낮아진 경우, 상기 센싱 전압 발생 회로가 제1 센싱 레벨의 상기 제1 전압을 출력하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 상기 센싱 전압 발생 회로가 상기 제1 센싱 레벨보다 높은 제2 센싱 레벨의 상기 제1 전압의 레벨을 출력하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 상기 센싱 전압 발생 회로가 상기 제2 센싱 레벨보다 높은 제3 센싱 레벨의 상기 제1 전압을 출력하고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 상기 센싱 전압 발생 회로가 상기 제3 센싱 레벨보다 높은 제4 센싱 레벨의 상기 제1 전압을 출력하는 반도체 메모리 장치.

**청구항 10**

제 5 항에 있어서,

상기 센싱 전압 발생 회로는 상기 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 상기 제1 전압이 인가된 후 상기 제2 전압이 인가될 때까지의 이벨

류에이션 타임이 더 감소하는 반도체 메모리 장치.

### 청구항 11

제 10 항에 있어서,

상기 메모리 셀의 문턱전압 레벨이 상기 소거 동작에 의해 낮아진 경우, 상기 이벨류에이션 타임이 제1 값으로 설정되고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우, 상기 이벨류에이션 타임이 상기 제1 값보다 작은 제2 값으로 설정되고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우, 상기 이벨류에이션 타임이 상기 제2 값보다 작은 제3 값으로 설정되고,

상기 문턱전압 레벨이 상기 프로그램 동작에 의해 상기 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우, 상기 이벨류에이션 타임이 상기 제3 값보다 작은 제4 값으로 설정되는 반도체 메모리 장치.

### 청구항 12

비트라인과 연결된 메모리 셀의 소거 동작을 실시하는 단계;

상기 소거 동작 후 상기 비트라인을 통해 흐르는 센싱 전류의 레벨을 제1 레벨로 설정하여 상기 메모리 셀에 저장된 데이터를 검증하는 단계;

상기 메모리 셀의 프로그램 동작을 실시하는 단계; 및

상기 프로그램 동작 후 상기 비트라인을 통해 흐르는 센싱 전류의 레벨을 제1 레벨보다 높게 설정하여 상기 메모리 셀에 저장된 데이터를 검증하는 단계를 포함하는 반도체 메모리 장치의 동작 방법.

### 청구항 13

제 12 항에 있어서,

상기 프로그램 동작에 의해 상기 메모리 셀의 문턱전압 레벨이 PV1 레벨까지 상승하는 경우 상기 센싱 전류의 레벨이 상기 제1 레벨보다 높은 제2 레벨로 설정되고,

상기 프로그램 동작에 의해 상기 문턱전압 레벨이 상기 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 상기 센싱 제어 회로가 상기 센싱 전류의 레벨을 상기 제2 레벨보다 높은 제3 레벨로 설정하고,

상기 프로그램 동작에 의해 상기 문턱전압 레벨이 상기 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 상기 센싱 제어 회로가 상기 센싱 전류의 레벨을 상기 제3 레벨보다 높은 제4 레벨로 설정하는 반도체 메모리 장치의 동작 방법.

## 명세서

### 기술 분야

[0001]

본 발명은 반도체 메모리 장치 및 이의 동작 방법에 관한 것으로, 특히 동작 조건을 최적화하기 위한 반도체 메모리 장치 및 이의 동작 방법에 관한 것이다.

### 배경기술

[0002]

반도체 메모리 장치는 입력된 데이터를 저장하고, 저장된 데이터를 출력한다. 플래시 메모리와 같은 불휘발성 메모리 장치에서는 프로그램 동작으로 데이터를 저장하고, 소거 동작으로 데이터를 삭제하며, 리드 동작으로 데

이터를 출력한다.

[0003] 플래시 메모리 장치에서 메모리 셀에 저장되는 데이터에 따라 메모리 셀의 문턱전압 레벨이 달라진다. 즉, 프로그램 동작이나 소거 동작에 의해 메모리 셀의 문턱전압이 변하는데, 메모리 셀의 문턱전압이 목표 전압으로 변하였는지를 확인하기 위하여 프로그램 검증 동작이나 소거 검증 동작을 실시한다.

[0004] 일반적인 플래시 메모리 장치에서, 비트라인을 제1 전압으로 프리차지하고 비트라인에 연결된 메모리 셀의 게이트에 검증 전압을 인가하면, 검증 전압과 메모리 셀의 문턱전압의 차이에 따라 비트라인의 전압이 유지되거나 변하게 된다. 비트라인의 전압 변화를 이용하여 메모리 셀의 문턱전압을 확인하는데, 프로그램 동작 후 실시되는 프로그램 검증 동작과 소거 동작 후 실시되는 소거 검증 동작에서 동일한 센싱 전류 레벨(Sensing Current Level)을 적용하여 문턱전압을 확인한다.

[0005] 소거 동작을 실시하면 메모리 셀의 문턱전압이 0V보다 낮아진다. 따라서, 소거 검증 동작에서는 0V보다 낮은 메모리 셀의 문턱전압 레벨을 센싱해야 한다.

[0006] 프로그램 검증 동작과 달리, 소거 검증 동작은 비트라인에 연결된 메모리 셀들의 모든 게이트들에 동일한 소거 검증 전압을 인가하여 메모리 셀들의 문턱전압들을 센싱한다. 이때, 게이트에 인가되는 소거 검증 전압은 프로그램 동작이 실시된 메모리 셀의 리드 동작 시 선택되지 않은 메모리 셀들의 게이트들에 인가되는 리드 패스 전압보다 낮다. 이로 인해, 실제로 센싱되는 문턱전압의 레벨은 게이트에 인가되는 전압보다 낮아지게 된다. 이를 BPD 효과(Back Pattern Dependency effect)라 한다. 이로써, 음전압을 사용하지 않고도 음전위의 문턱전압을 센싱할 수 있다.

[0007] 한편, 프로그램 동작과 소거 동작의 누적 실시 횟수가 증가됨에 따라 전류 감소(current degrade) 영향을 많이 받게 되고, 이로 인해 소거 검증 레벨은 점점 하향되는 특성을 보이게 된다. 소거 검증 레벨은 점점 하향됨에 따라, 소거 동작을 위해 인가되는 소거 전압의 레벨은 점점 높아지고, 메모리 셀의 전기적 특성이 저하된다.

[0008] 또한, 프로그램 동작과 소거 동작의 누적 실시 횟수가 많이 않은 경우에도, 센싱 전류 레벨에 따라 센싱되는 문턱전압의 레벨이 달라지기 때문에 소거 동작 시 인가되는 소거 전압의 레벨에도 영향을 미치게 된다.

## 발명의 내용

### 해결하려는 과제

[0009] 본 발명은 메모리 셀의 데이터(또는, 문턱전압)을 센싱하기 위한 조건을 동작 종류에 따라 다르게 설정함으로써, 프로그램 동작과 소거 동작의 반복 실시에 의해 메모리 장치의 물리적/전기적 특성이 저하되는 것을 최소화하고, 동작의 신뢰성을 향상시킬 수 있는 반도체 메모리 장치 및 이의 동작 방법을 제공한다.

### 과제의 해결 수단

[0010] 본 발명의 실시예에 따른 반도체 메모리 장치는 비트라인과 연결된 메모리 스트리밍과, 소거 동작 또는 프로그램 동작 후 메모리 스트리밍에 포함된 메모리 셀의 문턱전압 레벨에 따라 메모리 셀에 저장된 데이터를 검증하기 위한 페이지 버퍼, 및 메모리 셀의 데이터를 검증하기 위해 비트라인으로부터 페이지 버퍼로 공급되는 센싱 전류의 레벨을, 프로그램 동작 또는 소거 동작에 의해 변경된 메모리 셀의 문턱전압 레벨에 따라 조절하기 위한 센싱 제어 회로를 포함한다.

[0011] 센싱 제어 회로는 메모리 셀의 문턱전압 레벨에 비례하여 센싱 전류의 레벨을 조절한다.

[0012] 센싱 제어 회로는 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 센싱 전류의 레벨을 높게 설정한다.

[0013] 메모리 셀의 문턱전압 레벨이 소거 동작에 의해 낮아진 경우, 센싱 제어 회로가 센싱 전류의 레벨을 제1 레벨로 설정하고, 메모리 셀의 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 센싱 제어 회로가 센싱 전류의 레벨을 제1 레벨보다 높은 제2 레벨로 설정하고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 센싱 제어 회로가 센싱 전류의 레벨을 제2 레벨보다 높은 제3 레벨로 설정하고, 문턱전압 레벨이 프로그램 동작에 의해 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 센싱 제어 회로

가 센싱 전류의 레벨을 제3 레벨보다 높은 제4 레벨로 설정한다.

- [0014] 센싱 제어 회로는, 비트라인을 프리차지할 때 제1 전압을 출력하고, 비트라인으로부터 센싱 전류를 페이지 버퍼로 공급할 때 제1 전압보다 낮은 제2 전압을 출력하도록 구성된 센싱 전압 생성부, 및 제1 전압 또는 제2 전압에 응답하여 비트라인과 페이지 버퍼의 연결 저항을 조절하는 센싱 회로를 포함한다.

- [0015] 센싱 전압 발생 회로는 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 제2 전압의 레벨을 더 높게 출력할 수 있다.

- [0016] 메모리 셀의 문턱전압 레벨이 소거 동작에 의해 낮아진 경우, 센싱 전압 발생 회로가 제1 센싱 레벨의 제2 전압을 출력하고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 센싱 전압 발생 회로가 제1 센싱 레벨보다 높은 제2 센싱 레벨의 제2 전압의 레벨을 출력하고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 센싱 전압 발생 회로가 제2 센싱 레벨보다 높은 제3 센싱 레벨의 제2 전압을 출력하고, 문턱전압 레벨이 프로그램 동작에 의해 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 센싱 전압 발생 회로가 제3 센싱 레벨보다 높은 제4 센싱 레벨의 제2 전압을 출력한다.

- [0017] 센싱 전압 발생 회로는 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 제1 전압의 레벨을 더 높게 출력할 수 있다.

- [0018] 메모리 셀의 문턱전압 레벨이 소거 동작에 의해 낮아진 경우, 센싱 전압 발생 회로가 제1 센싱 레벨의 제1 전압을 출력하고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 센싱 전압 발생 회로가 제1 센싱 레벨보다 높은 제2 센싱 레벨의 제1 전압의 레벨을 출력하고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 센싱 전압 발생 회로가 제2 센싱 레벨보다 높은 제3 센싱 레벨의 제1 전압을 출력하고, 문턱전압 레벨이 프로그램 동작에 의해 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 센싱 전압 발생 회로가 제3 센싱 레벨보다 높은 제4 센싱 레벨의 제1 전압을 출력한다.

- [0019] 센싱 전압 발생 회로는 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 제1 전압이 인가된 후 제2 전압이 인가될 때까지의 이벨류에이션 타임이 더 감소시킬 수 있다.

- [0020] 메모리 셀의 문턱전압 레벨이 소거 동작에 의해 낮아진 경우, 이벨류에이션 타임이 제1 값으로 설정되고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우, 이벨류에이션 타임이 제1 값보다 작은 제2 값으로 설정되고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우, 이벨류에이션 타임이 제2 값보다 작은 제3 값으로 설정되고, 문턱전압 레벨이 프로그램 동작에 의해 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우, 이벨류에이션 타임이 제3 값보다 작은 제4 값으로 설정된다.

- [0021] 본 발명의 실시예에 따른 반도체 메모리 장치의 동작 방법은 비트라인과 연결된 메모리 셀의 소거 동작을 실시하는 단계와, 소거 동작 후 비트라인을 통해 흐르는 센싱 전류의 레벨을 제1 레벨로 설정하여 메모리 셀에 저장된 데이터를 검증하는 단계와, 메모리 셀의 프로그램 동작을 실시하는 단계, 및 프로그램 동작 후 비트라인을 통해 흐르는 센싱 전류의 레벨을 제1 레벨보다 높게 설정하여 메모리 셀에 저장된 데이터를 검증하는 단계를 포함한다.

- [0022] 프로그램 동작에 의해 메모리 셀의 문턱전압 레벨이 PV1 레벨까지 상승하는 경우 센싱 전류의 레벨이 제1 레벨보다 높은 제2 레벨로 설정되고, 프로그램 동작에 의해 문턱전압 레벨이 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 센싱 제어 회로가 센싱 전류의 레벨을 제2 레벨보다 높은 제3 레벨로 설정하고, 프로그램 동작에 의해 문턱전압 레벨이 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 센싱 제어 회로가 센싱 전류의 레벨을 제3 레벨보다 높은 제4 레벨로 설정한다.

### 발명의 효과

- [0023] 본 발명은 메모리 셀의 문턱전압을 센싱하기 위한 조건을 동작 종류에 따라 다르게 설정함으로써, 프로그램 동작과 소거 동작의 반복 실시에 의해 메모리 장치의 물리적/전기적 특성이 저하되는 것을 최소화하고, 동작의 신뢰성을 향상시킬 수 있다.

## 도면의 간단한 설명

[0024]

도 1a 및 도 1b는 본 발명의 반도체 메모리 장치를 설명하기 위한 도면이다.

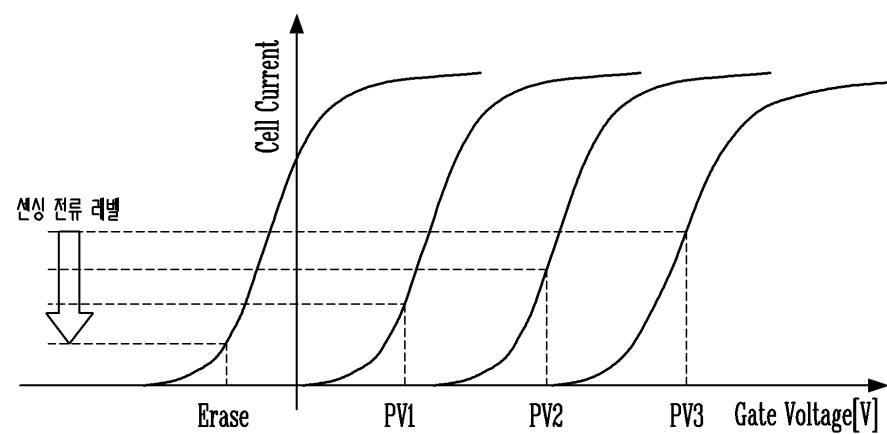

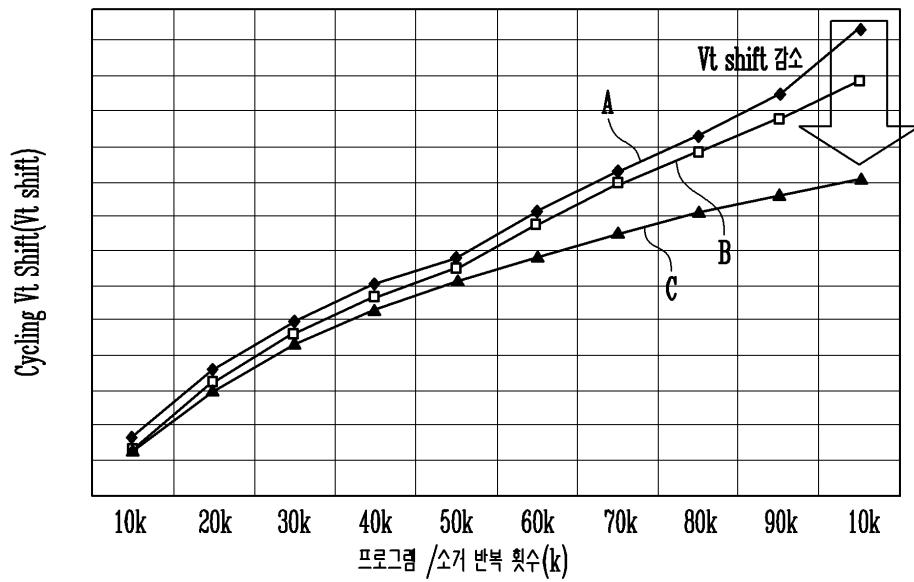

도 2는 프로그램/소거 동작 실시 횟수의 증가에 의해 발생하는 문턱전압의 변화를 설명하기 위한 그래프이다.

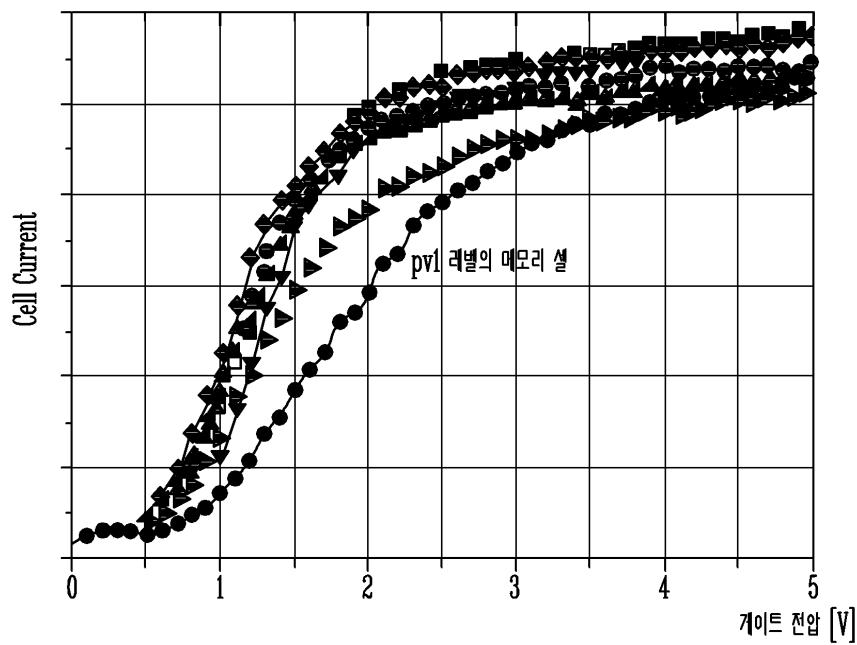

도 3은 메모리 셀들의 문턱전압들을 설명하기 위한 그래프이다.

도 4는 메모리 셀의 문턱전압 레벨에 따라 변경되는 센싱 전류의 레벨을 설명하기 위한 도면이다.

## 발명을 실시하기 위한 구체적인 내용

[0025]

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 설명하기로 한다. 그러나, 본 발명은 이하에서 개시되는 실시예에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 본 발명의 범위가 다음에 상술하는 실시예에 한정되는 것은 아니다. 단지 본 실시예는 본 발명의 개시가 완전하도록 하며 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명의 범위는 본원의 특허 청구 범위에 의해서 이해되어야 한다.

[0026]

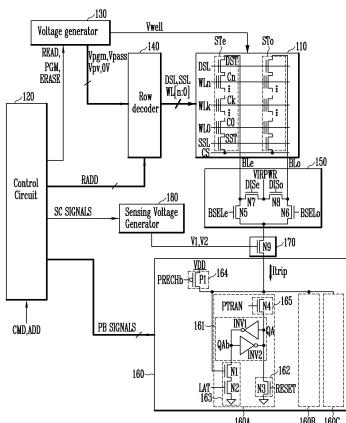

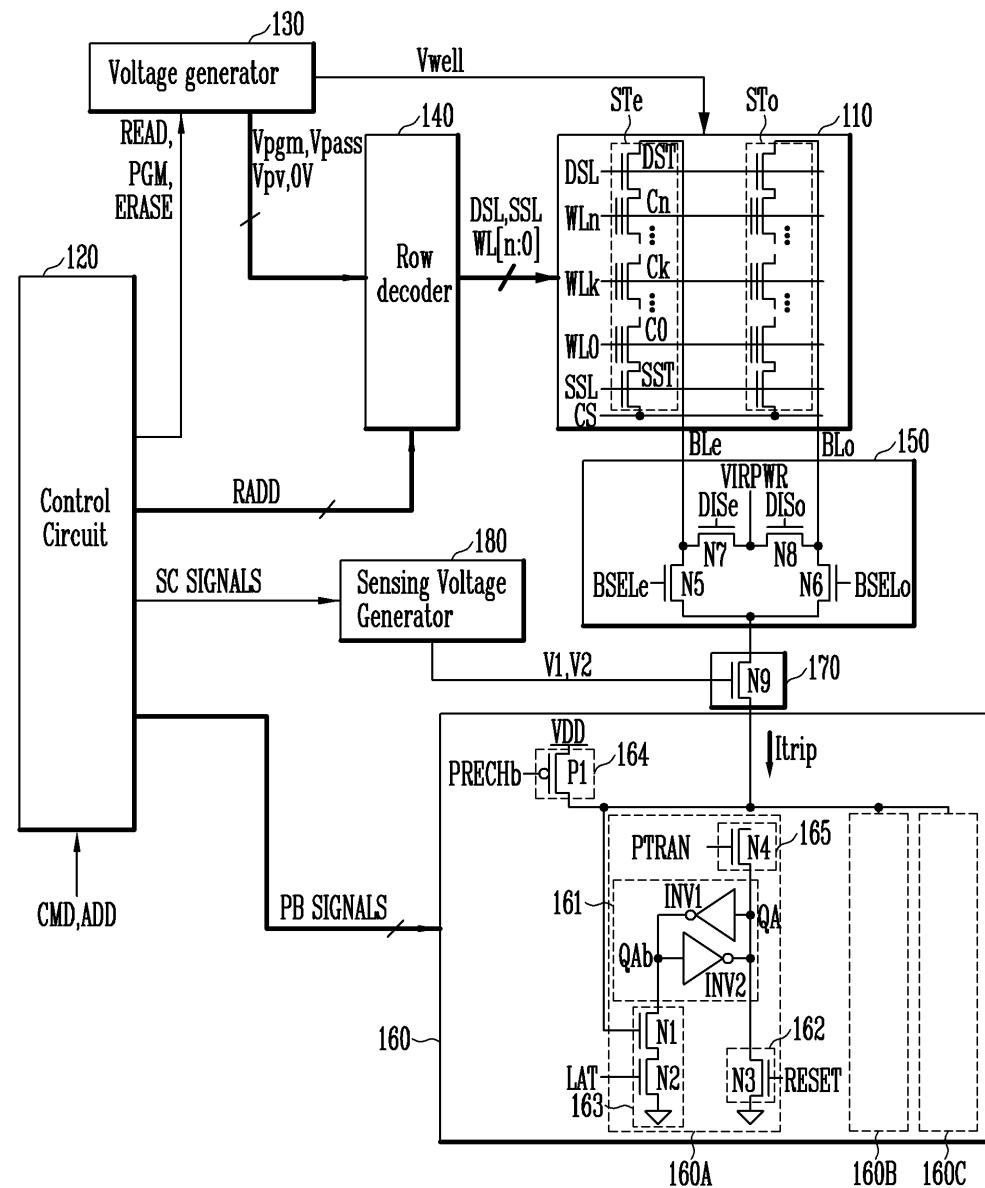

도 1a 및 도 1b는 본 발명의 반도체 메모리 장치를 설명하기 위한 도면이다.

[0027]

도 1a를 참조하면, 반도체 메모리 장치는 메모리 어레이(110), 제어 회로(120), 전압 공급 회로(130, 140), 비트라인 선택 회로(150), 페이지 버퍼(160), 센싱 제어 회로(170, 180)를 포함한다.

[0028]

메모리 어레이(110)는 다수의 메모리 블록들을 포함한다. 각각의 메모리 블록은 비트라인들(BLe, BLo)과 각각 연결되고 공통 소스 라인(CS)과 병렬로 연결되는 메모리 스트링들(STe, STo)을 포함한다. 편의상, 하나의 메모리 블록에 포함된 두 개의 메모리 스트링들(STe, STo)만을 도시하였다.

[0029]

메모리 스트링(STe)은 비트라인(BLe)과 공통 소스 라인(CS) 사이에 직렬로 연결된 드레인 셀렉트 트랜지스터(DST), 셀 스트링(Co 내지 Cn) 및 소스 셀렉트 트랜지스터(SST)를 포함한다. 셀 스트링은 드레인 셀렉트 트랜지스터(DST)와 소스 셀렉트 트랜지스터(SST) 사이에 직렬로 연결된 메모리 셀들(Co 내지 Cn)을 포함한다.

[0030]

구체적으로, 드레인 셀렉트 트랜지스터(DST)는 비트라인(BLe)과 셀 스트링(Co 내지 Cn) 사이에 연결되고, 드레인 셀렉트 라인(DSL)에 인가되는 전압에 따라 셀 스트링(Co 내지 Cn)을 비트라인(BLe)과 연결시킨다. 메모리 셀들(Co 내지 Cn)은 워드라인들(WL0 내지 WLn)에 인가되는 전압들에 따라 동작한다. 소스 셀렉트 트랜지스터(SS T)는 셀 스트링(Co 내지 Cn)과 공통 소스 라인(CS) 사이에 연결되며, 소스 셀렉트 라인(SSL)에 인가되는 전압에 따라 셀 스트링(Co 내지 Cn)을 공통 소스 라인(CS)과 연결시킨다.

[0031]

한편, 하나의 워드라인(WL0)에 연결된 메모리 셀들은 페이지가 된다. 또한, 하나의 워드라인(WL0)에 연결된 메모리 셀들 중 짹수 번째 비트라인(BLe)과 연결되는 짹수 번째 메모리 셀들은 이본 페이지가 되고, 홀수 번째 비트라인(BLo)과 연결되는 홀수 번째 메모리 셀들은 오드 페이지가 된다. 페이지는 프로그램 동작의 기본 단위가 되고, 메모리 블록은 소거 동작의 기본 단위가 된다.

[0032]

제어 회로(120)는 명령 신호(CMD)에 응답하여 내부적으로 프로그램 동작 신호(PGM), 리드 동작 신호(READ) 또는 소거 동작 신호(ERASE)를 출력하고, 동작 종류에 따라 페이지 버퍼(160)와 같은 내부 회로를 제어하기 위한 제어 신호들(PB SIGNALS)(예, PRECHb, PTRAN, LAT, RESET)을 출력한다. 또한, 제어 회로(120)는 어드레스 신호(ADD)에 응답하여 내부적으로 로우 어드레스 신호(RADD)와 컬럼 어드레스 신호(미도시)를 출력한다.

[0033]

전압 공급 회로(130, 140)는 제어부(120)의 신호(READ, PGE, ERASE, RADD)에 따라 메모리 셀들의 프로그램 동작, 소거 동작 또는 리드 동작에 필요한 동작 전압들을 선택된 메모리 블록으로 공급한다. 이러한 전압 공급 회로는 전압 발생 회로(130) 및 로우 디코더(140)를 포함하며, 이들의 구체적인 설명은 다음과 같다.

[0034]

전압 발생 회로(130)는 제어 회로(120)의 내부 명령 신호인 동작 신호들(PGM, READ)에 응답하여 메모리 셀들의 프로그램 동작 또는 리드 동작을 위한 전압들(예, Vpgm, Vpass, Vvp, OV)을 글로벌 라인들로 출력한다. 또한, 전압 발생 회로(130)는 소거 동작 신호(ERASE)에 응답하여 메모리 블록의 벌크(예, P-well)로 메모리 셀들의 소거 동작을 위한 전압(Vwell)을 출력한다.

[0035]

로우 디코더(140)는 전압 발생 회로(130)에서 발생된 동작 전압들을 제어 회로(120)의 로우 어드레스 신호들(RADD)에 응답하여 메모리 어레이(110)의 메모리 블록들 중 선택된 메모리 블록의 스트링들(STe, STo)로 전달한다. 즉, 동작 전압들은 선택된 메모리 블록의 로컬 라인들(DSL, WL[n:0], SSL)로 인가된다.

- [0036] 비트라인 선택 회로(150)는 비트라인 선택 신호들(BSLe, BSELo)에 응답하여 이븐 비트라인(BLe)과 오드 비트라인(BLo) 중 하나의 비트라인을 선택하고, 선택된 비트라인은 센싱 제어 회로의 센싱 회로(170)를 통해 페이지 버퍼(160)와 연결된다. 또한, 비트라인 선택 회로(150)는 이븐 비트라인(BLe)과 오드 비트라인(BLo) 모두 또는 하나의 비트라인을 프리차지하거나 디스차지시키는 기능을 수행한다. 이를 위해, 비트라인 선택 회로(150)는 비트라인 연결 회로(N5, N6)와 디스차지 회로(N7, N8)를 포함하며, 구체적으로 설명하면 다음과 같다.

- [0037] 디스차지 회로(N7, N8)는 신호(DISe, DISo)에 따라 비트라인들(BLe, BLo)을 가상 전압원(VIRPWR)으로 각각 연결하는 스위칭 소자들(N7, N8)을 포함한다. 이러한 디스차지 회로는 두 개의 스위칭 소자들(N7, N8)을 모두 턴온시켜 비트라인들(BLe, BLo)을 모두 프리차지하거나 디스차지시킬 수 있으며, 하나의 스위칭 소자만을 동작시켜 하나의 비트라인을 프리차지하거나 디스차지할 수 있다.

- [0038] 비트라인 연결 회로(N5, N6)는 이븐 비트라인(BLe)과 연결되고 이븐 비트라인 선택 신호(BSLe)에 응답하여 동작하는 스위칭 소자(N4)와 오드 비트라인(BLo)과 연결되고 오드 비트라인 선택 신호(BSLo)에 응답하여 동작하는 스위칭 소자(N5)를 포함한다. 이러한 비트라인 연결 회로(N5, N6)는 비트라인 선택 신호들(BSLe, BSLo)에 응답하여 한 쌍의 비트라인들(BLe, BLo) 중 하나의 비트라인을 다른 회로(예, 센싱 회로)와 연결시킨다.

- [0039] 이러한 비트라인 선택 회로(150)는 한쌍의 이븐 비트라인(BLe)과 오드 비트라인(BLo)에 하나의 페이지 버퍼(160)가 할당된 경우 필요하며, 비트라인마다 페이지 버퍼(160)가 할당되는 경우 생략 가능하다.

- [0040] 페이지 버퍼(160)는 비트라인 선택 회로(150)에 의해 선택된 비트라인과 센싱 제어 회로의 센싱 회로(170)를 통해 전기적으로 연결되며, 프로그램 동작 시 제어부(120)의 제어 신호들(PS SIGNALS; PRECHb, PTRAN, LAT, RESET)에 응답하여 메모리 셀에 데이터를 입출력하는데 필요한 전압을 선택된 비트라인에 인가한다. 구체적으로, 페이지 버퍼(160)는 메모리 셀의 프로그램 동작, 소거 동작 또는 리드 동작에 필요한 프리치자 동작 시 비트라인(BLe)을 프리차지하거나, 비트라인(BLe)의 전압 변화에 따라 검출된 메모리 셀의 문턱전압 레벨에 대응하는 데이터를 래치한다. 즉, 페이지 버퍼(160)는 메모리 셀에 저장되는 데이터에 따라 비트라인(BLe)의 전압을 조절하고, 메모리 셀에 저장된 데이터를 검출한다. 이러한 페이지 버퍼(160)의 구체적인 구성 및 동작을 설명하면 다음과 같다.

- [0041] 페이지 버퍼(160)는 프리차지 회로(164)와 래치 회로들(160A, 160B, 160C)을 포함한다.

- [0042] 프리차지 회로(164)는 전원전압 단자(VDD)와 감지 노드(S0) 사이에 접속되고 프리차지 신호(PRECHb)에 응답하여 동작하는 스위칭 소자(P1)를 포함한다. 이러한 프리차지 회로(161)는 프리차지 신호(PRECHb)에 응답하여 감지 노드(S0)를 프리차지한다.

- [0043] 각각의 래치 회로(160A)는 래치부(161), 리셋 회로(162), 래치 제어 회로(163), 및 전송 회로(165)를 포함한다. 래치부(161)는 2개의 인버터(INV1, INV2)로 구성되며, 메모리 셀에 저장될 데이터를 래치하거나 메모리 셀에 저장된 데이터를 래치한다.

- [0044] 센싱 회로(163)는 래치(161)의 제2 입력단자(QAb)와 접지 단자에 직렬로 접속된 스위칭 소자들(N1, N2)을 포함한다. 이 중에서 스위칭 소자(N1)는 감지 노드(S0)의 전압 레벨에 따라 동작하고, 스위칭 소자(N2)는 래치 신호(LAT)에 따라 동작한다. 즉, 센싱 회로(163)는 센싱된 메모리 셀의 데이터에 따라 달라지는 감지 노드(S0)의 전압 레벨과 래치 신호(LAT)에 응답하여 래치(161)의 데이터를 메모리 셀의 데이터로 변경한다.

- [0045] 리셋 회로(162)는 래치(161)의 제1 입력단자(QA)와 접지 단자 사이에 접속되고 리셋 신호(RESET)에 응답하여 동작하는 스위칭 소자(N3)를 포함한다. 이러한 리셋 회로(163)는 리셋 신호(RESET)에 응답하여 래치(161)에 저장된 데이터를 '0' 상태로 설정하는 래치(161)의 초기화 동작을 수행한다.

- [0046] 전송 회로(165)는 래치(161)의 제1 입력단자(QA)와 감지 노드(S0) 사이에 접속되고 전송 신호(PTRAN)에 응답하여 동작하는 스위칭 소자(N4)를 포함한다. 이러한 전송 회로(165)는 메모리 셀의 프로그램 동작 시 메모리 셀에 저장하기 위하여 래치(161)에 래치되어 있는 데이터에 따라 비트라인(BLe)의 전압을 조절하기 위한 동작을 수행한다.

- [0047] 래치 회로들(160A, 160B, 160C)은 모두 동일한 구성으로 이루어지고 입력되는 신호만 다르게 입력될 수 있다. 각각의 래치 회로들(160A, 160B, 160C)은 메모리 셀에 저장될 데이터를 래치하거나, 검증 동작의 결과를 래치하거나, 메모리 셀로부터 독출된 데이터를 저장하기 위하여 서로 다른 구성으로 이루어질 수도 있다.

- [0048] 센싱 제어 회로(170, 180)는 메모리 셀의 데이터 또는 문턱전압을 센싱하기 위하여 비트라인을 프리차지하거나 센싱의 기준이 되는 센싱 전류(Itrip)의 레벨을 조절하는 기능을 수행한다. 이러한 센싱 제어 회로는 제어 회로

(120)의 센싱 제어 신호(SC SIGNALS)에 따라 동작하는 센싱 전압 생성 회로(180)와 센싱 전압 생성 회로에서 출력되는 전압들(V1, V2)에 응답하여 동작하는 센싱 회로(170)를 포함한다.

[0049] 센싱 회로(170)는 비트라인과 페이지 버퍼(160)를 전기적으로 연결시키기 위한 스위칭 소자(N9)를 포함하며, 비트라인에 프리차지되는 전압과 페이지 버퍼(160)가 비트라인의 전압 레벨을 검출하기 위한 센싱 전류 레벨을 조절하는 기능을 수행한다. 구체적으로, 센싱 회로(170)는 비트라인을 프리차지 하기 위하여 센싱 전압 생성 회로(180)로부터 펄스 형태로 출력되는 제1 레벨의 제1 전압(V1)에 응답하여 페이지 버퍼(160)로부터 출력되는 전압을 비트라인으로 전달한다. 이어서, 전압 공급 회로(130, 140)가 선택된 메모리 셀에 검증 전압을 인가하고 나머지 메모리 셀들에 페스 전압을 인가하면, 선택된 메모리 셀의 문턱전압에 따라 비트라인에 프리차지된 전압이 유지되거나 디스차지된다. 이후, 비트라인의 전압을 센싱하기 위하여 센싱 전압 생성 회로(180)로부터 제1 레벨보다 낮은 제2 레벨의 펄스 형태로 출력되는 제2 전압(V2)에 응답하여 센싱 회로(170)는 비트라인의 전압을 페이지 버퍼(160)의 감지 노드(S0)로 전달하고, 페이지 버퍼(160)의 래치 제어 회로(163)는 감지 노드(S0)의 전위와 래치 신호(LAT)에 응답하여 래치부(161)의 데이터를 변경한다. 이로써 메모리 셀에 저장된 데이터가 센싱된다. 이러한 동작은 프로그램 검증 동작, 소거 검증 도작 또는 리드 동작 시 적용될 수 있다.

[0050] 한편, 도 1b에서와 같이, 센싱 제어 회로(190)가 제1 레벨 또는 제1 레벨보다 낮은 제2 레벨의 비트라인 선택 신호들(BSELe, BSEL0)을 비트라인 선택 회로(150)로 출력할 수 있다. 센싱 제어 회로(190)는 이븐 비트라인(BLe)이 선택되면 이븐 비트라인 선택 신호(BSELe)를 제1 레벨의 펄스 형태로 출력한 후, 이븐 비트라인 선택 신호(BSEL0)를 제1 레벨보다 낮은 제2 레벨의 펄스 형태로 출력한다. 또한, 센싱 제어 회로(190)는 오드 비트라인(BLo)이 선택되면 오드 비트라인 선택 신호(BSEL0)를 제1 레벨의 펄스 형태로 출력한 후, 오드 비트라인 선택 신호(BSELe)를 제1 레벨보다 낮은 제2 레벨의 펄스 형태로 출력한다.

[0051] 이 경우, 비트라인 선택 회로(150)(보다 구체적으로, 비트라인 선택 회로(150)의 스위칭 소자들(N5, N6))가 도 1a에서 설명한 센싱 회로(170)의 기능을 수행하게 되므로, 센싱 회로(170)를 생략할 수 있다. 이하, 도 1a에 도시된 센싱 제어 회로(170, 180)에 의해 센싱 전류의 레벨이 조절되는 경우를 설명하기로 한다. 센싱 제어 회로의 센싱 전압 발생 회로(180)에서 출력되는 전압들(V1, V2)의 펄스 레벨은 도 1b의 센싱 제어 회로(190)로부터 출력되는 비트라인 선택 신호들(BSELe, BSEL0)에 동일하게 적용될 수 있다.

[0052] 한편, 프로그램 검증 동작 또는 소거 검증 동작을 위해 비트라인의 전압을 센싱하기 위한 동작에서 센싱 회로(170)의 스위칭 소자(N9)를 통해 흐르는 센싱 전류(Itrip)의 양은 센싱 전압 생성 회로(180)로부터 인가되는 제1 전압(V1)의 레벨 및 제2 전압(V2)의 레벨에 따라 달라지며, 제1 전압(V1)을 인가한 후 제2 전압(V2)이 인가될 때까지의 시간(이하, '이밸류에이션 타임')에 따라 달라질 수도 있다.

[0053] 페이지 버퍼(160)는 센싱 회로(170)를 통해 흐르는 센싱 전류(Itrip)의 양에 따라 메모리 셀의 문턱전압 레벨을 센싱하는 기준이 달라진다. 예를 들어, 센싱 전류(Itrip)의 양이 적으면 페이지 버퍼(160)는 메모리 셀의 문턱전압이 검증 전압보다 높은 것으로 판단하고 메모리 셀의 데이터를 '0'으로 센싱하여 래치부(161)에 저장한다. 반대로, 센싱 전류(Itrip)의 양이 많으면 페이지 버퍼(160)는 메모리 셀의 문턱전압이 검증 전압보다 낮은 것으로 판단하고 메모리 셀에 저장된 데이터를 '1'로 센싱하여 래치부(161)에 저장한다. 따라서, 센싱 제어 회로(170, 180)가 센싱 전류(Itrip) 레벨을 높이면 메모리 셀의 문턱전압이 실제보다 낮게 센싱되고, 센싱 전류(Itrip) 레벨을 낮추면 메모리 셀의 문턱전압이 실제보다 높게 센싱될 수 있다.

[0054] 상기의 구성으로 이루어진 반도체 메모리 장치는 프로그램 동작 및 소거 동작을 반복 실시할수록 스트레스가 누적되어 전기적 특성이 열화된다. 예로써, 스트레스가 누적될수록 프로그램 동작이나 소거 동작을 위해 메모리 셀들로 인가되는 동작 전압의 레벨이 높아지게 되고, 이로 인해 스트레스는 더욱 더 심해진다.

[0055] 따라서, 스트레스를 줄이기 위해서는 메모리 셀들로 인가되는 동작 전압의 레벨을 낮춰야 하는데, 검증 동작에서 센싱 전류의 양을 조절하면 동작 전압의 레벨을 낮추어 스트레스를 줄일 수 있다. 예를 들어, 소거 동작 시 센싱 전류 레벨이 낮을수록 소거 전압은 점점 하향하는 특성을 보인다. 따라서, 소거 검증 동작 시 센싱 전류 레벨을 낮추는 것은 ISPE(Incremental Step Pulse Erase) 방식의 소거 동작에서 처음으로 인가되는 소거 시작 전압을 낮추는데 효과가 있다. 이를 보다 구체적으로 설명하면 다음과 같다.

[0056] 프로그램 동작 및 소거 동작이 반복 실시됨에 BPD 효과의 증가로 인해 소거 검증(Erase Verify)되는 레벨이 점점 낮아진다. 이로 인해, 소거 전압의 레벨은 높아지고 스트레스는 증가하게 된다. ISPE 방식의 소거 동작에서 소거 전압을 인가한 후 소거 검증 동작에서 메모리 셀의 문턱전압이 목표 전압까지 도달하지 않은 경우 정해진 스텝 전압만큼 상승시킨 소거 전압을 인가하여 소거 동작을 다시 실시한다. 이때, 소거 검증 동작 시 센싱 전류

(Itrip)의 레벨이 낮을수록 소거 전압이 상승되는 변동폭(즉, 스텝 전압)을 줄일 수 있으므로, 스트레스를 줄일 수 있다.

[0057] 도 2는 프로그램/소거 동작 실시 횟수의 증가에 의해 발생하는 문턱전압의 변화를 설명하기 위한 그래프이다.

[0058] 도 2를 참조하면, 소거 검증 동작에서 센싱 전류의 레벨이 제1 레벨로 설정된 경우(A)보다 제2 레벨(B)로 설정된 경우 프로그램/소거 동작의 실시횟수가 증가하더라도 문턱전압이 보다 덜 시프트되는 것을 알 수 있다. 따라서, 허용 범위 내에서 센싱 전류의 레벨이 가장 낮은 레벨(C)로 설정하면 문턱전압이 시프트되는 것을 최소화할 수 있다. 즉, 소거 검증 동작에서 센싱 전류의 레벨을 낮추면 메모리 셀에 가해지는 스트레스가 줄어드는 것을 확인할 수 있다.

[0059] 또한, 프로그램 검증 동작과 소거 검증 동작에서 센싱 전류(Itrip)의 레벨을 동일하게 설정하는 것과는 달리, 소거 검증 동작에서 센싱 전류(Itrip)의 레벨을 프로그램 검증 동작에서 센싱 전류(Itrip)의 레벨을 낮게 설정함으로써, 스트레스를 줄일 수 있다.

[0060] 한편, 하나의 메모리 셀에 2비트의 데이터를 저장하는 MLC(Multi Level Chip) 방식의 플래시 메모리 장치의 경우, 저장되는 데이터에 따라 메모리 셀의 문턱전압은 프로그램 동작에 의해 3개의 프로그램 레벨들 중 하나의 프로그램 레벨까지 상승하게 되는데, 문턱전압이 가장 낮은 PV1 레벨까지 상승한 제1 메모리 셀의 경우 인접한 제2 메모리 셀의 문턱전압이 가장 높은 PV3 레벨까지 상승하면, 낮은 트랜스컨덕턴스 효과(Low GM Effect)로 인하여 제1 메모리 셀의 문턱전압이 높아지는 현상이 발생한다.

[0061] 도 3은 메모리 셀들의 문턱전압들을 설명하기 위한 그래프이다.

[0062] 도 3을 참조하면, 메모리 셀의 문턱전압이 PV1 레벨까지 상승한 후, 인접한 메모리 셀의 프로그램 동작에 의해 메모리 셀의 문턱전압이 PV1 레벨에서 보다 더 상승함에 따라, 메모리 셀에서 흐르는 전류의 양이 감소되는 것을 확인할 수 있다. 이로 인해, 메모리 셀에 저장된 데이터를 독출하기 위한 리드 동작에서 메모리 셀의 문턱전압이 높게 센싱되어 다른 데이터가 독출되는 오류가 발생될 수 있다. 이러한 현상은 스트레스가 누적될수록 더욱 심하게 발생하게 된다.

[0063] 한편, 프로그램 검증 동작에서 센싱 전류(Itrip)의 레벨이 높을수록 실제로 메모리 셀의 플로팅 게이트로 주입되는 전자의 개수는 증가하고, 메모리 셀의 터널 산화막에 가해지는 스트레스는 증가한다. 따라서, MLC 방식의 플래시 메모리 장치의 경우, 각각의 프로그램 레벨별로 센싱 전류(Itrip)의 레벨을 다르게 설정함으로 스트레스에 의한 전기적 특성 변화를 개선할 수 있다.

[0064] 예를 들어, 문턱전압을 PV1 레벨까지 상승시키기 위하여 프로그램 동작을 실시한 후 프로그램 검증 동작을 실시할 때 센싱 전류의 레벨을 높게 설정하여 낮은 트랜스컨덕턴스 효과(Low GM Effect)를 최소화한다.

[0065] 전체적으로, 소거 검증 동작 시 센싱 전류의 레벨을 가장 낮은 제1 레벨로 설정하고, 문턱전압을 PV1레벨까지 상승시키기 위한 메모리 셀의 검증 동작 시 센싱 전류의 레벨을 제1 레벨보다 높은 제2 레벨로 설정하고, 문턱전압을 PV1 레벨보다 높은 PV2레벨까지 상승시키기 위한 메모리 셀의 검증 동작 시 센싱 전류의 레벨을 제2 레벨보다 높은 제3 레벨로 설정하고, 문턱전압을 PV2레벨보다 높은 PV3레벨까지 상승시키기 위한 메모리 셀의 검증 동작 시 센싱 전류의 레벨을 제3 레벨보다 높은 제4 레벨로 설정한다. 즉, 검증 동작에서 센싱하려는 메모리 셀의 문턱전압 레벨에 비례하여 센싱 전류의 레벨을 설정한다.

[0066] 상기와 같이 센싱 전류의 레벨을 설정하기 위한 회로들의 동작을 설명하면 다음과 같다.

[0067] 도 1을 참조하면, 메모리 셀들의 소거 동작 또는 프로그램 동작이 실시된 후 제어 회로(120)에서 출력되는 센싱 제어 신호(SG SIGNAL)에 응답하여 센싱 전압 발생 회로(180)는 제1 전압(V1)을 출력한다. 센싱 전압 발생 회로(180)의 제1 전압(V1)에 응답하여 센싱 회로(170)는 페이지 버퍼(160)로부터 출력되는 프리차지 전압을 비트라인(BLe)으로 전달한다. 이로 인해, 비트라인(BLe)은 V1-Vth(Vth: 스위칭 소자(N9)의 문턱전압)에 해당하는 레벨까지 프리차지된다. 이어서, 제1 전압(V1)의 공급을 중단하고, 이벨류에이션 타임 동안 검증 동작에 필요한 전압들이 워드라인들(WL0 내지 WLn)에 인가되면, 검증 전압(Vvp)과 선택된 메모리 셀의 문턱전압에 따라 비트라인(BLe)의 전압이 변한다. 즉, 선택된 메모리 셀의 문턱전압이 검증 전압(Vvp)보다 높으면 비트라인(BLe)의 전압은 변하지 않고, 검증 전압(Vvp)보다 낮으면 비트라인(BLe)의 전압은 낮아진다. 이후, 워드라인들(WL0 내지 WLn)에 인가된 전압들의 공급을 중단한다.

[0068] 센싱 전압 생성 회로(180)는 선택된 메모리 셀의 문턱전압 레벨에 따라 페이지 버퍼(160)가 메모리 셀에 저장된 데이터를 검증할 수 있도록 제2 전압(V2)을 출력한다. 제2 전압(V2)에 응답하여 센싱 회로(170)는 비트라인

(BLe)의 프리차지 전압이나 변경된 전압에 따라 센싱 전류(Itrip)가 페이지 버퍼(160)로 공급될 수 있도록 비트라인(BLe)과 페이지 버퍼(160)를 연결한다. 센싱 회로(170)는 제2 전압(V2)에 따라 센싱 전류(Itrip)의 레벨을 조절할 수 있다. 구체적으로 설명하면 다음과 같다.

[0069] 센싱 전압 발생 회로(180)는 소거 동작을 실시한 후 메모리 셀의 문턱전압 레벨을 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 문턱전압 레벨을 검증할 때 제2 전압(V2)을 보다 더 높게 출력한다. 이러한 제2 전압(V2)에 응답하여 센싱 회로(170)는 소거 동작을 실시한 후 메모리 셀의 문턱전압 레벨을 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 문턱전압을 검증할 때 센싱 전류(Itrip)의 레벨이 높아지게 한다. 다시 말해, 메모리 셀의 문턱전압이 소거 동작에 의해 낮아진 경우 센싱 제어 회로(170, 180)가 센싱 전류(Itrip)의 레벨을 제1 레벨로 설정하고, 문턱전압이 프로그램 동작에 의해 높아진 경우 센싱 제어 회로(170, 180)가 센싱 전류(Itrip)의 레벨을 제1 레벨보다 높은 레벨로 설정한다.

[0070] 만일, 프로그램 동작에 의해 메모리 셀들의 문턱전압들이 서로 다른 레벨들로 각각 높아진 경우, 센싱 제어 회로(170, 180)는 문턱전압이 높을수록 센싱 전류(Itrip)의 레벨을 높게 설정한다. 예를 들어, 메모리 셀의 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 센싱 제어 회로(170, 180)가 센싱 전류(Itrip)의 레벨을 제1 레벨보다 높은 제2 레벨로 설정한다. 메모리 셀의 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 센싱 제어 회로(170, 180)가 센싱 전류(Itrip)의 레벨을 제2 레벨보다 높은 제3 레벨로 설정한다. 메모리 셀의 문턱전압 레벨이 프로그램 동작에 의해 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 센싱 제어 회로(170, 180)가 센싱 전류(Itrip)의 레벨을 제3 레벨보다 높은 제4 레벨로 설정한다.

[0071] 상기와 같이 센싱 전류(Itrip)의 레벨을 설정하기 위하여, 센싱 전압 발생 회로(180)는 소거 동작을 실시한 후 메모리 셀의 데이터를 검증할 때보다 프로그램 동작을 실시한 후 메모리 셀의 데이터를 검증할 때 제2 전압(V2)의 레벨을 높게 출력한다. 즉, 센싱하려는 메모리 셀의 문턱전압 레벨에 비례하여 제2 전압(V2)의 레벨을 상승시킨다.

[0072] 예를 들어, 메모리 셀의 문턱전압 레벨이 소거 동작에 의해 낮아진 경우, 센싱 전압 발생 회로(180)가 제1 센싱 레벨의 상기 제2 전압(V2)을 출력하고, 문턱전압 레벨이 프로그램 동작에 의해 PV1 레벨까지 상승하는 경우 센싱 전압 발생 회로(180)가 제1 센싱 레벨보다 높은 제2 센싱 레벨의 제2 전압(V2)의 레벨을 출력하고, 문턱전압 레벨이 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 센싱 전압 발생 회로(180)가 제2 센싱 레벨보다 높은 제3 센싱 레벨의 제2 전압(V2)을 출력하고, 문턱전압 레벨이 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 센싱 전압 발생 회로(180)가 제3 센싱 레벨보다 높은 제4 센싱 레벨의 제2 전압(V2)을 출력한다.

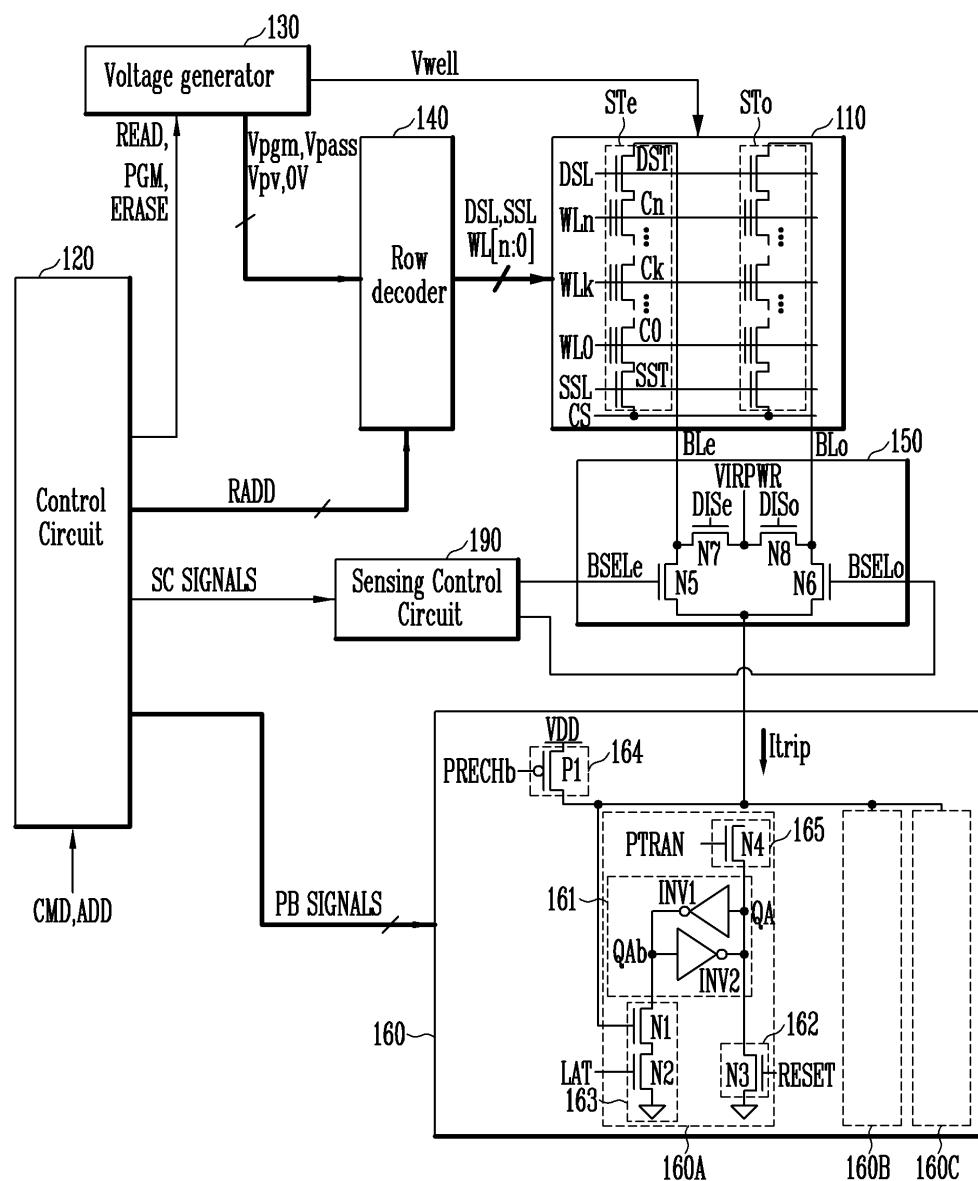

[0073] 도 4는 메모리 셀의 문턱전압 레벨에 따라 변경되는 센싱 전류의 레벨을 설명하기 위한 도면이다.

[0074] 도 4를 참조하면, 센싱 전압 발생 회로(180)에서 출력되는 제2 전압(V2)의 레벨이 앞서 설명한 것처럼 변함에 따라 센싱 회로(170)에 의해 비트라인(BLe)과 페이지 버퍼(160)의 연결 저항값이 달라지고, 그 결과 센싱 전류(Itrip)의 레벨이 변경된다.

[0075] 이렇듯, 메모리 셀의 데이터를 검증하기 위해 비트라인으로부터 페이지 버퍼로 공급되는 센싱 전류의 레벨을 프로그램 동작 또는 소거 동작에 의해 변경된 메모리 셀의 상기 문턱전압 레벨에 따라 조절함으로써, 프로그램 동작과 소거 동작의 반복 실시에 의해 메모리 장치의 물리적/전기적 특성이 저하되는 것과 스트레스 발생을 최소화할 수 있다.

[0076] 상기에서는 제2 전압(V2)의 레벨을 조절하여 센싱 전류(Itrip)의 레벨을 조절하는 방법을 설명하였으나, 비트라인을 프리차지하기 동작에서 출력되는 제1 전압(V1)의 레벨을 조절하여 센싱 전류(Itrip)의 레벨을 조절할 수도 있다. 예를 들어, 제1 전압(V1)의 레벨이 높아지면 비트라인에 프리차지되는 전압이 높아지므로, 제2 전압(V2)이 센싱 회로(170)로 인가될 때 센싱 전류(Itrip)의 레벨이 높아지게 된다. 따라서, 제1 전압(V1)과 같이 센싱하려는 메모리 셀의 문턱전압 레벨에 비례하여 제2 전압(V2)의 레벨을 상승시키면, 센싱 전류의 레벨을 센싱하려는 메모리 셀의 문턱전압 레벨에 증가시킬 수 있다.

[0077] 또한, 제1 전압(V1)이 인가된 후 제2 전압(V2)될 때까지의 이벨류에이션 타임을 조절하여 센싱 전류(Itrip)의 레벨을 조절할 수도 있다. 예를 들어, 이벨류에이션 타임이 증가하면 센싱 전류(Itrip)의 레벨이 낮아지고, 이벨류에이션 타임이 감소하면 센싱 전류(Itrip)의 레벨이 높아진다. 따라서, 센싱하려는 메모리 셀의 문턱전압 레벨에 반비례하여 이벨류에이션 타임을 조절하면, 센싱 전류의 레벨을 센싱하려는 메모리 셀의 문턱전압 레벨에 비례하여 증가시킬 수 있다.

[0078] 예를 들어, 메모리 셀의 문턱전압 레벨이 소거 동작에 의해 낮아진 경우, 이밸류에이션 타임이 제1 값으로 설정되고, 프로그램 동작에 의해 메모리 셀의 문턱전압 레벨이 PV1 레벨까지 상승하는 경우 센싱 전류의 레벨이 제1 레벨보다 높은 제2 레벨로 설정되고, 프로그램 동작에 의해 문턱전압 레벨이 PV1 레벨보다 높은 PV2 레벨까지 상승하는 경우 센싱 제어 회로가 센싱 전류의 레벨을 제2 레벨보다 높은 제3 레벨로 설정하고, 프로그램 동작에 의해 문턱전압 레벨이 PV2 레벨보다 높은 PV3 레벨까지 상승하는 경우 센싱 제어 회로가 센싱 전류의 레벨을 제3 레벨보다 높은 제4 레벨로 설정할 수 있다.

[0079] 뿐만 아니라, 상기의 방법들을 모두 적용하거나 선택적으로 적용하여 센싱 전류의 레벨을 조절할 수 있음은 당업자에게 자명하다.

### 부호의 설명

|                          |                   |

|--------------------------|-------------------|

| [0080] 110 : 메모리 어레이     | 120 : 제어 회로       |

| 130 : 전압 생성 회로           | 140 : 로우 디코더      |

| 150 : 비트라인 선택 회로         | 160 : 페이지 버퍼      |

| 160A, 160B, 160C : 래치 회로 | 161 : 래치부         |

| 162 : 리셋 회로              | 163 : 래치 제어 회로    |

| 164 : 프리차지 회로            | 165 : 전송 회로       |

| 170 : 센싱 회로              | 180 : 센싱 전압 생성 회로 |

| 190 : 센싱 제어 회로           |                   |

도면

도면1a

도면 1b

도면2

도면3

도면4