(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3863921号 (P3863921)

(45) 発行日 平成18年12月27日(2006.12.27)

(24) 登録日 平成18年10月6日 (2006.10.6)

(51) Int.C1.

FI

G 1 1 C 16/04 (2006.01)

G11C 17/00 621B

請求項の数 20 (全 18 頁)

(21) 出願番号 特願平6-182733

(22) 出願日 平成6年6月30日 (1994.6.30)

(65) 公開番号 特開平7-307097

(43) 公開日 平成7年11月21日 (1995.11.21) 審査請求日 平成13年6月11日 (2001.6.11)

(31) 優先権主張番号 085427

(32) 優先日 平成5年10月4日(1993.10.4)

(33) 優先権主張国 米国(US)

前置審查

|(73)特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテツド

アメリカ合衆国テキサス州ダラス, ノース セントラルエクスプレスウエイ 135

00

(74)代理人 100066692

弁理士 浅村 皓

|(74)代理人 100072040

弁理士 浅村 肇

(74)代理人 100094673

弁理士 林 鉐三

(74)代理人 100091339

弁理士 清水 邦明

最終頁に続く

(54) 【発明の名称】フローティングゲートメモリのプログラミング方法

# (57)【特許請求の範囲】

#### 【請求項1】

基準電圧に接続された基板を有する不揮発性集積回路メモリ内の複数のフローティング ゲートメモリセルのうち少なくとも1つの閾値電圧を増加させる方法であって、

前記メモリセルの夫々は単一トランジスタ、非分割ゲートタイプであり、

該方法は、

前記複数のメモリセル制御ゲートの電圧を前記基準電圧に対して正の値を有するようにし、

前記複数のメモリセルのソースの電圧を前記基準電圧に対して正の値を有するようにし

前記複数のメモリセルのドレーンの電圧を前記基準電圧に対して正の値を有するように

前記複数のメモリセルのドレーンとソースとの間に電流を流すようにする、 ことからなり、

制御ゲートの前記電圧は読み出しモード時の制御ゲートの読み出し電圧よりも小さく、前記複数のメモリセルのドレーンの前記電圧は前記複数のメモリセルのソースの前記電圧よりも大きく、制御ゲートの前記電圧は前記ソースの前記電圧を有する前記複数のメモリセルの代表的な閾値電圧よりも小さい値を有する、

方法。

【請求項2】

20

請求項1記載の方法において、前記ソースの前記正の電圧は前記ソースと前記基準電圧との間に少なくとも1つのダイオード接続された電界効果トランジスタに接続して得られる、方法。

# 【請求項3】

請求項1記載の方法において、前記ソースの前記正の電圧は前記メモリセルの前記制御ゲートに帰還増幅器により接続される、方法。

## 【請求項4】

請求項1記載の方法において、前記制御ゲートの前記電圧は最適なゲート電流注入効率を与えるように調整される、方法。

#### 【請求項5】

請求項1記載の方法において、前記制御ゲートの前記電圧は傾斜している、方法。

#### 【請求項6】

請求項1記載の方法において、前記ソースの前記正の電圧は前記ソースと前記基準電圧との間に接続された抵抗を流れる電流により得られる、方法。

## 【請求項7】

請求項1記載の方法において、前記複数のメモリセルは一列のメモリセルである、方法

### 【請求項8】

請求項1記載の方法において、前記複数のメモリセルは一行のメモリセルである、方法

#### 【請求項9】

請求項1記載の方法において、前記複数のメモリセルは前記メモリ内の全ての前記メモリセルである、方法。

#### 【請求項10】

請求項1記載の方法において、前記複数のメモリセルの夫々は並列に接続され、前記ソースの前記電圧は前記ソースから電流が流れることにより正の値を有するようにされ、前記電流は前記ドレーンに接続された電圧源により前記メモリセルの前記ドレーンに流入するようにされ、全てが約1秒の期間である、方法。

# 【請求項11】

請求項1記載の方法において、前記メモリはグランド電圧をさらに有し、前記基準電圧 はグランド電圧である、方法。

# 【請求項12】

基板を有する不揮発性集積回路メモリ内の複数のフローティングゲートメモリセルのうち少なくとも 1 つの閾値電圧を増加させる方法であって、前記メモリセルは単一トランジスタ、非分割ゲートタイプであり、該方法は、

前記メモリセルの制御ゲートの電圧が前記基板の電圧に対して正の値を有するようにし

前記メモリセルのソースを前記基板に対して逆バイアスし、

前記メモリセルのドレーンを前記基板に対して逆バイアスし、

前記複数のセルのうちの少なくともいくつかの前記ドレーンと前記ソースとの間に電流 40 が流れるようにし、

制御ゲートの前記電圧は読み出しモード時の制御ゲートの読み出し電圧よりも小さく、前記ドレーンと前記基板の間の逆バイアスが前記ソースと前記基板の間の逆バイアスよりも大きく、制御ゲートの前記電圧は逆バイアスされた前記ソースを有する前記複数のメモリセルの代表的な閾値電圧よりも小さい値を有する、

# 方法。

#### 【請求項13】

請求項12記載の方法において、前記ソースは前記ソースに直列に接続されたダイオー ド接続された電界効果トランジスタにより前記基板に対して逆バイアスされる、方法。

## 【請求項14】

10

20

30

40

50

請求項12記載の方法において、前記ソースの電圧は前記メモリセルの前記制御ゲートに帰還増幅器により接続される、方法。

### 【請求項15】

請求項12記載の方法において、前記ソースと前記基板との間に接続された抵抗を流れる電流により前記ソースが前記基板に対して逆バイアスされる、方法。

#### 【請求項16】

請求項12記載の方法において、前記複数のメモリセルは一列のメモリセルである、方法。

#### 【請求項17】

請求項12記載の方法において、前記複数のメモリセルは一行のメモリセルである、方 10 法。

#### 【請求項18】

請求項12記載の方法において、前記複数のメモリセルは前記メモリ内の全ての前記メモリセルである、方法。

#### 【請求項19】

請求項12記載の方法において、前記制御ゲートの前記電圧は傾斜している、方法。

## 【請求項20】

請求項1記載の方法において、消去後の閾値の分布を狭めるために、複数のフローティングゲートメモリセルの少なくとも1つに対する消去処理の後において、複数のフローティングゲートメモリセルのうち少なくとも1つの閾値電圧を増加させる、方法。

#### 【発明の詳細な説明】

### [0001]

## 【産業上の利用分野】

本発明は電気的に消去可能で、電気的にプログラム可能な読取専用メモリ(EEPROM)アレイのような非揮発性、集積回路メモリアレイに関する。特に本発明はフローティングゲートメモリアレイのプログラミング方法に関する。

# [0002]

#### 【従来の技術】

ファウラーノルドハイムのトンネルプログラミングと対照的に、ホットキャリア注入を使用したEEPROMが、(a)、IEDM 1985年(第616~619頁)のMukherjee等の論文 "シングルトランジスタEEPROMセルおよびその512 К С MOS EEPROMにおける実施"および、(b)、ISSCC 1989年(第140~141頁)のV.Kynett等の論文 "90 nS 100 K イレーズ / プログラムサイクルメガビットフラッシュメモリ"に記載されている。(a)の中心問題は米国特許第4,698,787号でも検討されている。

# [0003]

従来技術を使用したホットキャリア注入プログラミング方法では、基板電圧( $V_s_s_s$ 、恐らくは 0 V)に等しい基準電圧がプログラムされるセルのソースへ印加され、恐らくは 6  $V_s_s_s$  0 である第 1 の正電圧  $V_d_s_s$  0 がドレーンに印加され、恐らくは 1 2  $V_s_s_s$  0 正電圧が制御ゲートに印加される。このような状況の元では、ソースおよびドレーン間のチャネルは高導電性であり、ドレーン拡散接合が基板(チャネル)に対して逆バイアスされソース拡散接合は逆バイアスされない。ドレーン拡散に到達する電子には 2 つの電界が印加され、一方は逆バイアスドレーン拡散に関連しており他方は制御ゲートからフローティングゲートへ接続される正電圧に関連している。電界により電子(ホットキャリア)がフローティングゲートへ注入される。

# [0004]

#### 【発明が解決しようとする課題】

フラッシュEEPROMに生じる一つの問題はセルのオーバーイレーズである。オーバーイレーズされたセルは正電荷を有し、フローティングゲートの下のチャネルが導通する。オーバーイレーズされた導電性セルにより並列接続セルのカラム内の他のセルが短絡され

30

40

50

る。オーバーイレーズを補償する一つの方法はスプリットゲートを有するフラッシュEE PROMを形成することである。もう一つの方法は全EEPROMセルをプログラミング し、光消去パルスを段階的に印加し、各ステップの後で全セルが消去されているかどうか を調べることである。他の方法としては、例えば1992年7月21日発行の米国特許第5,132,935号および1992年8月16日発行の米国特許第5,122,985号およびその中の参照事項に記載されているプログラミングおよび消去ステップの交番実施が含まれる。両特許共フラッシュ消去されたセルの閾値電圧分布を圧縮すなわち狭くすることに関連しており、両特許共テキサスインスツルメンツ社が譲り受けている。

[0005]

従来技術のフラッシュEEPROMに付随する一つの問題点はフラッシュ消去操作後の閾値電圧の分布が広くなることである。これは一部ゲート絶縁膜内に捕捉されたホールもしくはフローティングゲートへのホットホールの注入による。

[0006]

フラッシュ消去手順実施後の閾値電圧分布は狭いことが望ましい。消去された閾値電圧分布を狭くするには、前記したようにフラッシュ消去法は最終消去ステップの前に少くとも 一つのフラッシュプログラミングステップを設けて最終的な狭い消去閾値電圧分布に到達 する必要がある。

[0007]

プログラムされた閾値電圧の分布を狭くする、すなわち "圧縮"するための方法が少くとも2つ提案されている。一般的にこれらの方法はいずれも閾値電圧の低いセルの閾値電圧を高めることができる。一つの方法ではワード線ストレスを使用してフローティングゲートへ電子のファウラーノルドハイム注入を行っている。この方法の利点はビット線リーク電流の制約を受けないことである。しかしながら、この方法では通常のプログラミング電圧よりも高いゲート電圧が必要である。ゲート電圧を高くするには、誘電体素子内の電界を低下させるか誘電体素子を強化するための特殊な製造ステップが必要となる。

[0008]

第2の方法はゲートへホットエレクトロンを注入することである。この方法はIEDM 1991年(第11、4、1~11、1、4頁)のヤマダ等の論文 "簡単なスタックゲートフラッシュEEPROMの自己集束消去法"に記載されている。第2の方法では、ビット線が6~7Vの電圧でバイアスされソースは接地され(基板電圧、すなわち0V)低電圧(0~2V)が制御ゲートに印加される。この方法で必要な電圧は充分回路の能力以内の電圧であるが、この第2の方法の欠点は大きなチャネル電流を必要とすることである。すなわち、いくつかのディプレートされたセルがドレーン・カラム線に接続されると、ドレーン・カラム線が過負荷となりプログラミング能力が低下する。ドレーン・カラム線リークが大き過ぎると、ドレーン・カラム電圧が崩壊して圧縮手順は失敗する。また、(ソースを接地させた)この第2の方法を使用すると、ゲートにホットホールが注入されてドレーン・カラム線リークが増大し圧縮の目的が挫折してしまうことがある。

[0009]

ソースを基板に対して正電圧でバイアスしてチャネルホット電子を使用してEPROMを プログラミングする方法が1993年6月8日発行の米国特許第5,218,571号に 記載されている。この特許に記載された方法では、制御ゲートはEPROMセルの閾値電 圧以上の電圧でバイアスされる。

[0010]

【課題を解決するための手段】

メモリセルのフラッシュプログラミングに使用すると、本発明の効率的で許容度の高い圧縮法により比較的狭い閾値電圧分布が得られる。接地ソースを使用する従来のプログラミング法の問題点であるドレーン・カラム線ローディング効果が本方法により解消される。さらに、本発明の方法ではワード線に高電圧を印加する必要がないため、"ワード線ストレス法"の制約が克服される。事実、ここで説明する方法で必要な電圧および電流は周知のチップ製造技術の充分能力以内であり、しかもワード線に接続された非選定セルが不注

意によりプログラムされる可能性が低下される。

[0011]

本発明の方法ではプログラムされるセルのソース・基板接合を逆バイアスすることにより 圧縮ゲート電流効率が向上する。逆バイアスは、例えば、ソースへバイアス電圧を印加す るかもしくはソースおよび基地(大地)間に抵抗や他のインピーダンスを配置して行われ る。逆バイアスによりフラッシュプログラミング圧縮ステップ中にプログラムされる個別 セルおよびアレイ全体のチャネル電流が制限される。

[0012]

従来の圧縮方法に較べれば、本方法では従来の解決方法の100倍を越えるゲート電流圧縮が行われる。さらに、本方法では圧縮工程に対するホットホール注入の望ましくない影響が低減される。

[0013]

さらに、本発明の方法によりアレイリークに対するマージンが増大する。

[0014]

前の圧縮消去ステップ中に何らかの理由によりセルのフローティングゲートの電荷が消失 しても、そのセルの電圧閾値は本方法により回復される。

[0015]

【実施例】

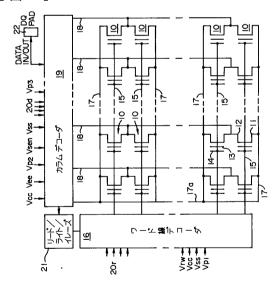

本発明の方法の使用について説明するために、メモリチップの一体部であるメモリセルアレイの一例を図1に示す。各セルはソース11、ドレーン12、フローティングゲート13、制御ゲート14を有するフローティングゲートトランジスタ10である。一行のセル10内の各制御ゲート14はワード線15に接続され、各ワード線15はワード線デコーダ16に接続されている。一行のセル10内の各ソース11はソース線17に接続されている。一列のセル10内の各ドレーン12はドレーン・カラム線18に接続されている。各ソース線17はコモン・カラム線17aを介してカラムデコーダ19に接続されるドレーン・カラム線18はカラムデコーダ19に接続されている。

[0016]

リードモードにおいて、ワード線デコーダ16は線20rを介したワード線アドレス信号 およびマイクロプロセッサ21からの信号に応答して予め選定された正電圧 $V_{cc}$ (およそ+5V)をセレクトされたワード線15へ印加し、低電圧(大地すなわち $V_{ss}$ )をディセレクトされたワード線15へ印加するように機能する。カラムデコーダ19は予め選定された正電圧 $V_{sen}$ (およそ+1V)を少くともセレクトされたドレーン・カラム線18に印加し低電圧(0V)をソース線17に印加するように機能する。カラムデコーダ19はまたアドレス線20dを介した信号に応答してセレクトされたセル10のセレクトされたドレーン・カラム線18およびセレクトされたワード線15に接続されているセル10の導通もしくは非導通状態はDATA IN/OUT端子22に接続された(図示せぬ)センスアンプにより検出される。

[0017]

フラッシュイレーズモード中に、カラムデコーダ19は全てのドレーン・カラム線18をフローティング("オフ"状態にバイアスされた電界効果型トランジスタ等の高インピーダンスに接続)するように機能することができる。ワード線デコーダ16は大地とすることができる基準電位に全てのワード線15を接続するように機能する。カラムデコーダ19はまた全てのソース線17に高い正電圧Vee(およそ+10V~+15V)を印加するように機能する。これらの消去電圧によりフローティングゲート13から電荷を転送するファウラーノルドハイムトンネル電流を発生するのに充分な電界強度がゲート酸化膜領域の両端間に生じてメモリセル10が消去される。ワード線15の電位が0Vであるため、消去中にセル10は非導通状態にとどまる。これとドレーン12がフロートしているという理由により、チャネルホットキャリアが発生する。

[0018]

50

40

10

20

従来のライトもしくはプログラムモードでは、ワード線デコーダ16は線20rを介した ワード線アドレス信号およびリード/ライト/イレーズ制御回路21(すなわちマイクロ プロセッサ21)からの信号に応答してセレクトされた制御ゲート14を含むセレクトさ れたワード線15に予め選定された第1のプログラミング電圧V。1(およそ+12V) を印加するように機能することができる。カラムデコーダ19はまたセレクトされたドレ ーン・カラム線18、したがってセレクトされたセル10のドレーン12、へ第2のプロ グラミング電圧V。2(およそ+5~+10V)を印加するように機能する。従来の方法 では、ソース線17は大地とすることができる基準電圧V、、に接続される。ディセレク トされたドレーン・カラム線18は全て基準電圧V。。に接続されるかもしくはフロート される。これらのプログラミング電圧によりセレクトされたメモリセル10のチャネル内 に高電流(ドレーン12からソース11)状態が生じ、ドレーン・チャネル接合付近にチ ャネルホット電子およひアバランシェ降伏電子が発生してチャネル酸化膜を横切してセレ クトされたセル10のフローティングゲート13へ注入される。プログラミング時間は( V。 1 が 0 Vである)チャネル領域に対しておよそ - 2 V~ - 6 Vの負のプログラム電荷 によりフローティングゲート13をプログラムするのに充分な長さに選定される。実施例 に従って製造されたメモリセル10については、制御ゲート14/ワード線15とフロー ティングゲート13間の結合効率はおよそ0.6である。したがって、セレクトされた制 御ゲート14を含むセレクトされたワード線15上の、例えば、12Vの従来のプログラ ミング電圧 V。 1 によりセレクトされたフローティングゲート 1 3 にはおよそ + 7 . 2 V の電圧が印加される。フローティングゲート13(およそ+7.2V)と接地された(お よそ0V)ソース線17間の電圧差はファウラーノルドハイムトンネル電流をソース11 とフローティングゲート13間のゲート酸化膜を横切してセレクトもしくはディセレクト されたセル10のフローティングゲート13をチャージさせるのに不充分である。セレク トされたセル 1 0 のフローティングゲート 1 3 はプログラミング中に注入されるホットエ レクトロンによりチャージされ、次にエレクトロンによりセレクトされたセル10のフロ ーティングゲート13の下のソース・ドレーンパスが非導通とされ、"ゼロ"ビットとし て読み出される状態となる。ディセレクトされたセル10のフローティングゲート13の 下のソース・ドレーンパスは導通したままであり、これらのセル10は"1"ビットとし て読み出される。

[0019]

ードでは、ワード線デコーダ16は線20rを介したアドレス信号およびリード/ライト / イレーズ制御回路 2 1 (すなわちマイクロプロセッサ 2 1 )からの信号に応答して予め 選定された第1のプログラミング電圧V。1(およそ+1V~+4V)を全てのワード線 15に印加するように機能する。カラムデコーダ19はまた第2のプログラミング電圧V 。2(およそ+6V~+7V)を全てのドレーン・カラム線18に印加するように機能す る。全てのソース線17が第3のプログラミング電圧V。3(およそ+1V~+2V)ま で高められる。これらのプログラミング電圧によりセレクトされたメモリセル10のチャ ネル内に比較的低い電流(ドレーン12からソース11)状態が生成され、チャネルホッ トエレクトロンおよびアバランシュ降伏電子が発生されてチャネル酸化膜を横切してセル 10のフローティングゲート13へ注入される。プログラミング時間は全てのフローティ ングゲート13から任意の正電荷を除去して閾値電圧Vょ分布を圧縮するのに充分な長さ に選定される。この時間は1秒程度の長さであり、チャージ電流が非常に小さいため従来 の方法より遥かに長い。しかしながら、この時間中にアレイ全体がプログラムされる。も ちろん、プログラミング電圧V。1が小さいため充分なファウラーノルドハイムトンネル 電流がソース11およびフローティングゲート13間のゲート酸化膜を横切してセル10 のフローティングゲート13をチャージすることはない。しかしながら、セル10のフロ

ーティングゲート13はプログラミング中に注入されるホットエレクトロンによりチャー

本発明による(従来のフラッシュイレーズサイクルに続く)フラッシュプログラム圧縮モ

ジされる。 【0020】

20

30

本発明のフラッシュプログラム法は消去する前に全セル10をプログラムしたり、1個のセルあるいは1行もしくは1列のセルをプログラムするのに使用され、プログラムされたセルのゲート電圧が前記した + 1  $\vee$  2 + 4  $\vee$  7 ではなく恐らくは + 1 0  $\vee$  0 の第1のプログラミング電圧  $\vee$  2 1 へ傾斜する点を除けば前記した圧縮方法と同じである。任意の正電荷を単に移動しかつ / もしくは電圧閾値  $\vee$  4 を圧縮するのではなく、フローティングゲートがチャネル領域に対しておよそ + 2  $\vee$  2  $\vee$  4 + 6  $\vee$  0 りのりのプログラム電荷によりプログラムされる。ここでも、所要時間長はチャージ電流が非常に低いために従来の方法に較べて遥かに長くなる。しかしながら、全チッププログラミング時間は比較できる長さとなる。

## [0021]

便宜上、リード、ライトおよびイレーズ電圧を表1に示す。

# 【表1】

| 表 1                        |                 |            |              |                       |            |

|----------------------------|-----------------|------------|--------------|-----------------------|------------|

|                            | リード             | <u>ライト</u> | 万分泊者去        | フラッシュプログラム            | 7579270774 |

| セレクトされた<br>ワード線            | 5 <b>Y</b>      | 12V        | OV (A11)     | 10V (A11)<br>(ramped) | 1-4V (A11) |

| ディセレクトされた<br>ワード線          | OV              | Vo         |              |                       |            |

| セレクトされた<br>ドレーン線           | 1. OV           | 5-10V      | Float (All)  | 5-10V(A11)            | 6-7V (A11) |

| ディセレクトされた<br>ドレーン <b>線</b> | <b>0V/</b> 7□-∤ | 0V/70-}    |              |                       |            |

| ソース線                       | OV              | οV         | 10-15V(Al 1) | 1-2V (A11)            | 1-2V (A11) |

30

10

20

## [0022]

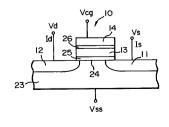

図1のメモリセルアレイで使用されるタイプの代表的なフローティングゲートセル10の断面を図2に示す。ソース11およびドレーン12拡散とは反対種別の不純物を有する半導体基板23内で不純物拡散を行ってソース11およびドレーン12が形成される。代表的にソース11は2種の不純物の拡散により形成される。ソース11とドレーン12間の基板23領域はセルチャネル24となる。フローティングゲート13はゲート絶縁膜25によりチャネル24から絶縁されたポリシリコン層により形成される。図1のワード線15の一部であるポリシリコン制御ゲート14は層間絶縁膜26によりフローティングゲート13から絶縁される。

## [0023]

本発明は数千の不完全なメモリセル10のテスト構造に対する実験データを参照して説明すると良く理解できる。一種のテスト構造はポリシリコンフローティングゲート13層の形成後ポリシリコン制御ゲート14層を形成する前の時点でフローティグゲートメモリセル10の製造工程が停止される点を除けば実際のセルアレイ10と同様である。ソース11およびドレーン12拡散は完全なセル10のアレイを形成するのに使用されるのと同じ手順を使用して形成される。テスト構造の不完全メモリセル10は等価フローティングゲート13に対する拡張されたポリシリコン電極を含み、フローティグゲート13ポリシリコンへのプローブアクセスが得られる。フローティングゲート13ポリシリコンへのプローブアクセスが得られる。フローティングゲート13へ流れる注入電流1gを測定するのに使用される。

30

40

50

### [0024]

第2のタイプのテスト構造はフローティングゲート13およびそれとは層間絶縁膜26により絶縁された制御ゲート14のあるセル10を有している。プログラミングは制御ゲート14ポリシリコン、ソース11導体、およびドレーン12導体に接続されたプロープへ電圧を印加して行われる。

### [0025]

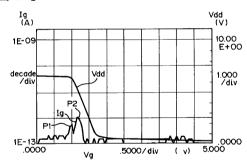

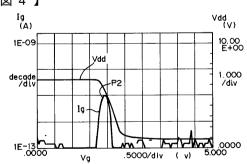

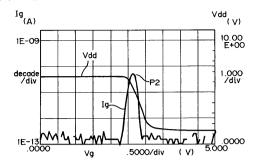

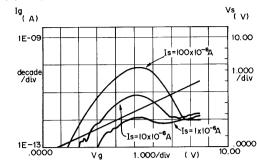

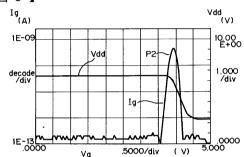

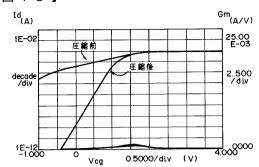

図3~図6にゲート電流Ⅰ。に対するソースバイアスの影響を示す。図3~図6のデータ は第1種別のテスト構造のドレーンを400 の抵抗を介して基板に対して+6.5Vの 電圧に接続して得たものである。フローティングゲート電圧V。はゲート電流I。の絶対 値を監視しながらソースバイアスをパラメータとして0V~+5Vまで傾斜している。V а d はデバイス 1 0 のドレーン 1 2 の電圧である。図 3 はソースを基板 2 3 に接地した場 合の従来の値を示す。左側の小さなピークP1はホール注入電流の絶対値に対応し、実際 の電流は負である。このピークP1は望ましくない電流成分を表わしており、それはセル 10の閾値V,をさらに低下することにより圧縮を行う目的がこの成分により挫折してし まうためである。図3のピークP2は望ましくない電子流を表わしている。図4~図6に 示すように、ソース・基板接合の逆バイアスによりゲート電流 Ig は著しく増加する(1) 00倍以上)。ゲート電流にはピークP2は一つしかない。このピークP2は電子流(所 望する電流成分)に対応し、ホール電流が存在しても圧縮に関しては意味がない。ボディ 効果により、ソースバイアス電圧を高くするとピーク電子注入電流が発生するゲートバイ アスが高くなる。実際には、使用する全電圧がチップレベルで利用できるバイアスの範囲 内であるためこれは重要ではない。本発明の方法を使用すれば、チャネル電流Ⅰ』したが って消費電力を増大することなくゲート電流Ⅰgが増加される(効率が向上する)。

# [0026]

およそ10,000セルを有する第1種別のテスト構造に対する総等価フローティングゲート電流  $I_g$  の変動を図7に示す。基板23を0Vとしドレーン12をおよそ+6.8Vとして、1 $\mu$  A、10 $\mu$  A および100 $\mu$  A の定電流  $I_s$  が共通ソース11に印加される。各定ソース電流  $I_s$  に対してゲート電圧  $V_g$  は0Vからおよそ+8.5Vまで変動し、各定ソース電流  $I_s$  に対する等価フローティングゲート・電極電流  $I_g$  が測定される。もちろん、このような小さい注入電流値を使用するにはバイアス条件を長時間適用して非揮発性メモリセルのフローティングゲートをプログラムしなければならない。図7には  $V_g$  が変化する時のソース電圧  $V_s$  も示されており  $I_s$  の全ての値に対して実際上同じである。これらのデータはゲート電流  $I_g$  がチャネル電流  $I_g$  に比例することを示している。

#### [0027]

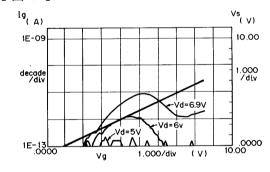

およそ10,000セルを有する第1種別のテスト構造に対するドレーンバイアスVaをパラメータとした場合の総等価フローティングゲート電流  $I_g$  を図8に示す。この場合には基板 2 3 を 0 Vとして100  $\mu$  A の電流  $I_g$  が共通ソース11電極へ印加される。ドレーン12電圧は5 V、6Vおよび6.9Vに固定される。各定ドレーン電圧Vaによりゲート電圧Vg は 0 Vからおよそ8.5 Vまで変動し各定ドレーン電圧Vaに対して等価フローティングゲート・電極電流  $I_g$  が測定される。

# [0028]

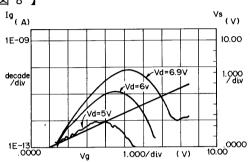

およそ10,000セルを有する第1種別のテスト構造に対する総等価フローティングゲート電流  $I_g$  の変動を図9に再び示す。ここでは、基板 2 3 を 0 V として 1 0  $\mu$  A の電流  $I_g$  が共通ソース 1 1 に印加される。ドレーン電圧  $V_d$  は 5 V、6 V および 6 . 9 V に固定される。各定ドレーン電圧  $V_d$  によりゲート電圧  $V_g$  は 0 V からおよそ 8 . 5 V まで変動し、各定ドレーン電圧  $V_d$  に対して等価フローティングゲート・電極電流  $I_g$  が測定される。

#### [0029]

制御ゲート電圧 V <sub>c g</sub> を + 5 V としドレーン電圧 V <sub>d</sub> を + 6 . 5 V として 3 0 μ A の電流を 1 秒間共通ソース 1 1 に印加した後のおよそ 1 0 , 0 0 0 セルを有する第 2 種別のテスト構造内の閾値電圧 V <sub>t</sub> の圧縮が改善される様子を図 1 0 に示す。圧縮の改善は圧縮手順

30

40

50

[0030]

[0031]

特定の10Kテスト構造に対する実験上のフラッシュ・プログラム・圧縮ステップは1秒を要しおよそ30µAの総ソース11電流を使用する(図10~図11)。

[0032]

前記した方法は操作中にソース11およびドレーン12接合間に存在するチャネル電流を頼りにしている。ある意味では前節で説明した方法ほど効率的ではないが、ソース11およびドレーン12間に外部から誘起されるチャネル電流の無い方法を使用することもできる。外部誘起チャネル電流が無いことの利点は過消去されたメモリアレイ内のディプリートされたビット線数に対して完全に無感応となることである。

[0033]

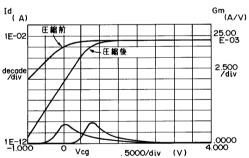

共通ソース11電極をフロートさせ("オフ"状態の電界効果型トランジスタ等の高インピーダンスに接続)制御ゲート電圧を+5 V として100μ A のドレーン電流 I  $_{\rm d}$  を 1 秒間共通ドレーン接続へ注入した後のおよそ10,000セルを有する第2種別のテスト構造内における閾値電圧 V  $_{\rm t}$  の圧縮が改善される様子を図12に示す。改善は圧縮前後に制御ゲート電圧 V  $_{\rm cg}$  が  $_{\rm t}$  1 V から  $_{\rm t}$  4 V まで変動する時のドレーン電流 I  $_{\rm td}$  のグラフによって示される。図10に示すように、ある点における圧縮前の傾斜は圧縮後の傾斜よりも勾配が小さくしかも直線でなく、制御ゲート電圧 V  $_{\rm td}$  g が増加する時にあるセル10は他よりも先に導通することを示している。圧縮後の傾斜は比較的急峻で直線となり、セル10は制御ゲート電圧 V  $_{\rm td}$  g が増加するのと同じ点で導通開始され、閾値電圧 V  $_{\rm td}$  の分布が圧縮されることを示している。

[0034]

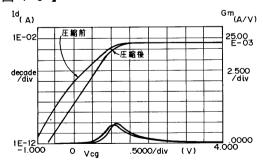

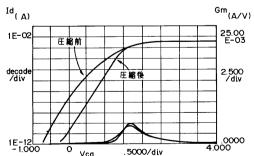

共通ソース 1 1 電極をフロートさせ (高インピーダンスに接続)制御ゲート電圧  $V_{cg}$ を + 5 Vとして 1 0  $\mu$  A のドレーン電流  $I_{g}$ を 1 0 秒間共通ドレーン 1 2 へ注入した後のおよそ 1 0 , 0 0 0 セルを有する第 2 種別のテスト構造内における閾値電圧  $V_{t}$ の圧縮が改善される様子を図 1 3 に示す。改善は圧縮の前後で制御ゲート電圧  $V_{cg}$ を - 1 Vから + 4 Vまで変動させた時のドレーン電流  $I_{d}$ のグラフで示される。図 1 1 と同様に、圧縮後の傾斜は圧縮前の傾斜よりも急峻であり、閾値電圧  $V_{t}$ の範囲が狭くなり分布が圧縮されたことを示している。

[0035]

ハウラーノルドハイムの場合に較べ、図 1 2 および図 1 3 のゲート電流  $I_g$  は低い制御ゲート電圧  $V_{cg}$  で開始される。したがって、ワード線 1 5 電圧を高くする必要がなくなる

30

40

50

。また、ソース11がフロートしたままとされるため、この技術はソース・ドレーンのリーク量、ディプリートされたセル10の数、これらのセル10内のディプレッションの程度により制約されることがない。

[0036]

ソース 1 1 に印加される正電圧バイアスを使用して注入効率が向上するため、例えば 1 メガビットフラッシュメモリアレイを本発明の圧縮手順を 1 秒以下だけ使用しておよそ 1 0 m A の総ソース 1 1 消費電流でフラッシュプログラムすることができる。

[0037]

圧縮プログラミングに使用されるソースバイアス法を図14~図16に示す。図14はプログラミング中にセル10のソース11をバイアス(例えば+0.7V)するのに使用されるダイオード接続電界効果型トランジスタ27を示す。(2個の直列ダイオード27時間して+1.4Vのバイアスを得る)。ダイオード27接続には他の動作中に他のをにトランジスタ27を使用できるようにする(図示せぬ)スイッチングトランジスタ27を使用できるようにする(図示せぬ)スイッチングトランジスタ27を使用できるようにする(図示せぬ)スイッチングトランジスタ27の替りに電圧源、電流源、抵抗、もしくはその組合せを使用することができる。図15はプログラミング圧縮操作中に図14のダイオード接続電界効果型トランジスタ27を抵抗29で置換した、プログラミングゲートで使用して制御ゲート電圧を制御する増幅器帰還回路を示す。図16は、図14のダイオード接続電界効果型トランジスタ27を抵抗29で置換した、プログラミングゲートで中に制御ゲート電圧を制御する第2の増幅器帰還回路を示す。フローティングゲートで中に制御ゲート電圧を制御する第2の増幅器帰還回路が米国特許第4,797,856号に記載されている。もう一つの方法はゲートでよることである。さらしての方法はゲート電圧を傾斜させながらソース11電流を制限することである。

[0038]

図15~図16の回路によりフラッシュ・プログラミング・圧縮ステップの開始時におけるゲートバイアス電圧 Vg が高くなり、工程の速度が高くなる。フラッシュ・プログラミング圧縮ステップが進行すると、ゲートバイアス電圧 Vg が低下し、プログラミング電流がおそくなってセル10の閾値電圧が収束すなわち圧縮される。

[0039]

もう一つの方法はゲート14へ所定のバイアス電圧を印加し、次にソース11へパルス電流を印加することである。次にアレイの状態が調べられる。リーク電流が所定値の点に達したら圧縮工程は停止される。

[0040]

本発明のゲート電流Ⅰ。の物理的源泉は下記の一つ以上の要因によるものである。

[0041]

1).ソース11接合から外部発生されドレーン12ディプレッション領域内で充分なエネルギを得てゲート絶縁膜障壁を越えて放出される電子。

[0042]

2).ドレーン12ディプレッション領域内の衝撃イオン化によりシリコン基板23内に 発生する電子(衝撃イオン化はアバランシェ接合もしくはディプレッション領域内の高電 界中を横切するバンド間トンネル誘起ホール電流により開始することができる)。

[0043]

前記 2 )の電子のいくらかはゲート 1 3 の下のディプレッション領域に集められる。これらの電子のほんの一部だけが(ゲート 1 3 に直角な経路で)ディプレッション領域を横切するエネルギを得、その後でゲート 1 3 への注入が行われる。フローティングソース 1 1 の場合には、前記 2 )の電子のいくらかは衝撃イオン化工程により生成され、フローティングソース 1 1 に集められる。ソース 1 1 導体がフローティング性であるため、これらの電子はシリコン表面に沿ってドレーン 1 2 接合へ引き戻される。 1 )で説明したのと同様な機構に従ってこれらの電子のほんの一部がフローティングゲート 1 3 中へ放出される。両者の違いは、1 )の場合にはソース 1 1 側から来る電子は外部から供給されるが、後者

の場合にはシリコン基板 2 3 内で進行中のキャリア増倍過程により電子が供給されることである。

### [0044]

前記した例では1種類のフローティングゲートセル10についてしか検討されていないが、本発明はいかなる種類の非スプリットゲート非揮発性メモリセル10を使用した非揮発性メモリにも使用できる。

#### [0045]

ここの実験データはテスト構造の等価フローティングゲート13の電圧に関するものであるが、これらの電圧は制御ゲート14に必要な適切な範囲の値へ変換して所望するフローティングゲート13電圧とすることができる。フローティングゲート13と基準電圧(Vss)との間の電圧Vg は次式で示され、

【数1】

$$Vg = (CppVcg + CsVs + CdVd + CchVch + Qf)/(Cpp + Cs + Cd + Cch)$$

ここに、 $C_{pp}$ は制御ゲート 1 4 とフローティングゲート 1 3 間の容量、 $C_{s}$ はフローティングゲート 1 3 とソース 1 1 間の容量、 $C_{d}$ はフローティングゲート 1 3 とドレーン 1 2 間の容量、 $C_{ch}$ はフローティングゲート 1 3 とソース 1 1 およびドレーン 1 2 間のチャネルとの間の容量、 $V_{cg}$ は制御ゲート 1 4 の電圧、 $V_{s}$ はソース 1 1 の電圧、 $V_{d}$ はドレーン 1 2 の電圧、 $V_{ch}$ はソース 1 1 およびドレーン 1 2 間のチャネルの電圧、  $Q_{f}$ はフローティングゲート 1 3 の電荷である。

## [0046]

ここの実験データはドレーン 1 2 に対するあるバイアス条件およびソース 1 1 に対する他のバイアス条件について記述している。多くの場合、ソース 1 1 およびドレーン 1 2 に対する一般的なバイアス条件は逆にすることができ、しかも同じ結果が得られる。したがって、"ソース"および"ドレーン"という用語は特許請求の範囲も含めて本明細書では取り替えて使うことができる。

# [0047]

したがってセルアレイを圧縮するために、ドレーン 1 2 は例えば基板 2 3 電圧に対して + 6 V ~ + 8 V に保持され、ソース 1 1 は例えば + 1 V ~ + 2 V に保持され、制御ゲート 1 4 はソース 1 1 電圧よりもおよそ + 1 V ~ + 2 V 高く保持される。

#### [0048]

第2の圧縮手順を使用して、ドレーン 1 2 は例えば基板 2 3 電圧に対して + 6 V ~ + 7 V に保持され、ソース 1 1 は高インピーダンスに接続され(フロートされる)、制御ゲート 1 4 は例えば + 2 V ~ + 5 V に保持される。制御ゲート 1 4 は定電圧に保持されるか、 2 つの電圧(例えば、 + 2 V と + 5 V)間でクロックされるか、あるいは制御ゲート 1 4 の電圧がゆるやかに傾斜される。

# [0049]

いずれの手順においても、制御ゲートの電圧はソースに正電圧(逆バイアス電圧)を有 40 するセルの代表的な閾値電圧よりも値が小さい。もちろん、ソースの逆バイアス電圧が増大するとセルの閾値電圧も増大する。

## [0050]

実施例について本発明を説明してきたが、本明細書は制約的意味合いを有するものではない。当業者ならば本明細書を参照すれば実施例のさまさまな修正や他の実施例が自明になるものと思われる。本発明の範囲内に入るこのような修正や実施例は全て特許請求の範囲に入るものとする。

## [0051]

以上の説明に関して更に以下の項を開示する。

## [0052]

20

(1).基準電圧に接続された基板を有する非揮発性集積回路メモリ内のフローティング ゲートメモリのプログラミング方法であって、該方法は、

前記メモリのソースを高インピーダンスに接続し、

前記メモリセルのドレーンへ電流を流し、

前記基準電圧に対して正である電圧を前記メモリセルの制御ゲートに印加する、

ことからなる、プログラミング方法。

[0053]

(2).第1項記載の方法であって、前記高インピーダンスを得るのに"オフ"状態の電 界効果型トランジスタが使用される、プログラミング方法。

[0054]

10

20

30

40

(3).第1項記載の方法であって、前記100µAの電流は前記10,00個のメモリセルの並列接続されたドレーンへ流され前記メモリセルの制御ゲートの前記電圧は前記基準電圧に対して+5Vであり、両方共1秒の期間であるプログラミング方法。

[0055]

(4).第1項記載の方法であって、2個以上のセルが同時にプログラムされる、プログラミング方法。

[0056]

(5).基準電圧に接続された基板を有する非揮発性集積回路メモリ内のフローティング ゲートメモリセルのプログラミング方法であって、該方法は、

前記メモリセルの制御ゲートの電圧を前記基準電圧に対して正の値を有するようにし、

前記メモリセルのソースの電圧を前記基準電圧に対して正の値を有するようにし、

前記メモリセルのドレーンへ電流を流すようにする、ことからなり、

制御ゲートの前記電圧はソースに前記電圧を有するセルの代表的な閾値電圧よりも小さい値を有する、プログラミング方法。

[0057]

(6).第5項記載の方法であって、前記ソースの前記正の電圧は前記ソースと前記基準電圧との間に少くとも1個のダイオードトランジスタを接続して得られる、プログラミング方法。

[0058]

(7).第5項記載の方法であって、前記ソースの前記正の電圧は帰還増幅器により前記 セルの前記制御ゲートに接続される、プログラミング方法。

[0059]

(8).第5項記載の方法であって、前記制御ゲートの前記電圧は最適ゲート電流注入を行うように調整される、プログラミング方法。

[0060]

(9).第5項記載の方法であって、前記制御ゲートの前記電圧は傾斜している、プログラミング方法。

[0061]

(10).第5項記載の方法であって、前記ソースの前記正の電圧が前記ソースと前記基準電圧との間に接続された抵抗を流れる電流により得られる、プログラミング方法。

[0062]

(11).第5項記載の方法であって、前記方法を使用して2個以上の前記メモリセルが同時にプログラムされる、プログラミング方法。

[0063]

(12).第5項記載の方法であって、前記方法を使用して1列のメモリセル内のセレクトされたメモリセルが同時にプログラムされる、プログラミング方法。

[0064]

(13).第5項記載の方法であって、前記方法を使用して前記アレイ内の前記メモリセルの全部が同時にプログラムされる、プログラミング方法。

[0065]

20

30

40

50

(14).第5項記載の方法であって、前記メモリセルが並列接続されており、前記ソー スの前記電圧は前記ソースから電流を除去することにより正の値をとるようにされ、前記 電流は前記ドレーンに接続された電圧源により前記メモリセルの前記ドレーンへ流入する ようにされ、全てが1秒の期間である、プログラミング方法。

[0066]

(15).基板を有する非揮発性集積回路メモリ内のフローティングゲートメモリセルの プログラミング方法であって、該方法は、

前記メモリセルの制御ゲートの電圧が前記基板の電圧に対して正の値を有するようにし、 前記メモリセルのソースを前記基板に対して逆バイアスし、

前記メモリセルのドレーンを前記基板について逆バイアスし、

前記ドレーンおよび前記ソース間に電流が流れるようにする、ことからなり、

制御ゲートの前記電圧は前記逆バイアスされたソースを有する前記セルの代表的な閾値電 圧よりも小さい値を有する、

プログラミング方法。

[0067]

( 1 6 ) . 第 1 5 項記載の方法であって、前記ソースがそれに直列接続されたトランジス タダイオードにより前記基板に対して逆バイアスされる、プログラミング方法。

[0068]

(17).第15項記載の方法であって、前記ソースの電圧が帰還増幅器により前記セル の前記制御ゲートに接続される、プログラミング方法。

[0069]

(18).第15項記載の方法であって、前記ソースと前記基板との間に接続された抵抗 を流れる電流により前記ソースが前記基板に対して逆バイアスされる、プログラミング方 法。

[0070]

(19).第15項記載の方法であって、前記方法を使用して2個以上の前記メモリセル が同時にプログラムされる、プログラミング方法。

[0071]

(20).第15項記載の方法であって、前記方法を使用して1列の前記メモリセル内の セレクトされたメモリセルが同時にプログラムされる、プログラミング方法。

[0072]

(21).第15項記載の方法であって、前記方法を使用して前記アレイの全メモリセル が同時にプログラムされる、プログラミング方法。

[0073]

(22).第15項記載の方法であって、前記制御ゲートの前記電圧が傾斜している、プ ログラミング方法。

[0074]

(23).本発明の方法によりプログラミング中により低いワード線電圧 V。1を使用す ることができる。さらに、本発明によりメモリセルアレイ10のフラッシュプログラミン グに使用した場合に比較的狭い閾値電圧V、分布が得られる。またプログラムされるセル のソース11/基板23接合を逆バイアスすることにより圧縮ゲート電流効率が向上する 。逆バイアスは、例えば、ソース11にバイアス電圧を印加するかもしくはソース11に 直列にダイオード27、抵抗29、もしくは他のインピーダンスを接続して行われる。逆 バイアスによりフラッシュプログラミング圧縮中にプログラムされるセルもしくはアレイ 全体のソース電流(IS)が制限される。

【図面の簡単な説明】

【図1】メモリセルアレイの部分ブロック形式の電気回路図。

【図2】図1のメモリセルアレイ内で使用される代表的なフローティングゲートセルの断 面図。

【図3】400 抵抗を介してドレーンに+6.5Vを接続しかつソースを接地して、多

セルテスト構造のゲート電圧を変えた時の従来のゲート電流の変化を示すグラフ。

- 【図4】ソースを+0.5 Vとした時の、図3と同様なゲート電流とゲート電圧の変化を示すグラフ。

- 【図5】ソースを+1.0 Vとした時の、図3と同様なゲート電流とゲート電圧の変化を示すグラフ。

- 【図 6 】ソースを + 0 . 2 V とした時の、図 3 と同様なゲート電流とゲート電圧の変化を示すグラフ。

- 【図7】ドレーンに+6.8Vを印加し等価フローティングゲート電圧が変動する場合の 、共通ソース電極に印加される3つの電流値に対する多セルテスト構造内の総等価フロー ティングゲート電流の変化を示すグラフ。

- 【図8】共通ソース電極に100μAの電流を印加し等価フローティングゲート電圧が変動する場合の、3つのドレーン電圧値に対する多セルテスト構造内の総等価フローティングゲート電流の変化を示すグラフ。

- 【図9】共通ソース電極に10μAの電流を印加し等価フローティングゲート電圧が変化する場合の、3つのドレーン電圧値に対する多セルテスト構造内の総等価フローティングゲート電流の変化を示すグラフ。

- 【図10】制御ゲート電圧を+5 Vとしドレーン電圧を+6.5 Vとして共通ソース電極に30 µ A の電流を1秒間印加した前後の、適度に過消去された多セルテスト構造の閾値電圧の圧縮量を比較するグラフ。

- 【図11】制御ゲート電圧を5 V としドレーン電圧を+6.5 V として共通ソース電極に30 μ A の電流を1 秒間印加した前後の、極端に過消去された多セルテスト構造内の閾値電圧の圧縮量を比較するグラフ。

- 【図12】共通ソース電極をフローティングし制御ゲート電圧を+5 V としてドレーンに 100μAの電流を1秒間印加した前後の、多セルテスト構造内の閾値電圧の圧縮量を比較するグラフ。

- 【図13】共通ソース電極をフローティングし制御ゲート電圧を+5 Vとしてドレーンに 10μAの電流を10秒間印加した前後の、多セルテスト構造内の閾値電圧の圧縮量を比較するグラフ。

- 【図14】プログラミング圧縮操作中に使用するバイアス回路の回路図。

- 【図15】プログラミング圧縮操作中にゲート電圧を制御する帰還回路の回路図。

- 【図16】プログラミング圧縮操作中にゲート電圧を制御する第2の帰還回路の回路図。

# 【符号の説明】

- 10 メモリセル

- 11 ソース

- 12 ドレーン

- 13 フローティングゲート

- 1 4 制御ゲート

- 15 ワード線

- 16 ワード線デコーダ

- 17 ソース線

- 18 ドレーン・カラム線

- 19 カラムデコーダ

- 2 0 d アドレス線

- 2 0 r 線

- 21 リード/ライト/イレーズ制御回路

- 22 DATA IN/OUT 端子

- 2 3 基板

- 24 チャネル

- 2 5 絶縁膜

- 26 層間絶縁膜

40

30

10

20

- 27 電界効果型トランジスタ

- 28 增幅器帰還回路

- 2 9 抵抗

【図2】

【図3】

【図4】

【図5】

# 【図7】

# 【図6】

# 【図8】

# 【図9】

# 【図11】

# 【図10】

【図12】

# 【図13】

# 【図16】

# 【図14】

# 【図15】

# フロントページの続き

(72)発明者セティン カヤアメリカ合衆国テキサス州ダラス, アドレタ ブールバード 9900, アパートメント ナンバー 1114

(72)発明者ウェイランドビー・ホランドアメリカ合衆国テキサス州ガーランド , ランカスターストリート 2 6 1 8

(72)発明者 ラバ メゼンナー アメリカ合衆国テキサス州リチャードソン,パーク ガーデン プレース 3122

審査官 石川 正二

(56)参考文献 特開平06-151785(JP,A) 特開平03-230566(JP,A)

(58)調査した分野(Int.CI., DB名) G11C 16/04