(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7445397号

(P7445397)

(45)発行日 令和6年3月7日(2024.3.7)

(24)登録日 令和6年2月28日(2024.2.28)

(51)国際特許分類

|        |                  |        |        |   |

|--------|------------------|--------|--------|---|

| H 01 L | 31/107 (2006.01) | H 01 L | 31/10  | B |

| H 01 L | 27/146 (2006.01) | H 01 L | 27/146 | A |

| H 04 N | 25/704 (2023.01) | H 04 N | 25/704 |   |

| H 04 N | 25/705 (2023.01) | H 04 N | 25/705 |   |

| G 01 S | 7/481 (2006.01)  | G 01 S | 7/481  | Z |

請求項の数 4 (全22頁)

(21)出願番号 特願2019-141690(P2019-141690)

(22)出願日 令和1年7月31日(2019.7.31)

(65)公開番号 特開2021-27084(P2021-27084A)

(43)公開日 令和3年2月22日(2021.2.22)

審査請求日 令和4年6月15日(2022.6.15)

(73)特許権者 316005926

ソニーセミコンダクタソリューションズ

株式会社

神奈川県厚木市旭町四丁目14番1号

(74)代理人 110002147

弁理士法人酒井国際特許事務所

村上 博亮

(72)発明者 神奈川県厚木市旭町四丁目14番1号

ソニーセミコンダクタソリューションズ

株式会社内

佐竹 政彦

審査官

最終頁に続く

(54)【発明の名称】 受光素子および電子機器

## (57)【特許請求の範囲】

## 【請求項1】

半導体層に形成され、アレイ状に配置される複数の画素ごとに設けられる S P A D ( Single Photon Avalanche Diode ) 素子と、

前記半導体層に隣接する配線層に少なくとも一部が形成され、前記 S P A D 素子に逆バイアス電圧を印加するカソード電極およびアノード電極と、

前記半導体層に形成され、前記カソード電極に直接接続される N 型のカソードコンタクト領域と、

前記半導体層に形成され、前記アノード電極に直接接続される P 型のアノードコンタクト領域と、

前記カソードコンタクト領域と前記半導体層の光入射側とは反対側の面との間に位置する絶縁性の埋め込み層と、

を備え、

平面視において、前記アノードコンタクト領域は、前記画素の周縁部に位置し、

平面視において、前記カソードコンタクト領域は、前記アノードコンタクト領域よりも前記画素の中央側に位置し、

前記カソードコンタクト領域は、前記アノードコンタクト領域よりも前記半導体層の光入射側に位置する

受光素子。

## 【請求項2】

前記半導体層における光入射側とは反対側の面に形成され、接地電位に接続される表面ピニング層をさらに備える

請求項 1 に記載の受光素子。

【請求項 3】

前記半導体層において前記カソードコンタクト領域と接する N 型拡散層をさらに備え、

前記 N 型拡散層と前記半導体層の光入射側とは反対側の面との間が前記埋め込み層で覆われる

請求項 1 に記載の受光素子。

【請求項 4】

半導体層に形成され、アレイ状に配置される複数の画素ごとに設けられる S P A D (Single Photon Avalanche Diode) 素子と、

前記半導体層に隣接する配線層に少なくとも一部が形成され、前記 S P A D 素子に逆バイアス電圧を印加するカソード電極およびアノード電極と、

前記半導体層に形成され、前記カソード電極に直接接続される N 型のカソードコンタクト領域と、

前記半導体層に形成され、前記アノード電極に直接接続される P 型のアノードコンタクト領域と、

前記カソードコンタクト領域と前記半導体層の光入射側とは反対側の面との間に位置する絶縁性の埋め込み層と、

を備える受光素子を備え、

平面視において、前記アノードコンタクト領域は、前記画素の周縁部に位置し、

平面視において、前記カソードコンタクト領域は、前記アノードコンタクト領域よりも前記画素の中央側に位置し、

前記カソードコンタクト領域は、前記アノードコンタクト領域よりも前記半導体層の光入射側に位置する

電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、受光素子および電子機器に関する。

30

【背景技術】

【0002】

光を用いて被測定物までの距離を測定する測距方式の一つとして、直接 T o F (Time of Flight) 方式と呼ばれる測距手法が知られている。かかる直接 T o F 方式では、光源から射出された光が被測定物により反射された反射光を受光素子により受光し、光が射出されてから反射光として受光されるまでの時間に基づき対象までの距離を計測する (たとえば、特許文献 1 参照)。

【先行技術文献】

【特許文献】

【0003】

【文献】特開 2004-319576 号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0004】

本開示では、受光素子の面積拡大を抑制しつつ、カソードコンタクト領域とアノードコンタクト領域との間の電界緩和を図ることができる受光素子および電子機器を提案する。

【課題を解決するための手段】

【0005】

本開示によれば、受光素子が提供される。受光素子は、S P A D (Single Photon Avalanche Diode) 素子と、カソード電極およびアノード電極と、カソードコンタクト領

50

域と、アノードコンタクト領域と、埋め込み層とを備える。S P A D 素子は、半導体層に形成され、アレイ状に配置される複数の画素ごとに設けられる。カソード電極およびアノード電極は、前記半導体層に隣接する配線層に少なくとも一部が形成され、前記S P A D 素子に逆バイアス電圧を印加する。N型のカソードコンタクト領域は、前記半導体層に形成され、前記カソード電極に直接接続される。P型のアノードコンタクト領域は、前記半導体層に形成され、前記アノード電極に直接接続される。絶縁性の埋め込み層は、前記カソードコンタクト領域および前記アノードコンタクト領域のいずれか一方と、前記半導体層の光入射側とは反対側の面との間に位置する。

【発明の効果】

【0006】

本開示によれば、受光素子の面積拡大を抑制しつつ、アノードコンタクト領域とカソードコンタクト領域との間の電界緩和を図ることができる。なお、ここに記載された効果は必ずしも限定されるものではなく、本開示中に記載されたいずれかの効果であってもよい。

10

【図面の簡単な説明】

【0007】

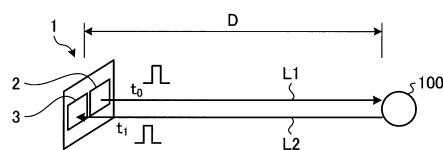

【図1】本開示の実施形態に適用可能である直接T o F方式による測距を模式的に示す図である。

【図2】本開示の実施形態に適用可能である受光チップが受光した時刻に基づく一例のヒストグラムを示す図である。

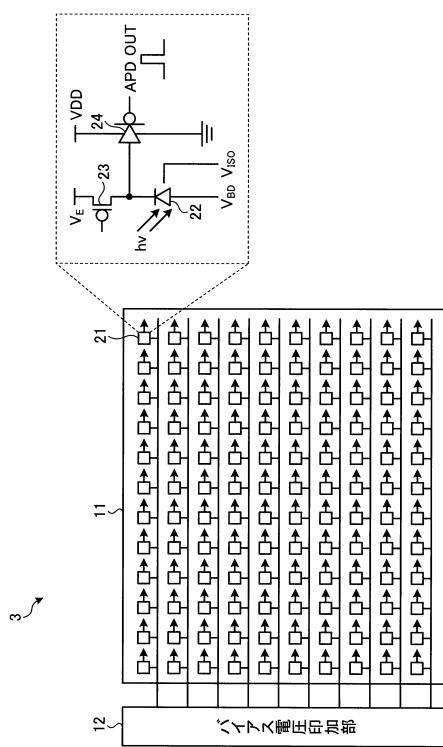

【図3】本開示の実施形態に係る受光チップの構成例を示すブロック図である。

20

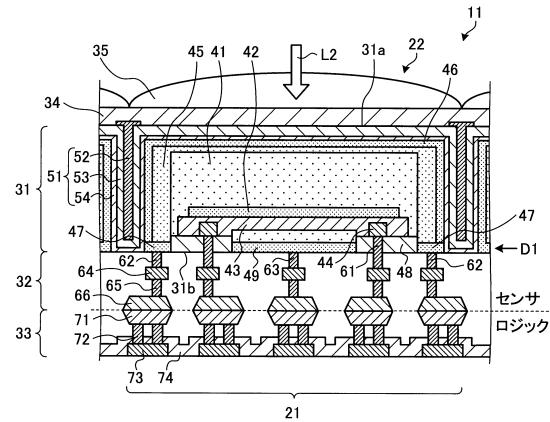

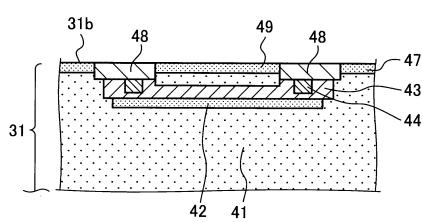

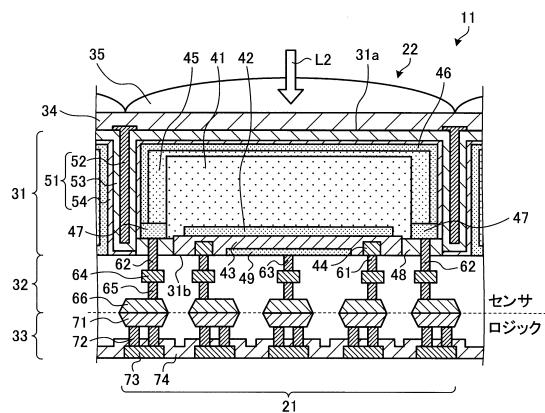

【図4】本開示の実施形態に係る画素アレイ部の構成例を示す断面図である。

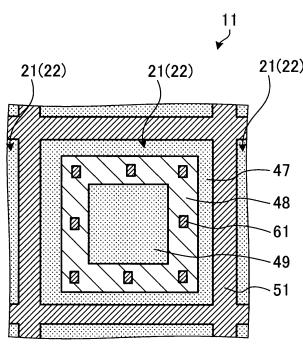

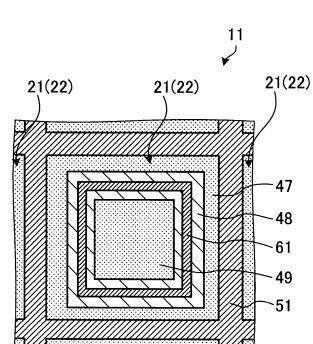

【図5】図4に示す深さD1の平面構造の一例を示す図である。

【図6】図4に示す深さD1の平面構造の別の例を示す図である。

【図7】本開示の実施形態に係る画素アレイ部の一製造工程を模式的に示す断面図である。

【図8】本開示の実施形態に係る画素アレイ部の一製造工程を模式的に示す断面図である。

【図9】本開示の実施形態に係る画素アレイ部の一製造工程を模式的に示す断面図である。

【図10】本開示の実施形態に係る画素アレイ部の一製造工程を模式的に示す断面図である。

【図11】本開示の実施形態に係る画素アレイ部の一製造工程を模式的に示す断面図である。

30

【図12】本開示の実施形態に係る画素アレイ部の一製造工程を模式的に示す断面図である。

【図13】本開示の実施形態の変形例1に係る画素アレイ部の構成例を示す断面図である。

【図14】本開示の実施形態の変形例2に係る画素アレイ部の構成例を示す断面図である。

【図15】本開示の実施形態の変形例3に係る画素アレイ部の構成例を示す断面図である。

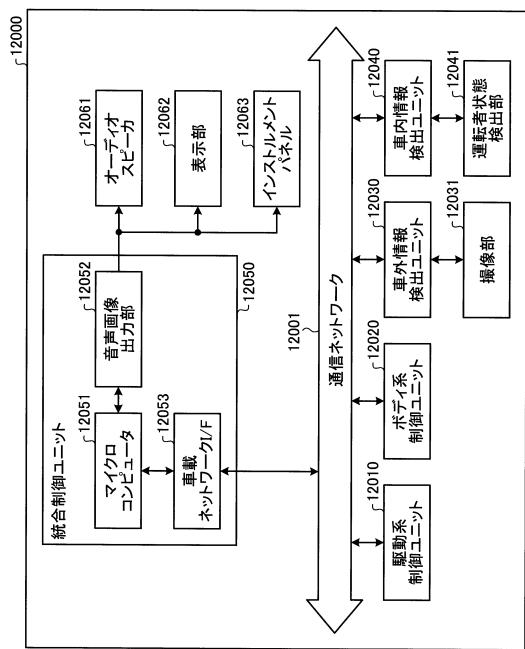

【図16】電子機器の概略的な構成の一例を示すブロック図である。

【図17】車両制御システムの概略的な構成の一例を示すブロック図である。

【図18】車外情報検出部及び撮像部の設置位置の一例を示す説明図である。

【発明を実施するための形態】

【0008】

40

以下に、本開示の各実施形態について図面に基づいて詳細に説明する。なお、以下の各実施形態において、同一の部位には同一の符号を付することにより重複する説明を省略する。

【0009】

光を用いて被測定物までの距離を測定する測距方式の一つとして、直接T o F (Time of Flight)方式と呼ばれる測距手法が知られている。かかる直接T o F 方式では、光源から射出された光が被測定物により反射された反射光を受光素子により受光し、光が射出されてから反射光として受光されるまでの時間に基づき対象までの距離を計測する。

【0010】

かかる測距手法には、内部にS P A D (Single Photon Avalanche Diode) 素子を

50

備えた受光素子が用いられる。かかるS P A D 素子は、アバランシェ増倍が発生する大きな逆バイアス電圧（たとえば、- 2 0 V程度）をアノードとカソードとの間に印加することにより、1光子の入射に応じて発生した電子に起因して、内部でアバランシェ増倍が生じる。これにより、反射光に含まれる1光子の入射を高感度で検知することができる。

【0011】

しかしながら、S P A D 素子が形成される半導体層の裏面側において、互いに隣接するカソードコンタクト領域とアノードコンタクト領域との間には大きな逆バイアス電圧が印加される。これにより、カソードコンタクト領域とアノードコンタクト領域との間では電界が集中し、暗電流特性の悪化等の不具合が生じる場合がある。

【0012】

一方で、従来の技術に記載されているように、カソードコンタクト領域とアノードコンタクト領域との間にS T I (Shallow Trench Isolation) を形成した場合、かかるS T I の分だけ受光素子の面積が大きくなってしまうという問題が生じる。

【0013】

そこで、上述の問題点を克服し、受光素子の面積拡大を抑制しつつ、カソードコンタクト領域とアノードコンタクト領域との間の電界緩和を図ることができる受光素子および電子機器の実現が期待されている。

【0014】

【測距方法】

本開示は、光を用いて測距を行う技術に関するものである。そこで、本開示の実施形態の理解を容易とするために、図1および図2を参照しながら、実施形態に適用可能な測距方法について説明する。

20

【0015】

図1は、本開示の実施形態に適用可能である直接T o F方式による測距を模式的に示す図である。実施形態では、測距方式として直接T o F方式を適用する。

【0016】

かかる直接T o F方式は、光源2からの射出光L1が被測定物100により反射した反射光L2を受光チップ3により受光し、光の射出タイミングと受光タイミングとの差分の時間に基づき測距を行う方式である。

【0017】

測距装置1は、光源2と、受光チップ3とを備える。光源2は、たとえばレーザダイオードであり、レーザ光をパルス状に発光するように駆動される。

30

【0018】

光源2からの射出光L1は、被測定物100により反射され、反射光L2として受光チップ3に受光される。受光チップ3は、光電変換によって光を電気信号に変換し、受光した光に応じた信号を出力する。

【0019】

ここで、光源2が発光した時刻（発光タイミング）を時間 $t_0$ 、光源2からの射出光L1が被測定物100により反射された反射光L2を受光チップ3が受光した時刻（受光タイミング）を時間 $t_1$ とする。

40

【0020】

定数cを光速度（ $2.9979 \times 10^8$  [m/sec]）とすると、測距装置1と被測定物100との間の距離Dは、次式（1）により算出することができる。

$$D = (c/2) \times (t_1 - t_0) \quad \dots (1)$$

【0021】

より具体的には、測距装置1は、発光タイミングの時間 $t_0$ から受光チップ3に光が受光された受光タイミングまでの時間 $t_m$ （以下、「受光時間 $t_m$ 」とも呼称する。）を階級（ビン(bins)）に基づき分類し、ヒストグラムを生成する。

【0022】

図2は、本開示の実施形態に適用可能である受光チップ3が受光した時刻に基づく一例

50

のヒストグラムを示す図である。図2において、横軸はBIN、縦軸はBIN毎の頻度を示す。BINは、受光時間  $t_m$  を所定の単位時間  $d$  毎に分類したものである。

#### 【0023】

具体的には、BIN # 0 が  $0 \leq t_m < d$ 、BIN # 1 が  $d \leq t_m < 2 \times d$ 、BIN # 2 が  $2 \times d \leq t_m < 3 \times d$ 、...、BIN # (  $N - 2$  ) が  $(N - 2) \times d \leq t_m < (N - 1) \times d$  となる。受光チップ3の露光時間を時間  $t_{ep}$  とした場合、 $t_{ep} = N \times d$  となる。

#### 【0024】

測距装置1は、受光時間  $t_m$  を取得した回数をBINに基づき計数してBIN毎の頻度300を求め、ヒストグラムを生成する。ここで、受光チップ3は、光源2からの射出光L1が反射された反射光L2以外の光も受光する。

10

#### 【0025】

たとえば、対象となる反射光L2以外の光の例として、測距装置1の周囲の環境光がある。かかる環境光は、受光チップ3にランダムに入射する光であって、ヒストグラムにおける環境光による環境光成分301は、対象となる反射光L2に対するノイズとなる。

#### 【0026】

一方、対象となる反射光L2は、特定の距離に応じて受光される光であって、ヒストグラムにおいてアクティブ光成分302として現れる。このアクティブ光成分302内のピーカの頻度に対応するBINが、被測定物100の距離Dに対応するBINとなる。

#### 【0027】

測距装置1は、そのBINの代表時間(たとえばBINの中央の時間)を上述した時間  $t_1$  として取得することで、上述した式(1)に従い、被測定物100までの距離Dを算出することができる。このように、複数の受光結果を用いることで、ランダムなノイズに対して適切な測距が実行可能となる。

20

#### 【0028】

##### 【受光チップの構成】

つづいて、実施形態に係る受光チップ3の構成について、図3を参照しながら説明する。図3は、本開示の実施形態に係る受光チップ3の構成例を示すブロック図である。図1に示すように、実施形態に係る受光チップ3は、画素アレイ部11と、バイアス電圧印加部12とを備える。画素アレイ部11は、受光素子の一例である。

#### 【0029】

画素アレイ部11は、オンチップレンズ35(図4参照)などの光学系により集光される反射光L2(図4参照)を受光する受光面を有し、複数の画素21がアレイ状に配置される。かかる画素アレイ部11の構成については後述する。

30

#### 【0030】

図3の右側に示すように、画素21は、たとえば、SPAD素子22と、P型MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)23と、CMOSインバータ24とを備える。

#### 【0031】

SPAD素子22は、アノードとカソードとの間に大きな負電圧  $V_{BD}$  (たとえば、-20V程度)を印加することによってアバランシェ増倍領域を形成し、1光子の入射で発生する電子をアバランシェ増倍させることができる。

40

#### 【0032】

P型MOSFET23は、SPAD素子22でアバランシェ増倍された電子による電圧が負電圧  $V_{BD}$  に達すると、SPAD素子22で増倍された電子を放出して、初期電圧に戻すクエンチング(quenting)を行う。

#### 【0033】

CMOSインバータ24は、SPAD素子22で増倍された電子により発生する電圧を整形することで、1光子の到来時刻を始点としてパルス波形が発生する受光信号(APDOUT)を出力する。

#### 【0034】

50

バイアス電圧印加部 1 2 は、画素アレイ部 1 1 に配置される複数の画素 2 1 それぞれにに対して逆バイアス電圧を印加する。

【 0 0 3 5 】

このように構成されている受光チップ 3 からは、画素 2 1 ごとに受光信号が出力され、図示しない後段の演算処理部に供給される。かかる演算処理部は、たとえば、それぞれの受光信号において 1 光子の到来時刻を示すパルスが発生したタイミングに基づいて、被測定物 1 0 0 までの距離 D を求める演算処理を行い、画素 2 1 ごとに距離 D を求める。

【 0 0 3 6 】

そして、求められた距離 D に基づいて、複数の画素 2 1 により検出されたそれぞれの被測定物 1 0 0 までの距離 D を平面的に並べた距離画像が生成される。

10

【 0 0 3 7 】

[ 画素アレイ部の構成 ]

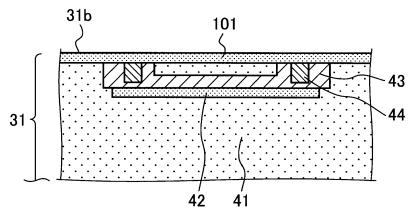

つづいて、実施形態に係る画素アレイ部 1 1 の構成について、図 4 ~ 図 6 を参照しながら説明する。図 4 は、本開示の実施形態に係る画素アレイ部 1 1 の構成例を示す断面図である。

【 0 0 3 8 】

図 4 に示すように、実施形態に係る画素アレイ部 1 1 は、半導体層 3 1 と、センサ側配線層 3 2 と、ロジック側配線層 3 3 と、平坦化層 3 4 と、オンチップレンズ 3 5 とを備える。センサ側配線層 3 2 は、配線層の一例である。

【 0 0 3 9 】

そして、反射光 L 2 が入射される側から順に、オンチップレンズ 3 5 、平坦化層 3 4 、半導体層 3 1 、センサ側配線層 3 2 およびロジック側配線層 3 3 が積層されて画素アレイ部 1 1 が構成される。

20

【 0 0 4 0 】

さらに、ロジック側配線層 3 3 に対して、図示しないロジック側基板がさらに積層される。かかるロジック側基板には、たとえば、図 3 に示したバイアス電圧印加部 1 2 や P 型 MOSFET 2 3 、 CMOS インバータ 2 4 などが形成されている。

【 0 0 4 1 】

たとえば、半導体層 3 1 に対してセンサ側配線層 3 2 を形成するとともに、ロジック回路基板に対してロジック側配線層 3 3 を形成する。その後、センサ側配線層 3 2 とロジック側配線層 3 3 とを接合面（図 4 の破線で示す面）で接合する製造方法により、画素アレイ部 1 1 を製造することができる。

30

【 0 0 4 2 】

センサ側配線層 3 2 とロジック側配線層 3 3 との接合手法としては、たとえば、両方の接合界面でそれぞれ Cu パッドを露出させ、かかる両方の Cu パッドを直接接合することで電気的導通も確保する、いわゆる「 Cu - Cu 接合」を用いることができる。

【 0 0 4 3 】

半導体層 3 1 は、たとえば、単結晶のシリコンなどの半導体基板を薄く研削した層であって、P 型または N 型の不純物濃度が制御されており、画素 2 1 ごとに SPAD 素子 2 2 が形成される。

40

【 0 0 4 4 】

また、図 4 において半導体層 3 1 の上側を向く面が、反射光 L 2 が入射する入射面 3 1 a とされ、その入射面 3 1 a の反対側となる反対面 3 1 b に対してセンサ側配線層 3 2 が積層される。

【 0 0 4 5 】

センサ側配線層 3 2 およびロジック側配線層 3 3 には、SPAD 素子 2 2 に印加される電圧を供給するための配線や、SPAD 素子 2 2 で発生した電子を半導体層 3 1 から取り出すための配線などが形成される。

【 0 0 4 6 】

SPAD 素子 2 2 は、半導体層 3 1 に形成される P ウェル 4 1 、 P 型拡散層 4 2 、 N 型

50

拡散層43、カソードコンタクト領域44、ホール蓄積層45、ピニング層46およびアノードコンタクト領域47により構成される。そして、S P A D 素子22では、P型拡散層42とN型拡散層43との接合領域に形成される空乏層によって、アバランシェ増倍領域が形成される。

#### 【0047】

かかるアバランシェ増倍領域は、N型拡散層43に印加される大きな負電圧によってP型拡散層42およびN型拡散層43の境界面に形成される高電界領域であって、S P A D 素子22に入射する1光子で発生する電子を増倍する。

#### 【0048】

Pウェル41は、半導体層31の不純物濃度がP型に制御されることにより形成され、S P A D 素子22における光電変換により発生する電子をアバランシェ増倍領域へ転送する電界を形成する。なお、Pウェル41に替えて、半導体層31の不純物濃度がN型に制御されてNウェルを形成してもよい。

#### 【0049】

P型拡散層42は、半導体層31の反対面31b近傍であってN型拡散層43に対して入射面31a側（図4の上側）に形成される濃いP型の拡散層（P<sup>+</sup>）であり、S P A D 素子22のほぼ全面に亘るように形成される。

#### 【0050】

N型拡散層43は、半導体層31の反対面31b近傍であってP型拡散層42に対して反対面31b側（図4の下側）に形成されるN型の拡散層（N）であり、S P A D 素子22のほぼ全面に亘るように形成される。

#### 【0051】

カソードコンタクト領域44は、N型拡散層43の内部において反対面31b側（図4の下側）に形成される濃いN型の拡散層（N<sup>+</sup>）である。かかるカソードコンタクト領域44は、N型拡散層43にアバランシェ増倍領域を形成するための電圧を供給するカソード電極61と直接接続される。

#### 【0052】

ホール蓄積層45は、Pウェル41の側面および光入射側の面を囲うように形成されるP型の拡散層（P）であり、ホールを蓄積している。また、ホール蓄積層45は、S P A D 素子22のアノードと電気的に接続されており、バイアス調整を可能とする。

#### 【0053】

これにより、ホール蓄積層45のホール濃度が強化されることから、ピニング層46を含むピニングを強固にすることができる。したがって、実施形態によれば、暗電流の発生を抑制することができる。

#### 【0054】

ピニング層46は、ホール蓄積層45よりも外側の表面（半導体層31の入射面31aや画素間分離部51と接する側面）に形成される濃いP型の拡散層（P<sup>+</sup>）であり、ホール蓄積層45と同様に、たとえば、暗電流の発生を抑制する。

#### 【0055】

アノードコンタクト領域47は、半導体層31の反対面31b近傍においてピニング層46と接するように形成される濃いP型の拡散層（P<sup>+</sup>）である。かかるアノードコンタクト領域47は、ピニング層46、ホール蓄積層45およびPウェル41を介して、P型拡散層42にアバランシェ増倍領域を形成するための電圧を供給するアノード電極62と直接接続される。

#### 【0056】

ここで、実施形態では、カソードコンタクト領域44およびアノードコンタクト領域47のいずれか一方と、半導体層31の反対面31bとの間に、絶縁性の埋め込み層48が設けられる。図4の例では、カソードコンタクト領域44と半導体層31の反対面31bとの間に、埋め込み層48が設けられる。

#### 【0057】

10

20

30

40

50

埋め込み層 4 8 は、たとえば、酸化シリコン (SiO<sub>2</sub>) などの絶縁体で構成される。そして、センサ側配線層 3 2 に形成されるカソード電極 6 1 が、かかる埋め込み層 4 8 を貫通し、カソードコンタクト領域 4 4 に直接接続される。

【0058】

このような埋め込み層 4 8 を設けることにより、大きな逆バイアス電圧が印加されるアノードコンタクト領域 4 7 とカソードコンタクト領域 4 4 との間を、水平方向のみならず垂直方向にも離間させながら絶縁分離することができる。

【0059】

すなわち、カソードコンタクト領域 4 4 とアノードコンタクト領域 4 7 との水平方向の距離を保ちつつ、カソードコンタクト領域 4 4 とアノードコンタクト領域 4 7 とをトータルで電界緩和を図ることができる距離だけ離間させることができる。

10

【0060】

したがって、実施形態によれば、画素アレイ部 1 1 の面積拡大を抑制しつつ、カソードコンタクト領域 4 4 とアノードコンタクト領域 4 7 との間の電界緩和を図ることができる。

【0061】

画素アレイ部 1 1 におけるその他の部位についての説明を続ける。表面ピニング層 4 9 は、半導体層 3 1 の反対面 3 1 b において、アノードコンタクト領域 4 7 、埋め込み層 4 8 および画素間分離部 5 1 以外の箇所に形成される濃いP型の拡散層 (P<sup>+</sup>) である。表面ピニング層 4 9 は、コンタクト電極 6 3 を介して接地電位に接続される。

【0062】

かかる表面ピニング層 4 9 を設けることにより、反対面 3 1 b の界面準位を抑えることができるところから、画素アレイ部 1 1 の暗時特性を向上させることができる。

20

【0063】

図 5 は、図 4 に示す深さ D 1 の平面構造の一例を示す図である。図 5 に示すように、画素アレイ部 1 1 では、互いに隣接する S P A D 素子 2 2 同士の間に画素間分離部 5 1 を設けることによって、それぞれの S P A D 素子 2 2 が電気的および光学的に分離される。

【0064】

実施形態では、たとえば平面視において、表面ピニング層 4 9 を囲むように枠形状の埋め込み層 4 8 が形成され、かかる埋め込み層 4 8 を囲むように枠形状のアノードコンタクト領域 4 7 が形成される。また、埋め込み層 4 8 の内部には、複数 (図では 8 個) のカソード電極 6 1 が周方向に均等に配置される。

30

【0065】

なお、埋め込み層 4 8 の内部におけるカソード電極 6 1 の配置は、図 5 の例に限られない。たとえば、図 6 に示すように、平面視で枠形状のカソード電極 6 1 が、埋め込み層 4 8 に沿うように配置されてもよい。図 6 は、図 4 に示す深さ D 1 の平面構造の別の一例を示す図である。

【0066】

図 4 の説明に戻る。図 4 に示すように、画素間分離部 5 1 は、たとえば、半導体層 3 1 の入射面 3 1 a から反対面 3 1 b まで貫通するように形成される。画素間分離部 5 1 は、たとえば、内側から順に金属膜 5 2 、絶縁膜 5 3 および固定電荷膜 5 4 で構成される三重構造を有する。

40

【0067】

金属膜 5 2 は、たとえば、光を反射する金属 (たとえば、タンクステンなど) で構成される。絶縁膜 5 3 は、たとえば、酸化シリコン (SiO<sub>2</sub>) などの絶縁体で構成される。

【0068】

固定電荷膜 5 4 は、ピニング層 4 6 との界面部分において正電荷 (ホール) 蓄積領域が形成されて暗電流の発生が抑制されるように、負の固定電荷を有する高誘電体を用いて形成される。固定電荷膜 5 4 が負の固定電荷を有するように形成されることで、その負の固定電荷によってピニング層 4 6 との界面に電界が加わり、正電荷 (ホール) 蓄積領域が形成される。

50

## 【0069】

固定電荷膜 54 は、たとえば、ハフニウム酸化膜 (HfO<sub>2</sub> 膜) で形成することができる。また、固定電荷膜 54 は、その他、たとえば、ハフニウム、ジルコニウム、アルミニウム、タンタル、チタン、マグネシウム、イットリウム、ランタノイド元素などの酸化物の少なくとも 1 つを含むように形成することができる。

## 【0070】

センサ側配線層 32 には、カソード電極 61、アノード電極 62、コンタクト電極 63、メタル配線 64、コンタクト電極 65 およびメタルパッド 66 が形成される。なお、センサ側配線層 32 において、これらの部位以外の箇所には、層間絶縁膜が形成される。

## 【0071】

そして、カソード電極 61、アノード電極 62 およびコンタクト電極 63 は、それぞれメタル配線 64 およびコンタクト電極 65 を介して、対応するメタルパッド 66 に電気的に接続される。

## 【0072】

ロジック側配線層 33 には、メタルパッド 71、コンタクト電極 72、電極パッド 73 および絶縁層 74 が形成される。なお、ロジック側配線層 33 において、これらの部位以外の箇所には、層間絶縁膜が形成される。

## 【0073】

そして、カソード電極 61、アノード電極 62 およびコンタクト電極 63 に対応するメタルパッド 66 は、それぞれメタルパッド 71 およびコンタクト電極 72 を介して、対応する電極パッド 73 に電気的に接続される。絶縁層 74 は、互いに隣接する電極パッド 73 同士を絶縁する。

## 【0074】

すなわち、カソードコンタクト領域 44、アノードコンタクト領域 47 および表面ピニング層 49 は、センサ側配線層 32 およびロジック側配線層 33 に形成される各種配線を介して、対応する電極パッド 73 に電気的に接続される。

## 【0075】

平坦化層 34 は、半導体層 31 の入射面 31a 全体に密着して形成され、半導体層 31 の入射面 31a を平坦化するために設けられる。平坦化層 34 は、反射光 L2 を透過する材料（たとえば、透過性の樹脂材料など）で構成される。

## 【0076】

オンチップレンズ 35 は、たとえば、1 つの画素 21 ごとに形成され、対応する画素 21 に入射する反射光 L2 を集光する。なお、オンチップレンズ 35 は、1 つの画素 21 ごとに形成される場合に限らず、たとえば、互いに隣接する複数の画素 21 ごとに形成されてもよい。

## 【0077】

## [画素アレイ部の製造工程]

つづいて、実施形態に係る画素アレイ部 11 の製造工程、特に埋め込み層 48 の形成工程について、図 7 ~ 図 12 を参照しながら説明する。図 7 ~ 図 12 は、本開示の実施形態に係る画素アレイ部 11 の一製造工程を模式的に示す断面図である。

## 【0078】

図 7 に示すように、不純物濃度が P 型に制御された（すなわち、P ウェル 41 を有する）半導体層 31 に対して、反対面 31b の近傍に、P 型拡散層 42 と、N 型拡散層 43 と、カソードコンタクト領域 44 と、P 型拡散層 101 とを公知の手法により形成する。P 型拡散層 101 は、濃い P 型の拡散層 (P<sup>+</sup>) であり、反対面 31b の全面に形成される。

## 【0079】

なお、図 7 の状態において、半導体層 31 の入射面 31a 側は研削されていないことから、図 7 の状態における半導体層 31 は図 4 に示した半導体層 31 よりも厚い状態である。

## 【0080】

また、半導体層 31 が所定の厚さに研削された後にホール蓄積層 45 やピニング層 46

10

20

30

40

50

、画素間分離部 5 1、平坦化層 3 4、オンチップレンズ 3 5などが形成されることから、これらの部位は図 7 の状態では形成されていない。

【 0 0 8 1 】

次に、図 8 に示すように、少なくともカソードコンタクト領域 4 4 が底面で露出するよう、反対面 3 1 b の表面に穴部 1 0 2 を公知の手法により形成する。かかる穴部 1 0 2 は、埋め込み層 4 8 に対応する位置に形成される。

【 0 0 8 2 】

次に、図 9 に示すように、公知の手法を用いて穴部 1 0 2 の内部を絶縁体で埋め込むことにより、埋め込み層 4 8 を形成する。なお、かかる埋め込み層 4 8 を形成することにより、P 型拡散層 1 0 1 がアノードコンタクト領域 4 7 と表面ピニング層 4 9 とに分離される。

10

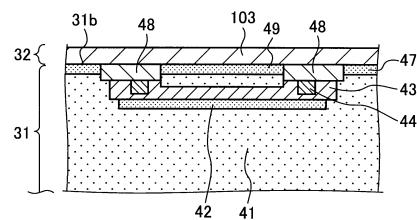

【 0 0 8 3 】

次に、図 1 0 に示すように、所定の厚さを有する絶縁層 1 0 3 を反対面 3 1 b の表面に公知の手法により形成する。なお、かかる絶縁層 1 0 3 は、センサ側配線層 3 2 の層間絶縁膜の一部に対応する部位である。

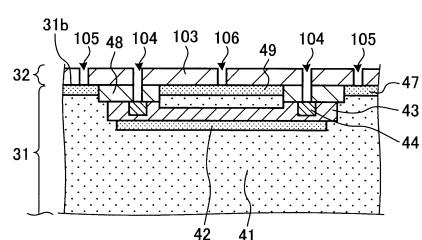

【 0 0 8 4 】

次に、図 1 1 に示すように、少なくともカソードコンタクト領域 4 4 が底面で露出するよう、絶縁層 1 0 3 の表面に穴部 1 0 4 を公知の手法により形成する。かかる穴部 1 0 4 は、カソード電極 6 1 に対応する位置に形成される。

20

【 0 0 8 5 】

また、少なくともアノードコンタクト領域 4 7 が底面で露出するよう、絶縁層 1 0 3 の表面に穴部 1 0 5 を公知の手法により形成する。かかる穴部 1 0 5 は、アノード電極 6 2 に対応する位置に形成される。

【 0 0 8 6 】

また、少なくとも表面ピニング層 4 9 が底面で露出するよう、絶縁層 1 0 3 の表面に穴部 1 0 6 を公知の手法により形成する。かかる穴部 1 0 6 は、コンタクト電極 6 3 に対応する位置に形成される。

【 0 0 8 7 】

次に、図 1 2 に示すように、公知の手法を用いて穴部 1 0 4 ~ 1 0 6 の内部を金属で埋め込むことにより、カソード電極 6 1、アノード電極 6 2 およびコンタクト電極 6 3 を形成する。

30

【 0 0 8 8 】

以降の工程としては、所望のセンサ側配線層 3 2 を公知の手法で形成するとともに、ロジック側基板にロジック側配線層 3 3 を公知の手法で形成する。そして、Cu - Cu 接合などの手法を用いて、センサ側配線層 3 2 とロジック側配線層 3 3 とを接合する。

【 0 0 8 9 】

次に、半導体層 3 1 のセンサ側配線層 3 2 とは反対側の面を公知の手法で所定の厚さに研削し、入射面 3 1 a を形成する。そして、半導体層 3 1 の入射面 3 1 a 側から、ホール蓄積層 4 5 やピニング層 4 6、画素間分離部 5 1 などを公知の手法で形成する。

【 0 0 9 0 】

最後に、半導体層 3 1 の入射面 3 1 a 側に平坦化層 3 4 とオンチップレンズ 3 5 とを形成して、実施形態に係る画素アレイ部 1 1 が完成する。

40

【 0 0 9 1 】

なお、実施形態に係る画素アレイ部 1 1 の製造工程は、上記の工程に限られない。たとえば、埋め込み層 4 8 と絶縁層 1 0 3 とが同じ材料でよい場合、埋め込み層 4 8 と絶縁層 1 0 3 とを同じ工程で形成してもよい。

【 0 0 9 2 】

また、図 9 に示した状態から、埋め込み層 4 8 にカソード電極 6 1 の一部を形成し、その後に絶縁層 1 0 3 を形成してもよい。

【 0 0 9 3 】

50

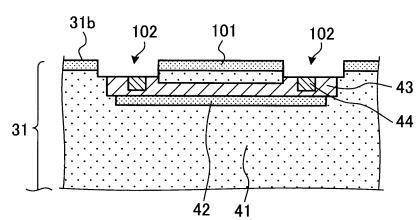

## [ 各種変形例 ]

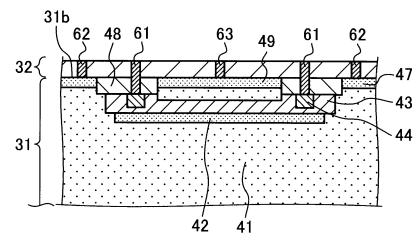

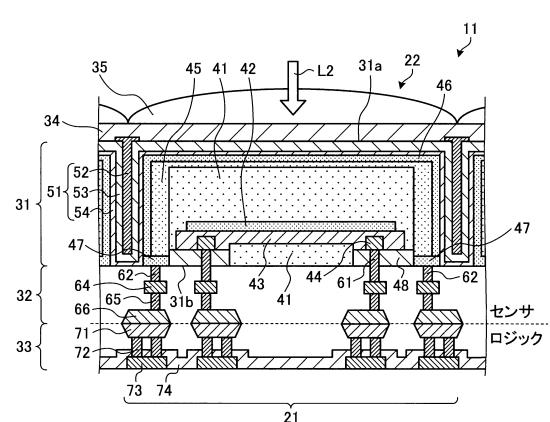

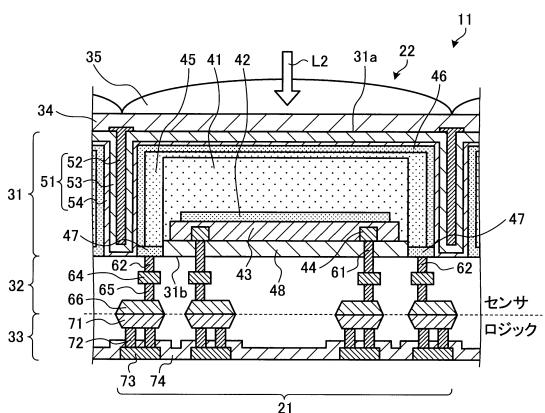

つづいて、実施形態の各種変形例について、図13～図15を参照しながら説明する。図13は、本開示の実施形態の変形例1に係る画素アレイ部11の構成例を示す断面図である。

## 【 0 0 9 4 】

上述の実施形態では、カソードコンタクト領域44と半導体層31の反対面31bとの間に埋め込み層48が設けられる例について示したが、アノードコンタクト領域47と半導体層31の反対面31bとの間に埋め込み層48が設けられてもよい。

## 【 0 0 9 5 】

たとえば、図13に示すように、カソードコンタクト領域44を半導体層31の反対面31bに接するように配置するととも、アノードコンタクト領域47と半導体層31の反対面31bとの間に埋め込み層48を配置する。

10

## 【 0 0 9 6 】

このような構成であっても、カソードコンタクト領域44とアノードコンタクト領域47との間を、水平方向のみならず垂直方向にも離間させながら絶縁分離することができる。したがって、画素アレイ部11の面積拡大を抑制しつつ、カソードコンタクト領域44とアノードコンタクト領域47との間の電界緩和を図ることができる。

## 【 0 0 9 7 】

図14は、本開示の実施形態の変形例2に係る画素アレイ部11の構成例を示す断面図である。図14に示すように、変形例2に係る画素アレイ部11は、半導体層31の反対面31b側に表面ピニング層49が設けられていない例である。

20

## 【 0 0 9 8 】

この変形例2では、半導体層31に表面ピニング層49が設けられていないことから、かかる表面ピニング層49を接地電位に接続する各種配線が不要となる。したがって、変形例2によれば、センサ側配線層32やロジック側配線層33の構成を簡素化することができることから、画素アレイ部11の製造コストを低減することができる。

## 【 0 0 9 9 】

図15は、本開示の実施形態の変形例3に係る画素アレイ部11の構成例を示す断面図である。図15に示すように、変形例3に係る画素アレイ部11は、N型拡散層43と半導体層31の反対面31bとの間が埋め込み層48で全体的に覆われている例である。

30

## 【 0 1 0 0 】

この変形例3でも、上述の変形例2と同様、半導体層31に表面ピニング層49が設けられていないことから、かかる表面ピニング層49を接地電位に接続する各種配線が不要となる。したがって、変形例3によれば、センサ側配線層32やロジック側配線層33の構成を簡素化することができることから、画素アレイ部11の製造コストを低減することができる。

## 【 0 1 0 1 】

## [ 効果 ]

実施形態に係る受光素子（画素アレイ部11）は、SPAD素子22と、カソード電極61およびアノード電極62と、カソードコンタクト領域44と、アノードコンタクト領域47と、埋め込み層48とを備える。SPAD素子22は、半導体層31に形成され、アレイ状に配置される複数の画素21ごとに設けられる。カソード電極61およびアノード電極62は、半導体層31に隣接する配線層（センサ側配線層32）に少なくとも一部が形成され、SPAD素子22に逆バイアス電圧を印加する。N型のカソードコンタクト領域44は、半導体層31に形成され、カソード電極61に直接接続される。P型のアノードコンタクト領域47は、半導体層31に形成され、アノード電極62に直接接続される。絶縁性の埋め込み層48は、カソードコンタクト領域44およびアノードコンタクト領域47のいずれか一方と、半導体層31の光入射側とは反対側の面（反対面31b）との間に位置する。

40

## 【 0 1 0 2 】

50

これにより、画素アレイ部 11 の面積拡大を抑制しつつ、カソードコンタクト領域 44 とアノードコンタクト領域 47 との間の電界緩和を図ることができる。

【0103】

また、実施形態に係る受光素子（画素アレイ部 11）は、半導体層 30 における光入射側とは反対側の面（反対面 31b）に形成され、接地電位に接続される表面ピニング層 49 をさらに備える。

【0104】

これにより、画素アレイ部 11 の暗時特性を向上させることができる。

【0105】

また、実施形態に係る受光素子（画素アレイ部 11）は、半導体層 31 においてカソードコンタクト領域 44 と接するN型拡散層 43 をさらに備える。そして、N型拡散層 43 と半導体層 31 の光入射側とは反対側の面（反対面 31b）との間が埋め込み層 48 で覆われる。

10

【0106】

これにより、画素アレイ部 11 の製造コストを低減することができる。

【0107】

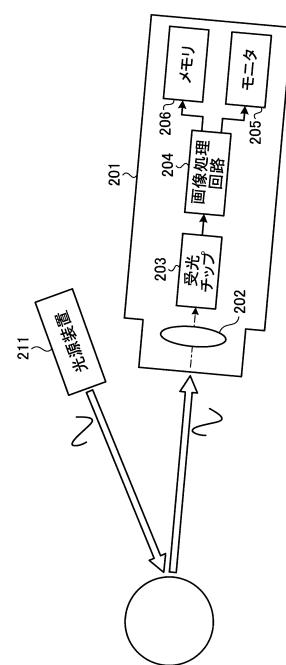

[電子機器]

図 16 は、受光チップ 3 を利用した電子機器である距離画像センサの構成例を示すブロック図である。

20

【0108】

図 16 に示すように、距離画像センサ 201 は、光学系 202 と、受光チップ 203 と、画像処理回路 204 と、モニタ 205 と、メモリ 206 とを備えて構成される。そして、距離画像センサ 201 は、光源装置 211 から被写体に向かって投光され、被写体の表面で反射された光（変調光やパルス光）を受光することにより、被写体までの距離に応じた距離画像を取得することができる。

【0109】

光学系 202 は、1枚または複数枚のレンズを有して構成され、被写体からの像光（入射光）を受光チップ 203 に導き、受光チップ 203 の画素アレイ部 11 に結像させる。

【0110】

受光チップ 203 としては、上述した各実施形態の受光チップ 3 が適用され、受光チップ 203 から出力される受光信号（A P D O U T）から求められる距離を示す距離信号が画像処理回路 204 に供給される。

30

【0111】

画像処理回路 204 は、受光チップ 203 から供給された距離信号に基づいて距離画像を構築する画像処理を行う。かかる画像処理回路 204 の画像処理により得られた距離画像（画像データ）は、モニタ 205 に供給されて表示されたり、メモリ 206 に供給されて記憶（記録）されたりする。

【0112】

このように構成される距離画像センサ 201 では、上述した受光チップ 3 を適用することで、画素アレイ部 11 の面積拡大を抑制しつつ、カソードコンタクト領域 44 とアノードコンタクト領域 47 との間の電界緩和が図られた受光チップ 3 を用いることができる。

40

【0113】

[移動体への応用例]

本開示に係る技術（本技術）は、様々な製品へ応用することができる。例えば、本開示に係る技術は、自動車、電気自動車、ハイブリッド電気自動車、自動二輪車、自転車、パーソナルモビリティ、飛行機、ドローン、船舶、ロボット等のいずれかの種類の移動体に搭載される装置として実現されてもよい。

【0114】

図 17 は、本開示に係る技術が適用され得る移動体制御システムの一例である車両制御システムの概略的な構成例を示すブロック図である。

50

## 【0115】

車両制御システム12000は、通信ネットワーク12001を介して接続された複数の電子制御ユニットを備える。図17に示した例では、車両制御システム12000は、駆動系制御ユニット12010、ボディ系制御ユニット12020、車外情報検出ユニット12030、車内情報検出ユニット12040、及び統合制御ユニット12050を備える。また、統合制御ユニット12050の機能構成として、マイクロコンピュータ12051、音声画像出力部12052、及び車載ネットワークI/F(Interface)12053が図示されている。

## 【0116】

駆動系制御ユニット12010は、各種プログラムにしたがって車両の駆動系に関連する装置の動作を制御する。例えば、駆動系制御ユニット12010は、内燃機関又は駆動用モータ等の車両の駆動力を発生させるための駆動力発生装置、駆動力を車輪に伝達するための駆動力伝達機構、車両の舵角を調節するステアリング機構、及び、車両の制動力を発生させる制動装置等の制御装置として機能する。

10

## 【0117】

ボディ系制御ユニット12020は、各種プログラムにしたがって車体に装備された各種装置の動作を制御する。例えば、ボディ系制御ユニット12020は、キーレスエントリーシステム、スマートキーシステム、パワーウィンドウ装置、あるいは、ヘッドライト、バックランプ、ブレーキランプ、ウィンカー又はフォグランプ等の各種ランプの制御装置として機能する。この場合、ボディ系制御ユニット12020には、鍵を代替する携帯機から発信される電波又は各種スイッチの信号が入力され得る。ボディ系制御ユニット12020は、これらの電波又は信号の入力を受け付け、車両のドアロック装置、パワーウィンドウ装置、ランプ等を制御する。

20

## 【0118】

車外情報検出ユニット12030は、車両制御システム12000を搭載した車両の外部の情報を検出する。例えば、車外情報検出ユニット12030には、撮像部12031が接続される。車外情報検出ユニット12030は、撮像部12031に車外の画像を撮像させるとともに、撮像された画像を受信する。車外情報検出ユニット12030は、受信した画像に基づいて、人、車、障害物、標識又は路面上の文字等の物体検出処理又は距離検出処理を行ってもよい。

30

## 【0119】

撮像部12031は、光を受光し、その光の受光量に応じた電気信号を出力する光センサである。撮像部12031は、電気信号を画像として出力することもできるし、測距の情報として出力することもできる。また、撮像部12031が受光する光は、可視光であっても良いし、赤外線等の非可視光であっても良い。

## 【0120】

車内情報検出ユニット12040は、車内の情報を検出する。車内情報検出ユニット12040には、例えば、運転者の状態を検出する運転者状態検出部12041が接続される。運転者状態検出部12041は、例えば運転者を撮像するカメラを含み、車内情報検出ユニット12040は、運転者状態検出部12041から入力される検出情報に基づいて、運転者の疲労度合い又は集中度合いを算出してもよいし、運転者が居眠りをしているかを判別してもよい。

40

## 【0121】

マイクロコンピュータ12051は、車外情報検出ユニット12030又は車内情報検出ユニット12040で取得される車内外の情報に基づいて、駆動力発生装置、ステアリング機構又は制動装置の制御目標値を演算し、駆動系制御ユニット12010に対して制御指令を出力することができる。例えば、マイクロコンピュータ12051は、車両の衝突回避あるいは衝撃緩和、車間距離に基づく追従走行、車速維持走行、車両の衝突警告、又は車両のレーン逸脱警告等を含むADAS(Advanced Driver Assistance System)の機能実現を目的とした協調制御を行うことができる。

50

**【0122】**

また、マイクロコンピュータ12051は、車外情報検出ユニット12030又は車内情報検出ユニット12040で取得される車両の周囲の情報に基づいて駆動力発生装置、ステアリング機構又は制動装置等を制御することにより、運転者の操作に拘らずに自律的に走行する自動運転等を目的とした協調制御を行うことができる。

**【0123】**

また、マイクロコンピュータ12051は、車外情報検出ユニット12030で取得される車外の情報に基づいて、ボディ系制御ユニット12020に対して制御指令を出力することができる。例えば、マイクロコンピュータ12051は、車外情報検出ユニット12030で検知した先行車又は対向車の位置に応じてヘッドライトを制御し、ハイビームをロービームに切り替える等の防眩を図ることを目的とした協調制御を行うことができる。10

**【0124】**

音声画像出力部12052は、車両の搭乗者又は車外に対して、視覚的又は聴覚的に情報を通知することが可能な出力装置へ音声及び画像のうちの少なくとも一方の出力信号を送信する。図17の例では、出力装置として、オーディオスピーカ12061、表示部12062及びインストルメントパネル12063が例示されている。表示部12062は、例えば、オンボードディスプレイ及びヘッドアップディスプレイの少なくとも一つを含んでいてもよい。

**【0125】**

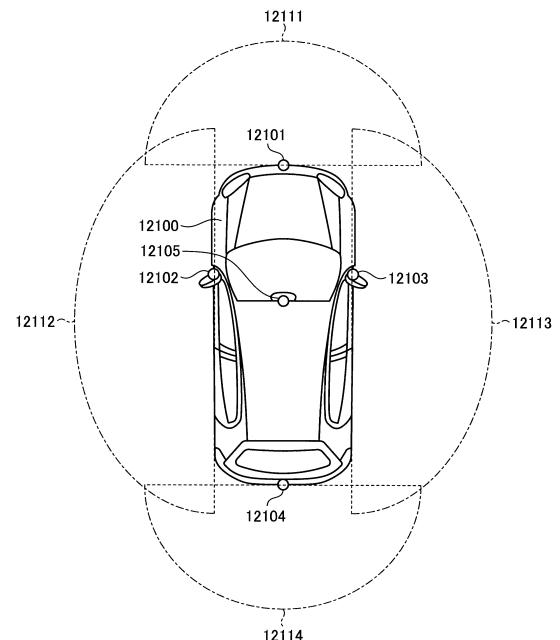

図18は、撮像部12031の設置位置の例を示す図である。20

**【0126】**

図18では、撮像部12031として、撮像部12101、12102、12103、12104、12105を有する。

**【0127】**

撮像部12101、12102、12103、12104、12105は、例えば、車両12100のフロントノーズ、サイドミラー、リアバンパ、バックドア及び車室内のフロントガラスの上部等の位置に設けられる。フロントノーズに備えられる撮像部12101及び車室内のフロントガラスの上部に備えられる撮像部12105は、主として車両12100の前方の画像を取得する。サイドミラーに備えられる撮像部12102、12103は、主として車両12100の側方の画像を取得する。リアバンパ又はバックドアに備えられる撮像部12104は、主として車両12100の後方の画像を取得する。車室内のフロントガラスの上部に備えられる撮像部12105は、主として先行車両又は、歩行者、障害物、信号機、交通標識又は車線等の検出に用いられる。30

**【0128】**

なお、図18には、撮像部12101ないし12104の撮影範囲の一例が示されている。撮像範囲12111は、フロントノーズに設けられた撮像部12101の撮像範囲を示し、撮像範囲12112、12113は、それぞれサイドミラーに設けられた撮像部12102、12103の撮像範囲を示し、撮像範囲12114は、リアバンパ又はバックドアに設けられた撮像部12104の撮像範囲を示す。例えば、撮像部12101ないし12104で撮像された画像データが重ね合わせられることにより、車両12100を上方から見た俯瞰画像が得られる。40

**【0129】**

撮像部12101ないし12104の少なくとも1つは、距離情報を取得する機能を有していてもよい。例えば、撮像部12101ないし12104の少なくとも1つは、複数の撮像素子からなるステレオカメラであってもよいし、位相差検出用の画素を有する撮像素子であってもよい。

**【0130】**

例えば、マイクロコンピュータ12051は、撮像部12101ないし12104から得られた距離情報を基に、撮像範囲12111ないし12114内における各立体物までの距離と、この距離の時間的变化（車両12100に対する相対速度）を求めるこによ50

り、特に車両 12100 の進行路上にある最も近い立体物で、車両 12100 と略同じ方向に所定の速度（例えば、0 km/h 以上）で走行する立体物を先行車として抽出することができる。さらに、マイクロコンピュータ 12051 は、先行車の手前に予め確保すべき車間距離を設定し、自動ブレーキ制御（追従停止制御も含む）や自動加速制御（追従発進制御も含む）等を行うことができる。このように運転者の操作に拘らずに自律的に走行する自動運転等を目的とした協調制御を行うことができる。

#### 【0131】

例えば、マイクロコンピュータ 12051 は、撮像部 12101 ないし 12104 から得られた距離情報を元に、立体物に関する立体物データを、2輪車、普通車両、大型車両、歩行者、電柱等その他の立体物に分類して抽出し、障害物の自動回避に用いることができる。例えば、マイクロコンピュータ 12051 は、車両 12100 の周辺の障害物を、車両 12100 のドライバが視認可能な障害物と視認困難な障害物とに識別する。そして、マイクロコンピュータ 12051 は、各障害物との衝突の危険度を示す衝突リスクを判断し、衝突リスクが設定値以上で衝突可能性がある状況であるときには、オーディオスピーカ 12061 や表示部 12062 を介してドライバに警報を出力することや、駆動系制御ユニット 12010 を介して強制減速や回避操舵を行うことで、衝突回避のための運転支援を行うことができる。

#### 【0132】

撮像部 12101 ないし 12104 の少なくとも 1 つは、赤外線を検出する赤外線カメラであってもよい。例えば、マイクロコンピュータ 12051 は、撮像部 12101 ないし 12104 の撮像画像中に歩行者が存在するか否かを判定することで歩行者を認識することができる。かかる歩行者の認識は、例えば赤外線カメラとしての撮像部 12101 ないし 12104 の撮像画像における特徴点を抽出する手順と、物体の輪郭を示す一連の特徴点にパターンマッチング処理を行って歩行者か否かを判別する手順によって行われる。マイクロコンピュータ 12051 が、撮像部 12101 ないし 12104 の撮像画像中に歩行者が存在すると判定し、歩行者を認識すると、音声画像出力部 12052 は、当該認識された歩行者に強調のための方形輪郭線を重畠表示するように、表示部 12062 を制御する。また、音声画像出力部 12052 は、歩行者を示すアイコン等を所望の位置に表示するように表示部 12062 を制御してもよい。

#### 【0133】

以上、本開示に係る技術が適用され得る車両制御システムの一例について説明した。本開示に係る技術は、以上説明した構成のうち、撮像部 12031 に適用され得る。具体的には、図 1 の測距装置 1 は、撮像部 12031 に適用することができる。撮像部 12031 に本開示に係る技術を適用することにより、画素アレイ部 11 の面積拡大を抑制しつつ、カソードコンタクト領域 44 とアノードコンタクト領域 47 との間の電界緩和が図られた受光チップ 3 を用いることができる。

#### 【0134】

以上、本開示の実施形態について説明したが、本開示の技術的範囲は、上述の実施形態そのままに限定されるものではなく、本開示の要旨を逸脱しない範囲において種々の変更が可能である。また、異なる実施形態及び変形例にわたる構成要素を適宜組み合わせてもよい。

#### 【0135】

たとえば、上述の実施形態に示した画素アレイ部 11 の素子構造において、P 型の導電型と N 型の導電型とを入れ替えた素子構造を実施形態として用いてもよい。

#### 【0136】

また、本明細書に記載された効果はあくまで例示であって限定されるものではなく、また他の効果があってもよい。

#### 【0137】

なお、本技術は以下のような構成も取ることができる。

半導体層に形成され、アレイ状に配置される複数の画素ごとに設けられる S P A D ( Single Photon Avalanche Diode ) 素子と、

前記半導体層に隣接する配線層に少なくとも一部が形成され、前記 S P A D 素子に逆バイアス電圧を印加するカソード電極およびアノード電極と、

前記半導体層に形成され、前記カソード電極に直接接続される N 型のカソードコンタクト領域と、

前記半導体層に形成され、前記アノード電極に直接接続される P 型のアノードコンタクト領域と、

前記カソードコンタクト領域および前記アノードコンタクト領域のいずれか一方と、前記半導体層の光入射側とは反対側の面との間に位置する絶縁性の埋め込み層と、

を備える受光素子。

( 2 )

前記半導体層における光入射側とは反対側の面に形成され、接地電位に接続される表面ピニング層をさらに備える

前記 ( 1 ) に記載の受光素子。

( 3 )

前記半導体層において前記カソードコンタクト領域と接する N 型拡散層をさらに備え、

前記 N 型拡散層と前記半導体層の光入射側とは反対側の面との間が前記埋め込み層で覆われる

前記 ( 1 ) に記載の受光素子。

20

( 4 )

半導体層に形成され、アレイ状に配置される複数の画素ごとに設けられる S P A D ( Single Photon Avalanche Diode ) 素子と、

前記半導体層に隣接する配線層に少なくとも一部が形成され、前記 S P A D 素子に逆バイアス電圧を印加するカソード電極およびアノード電極と、

前記半導体層に形成され、前記カソード電極に直接接続される N 型のカソードコンタクト領域と、

前記半導体層に形成され、前記アノード電極に直接接続される P 型のアノードコンタクト領域と、

前記カソードコンタクト領域および前記アノードコンタクト領域のいずれか一方と、前記半導体層の光入射側とは反対側の面との間に位置する絶縁性の埋め込み層と、

30

を備える受光素子を備える

電子機器。

( 5 )

前記受光素子は、前記半導体層における光入射側とは反対側の面に形成され、接地電位に接続される表面ピニング層をさらに備える

前記 ( 4 ) に記載の電子機器。

( 6 )

前記受光素子は、前記半導体層において前記カソードコンタクト領域と接する N 型拡散層をさらに備え、

40

前記 N 型拡散層と前記半導体層の光入射側とは反対側の面との間が前記埋め込み層で覆われる

前記 ( 4 ) に記載の電子機器。

【符号の説明】

【 0 1 3 8 】

1 測距装置

3 受光チップ

1 1 画素アレイ部 ( 受光素子の一例 )

2 1 画素

2 2 S P A D 素子

50

- 3 1 半導体層

3 1 a 入射面

3 1 b 反対面

3 2 センサ側配線層（配線層の一例）

4 3 N型拡散層

4 4 カソードコンタクト領域

4 7 アノードコンタクト領域

4 8 埋め込み層

4 9 表面ピニング層

6 1 カソード電極

6 2 アノード電極

【図面】

【図1】

【図2】

10

20

30

40

50

【 义 3 】

【 図 4 】

【 5 】

【 図 6 】

10

20

30

40

50

【図 7】

【図 8】

10

【図 9】

【図 10】

20

【図 11】

【図 12】

30

40

50

【図 1 3】

【図 1 4】

10

20

【図 1 5】

【図 1 6】

30

40

50

【図17】

【図18】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 米国特許第10204950(US, B1)

特開2019-033136(JP, A)

米国特許出願公開第2017/0186798(US, A1)

国際公開第2018/174090(WO, A1)

- (58)調査した分野 (Int.Cl., DB名)

- H01L 31/08 - 31/119

H01L 27/146 - 27/148