(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-96036

(P2007-96036A)

(43) 公開日 平成19年4月12日(2007.4.12)

(51) Int.CI.

F 1

テーマコード(参考)

|        |         |           |

|--------|---------|-----------|

| HO 1 L | 21/822  | (2006.01) |

| HO 1 L | 27/04   | (2006.01) |

| HO 1 L | 21/8234 | (2006.01) |

| HO 1 L | 27/06   | (2006.01) |

| HO 3 K | 5/02    | (2006.01) |

|        |       |

|--------|-------|

| HO 1 L | 27/04 |

| HO 1 L | 27/06 |

| HO 1 L | 27/04 |

| HO 3 K | 5/02  |

|         |

|---------|

| G       |

| 1 O 2 A |

| C       |

| C       |

|           |

|-----------|

| 5 F 0 3 8 |

| 5 F 0 4 8 |

| 5 J 0 3 9 |

審査請求 未請求 請求項の数 9 O L (全 12 頁)

(21) 出願番号

特願2005-284153 (P2005-284153)

(22) 出願日

平成17年9月29日 (2005.9.29)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100094134

弁理士 小山 廣毅

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】昇圧回路

## (57) 【要約】

【課題】レイアウトの小面積化を実現する標準CMOSプロセスのLSIに混載可能な昇圧回路を提供する。

【解決手段】各段がMOSトランジスタ(M04、M14、M24、M34)と、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタ(C14、C24a、C24b、C34a、C34b、C34c)とからなり、前記MOSトランジスタが縦列接続されることによって各段が接続され、各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続される。バックバイアス効果が抑制され、かつレイアウト面積を縮小することができる。また、後段の昇圧キャパシタを複数の直列キャパシタで構成することにより、各キャパシタの耐圧劣化を抑制することができる。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

各段がMOSトランジスタと、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、前記MOSトランジスタが縦列接続されることによって各段が接続されており、

各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続されていることを特徴とする昇圧回路。

**【請求項 2】**

請求項1記載の昇圧回路において、

連続する2段の前記キャパシタの他端に逆位相の1対のクロック信号が入力されることを特徴とする昇圧回路。

**【請求項 3】**

請求項1記載の昇圧回路において、

前記MOSトランジスタがN型ウェル領域に形成されたPMOSトランジスタであることを特徴とする昇圧回路。

**【請求項 4】**

請求項1記載の昇圧回路において、

前記MOSトランジスタがP型ウェル領域に形成されたNMOSトランジスタであることを特徴とする昇圧回路。

**【請求項 5】**

請求項1記載の昇圧回路において、

少なくとも1つの段のキャパシタは複数の直列接続されたキャパシタからなることを特徴とする昇圧回路。

**【請求項 6】**

各段がMOSトランジスタと、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、少なくとも1つの段のキャパシタは複数の直列接続されたキャパシタからなることを特徴とする昇圧回路。

**【請求項 7】**

請求項6記載の昇圧回路において、

前記キャパシタがN型のデプレッションMOSトランジスタで構成されたことを特徴とする昇圧回路。

**【請求項 8】**

請求項6記載の昇圧回路において、

前記キャパシタがPMOSトランジスタで構成されたことを特徴とする昇圧回路。

**【請求項 9】**

請求項1又は6に記載の昇圧回路において、

各段がLSIの入出力回路を形成するMOSトランジスタと同一のプロセスで製造するMOSトランジスタで構成されたことを特徴とする昇圧回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、シリコン基板上に形成される昇圧回路に関し、更に詳しくは標準CMOSプロセスのLSIに混載可能な昇圧回路に関するものである。

**【背景技術】****【0002】**

シリコン基板上に形成可能なコッククロフト・ウォルトン(Cockcroft-Walton)型の昇圧回路が、1976年の論文に掲載された。これは、ドレインとゲートとを接続した駆動MOSトランジスタと、キャパシタとで各段の昇圧セルを構成し、2相のクロック信号に

10

20

30

40

50

応じて順次次段の昇圧セルに前段の電圧を重畠してゆき、最終段の昇圧セルで所望の電圧を得るものである（非特許文献1参照）。

#### 【0003】

上記コッククロフト・ウォルトン型の昇圧回路では、昇圧電位が大きくなるにつれ、バックバイアス効果の影響が大きくなり、駆動トランジスタの閾値電圧が上昇し、それゆえ昇圧効率が低下するという問題があった。

#### 【0004】

そこで、ある従来技術によれば、バックバイアス効果の影響を小さくするため、P型シリコン基板上において各駆動PMOSトランジスタを形成するN型ウェル領域を互いに電気的に分離し、かつ各段にて基板電位を各駆動PMOSトランジスタのソース電位に固定することとした（特許文献1参照）。

#### 【0005】

他の従来技術によれば、P型シリコン基板上にトリプルウェル構造を採用し、バックバイアス効果の影響を小さくするため、各駆動NMOSトランジスタを形成するP型ウェル領域を互いに電気的に分離し、かつ各段にて基板電位を各駆動NMOSトランジスタのドレイン電位に固定することとした。また、4相クロック信号タイプの昇圧回路も紹介されている（特許文献2参照）。

【非特許文献1】J. F. Dickson, "On-Chip High-Voltage Generation in MNOS Integrated Circuits Using an Improved Voltage Multiplier Technique," IEEE J. Solid-State Circuits, Vol. SC-11, No. 3, pp. 374-378, June 1976.

【特許文献1】特開平7-298607号公報

【特許文献2】特開平11-283392号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

さて、フラッシュメモリ、EEPROM等の不揮発性半導体記憶装置においては、信号の書き込みや消去時に電源電圧よりも高い電圧を必要とする。フラッシュメモリの場合、昇圧回路には高バイアス対策用の高耐圧トランジスタを専用プロセスで用いることができる。ところが、先端標準CMOSプロセスのLSIに昇圧回路を搭載する際、専用プロセスの高耐圧トランジスタを用いることができない。したがって、昇圧回路のキャパシタを1つのMOSトランジスタで構成すると、ゲートと基板との間に高電圧が印加され、経時絶縁破壊（Time Dependent Dielectric Breakdown: TDDDB）によりキャパシタの耐圧が保証できない等の問題が生じ、先端標準CMOSプロセスのLSIに昇圧回路を搭載することが難しい。

#### 【0007】

また、上記のようにバックバイアス効果の対策として各駆動MOSトランジスタを形成するウェル領域を互いに電気的に分離することとすると、各段間で分離層が必要となるため、昇圧回路のレイアウト面積が増加する等の問題が生じる。

#### 【課題を解決するための手段】

#### 【0008】

本発明によれば、各段がMOSトランジスタと、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、前記MOSトランジスタが縦列接続されることによって各段が接続されており、各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続されていることを特徴とする昇圧回路が提供される。

#### 【0009】

上記構成の昇圧回路によれば、少なくとも1組の隣接する駆動MOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続されているため、バックバイアス効果が抑制され、昇圧効率の低下を抑制することができる。しかも、少なくとも1組の

10

20

30

40

50

隣接するMOSトランジスタの基板が共通であることにより基板分離領域を削減することができ、レイアウト面積を縮小することができる。

#### 【0010】

また、本発明によれば、昇圧回路の各段にてキャパシタを直列接続することで、各キャパシタの両端に印加される電圧を分圧し、キャパシタの耐圧劣化を抑制することができるため、先端標準CMOSプロセスのLSIに昇圧回路を搭載することができる。

#### 【発明の効果】

#### 【0011】

請求項1、2に記載の発明は、各段がMOSトランジスタと、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、前記MOSトランジスタが縦列接続されることによって各段が接続されており、各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続されていることを特徴とする昇圧回路であって、MOSトランジスタのバックバイアス効果を緩和し、昇圧効率の劣化を抑制し、かつレイアウト面積を縮小することができるという効果を有する。10

#### 【0012】

請求項3に記載の発明は前記MOSトランジスタがN型ウェル領域に形成されたPMOSトランジスタであることを特徴とする請求項1に記載の昇圧回路であり、請求項4に記載の発明は前記MOSトランジスタがP型ウェル領域に形成されたNMOSトランジスタであることを特徴とする請求項1に記載の昇圧回路であって、駆動MOSトランジスタをウェル上に形成することで、駆動MOSトランジスタの基板を隣接する駆動MOSトランジスタで共通にすることが可能となり、MOSトランジスタのバックバイアス効果を緩和し、昇圧効率の劣化を抑制し、かつレイアウト面積を縮小することができるという効果を有する。20

#### 【0013】

請求項5に記載の発明は、少なくとも1つの段のキャパシタは複数の直列接続されたキャパシタからなることを特徴とする請求項1に記載の昇圧回路であって、各キャパシタの両端に印加される電圧を分圧し、キャパシタの耐圧劣化を抑制できるという効果を有する。30

#### 【0014】

請求項6に記載の発明は、各段がMOSトランジスタと、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、少なくとも1つの段のキャパシタは複数の直列接続されたキャパシタからなることを特徴とする昇圧回路であって、各キャパシタの両端に印加される電圧を分圧し、キャパシタの耐圧劣化を抑制できるという効果を有する。

#### 【0015】

請求項7に記載の発明は前記キャパシタがN型のデプレッション(Depletion)MOSトランジスタで構成されたことを特徴とする請求項6に記載の昇圧回路であり、請求項8に記載の発明は前記キャパシタがPMOSトランジスタで構成されたことを特徴とする請求項6に記載の昇圧回路であって、ウェル分離が可能なのでキャパシタを複数直列接続することが可能であり、キャパシタの耐圧劣化を抑制できるという効果を有する。40

#### 【0016】

請求項9に記載の発明は、各段がLSIの入出力回路を形成するMOSトランジスタと同一のプロセスで製造するMOSトランジスタで構成されたことを特徴とする請求項1又は6に記載の昇圧回路であって、先端標準CMOSプロセスのLSIに混載可能な昇圧回路を実現するという効果を有する。

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、本発明の実施形態について図面を用いながら説明する。

10

20

30

40

50

## 【0018】

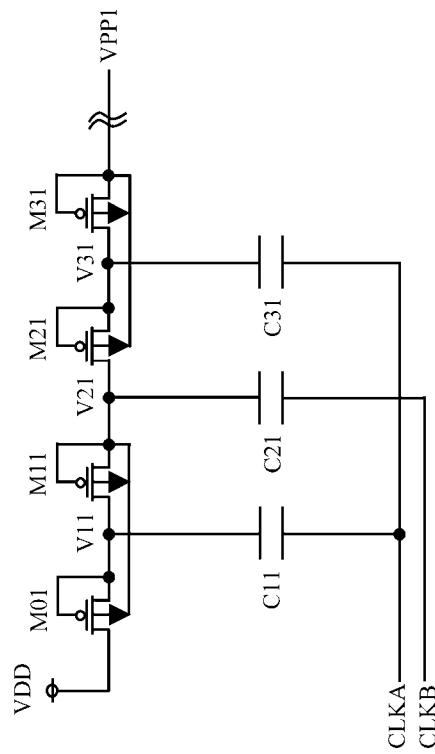

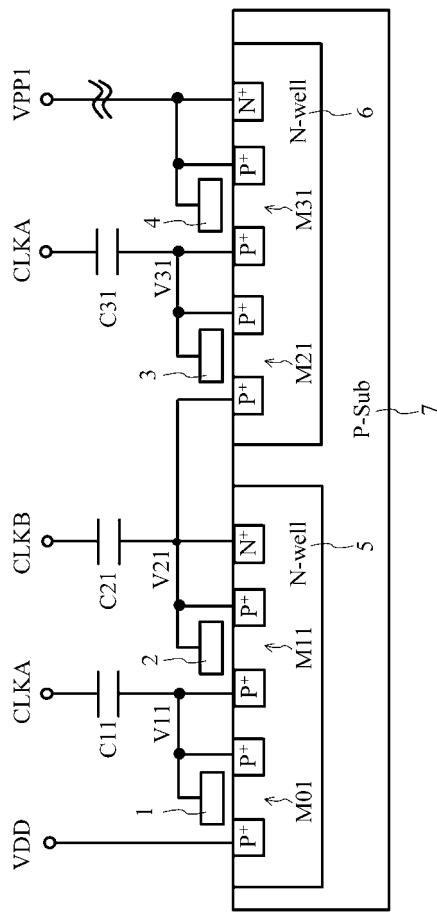

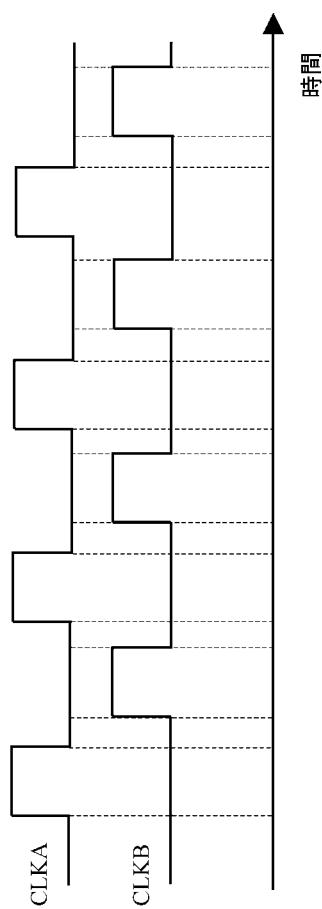

図1は、本発明の実施形態1における昇圧回路の構成を示す回路図である。図2は、本発明の実施形態1における昇圧回路の素子構造を示す断面図である。1～4はゲート、5、6はN型ウェル領域、7はP型シリコン基板である。図2に示されるように、N型ウェル領域上に形成されたPMOSトランジスタを利用して昇圧回路を構成している。2相クロック信号タイプの昇圧回路であり、キャパシタCp(C11、C21、C31)と駆動トランジスタM(M01、M11、M21、M31)とで構成され、それを駆動するためのクロック信号CLKAとそのCLKAを反転した反転クロック信号CLKBとがキャパシタの一端に印加される。ここでは、駆動トランジスタはPMOSトランジスタ(M01、M11、M21、M31)の4つ、キャパシタ(C11、C21、C31)が3段の場合を示している。駆動トランジスタM01、M11、M21、M31を直列に接続し、そのトランジスタ間の拡散層に昇圧用のキャパシタCpの一端を接続し、その他端にクロック信号が印加される。クロック信号は図3に示すCLKAとCLKBの2相の組み合わせで印加される。駆動トランジスタ(M01、M11、M21、M31)はドレインとゲートとを接続したMOS構成である。この昇圧回路では、クロック信号CLKAとCLKBとに応じて順次次段の昇圧セルに前段の電圧を重畠して昇圧され、最終段の昇圧セルで所望の電圧を得ることができる。

## 【0019】

次に昇圧電圧について述べる。図1において駆動トランジスタ(M01、M11、M21、M31)の閾値電圧をそれぞれVt0、Vt1、Vt2、Vt3とする。電源電圧をVDDとし、キャパシタに印加するクロック信号の電圧振幅をVDDとする。昇圧動作に入ると、ノードV11には(VDD - Vt0 + VDD)の電位が、ノードV21には(VDD - Vt0 + VDD - Vt1 + VDD)の電位が、ノードV31には(VDD - Vt0 + VDD - Vt1 + VDD - Vt2 + VDD)の電位が与えられ、最終駆動トランジスタM31のドレイン電位である昇圧電圧VPP1は、

$$V_{PP1} = (VDD - Vt0) + VDD \times 3 - (Vt1 + Vt2 + Vt3)$$

の電位まで昇圧される。

## 【0020】

駆動トランジスタがn段の場合、n段目の駆動トランジスタのドレイン電位である昇圧電圧VPP1は、

$$V_{PP1} = (VDD - Vt0) + VDD \times n - (Vt1 + Vt2 + Vt3 + \dots + Vtn)$$

の電位まで昇圧される。

## 【0021】

図6xは、従来技術2の昇圧回路(キャパシタをN型のデプレッションMOS(DMOS)で構成した場合)のレイアウト図を示す。

## 【0022】

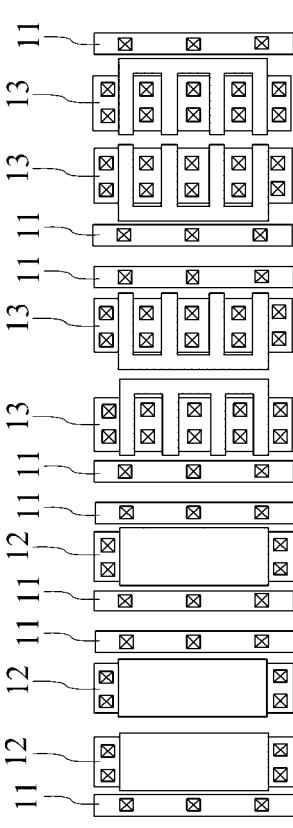

図4は、本発明の実施形態1における図1の昇圧回路においてキャパシタをN型のデプレッションMOS(DMOS)で構成した場合のレイアウト図である。ここで、11は駆動PMOSトランジスタのウェル電位を与えるウェルコンタクト領域、12はN型DMOSのキャパシタ、13は駆動PMOSトランジスタである。本発明の昇圧回路では、駆動PMOSトランジスタM01とM11、M21とM31のウェルコンタクト領域を共通化することができるのでレイアウト面積を縮小することができる。

## 【0023】

以上のとおり、本発明の実施形態1における昇圧回路は、各段がPMOSトランジスタと、前記PMOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタとからなり、前記PMOSトランジスタが縦列接続されることによって各段が接続されており、各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するPMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続されているため、昇圧電位が

10

20

30

40

50

大きくなってもバックバイアス効果の影響を小さくし、駆動トランジスタの閾値電圧上昇を抑制することができる。したがって、図1に示される本発明の昇圧回路は昇圧効率が劣化しない。また、この昇圧回路は少なくとも1組の隣接するPMOSトランジスタの基板が共通であることにより基板分離領域（ウェル分離）を削減することができるので、レイアウト面積を縮小することができる。

#### 【0024】

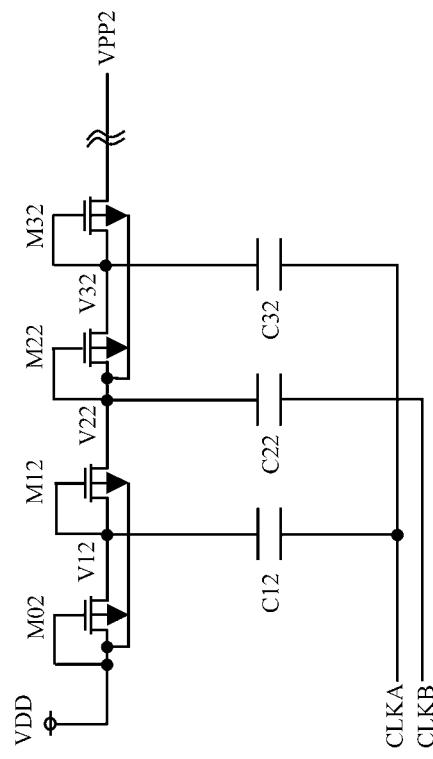

図5は、本発明の実施形態2における昇圧回路の構成を示す回路図である。図6は、本発明の実施形態2における昇圧回路の素子構造を示す断面図である。ここで、14、15、16、17はゲート、18、20はP型ウェル領域、19、21はN型ウェル領域、22はP型シリコン基板である。図6に示されるように、トリプルウェル（N型ウェル上のP型ウェル）上に形成されたNMOSトランジスタを利用して昇圧回路を構成している。本発明の昇圧回路において、駆動MOSトランジスタ（M02、M12、M22、M32）にNMOSを用いる場合には、トリプルウェルプロセスが必要となる。2相クロック信号タイプの昇圧回路であり、キャパシタCp（C12、C22、C32）と駆動トランジスタM（M02、M12、M22、M32）とで構成され、それを駆動するためのクロック信号CLKAとそのCLKAを反転した反転クロック信号CLKBとがキャパシタの一端に印加される。ここでは、駆動トランジスタがM02、M12、M22、M32の4つ、キャパシタが3段の場合を示している。駆動トランジスタ（M02、M12、M22、M32）を直列に接続し、そのトランジスタ間の拡散層に昇圧用のキャパシタCpの一端を接続し、その他端にクロック信号が印加される。図3に示されるように、クロック信号はCLKAとCLKBの2相の組み合わせで印加される。駆動トランジスタ（M02、M12、M22、M32）はドレインとゲートとを接続したMOS構成である。

#### 【0025】

この昇圧回路では、クロック信号CLKAとCLKBに応じて順次次段の昇圧セルに前段の電圧を重畠して昇圧され、n段目の昇圧セルで所望の電圧を得ることができる。

#### 【0026】

図1に示される実施形態1の昇圧回路と同じ構成であり、各段がNMOSトランジスタと、前記NMOSトランジスタのソースに一端が接続されたキャパシタとからなり、前記NMOSトランジスタ（M02、M12、M22、M32）が縦列接続されることによって各段が接続されており、各段における前記NMOSトランジスタ（M02、M12、M22、M32）のゲートヒドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するNMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続されているため、昇圧電位が大きくなてもバックバイアス効果の影響を小さくし、駆動NMOSトランジスタ（M02、M12、M22、M32）の閾値電圧の上昇を抑制することができる。したがって、図5に示される本発明の実施形態2における昇圧回路は昇圧効率が劣化しない。また、この昇圧回路は少なくとも1組の隣接するNMOSトランジスタ（M02、M12、M22、M32）の基板が共通であることにより基板分離領域を削減することができるので、レイアウト面積を縮小することができる。

#### 【0027】

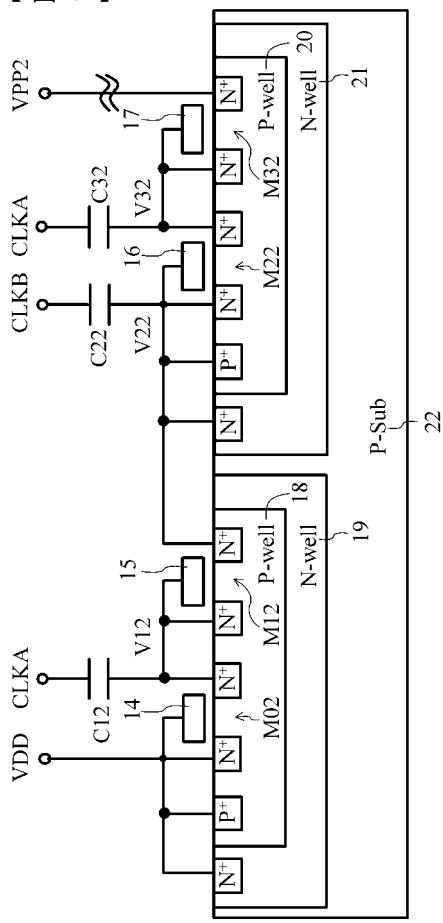

図7は、本発明の実施形態3における昇圧回路の構成を示す回路図である。各段がPMOSトランジスタ（M03、M13、M23、M33）と、前記PMOSトランジスタ（M03、M13、M23、M33）のドレイン又はソースの一方に一端が接続されたキャパシタとからなり、1段目のキャパシタC13は1つ、2段目のキャパシタは2つのキャパシタC23a、C23bの直列接続、3段目のキャパシタは3つのキャパシタC33a、C33b、C33cの直列接続により構成されることを特徴とする昇圧回路である。

#### 【0028】

上述したように、昇圧動作に入ると、ノードV13には（VDD - Vt0 + VDD）の電位が、ノードV23には（VDD - Vt0 + VDD - Vt1 + VDD）の電位が与えられる。ノードV33には（VDD - Vt0 + VDD - Vt1 + VDD - Vt2 + VDD）

10

20

30

40

50

の電位が与えられる。後段のノードほど高電圧になるため、ここでは1段目のキャパシタC13は1つ、2段目のキャパシタは2つのキャパシタC23a、C23bの直列接続、3段目のキャパシタは3つのキャパシタC33a、C33b、C33cの直列接続により、各キャパシタの両端に印加される電圧を分圧し、キャパシタの耐圧を抑制することができる。各段におけるキャパシタの直列接続数は、各段のノードに印加される最大電圧及びキャパシタのTDDDB特性等を考慮して決める。以上のようなキャパシタ構成にすることで、先端CMOS標準プロセスで追加のマスク無くキャパシタの耐圧劣化を抑制し、昇圧回路を搭載することが可能になる。

#### 【0029】

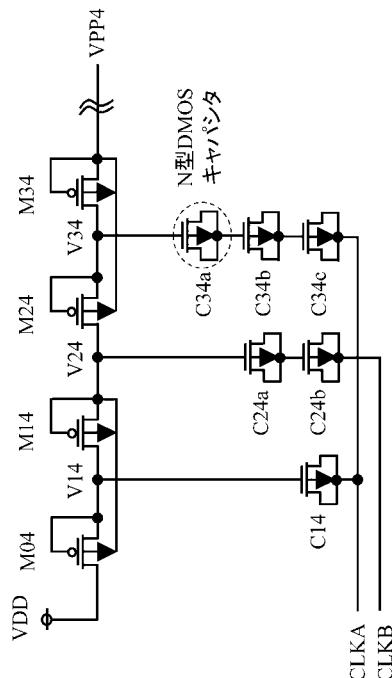

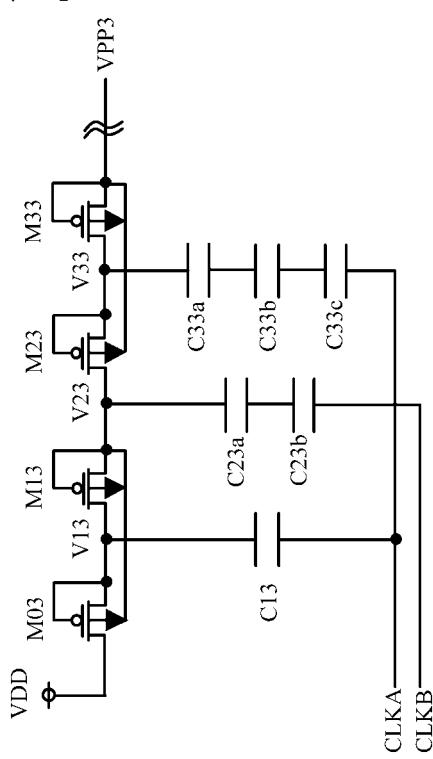

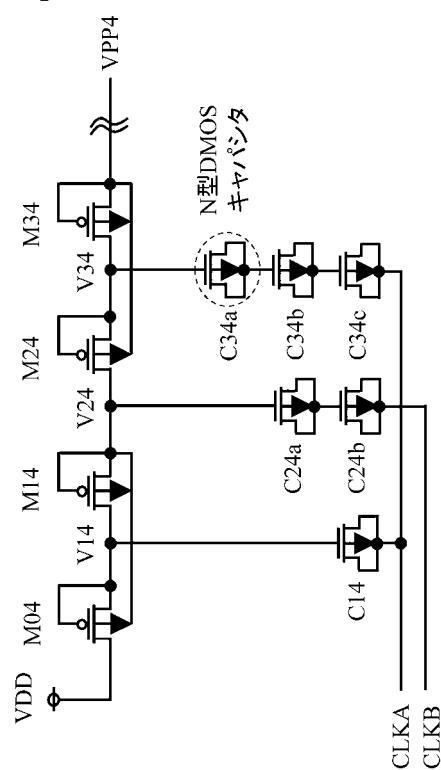

図8は、本発明の実施形態4における昇圧回路の構成を示す回路図である。この昇圧回路のキャパシタ(C14、C24a、C24b、C34a、C34b、C34c)はN型のDMOSキャパシタで構成され、1段目はN型DMOSキャパシタC14、2段目はN型DMOSキャパシタC24a及びC24b、3段目はN型DMOSキャパシタC34a、C34b及びC34cからなる。キャパシタにN型DMOSキャパシタを用いる場合、図8に示されるようにN型DMOSキャパシタのゲートを高電圧側であるV14、V24、V34に、N型ウェルを低電圧側(CLKA、CLKB)に接続することで安定したチャネル反転容量が得られる。

#### 【0030】

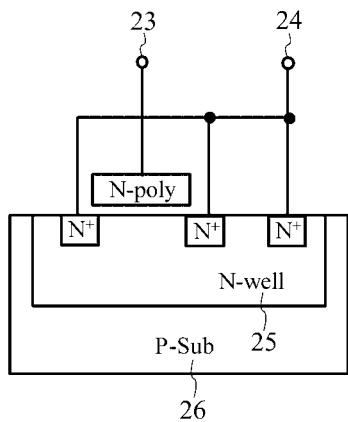

図9は、本発明の実施形態4における昇圧回路に用いるN型DMOSキャパシタの断面図である。23はN型DMOSキャパシタのゲート端子、24はN型DMOSキャパシタのN型ウェル(拡散層)端子、25はN型ウェル領域、26はP型シリコン基板である。

#### 【0031】

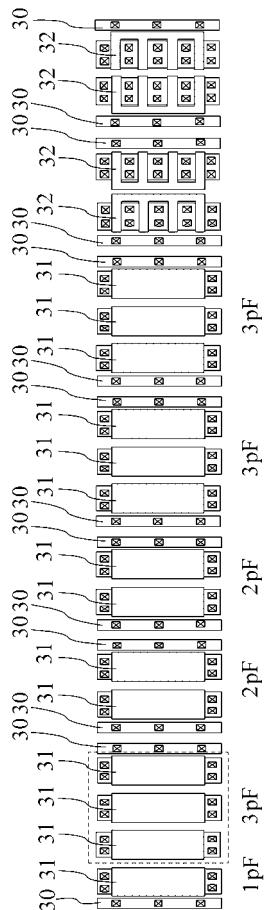

図10は、N型DMOSキャパシタを用いた本発明の実施形態4における昇圧回路のレイアウト図である。ここに、30はウェルコンタクト領域、31はキャパシタ、32は駆動MOSトランジスタである。昇圧キャパシタの値は1pFで、図8においてC14は1pF、C24aとC24bは2pF、C34aとC34bとC34cは3pFである。図8に示される本発明の昇圧回路では駆動PMOSトランジスタ(M04、M14、M24、M34)のウェルが共通に接続されているため、ウェル分離領域を削減することができるので、昇圧回路のレイアウト面積を縮小することができる。

#### 【0032】

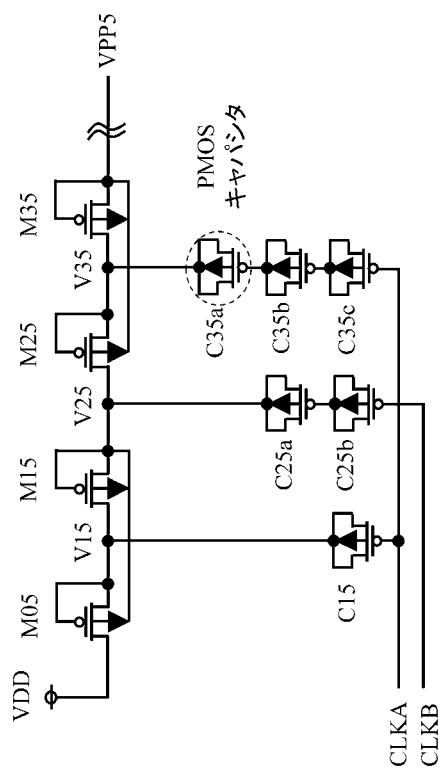

図11は、本発明の実施形態5における昇圧回路の構成を示す回路図である。この昇圧回路のキャパシタはPMOSキャパシタ(C15、C25a、C25b、C35a、C35b、C35c)で構成され、1段目はPMOSキャパシタC15、2段目はPMOSキャパシタC25a及びC25b、3段目はPMOSキャパシタC35a、C35b及びC35cからなる。昇圧キャパシタにPMOSキャパシタを用いる場合、図11に示されるようにPMOSキャパシタのゲートを低電圧側(CLKA、CLKB)に、N型ウェルを高電圧側(V15、V25、V35)に接続することで安定したチャネル反転容量が得られる。

#### 【0033】

なお、上記各実施形態において、LSIの入出力回路を形成するMOSトランジスタと同一のプロセスで製造するMOSトランジスタで各段を構成すれば、先端標準CMOSプロセスのLSIに混載可能な昇圧回路を実現できる。

#### 【産業上の利用可能性】

#### 【0034】

本発明に係る昇圧回路は、標準CMOSプロセスのLSIにおける不揮発性メモリの内蔵昇圧回路として有用である。

#### 【図面の簡単な説明】

#### 【0035】

【図1】本発明の実施形態1における昇圧回路の構成を示す回路図である。

【図2】本発明の実施形態1における昇圧回路の素子構造を示す断面図である。

10

20

30

40

50

【図3】本発明の実施形態1における昇圧回路のクロック信号タイミングを示す図である。

【図4】本発明の実施形態1における昇圧回路（N型DMOSキャパシタ）のレイアウト図である。

【図5】本発明の実施形態2における昇圧回路の構成を示す回路図である。

【図6】本発明の実施形態2における昇圧回路の素子構造を示す断面図である。

【図7】本発明の実施形態3における昇圧回路の構成を示す回路図である。

【図8】本発明の実施形態4における昇圧回路の構成を示す回路図である。

【図9】本発明の実施形態4における昇圧回路のN型DMOSキャパシタの断面図である。

【図10】本発明の実施形態4における昇圧回路（N型DMOSキャパシタ）のレイアウト図である。

【図11】本発明の実施形態5における昇圧回路の構成を示す回路図である。

#### 【符号の説明】

##### 【0036】

1、2、3、4、14、15、16、17 ゲート

5、6、19、21、25 N型ウェル領域

7、22、26 P型シリコン基板

11、30 ウェルコンタクト領域

12、31 キャパシタ領域

13、32 MOSトランジスタ

18、20 P型ウェル領域

23 N型DMOSキャパシタのゲート端子

24 N型DMOSキャパシタのN型ウェル（拡散層）端子

C11、C21、C31 キャパシタ

C12、C22、C32 キャパシタ

C13、C23a、C23b、C33a、C33b、C33c キャパシタ

C14、C24a、C24b、C34a、C34b、C34c キャパシタ

C15、C25a、C25b、C35a、C35b、C35c キャパシタ

C L K A、C L K B クロック信号

M01、M11、M21、M31 駆動PMOSトランジスタ

M02、M12、M22、M32 駆動NMOSトランジスタ

M03、M13、M23、M33 駆動PMOSトランジスタ

M04、M14、M24、M34 駆動PMOSトランジスタ

M05、M15、M25、M35 駆動PMOSトランジスタ

V11、V21、V31 ノード

V12、V22、V32 ノード

V13、V23、V33 ノード

V14、V24、V34 ノード

V15、V25、V35 ノード

VDD 電源電圧

VPP1 ~ VPP5 昇圧回路の出力電圧

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

【 図 1 0 】

【 四 1 1 】

---

フロントページの続き

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 山本 安衛

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 縣 政志

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 白瀬 政則

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 川崎 利昭

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5F038 AC03 AC05 AC17 BG03 BG05 BG08 EZ08 EZ12 EZ20

5F048 AA01 AA07 AB10 AC01 AC03 AC10 BA01 BB06 BE02 BE03

BE09 BF18

5J039 CC13 CC14 CC15 KK00 MM16