(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2008-544551

(P2008-544551A)

(43) 公表日 平成20年12月4日(2008.12.4)

(51) Int.Cl.

H05K 1/16 (2006.01)

H01C 13/00 (2006.01)

F 1

H05K 1/16

H01C 13/00

H05K 1/16C

A

D

テーマコード(参考)

4 E 3 5 1

審査請求 未請求 予備審査請求 未請求 (全 29 頁)

(21) 出願番号 特願2008-518316 (P2008-518316)

(86) (22) 出願日 平成18年6月21日 (2006. 6. 21)

(85) 翻訳文提出日 平成20年1月30日 (2008. 1. 30)

(86) 国際出願番号 PCT/US2006/023998

(87) 国際公開番号 WO2007/002100

(87) 国際公開日 平成19年1月4日 (2007. 1. 4)

(31) 優先権主張番号 11/157,531

(32) 優先日 平成17年6月21日 (2005. 6. 21)

(33) 優先権主張国 米国(US)

(71) 出願人 599056437

スリーエム イノベイティブ プロパティ

ズ カンパニー

アメリカ合衆国 55133-3427

ミネソタ州, セント ポール, スリーエム

センター ポスト オフィス ボックス

33427

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100101454

弁理士 山田 車二

(74) 代理人 100088801

弁理士 山本 宗雄

(74) 代理人 100122297

弁理士 西下 正石

最終頁に続く

(54) 【発明の名称】受動的電気物品

## (57) 【要約】

受動的電気物品は、主要面を有する第1の導電性基材と、主要面を有する第2の導電性基材を含む。第2の基材の主要面は、第1の基材の主要面と向き合っている。第1の基材の主要面および第2の基材の主要面の少なくとも1つに、電気的抵抗層が設けられる。第1および第2の基材の間には、電気的抵抗層と接触する状態で電気的絶縁層が設けられる。絶縁層は、厚さ約1 μm～約20 μmの範囲のポリマーである。絶縁層の厚さはほぼ均一である。

**【特許請求の範囲】****【請求項 1】**

主要面を有する第1の導電性基材、

前記第1の基材の前記主要面に対向する主要面を有する第2の導電性基材、

前記第1の基材の前記主要面および前記第2の基材の前記主要面の少なくとも1つに設けられる電気的抵抗層、及び

前記第1および第2の基材の間に設けられて前記電気的抵抗層と接触する、厚さ約1μm～約20μmの範囲のポリマーを含む電気的絶縁層、を含み、

前記絶縁層の厚さがほぼ均一である、受動的電気物品。

**【請求項 2】**

10

前記第1および第2の基材のうちの少なくとも1つが自立型である、請求項1に記載の受動的電気物品。

**【請求項 3】**

前記第1および第2の基材のうちの少なくとも1つが、少なくとも約10μmの厚さを有する、請求項2に記載の受動的電気物品。

**【請求項 4】**

前記抵抗層が約2μm未満の厚さを有する、請求項1に記載の受動的電気物品。

**【請求項 5】**

20

前記第1および第2の基材が、グラファイト、金属、およびこれらの組み合わせのうちのいずれかを含む層を少なくとも1つ含む、請求項1に記載の受動的電気物品。

**【請求項 6】**

前記第1および第2の基材のうちの少なくとも1つが銅である、請求項5に記載の受動的電気物品。

**【請求項 7】**

前記金属がポリマーマトリクス中に存在する、請求項5に記載の受動的電気物品。

**【請求項 8】**

前記第1の基材または前記第2の基材のいずれか一方が多層ラミネートを含む、請求項1に記載の受動的電気物品。

**【請求項 9】**

30

前記ラミネートが、銅の層およびポリイミドの層を含む、請求項8に記載の受動的電気物品。

**【請求項 10】**

前記第1および第2の基材の前記主要面が約300nm未満の平均表面粗さを有する、請求項1に記載の受動的電気物品。

**【請求項 11】**

前記第1および第2の基材の一方を90度の剥離角度で前記絶縁層から分離するために必要な力が、約3ポンド/インチ(約0.5kN/m)よりも大きい、請求項1に記載の受動的電気物品。

**【請求項 12】**

40

前記抵抗層を90度の剥離角度で前記絶縁層から分離するために必要な力が、約3ポンド/インチ(約0.5kN/m)よりも大きい、請求項1に記載の受動的電気物品。

**【請求項 13】**

前記抵抗層を90度の剥離角度で前記基材から分離するために必要な力が、約3ポンド/インチ(約0.5kN/m)よりも大きい、請求項1に記載の受動的電気物品。

**【請求項 14】**

前記絶縁層が、エポキシ、ポリイミド、ポリフッ化ビニリデン、シアノエチルプルラン、ベンゾシクロブテン、ポリノルボルネン、ポリテトラフルオロエチレン、アクリレート、ポリフェニレンオキサイド(PPO)、シアノ酸エステル、ビスマレイミドトリアジン(BT)、アリル化ポリフェニレンエーテル(APPE)、またはこれらの混合物を含む、乾燥樹脂または硬化樹脂を含む、請求項1に記載の受動的電気物品。

50

## 【請求項 1 5】

前記絶縁層が、エポキシ樹脂の混合物を含む硬化樹脂を含む、請求項 1 4 に記載の受動的電気物品。

## 【請求項 1 6】

前記絶縁層が、誘電粒子、導電粒子、およびこれらの混合を含む、請求項 1 4 に記載の受動的電気物品。

## 【請求項 1 7】

前記誘電粒子が約 10  $\mu\text{m}$  未満の大きさを有する、請求項 1 6 に記載の受動的電気物品。

## 【請求項 1 8】

前記粒子が、チタン酸バリウム、チタン酸バリウムストロンチウム、チタン酸化物、チタン酸ジルコン酸鉛、銀、ニッケル、ニッケルコーティングされたポリマー球、金コーティングされたポリマー球、はんだ、グラファイト、窒化タンタル、および窒化金属シリコン (metal silicon nitride) から成る群より選択されるかまたはこれらの混合物である、請求項 1 6 に記載の受動的電気物品。

## 【請求項 1 9】

粒子荷重が、前記絶縁層の総体積を基準として 20 ~ 70 体積パーセントである、請求項 1 6 に記載の受動的電気物品。

## 【請求項 2 0】

前記絶縁層が約 4 より高い誘電率を有する、請求項 1 に記載の受動的電気物品。

## 【請求項 2 1】

前記物品が約  $1 \text{nF} / \text{in}^2$  ( $0.16 \text{nF} / \text{cm}^2$ ) より高い静電容量密度を有する、請求項 1 に記載の受動的電気物品。

## 【請求項 2 2】

前記絶縁層が約  $0.2 \text{W} / \text{m} \cdot \text{K}$  より高い熱伝導率を有する、請求項 1 に記載の受動的電気物品。

## 【請求項 2 3】

前記抵抗層が約 25 / 平方 (Ohms/Sq) より高い抵抗率を有する、請求項 1 に記載の受動的電気物品。

## 【請求項 2 4】

前記抵抗層が約 10 より大きい相対透過性を有する、請求項 1 に記載の受動的電気物品。

## 【請求項 2 5】

前記第 1 の基材、前記第 2 の基材、前記抵抗層、および前記絶縁層のうちの少なくとも 1 つに、レジスタ、コンデンサ、およびインダクタのうちの少なくとも 1 つを形成するパターンが付加されている、請求項 1 に記載の受動的電気物品。

## 【請求項 2 6】

受動的電気物品を形成するための方法であって、前記方法は、主要面を有する第 1 の導電性基材、前記第 1 の基材の前記主要面に対向する主要面を有する第 2 の導電性基材、前記第 1 の基材の前記主要面および前記第 2 の基材の前記主要面の少なくとも 1 つに設けられる電気的抵抗層、および前記第 1 および第 2 の基材の間に設けられ前記電気的抵抗層と接触する電気的絶縁層であって、前記絶縁層が厚さ約  $1 \mu\text{m}$  ~ 約  $20 \mu\text{m}$  の範囲のポリマーを含み、前記絶縁層の厚さがほぼ均一である電気的絶縁層、を含むラミネート構造を作成する工程と、

前記第 1 の基材、前記第 2 の基材、前記抵抗層のうち少なくとも 1 つが、レジスタ、コンデンサ、およびインダクタの中の少なくとも 1 つを形成するように回路形成する工程と、を含む方法。

## 【請求項 2 7】

前記回路形成されたラミネートをプリント回路に埋め込むことをさらに含む、請求項 2 6 に記載の方法。

10

20

30

40

50

**【請求項 28】**

前記プリント回路が剛性のプリント回路基板である、請求項27に記載の方法。

**【請求項 29】**

前記プリント回路が可撓性回路である、請求項27に記載の方法。

**【請求項 30】**

複数個の前記回路形成されたラミネートをプリント回路に埋め込むことをさらに含む、請求項26に記載の方法。

**【請求項 31】**

回路形成されたラミネート構造が埋め込まれたプリント回路であって、前記ラミネート構造が、主要面を有する第1の導電性基材、前記第1の基材の前記主要面に対向する主要面を有する第2の導電性基材、前記第1の基材の前記主要面および前記第2の基材の前記主要面の少なくとも1つに設けられる電気的抵抗層、および前記第1および第2の基材の間に設けられ前記電気的抵抗層と接触する電気的絶縁層であって、前記絶縁層が厚さ約1 $\mu\text{m}$ ～約20 $\mu\text{m}$ の範囲のポリマーを含み、前記絶縁層の厚さがほぼ均一である電気的絶縁層を含む、プリント回路。

10

**【請求項 32】**

前記ラミネート構造が、レジスタ、コンデンサ、およびインダクタのうちの少なくとも1つを形成するように回路形成される請求項31に記載のプリント回路。

**【請求項 33】**

前記ラミネート構造がレジスタおよびコンデンサを形成するように回路形成される、請求項31に記載のプリント回路。

20

**【請求項 34】**

前記ラミネート構造がコンデンサおよびインダクタを形成するように回路形成される、請求項31に記載のプリント回路。

**【請求項 35】**

前記ラミネート構造がレジスタおよびインダクタを形成するように回路形成される、請求項31に記載のプリント回路。

**【請求項 36】**

前記ラミネート構造がレジスタ、コンデンサ、およびインダクタを形成するように回路形成される、請求項31に記載のプリント回路。

30

**【発明の詳細な説明】****【背景技術】****【0001】**

エレクトロニクス業界では、電子回路の小型化と、それに伴う電子回路の回路素子密度増加の傾向が続いている。従来のプリント回路基板では、レジスタ、コンデンサ、およびインダクタなどの表面実装型の受動的電気機器によって、基板の表面積の大きな部分が占められていた。電気回路の回路素子密度を高める1つの手段は、受動的機器を回路基板の表面から取り去り、回路基板自体に受動的機器を埋め込みもしくは集積することである。これにはさらなる利点があり、受動的機器をより能動的回路構成要素に接近させて配置することができる。これにより、電気リード線の長さの短縮、リードインダクタンスの低減、回路速度の向上、信号ノイズの低減が可能となる。信号ノイズは、信号インテグリティ問題や電磁妨害(EMI)問題を引き起こすことがある。受動的構成要素を基板に埋め込めば、基板のサイズ、厚さ、層数を小型化または減少させることができ、延いては、回路基板コストの大幅な削減が可能となる。基板の小型化と厚さの低減に加え、表面実装構成要素と、それに関連するビアおよびはんだ接続を除去することにより、重量の大幅削減と信頼性の向上が可能となる。

40

**【発明の開示】****【発明が解決しようとする課題】****【0002】**

最後に、信号立ち上がり時間、周波数、電流、基板密度が増加し続けるに連れ、プリン

50

ト回路基板レベルで熱放散を改善することが必要となる。薄い埋め込み型受動層によっても、熱放散を改善することができる。

#### 【課題を解決するための手段】

##### 【0003】

本発明の1態様は、受動的電気物品を提供する。実施形態の1つにおいて、受動的電気物品は、主要面を有する第1の導電性基材と、主要面を有する第2の導電性基材を含み、第2の基材の主要面は、第1の基材の主要面に対向する。第1の基材の主要面および第2の基材の主要面の少なくとも1つに、電気的抵抗層が設けられる。第1および第2の基材の間には、電気的抵抗層と接触する状態で電気的絶縁層が設けられる。絶縁層は、厚さ約1μm～約20μmの範囲のポリマーを含む。絶縁層の厚さはほぼ均一である。

10

##### 【0004】

本発明の別の態様は、受動的電気物品の形成方法を提供する。1つの実施形態において、この方法は、主要面を有する第1の導電性基材と、主要面を有する第2の導電性基材を含み、第2の基材の主要面は第1の基材の主要面に対向し、第1の基材の主要面および第2の基材の主要面の少なくとも1つに電気的抵抗層が設けられ、第1および第2の基材の間には電気的抵抗層と接触する状態で電気的絶縁層が設けられ、絶縁層は厚さ約1μm～約20μmの範囲のポリマーを含み、絶縁層の厚さはほぼ均一であるラミネート構造を提供することを含む。第1の基材、第2の基材、抵抗層のうち少なくとも1つは、レジスタ、コンデンサ、およびインダクタの中の少なくとも1つを形成するように回路形成される。

20

##### 【0005】

本発明の別の態様は、回路形成された埋め込み型ラミネート構造を有するプリント回路を提供する。1つの実施形態において、このラミネート構造は、主要面を有する第1の導電性基材と、主要面を有する第2の導電性基材を含み、第2の基材の主要面は第1の基材の主要面に対向し、第1の基材の主要面および第2の基材の主要面の少なくとも1つに電気的抵抗層が設けられ、第1および第2の基材の間には電気的抵抗層と接触する状態で電気的絶縁層が設けられ、絶縁層は厚さ約1μm～約20μmの範囲のポリマーを含み、絶縁層の厚さはほぼ均一である。

#### 【発明を実施するための最良の形態】

##### 【0006】

以下の発明を実施するための最良の形態では、本明細書の一部を構成する添付の図面を参照し、本発明を実施することができる特定の実施形態を例として示す。この点に関して、「上部」、「下部」、「前部」、「後部」、「リーディング」、「トレーリング」などのような方向に関する用語が、記載されている図の方向に関して使われる。本発明の実施形態の構成要素は多くの異なる方向に置かれ得るので、方向に関する用語は、説明のために使われるものであって、決して限定するものではない。他の実施形態を使用してもよく、また本発明の範囲から逸脱することなく構造上又は論理上の変更を成してもよいことが理解されるものである。したがって、以下の詳細説明は、制限する意味で理解されるべきではなく、また、本発明の範囲は、添付の特許請求の範囲によって定義される。

30

##### 【0007】

本発明は、コンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能するパターンを付加することができ、例えばプリント回路基板（PCB）や可撓性回路（可撓性回路はPCBの一種）などの、回路の構成要素として埋め込みまたは集積されてもよい受動的電気物品を目的とする。さらに、受動的電気物品そのものは、ある程度の変更が加えられても、電気回路として機能することができる。

40

##### 【0008】

#### 受動的電気物品

本発明の受動的電気物品の1実施形態は、主要面を有する第1の導電性基材、第1の基材の主要面に対向する主要面を有する第2の導電性基材、第1の基材の主要面および第2の基材の主要面の少なくとも1つに設けられる電気的抵抗層、第1および第2の基材の間

50

には電気的抵抗層と接触する状態で設けられる電気的絶縁層を含む。コンデンサ、レジスタ、インダクタ、およびこれらの組み合わせなどの受動的素子を形成する上では、第1の基材、第2の基材、抵抗層、絶縁層に選択的にパターンが付加される。コンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能する本発明の受動的電気物品の潜在的な用途は多岐にわたり、望ましいコンデンサ、レジスタ、インダクタンスの範囲は、その目的とする用途に応じて変化する。

【0009】

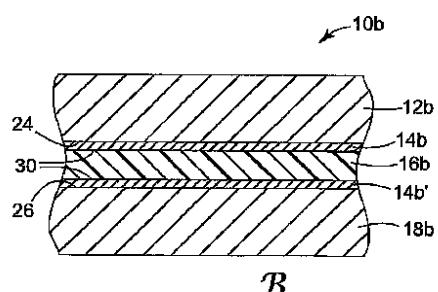

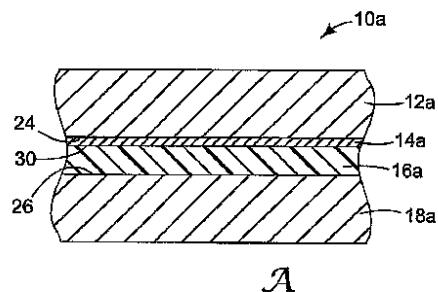

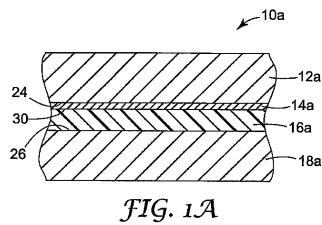

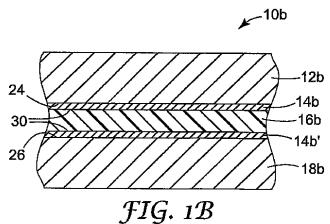

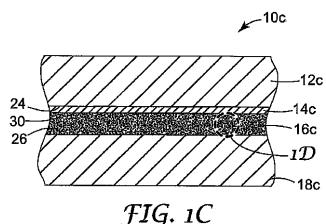

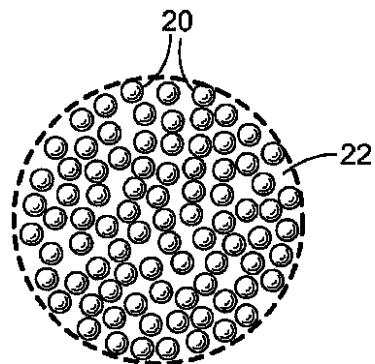

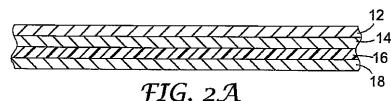

図1A～1Cは、本発明の受動的電気物品10a、10b、10cの代表的な実施形態をそれぞれ示している。これらは、コンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能してよい。図1Aにおいて、受動的電気物品10aは、第1の基材12a、電気的抵抗層14a、電気的絶縁層16a、および第2の基材18aからなるラミネートを含む。図1Bにおいて、受動的電気物品10bは、受動的電気物品10aに類似した構成を有する。ただし、図1Bでは、両方の基材に1つの抵抗層が隣接して配置されるように、さらなる電気的抵抗層（抵抗率が異なるものでもよい）がラミネート内に設けられている。特に、受動的電気物品10bは、第1の基材12b、電気的抵抗層14b、電気的絶縁層16b、第2の電気的抵抗層14b'、および第2の基材18bを含む。ここで図1Cを参照すると、受動的電気物品10cは、受動的電気物品10aと類似した構成を有する。特に、受動的電気物品10cは、第1の基材12c、電気的抵抗層14c、電気的絶縁層16c、および第2の基材18cを含む。絶縁層16cは、ポリマー22中に複数個の粒子20を含有する（図1Dの拡大図参照）。粒子20は、互いに接触しても、しなくても、いずれでもよい。また、目的とする最終的な用途に応じて、予め定められた方法で配置されてよい（例えば、均一もしくは無作為）。1つの実施形態では、粒子20はほぼ球形状をなす。別の実施形態では、粒子20は非球形の別形状を有する。1つの実施形態では、粒子20は一定の大きさと形状を有し、別の実施形態では、粒子20が不規則な形状および/または大きさを有する。

10

20

30

40

【0010】

説明を明確かつ容易にするため、特に断りがない限り、ここでは、受動的電気物品10a、10b、10c、第1の基材12a、12b、12c、抵抗層14a、14b、14b'、14c、絶縁層16a、16b、16c、第2の基材18a、18b、18cを、一般に、受動的電気物品10、第1の基材12、抵抗層14、絶縁層16、第2の基材18と記載する。

【0011】

受動的電気物品10がコンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能できるようにするため、第1の基材12および第2の基材18は導電性を有する。あるいは、第1の基材12の主要面24および第2の基材18の主要面26の少なくとも1つが導電性を有する。抵抗層14もまた導電性を有する。ただし、その導電性は、隣接する第1および第2の基材12、18のそれより低くなっている。第1および第2の基材12、18と抵抗層14の間の導電性は、材料特性および/または寸法の相違によって発生してもよい。1つの実施形態において、第2の基材18は、本来、受動的電気物品を構成するラミネート構造に含まれない。その代わり、第2の基材は、受動的電気物品が結合されるプリント回路の層の1つを構成する。図1A～1Cに示す実施形態のそれにおいて、絶縁層16は、ほぼ均一な厚さを有する。1つの実施形態では、第1の基材12、第2の基材18、抵抗層14、絶縁層16のそれぞれが、ほぼ均一な厚さを有する。

【0012】

図1A～1Cにおいて、受動的電気物品10にコンデンサを形成するためのパターンが付加されている場合は、抵抗層14から、抵抗層14の平面を介して電流が流れる。電流の入力用および出力用の接触パッド（図示せず）が第1の基材12に形成され、この接触パッド間に電流が流れる。第2の基材18に隣接させて抵抗層14も設けられる場合、物品の第2の側においてレジスタが同様に形成されてもよい。受動的電気物品10にコンデ

50

ンサを形成するパターンが付加される場合、これに対向する容量性プレート(図示せず)が第1の基材12および第2の基材18に形成される。一部の実施形態において、抵抗層14(これもまた導電性だが、基材12、18よりは導電性が低い)は、容量性プレートをパターン付基材12、18の縁部の外まで広げてもよい。受動的電気物品10にインダクタを形成するパターンが付加される場合、入力用および出力用の接点を有するコイル構造(図示せず)が基材12、18の一方または両方に形成される。

#### 【0013】

図1A～1Cに示す受動的電気物品10の層は、分離、層間剥離、または凝集破壊などに対する耐性を有する。1つの実施形態において、受動的電気物品10に含まれる層の分離や、剥離角度90度でのいずれかの層における凝集破壊の誘発に必要とされる力は、約3ポンド/インチ(0.5キロニュートン/メートル(kN/m))以上、好ましくは4ポンド/インチ(0.7kN/m)以上、より好ましくは6ポンド/インチ(1kN/m)以上である(IPC(Institute for Interconnecting and Packaging Electronic Circuits)発行のIPC試験方法手引き(IPC Test Method Manual)、IPC-TM-650、試験番号2.4.9(1988年10月付)に従って測定)。この力は、受動的電気物品10のラミネートに含まれる隣接し合ういかなる層を分離する場合にも必要とされる。例えば、基材12、18これらに隣接する絶縁層16、基材12、18これらに隣接する抵抗層14、または絶縁層16とこれに隣接する抵抗層14の分離、あるいは、基材12、18、抵抗層14、または絶縁層16における凝集破壊などで必要とされる。

10

#### 【0014】

1実施形態において、物品10の静電容量密度は1nF/in<sup>2</sup>(0.16nF/cm<sup>2</sup>)以上、好ましくは4nF/in<sup>2</sup>(0.62nF/cm<sup>2</sup>)以上、より好ましくは10nF/in<sup>2</sup>(1.55nF/cm<sup>2</sup>)以上である。

20

#### 【0015】

##### 基板

受動的電気物品10の基材12、18は、単層または多層を含んでもよい(例えば、ラミネート)。基材12、18は、グラファイト、複合材料(例えば、ポリマーマトリクスに含まれる銀粒子)、金属(例えば、銅やアルミニウム)、これらの組み合わせ、またはラミネートそのものなどを含んでもよい。多層基材の実施例には、ポリイミドに付着した銅が含まれる。第1および第2の基材12、18は、材料および構造が同一でも、異なっても、いずれでもよい。

30

#### 【0016】

本発明では、基材12、18のうちの少なくとも1つは、自立性基材である。本明細書で使用する場合、「自立性基材」とは、支持用のキャリアを使用せずに基材のコーティングや取り扱いができるよう、十分な構造一体性を有する基材を意味する。基材12、18は可撓性を有することが好ましい。ただし、剛直な基材も基材12、18として使用してよい。1つの実施形態において、基材12、18は、約5～8μmの範囲の厚さを有する。より好ましくは、約10～40μmの範囲の厚さとする。高熱負荷を拡散する機能や、高電流を処理する機能が求められる場合、基材の厚さは高い数値の範囲内にあることが好ましい(例えば、約70μm以上の厚さ)。

40

#### 【0017】

通常、電気的抵抗層14と接触する第1の基材12の主要面24は導電性を有する。また、電気的絶縁層16(図1A参照)または電気的抵抗層14(図1B参照)と接触する第2の基材18の主要面26も導電性を有する。表面処理では、酸化、またはカップリング剤(例えば、官能基で終端されたシラン)との反応を利用して、これらの主要面24、26に材料を追加する。この表面処理は、隣接し合う層の間の接着を促進するために使用してもよい。結果として基材12、18自体の主要面24、26に付着する材料は、必ずしも導電性を有する必要はない。特に、主要面が絶縁層16と接触する(かつ、抵抗層14と接触しない)場合は、主要面に付着する材料が導電性を備える必要はない。これは、基材そのものに導電性があればコンデンサを形成できるからである。

50

## 【0018】

1つの実施形態において、第1および第2の基材12、18の主要面24、26は、平均的な表面粗さが、約10nm～約300nmの範囲内、好ましくは10nm～100nmの範囲内、さらに好ましくは10nm～50nmの範囲内にある。電気的絶縁層16の厚さが1μm以下の場合は、平均的表面粗さが10nm～50nmの範囲内であることが好ましい。平均的表面粗さ(RMS)は、平均値( $[(z_1)^2 + (z_2)^2 + (z_3)^2 + \dots + (z_n)^2] / n$ )の平方根を利用して測定する。ここで、 $z$ は基材表面の平均から上下への隔たり、 $n$ は測定点の数(少なくとも1000個)に相当する。測定領域は、少なくとも $0.2\text{mm}^2$ である。好ましくは、いずれの $z_n$ も、電気的絶縁層または電気的抵抗層の厚さの半分を超えないこと。

10

## 【0019】

基材が金属の場合、その金属は、電気的絶縁層16の硬化温度と同一またはそれより低いアニール温度を有することが好ましい。つまり、その金属は、電気的絶縁層14がコーティングされる前にアニールされる。

## 【0020】

好ましい基材は銅である。代表的な銅としては、カール・シュレンク社(Carl Schlenk, AG)(ドイツ、ニュルンベルク(Nurnberg, Germany) )製またはオーリン社(Olin Corporation)のシン・ストリップ/プラス・グループ(米国コネチカット州、ウォーターベリー(Waterbury, Connecticut) )製の銅フォイルが挙げられる。

20

## 【0021】

## 電気的抵抗層

受動的電気物品10の電気的抵抗層14は、高オーム材料からなる薄膜を含む。代表的な高オーム材料としては、ニッケルクロム(NiCr)、ニッケルクロムアルミニウムシリコン(NiCrAlSi)、ニッケルリン(NiP)、またはドープ導電体(ドープ白金など)が挙げられる。ただし、これらに限定されるものではない。1つの実施形態において、抵抗層14は、透磁率が高い材料で形成される。そのような材料には、たとえば、フェライト材料、ニッケル鉄合金(パーマロイなど)、シリコン鋼またはコバルト鋼などがある。受動的物品にインダクタを形成するパターンが付されている場合により大きなインダクタンスを得るには、10以上の高い相対透磁率を有する材料が好ましい。さらに好ましくは、相対透磁率が100を超える材料を使用する。1つの実施形態において、抵抗層14は、約2μm未満の厚さを有する。1つの実施形態において、抵抗層14は、25 / 平方(Ohms/Sq)以上、より好ましくは250 / 平方(Ohms/Sq)以上、さらに好ましくは500 / 平方(Ohms/Sq)以上の抵抗を有する。

30

## 【0022】

1つの実施形態において、抵抗層14は、基材12、18の一方または両方に設けられる。そのための手段としては、スパッタリング、物理気相成膜法、化学気相成膜法、電気メッキ、または、抵抗層14および基材12、18に使用されている材料に適した方法であって当該技術分野において既知となっているその他のあらゆる好適な方法が使用される。銅基材上に設けられる好適な抵抗層は、集積薄膜抵抗(integrated thin film resistor)付きの銅基材を含む。そのような銅基材としては、例えば、グールド・エレクトロニクス社(Gould Electronics Inc.)(米国アリゾナ州チャンドラー(Chandler, Arizona) )からTCRおよびTCR+の商業表記で販売されているもの、ローム・アンド・ハース・エレクトロニック・マテリアルズ社(Rohm & Haas Electronic Materials)(米国マサチューセッツ州モールバラ(Marlborough, Massachusetts) )製のイン・サイチュ内臓レジスター(INSITE Embedded Resistor)、オメガ・テクノロジー社(Ohmega Technologies)(米国カリフォルニア州カルバーシティ(Culver City, California) )製のオメガ・プライ・レジスター・コンダクター・マテリアル(Ohmega-Ply Resistor-Conductor Material)が挙げられる。

40

## 【0023】

絶縁層16と接合される抵抗層14の面30は、上述した第1および第2の基材12、

50

18の主要面24、26に類似する表面粗さ特性を有することとなる。特に、1つの実施形態において、面30は、平均的な表面粗さが、約10nm～約300nmの範囲内、好ましくは10nm～100nmの範囲内、さらに好ましくは10nm～50nmの範囲内にある。電気的絶縁層16の厚さが1μm以下の場合は、平均的表面粗さが10nm～50nmの範囲内であることが好ましい。平均的表面粗さ(RMS)の測定は、既に説明した方法により行う。

#### 【0024】

##### 電気的絶縁層

受動的電気物品10の電気的絶縁層16(それ自体が1以上の層を含んでもよい)は、ポリマーを含む。好ましくは、電気的絶縁層16は、ポリマーおよび複数個の粒子を含み、樹脂および粒子の混合物で形成される。

10

#### 【0025】

基材材料12、18および抵抗層14の表面粗さに関し、電気的絶縁層16は、絶縁層16から隣接する層を分離するために上述の力が必要とされる受動的電気物品を提供するように選択される。

#### 【0026】

電気的絶縁層16に好適な樹脂としては、エポキシ、ポリイミド、ポリフッ化ビニリデン、シアノエチルプルラン、ベンゾシクロブテン、ポリノルボルネン、ポリテトラフルオロエチレン、アクリレート、ポリフェニレンオキサイド(PPO)、シアン酸エステル、ビスマレイミドトリアジン(BT)、アリル化ポリフェニレンエーテル(APPE)、およびこれらの混合物が挙げられる。米国特許公開第2004/0222412号(これと共に譲渡されたものであり、その全体は参照により包含されている)に記載された有機ポリマーは、絶縁層16の好適な材料のさらなる実施形態である。

20

#### 【0027】

市販のエポキシとしては、レゾリューション・パフォーマンス・プロダクト社(Resolution Performance Product)(米国テキサス州ヒューストン(Houston, Texas))からEPON 1001FおよびEPON 1050の商業表記で販売されているものが挙げられる。好ましくは、樹脂は、通常のはんだリフロー工程で発生する温度(例えば、約180～約290の範囲)に耐えることができる。これらの樹脂は、電気的絶縁層または導電層を形成する上で、乾燥または硬化させてもよい。

30

#### 【0028】

代表的な混合物としては、エポキシ混合物、好ましくは、ビスフェノールAのジグリジルエーテルとノボラックエポキシとの混合物(例えば、樹脂の総重量を基にした場合に、重量の90～70%をEPON 1001F、重量の10～30%をEPON 1050としたもの)が挙げられる。

#### 【0029】

粒子が存在する場合、その粒子は、誘電(つまり絶縁)粒子または導電粒子もしくはこれらの混合物である。粒子の分布は、無作為、または一定の秩序を有する。通常、絶縁層の粒子は、誘電粒子または絶縁粒子を含む。ただし、粒子の混合物は、樹脂および粒子混合物が全体的に絶縁効果を有するよう、好適な状態に整えられる。

40

#### 【0030】

代表的な誘電粒子または絶縁粒子としては、バリウム、チタン酸塩、チタン酸バリウムストロンチウム、チタン酸化物、チタン酸ジルコン酸鉛、およびこれらの混合物が挙げられる。市販のチタン酸バリウムは、日本化学工業株式会社(東京)からAKBTの商業表記で販売されている。

#### 【0031】

粒子はいかなる形状であってもよい。また、規則的な形状や、不規則な形状でもよい。代表的な形状としては、球体、小板、立方体、針、扁球、長球、角錐、角柱、フレーク、棒、平板、繊維、小片、ウィスカ、およびこれらの混合が挙げられる。

#### 【0032】

50

流径（粒子の最小寸法）は、通常、約0.05～約10μm、好ましくは0.05～5μm、より好ましくは0.05～2μmの範囲である。粒子は、電気的絶縁層の厚さ内で少なくとも2～3個の粒子を垂直方向に積み重ねられる大きさを有することが好ましい。電気的絶縁層の厚さよりもやや大きい粒径を有する比較的大型の粒子は、絶縁層のそれぞれの側で個々の粒子により層間の隙間が埋められることを許容するが、これは好ましくない。ラミネーションの最中に、これらの比較的大型の粒子により、表面の変形と、粒子と基材との接合面または粒子と抵抗層との接合面での「ワイピング」動作とを引き起こす圧縮力が発生する。なお、ワイピング動作により、表面酸化層が除去されてもよい。

## 【0033】

ポリマーに占める粒子の荷重は、電気的絶縁層の層体積を基準とした場合に、通常、20～70体積パーセント、好ましくは30～60体積パーセント、より好ましくは40～50体積パーセントである。

## 【0034】

1実施形態において、電気的絶縁層16（1以上の層を含む）の厚さは、約1～20μmの範囲である。別の実施形態において、電気的絶縁層16の厚さは、約8～16μmの範囲である。

## 【0035】

1つの実施形態において、絶縁層16の誘電定数は、約4以上、好ましくは約11以上、さらに好ましくは約15以上である。

## 【0036】

1つの実施形態において、絶縁層16は、約0.2W/m-K以上、好ましくは約0.35W/m-K以上、さらに好ましくは約0.5W/m-K以上の熱伝導率を有する。

## 【0037】

## 受動的電気物品の製造方法

本発明の受動的電気物品10の製造方法は、デブリ、または化学吸着もしくは吸収された材料がほとんど存在しない主要面24を有する第1の基材12の提供と、少なくとも第1の基材12の主要面24上に設けられる抵抗層14の提供を含む。抵抗層14を主要面24上に設ける手段としては、スパッタリング、物理的または化学的な気相成膜法、電気メッキ、もしくは当該技術分野において既知となっているその他の好適な方法を使用してよい。抵抗層14の面30は樹脂を含む混合物でコーティングされ、この混合物に第2の基材18の主要面26が張り付けられる。この混合物は、その後硬化または乾燥させられる。あるいは、混合物で第2の基材18の主要面26をコーティングし、第2の基材18の混合物コーティングされた主要面26を、第1の基材12の抵抗層14の面30に張り付けてよい。あるいは、混合物で抵抗層14の面30および第2の基材18の主要面26をコーティングし混合物コーティングされた面30、26を、互いに張り合わせてもよい。上述した受動的電気物品10の製造方法は、図1Cに示す実施形態となることが認められる。別の実施形態では、図1Aまたは図1Bの受動的電気物品を形成するよう、抵抗層14も第2の基材18の主要面26上に設けることができる他/または、絶縁層16を形成するために別の材料を使用してもよい。

## 【0038】

電気的抵抗層14と電気的絶縁層16との接着力を最大化するには、基材12、18にデブリまたは化学吸着もしくは吸収された材料がほとんど存在しないことが好ましい。これは、例えば、基材24、26上の有機残留物の量を減少させること、および、基材24、26からデブリを除去することにより実現される。代表的な方法として、後述する表面処理が挙げられる。

## 【0039】

本発明の工程では、第1および第2の基材12、18としての銅箔、抵抗層14としてのドープ白金、エポキシ粒子およびチタン酸バリウム粒子で形成された電気絶縁層16に関して詳しく説明している。

## 【0040】

10

20

30

40

50

銅フォイルは、第1および第2の基材12、18に施される。第1の基材12の銅フォイルは、ドープ白金の抵抗層14（ローム・アンド・ハース・エレクトロニック・マテリアルズ社（Rohm & Haas Electronic Materials）（米国マサチューセッツ州モールバラ（Marlborough, Massachusetts）））製のイン・サイチュレジスター・マテリアル（INSITE Resistor Material）と共に事前にコーティングされる。基材12、18の銅フォイルおよびドープ白金の抵抗層14では、有機系腐食防止剤（例えば、ベンゾトリアゾール誘導体）および／またはローリング工程の樹脂油などの材料が、露出した面に付着する場合がある。そのため、基材12、18の銅フォイルおよびドープ白金の抵抗層14について表面処理が行われる。これは、例えば、電気的絶縁層16と、第1の銅フォイル基材12上に設けられたドープ白金抵抗層14の面30との良好な接着を実現すること、また、絶縁層16と第2の銅フォイル基材18の面26との接着を良好に行うことなどを目的とする。除去は、例えば、銅フォイル基材および／またはドープ白金抵抗層をアルゴン・酸素プラズマや空気コロナで処理することにより達成できる。また、湿式化学処理を使用できることも、当該技術分野において周知である。銅フォイル基材およびドープ白金抵抗層の露出面に付着した微粒子は、例えば、ウェブ・システムズ社（Web Systems Inc.）、ボルダー社（Boulder, CO）からウルトラクリーナー（ULTRACLEANER）の商業表記を付して市販されている超音波／真空ウェブクリーニング機器を使用して除去することができる。銅フォイルおよび抵抗層については、この表面処理工程の最中にかき傷、くぼみ、屈曲などができるないことが好ましい。これは、コーティング問題およびコーティングの欠陥が発生する可能性を回避するためであり、このような問題や欠陥は、コーティングの不均一さや、コンデンサなどの物品のショートを招く恐れがある。

10

20

30

40

50

#### 【0041】

絶縁層16に使用される混合物を作成する際には、エポキシなどの樹脂、所望により複数個の誘電粒子または絶縁粒子（チタン酸バリウムなど）、さらに任意で触媒を使用してよい。製造工程で生じた粒子（例えば、炭酸塩）に付着した吸着水または樹脂材料は、その粒子の表面から使用前に除去することができる。除去は、空気中の粒子を特定温度で一定時間（例えば、350で15時間）熱することにより行ってもよい。加熱後、混合物に使用する前は、粒子をデシケータに格納してもよい。

#### 【0042】

チタン酸バリウム粒子とエポキシの混合物は、以下の方法で作成してよい。最初に、チタン酸バリウム粒子を、分散剤含有のケトン溶媒と混ぜ合わせる。一般的なミキシング装置として、プロペラ式の攪拌器が考えられる。構成成分の重量比は、通常、チタン酸バリウム85%、溶媒13.5%、分散剤1.5%である。粒塊を分散、破断させるため、ホモジナイザーを使用して混合物をかき回すことができる。ホモジナイザーとしては、例えばA P V社（米国ウィスコンシン州レイクミルズ）販売のG a u l i nホモジナイザーが挙げられる。濃縮された分散物をフィルターで濾して、分散していない粒子を取り除く。通常、一連のフィルターの最後に当たるフィルターは、10μのアブソリュートフィルターである。フィルターで濾され、濃縮されたこの分散物は、引き続き、エポキシポリマー溶液およびその他の添加剤と混合することができる。これにより、コーティングに適した分散性の混合物が作られる。最終的なコーティング分散物は、コーティング作業の直前に再度フィルターにかけられることが好ましい。

#### 【0043】

この混合物は、分散剤（好ましくは、非イオン性分散剤）などの添加剤および溶媒を含んでよい。分散剤の実施例としては、例えば、アビシア・ピグメント・アンド・アディティブ社（Avecia Pigments & Additives）（英国マン彻スター（Manchester, UK））からソルスパース（SOLSPERSE）24000の商業表記で販売されている、ポリエステルとポリアミンのコポリマーが挙げられる。溶媒の実施例としては、例えば、いずれもアルドリッヂ・ケミカル社（Aldrich Chemical）（米国ウィスコンシン州ミルウォーキー（Milwaukee, WI））製のメチルエチルケトンおよびメチルイソブチルケトンが挙げられる。好ましいシステムの場合は、その他の添加物が必要とされない。ただし、粘度の変更や均一

なコーティングの実現のために、追加の構成成分を使用することは可能である。

#### 【0044】

触媒や硬化剤を混合物に追加してもよい。触媒や硬化剤を使用する場合は、コーティング工程の前に触媒や硬化剤を追加できる。好ましくは、コーティング工程の直前に触媒や硬化剤を追加する。

#### 【0045】

代表的な触媒として、アミンおよびイミダゾールが挙げられる。塩基面を有する（つまり、pHが7以上の）粒子が存在しない場合、代表的な触媒は、スルホニウム塩などの、酸性物質を生成する（つまり、pHが7未満の）ものを含むことができる。市販されている触媒は、アルドリッヂ・ケミカル社（Aldrich Chemical）（米国ウィスコンシン州ミルウォーキー（Milwaukee, WI））製の2,4,6-トリス（ジメチルアミノメチル）フェノールである。通常、触媒は、樹脂の重量を基準として約0.5～約8重量パーセントの範囲内、好ましくは0.5～1.5重量パーセントの範囲内の量で使用される。2,4,6-トリス（ジメチルアミノメチル）フェノールを使用する場合は、樹脂の重量の0.5～1重量パーセントとすることが好ましい。

10

#### 【0046】

代表的な硬化剤としては、ポリアミン、ポリアミド、ポリフェノール、およびこれらの誘導体が挙げられる。市販の硬化剤は、イー・アイ・デュポン・ドゥ・ヌムール・アンド・カンパニー（E. I. DuPont de Nemours Company）（米国デラウェア州ウィルミントン（Wilmington, DE））製の1,3-フェニレンジアミンである。通常、硬化剤は、樹脂の重量を基準として約10～約100重量パーセントの範囲内、好ましくは10～50重量パーセントの範囲内の量で使用される。

20

#### 【0047】

付着物が除去されたドープ白金抵抗層14の面30と、付着物が除去された銅フォイル基材18の面26は、混合物でコーティングされる。コーティングは、例えばグラビアコータなど、いずれかの好適な方法を用いて行う。コーティングは、汚染や混入を最小限に留めるため、クリーンルーム内で実施することが好ましい。コーティングの乾燥厚さは、混合物に含まれる固体の割合、グラビアロールとコーティング基材の相対速度、使用されるグラビアのセルボリュームによって変動する。通常、約0.5～約10μmの範囲内の乾燥厚さを実現するには、固体割合を20～60重量パーセントの範囲内とする。コーティングは、コータのオーブンに入れて、粘着性がなくなるまで乾燥させる。オーブンの温度は、通常は約100未満だが、好ましくは、乾燥開始時の温度約30、終了時の温度約100とする。また、乾燥終了後はロールに巻かれる。乾燥終了時の温度をさらに高くなる（例えば、最高約200）こともできるが、それは必要とされていない。一般に、乾燥工程の最中にごく小さな架橋が発生する。その目的は、主として、できるだけ多くの溶媒を除去することにある。保持された溶媒は、コーティングがロールに蓄積されるときの（つまり、不必要的層間接合の）ブロックとなる。また、ラミネートの粘着力を弱めることになる。

30

#### 【0048】

欠陥を回避するコーティング技術としては、インライン濾過と、コーティング混合の脱気（空泡を除去するため）が挙げられる。1つの実施形態において、硬化の必要な樹脂を使用する場合は、電気的絶縁層でコーティングされた2つの基材をラミネートする前に、少なくとも1つの電気的絶縁層が、部分的に、好ましくは空气中で、硬化させられる。特に、ラミネーション前にコーティングを熱処理することにより、基材の粘着力が向上する。熱処理の時間は短いことが好ましい（例えば、約10秒未満）。特に高温の場合は短時間とすることが好ましい。

40

#### 【0049】

電気的絶縁層でコーティングされた面26、30のラミネーションは、ラミネーターが例えばラミネーション温度より約5～25低い温度範囲に達する前に、基材12、18の一方または両方を表面の絶縁コーティングと共にオーブンを通して送ることにより実行

50

される。電気的絶縁層は、ラミネーション中に一切接触しないことが好ましい。また、ラミネーションは、クリーンルーム内で実施されることが好ましい。本発明の受動的電気物品を作成するには、コーティングされた基材を電気的絶縁層対電気的絶縁層でラミネートする。ラミネートには、2個のニップローラーを有するラミネーターを使用する。また、2個のニップローラーは、約150～200の範囲の温度、好ましくは約150まで温めておく。ラミネーターロールには好適な空気圧を印加する。好適な空気圧は、好ましくは、5psi(34kPa)～40psi(280kPa)の範囲、より好ましくは(15psi100kPa)である。ローラー速度は、好適な値のいずれに設定することもできるが、好ましくは12in/分(0.5cm/秒)～72in/分(3.0cm/秒)、より好ましくは15in/分(0.64cm/秒)～36in/分(1.5cm/秒)とする。この工程は、バッチモードで実施することもできる。

10

#### 【0050】

ラミネートされた材料は、所望の長さのシートにカットしたり、好適なコアに巻きつけたりすることができる。ラミネーションの完了後は、好ましいクリーンルームはもはや必要とされない。

#### 【0051】

樹脂を硬化させる必要がある場合は、ラミネートされた材料をここで硬化させる。代表的な硬化温度としては、約140～約200の範囲、好ましくは160～190の範囲の温度が挙げられる。また、代表的な硬化時間として、約60～約180分の期間、好ましくは60～100分の期間が挙げられる。

20

#### 【0052】

電気的絶縁層16とドープ白金抵抗層14の面30ならびに銅フォイル18の面26との接合は、金属がコーティング時に十分に柔らかい場合や、ラミネーションおよび/または硬化中に柔らかくなる場合には、強化されてよい。つまり、フォイルおよび/または抵抗層は、コーティング前にアニールされるか、または後続の処理中にアニールされる。金属アニール温度が樹脂の硬化温度と同一またはそれよりも低い場合、アニールは、コーティング工程前の加熱により、または、硬化工程や乾燥工程の結果として実施される。好ましくは、硬化または乾燥およびラミネーションの発生する温度よりもアニール温度が低い金属基材を使用する。アニール条件は、使用する金属基材によって異なる。銅の場合は、この工程に含まれる段階のいずれかにおいて、10gの負荷を使用して、金属基材が約75kg/mm<sup>2</sup>未満のビックース硬度を取得することが好ましい。銅でこの硬度を実現するための好ましい温度範囲は、約100～約180、より好ましくは120～160である。

30

#### 【0053】

本発明の受動的電気物品は、作成された通りに機能することができる。ただし、受動的電気物品は、例えば横導電性を制限するために分離された島や除去された領域を形成する目的で、後述のようにパターンを付加することが好ましい場合がある。パターン付電気物品は、後述のように、回路物品そのものまたは回路物品の構成要素として使用されてもよい。

30

#### 【0054】

##### パターンニング

レジスタ、コンデンサ、およびインダクタの各素子は、第1の基材12、第2の基材18、または抵抗層14へのパターンニングにより形成することができる。レジスタ、コンデンサまたは誘電素子、貫通孔接触パッド、貫通孔のすきま(電気的連絡はまったく必要なない)に接続する機能を含む、回路トレースなどのその他の機能もまた、第1の基材12、第2の基材18、抵抗層14、または絶縁層16へのパターンニングにより形成できる。用語「貫通孔」は、例えば貫通孔、ベリードビア、ブラインドビアなど、すべての垂直方向の相互接続形状を含む一般用語として使用されている。

40

#### 【0055】

当該技術分野において既知の好適なパターンニング技術のいずれを採用してもよい。例え

50

ば、受動的電気物品のパターニングは、当該技術分野において周知である通り、フォトリソグラフィおよび／またはレーザアブレーションにより実施してもよい。

#### 【0056】

基材12、18のフォトリソグラフィは、フォトレジストを受動的電気物品に塗布することにより施してもよい。このフォトレジストは、隠れた基材領域および暴露された基材領域のパターンを受動的電気物品上に形成するため、塗布後に暴露および顕色される。次に、受動的電気物品が、基材を化学的に劣化またはエッティングするための既知の溶液に曝される場合は、基材の選択領域を除去することができる。次に、残った領域のフォトレジストを除去するために、水酸化カリウムのような剥離剤が使用される。この工程により、回路構造に必要な基材領域を除去することが可能となる。

10

#### 【0057】

基材12および抵抗層14の両方を除去する領域では、任意で、基材12の直後に抵抗層14をエッティングすることができる。一部の抵抗材料については、基材層12と抵抗層14に同一の腐食液が使用される。

#### 【0058】

抵抗層14にパターンを付加する上で、同一または類似のフォトリソグラフィ工程を実施してもよい。抵抗層14のフォトリソグラフィは、（基材12のフォトリソグラフィなどにより）既に暴露された抵抗層14の部分を有する受動的電気物品にフォトレジストを塗布することにより施してもよい。この工程により、回路構造に必要な抵抗層領域を除去することが可能となる。好ましくは、基材12、18および抵抗層14に、選択的にエッティングを施す。つまり、基材12、18のエッティングに使用される溶液では抵抗層14にエッティングが施されず、抵抗層14のエッティングに使用される溶液では基材12、18にエッティングが施されない。

20

#### 【0059】

受動的電気物品のいずれかの層もしくはすべての層から材料を熱により選択的に除去するために、レーザを使用してレーザアブレーションを実施してもよい。フォトリソグラフィおよびレーザアブレーションは、組み合わせて使用してもよい。

#### 【0060】

電気的絶縁層16の厚さは、本発明の受動的電気物品にパターンを付加する方法を制限するものであってよい。これは、絶縁層16そのものが、基材12、18を機械的に支持しないからである。基材12、18の少なくとも1つによって常に受動的電気物品が支持されるように、電極は基材12、18にパターンとして設けられてよい。受動的電気物品の第1の基材はパターンを付加されてよい。また、第2の基材18は、受動的電気物品が「構造一体化」（つまり、受動的電気物品が支持用のキャリアなしで取り扱え、自立したままであること）を有するように、連続的な（またはパターンが付加されない）状態のままでよい。通常、受動的電気物品にはパターンが二重（つまり両側）に施される。その際、受動的電気物品が構造一体化を有する限り、支持体は使用されない。

30

#### 【0061】

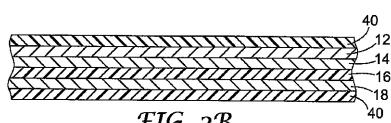

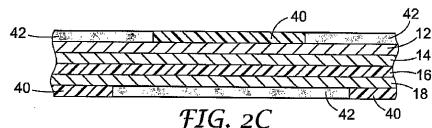

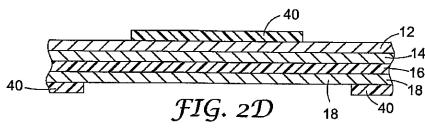

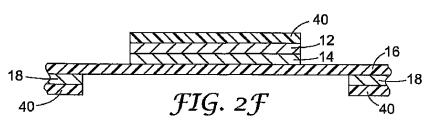

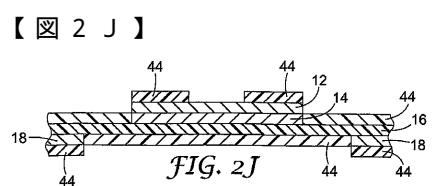

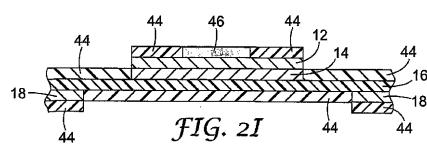

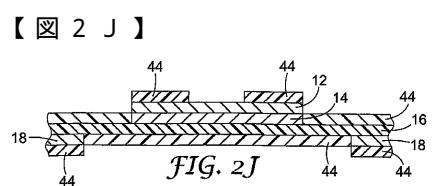

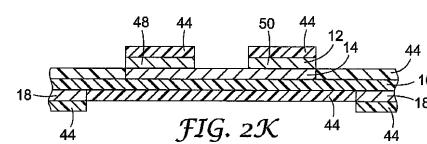

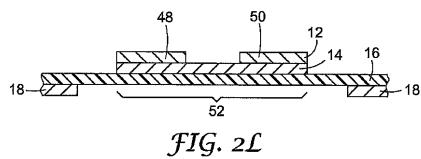

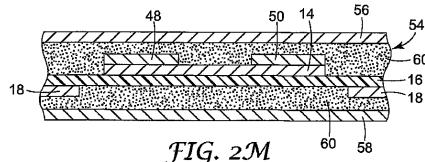

図2A～2Mは、図1Aまたは図1Cに示した受動的電気物品10からレジスタを形成するための代表的なフォトリソグラフィプロセスを示している。受動的電気物品10は、第1の導電性基材12、電気的抵抗層14、電気的絶縁層16、および第2の導電性基材18を含み（図2A）、フォトレジスト40が導電性基材12、18に塗布されている（図2B）。フォトレジスト40の選択部分は、紫外線に対する暴露などにより暴露される（図2C）。また、フォトレジスト40は、フォトレジストの未暴露部分42を除去するために顕色される（図2D）。第1のエッティング溶液は、導電層12、18の露呈部分をエッティングするために使用される（図2E）。また、第2のエッティング溶液は、抵抗層14の露呈部分のエッティングに使用される（図2F）。しかし、抵抗材料によっては、導電材料および抵抗材料の両方に同一の腐食液を使用できるので、注意する必要がある。フォトレジスト40は物品から取り除かれ（図2G）、これによって露呈した面にフォトレジスト44の新しい層が塗布される（図2H）。フォトレジスト44の新しい層は選択的に

40

50

暴露される(図2I)。また、フォトレジスト44は、フォトレジストの未暴露部分46を除去するために顯色される(図2J)。導電性基材12、18の露呈部分(実施例では基材12の部分だけが露呈している)は、2個の分離した電極48、50(図2K)を画定するためにエッチングされ、フォトレジストが再度取り除かれる(図2L)。これにより、導電性基材12の電極48、50間でレジスタ52が画定される。最後にレジスタ52を有するパターン付き物品をラミネートして、プリント回路基板などのプリント回路54が出来上がる(図2M)。物品10の導電性基材12、18は、プリント回路基板54の導電層56、58から誘電材料60により絶縁される。当該技術分野において既に知られているように、電極48、50は、導電層56、58に対して導電ビア(図示せず)により選択的に接続されてもよい。

10

## 【0062】

図2Eおよび図2Fは、導電性基材層12、18および抵抗層14がそれぞれエッチングされた様子を示しているが、これらの図は、別の実施形態において、導電性基材層12、18がエッチングされた様子を示す図2Kと交換することができる。追加の工程(例えば、絶縁接着促進のための洗浄、水分を除去するためのベーキング、隣接する誘電体に向向する外側コンダクタ面を改善するための銅面処理の実施、など)もまた、プロセス中の適切な個所で実施することができる。類似の技術を使用して、コンデンサ、レジスタ、インダクタ、およびこれらの組み合わせを含む別の種類の受動的電気機器を形成してもよい。さらに、レジスタの許容度に正確性が求められる場合は、レーザトリミングなどのプロセスを実施することができる。

20

## 【0063】

## 回路物品

本発明の受動的電気物品そのものは、ある程度の変更が加えられても、電気回路として機能することができる。1つの実施例において、受動的電気物品10にはパターンが付加されてもよい。このような実施例の場合、回路物品は、本発明の受動的電気物品10を作成することと、電気的接続用の接触を実現するために、上述のように受動的電気物品10にパターンングを施すことにより作成されてよい。受動的電気物品10の基材12、18のいずれか一方または両方には、第1および第2の基材12、18の各面へのアクセスを可能とするため、および、貫通孔接続を形成するために、パターンが付加される。

30

## 【0064】

別の実施形態において、回路物品は、本発明の受動的電気物品10を作成する工程、少なくとも1つの電気的接続を作成する工程、この接続を受動的電気物品10の基材12、18の少なくとも1つに接続する工程を含む方法により作成されてよい。

## 【0065】

本発明の受動的電気物品はさらに、例えば、プリント回路基板や可撓性回路を作成するための追加の層を1以上含んでもよい。追加の層は、剛性と可撓性のいずれでもよい。代表的な剛性層としては、ファイバーグラス/エポキシ複合物、セラミック、金属、またはこれらの組み合わせが挙げられる。なお、ファイバーグラス/エポキシ複合物は、ポリクラッド社(Polyclad)(米国ニューハンプシャー州フランクリン(Franklin, NH))からPCL-FR-226の商業表記で販売されている。代表的な可撓性層は、ポリイミドやポリエステルなどのポリマーフィルム、金属箔、またはこれらの組み合わせを含む。ポリイミドは、イー・アイ・デュポン・ドウ・ヌムール・アンド・カンパニー(E.I. DuPont de Nemours Company)(米国デラウェア州ウィルミントン(Wilmington, DE))からKAPTONの商業表記で販売されている。また、ポリエステルは、3M社(米国ミネソタ州セントポール(St. Paul, Minnesota))からSCOTCHPACの商業表記で販売されている。これらの追加の層もまた、層の上面に設けられた導電トレースまたは層内に埋め込まれた導電トレースを含んでよい。用語「導電トレース」は、電流を伝達するように設計された導電性材料のストリップやパターンを指す。導電トレースの好適な材料の実施例としては、銅、アルミニウム、はんだ、銀ペースト、金、およびこれらの組み合わせが挙げられる。

40

50

## 【0066】

この実施形態において、回路物品の好ましい製造方法は、本発明の受動的電気物品を作成する工程、受動的電気物品の基材12、18の少なくとも1つにパターニングを施す工程、追加の層を作成する工程、受動的電気物品10に層を接着する工程、受動的電気物品の基材12、18の少なくとも1つに対して少なくとも1つの電気的接続を設ける工程を含む。好ましくは、第2の追加層を作成して受動的電気物品に接着する。

## 【0067】

## プリント配線基板および可撓性回路

本発明の受動的電気物品は、コンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能する構成要素として、プリント回路基板や可撓性回路に使用することができる。受動的電気物品は、プリント回路基板や可撓性回路に対し、埋め込みまたは集積されてよい。

10

## 【0068】

プリント回路基板は、通常、2つの材料層（例えば、エポキシおよびファイバーグラスのラミネート）を含む。これらの層は、1つまたは2つの銅表面を有して、接着剤層またはプリプレグ層（プリプレグ層は、1以上のプリプレグ「層」を有することができる）を間に挟み込んでもよい。可撓性回路は、通常、可撓性層（例えば、銅でコーティングされたポリイミド層、およびポリイミド上の接着剤層）を含む。あらゆる好適なプリント回路基板または可撓性回路における本発明の受動的電気物品の位置、および、あらゆる好適なプリント回路基板または可撓性回路における本発明の受動的電気物品の埋め込みプロセスまたは集積プロセスは、当該技術分野において周知である。特に、プリント回路基板または可撓性回路のいずれかでは、プリント回路基板または可撓性回路層／構成要素を整列させるために注意する必要がある。

20

## 【0069】

上述のように、電気的絶縁層16の厚さは、物品10に対するパターニング方法によって決まる。受動的電気物品10がプリント回路基板または可撓性回路に包含される場合、さらなる独自のパターニング技術に備え、プリント回路基板または可撓性回路で受動的電気物品がさらに支持されてもよい。

## 【0070】

例えば、ダブルパターニングおよびラミネーション法が有用である。ダブルパターニングおよびラミネーション法は、上述の基材12、18の1つにフォトリソグラフィパターニングを施した後に発生する可能性がある工程を含む。このプロセスにおいて、パターン付き基材は、回路基板層（例えばFR4）などの支持材料に対してラミネートされる。このとき、パターン付きの側が支持材料に向けられる。本質的に類似の技術によって、他の基材にパターンを付加することができる。これは、電気的絶縁層16およびパターン付き基材は、この時点で、支持材料により十分に支持されているからである。プロセスを完了させるため、第2の基材の暴露側における第2のラミネーションは、ここで実施される。

30

## 【0071】

図3A～5Dは、コンデンサ、レジスタ、インダクタおよびこれらの様々な組み合わせを形成するためのパターンが施された、図1A～1Cの受動的電気物品の実施例を示している。

40

## 【0072】

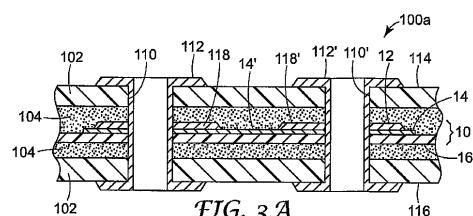

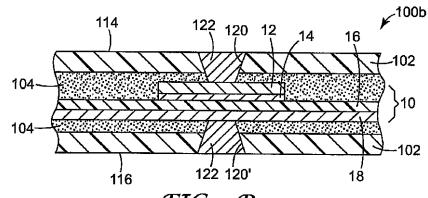

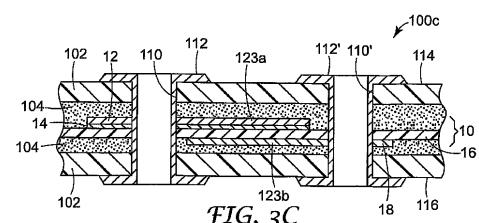

図3A～3Cは、図1Aまたは図1Cの受動的電気物品（内部に抵抗層14が1つ作成されている）にパターンが付加されたものが埋め込まれたプリント回路基板100a、100b、100cをそれぞれ示している。プリント回路基板100a、100b、100cはそれぞれ2つの層102を有する。この2つの層102は、エポキシ／ファイバーグラスなどの材料からなり、絶縁性の接着剤またはプリプレグ、および本発明の受動的電気物品10を間に挟んで位置する。この受動的電気物品10は、図3Aではレジスタ、図3Bではコンデンサ、図3Cではインダクタとして機能する図3A～3Dの実施形態は説明専用であり、限定することを目的とするものではない。他の実施形態では、例えば、層1

50

02の一方または両方を省略してもよい。

【0073】

図3Aは、本発明の受動的電気物品10(レジスタとして機能する)を含むプリント回路基板100aを示している。図3Aにおいて、信号や電流は、貫通孔110および110'によりプリント回路基板100a全体に送られる。貫通孔110および110'は、例えば、表面銅構造112および112'を形成するための銅を使用した電気メッキにより、導電性を付加されている。表面銅構造112および112'は、プリント回路基板100aの上面114または底面116のいずれかに設けられた導電トレース(図示せず)間で信号を送る。第1および第2の基材12、18と抵抗層14には、抵抗層14の一部を覆うパッド118および118'を形成するためのパターンが付加される。(受動的物品10の図示された範囲において、第2の基材18は完全に除去されている)。パッド118、118'は、抵抗層14の一部14'により接合される。表面銅構造112、112'は、2つのパッド118、118'間の抵抗層14の一部14'の形状(長さおよび幅)に基づいて制御された抵抗がパッド118、118'間で測定されるように、パッド118、118'をそれぞれ接触させるために使用される。他の実施形態では、パッド118、118'との電気的接続を形成するために異なる構造と方法を利用してもよい。例としては、導電性のブラインドビアなどが挙げられる。他の実施形態において、パッド118、118'は、プリント回路基板内部のトレースと電気的に接続される。他の実施形態では、層102、104は、完成した回路物品が可撓性を有するように、可撓性材料を含む。

10

20

30

40

【0074】

図3Bは、本発明の受動的電気物品10(コンデンサとして機能する)を含むプリント回路基板100bを示している。図3Bにおいて、信号や電流は、ビア120および120'によりプリント回路基板100b全体に送られる。ビア120および120'は、例えば、導電性材料122でビア120および120'を満たすことにより、または銅などで電気メッキを施すことにより、導電性を付加されている。導電性のビア120、120'は、プリント回路基板100bの上面114または底面116のいずれかに設けられた導電トレース(図示せず)間で信号を送る。第1および第2の基材12、18と抵抗層14には、絶縁層16のいずれかの側に容量性プレートを形成するためのパターンが付加される。他の実施形態では、導電性の基材12、18と電気的に接続するための別の構造と方法が使用されてよい。他の実施形態において、導電性の基材12、18は、プリント回路基板内部のトレースと電気的に接続される。他の実施形態では、層102、104は、完成した回路物品が可撓性を有するように、可撓性材料を含む。

【0075】

図3Cは、本発明の受動的電気物品10(コンデンサとして機能する)の別の実施形態を示している。図3Cにおいて、信号や電流は、貫通孔110および110'によりプリント回路基板100a全体に送られる。貫通孔110および110'は、例えば、表面銅構造112および112'を形成するための銅を使用した電気メッキにより、導電性を付加されている。表面銅構造112および112'は、プリント回路基板100cの上面114または底面116のいずれかに設けられた導電トレース(図示せず)間で信号を送る。第1および第2の基材12、18と抵抗層14には、絶縁層16の両側に容量性プレート123a、123bを形成するためのパターンが付加される。他の実施形態では、導電性の基材12、18と電気的に接続する上で、別の構造と方法が使用されてよい。他の実施形態において、導電性の基材12、18は、プリント回路基板内部のトレースと電気的に接続される。他の実施形態では、層102、104は、完成した回路物品が可撓性を有するように、可撓性材料を含む。

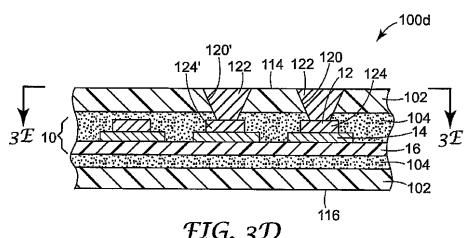

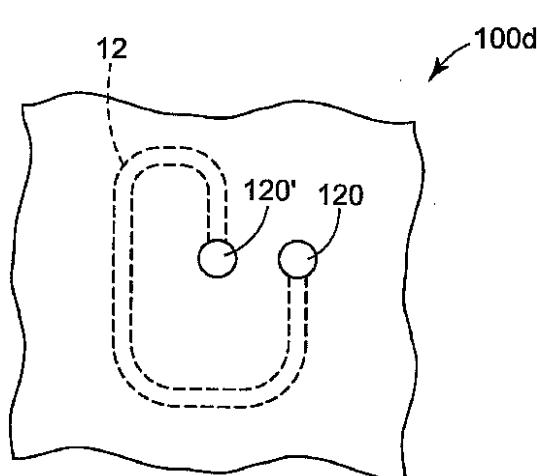

【0076】

図3Dおよび3Eは、本発明の受動的電気物品10(インダクタとして機能する)を含むプリント回路基板100cを示している。図3Dにおいて、信号や電流は、ビア120および120'によりプリント回路基板100d全体に送られる。ビア120および120'

50

0' は、例えば、導電性材料 122 でビア 120 および 120' を満たすことにより、または銅などで電気メッキを施すことにより、導電性を付加されている。導電性のビア 120、120' は、プリント回路基板 100d の上面 114 または底面 116 のいずれかに設けられた導電トレース（図示せず）間で信号を送る。第 1 および第 2 の基材 12、18 と抵抗層 14 には、接触パッド 124、124' を有する絶縁層 16 の一方の側にコイル状の誘電素子を形成するためのパターンが付加される。（受動的物品 10 の図示された範囲において、第 2 の基材 18 は完全に除去されている）。1 つの実施形態において、抵抗層 14 は、フェライト材料などの高透過性材料である。また、高透過性材料が誘電コイルのコアに含まれるように、導電性基材 12 のパターン付きコイル間に少なくとも部分的に広がるパターンが付加される。このため、インダクタに高いインダクタンスが供給される。別の実施形態において、抵抗層 14 は、導電性基材 12 と同一の幅を有する。導電ビア 120、120' は、パッド 124、124' とそれぞれ電気的に接続するために使用される。他の実施形態では、パッド 124、124' と電気的に接続するための別の構造と方法が使用されてよい。他の実施形態において、パッド 124、124' は、プリント回路基板内部のトレースと電気的に接続される。他の実施形態では、層 102、104 は、完成した回路物品が可撓性を有するように、可撓性材料を含む。

10

20

30

40

50

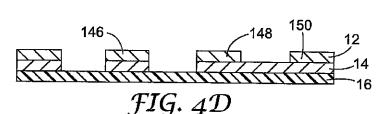

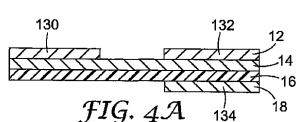

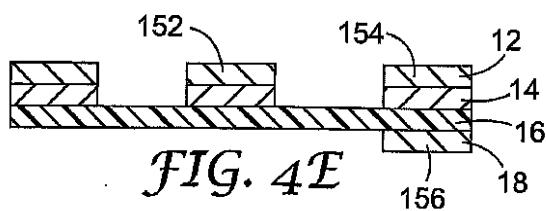

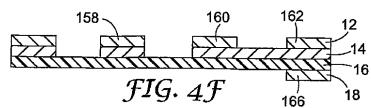

## 【0077】

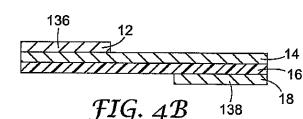

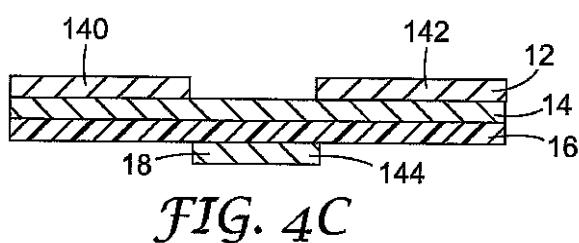

図 4A～4F は、図 1A または 1C の受動的電気物品（内部に抵抗層 14 が 1 つ形成されている）に対して様々な電気素子（特に、多様な組み合わせの受動的回路素子）を形成するパターンを付加する方法の実施例を示している。明快にするため、パターン付きの物品は、図 3A～3C のようなプリント回路基板または可撓性回路に埋め込まれた状態で図示されていない。しかし、図 4A～4F のパターン付き物品がそのような用途を目的としていることは言うまでもない。

## 【0078】

図 4A は、コンデンサと直列のレジスタを示している。抵抗素子は、図 3A を参照しながら説明したように、導電パッド 130 および 132 の間に形成される。容量素子は、図 3B を参照しながら説明したように、導電パッド 132 および 134 の間に形成される。

## 【0079】

図 4B は、コンデンサと直列のレジスタの別の実施形態を示している。抵抗素子および容量素子は、両方とも、導電パッド 136 と 138 の間に形成される。導電パッド 136、138 が互いにオフセットするため、抵抗層 14（これもまた導電性を有するが、基材 12、18 よりも導電性は低い）は、抵抗素子として機能するほか、導電パッド 136 の容量性プレートの延長としても機能する。

## 【0080】

図 4C は、さらに別の抵抗・容量性構造を示している。抵抗素子は、導電パッド 140 および 142 の間に形成される。抵抗材料層 14 はコンデンサの上部電極を形成し、コンデンサの底部電極は導電パッド 144 となっている。

## 【0081】

図 4D は、レジスタと直列のインダクタを示している。誘電素子は導電パッド 146、148 の間に形成され、抵抗素子は導電パッド 148、150 の間に形成される。

## 【0082】

図 4E は、コンデンサと直列のインダクタを示している。誘電素子は導電パッド 152、154 の間に形成され、容量素子は導電パッド 154、156 の間に形成される。

## 【0083】

図 4F は、レジスタおよびコンデンサと直列のインダクタを示している。誘電素子は導電パッド 158、160 の間に形成され、抵抗素子は導電パッド 160、162 の間に形成される。また、容量素子は導電パッド 162 および 166 の間に形成される。抵抗素子、容量素子、誘電素子もまた、必要に応じて互いに並列に接続することができる。

## 【0084】

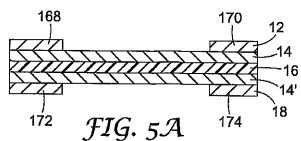

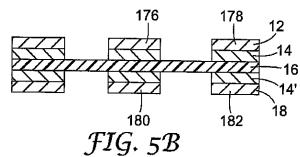

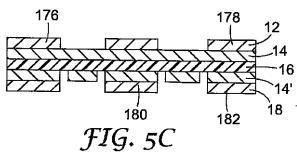

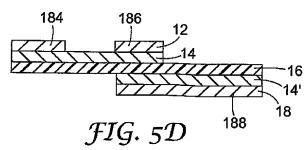

図 5A～5D は、図 1B の受動的電気物品（基材 12、18 のそれぞれに抵抗層 14 が

形成されている)に対して様々な電気素子(特に、多様な組み合わせの受動的回路素子)を形成するパターンを付加する方法の実施例を示している。明快にするため、パターン付きの物品は、図3A~3Cのようなプリント回路基板または可撓性回路に埋め込まれた状態で図示されていない。しかし、図5A~5Dのパターン付き物品がそのような用途を目的としていることは言うまでもない。

【0085】

図5Aは、絶縁層16の両側にレジスタを有する物品を示している。導電パッド168、170間におよび導電パッド172、174間にそれぞれ別の抵抗素子が形成される。この方法で、複数個の受動的素子がプリント回路の同一のX-Y領域内に配置されてよい。これらの抵抗素子は、相互に電気的に絶縁することができる。もしくは、必要に応じて、直列または並列に相互接続することができる。

10

【0086】

図5Bおよび5Cは、絶縁層16の両側にインダクタを有する物品を示している。導電パッド176、178間におよび導電パッド180、182間にそれぞれ別の誘導素子が形成される。図5Cの物品において、抵抗層14、14'は高透過性材料であり、高インダクタンスを実現するために、導電性基材12、18のコイルの間に広げられる。抵抗層14、14'の高透過性材料は、インダクタの導電コイルに対して電気的に接続されるか、もしくは導電コイルから電気的に絶縁することができる。例えば、図5Cは、層12の導電コイルに対して電気的に接続された層14の高透過性材料と、層18の導電コイルから電気的に絶縁された層14'の高透過性材料を示している。

20

【0087】

図5Dは、コンデンサと直列のレジスタを示している。抵抗素子は導電パッド184、186の間に形成され、容量素子は導電パッド186、188の間に形成される。

【0088】

本発明はまた、プリント回路基板または可撓性回路の電気回路として機能する本発明の受動的電気物品を含んだ電気機器をも包含するが、これは本発明の受動的電気物品を含む。電気機器は、いかなる電気機器を含んでもよいが、これら電気機器は通常、容量構成要素または抵抗構成要素を有するプリント回路基板または可撓性回路を使用している。代表的な電気機器としては、携帯電話機、電話機、ファクシミリ、コンピュータ、プリンタ、ペーパージャ、当業者に知られているその他の機器が挙げられる。本発明の受動的電気物品は、スペースがきわめて少ない電気機器において特に有用である。

30

【0089】

本発明は下記の実施例によって例示されるが、これらの実施例において列挙された特定の材料及びその量は、他の諸条件及び詳細と同様に本発明を過度に制限するものと解釈すべきではない。

【実施例】

【0090】

(実施例1)

メチルエチルケトン/メチルイソブチルケトン中の0.3μ分散のチタン酸バリウムは、ポリエステル/ポリアミンコポリマー分散剤を使用して市販のビーズミルにより作成された。チタン酸バリウム対エポキシの容量比率を45:55にするため、十分なエポキシ結合剤溶液(EPON 1001FにEPON 1050を加えたもの)が追加された。結果として得られた分散(固体含有量60%w/w)は、グラビアコーダを使用して、35μ(1オンス)銅箔上にコーティングされた。この銅箔には、事前に1μm未満のドープ白金抵抗層(公称抵抗率1000/平方)でコーティングが施されている。また、このドープ白金抵抗層は、INSITEの商業表記でローム・アンド・ハース・エレクトロニック・マテリアルズ社(Rohm & Haas Electronic Materials)(米国マサチューセッツ州モールバラ(Marlborough, Massachusetts))から販売されている。乾燥後、チタン酸バリウム/エポキシ層は5~6μの厚さとなった。35μ銅箔の第2のサンプルは、抵抗層を持たないものであるが、これにも同一の条件でコーティングが施

40

50

された。2つのコーティングは、約135に設定されたロールラミネーターを使用し、速度 $5.93 \times 10^{-3}$  m/s (14インチ/分 (ipm)) で、コーティング側同士がラミネートされた。ラミネートは、190のオーブンで4時間かけて硬化させられた。

#### 【0091】

硬化ラミネートの接着は、90度剥離試験によって測定された。抵抗材料と誘電体との接着は、少なくとも3.156 kN/m (6ポンド/インチ (pounds per linear inch) (p1i)) であった。抵抗材料とその銅基材との接着も、同様に、少なくとも3.156 kN/m (6p1i) であった。これは、抵抗-誘電体接合面で破損が生じたのに対し、抵抗-銅接合面は破損が生じなかったことによる。誘電体と銅との接着は、約1.578 kN/m (3p1i) であった。硬化ラミネートの接着についても、(プリント回路基板プロセスにおける2つのラミネーション周期をシミュレートするため) 190でさらに4時間焼いた後に試験が実施された。いずれの接合面の接着にも重大な変化はなかった。

10

#### 【0092】

硬化ラミネートの電気特性についても試験が行われた。コンデンサおよびレジスタの構造については、当該技術分野において周知のフォトイソグラフィ方法を使用することにより、導電材料および抵抗材料にパターンが付加された。抵抗および静電容量は、周波数1 kHzでLCRメーターにより測定された。平均約1000/平方の抵抗率が観測された。従って、ラミネートの組み立てプロセスまたはパターニングプロセスによる抵抗率の重大な変化はなかった。静電容量の測定結果は約0.0155 nF/mm<sup>2</sup> (10 nF/in<sup>2</sup>) であった。23 ~ 180の範囲を超えた温度から23に戻したときの静電容量の変化についても測定が行われた。23 ~ 180の範囲を超えた温度における静電容量の増加率は、15%未満であった。サンプルの温度が23に戻ったときは、本質的な静電容量の変化はなかった。

20

#### 【0093】

##### (実施例2)

厚さ5 ~ 6 μmの誘電層で35 μm (1オンス) 銅フォイルをコーティングするために、上記と同一のプロセスおよび材料を使用した。引き続き、これらの層のうち2つは、約135に設定されたホットロールラミネーターを使用し、速度 $5.93 \times 10^{-3}$  m/s (14ipm) で、コーティング側同士がラミネートされた。2つの銅フォイルのうち1つはラミネート構造から剥し取られ、これにより、その銅フォイルの誘電コーティングは別の誘電コーティングされた銅へと移動させられることとなる。誘電コーティングされた銅基材 (この時点の誘電厚さ約10 - 11 μm) は、次に、18 μm (1/2オンス) の銅フォイルにラミネートされた。これには、1 μm未満の、スパッタリングされた、シート抵抗25/平方のニッケル-クロム抵抗材料 (この抵抗材料に誘電側が面する) が使用された。表面に抵抗材料を有する銅フォイルは、グールド・エレクトロニクス社 (Gould Electronics Inc.) (米国アリゾナ州チャンドラー (Chandler, Arizona)) 製のグールドTCR (Gould TCR) 抵抗コンダクタ材料であった。ラミネートは、190で4時間かけて硬化させられた。

30

#### 【0094】

ラミネートの接着は、90度剥離角度によって測定された。抵抗材料と誘電体との接着は、少なくとも3.156 kN/m (6p1i) であった。実施例1の場合のように、抵抗材料とその銅基材との接着も、同様に、少なくとも3.156 kN/m (6p1i) であった。これは、抵抗-誘電体接合面で破損が生じたのに対し、抵抗-銅接合面は破損が生じなかったことによる。銅と誘電体との接着は、約2.104 kN/m (4p1i) であった。硬化ラミネートの接着についても、(プリント回路基板プロセスにおける2つのラミネーション周期をシミュレートするため) 190でさらに4時間焼いた後に試験が実施された。いずれの接合面の接着にも重大な変化はなかった。

40

#### 【0095】

硬化ラミネートの電気特性についても試験が行われた。コンデンサおよびレジスタの構

50

造については、当該技術分野において周知のフォトイソグラフィ方法を使用することにより、導電材料および抵抗材料にパターンが付加された。抵抗および静電容量は、周波数 1 kHz で L C R メーターにより測定された。静電容量の測定結果は約 0.0155 nF / mm<sup>2</sup> (10 nF / in<sup>2</sup>) であった。ラミネートのシート抵抗を測定した結果は 25 / 平方であった。

【0096】

(実施例 3)

実施例 1 および実施例 2 と同一の処方による誘電材料が、35 μm (1 オンス) 銅箔上にコーティングされた。これには、上述の実施例 1 および実施例 2 と類似のプロセスが使用された。ただし、ここでは誘電コーティングの厚さが約 8 μm とされた。この場合、硬化ラミネートは、誘電コーティングを施した銅箔と、35 μm 銅箔とをラミネートして硬化されることにより作成された。なお、35 μm 銅箔は、厚さ 1 μm 未満の平板状ニッケル - リン抵抗材料 (誘電側が抵抗材料に面している) を有し、そのシート抵抗は 25 / 平方であった。表面に抵抗材料を有する銅箔は、オメガ・テクノロジー社 (Ohmega Technologies) (米国カリフォルニア州カルバーシティ (Culver City, California)) 製のオメガ - プライ抵抗容量性マテリアル (OHMEGA-PLY Resistive Capacitive Material) であった。ラミネートは、真空ラミネーションプレスに入れられ、温度 177 、圧力  $2.07 \times 10^6 \text{ N/m}^2$  (300 psi) で、2 時間硬化させられた。

10

【0097】

(実施例 4)

実施例 1 および実施例 2 と同一の処方による誘電材料が、35 μm (1 オンス) 銅箔上にコーティングされた。これには、上述の実施例 1 および実施例 2 と類似のプロセスが使用された。ただし、ここでは誘電コーティングの厚さが約 4 μm とされた。誘電コーティングが施された銅箔は、実施例 3 (誘電材料と抵抗材料) に基づき、抵抗コーティングが施された銅箔にラミネートされた。これには、温度 135 、速度 305 mm / m (12 ipm) 、ロール圧力  $1.03 \times 10^5 \text{ N/m}^2$  (15 psi) のホットロールラミネーターが使用された。元から厚さ 4 μm の誘電体でコーティングされていた銅箔は、180 度の角度で剥し取られ、これにより銅箔から抵抗面へと誘電層が移動させられた。このプロセスは、厚さ 4 μm の誘電体コーティング済み抵抗 - コンダクタ材料シートを 2 枚作成するため、別のサンプルについても繰返された。この 2 枚のシートは、次に、誘電体同士をラミネートされた。これにより、厚さ 8 μm の誘電体と、この誘電体および 2 つの銅箔それぞれの間に位置する抵抗層を作成された。このラミネートは、次に、180 のオーブンで 2 時間かけて硬化させられた。

20

30

【0098】

ラミネートの接着は、90 度剥離角度によって測定された。抵抗材料と誘電体との接着は、少なくとも約 2.367 kN / m (4.5 psi) であった。実施例 1 の場合のように、抵抗材料とその銅基材との接着も、同様に、少なくとも約 2.367 kN / m (4.5 psi) であった。これは、抵抗 - 誘電体接合面で破損が生じたのに対し、抵抗 - 銅接合面では破損が生じなかつたことによる。

40

【0099】

本明細書において特定の実施形態が例示及び説明されてきたが、本発明の範囲から逸脱することなく、多様な代替及び / 又は同等の実施態様が特定の実施形態と置き換えられ得ることは、当業者には明白であろう。本出願は、本明細書で説明された特定の実施形態のいかなる翻案又は変形をも包含すべく意図されている。従って、本発明が請求項及びその同等物によってのみ限定されることを、意図するものである。

【0100】

本発明は、添付の図を参照することによりさらに詳しく説明される。ここでは、幾つかの図にわたって同様の構造に同様の数字が付されている。また、層の厚さは必ずしも縮尺に沿って表されていない。

50

## 【図面の簡単な説明】

## 【0101】

【図1A】コンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能することができる、本発明の受動的電気物品を示す断面図。

【図1B】コンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能することができる、本発明の受動的電気物品を示す断面図。

【図1C】コンデンサ、レジスタ、インダクタ、またはこれらの組み合わせとして機能することができる、本発明の受動的電気物品を示す断面図。

## 【図1D】図1Cにおける電気的絶縁層の拡大図。

【図2A】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。 10

【図2B】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2C】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2D】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2E】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2F】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。 20

【図2G】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2H】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2I】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2J】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2K】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。 30

【図2L】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図2M】本発明の受動的電気物品を使用したレジスタを形成するための代表的なフォトリソグラフィプロセスを示す図。

【図3A】レジスタ（図3A）、コンデンサ（図3Bおよび3C）、インダクタ（図3Dおよび3E）として機能するようにパターンが付加されている、本発明の受動的電気物品が埋め込まれたプリント回路基板の代表的な実施形態を示す図。

【図3B】レジスタ（図3A）、コンデンサ（図3Bおよび3C）、インダクタ（図3Dおよび3E）として機能するようにパターンが付加されている、本発明の受動的電気物品が埋め込まれたプリント回路基板の代表的な実施形態を示す図。 40

【図3C】レジスタ（図3A）、コンデンサ（図3Bおよび3C）、インダクタ（図3Dおよび3E）として機能するようにパターンが付加されている、本発明の受動的電気物品が埋め込まれたプリント回路基板の代表的な実施形態を示す図。

【図3D】レジスタ（図3A）、コンデンサ（図3Bおよび3C）、インダクタ（図3Dおよび3E）として機能するようにパターンが付加されている、本発明の受動的電気物品が埋め込まれたプリント回路基板の代表的な実施形態を示す図。

【図3E】レジスタ（図3A）、コンデンサ（図3Bおよび3C）、インダクタ（図3Dおよび3E）として機能するようにパターンが付加されている、本発明の受動的電気物品が埋め込まれたプリント回路基板の代表的な実施形態を示す図。 50

【図 4 A】本発明の 1 実施形態に従い 1 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。

【図 4 B】本発明の 1 実施形態に従い 1 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。

【図 4 C】本発明の 1 実施形態に従い 1 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。

【図 4 D】本発明の 1 実施形態に従い 1 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。 10

【図 4 E】本発明の 1 実施形態に従い 1 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。

【図 4 F】本発明の 1 実施形態に従い 1 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。

【図 5 A】本発明の 1 実施形態に従い 2 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。 20

【図 5 B】本発明の 1 実施形態に従い 2 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。

【図 5 C】本発明の 1 実施形態に従い 2 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。

【図 5 D】本発明の 1 実施形態に従い 2 つの抵抗層を有する、受動的電気素子の多様な組み合わせとして機能するパターンが付加されている受動的電気物品の代表的な実施形態を示す図。 30

【図 1 A】

FIG. 1A

【図 1 B】

FIG. 1B

【図 1 C】

FIG. 1C

【図 1 D】

FIG. 1D

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

【図 2 C】

FIG. 2C

【図 2 D】

FIG. 2D

【図 2 E】

FIG. 2E

【図 2 F】

FIG. 2F

【図 2 G】

FIG. 2G

FIG. 2H

【図 2 I】

FIG. 2I

FIG. 2J

【図 2 K】

FIG. 2K

【図 2 L】

FIG. 2L

【図 2 M】

FIG. 2M

【図 3 A】

FIG. 3A

【図 3 B】

FIG. 3B

【図 3 C】

FIG. 3C

【図 3 D】

FIG. 3D

【図 3 E】

FIG. 3E

【図 4 B】

FIG. 4B

【図 4 C】

FIG. 4C

【図 4 D】

FIG. 4D

【図 4 A】

FIG. 4A

【図 4 E】

【図 4 F】

【図 5 A】

【図 5 B】

【図 5 C】

【図 5 D】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2006/023998

A. CLASSIFICATION OF SUBJECT MATTER

INV. H05K1/16

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H05K

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the International search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, IBM-TDB, COMPENDEX, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                      | Relevant to claim No. |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y        | WO 00/45624 A (3M INNOVATIVE PROPERTIES CO [US]) 3 August 2000 (2000-08-03)<br>page 5, line 19 - page 6, line 22; figure 1a<br>page 11, line 6 - line 8 | 1-36                  |

| Y        | US 2002/146556 A1 (PANKOW JOEL W [US] ET AL) 10 October 2002 (2002-10-10)<br>paragraph [0013]; figure 1                                                 | 1-36                  |

| Y        | US 6 631 551 B1 (BOWLES PHILIP HARBAUGH [US] ET AL) 14 October 2003 (2003-10-14)<br>column 4, line 11 - line 44; figure 2                               | 1-36                  |

| Y        | JP 2003 200524 A (FURUKAWA CIRCUIT FOIL KK) 15 July 2003 (2003-07-15)<br>abstract                                                                       | 1-36                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the International filing date but later than the priority date claimed

\*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

|                                                                                                                                                                                        |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search                                                                                                                              | Date of mailing of the International search report |

| 10 October 2006                                                                                                                                                                        | 18/10/2006                                         |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5618 Patentlaan 2<br>NL- 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax. (+31-70) 340-3016 | Authorized officer<br>Dobbs, Harvey                |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2006/023998

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                                    | Publication date                                                                                             |

|----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| WO 0045624                             | A 03-08-2000     | AU 4418499 A<br>DE 69920280 D1<br>DE 69920280 T2<br>EP 1153531 A1<br>HK 1043016 A1<br>JP 2002536825 T<br>US 6274224 B1<br>US 2001038906 A1 | 18-08-2000<br>21-10-2004<br>29-09-2005<br>14-11-2001<br>13-05-2005<br>29-10-2002<br>14-08-2001<br>08-11-2001 |

| US 2002146556                          | A1 10-10-2002    | NONE                                                                                                                                       |                                                                                                              |

| US 6631551                             | B1 14-10-2003    | NONE                                                                                                                                       |                                                                                                              |

| JP 2003200524                          | A 15-07-2003     | NONE                                                                                                                                       |                                                                                                              |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,LV,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,L,C,LK,LR,LS,LT,LU,LY,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(74)代理人 100126789

弁理士 後藤 裕子

(72)発明者 ジョエル・エス・ペイファー

アメリカ合衆国 5 5 1 3 3 - 3 4 2 7 ミネソタ州セント・ポール、ポスト・オフィス・ボックス 3

3 4 2 7、スリーエム・センター

(72)発明者 ネルソン・ビー・オブライアン

アメリカ合衆国 5 5 1 2 5 ミネソタ州ウッドベリー、グレンベイ・コート 1 5 1 8 番

F ターム(参考) 4E351 AA03 AA04 AA05 BB03 BB05 BB09 BB24 BB32 BB33 BB35

DD04 DD23 DD56 GG06